Micro Linear Corporation ML6411 Datasheet

September 1999

PRELIMINARY

ML6411

Programmable Video Digitizer

with Selectable Gain and Clamps

GENERAL DESCRIPTION

The ML6411 is a Dual Video A/D converter, incorporating

two input sample and holds, two high speed 8-Bit A/D

converters, programmable gain control, selectable clamps,

multi-phase clocking, and reference voltage generation.

The ML6411 can be used to convert the follo wing analog

signals to digital signals: two composite channels or Svideo channel.

All inputs are provided with appropriate input selectable

clamps to establish DC level. The clamps are full DC

restore circuits with the A-to-D converters in each

respective correction loop. The clamps are selectable to

16, 24, 64, and 128. The programmable gain control

provides various possibilities to select and adjust the gain

via two separate mechanisms: Sync-Suppressed Gain

Control (SGC) for sync suppressed video such as RGB, and

User Gain Control (UGC) for video formats that require

scalable gain settings. Each of these can be programmed

through a serial bus.

FEATURES

■ Complete video digitizer for Y/C and CV video

■ Contains A/D’s with scalable gain, selectable clamps,

and clock generation (programmable via serial bus)

■ Two 8-Bit +/- ½ LSB Differential Non-Linearity with

30MHz guaranteed conversion

■ Two Gain Control Mechanisms for programmable

or sync-suppressed video gain control

■ Selectable Video Clamping: 16, 24, 64, 128

■ Selectable Video Gain: 3dB to –6dB

■ Operating total power dissipation less than 425mW

■ Power do wn mode and T ri-state output control

■ Applications: Video Capture, Video Editing, Video

Cameras, Y/C and CV analog to digital conversion

■ 44-pin TQFP

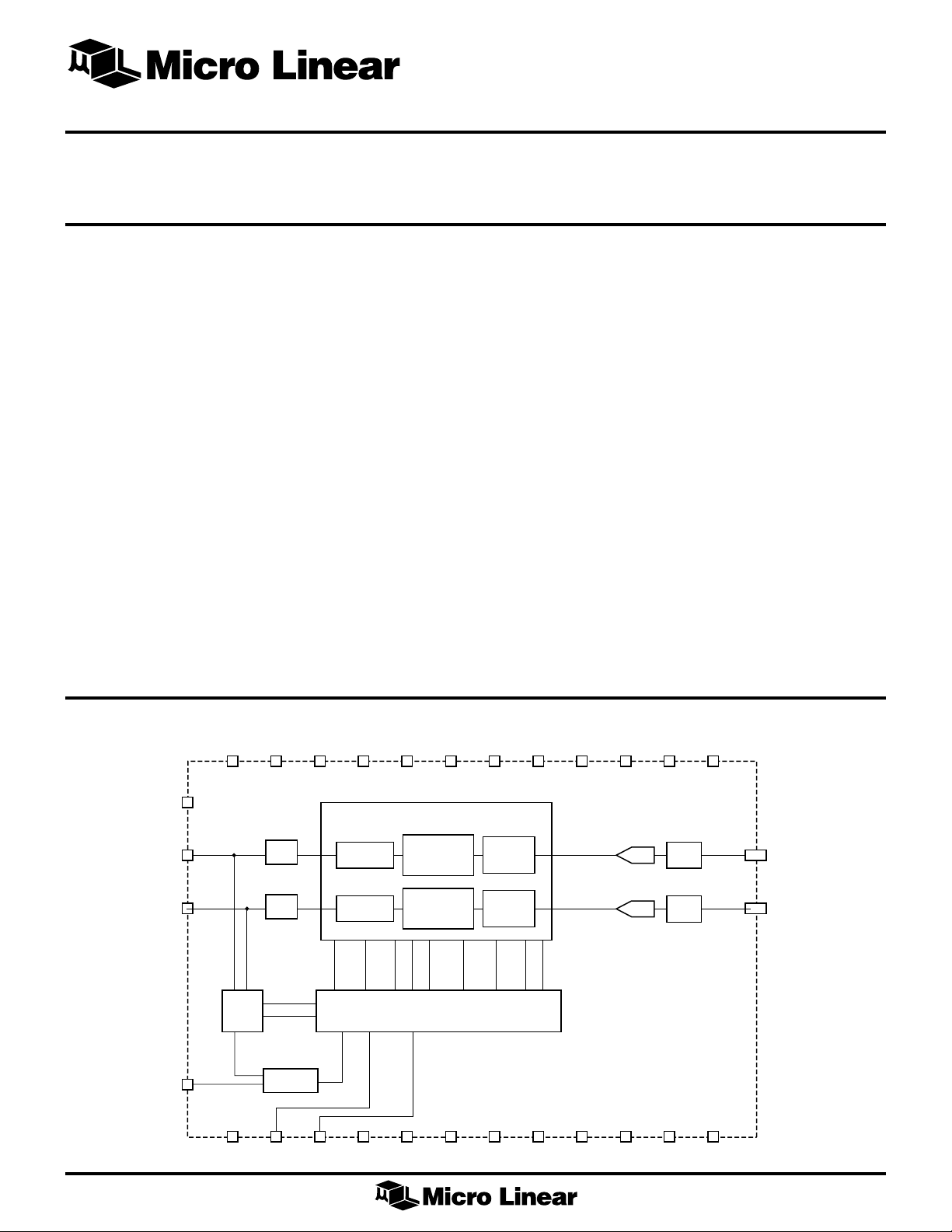

BLOCK DIAGRAM

35

AVCC1

REF1

44

Y/CV1

36

C/CV2

42

CLAMP

SELECT

CLK

14

1

PD

AVCC238AVCC341DVCC17VCCO

CHANNEL A

S/H

CHANNEL B

S/H

CLPA<1:0>

CLPB<1:0>

LEVEL

TIMING

GENERATOR

SCLK19SDAT20REF

GAIN PRESET

GAIN PRESET

STDA <1:0>

CLKDIV

STDB <1:0>

21

IN

APEAK

REF

15 2 33

CLAMP

DGND DVCC

GATE

SGC

SYNC SUPPRESS

GAIN CONTROL

SGC

SYNC SUPPRESS

GAIN CONTROL

BPEAK

22 12 37

OUT

GNA<5:0>

SERIAL BUS

V

CC

GNB<5:0>

AGNDI AGND2

UGC

USER GAIN

CONTROL

UGC

USER GAIN

CONTROL

BOOSTA

32

BOOSTB

CV/S_MODE

40

18

RESET

Y OR CV1

CHANNEL A

C OR CV2

CHANNEL B

43

AGND3

23

OEA

13

GNDO

ADC

ADC

11

OEB

16

DGND

LATCH

Y/CV1

LATCH

C/CV2

39

VINN

A

B

34

NC

OUT

OUT

<7:0>

<7:0>

24:31

3:10

1

ML6411

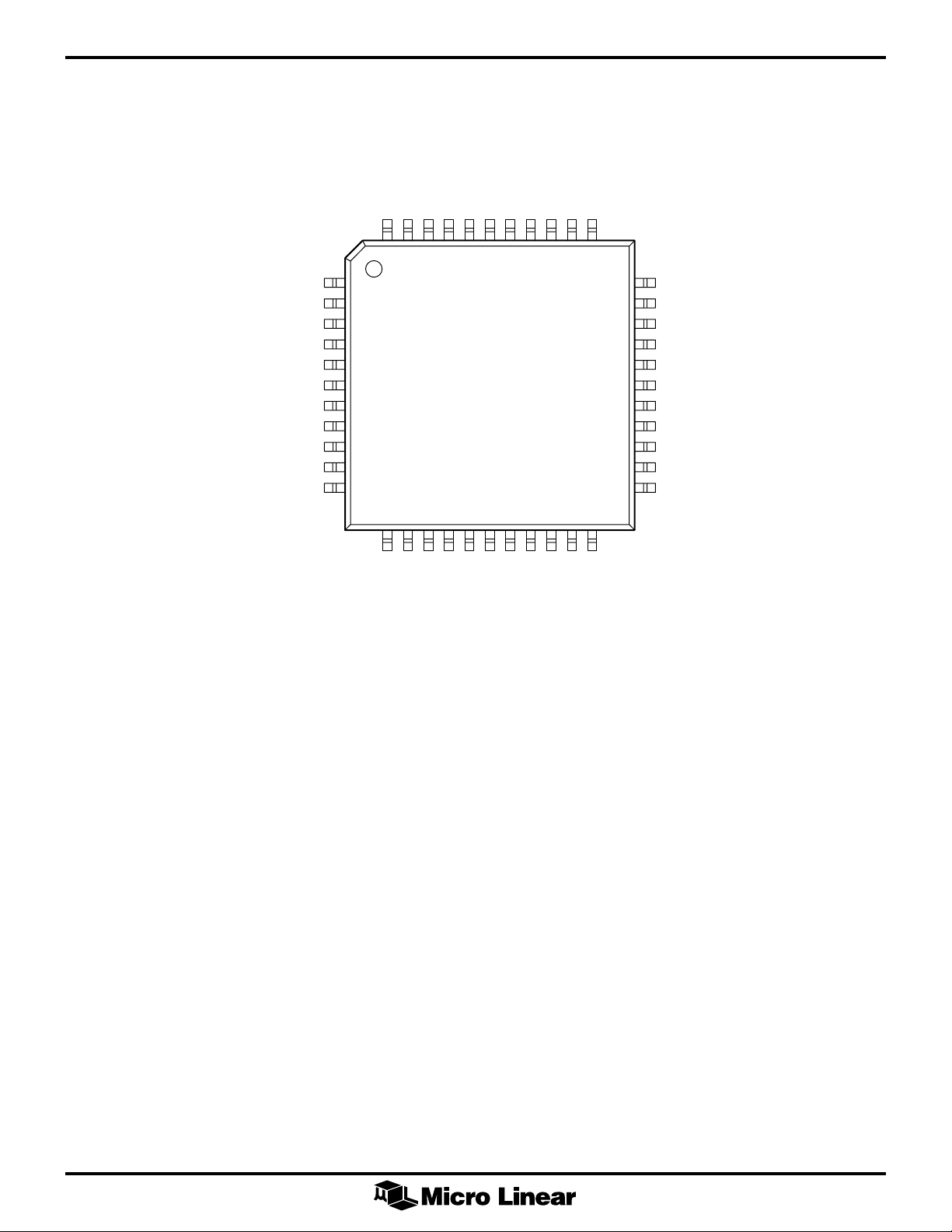

PIN CONFIGURATION

ML6411

44-Pin TQFP (H44-14)

REF1

AGND3

C/CV2

AVCC3

AGND2

VINN

AVCC2

AGND1

Y/CV1

AVCC1

NC

PD

CLAMP GATE

B

OUT

B

OUT

B

OUT

B

OUT

B

OUT

B

OUT

B

OUT

B

OUT

OEB

44 43 42 41 40

1

2

3

0

4

1

5

2

6

3

7

4

8

5

9

6

10

7

11

12 13 14 15 16 17 18 19 20 21 22

CC

CLK

V

GNDO

39 38 37 36 35 34

RESET

DVCC

VCCO

DGND

SCLK

SDAT

IN

REF

OUT

REF

33

32

31

30

29

28

27

26

25

24

23

DGND

DVCC

A

OUT

A

OUT

A

OUT

A

OUT

A

OUT

A

OUT

A

OUT

A

OUT

OEA

7

6

5

4

3

2

1

0

2

PIN DESCRIPTION

ML6411

PIN NAME FUNCTION

1 PD When high, power downs the chip.

TTL compatible

2 Clamp Gate Luma clamp gate input. Clamps to

selected level when high. TTL

compatible

3-10 B

<7:0> Either chroma bits 7 (B

OUT

(B

0 LSB) or composite bits 7 (MSB)

OUT

7MSB) to 0

OUT

to 0 (LSB). TTL compatible

11 OEB Output enable for the BOUT channel.

Active low. TTL compatible

12 VCC Reference voltage. Tie to Digital V

CC

13 GNDO Output ground pin

14 CLK Clock input pin. TTL compatible

15 VCCO Output supply pin

16 DGND Digital ground pin

17 DVCC Digital supply pin

PIN NAME FUNCTION

23 OEA Output enable for the AOUT channel.

Active high. TTL compatible

24-31 A

<7:0> Luma bit 7 (A

OUT

0 (A

7 MSB) thru Luma bit

OUT

0 LSB) outputs or Composite

OUT

bit 7 (MSB) thru Composite bit 0 (LSB)

outputs. TTL compatible

32 DVCC Digital supply pin

33 DGND Digital ground pin

34 NC No connection

35 AVCC1 Analog supply pin

36 Y/CV1 Y or CV (primary composite) input pin

37 AGND1 Analog ground pin

38 AVCC2 Analog supply pin

39 VINN Internal common mode bias of the A/D

40 AGND2 Analog ground pin

18 RESET Resets the control registers to nominal

values. Active HIGH. TTL compatible

input

19 SCLK Control Bus Clock. Address latched on

rising edge, data on falling edge

20 SDA T Control data

21 REF

22 REF

IN

OUT

Internal reference tied to REF

Internal reference tied to REF

OUT

IN

41 AVCC3 Analog supply pin

42 C/CV2 C (modulated chroma) or CV (2

nd

composite for dual channel mode)

input pin

43 AGND3 Analog ground pin

44 REF1 Internal reference. Tie this pin thru

0.1uF capacitor to analog ground for

proper operation

3

ML6411

ABSOLUTE MAXIMUM RATINGS

Absolute maximum ratings are those values beyond which

the device could be permanently damaged. Absolute

OPERATING CONDITIONS

Temperature Range........................................ 0°C to 70°C

Supply Range (AVCC, DVCC, VCCO) ...........4.5V to 5.5V

maximum ratings are stress ratings only and functional

device operation is not implied.

DC Supply Voltage (AVCC, DVCC, VCCO) .... -0.3V to 7V

Analog & Digital Inputs/Outputs ........ -0.3 to AVCC+0.3V

Input Current Per Pin .............................. -25mA to 25mA

Storage Temperature Range...................... –65°C to 150°C

Junction T emperature............................................. 125°C

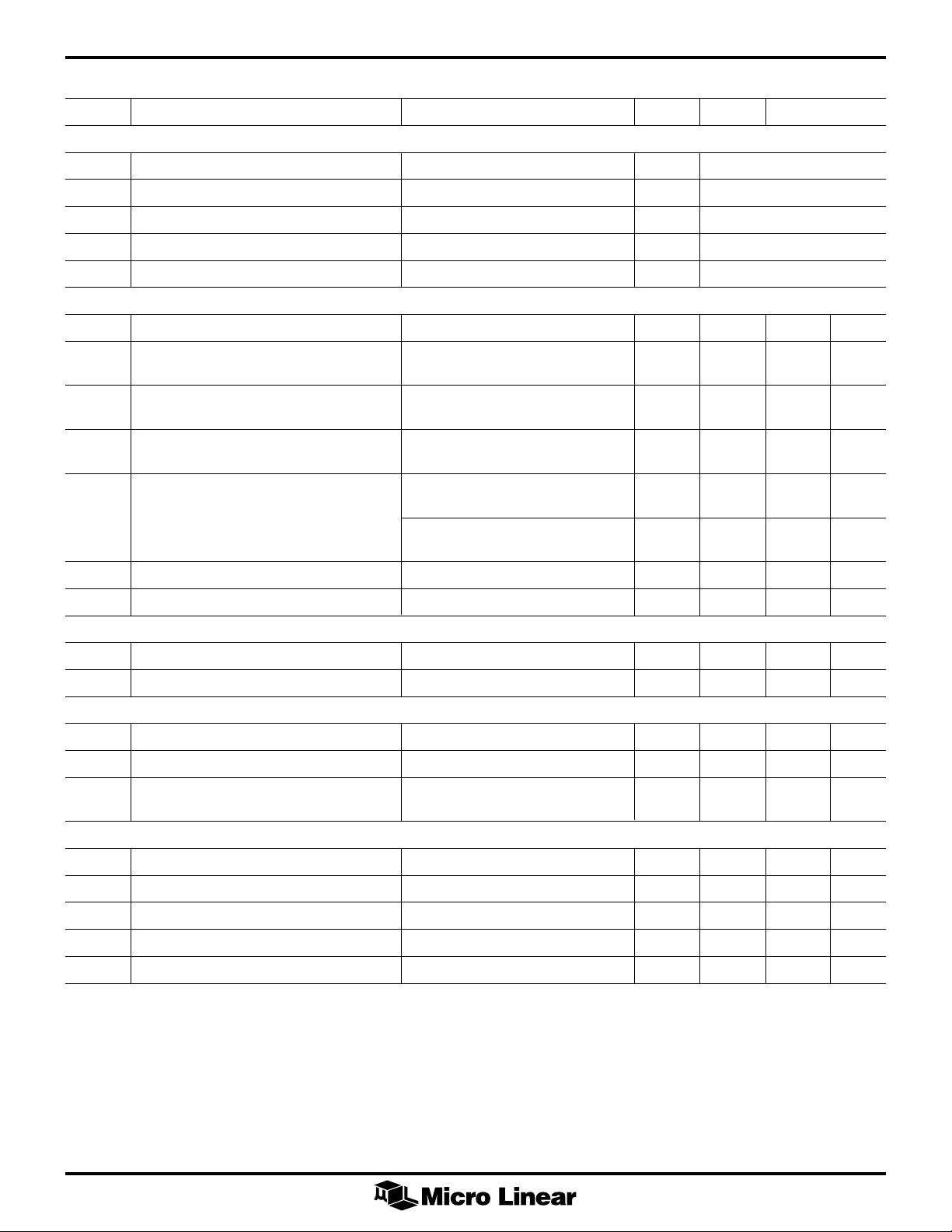

ELECTRICAL CHARACTERISTICS

Unless otherwise specified, AVCC, DVCC, VCCO = 4.5V to 5.5V , TA = Operating Temperature Range (Note 1)

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

POWER CONSUMPTION

P

diss

SUPPLY

AVCC Analog supply voltage 4.5 5.5 V

Max power dissipation Cload = 0pF 425 600 mW

DVCC Digital supply voltage 4.5 5.5 V

VCCO Output supply voltage 4.5 5.5 V

IDD Digital supply current FCLK = 30MHz 17 30 mA

I

I

shut

INPUT SIGNALS (CLK, CLAMP GATE, OEA, OEB)

V

V

I

C

IN1

INPUT SIGNALS (Y / CV1, C / CV2)

V

C

Input Capacitance 3pF

IN2

I

charge

I

disch

Output supply current FCLK=30MHz, VIN=NTSC, 7 mA

O

Shutdown current 5mA

Input Low Voltage 0 0.8 V

IL

Input High Voltage 2.4 DV

IH

High level Input Current DVCC - 0.1V -5 5 µA

IL

Input Capacitance 3pF

Input Voltage Peak-to-peak for 2V 1.0 2.0 3.0 V

IN

Clamp Charge Current Clamp Gate = High, 700 µA

Clamp Discharge Current Clamp Gate = High, –700 µA

40IRE modulated rate, Cload=0pF

CC

Peak-to-peak for 1V 0.5 1.0 1.5 V

Digital Output < Clamp level

Digital Output > Clamp level

V

A TO D CONVERTER OUTPUTS (A

Low level output voltage Io = 2mA 0 0.6 V

High level output voltage 2.4 VCCO

Leakage current Tri-state mode -20 20 µA

4

OUT

<7:0>, B

OUT

<7:0>)

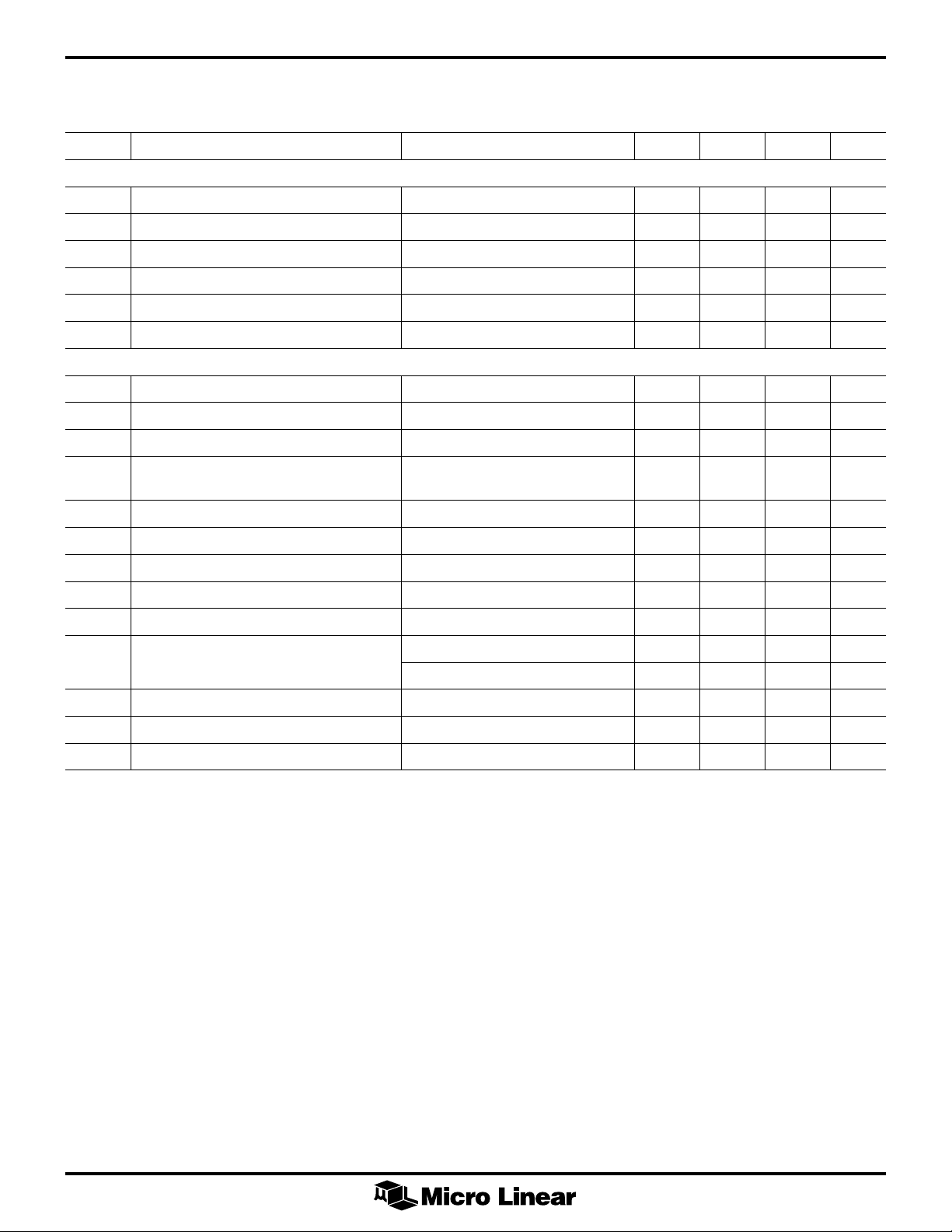

ML6411

ELECTRICAL CHARACTERISTICS (Continued)

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

SWITCHING CHARACTERISTICS

FCLK Clock input max frequency 30 MHz

T

cph

T

Clock input min high time See Figure 2 15 ns

Clock input min low time See Figure 2 15 ns

cpl

Clamp Gate Width VIN magnitude 2V max 1.5 µs

Clamp Gate Width VIN magnitude > 2V 3.5 µs

ANALOG SIGNAL PROCESSING

Y/C Gain Match CGAIN1 = CGAIN2 = 0 1.01 V/V

Chroma Crosstalk Y

Differential Gain V

Differential Phase V

Signal to Noise Ratio V

Distortion VIN = 2V, 10MHz, FCLK = 20MHz 0.3 %

SFDR VIN = 2V, 10MHz, FCLK = 20MHz 54 dB

TRANSFER FUNCTION

= 5MHz and CIN = at DC; –60 dB

IN

or YIN = at DC and CIN = 5MHz

= NTSC 40 IRE modulated ramp 2 %

IN

FCLK = 27 MHz

= NTSC 40 IRE modulated ramp 1 degree

IN

FCLK = 27 MHz

= 2V, 10MHz sinewave, 48 dB

IN

FCLK = 20MHz

VIN = 2V, 10MHz sinewave, 45 dB

FCLK = 30MHz

DC integral linearity @ 27MHz ±0.8 LSB

DC differential linearity @ 27MHz ±0.5 LSB

GAIN CONTROL

G

Gain accuracy of UGC for a given gain level Input = 1V

RES

P-P or 2VP-P

Absolute gain error 5%

Gain accuracy for standard preset gain, 1 %

G

PRESET

OUTPUT TIMING

t

t

ho

t

do

t

t

od

Note 1: Limits are guaranteed by 100% testing, sampling, or correlation with worst-case test conditions.

Note 2: Volt Peak-to-Peak = V

Sampling delay See Figure 2 8 ns

ds

Output hold time See Figure 2 10 ns

Output delay time See Figure 2 12 ns

Output enable time See Figure 2 5 ns

oe

Output disable time See Figure 2 5 ns

P-P

(See Note 2) -30mV 30mV %

5

ML6411

SERIAL BUS

Unless otherwise specified, AVCC, DVCC, VCCO = 4.5V to 5.5V , TA = Operating Temperature Range (Note 1)

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

INPUT (SDAT)

V

V

I

I

Z

C

Low Level Input Voltage 0 0.8 V

IL

High Level Input Voltage VCC – 0.8 V

IH

Low Level Input Current VIN = 0V 1.0 mA

IL

High Level Input Current VIN = DV

IH

Input Impedance f

IN

Input Capacitance 2pF

IN

SYSTEM TIMING (SCLK)

f

CLOCKSCLK

V

HYS

t

SPIKE

t

WAIT

t

HD/START

t

SU/START

t

LOW

t

HI

t

HD/DATA

t

SU/DATA

Frequency 100 kHz

Input Hysteresis 0.2 V

Spike Suppression Max Length for Zero Response 50 ns

Wait Time From STOP to START

On S

DATA

Hold Time for START On S

Setup Time for START On S

Min LOW Time On S

Min HIGH Time On S

Hold Time On S

Setup Time On Fast mode 100 ns

DATA

CLK

CLK

DATA

DATA

CC

CC

= 100kHz 1 MW

CLK

1.0 mA

1.3 µs

0.6 µs

0.6 µs

1.3 µs

0.6 µs

5.0 µs

Slow mode 250 ns

V

t

LH

t

HL

t

SU/STOP

Note 1: Limits are guaranteed by 100% testing, sampling, or correlation with worst case test conditions.

Note 2: All specifications include reconstruction filter and line driver.

Note 3: Normalized to burst.

Rise Time for S

Fall Time for S

CLK

CLK

& S

& S

DATA

DATA

Setup Time for STOP On S

DATA

30 300 ns

30 300 ns

0.6 µs

6

FUNCTIONAL DESCRIPTION

ML6411

GENERAL

The Univ ersal Video Digitizer is a single-chip Video A/D

converter with an analog front end which is intended for

analog to digital conversion of 2V peak-to-peak (V

1V

signals at rates up to 30 MSPS through a high

P-P

P-P

) or

performance A/D with ±½ DNL performance. It forms a

complete solution for data conversion of dual CV and Y/C

signals including gain settings and clamp settings by

incorporating clamps, user selectable gain controls (UGC

and SGC), bias and clock generation.

The ML6411 consist of two video clamps, two sample and

hold amplifiers, two three-stage pipeline A/D converters,

digital error correction circuitry, selectable clamps,

programmable gain control, bias voltage generation and

clock generation. The operating power dissipation is

425mW typical.

INPUT FOR VARIOUS VIDEO MODES

The ML6411 can digitize various analog video inputs:

S-Video (Y/C), or composite video (CV). Again, for each

video channel, the gain and clamps can be selected.

A description of each of these modes is described

below. The Table 1 below provides a summary of the

various modes.

Dual Channel Composite Video (CV1 and CV2) Mode

Control (UGC). Standard gain selection can also be

chosen using the preset gain modes for 2V

For 1V

signals, the preset gain selection mode is not

P-P

signals only.

P-P

available; however the UGC functions can be used to

select gain values. The preset gain modes are for typical

NTSC or PAL S-Video and are selectable via serial bus

through the STDA<1:0> and STDB<1:0> (Register B , Bits

B4, B3, B2, and B1) bits. When using the preset gain

mode, the output signals are enhanced by amplifying the

input signal by the value of G

(see Table 2). In

PRESET

addition, the clamp levels can be selected for either

channel for 16, 24, 64, and 128 binary levels (depending

on the channel 24 not av ailable for C-c hannel) via the

serial bus through the CLPA<1:0> and CLPB<1:0> bits (see

Table 3).

Input Voltage Selection

The ML6411 can support 1V

and 2V

P-P

input video.

P-P

Selection for the voltage input is programmed via control

register on the APEAK and BPEAK bits, A channel and B

channel, respectively (see Table 7).

GAIN SELECTION CONTROL (UGC AND SGC)

There are two separ ate control mechanisms that can be

used to scale gain settings for the incoming video format:

User Gain Control (UGC) and Sync-suppressed Gain

Control (SGC).

The composite input channels are provided through the Y/

CV1 (A channel) and C/CV2 (B channel) pins. T o activate

this mode, the CV/S_Mode Bit (Register D, Bit D3) must set

HIGH (D3=1). This mode is selectable via serial bus. In

this mode, the two S&H circuits for each channel can be

clocked up to 30MHz. Each CV channel can be then

scaled for a desired gain setting using the User Gain

Control (UGC). Standard gain selection can also be

chosen using the preset gain modes for 2V

For 1V

signals, the preset gain selection mode is not

P-P

signals only.

P-P

available; however the UGC functions can be used to

select gain values. The preset gain modes are for typical

NTSC or PAL composite video and are selectable via serial

bus through the STDA<1:0> and STDB<1:0> (Register B ,

Bits B4, B3, B2, and B1) bits. When using the preset gain

mode, the output signals are enhanced by amplifying the

input signal by the value of G

(see Table 2). In

PRESET

addition, the clamp levels can be selected for either

channel for 16, 24, 64, and 128 binary levels (depending

on the channel) via the serial bus through the CLPA<1:0>

and CLPB<1:0> bits (see Table 3).

S-Video (Y / C) Mode

The input channels are pro vided through the Y/CV1 (A

channel) and C/CV2 (B channel) pins. To activate this

mode, the CV/S_Mode Bit (Register D, Bit D3) must be set

LOW (D3=0). This mode is selectable via serial bus. In this

mode, the two S&H circuits for each channel can be

clocked up to 30MHz. Each channel (Y and C) can be

then scaled for a desired gain setting using the User Gain

User Gain Control (UGC)

The user gain control function is achiev ed through a

variation of the full scale range of the A/D con v erters. This

will provide the user with approximately +/-3dB gain

variation as needed. Y reference and C reference are

supplied by two independent DACs. The user can adjust

the gain of each ADC independently providing the 6-Bit

code for the gain control through serial interface for each

A/D. Each step change can increment or decrement the

gain by 3% and allows for up to 64 different gain setting

levels per channel. The UGC can be used for both 1V and

2V

inputs. When using the UGC mode, the output

P-P

signals are enhanced by amplifying the input signal by the

value of G

. Table 4 provides a summary of the possible

UGC

incremental ranges. The gain accuracy of the UGC for

each of the 64 levels is +/-1.5%. The UGC gain settings

are selected via serial bus by programming Registers C, D,

and E on the GNA<5:0> bits for the A-channel and

GNB<5:0> bits for the B-channel.

Unity gain is set at default for GNA<5:0> = 100,000 and

GNB<5:0> = 100,000. For v alues of GNA<5:0> and

GNB<5:0> from 100,000 to 111,111, the gain increases

monotonically from 0dB (unity gain) to almost 3dB

(actually 1.48x), while from 100,000 to 000,000 the gain

decreases monotonically from 0dB (unity gain) to –3dB

(0.5x). Note that Table 4 provides only approximation of

gain values: actual gain values can vary from device to

device.

7

ML6411

FUNCTIONAL DESCRIPTION (Continued)

Sync-suppress Gain Control (SGC)

This control function is used for video where the sync

signal is suppressed (i.e., chroma signal). In which case,

the SGC can be activated to provide a 25% gain boost to

each channel (Y and C). The SGC is activated via serial bus

(Register D, Bits D1 and D2), also called the BOOSTA and

BOOSTB programming bits. In the SGC mode, the output

signals are enhanced by amplifying the input signal by the

value of G

(see Table 5).

SGC

Using The Gain Control Blocks Together

The UGC combined provides digital gain control data to a

variable gain control circuit while the SGC is directly in

the A/D processing path. Hence the UGC sets variable

gain control of the A/D.

When the UGC and the SGC are enabled. In this mode,

the output gain is the combination of the different gain

setting mechanisms:

For 1V

signals,

P-P

Equation 1: Output Gain = [<Input Signal> x

G

UGC

For 2V

x G

P-P

] + Clamp Level

SGC

signals,

Equation 2: Output Gain = [<Input Signal> x

G

x G

UGC

Note that separate G

SGC

UGC

x G

PRESET

, G

] + Clamp Level

, and G

SGC

PRESET

values are

available for both c hannels A and B. There are up to 640

combinations of gain settings possible.

WARNING

Note that it is possible to exceed the output voltage ranges

for standard video using the combination of the gain

setting mechanisms on the input signal. The user should

take precaution in understanding the gain limits necessary

and make the proper selection for each of the gain

mechanism.

A/D CONVERTER

cycle later, after the subtraction/amplification of the first

stage has settled. The third stage A/D performs the

conversion after another one-half cycle dela y, when the

second stage has settled. Error correction is then

performed and, one clock cycle later, data is transferred to

the output latch. This creates a 3 clock latency.

INPUT SAMPLE AND HOLD

The input sample and hold consist of a bottom plate

sampling capacitor feedback amplifier. The input

capacitance is 0.4pF, plus transmission gate. The input to

the sample and hold is driven differentially. The sample

and hold samples the input signal during the positive half

cycle of the input clock, and holds the last v alue of the

input during the negative half cycle of the input cloc k. The

settling time of the amplifier is less than 10nS.

INPUT COUPLING AND DC CLAMP PROGRAM

SELECTION

All inputs are A C coupled into the positi v e sampling

capacitor of the sample and hold. Each input capacitor

becomes the integrating component for the DC restore

clamps. The direction of clamp current depends on the

data at the A/D output during the clamp gating pulse. For

the color channel (i.e. C in Y/C mode) the clamp level is

128. If the code is above this number during the gate

pulse, the current source will sink current from the input

capacitor in order to drive the input voltage lo wer.

Otherwise, the current source will source current to raise

the input voltage. Clamp currents are shown in Table 6.

The clamp values of 16, 24, 64, 128 can be select via

register program (Register A and B) through the serial bus.

Note that there is no Level 24 in the B channel. The

CLPA<1:0> controls the clamp settings for the

A-channel, while the CLPB<1:0> controls the clamp

settings for the B-channel. For example, clamp values can

be selected independently for the chroma channel in Y/C

mode (CLPB<1:0>). Once the clamp settings are selected,

the clamps are active when the ClampGate is asserted

HIGH. The ClampGate signal is an external signal provided

by a genlock/sync cloc k device that is genloc ked to the

horizontal sync of the video input. T he ML6431 can be used

to generate the ClampGate signal (see Application Section).

The A/D conversion is performed via a three stage pipeline

architecture. The first two stages quantize their input signal

to the three bits, then subtract the result from the input and

amplify by a factor of four. This creates a residue signal

which spans the full scale range of the following converter.

The subtraction and amplification is performed via a

bottom plate sampling capacitor feedback amplifier,

similar to the input sample and hold. The third stage

quantizes the signal to four bits. One bit from each of the

last two stages is used for error correction.

The first stage A/D performs the conversion at the end of

the sample and holds period, approximately one-half

8

SERIAL PROGRAM

The ML6411 can be register programmed through the

serial bus. Clamping and gain setting can be selected for

various video formats. This serial bus is a standard threepin interface with data, clock, and ground. See Timing

Control information. Table 7 provides a description the

Register information. Please see section “Input Coupling

and DC Clamp Program Selection” and “Gain Select

Control”.

Loading...

Loading...