Micro Linear Corporation ML4658CP, ML4658CQ Datasheet

November 1998

ML4658

10BASE-T Transceiver

GENERAL DESCRIPTION

The ML4658 10BASE-T Transceiver is a single chip cable

line driver/receiver that provides all of the functionality

required to implement both an internal and external IEEE

802.3 10BASE-T MAU. This part offers a standard IEEE

802.3 AU interface that allows it to directly connect to

industry standard manchester encoder/decoder chips or to

an AUI cable.

The ML4658 requires a minimal number of external

components, and is compliant to the IEEE 802.3 10BASE-T

standard. The differential current driven transmitter offers

superior performance because of its highly symetrical

switching. This results in low RFI noise and low jitter.

The Transceiver easily interfaces to 100Ω unshielded

twisted pair cable, 150Ω shielded twisted pair cable, or a

range of other characteristic impedances by simply

changing one external resistor. Jabber, Link Test, and SQE

Test are fully integrated onto the chip with enable/disable

options. A polarity detection status pin, which can drive

an LED, is provided for receive data, and the ML4658

offers automatic polarity correction.

BLOCK DIAGRAM

FEATURES

■ Complete implementation of IEEE 802.3 10BASE-T

Medium Attachment Unit (MAU)

■ Incorporates an AU interface for use in an external

MAU or internal MAU

■ Single 5V supply ±10%

■ No crystal or clock input

■ Current Driven Output for low RFI noise and low jitter

■ Capable of driving 100Ω unshielded twisted pair cable

or 150Ω shielded twisted pair cable

■ Polarity detect status pin capable of driving an LED

■ Automatic Polarity Correction

■ On-chip Jabber logic, Link Test, and SQE test with

enable/disable option

■ Provides six network status LED ouput pins

Tx+

Tx–

COL+

COL–

Rx+

Rx–

AUI

RECEIVER

TRANSMIT

SQUELCH

AUI

DRIVER

AUI

DRIVER

GND

V

CC

SQEN/LTD/JABD

10MHz GATED

OSCILLATOR

LOOPBACK

MUX

(

5V)

5V

SQE

RRSET

5V

RTSET

LINK PULSE

TxTP+

PRE-EQUALIZED

TRANSMIT DRIVER

JABBER

RECEIVE

SQUELCH

LINE

RECEIVER

Tx

Rx

LINK TEST

RECEIVE LOGIC

LED DRIVERS

CLSN JAB RCV LTFXMT POLRD

AUTOMATIC

POLARITY

CORRECTION

TxTP–

TxCAP0

TxCAP1

RxTP+

RxTP–

BIAS

1

ML4658

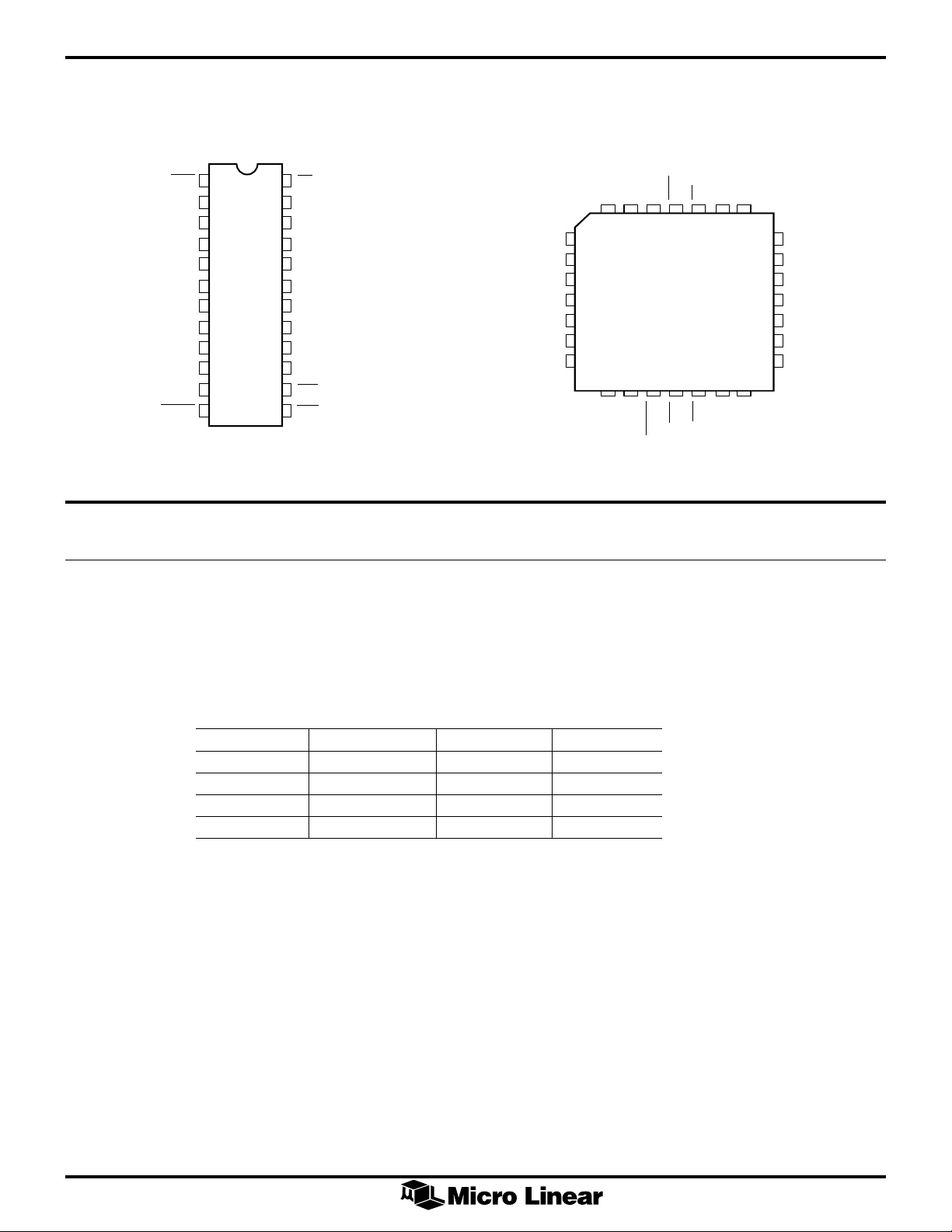

PIN CONFIGURATION

ML4658

24-Pin DIP

ML4658

28-Pin PCC

CLSN

COL+

COL–

SQEN/LTD/JABD

Rx+

Rx–

V

CC

Tx+

Tx–

RTSET

RRSET

POLRD

1

2

3

4

5

6

7

8

9

10

11

12

TOP VIEW

JAB

24

COL–

BIAS

23

RxTP+

22

RxTP–

21

LTF

20

TxCAP0

19

TxCAP1

18

GND

17

TxTP+

16

TxTP–

15

RCV

14

XMT

13

NC

Rx+

Rx–

V

V

Tx+

Tx–

CC

CC

SQEN/LTD/JABD

4 3 2 1 28 27 26

5

6

7

8

9

10

11

12 13 14 15 16 17 18

RTSET

COL+

RRSET

POLRD

TOP VIEW

CLSN

XMT

JAB

RCV

BIAS

TxTP–

RxTP+

25

24

23

22

21

20

19

TxTP+

RxTP–

LTF

NC

TxCAP0

TxCAP1

GND

GND

PIN DESCRIPTION (DIP)

PIN# NAME FUNCTION

1 CLSN Indicates that a collision is taking place. Active low LED driver, open collector. Event is extended

100ms for visibility.

2 COL+ Gated 10MHz signal used to indicate a collision, SQE test, or jabber. Balanced differential

3 COL– line driver outputs that meet AU interface specifications. AC or DC coupled.

4 SQEN/LTD/ SQE Test Enable, Link Test Disabled, Jabber Disabled. This input uses four voltage levels to

JABD configure the chip as shown in Table 1.

Table 1. SQEN/LTD/JABD Pin Configuration

Pin SQE Test Link Test Jabber

0V (GND) Disabled Enabled Enabled

1.2V Disabled Disabled Disabled

BIAS Enabled Disabled Enabled

5V (VCC) Enabled Enabled Enabled

When link test is disabled, no link pulses are transmitted, and the transmitter and receiver will not be

disabled as a result of a loss of receive link pulses. When Jabber is disabled the transmitter can

transmit continuously without interruption, and the collision oscillator will not be activated.

5 Rx+ Manchester encoded receive data output to the local device. Balanced differential line driver outputs

6 Rx– that meet AU interface specifications. AC or DC coupled.

7V

CC

5 Volt power input.

8 Tx+ Balanced differential line receiver inputs that meet AU interface specifications. These inputs may be

9 Tx– AC or DC coupled. When AC coupled, the BIAS pin is used to set the common mode voltage. Signals

meeting the transmitter squelch input requirements are pre-equalized and output on TxTP+ and TxTP–.

10 RTSET When using 100Ω unshielded twisted pair, a 220Ω resistor is tied between this pin and VCC. When

using 150Ω shielded twisted pair, a 330Ω resistor is tied between this pin and VCC.

1 1 RRSET A 1% 61.9KΩ resistor tied from this pin to VCC is used for internal biasing.

2

ML4658

PIN DESCRIPTION (DIP)

PIN# NAME FUNCTION

12 POLRD Receive Polarity status. Active low LED Driver, open collector output. Indicates the polarity of the

receive twisted pair regardless of auto polarity correction. When this pin is high, the receive polarity

is correct, and when this pin is low the receive polarity is reversed.

13 XMT Indicates that transmission is taking place on the TxTP+, TxTP– pair. Active low LED driver, open

collector. It is extended 100ms for visibility.

14 RCV Indicates that the transceiver has unsquelched and is receiving data from the twisted pair. Active low

LED driver, open collector. It is extended 100ms for visibility.

15 TxTP– Pre-equalized differential balanced current driven output. These ouputs are connected to a balanced

16 TxTP+ transmit output filter which drives the twisted pair cable through pulse transformers. The output current

is set with an external resistor connected to RTSET allowing the chip to drive 100Ω unshielded twisted

pair, 150Ω shielded twisted pair cables or a range of other characteristic impedances.

17 G N D Ground reference.

18 TxCAP1 An external capacitor of 330pF is tied between these two pins to set the pulse width for the pre-

19 TxCAP0 equalization on the transmitter. If these two pins are shorted together, no pre-equalization occurs.

20 LTF Link Test Fail. Active high. Normally this pin is low, indicating that the link is operational. If the link

goes down resulting from the absence of link pulses or frames being received, the chip will go into

the Link Test Fail state and bring LTF high. In the Link Test Fail state, both the transmitter and receiver

are disabled, however link pulses are still sent. A station that only has access to the AUI can detect a

Link Test Fail by the absence of loopback. This pin is low when the Link Test is disabled. Open

collector LED output.

(Continued)

21 RxTP– Twisted Pair receive data input. When this signal exceeds the receive squelch requirements the

receive

22 RxTP+ data is buffered and sent to the Rx± outputs.

23 BIAS Bias voltage, output. Used to bias the receive twisted pair inputs as well as the Tx± inputs when they

are AC coupled.

24 JAB Open collector TTL output capable of driving an LED. When in the Jabber state, this pin will be low

and the transmitter will be disabled. In the Jabber “OK” state this pin will be high.

3

ML4658

ABSOLUTE MAXIMUM RATINGS (Note 1)

Power Supply Voltage Range

V

...............................................................................–0.3 to 6V

CC

Input Voltage Range

Digital Inputs (SQEN, LTD)........................ –0.3 to V

Tx+, Tx–, RxTP+, RxTP– ............................ –0.3 to V

CC

CC

OPERATING CONDITIONS

Supply Voltage (VCC).........................................5V ±10%

LED on Current....................................................... 10mA

RRSET ......................................................... 61.9KΩ ±1%

RTSET ............................................................ 220Ω ±1%

TxC AP....................................................................330pF

Input Current

RRSET, RTSET, JAB, CLSN, XMT, RCV, LTF .......... 60mA

Output Current

TxTP+, TxTP–...................................................... 80mA

Storage Temperature................................ –65°C to 150°C

Lead Temperature (Soldering 10 sec.) .....................260°C

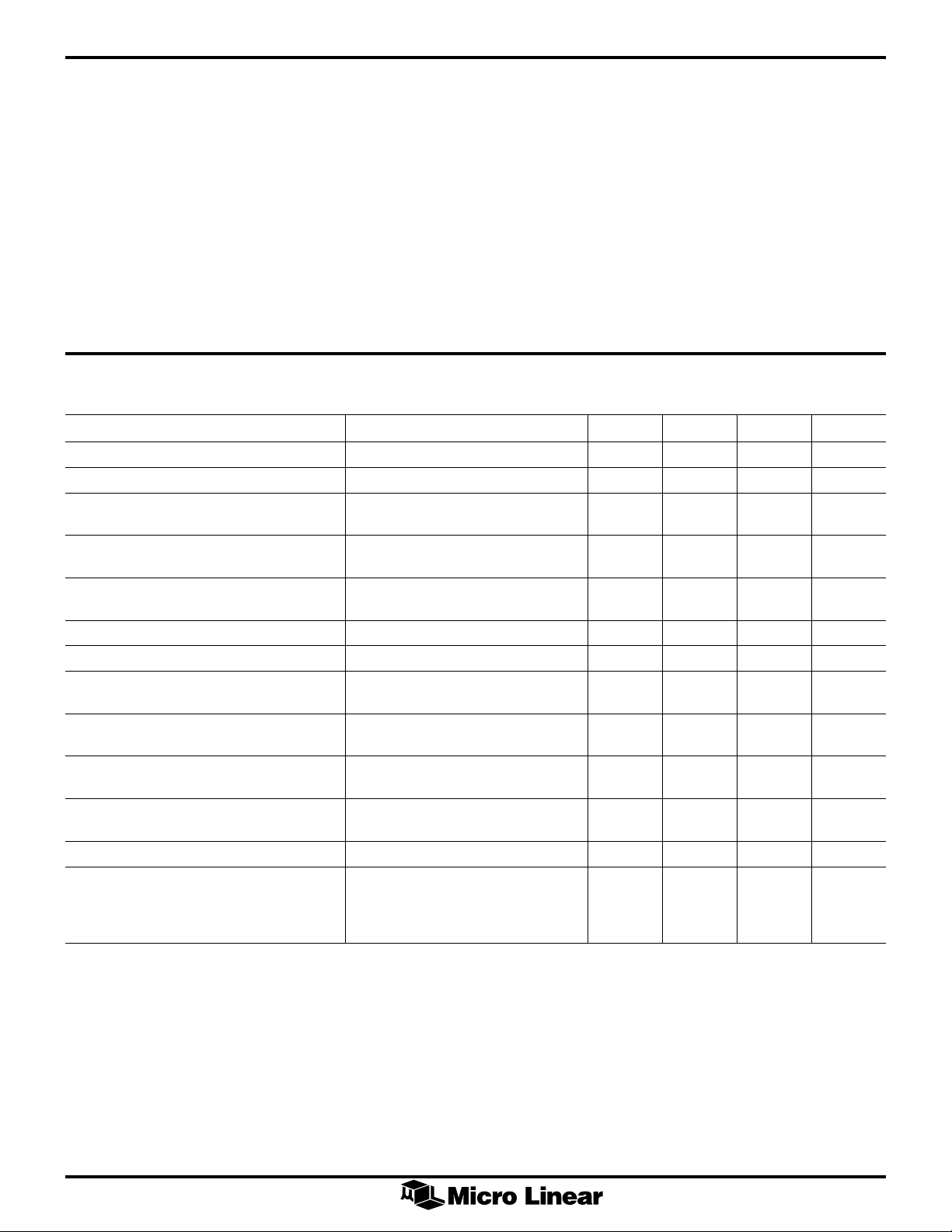

ELECTRICAL CHARACTERISTICS

Unless otherwise specified, TA = 0°C to 70°C (Note 3), VCC = 5V ±10% (Note 2)

PARAMETER CONDITIONS MIN TYP MAX UNITS

Power Supply Current ICC (Note 4) VCC = 5V 14 0 mA

LED Drivers: V

Transmit Peak Output Current RTSET = 220Ω 42 mA

Transmit Squelch Voltage Level

(Tx+, Tx–) –170 mV

Differential Input Voltage

(RxTP+, RxTP–) ±0.300 ±3.1 V

Receiver Input Resistance 10 kΩ

SQEN/LTD/JABD Input Resistance 12 kΩ

Receive Squelch Voltage Level

(RxTP+, RxTP–) 300 450 585 mV-p

Differential Output Voltage

(Rx±, COL±) ±550 ±1200 mV

Common Mode Output Voltage

(Rx±, COL±) 4.0 V

Differential Output Voltage Imbalance

(Rx±, COL±) 2 ±40 mV

BIAS Voltage 3.2 V

SQEN/LTD/JABD SQE TEST disabled 0.3 V

OL

RL = 510Ω (Note 5) 0.8 V

(Note 6)

All disabled 1.1 1.4

Link Test Disabled BIAS – 0.15 BIAS + 0.15

All Enabled VCC – 0.05V

Note 1: Absolute maximum ratings are limits beyond which the life of the integrated circuit may be impaired. All voltages unless otherwise specified are measured with

respect to ground.

Note 2: Limits are guaranteed by 100% testing, sampling, or correlation with worst-case test conditions.

Note 3: Low Duty cycle pulse testing is performed at T

Note 4: This does not include the current from the AUI pull down resistors, the transmit pins TxTP+ and TxTP– or the LED output pins.

Note 5: LED drivers can sink up to 20mA, but VOL will be higher.

Note 6: This current will result in a 2.5V peak output voltage on unshielded twisted pair cable when connected through an external filter and transformer as shown in Figure 12.

.

A

4

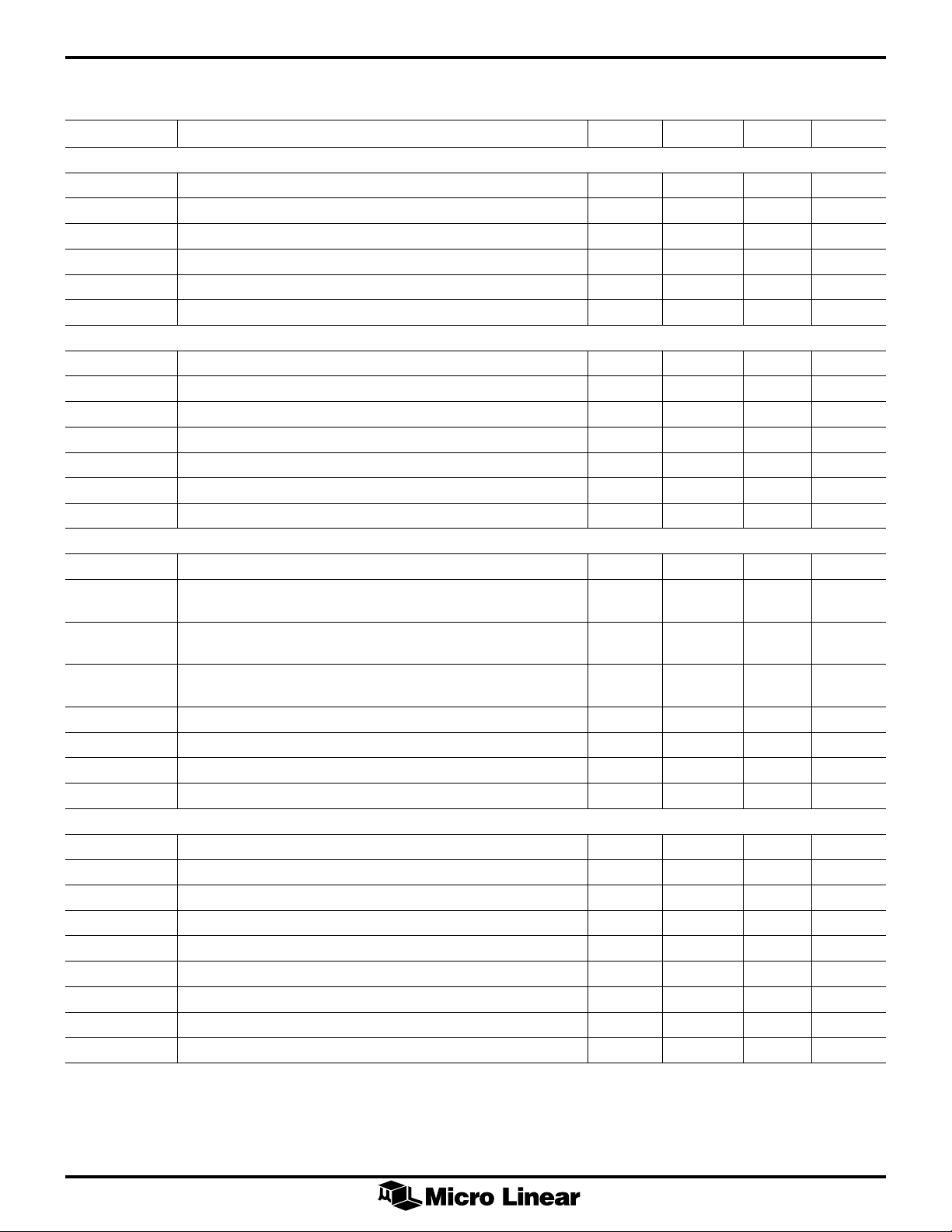

ML4658

ELECTRICAL CHARACTERISTICS (Continued)

AC ELECTRICAL CHARACTERISTICS

SYMBOL PARAMETER MIN TYP MAX UNITS

Transmit

t

TXNPW

t

TXFPW

t

TXLP

t

TXODY

t

TXSDY

t

TXJ

Receive

t

RXODY

t

RXTDY

t

RXFX

t

RXSDY

t

RXJ

t

AR

t

AF

Collision

t

CPSQE

t

TXRX

t

SQEXR

t

SQEXT

t

CLF

t

CLPDC

t

SQEDY

t

SQETD

Jabber, Link Test and LED Timing

t

JAD

t

JRT

t

JSQE

t

LLT

t

LTN

t

LTX

t

TLP

t

LTPW

t

LEDT

Transmit Turn-On Pulse Width 20 n s

Transmit Turn-Off Pulse Width 18 0 ns

Transmit Loopback Startup Delay 200 ns

Tranmitter Turn-On Delay 200 ns

Transmit Steady State Prop. Delay 15 100 ns

Transmitter Jitter ±2 ±3.5 ns

Receive Turn-On Delay if Transmit is Idle 420 500 ns

Receive Turn-On Delay if Tranmit is Active 650 800 ns

Last Bit Received to Start Slow Decay Output 230 800 ns

Receive Steady State Prop. Delay 15 100 ns

Receiver Jitter ±0.7 ±1.5 ns

Differential Output Rise Time 20% to 80% (Rx±, COL±) 3 ns

Differential Output Fall Time 20% to 80% (Rx±, COL±) 3 ns

Collision Present to SQE Assert 0 900 ns

Time for Loopback to swtich from Tx to RxTP

during a collision 0 900 ns

Time for SQE to deactivate given that RxTP goes idle and

TxTP continues 0 90 0 n s

Time for SQE to deactivate given that TxTP goes idle

and RxTP continues 0 90 0 n s

Collision Frequency 8.5 10 11.5 MHz

Collision Pulse Duty Cycle 40 50 60 %

SQE Test Delay (Tx Inactive to SQE) 0.6 1.1 1.6 µs

SQE Test Duration 0.5 1.0 1.5 µs

Jabber Activation Delay 20 70 150 ms

Jabber Reset Unjab Time 250 450 750 ms

Delay from Outputs Disabled to Collision Oscillator On 100 ns

Link Loss Time 5 0 95 150 ms

Link Test Pulse Receive Minimum Time 2 4.2 7 ms

Link Test Pulse Receive Maximum Time 25 70 150 ms

Link Test Pulse Repetition Rate 8 16 24 ms

Link Test Pulse Width 85 100 200 ns

XMT, RCV, CLSN On Time 30 100 300 ms

5

ML4658

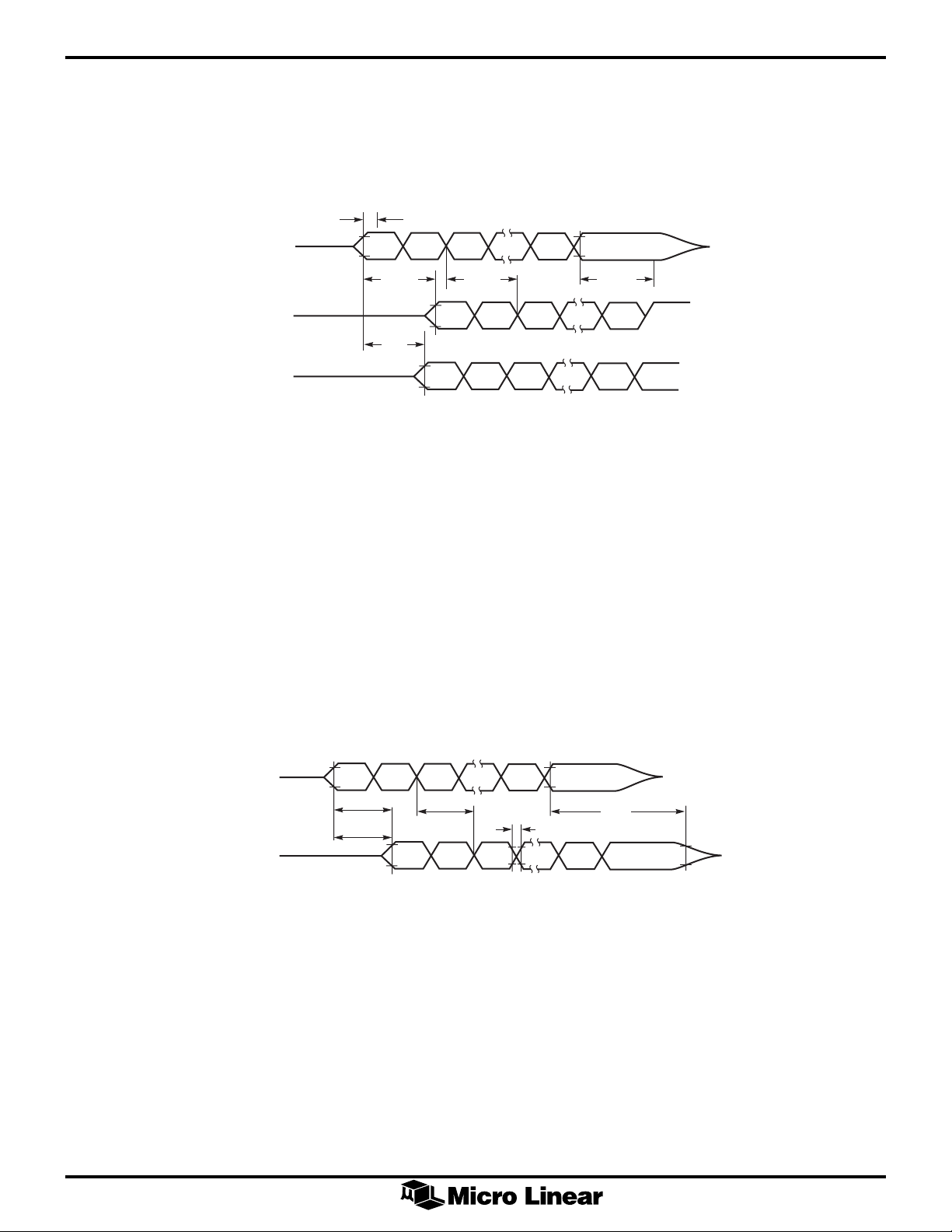

TIMING DIAGRAMS

Tx+

Tx–

TxTP+

TxTP–

Rx+

Rx–

t

TXNPW

VALID DATA

t

TXODY

t

TXLP

t

TXSDY

VALID DATA

DATAVALID

Figure 1. Transmit and Loopback Timing

t

TXFPW

RxTP+

RxTP–

Rx+

Rx–

t

RXODY

t

RXTDY

VALID DATA

t

RXSDY

t

RXFX

t

AR

DATAVALID

t

AF

Figure 2. Receive Timing

6

Loading...

Loading...