Micro Linear Corporation ML2653CQ, ML2652CQ Datasheet

July 2000

ML2652/ML2653

10Base-T Physical Interface Chip

GENERAL DESCRIPTION

The ML2652, 10BASE-T Physical Interface Chip, is a

complete physical interface for twisted pair and AUI

Ethernet applications. It combines a 10BASE-T MAU,

Manchester Encoder/Decoder, and Twisted Pair Interface

filters in one monolithic IC. A complete DTE interface for

twisted pair Ethernet can be implemented by combining

the ML2652, an Ethernet controller, and transformers.

The ML2652 can automatically select between an AUI and

twisted pair interface based on Link Pulses. Six LED

outputs provide complete status at the physical link. Link

pulse testing can be enabled or disabled through the

LTP LED Pin.

The unique transmitter design uses a waveform generator

and low pass filter to meet the 10BASE-T transmitter

requirements without the need for an external filter. The

differential current driven output reduces common mode

which in turn results in very low EMI and RFI noise.

The ML2652 and ML2653 (28 pin version) are implemented

in a low power double polysilicon CMOS technology. The

ML2653 does not include the AUI interface.

FEATURES

■ Complete physical interface solution

■ Conforms to IEEE 802.3i–1990 (10Base-T)

■ On-chip transmit and receive filters

■ Automatic AUI/Twisted Pair selection (ML2652 only)

■ Power down mode

■ Pin selectable controller interface-(CS0 – CS2)

Intel 82586, 82596

NSC DP8390

Seeq 8003, 8005

AMD 7990

■ Automatic polarity correction

■ Pin selectable receive squelch levels

■ Status pins for: link detect, receive &

transmit activity, collision, jabber, AUI selection

■ Single supply 5V ±5%

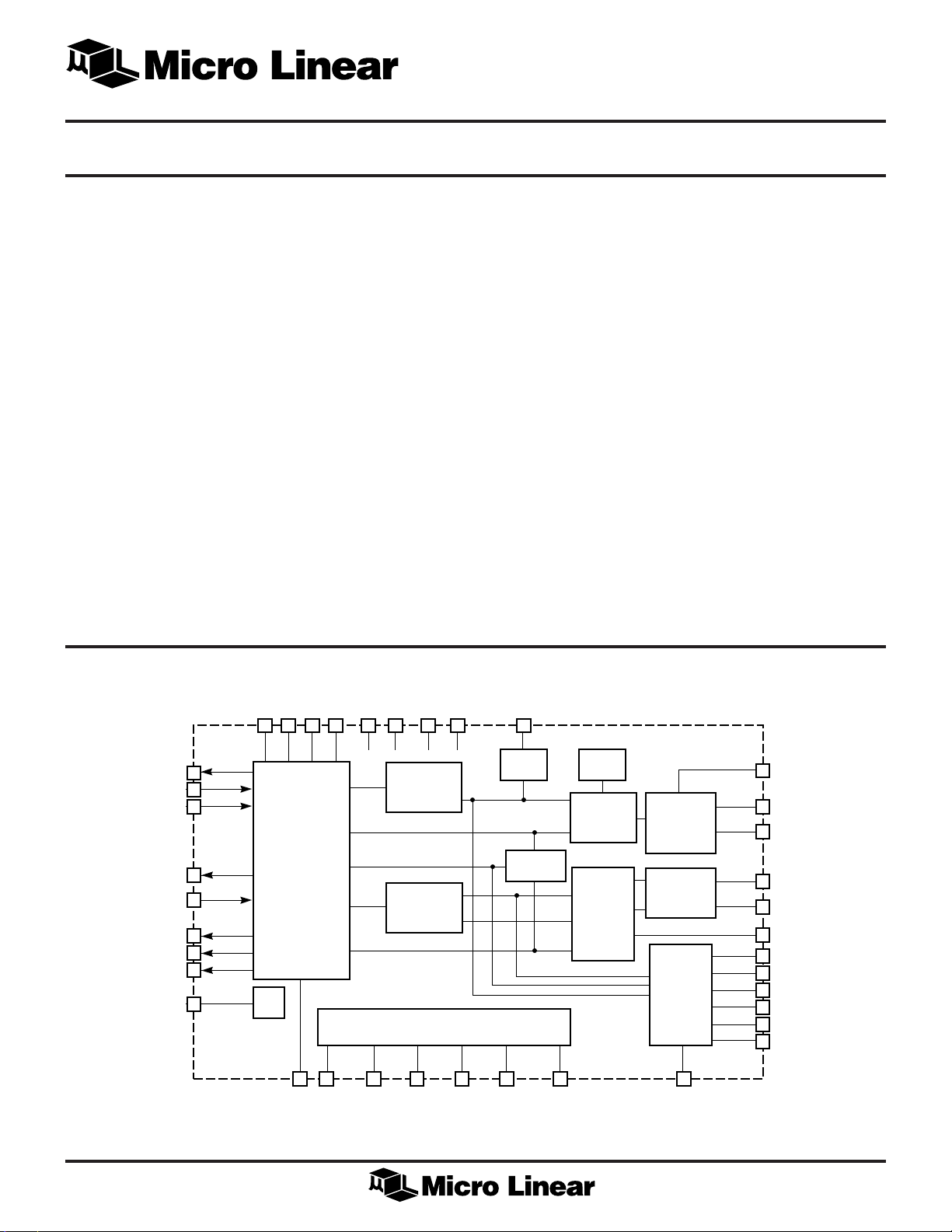

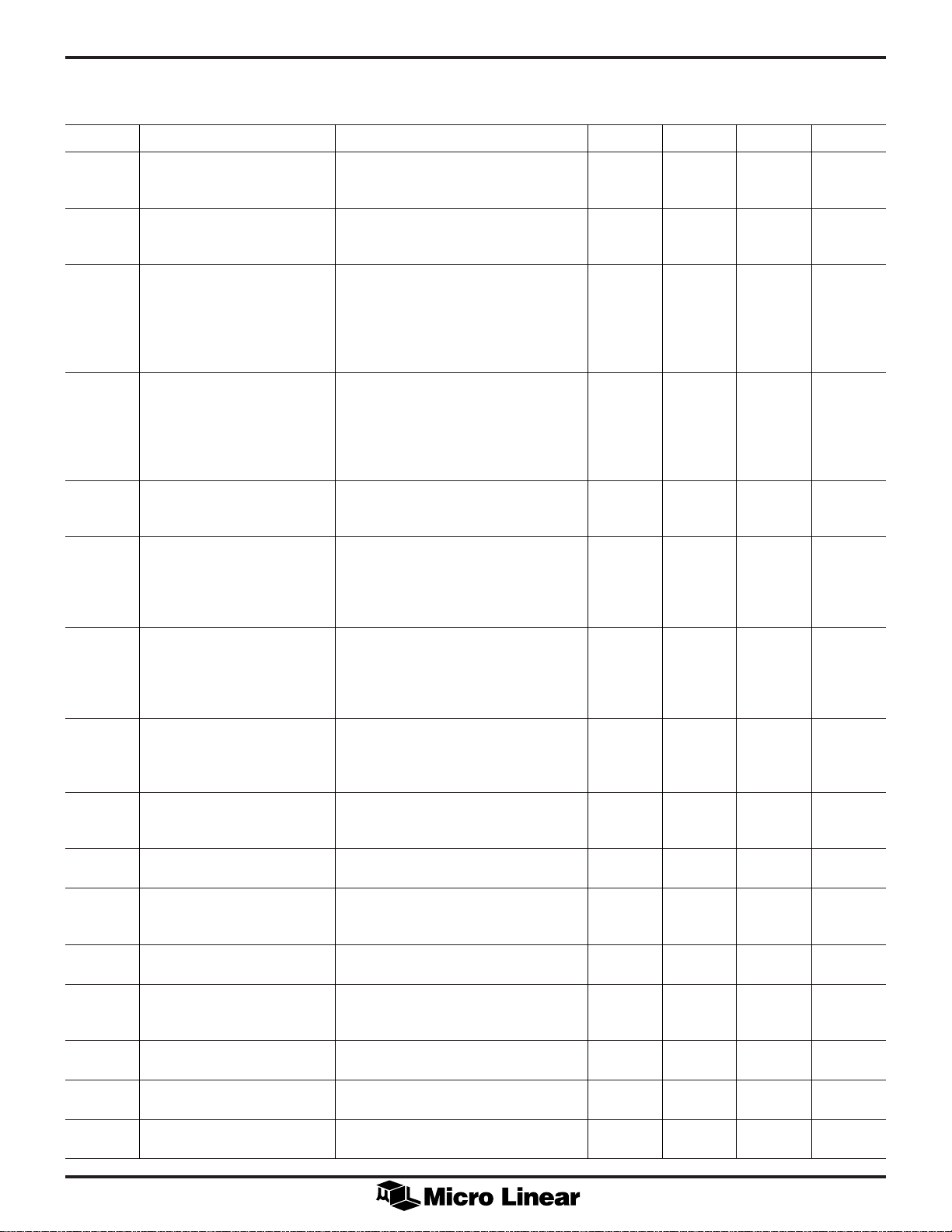

ML2652 BLOCK DIAGRAM

CS1 CS2 FD V

CS0

TxC

TxE

TxD

COL

LPBK

RxC

RxE

RxD

CLK

CONTROLLER

INTERFACE

OSC

RPOL

CCVCC

DATA

ENABLE

COLLISION

DATA

ENABLE

AUISEL RCVCLS

GND GND

MANCHESTER

ENCODER

MANCHESTER

DECODER

XMT

LEDS

JABDIS

JABBER

DETECT

COLLISION

DETECT

LTP JAB

LINK

PULSE

XMT

WAVEFORM

GEN & LPF

RECEIVER

CURRENT

DRIVEN XMT

OUTPUT

DRIVER

RECEIVE

LPF

AUI

AUI/TP

RTX

Tx+

Tx–

Rx+

Rx–

RSL

DO+

DO–

CI+

CI–

DI+

DI–

1

ML2652/ML2653

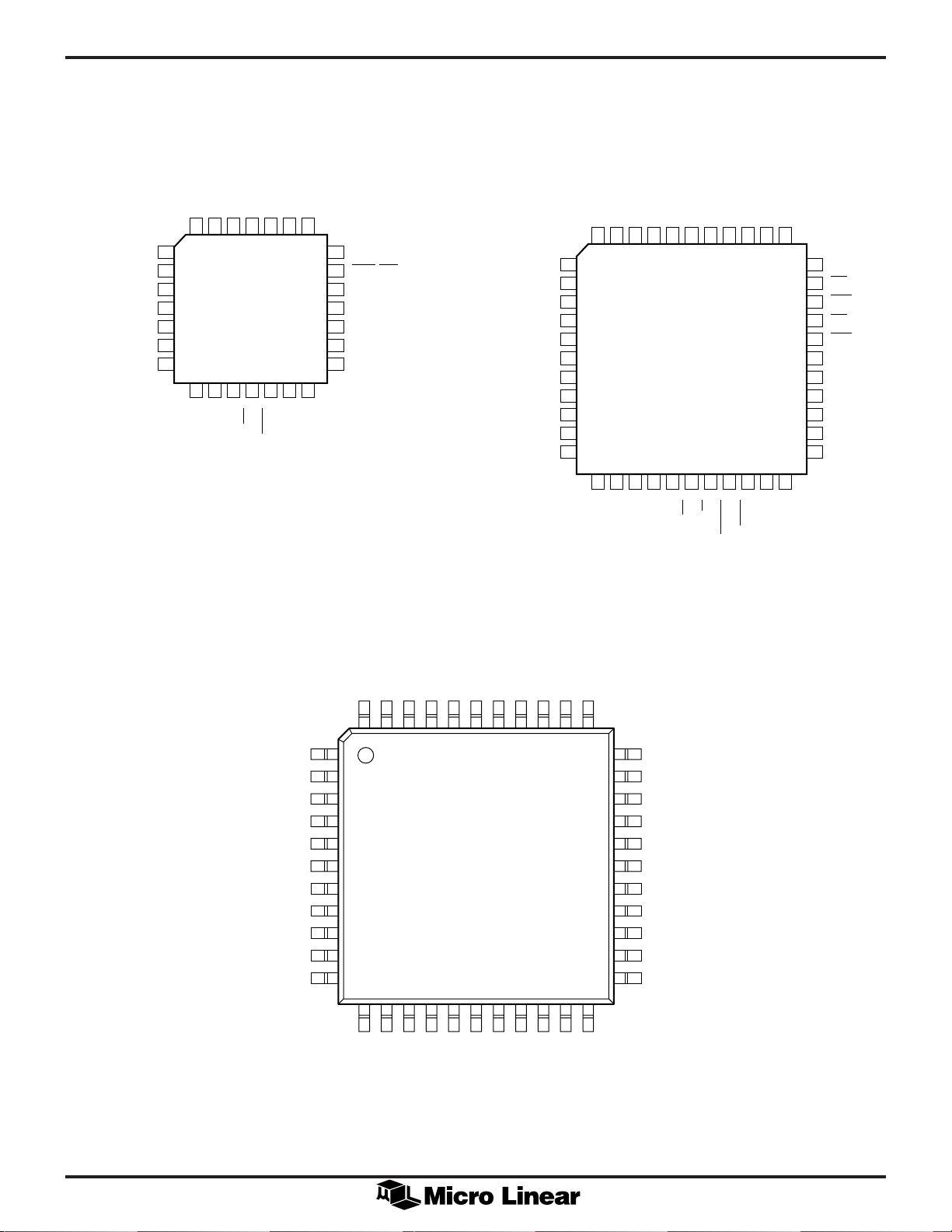

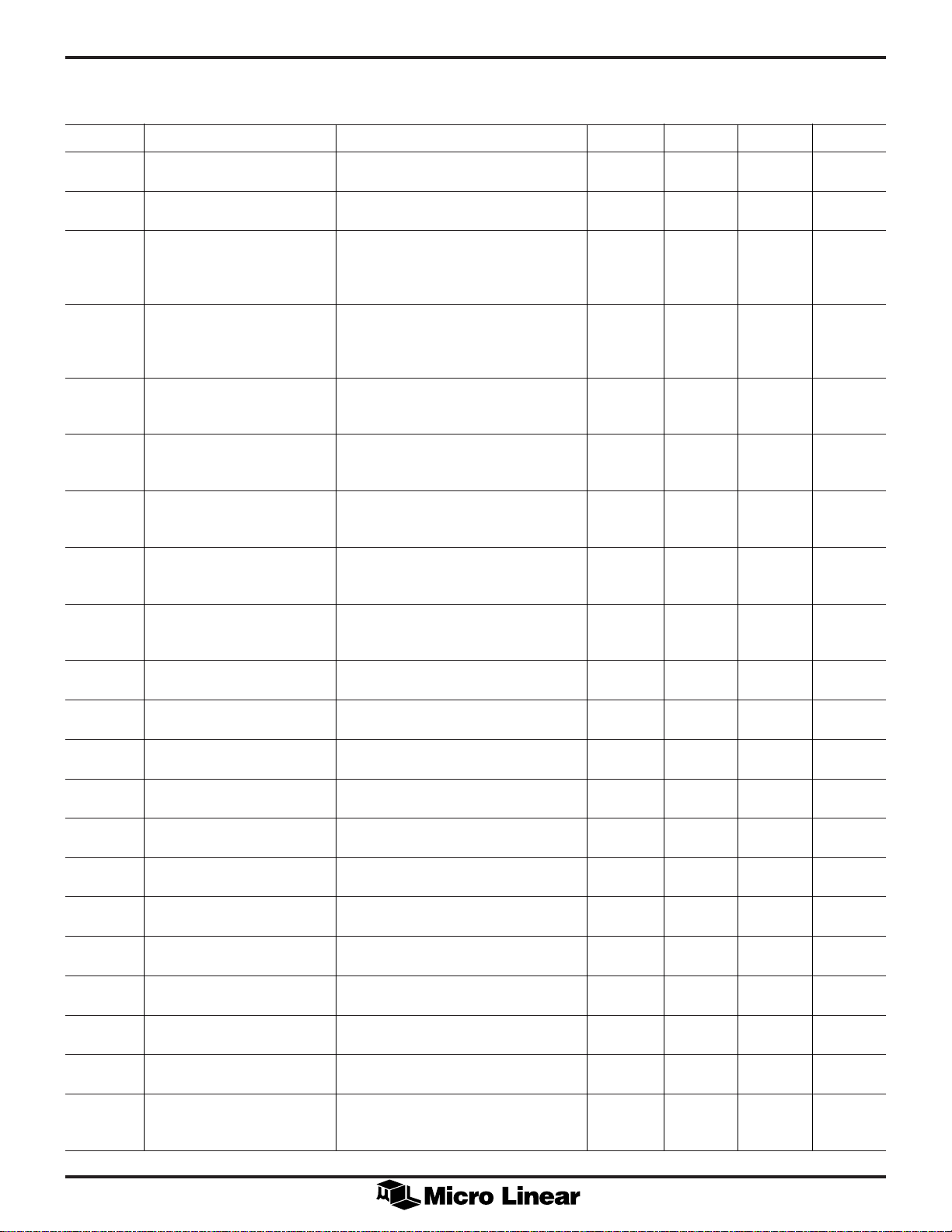

PIN CONNECTIONS

Tx–

NC

CLK

LPBK

Rx+

Rx–

NC

28-Pin PLCC (Q28)

GND

5

6

7

8

9

10

11

Tx+

4321282726

12 13 14 15 16 17 18

CCVCC

V

ML2653

GND

TxC

TxD

FD

LTP

RPOL

TxE

COL

RTX

CS0

25

24

23

22

21

20

19

RSL

XMT/RCV

RxD

RxC

RxE

CS2

CS1

DO+

DO–

CLK

LPBK

GND

Rx+

Rx–

NC

NC

DI+

DI–

ML2652

44-Pin PLCC (Q44)

NCNCTx–

6543214443424140

7

8

9

10

11

12

13

14

15

16

17

18 19 20 21 22 23 24 25 26 27 28

CI+

CI–

CCVCC

V

GND

Tx+

FD

GND

LTP

TxC

AUI/TP

TxD

AUISEL

TxE

RPOL

RTX

COL

JABDIS

CS0

RSL

39

JAB

38

XMT

37

CLS

36

RCV

35

RXD

34

RxC

33

RxE

32

CS2

31

CS1

30

GND

29

NC

NC

CLK

LPBK

NC

Rx+

Rx–

NC

NC

NC

NC

44-Pin TQFP (H44-10)

NCNCTx–

44 43 42 41 40

1

2

3

4

5

6

7

8

9

10

11

12 13 14 15 16

NC

NC

VCCV

ML2653

GND

Tx+

GND

TxC

39 381937203621352234

17 18

FD

CC

LTP

AUI/TP

TxD

NC

TxE

RPOL

RTX

COL

JABDIS

33

32

31

30

29

28

27

26

25

24

23

CS0

RSL

JAB

XMT

CLS

RCV

RXD

RxC

RxE

CS2

CS1

NC

2

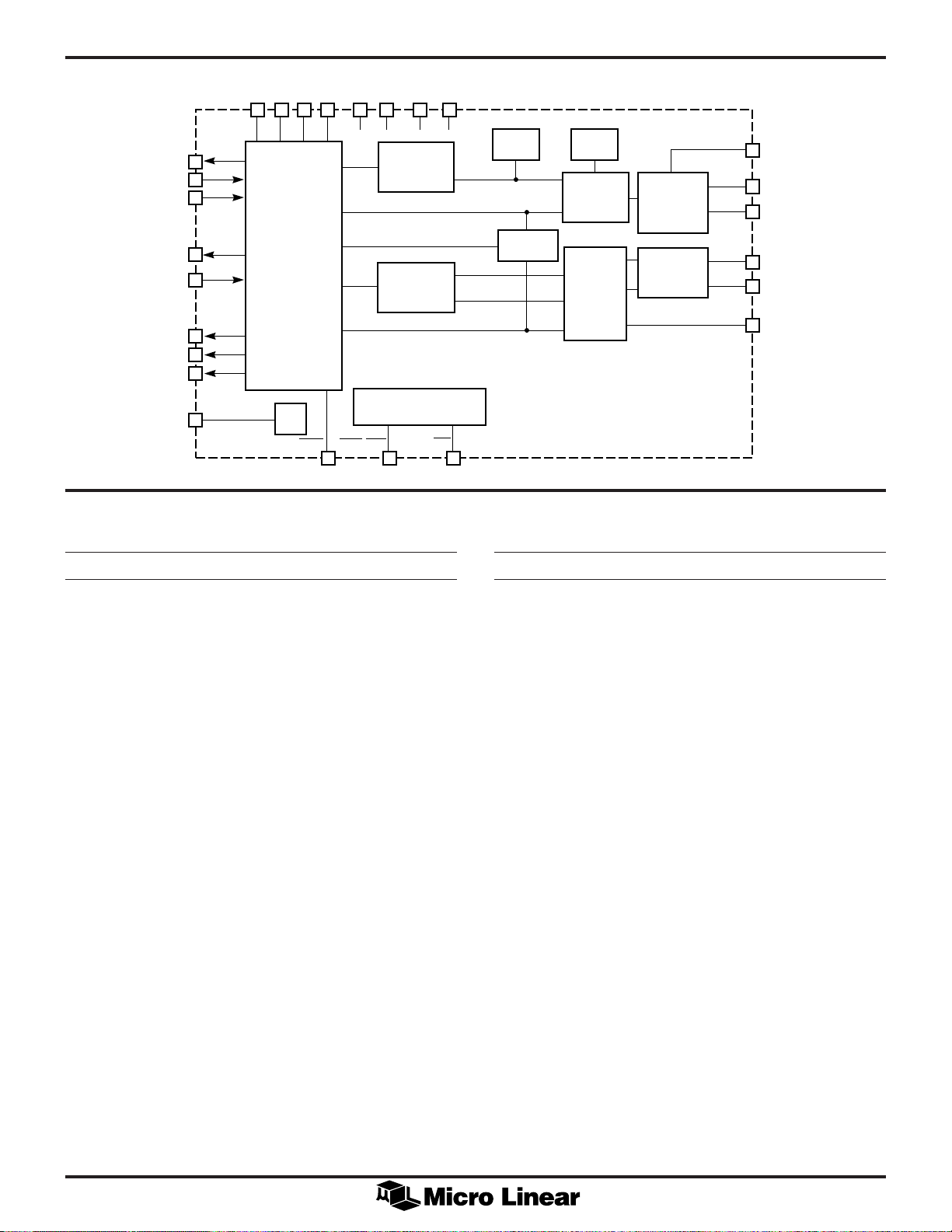

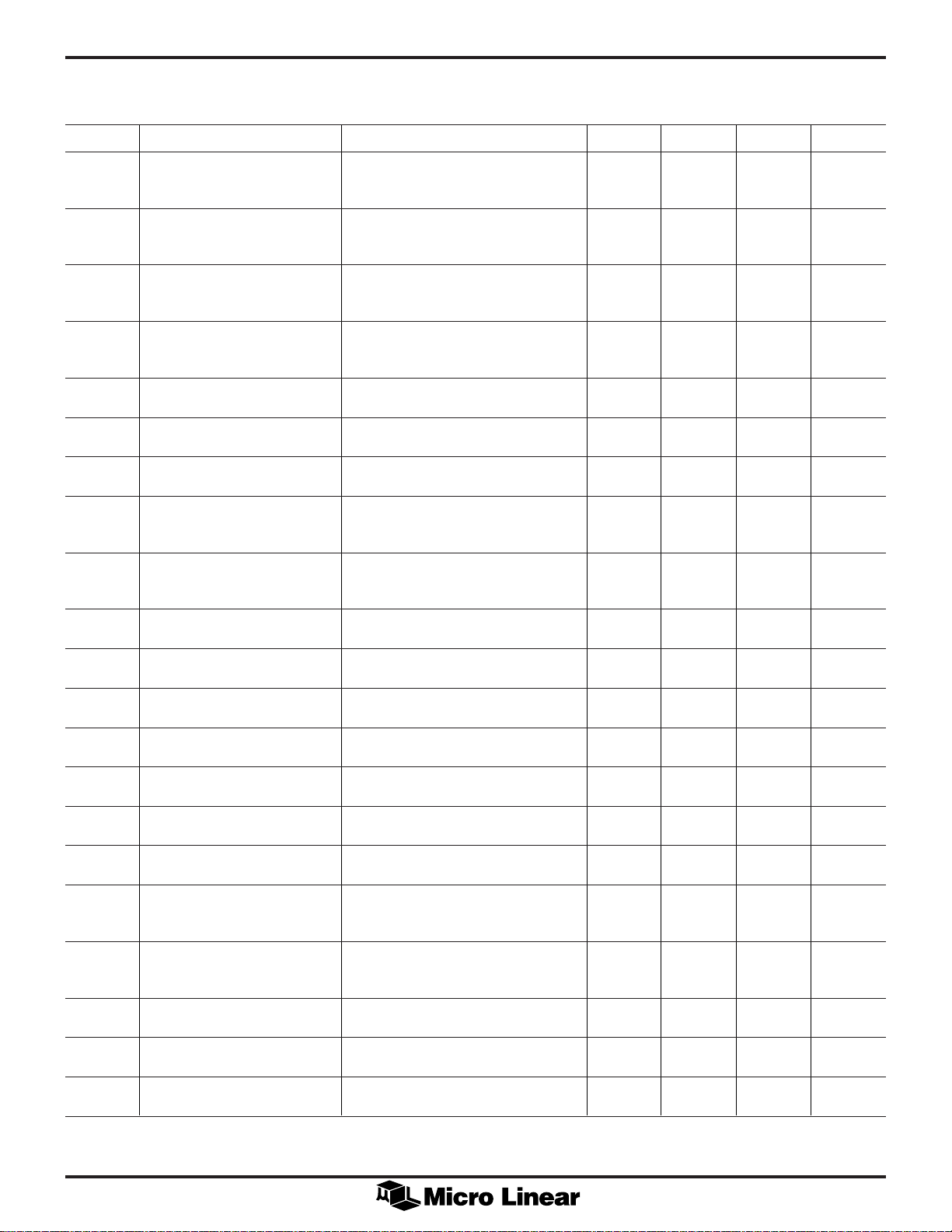

ML2653 BLOCK DIAGRAM

ML2652/ML2653

TxC

TxE

TxD

COL

LPBK

RxC

RxE

RxD

CLK

PIN DESCRIPTION

NAME FUNCTION

CS0 CS1 CS2 FD V

CONTROLLER

INTERFACE

OSC

V

CC

MANCHESTER

DATA

ENABLE

COLLISION

DATA

MANCHESTER

ENABLE

XMT/RCVRPOL LTP

GND

CC

ENCODER

DECODER

LEDS

GND

JABBER

DETECT

COLLISION

DETECT

NAME FUNCTION

LINK

PULSE

XMT

WAVEFORM

GEN & LPF

RECEIVER

CURRENT

DRIVEN XMT

OUTPUT

DRIVER

RECEIVE

LPF

RTX

Tx+

Tx–

Rx+

Rx–

RSL

V

Positive supply. +5V

CC

GND Ground. 0 volts. All inputs and outputs referenced

to this point.

CLK Clock input. There must be either a 20 MHz

crystal or a 20 MHz clock between this pin

and GND.

Tx+ Transmit positive twisted pair output. This output

is a current source that drives the twisted pair

cable through a pulse transformer.

Tx– Transmit negative twisted pair output. This output

is a current source that drives the twisted pair

cable through a pulse transformer.

Rx+ Receive positive twisted pair input. This input

receives data from the twisted pair cable through

a pulse transformer.

Rx– Receive negative twisted pair input. This input

receives data from the twisted pair cable through

a pulse transformer.

DO+ AUI positive transmit output. AUI transmit data

output to optional external transceiver.

DI– AUI negative receive data input from optional

external transceiver.

CI+ AUI positive collision input from optional external

transceiver.

CI– AUI negative collision input from optional

external transceiver.

RTX Transmit current set. An external resistor between

this pin and GND programs the absolute value of

output current on Tx±.

TxC Transmit clock output. Digital output which clocks

the transmit data (TxD) into the device from the

controller.

TxD Transmit data input. Digital input which contains

transmit data from the controller.

TxE Transmit enable input. Digital input from the

controller that indicates when the transmit data

(TxD) is valid.

COL Collision output Digital output to the controller

which indicates when a collision condition is

present.

DO– AUI negative transmit output. AUI transmit data

output to optional external transceiver.

DI+ AUI positive receive data input from optional

external transceiver.

RxC Receive clock output. Digital output which clocks

receive data (RxD) from the device into the

controller.

3

ML2652/ML2653

PIN DESCRIPTION

NAME FUNCTION

RxD Receive data output. Digital output which

contains receive data sent to the controller.

RxE Receive data valid. Digital output to the controller

that indicates when the receive data (RxD) is

valid.

LPBK Local loopback. Digital input from the controller

which forces the device to loopback transmit data

without sending it on the media.

FD Full Duplex Enable. When enabled the 10BASE-T

MAU loopback and collision detect are disabled.

LPBK must be disabled when using this function.

CS0 Controller selection input. Digital input which

selects one of four standard controller timing

interfaces. This pin has an internal pulldown

resistor to GND.

CS1 Controller select input. Digital input which selects

one of four standard controller timing interfaces.

This pin has an internal pulldown resistor to GND.

CS2 Controller select input. Digital input which selects

one of four standard controller timing interfaces.

This pin has an internal pulldown resistor to GND.

RSL Receive squelch level select input. Pin has

internal pullup resistor to VCC.

RSL = High Receive squelch level = 10Base-T

RSL = Low Receive squelch level = extended

XMT Transmit status output. Digital output which

indicates data transmission on Tx+ and Tx–.

Pin is open drain output with resistor pullup and is

capable of driving an LED. XMT pin and RCV pin

are the same pin for the ML2653.

(Continued)

distance

NAME FUNCTION

CLS Collision status output. Digital output which

indicates that collision condition has been

detected. Pin is an open drain output with resistor

pullup and is capable of driving an LED.

LTP Link test pass output/input. This pin consists of an

open drain output transistor with a resistor pullup

that serves both as a link test pass output and a

link test disable input. When used as an output,

this pin is capable of driving an LED.

LTP = High, link test failed

LTP = Low, link test pass

LTP = GND, link test disabled

AUI/TP AUI/twisted pair interface select input.

AUI/TP = High, AUI selected

AUI/TP = Low, TP selected

RPOL This pin must be grounded at all times.

JAB Jabber detect output. Digital output which

indicates that the jabber condition has been

detected. Pin is an open drain output with resister

pullup and is capable of driving a LED.

JAB = High, normal

JAB = Low, jabber detected

AUISEL AUI/TP port output status

AUISEL = High, TP port selected

AUISEL = Low, AUI port selected

JABDIS Jabber disable input

JABDIS = High, jabber disabled

JABDIS = Low, normal operation

NC No connect. Leave this pin open circuit.

RCV Receive status output. Digital output which

indicates unsquelched data reception on Rx+

and Rx–. Pin is an open drain output with resistor

pullup and is capable of driving an LED.

ABSOLUTE MAXIMUM RATINGS

Absolute maximum ratings are limits beyond which the

life of the integrated circuit may be impaired. All voltages

unless otherwise specified are measured with respect to

GND. (Note 1)

VCC supply voltage .................................................. +6.5V

All inputs and outputs....................... –0.3V to VCC + 0.3V

Input current per pin.............................................±25 mA

Power dissipation .............................................. 0.75 Watt

4

Storage temperature range ........................ –65°C to 150°C

Junction Temperature .............................................. 150°C

Lead temperature (soldering, 10 sec)....................... 260°C

Thermal Resistance (qJA)

28-Lead PLCC................................................... 60°C/W

44-Lead PLCC................................................... 54°C/W

44-Lead TQFP ................................................... 67°C/W

ML2652/ML2653

ELECTRICAL CHARACTERISTICS

(Continued)

Unless otherwise specified TA = 0°C to 70°C, VCC = 5V +5%. Note 2 & 3.

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

VIL Digital input low voltage All except CLK .8 V

CLK 1.5 V

VIH Digital input high voltage All except CLK 2.0 V

CLK 3.5 V

IIL Digital input low current VIN=GND TxD, TxE, AUI/TP –5 µA

VIN=GND LPBK, CS2–0, LBDIS,JABDIS –5 µA

VIN=GND RSL –10 –25 –50 µA

VIN=GND LTP, RPOL, –15 –250 –500 µA

VIN=GND CLK –300 µA

IIH Digital input high current VIN=VCC TxD, TxE, AUI/TP 1µA

VIN=VCC LPBK, CS2–0, LBDIS, JABDIS 10 25 50 µA

VIN=VCC RSL 1 µA

VIN=VCC LTP, RPOL 1 µA

VIN=VCC CLK 250 µA

CIN Digital input capacitance All except CLK 5 pF

CLK 10 pF

VOL Digital output low voltage IOL=–2mA TxC, COL,

RxC, RxD, RxE .4 V

IOL=–10mA XMT, RCV,

CLS, LTP, RPOL, JAB .6 V

VOH Digital output high voltage IOH=2mA TxC, COL,

RxC, RxD, RxE 4.0 V

IOL=10uA XMT, RCV, CLS,

LTP, RPOL, JAB 2.4 V

ICC VCC supply current TX transmission 140 mA

No transmission 105 mA

Powerdown mode 2 mA

TOV Tx± differential

output voltage RTX = 10K 2.2 2.5 2.8 Vp

THD Tx± harmonic distortion TxD=all ones –27 dB

TCM Tx± common mode

output voltage ± 50 mVp

TCMR Tx± common mode rejection VCM=15vp, 10.1 MHz sine ± 100 mVp

TOVI Tx± differential output

voltage during idle ± 50 mVp

TOIA Tx± output current accuracy RTX=10K 50 mA

TRO Tx± output resistance 1 Mohm

TCO Tx± output capacitance 10 pF

5

ML2652/ML2653

ELECTRICAL CHARACTERISTICS

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

RRI Receive input resistance 2.5K 10K ohms

RCI Receive input capacitance 10 pF

RSON Receive squelch on level RSL=1 275 520 mVp

(Differential zero RSL=0 150 325 mVp

to peak voltage)

RSOF Receive squelch off level RSL=1 150 325 mVp

(Differental zero RSL=0 100 225 mVp

to peak voltage)

DOV DO± differential

output voltage ± 550 ± 1170 mV

DOVI DO± differential

output voltage during idle ± 40 mV

DOUS DO±differential output

voltage return to 0 undershoot –100 mV

(Continued)

DOCMA DO± common mode AC

output voltage ± 40 mV

DOCMA DO± common mode DC

output voltage VCC *.5 V

DIRI DI/CI input resistance 2.5K 10K ohms

DICI DI/CI input capacitance 10 pF

DIBV DI/CI input bias voltage DI/CI floating VCC *.5 V

DISON DI/CI squelch on level –175 –325 mVp

t1 TxC on time 45 55 ns

t2 TxC off time 45 55 ns

t3 TxC period 100 ns

t4 TxE setup time 25 ns

t5 TxE hold time 0 ns

t6 TxD setup time 25 ns

t7 TxD hold time 0 ns

t8 Transmit propagation delay Tx± 60 200 ns

DO± 200 ns

6

ML2652/ML2653

ELECTRICAL CHARACTERISTICS

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

t9 Start of Idle Tx±

Pulse Width DO± 200 350 ns

t10 SOI pulse width to within Tx± 4500 ns

40mV of final value DO± 8000 ns

t11 Transmit output jitter Tx± ± 8.0 ns

t12 Transmit output

rise and fall time Tx± , 10–90% 5 ns

t13 TxE to XMT assert 250 ms

t14 XMT blinker pulse period 95 115 ms

t15 XMT duty cycle 45 55 %

t20 Start of receive packet Rx± 600 ns

to RxE assert DI± 200 ns

(Continued)

DO± ± .5 ns

t21 Start of receive packet Rx+ 1600 ns

to RxC active DI+ 1300 ns

t22 RxC on time 45 900 ns

t23 RxC off time 45 55 ns

t24 RxD valid before RxC 45 ns

t25 RxD valid after RxC 35 ns

t26 RxE assert to RCV assert 250 ms

t27 RCV blinker pulse period 95 115 ms

t28 RCV duty cycle 45 55 %

t29 Receive input jitter Preamble ± 12 ns

Data ± 18 ns

t30 Receive propagation delay Tx± 160 ns

DI± 160 ns

t31 RxC to RxE assert 30 60 ns

t32 RxC to RxE deassert 20 45 ns

t33 RxE deassert to RxC switchover 100 200 ns

7

Loading...

Loading...