Micro Linear Corporation ML2280BCS, ML2283CCP, ML2283CIP, ML2280CIS, ML2280CCS Datasheet

...

May 1997

ML2280*, ML2283**

Serial I/O 8-Bit A/D Converters

GENERAL DESCRIPTION

The ML2280 and ML2283 are 8-bit successive

approximation A/D converters with serial I/O and

configurable input multiplexers with up to 4 input

channels.

All errors of the sample-and-hold incorporated on the

ML2280 and ML2283 are accounted for in the analog-todigital converters accuracy specification.

The voltage reference can be externally set to any value

between GND and VCC, thus allowing a full conversion

over a relatively small voltage span if desired.

The ML2283 is an enhanced double polysilicon, CMOS,

pin-compatible second source for the ADC0833 A/D

converter. All parameters are guaranteed over temperature

with a power supply voltage of 5V ±10%.

FEATURES

■ Conversion time: 6µs

■ ML2280 capable of digitizing a 5V, 40kHz sine wave

■ Total unadjusted error with external

reference: ±1/2LSB or ±1LSB

■ Sample-and-hold: 375ns acquisition

■ 0 to 5V analog input range with single 5V

power supply

■ 2.5V reference provides 0 to 5V analog input range

■ No zero- or full-scale adjust required

■ Low power: 12.5mW MAX

■ Analog input protection: 25mA (min) per input

■ Differential analog voltage inputs (ML2280)

■ Programmable multiplexer with differential or single

ended analog inputs (ML2283)

■ 0.3" width 8- or 14-pin DIP, or 8-Pin SOIC (ML2280)

■ Superior pin-compatible replacement for ADC0833

* This Part Is Obsolete

** This Part Is End Of Life As Of August 1, 2000

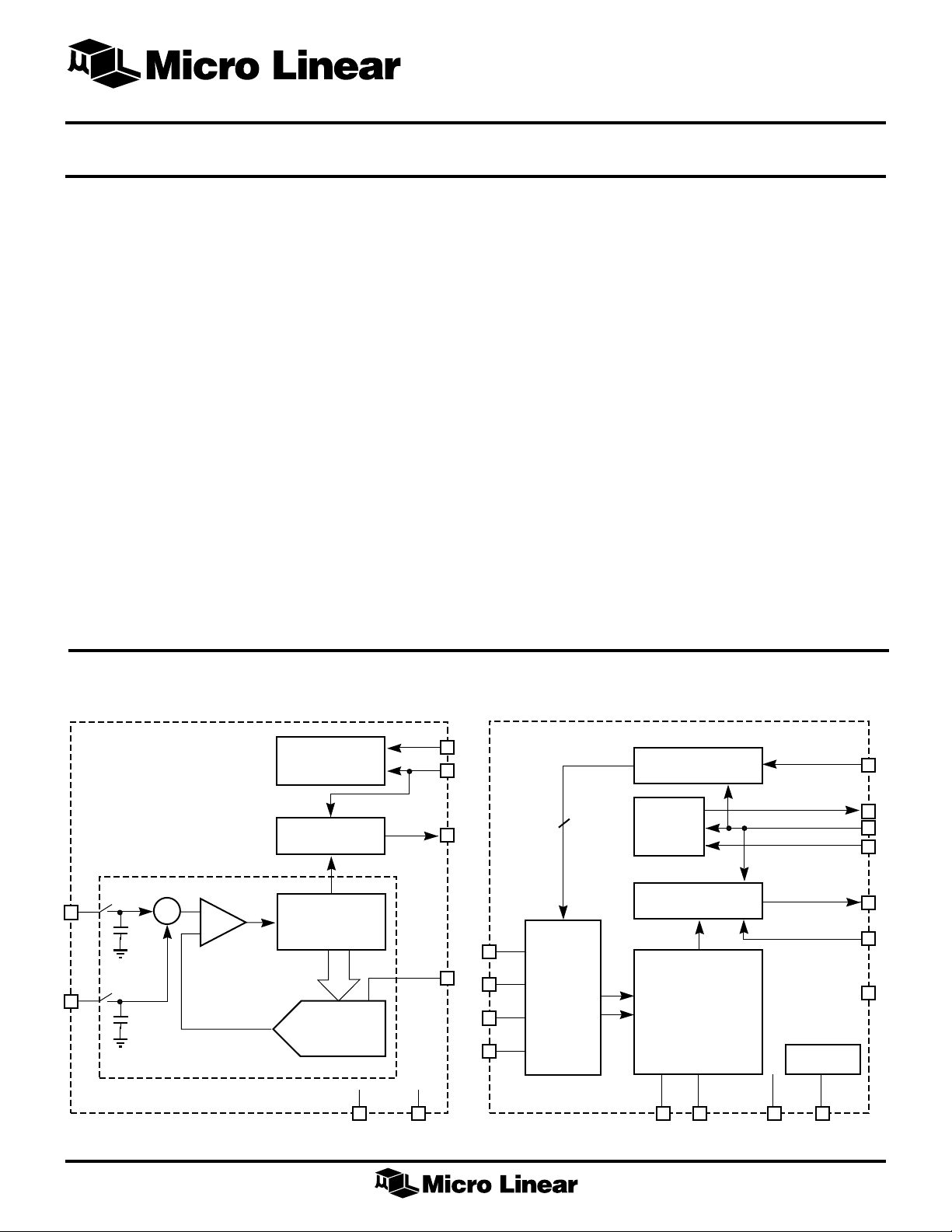

BLOCK DIAGRAM

ML2281

A/D WITH SAMPLE & HOLD FUNCTION

V

IN+

V

IN–

8pF

8pF

+

+

Σ

COMP

–

–

CONTROL

AND

TIMING

OUTPUT

SHIFT-REGISTER

SUCCESSIVE

APPROXIMATION

REGISTER

D/A

CONVERTER

V

CC

GND

V

CS

CLK

DO

REF/2

CH0

CH1

CH2

CH3

4-BIT

4-CHANNEL

S.E.

OR

2-CHANNEL

DIFF

MULTIPLEXER

ML2283

SHIFT-REGISTER

CONTROL

AND

TIMING

SHIFT-REGISTER

CONVERTER

SAMPLE & HOLD

V

AGND

INPUT

OUTPUT

A/D

WITH

FUNCTION

REF/2

V

CC

DI

SARS

CLK

CS

DO

SE

DGND

SHUNT

REGULATOR

V+

1

ML2280, ML2283

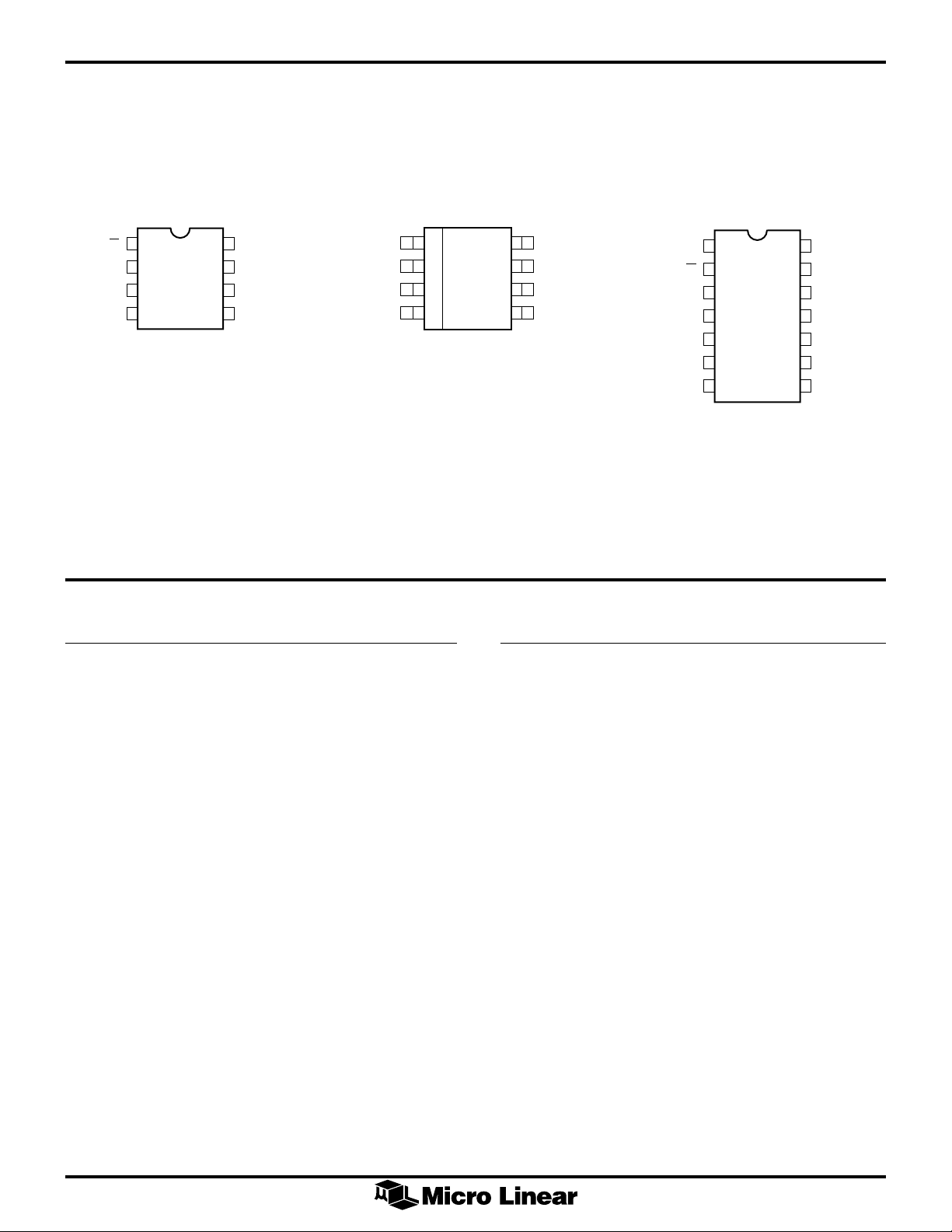

PIN CONFIGURATION

ML2280

Single Differential Input

8-Pin PDIP

CS

V

IN

V

IN

GND

1

2

+

3

–

4

TOP VIEW

8

7

6

5

PIN DESCRIPTION

V

CLK

DO

V

CC

REF/2

ML2280

Single Differential Input

8-Pin SOIC

CS

V

IN

V

IN

GND

1

2

+

3

–

4

TOP VIEW

8

7

6

5

V

CLK

DO

V

CC

REF/2

4-Channel MUX

14-Pin PDIP

1

V+

2

CS

3

CH0

4

CH1

5

CH2

6

CH3

DGND

7

ML2283

TOP VIEW

8

V

CC

9

DI

10

CLK

11

SARS

12

DO

13

V

REF/2

14

AGND

NAME FUNCTION

V

CC

Positive supply. 5V ± 10%

DGND Digital ground. 0 volts. All digital inputs and

outputs are referenced to this point.

AGND Analog ground. The negative reference voltage

for A/D converter.

GND Combined analog and digital ground.

CH0, Analog inputs. Digitally selected to be single

VIN+, VIN– ended (VIN) or; VIN+ or VIN– of a differential

input. Analog range = GND - VIN - VCC.

V

REF/2

Reference. The analog input range is twice the

positive reference voltage value applied to this

pin.

V+ Input to the Shunt Regulator.

DO Data out. Digital output which contains result

of A/D conversion. The serial data is clocked

out on falling edges of CLK.

NAME FUNCTION

SARS Successive approximation register status.

Digital output which indicates that a

conversion is in progress. When SARS goes

to 1, the sampling window is closed and

conversion begins. When SARS goes to 0,

conversion is completed. When CS = 1, SARS

is in high impedance state.

CLK Clock. Digital input which clocks data in on

DI on rising edges and out on DO on falling

edges. Also used to generate clocks for A/D

conversion.

DI Data input. Digital input which contains serial

data to program the MUX and channel

assignments.

CS Chip select. Selects the chip for multiplexer

and channel assignment and A/D conversion.

When CS = 1, all digital outputs are in high

impedance state. When CS = 0, normal A/D

conversion takes place.

2

ML2280, ML2283

ABSOLUTE MAXIMUM RATINGS

Absolute maximum ratings are those values beyond which

the device could be permanently damaged. Absolute

maximum ratings are stress ratings only and functional

device operation is not implied.

Current into V+ ...................................................... 15mA

Supply Voltage, VCC................................................. 6.5V

Voltage

Logic Inputs ........................................... –7 to VCC +7V

Analog Inputs ................................ –0.3V to VCC +0.3V

Input Current per Pin (Note 1) .............................. ±25mA

Storage Temperature ................................ –65°C to 150°C

Package Dissipation

at TA = 25°C (Board Mount) .............................800mW

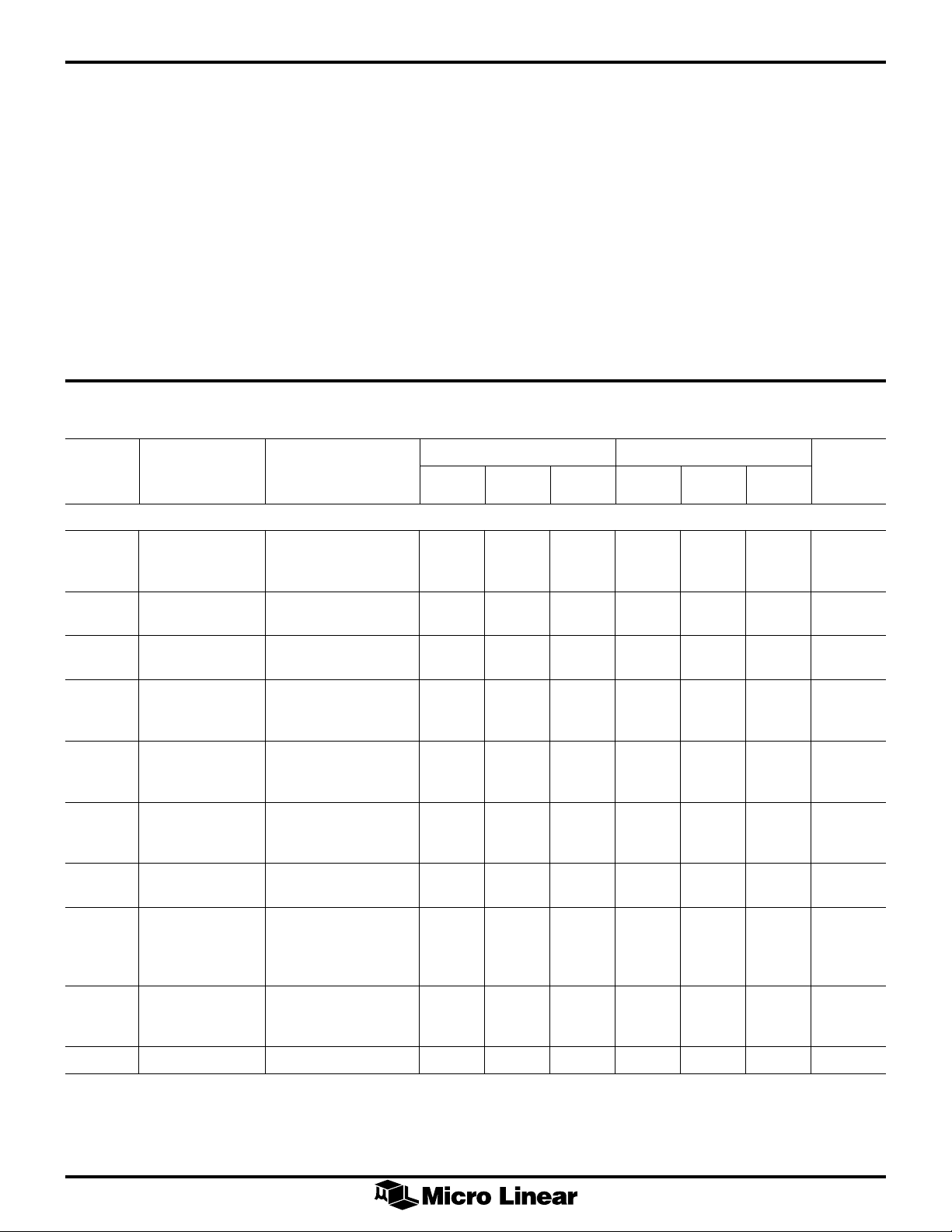

ELECTRICAL CHARACTERISTICS

Unless otherwise specified, TA = T

SYMBOL PARAMETER CONDITIONS MIN NOTE 3 MAX MIN NOTE 3 MAX UNITS

MIN

to T

, VCC = 5V ±10%, f

MAX

Lead Temperature (Soldering 10 sec.)

Dual-In-Line Package (Molded) .......................... 260°C

Dual-In-Line Package (Ceramic) ......................... 300°C

OPERATING CONDITIONS

Supply Voltage, VCC............................ 4.5VDC to 6.3V

Temperature Range (Note 2) ................. T

ML2280 BIP, ML2283 BIP ...................... –40°C to 85°C

ML2280 CIP, ML2283 CIP

ML2280 BCP, ML2283 BCP ......................0°C to 70°C

ML2280 CCP, ML2283 CCP

= 1.333MHz, and V

CLK

ML228XB ML228XC

TYP TYP

REF/2

= 2.5V.

MIN

- TA - T

DC

MAX

CONVERTER AND MULTIPLEXER CHARACTERISTICS

Total Unadjusted V

Error V

Reference Input (Note 4) 10 15 20 10 15 20 kW

Resistance

Common-Mode (Notes 4, 7) GND V

Input Range –0.05 +0.05 –0.05 +0.05

DC Common-Mode Common mode voltage ±1/16 ±1/4 ±1/16 ±1/4 LSB

Error voltage GND to V

AC Common-Mode Common mode voltage ±1/4 ±1/4 LSB

Error GND to V

DC Power Supply V

Sensitivity V

AC Power Supply 100mV

Sensitivity on V

Change in Zero 15mA into V+ ±1/2 ±1/2 LSB

Error from V

to Internal Zener V

Operation

=5V VCC = N.C.

CC

= 2.5V ±1/2 ±1 LSB

REF/2

not connected ±2 ±2 LSB

REF/2

(Notes 4, 6)

(Note 5)

0 to 50kHz (Note 5)

= 5V ±10% ±1/32 ±1/4 ±1/32 ±1/4 LSB

CC

- VCC +0.1V

REF

(Note 5)

P-P

(Note 5)

CC

= 2.5V (Note 5)

REF/2

CC/2

,

CC

, 25kHz sine ±1/4 ±1/4 LSB

CC

GND V

CC

V

V

V+ Input Resistance (Note 4) 20 35 20 35 kW

Internal Diode 15mA into V+ 6.9 6.9 V

Z

Regulated Breakdown (at V+)

3

ML2280, ML2283

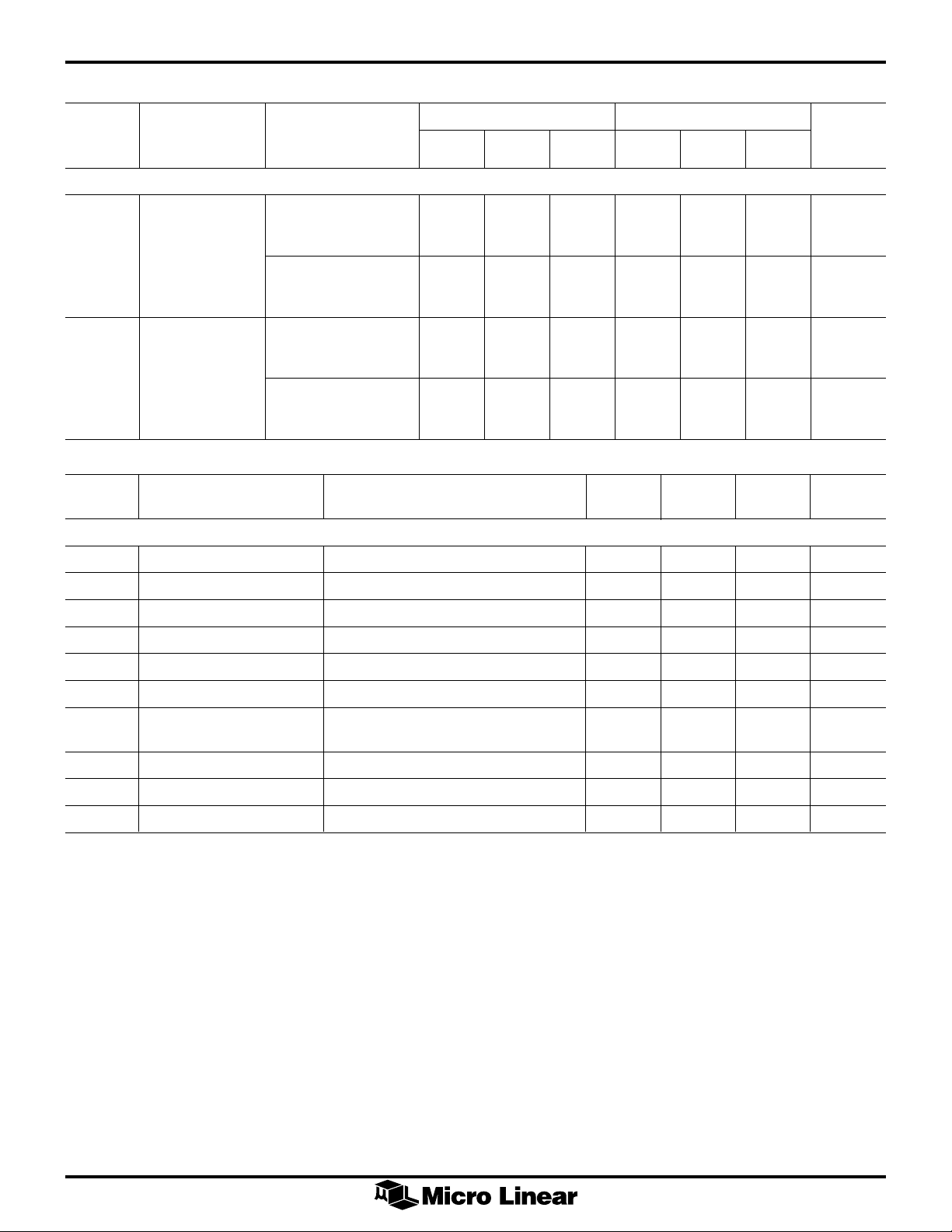

ELECTRICAL CHARACTERISTICS (Continued)

ML228XB ML228XC

TYP TYP

SYMBOL PARAMETER CONDITIONS MIN NOTE 3 MAX MIN NOTE 3 MAX UNITS

CONVERTER AND MULTIPLEXER CHARACTERISTICS (Continued)

I

OFF

Off Channel On channel = V

CC

–1 –1 µA

Leakage Current Off channel = 0V

(Notes 4, 8)

On channel = 0V +1 +1 µA

Off channel = V

CC

(Notes 4, 8)

I

ON

On Channel On channel = 0V –1 –1 µA

Leakage Current Off channel = V

CC

(Notes 4, 8)

On channel = V

CC

+1 +1 µA

Off channel = 0V

(Notes 4, 8)

TYP

SYMBOL PARAMETER CONDITIONS MIN NOTE 3 MAX UNITS

DIGITAL AND DC CHARACTERISTICS

V

IN(1)

V

IN(0)

I

IN(1)

I

IN(0)

V

OUT(1

V

OUT(0)

I

OUT

I

SOURCE

I

SINK

I

CC

Logical “1” Input Voltage (Note 4) 2.0 V

Logical “0” Input Voltage (Note 4) 0.8 V

Logical “1” Input Current VIN = V

(Note 4) 1 µA

CC

Logical “0” Input Current VIN = 0V (Note 4) –1 µA

Logical “1” Output Voltage I

Logical “0” Output Voltage I

HI-Z Output Current V

Output Source Current V

Output Sink Current V

= –2mA (Note 4) 4.0 V

OUT

= 2mA (Note 4) 0.4 V

OUT

= 0V (Note 4) –1 µA

OUT

V

= V

OUT

OUT

OUT

CC

= 0V (Note 4) –6.5 mA

= V

(Note 4) 8.0 mA

CC

1µA

Supply Current (Note 4) 1.3 2.5 mA

4

ML2280, ML2283

ELECTRICAL CHARACTERISTICS (Continued)

TYP

SYMBOL PARAMETER CONDITIONS MIN NOTE 3 MAX UNITS

AC ELECTRICAL CHARACTERISTICS

f

CLK

t

ACQ

t

C

Clock Frequency (Note 4) 10 1333 kHz

Sample-and-Hold Acquisition 1/2 1/f

Conversion Time Not including MUX adddressing time 8 1/f

SNR Signal to Noise Ratio VIN = 40kHz, 5V sine. f

ML2280 (f

SAMPLING

@ 120kHz). Noise is sum of all

nonfundamental components up to 1/2

of f

SAMPLING

(Note 11)

THD Total Harmonic Distortion VIN = 40kHz, 5V sine. f

ML2280 (f

SAMPLING

@ 120kHz). THD is sum of 2,

3, 4, 5 harmonics relative to fundamental

(Note 11)

IMD Intermodulation Distortion V

ML2280 f

= fA + fB. fA = 40kHz, 2.5V sine. –60 dB

IN

= 39.8kHz, 2.5V Sine, f

B

(f

SAMPLING

(f

A

@ 120kHz). IMD is (fA + fB),

– fB), (2fA + fB), (2fA – fB), (fA + 2fB),

(fA – 2fB) relative to fundamental (Note 11)

Clock Duty Cycle (Notes 4, 9) 40 60 %

t

SET-UP

CS Falling Edge or Data Input (Note 4) 130 ns

Valid to CLK Rising Edge

t

HOLD

Data Input Valid after (Note 4) 80 ns

CLK Rising Edge

t

, CLK Falling Edge to Output CL = 100pF (Note 4 & 10)

PD1

t

PD0

Data Valid Data MSB first 90 200 ns

Data LSB first 50 110 ns

= 1.333MHz 47 dB

CLK

= 1.333MHz –60 dB

CLK

= 1.333MHz

CLK

CLK

CLK

t

, Rising Edge of CS to Data CL = 10pF, RL = 10kW (see high impedance 40 90 ns

1H

t

0H

Output and SARS Hi-Z test circuits) (Note 5)

CL = 100pF, RL = 2kW (Note 5) 80 160 ns

C

IN

C

OUT

Note 1: When the input voltage (VIN) at any pin exceeds the power supply rails (VIN < GND < or VIN > VCC) the absolute value of current at that pin should be limited to

Note 2: 0°C to 70°C and –40°C to 85°C operating temperature range devices are 100% tested with temperature limits guaranteed by 100% testing, sampling, or by

Note 3: Typicals are parametric norm at 25°C.

Note 4: Parameter guaranteed and 100% tested.

Note 5: Parameter guaranteed. Parameters not 100% tested are not in outgoing quality level calculation.

Note 6: Total unadjusted error includes offset, full-scale, linearity, multiplexer and sample-and-hold errors.

Note 7: For VIN– • VIN+ the digital output code will be 0000 0000. Two on-chip diodes are tied to each analog input (see Block Diagram) which will forward conduct for

Note 8: Leakage current is measured with the clock not switching.

Note 9: A 40% to 60% clock duty cycle range insures proper operation at all clock frequencies. In the case that an available clock has a duty cycle outside of these limits,

Note 10: Since data, MSB first, is the output of the comparator used in the successive approximation loop, an additional delay is built in (see Block Diagram) to allow for

Note 11: Because of multiplexer addressing, test conditions for the ML2283 is V

Capacitance of Logic Input 5 pF

Capacitance of Logic Outputs 5 pF

25mA or less.

correlation with worst-case test conditions.

analog input voltages one diode drop below ground or one diode drop greater than the V

analog inputs (5V) can cause this input diode to conduct—especially at elevated temperatures, and cause errors for analog inputs near full-scale. The spec allows

50mV forward bias of either diode. This means that as long as the analog V

be correct. To achieve an absolute 0V to 5V input voltage range will therefore require a minimum supply voltage of 4.950V

tolerance and loading.

the minimum time the clock is high or the minimum time the clock is low must be at least 300ns. The maximum time the clock can be high or low is 60µs.

comparator response time..

or V

IN

= 30kHz, 5V sine (f

IN

supply. Be careful, during testing at low VCC levels (4.5V), as high level

CC

does not exceed the supply voltage by more than 50mV, the output code will

REF

SAMPLING

ª 89kHz)

over temperature variations, initial

DC

5

ML2280, ML2283

DATA

OUTPUT

DATA

OUTPUT

t

1H

V

CC

CS

R

C

L

L

DO AND

SARS OUTPUTS

t

0H

V

CC

R

L

C

L

DO AND

SARS OUTPUTS

CS

GND

V

OH

GND

V

GND

V

V

t

1H

t

r

90%

50%

10%

t

1H

90%

t

0H

t

50%

10%

90%

t

0H

r

10%

CC

CC

OL

Figure 1. High Impedance Test Circuits and Waveforms

CLK

CS

DATA

IN (DI)

Data Input Timing

t

SET-UP

t

HOLD

CLK

CS

t

SET-UP

t

HOLD

ML2281 Start Conversion Timing

t

SET-UP

START CONVERSION

CLK

DATA

OUT (DO)

Data Output Timing

t

PD0, tPD1

SE

t

SET-UP

t

PD0, tPD1

DO

BIT 7

(MSB)

BIT 6

Figure 2. Timing Diagrams

6

Loading...

Loading...