Microchip Technology Inc PIC18F010-I-P, PIC18F010-I-SN, PIC18F020-I-P, PIC18F020-I-SN Datasheet

2001 Microchip Technology Inc. Preliminary DS41142A

PIC18F010/020

Data Sheet

High Performance Microcontrollers

DS41142A - page ii Preliminary 2001 Microchip Technology Inc.

“All rights reserved. Copyright © 2001, Microchip Technology

Incorporated, USA. Information contained in this publication

regarding device applications and the like is intended through

suggestion only and may be superseded by updates. No representation or warranty is given and no liability is assumed by

Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or

other intellectual property rights arising from such use or ot herwise. Use of Microchip’s products as critical components in

life support systems is not authorized except with express

written approval by Microchip. No licenses are conveyed,

implicitly or otherwise, under any intellectual property rights.

The Microchip logo and name are registered trademarks of

Microchip Technology Inc. in the U.S.A. and other countries.

All rights reserved. All other trademarks mentioned herein are

the property of their respective companies. No licenses are

conveyed, implicitly or otherwise, under any intellectual property rights.”

Trademarks

The Microchip name, logo, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, K

EELOQ, SEEVAL, MPLAB and The

Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and

other countries.

Total Endurance, ICSP, In-Circuit Serial Programming, FilterLab, MXDEV, microID, FlexROM, fuzzyLAB, MPASM,

MPLINK, MPLIB, PICDEM, ICEPIC, Migratable Memory,

FanSense, ECONOMONITOR and SelectMode are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick T erm Programming (SQTP) is a service mark

of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2001, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system

certification for its worldwide headquarters,

design and wafer fabrication facilities in

Chandler and Tempe, Arizona in July 1999. The

Company’s quality system processes and

procedures are QS-9000 compliant for its

PICmicro

®

8-bit MCUs, KEELOQ

®

code hoppin g

devices, Serial EEPROMs and microperipheral

products. In addition, Microchip’s quality

system for the design and manufacture of

development systems is ISO 9001 certified.

2001 Microchip Technology Inc. Preliminary DS41142A-page 1

PIC18F010/020

High Performance RISC CPU:

• C compiler optimized instru ction set

• Linear program memory addressing

- 4096 x 8 on-chip FLASH program memory

- 2048 x 8 on-chip FLASH program memory

(PIC18F010)

• Linear data memory addressing

- 256 x 8 general purpose registers

- 64 x 8 EEPROM

• Operating speed:

- DC - 40MHz clock input

- DC - 100 ns instruction cycle

- Internal oscillator with 5 program

selectable speeds (32kHz, 500kHz, 1MHz,

4MHz, 8MHz)

• 2.0V operation (4MHz)

• 16-bit wide instructions

• 8-bit wide data path

• 31 levels of hardware stack

• Software stack capability

• Multi-vector interrupt capability

• 8 x 8 multiply single cycle hardware

Special Microcontroll er Features:

• Power-on Reset (POR), Power-up Timer (PWR T )

and Oscillator Start-up Timer (OST)

• Brown-out Reset (BOR)

• Programmable Low Voltage Detection circuitry

(PLVD)

• Watchdog Timer (WDT) with its own on-chip

RC oscillator for reliable operation

• Programmable code protection

• Power saving SLEEP mode with Wake-up on Pin

Change

• In-Circuit Serial Programming (ICSPTM) via two

pins

• Low cost MPLAB

®

ICD available

Peripheral Features:

• High current sink/source 25mA/25mA

• Timer0: 8-bit/16-bit timer/counter with 8-bit

programmable prescaler

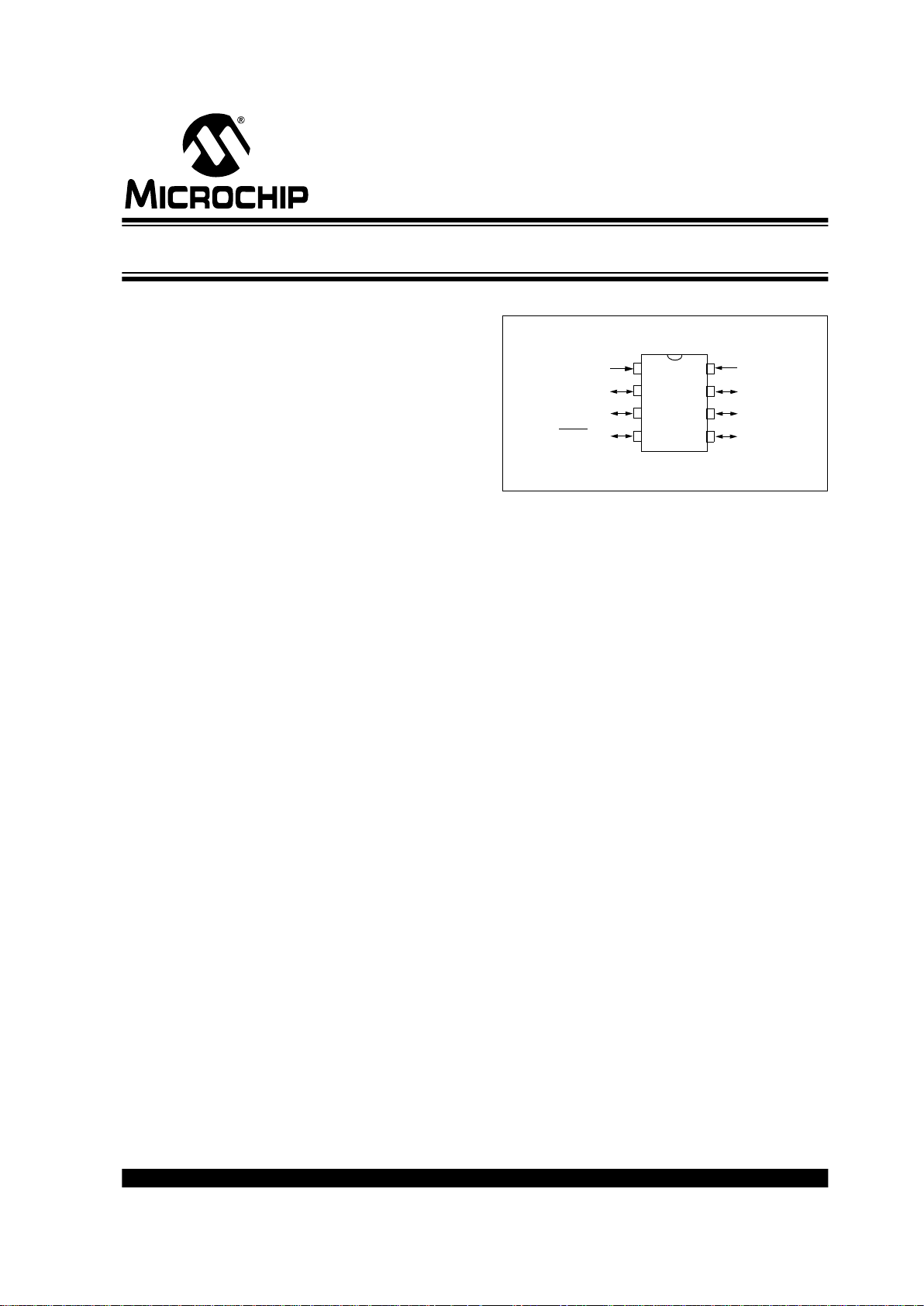

Pinout Diagram:

CMOS T echnology:

• Low power, high speed C MOS FLASH technology

• Fully static design

• Wide operating voltage range (2.0V to 5.5V)

• Commercial, Industrial and Extended

temperature ranges

• Low power consumption

PDIP, SOIC

8

7

6

5

1

2

3

4

VDD

RB5/OSC1/CLKIN

RB4/OSC2/CLKOUT

RB3/MCLR

/VPP

VSS

RB0/ICSPDAT

RB1/ICSPCLK

RB2/T0CKI/INT0

PIC18F010/020

High Performance Microcontr ollers

PIC18F010/020

DS41142A-page 2 Preliminary 2001 Microchip Technology Inc.

Table of Contents

1.0 Device Overview............................... ...... ..... ...... ....................................... ...... ...... ..... ........................................3

2.0 Oscillator Configurations....................................................................................................................................7

3.0 Reset................................................................................................................................................................15

4.0 Memory Organization.......................................................................................................................................23

5.0 Data EEPROM Memory...................................................................................................................................43

6.0 Table Read/Write Instructions..........................................................................................................................47

7.0 8 X 8 Hardware Multiplier.................................................................................................................................55

8.0 Interrupts..........................................................................................................................................................59

9.0 I/O Port.............................................................................................................................................................67

10.0 Timer0 Module.................................................................................................................................................73

11.0 Low Voltage Detect..........................................................................................................................................77

12.0 Special Features of the CPU............................................................................................................................83

13.0 Instruction Set Summary..................................................................................................................................95

14.0 Development Support.....................................................................................................................................139

15.0 Electrical Characteristics........................................................... .....................................................................145

16.0 DC and AC Characteristics Graphs and Tables.............................................................................................157

17.0 Packaging Information....................................................................................................................................159

Appendix A: Conversion Considerations ..................................................................................................................163

Appendix B: Migration from Baseline to Enhanced Devices.....................................................................................163

Appendix C: Migration from Mid-range to Enhanced Devices..................................................................................164

Appendix D: Migration from High-end to Enhanced Devices....................................................................................164

Index .......................................................................................................................................................................165

On-Line Support..........................................................................................................................................................169

Reader Response.......................................................................................................................................................170

PIC18F010/020 Product Identification System............................................................................................................171

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or co mm ents regarding this publication, please contact the Marketing Communications Department via

E-mail at docerrors@mail.microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150.

We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision

of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

• The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

Customer Notification System

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

2001 Microchip Technology Inc. Preliminary DS41142A-page 3

PIC18F010/020

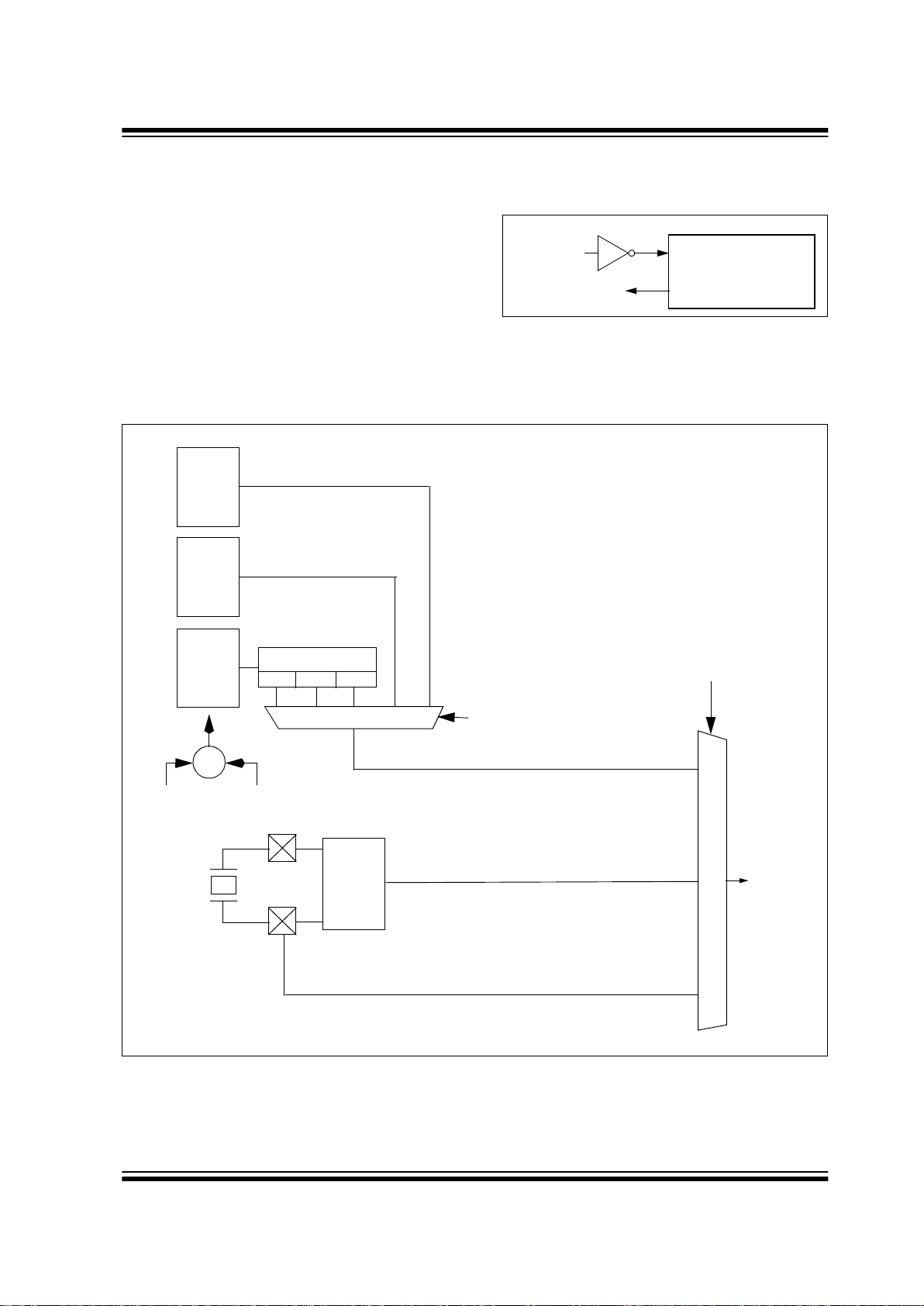

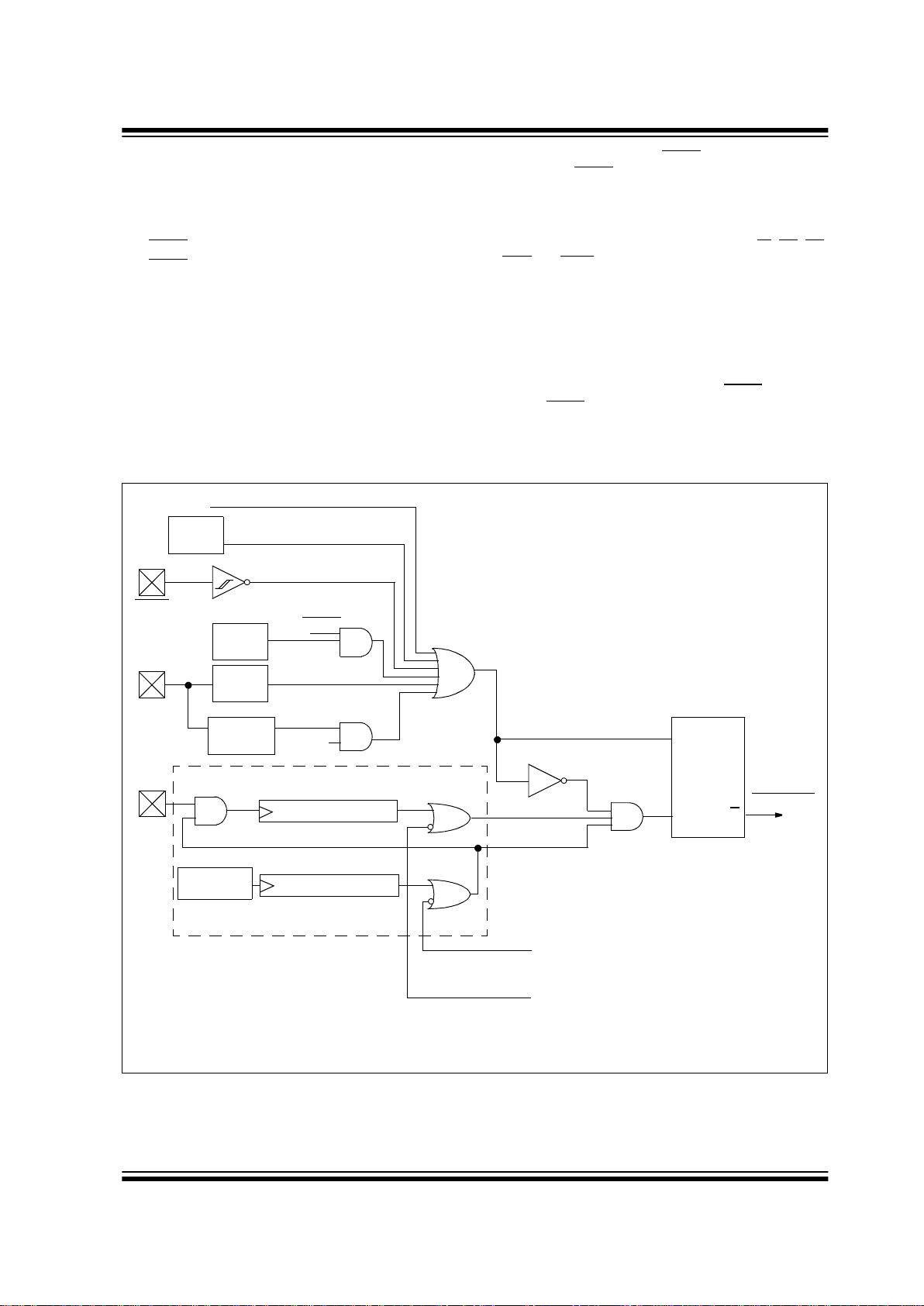

1.0 DEVICE OVERVIEW

This document co nta i ns dev ice sp ec if i c in for m at ion fo r

the PIC18F010/020 microcontrollers. These devices

come in 8-pin pac kages. Table1-1 is an overview of the

features. Figure 1-1 presents the block diag ram for th e

PIC18F010/020 devices and Table 1-2 gives the pin

descriptions.

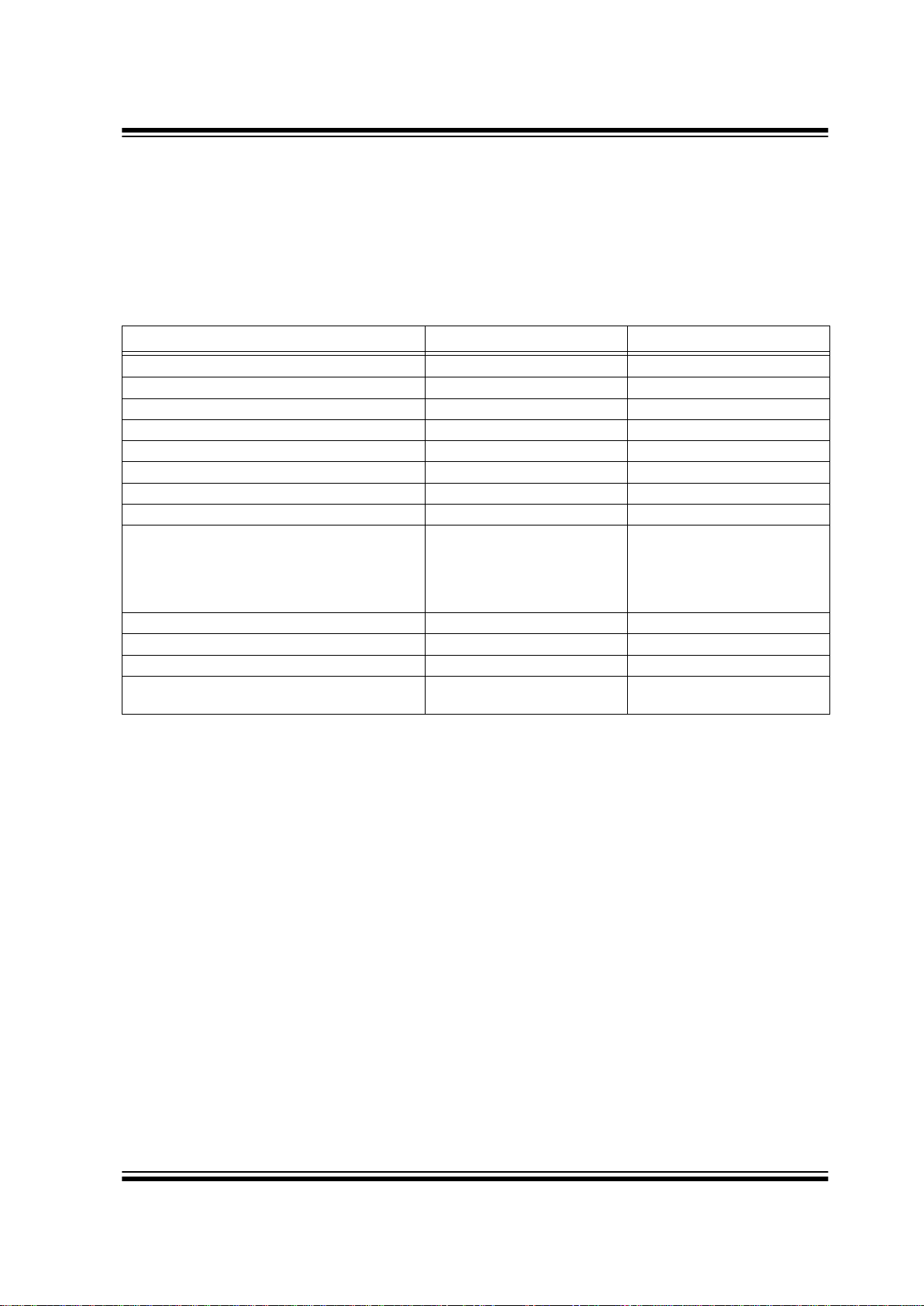

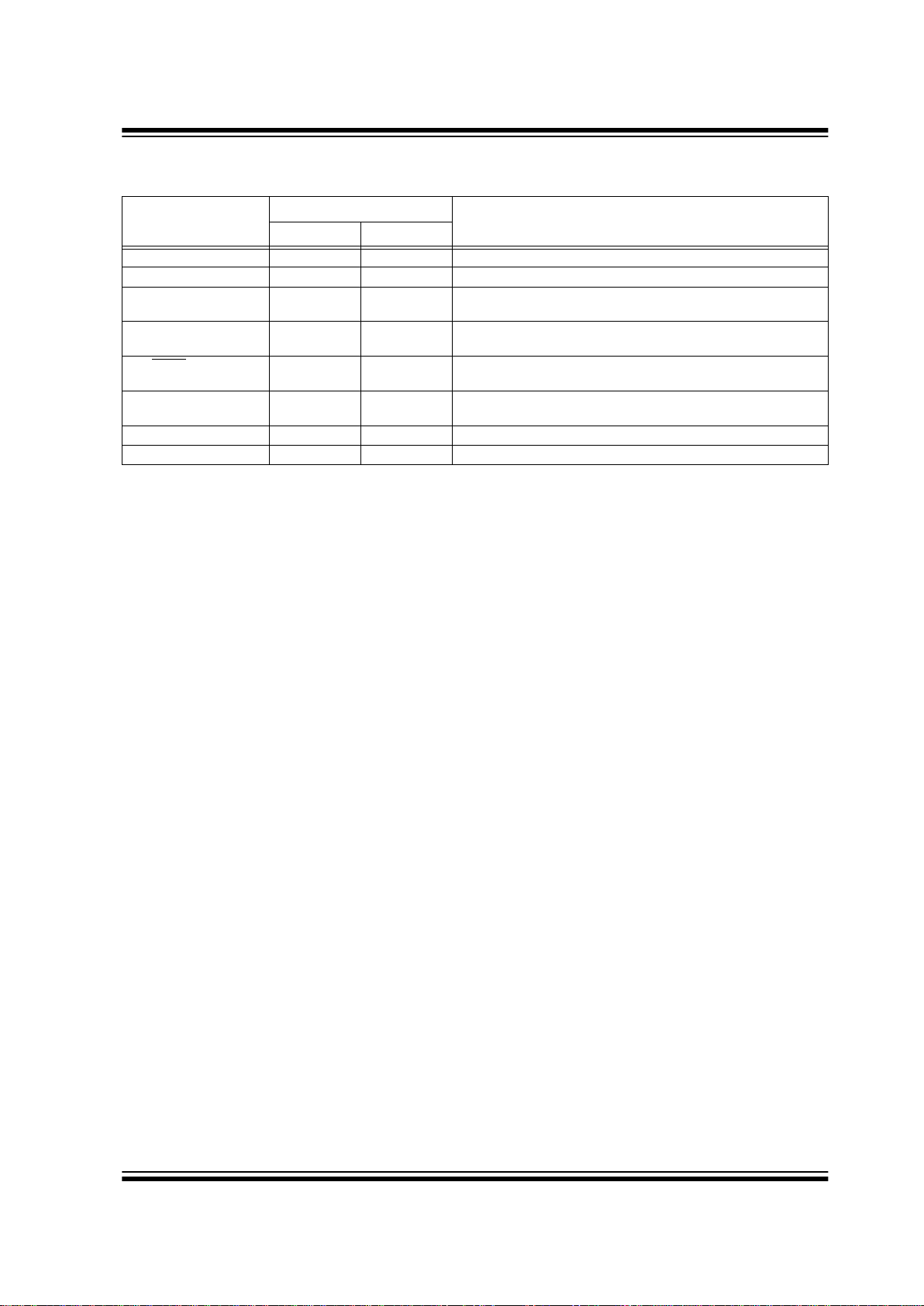

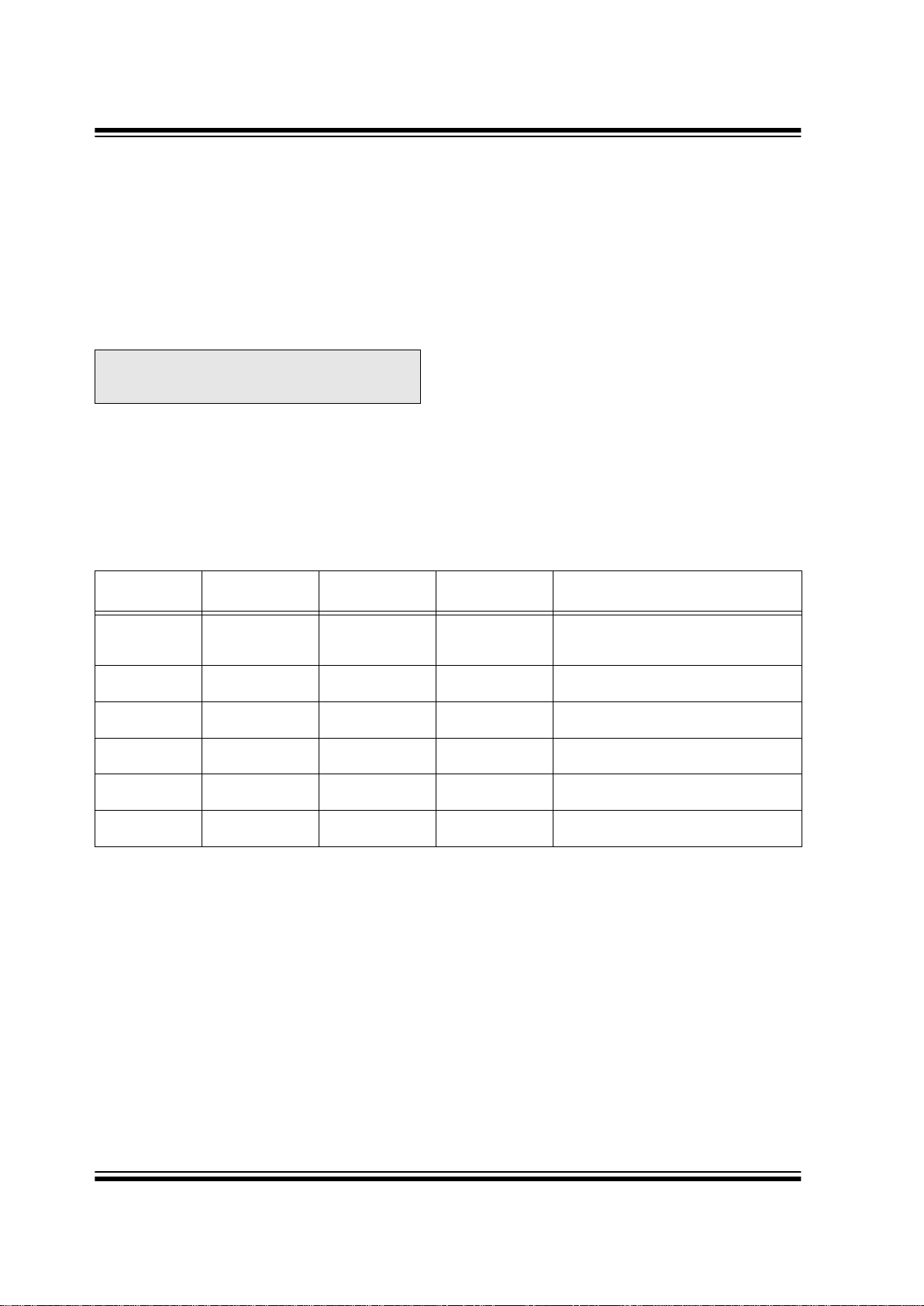

TABLE 1-1: DEVICE FEATURES

Features PIC18F010 PIC18F020

Operating Frequency DC - 40 MHz DC - 40 MHz

Program Memory (Bytes) 2K 4K

Program Memory (Instructio ns) 1024 2048

Data Memory (SRAM) 256 256

Data Memory (EEPROM) 64 64

Interrupt Sources 5 5

I/O Ports PORTB (6-bit) PORTB (6-bit)

Timers 1 (8/16-bit) 1 (8/16-bit)

RESETS (and Delays) POR, BOR,

RESET Instruction,

Stack Full,

Stack Underflow

(PWRT, OST)

POR, BOR,

RESET Instruction,

Stack Full,

Stack Underflow

(PWRT, OST)

Programmable Low Voltage Detect Yes Yes

Programmable Brown-out Reset Yes Yes

Instruction Set 75 75

Packages 8-pin PDIP

8-pin SOIC

8-pin PDIP

8-pin SOIC

PIC18F010/020

DS41142A-page 4 Preliminary 2001 Microchip Technology Inc.

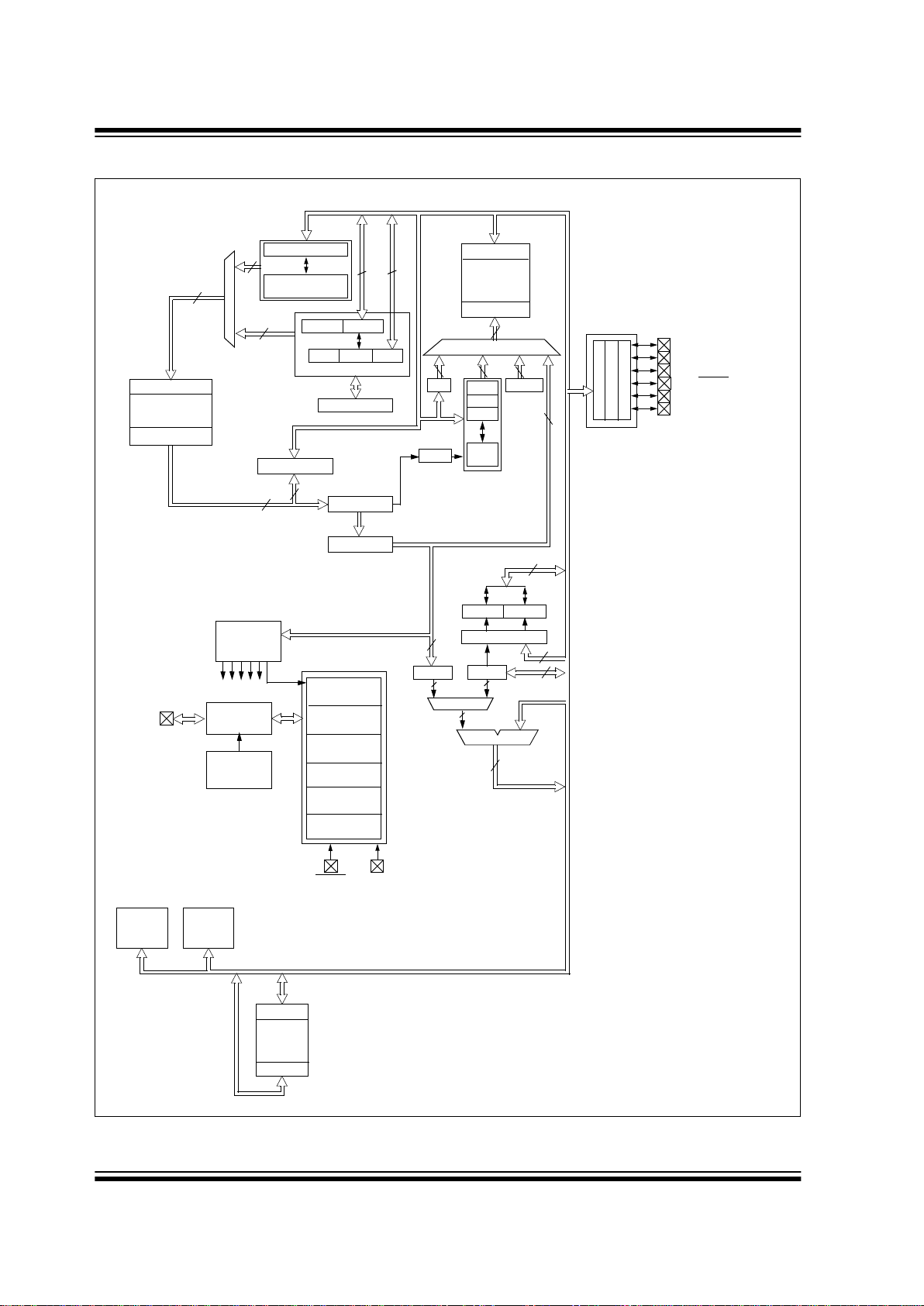

FIGURE 1-1: PIC18F010/020 BLOCK DIAGRAM

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

Instruction

Decode &

Control

OSC1/CLKIN

OSC2/CLKOUT

MCLR

VDD, VSS

PORTB

RB0/ICSPDAT

RB4/OSC2/CLKOUT

Brown-out

Reset

Timer0

Timing

Generation

RB1/ICSPCLK

Data Latch

Data RAM

256 bytes

Address Latch

Address<12>

12

Bank0,F

BSR

FSR0

FSR1

FSR2

inc/dec

logic

Decode

4

12

4

PCH PCL

PCLATH

8

31 Level Stack

Program Counter

PRODLPRODH

8 x 8 Multiply

W

8

BITOP

8

8

ALU<8>

8

Te st Mode

Select

Address Latch

Program Memory

(4 Kbytes)

Data Latch

20

21

16

8

8

8

Table Pointer<21>

inc/dec logic

21

8

Data Bus<8>

Table Latch

8

IR

12

3

ROM Latch

RB2/T0CKI/INT0

RB3/MCLR/VPP

PCLATU

PCU

RB5/OSC1/CLKIN

BOR

PLVD

Internal

DATA

EEPROM

64 bytes

EEDATA

EEADDR

Oscillator

2001 Microchip Technology Inc. Preliminary DS41142A-page 5

PIC18F010/020

TABLE 1-2: PIC18F010/020 PRODUCT PINOUT OVERVIEW

Bondpad Name

Devices

Function/Description

8-Pin PDIP 8-Pin SOIC

V

DD 11Power

V

SS 8 8 Ground

RB5/OSC1/CLKIN 2 2 Bi-directional I/O pin (TTL) with optional interrupt-on-change, clock

input, or oscillator input

RB4/OSC2/CLKOUT 3 3 Bi-directional I/O pin (TTL) with optional interrupt-on-change,

oscillator output, or CLKOUT output

RB3/MCLR

/VPP 4 4 Bi-directional I/O pin (TTL), open drain, with optional

interrupt-on-change, or Master Clear External Reset input (ST)

RB2/T0CKI/INT0 5 5 Bi-directional I/O pin (TTL) with optional interrupt-on-change, TMR0

clock input (ST), or interrupt input (ST)

RB1 6 6 Bi-directional I/O pin (TTL) with optional interrupt-on-change

RB0 7 7 Bi-directional I/O pin (TTL) with optional interrupt-on-change

PIC18F010/020

DS41142A-page 6 Preliminary 2001 Microchip Technology Inc.

NOTES:

2001 Microchip Technology Inc. Preliminary DS41142A-page 7

PIC18F010/020

2.0 OSCILLATOR

CONFIGURATIONS

2.1 Oscillator Types

The PIC18F010/020 can be operated in eight different

oscillator modes. Programming these modes is done

via the CONFIG1H register (FOSC2, FOSC1, and

FOSC0).

1. LP Low Power Crystal

2. XT Crystal/Resonator

3. HS High Speed Crystal/Resonator

4. EC External Clock

5. RC External Resistor/Capa citor

6. RCIO External Resistor/Capacitor with

I/O pin enabled

7. INTOSC Precision Internal Oscillator

8. INTOSCIO Precision Internal Oscillator with

I/O pin enabled

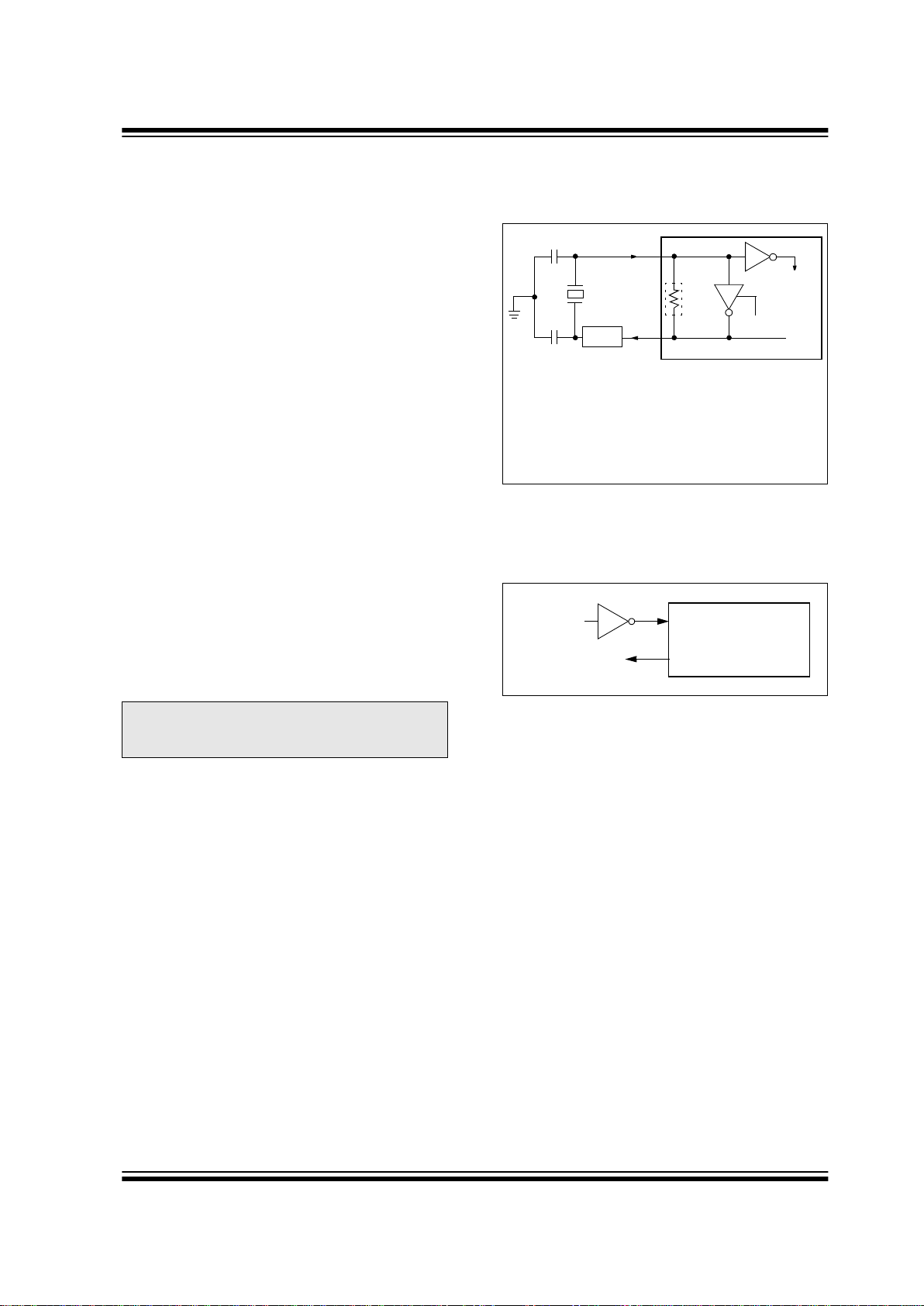

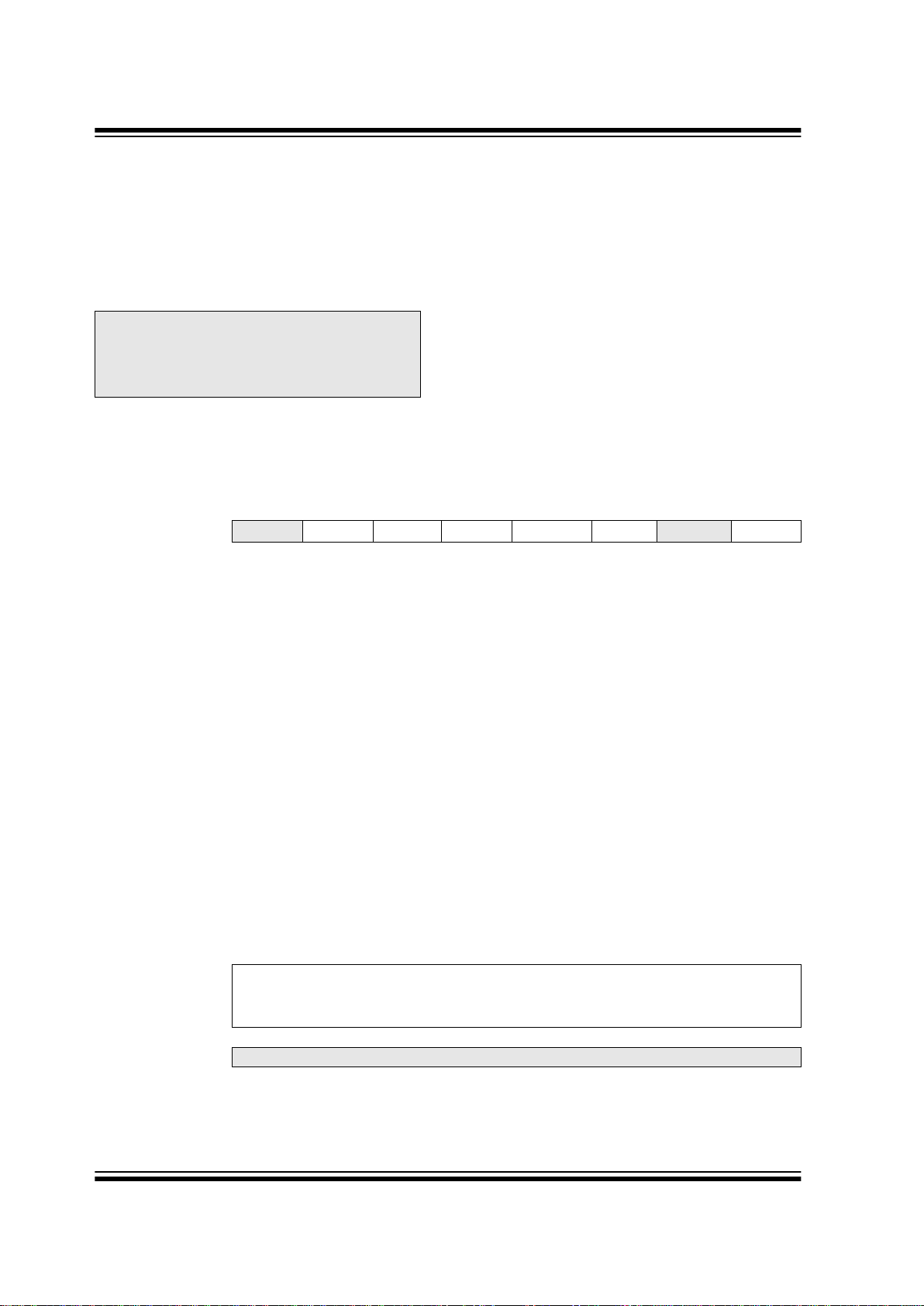

2.2 Crystal Oscillator/Ceramic

Resonators

In XT, LP, or HS oscillator modes, a crystal or ceramic

resonator is connected to the RB5/OSC1 and RB4/

OSC2 pins to establish oscillation. Figure 2-1 shows the

pin connections. An external clock source may also be

connected to the OSC1 pin in these modes, as sh own in

Figure 2-2.

The PIC18F010/020 oscillator design requires the use

of a parallel cut crystal.

FIGURE 2-1: CRYSTAL/CERAMIC

RESONATOR OPERATION

(HS, XT OR LP

OSC CONFIGURATION)

FIGURE 2-2: EXTERNAL CLOCK INPUT

OPERATION (HS, XT OR

LP OSC CONFIGURATION)

Note: Use of a series cut crystal may give a fre-

quency out of the crystal manufacturers

specifications.

Note 1: See Table 2-1 and Table 2-2 for recom-

mended values of C1 and C2.

2: A series resistor (R

S) may be required for AT

strip cut crystals.

3: R

F varies with the crystal chosen.

C1

(1)

C2

(1)

XTAL

OSC2

OSC1

RF

(3)

SLEEP

To

logic

RS

(2)

internal

RB5/OSC1

RB4/OSC2

Open

Clock from

ext. system

PIC18F010/020

PIC18F010/020

DS41142A-page 8 Preliminary 2001 Microchip Technology Inc.

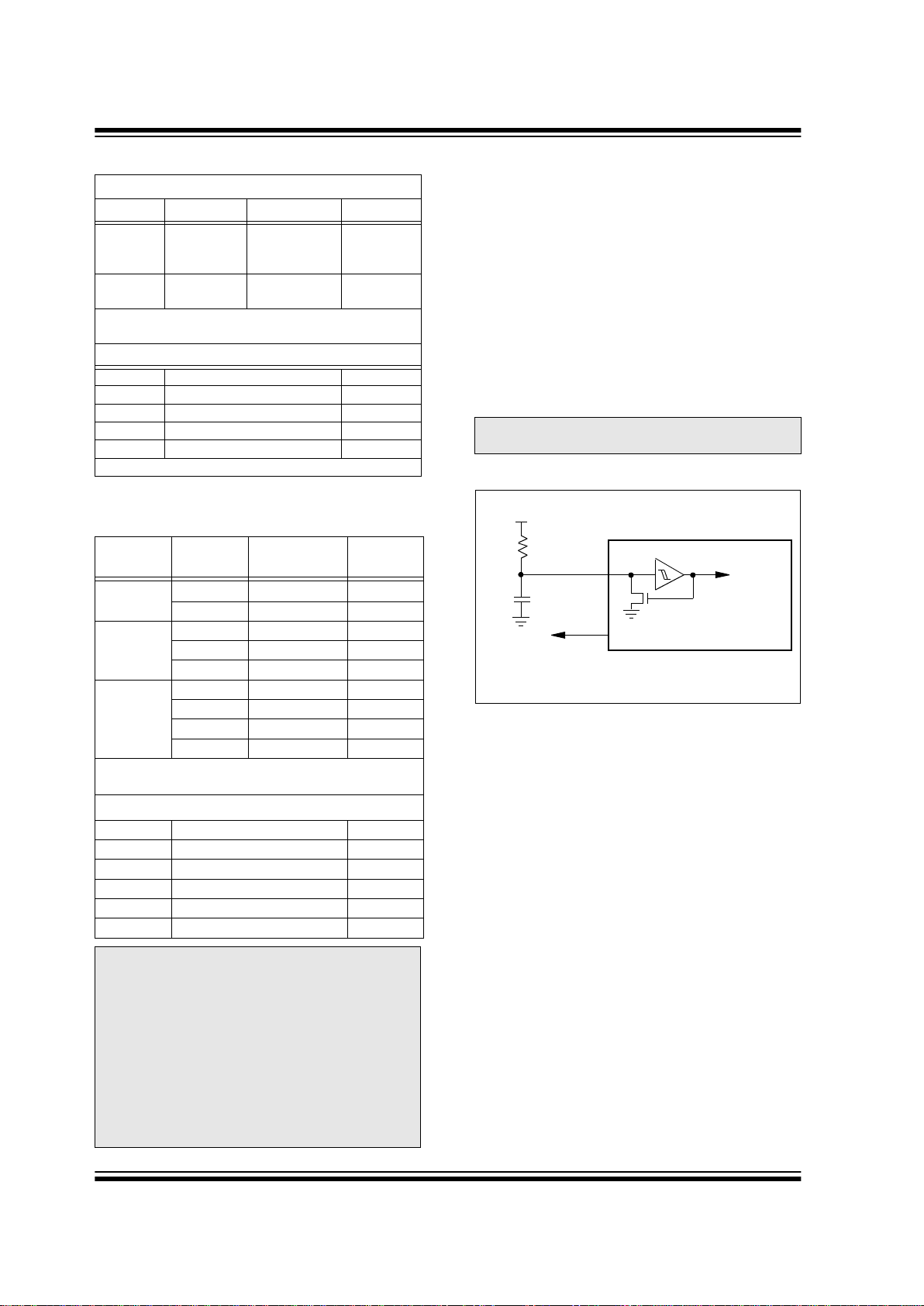

TABLE 2-1: CERAMIC RESONATORS

TABLE 2-2: CAPACITOR SELECTION FOR

CRYSTAL OSCILLATOR

2.3 RC Oscillator

For applications where precise timing is not a requirement, the RC and RCI O oscillator option s are availabl e.

The operation and functionality of the RC oscillator is

dependent on a number of varia bles. The RC oscil lat or

is a function of the supply voltage, the resistor (REXT)

and capacitor (C

EXT) values, and the operating temper-

ature. The oscillator fre quency will va ry from unit to unit

due to normal process parameter variation. Plus, the

difference in le ad fram e c apacitance betw ee n package

types will also affect the oscillation frequency, especially for low C

EXT values. The user also needs to

account for the tolerance of the external R and C components. Figure2-3 shows how the R /C comb inat ion i s

connected.

FIGURE 2-3: RC OSCILLATOR MODE

In the RC mode, the oscilla tor frequen cy divi ded by 4 is

available on the OS C2 pin. This signal ma y be used for

test purposes, or to synchronize other logic. In the

RCIO mode, the OSC2 pin be comes a general purp ose

I/O pin. This pin is RB4 of PORTB.

2.4 The Internal Oscillator

The INTOSC and INTOSCIO device options are available to minimize part count and cost, wh ile ma xim iz in g

the number of I/O pins. There are five d ifferent frequencies of which the user h as the opti on to select. They ar e

32 kHz, 500 kHz, 1 MHz, 4 MHz, and 8 MHz. The 1

MHz, 4 MHz, and 8 MHz internal clock selections are

all derived from one 8 MHz clo ck sou rce, and the other

two are produced ind ependently. T uning is available for

the 1 MHz, 4 MHz, and 8 MHz options; refer to

Section 2.10.

Ranges Tested:

Mode Freq. OSC1 OSC2

XT 455 kHz

2.0 MHz

4.0 MHz

68 - 100 pF

15 - 68 pF

15 - 68 pF

68 - 100 pF

15 - 68 pF

15 - 68 pF

HS 8.0 MHz

16.0 MHz

10 - 68 pF

10 - 22 pF

10 - 68 pF

10 - 22 pF

These values are for design guidance only.

See notes at bottom of page.

Resonators Used:

455 kHz Panasonic EFO-A455K04B ± 0.3%

2.0 MHz Murata Erie C SA2.00MG ± 0.5%

4.0 MHz Murata Erie C SA4.00MG ± 0.5%

8.0 MHz Murata Erie CSA8.00MT ± 0.5%

16.0 MHz Murata Erie CSA16.00MX ± 0.5%

All resonators used did not have built-in capacitors.

Osc Type

Crystal

Freq.

Cap. Range

C1

Cap.

Range C2

LP 32.0 kHz 33 pF 33 pF

200 kHz 15 pF 15 pF

XT 200 kHz 47-68 pF 47-68 pF

1.0 MHz 15 pF 15 pF

4.0 MHz 15 pF 15 pF

HS 4.0 MHz 15 pF 15 pF

8.0 MHz 15- 33 pF 15-33 pF

20.0 MHz 15-33 pF 15-33 pF

25.0 MHz TBD TBD

These val ues are for de sign guidance only.

See notes at bottom of page.

Crystals Used

32.0 kHz Epson C-001R32.768K-A ± 20 PPM

200 kHz STD XTL 200.000KHz ± 20 PPM

1.0 MHz ECS ECS-10-13-1 ± 50 PPM

4.0 MHz ECS ECS-40-20-1 ± 50 PPM

8.0 MHz EPSON CA-301 8.000M-C ± 30 PPM

20.0 MHz EPSON CA-301 20.000M-C ± 30 PPM

Note 1: Recommended values of C1 and C2 are

identical to the ranges tested (Table 2-1).

2: Higher capacitance increases the stability

of the oscillator, but also increases the

start-up time.

3: Since each resonator/crystal has its own

characteristics , the user sh ould co nsult the

resonator/crystal manufacturer for appropriate values of external components.

4: Rs may be required in HS mode, as well as

XT mode, to avoid overdriv ing crys tals with

low drive level specification.

Note: The RC oscillator is not recommended for

applications that require precise timing.

OSC2/CLKO

CEXT

REXT

PIC18F010/020

OSC1

F

OSC/4

Internal

Clock

VDD

VSS

Recommended values: 3 kΩ ≤ REXT ≤ 100 kΩ

C

EXT > 20pF

2001 Microchip Technology Inc. Preliminary DS41142A-page 9

PIC18F010/020

2.5 External Clock Input

The EC oscillator mode requires an external clock

source to be conne cted to the OSC1 pi n. The feedback

device between OSC1 and OSC2 is turned off in this

mode to save current. There is no oscillator start-up

time required after a Power-on Reset or after a recovery from SLEEP mode.

In the EC oscillator mode, the oscillator frequency

divided by 4 is available on the OSC2 pin. This signal

may be used for t est pu rp os es or to sy nc hr o niz e o t he r

logic. Figure 2-4 shows the pin connections fo r the EC

oscillator mode.

FIGURE 2-4: EXTERNAL CLOCK INPUT

OPERATION (EC OSC

CONFIGURATION)

FIGURE 2-5: PIC18F010/020 OSCILLATOR CONFIGURATION

OSC1

OSC2

F

OSC/4

Clock from

ext. system

PIC18F010/020

MUX

Configuration bits

OSCOUT

OSCIN

Crystal

Osc

SYSCLK

Ext Osc

and

Divider

82

1

IRCF Speed Selects

MUX

OSCTUNEOSCCAL

+

Analog

Summation

External Clock In

500kHz

Internal

8MHz

Internal

OSC

OSC

32kHz

Internal

OSC

PIC18F010/020

DS41142A-page 10 Preliminary 2001 Microchip Technology Inc.

2.6 Two-Speed Clock Start-up Mode

In order to minimize the latency between oscillator

start-up and code execution, a mode which allows the

system clock to initially use the internal clock, may be

selected with IESO (Internal-External Switchover) bit.

In this mode and upon RESET, the system will begin

execution with the internal oscillator at the frequency

selected by the IRCFx bits of the OSCCON register.

After the OST h as timed o ut, a glitchle ss switcho ver will

be made to the oscillator mode selected by F

OSCx in

the CONFIG1H register. The software may read the

OSTO bit to determine when the switchover takes

place, so that any software timing delays may be

adjusted.

Wake-up from SLEEP causes a unique start-up procedure. The power supply is assumed to be stable, since

neither the POR nor the BOR Resets have been

invoked. This assumption allows the Power-on Timer

(PWRT) time-out to be bypassed, and only the OST

time-out to be used. This results in almost immediate

code execution with the minimum of delay. The internal

oscillator frequency can be selected to be close to final

crystal frequency to reduce timing differences , or a lower

frequency can be chosen to reduce power consumption.

REGISTER 2-1: OSCCON REGISTER (ADDRESS FD3h)

Note: Only on Power-on Reset, the register con-

tents are zeroed by the POR circuitry and

the frequency selectio n is forced to 32 kHz.

The register is not effected by any other

forms of RESET.

U-0 R/W-0 R/W-0 R/W-0 R-0 R/W-0 U-0 R/W-0

— IRCF2 IRCF1 IRCF0 OSTO IESO — SCS

bit 7 bit 0

bit 7 Unimplemented: Read as ‘0’

bit 6-4 IRCF<2:0>: Internal Oscillator Frequency Select bits

000 = 32 kHz

001 = Reserved

010 = Reserved

011 = 500 kHz

100 = 1 MHz

101 = Reserved

110 = 4 MHz

111 = 8 MHz

bit 3 OSTO: Oscillator Start-up Time-out Status bit

1 = Oscillator Start-up Timer has timed out

0 = Oscillator Start-up Timer running

bit 2 IESO: Internal-External Switchover bit

1 = Start with internal oscillator, then switch over to selected oscillator mode after OST

0 = No switch from internal oscillator from RESET

bit 1 Unimplemented: Read as ‘0’

bit 0 SCS: System Clock Switch bit

1 = Clock source comes from internal oscillator input

0 = Clock source comes from external clock source on OSC1

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

Note: This register must be unlocked to modify, see Section 12.4.

2001 Microchip Technology Inc. Preliminary DS41142A-page 11

PIC18F010/020

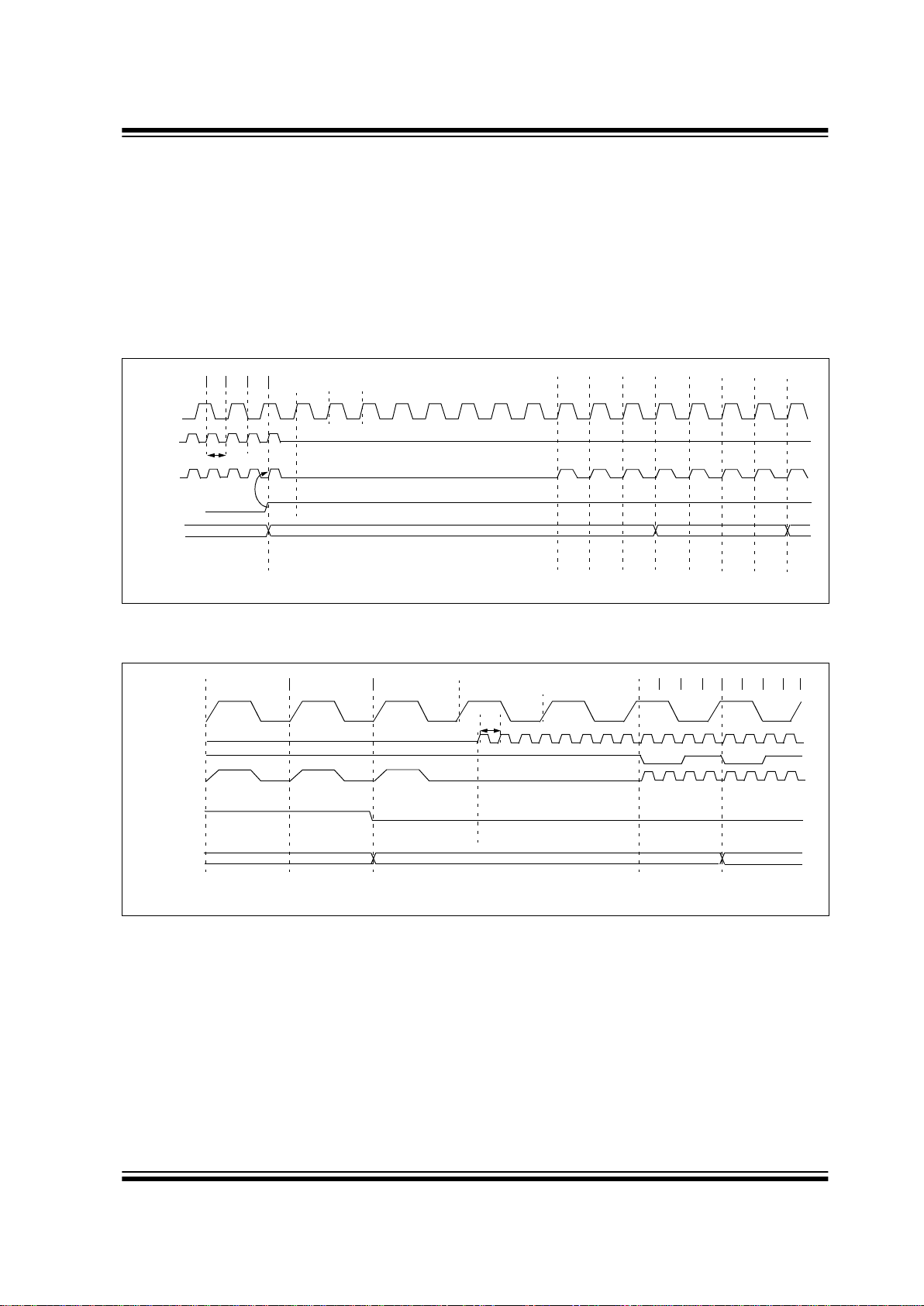

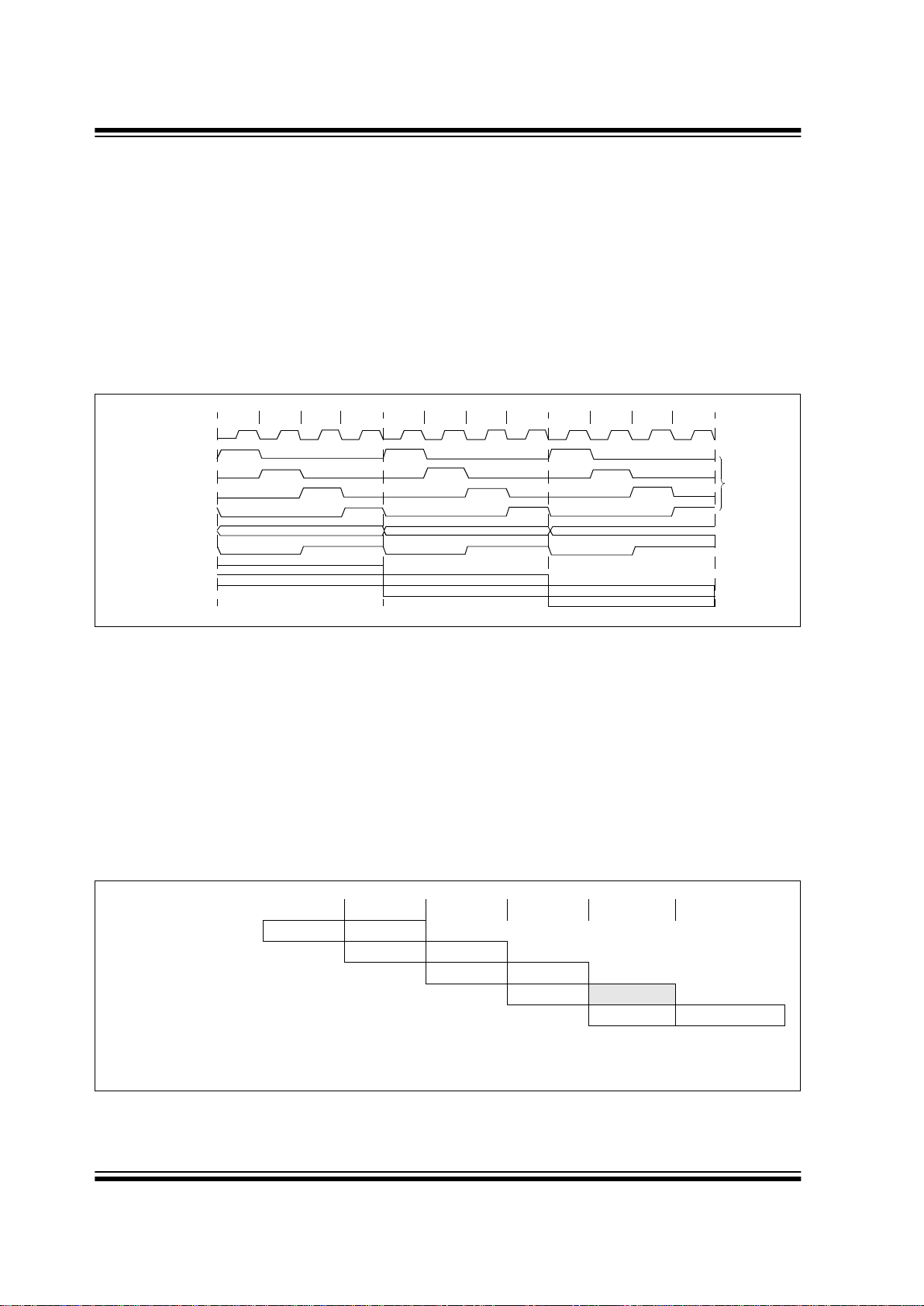

2.6.1 OSCILLATOR TRANSITIONS

The PIC18F010/020 devices contain circuitry to prevent "glitches" when switching between oscillator

sources. Essentially, the circuitry waits for eight rising

edges of the clock source that the processor is switching to. This en sures tha t the new clock s ource is stabl e

and that its pulse wid th will no t be less than the sho rtest

pulse width of the two clock sources.

A timing diagram, indicating th e transition f rom the in ternal oscillator to the external crystal is shown in Figure 2-6.

The internal oscillator is assumed to be running all the

time. After the OST bi t is set, the pr oce ssor is froz en at

the next occurring Q1 cycle. Af ter eight synchroniza tion

cycles are counted from the external oscillator, operation resumes. No additional delays are required after

the synchronization cycles.

FIGURE 2-6: TIMING DIAGRAM FOR TRANSITION FROM EXTERNAL OSCILLATOR TO

INTERNAL OSCILLATOR

FIGURE 2-7: TIMING FOR TRANSITION BETWEEN INTERNAL OSCILLATOR AND OSC1 (EC)

Q3Q2Q1Q4Q3Q2

OSC1

Internal

OSTO

(OSCCON<0>)

Program

PC + 2PC

Note 1: Delay on internal system clock is eight oscillator cycles for synchronization.

INTOSC

Q4 Q1

PC + 4

Q1

Clock

Counter

System

Q2 Q3 Q4 Q1

TOSC

21 34 5678

Q3 Q4

Q1

Q1 Q2 Q3 Q4 Q1 Q2 Q3

OSC1

Internal System

SCS

(OSCCON<0>)

Program Counter

PC PC + 2

Note 1: Internal oscillator mode assumed.

PC + 4

INTOSC

Clock

OSC2

Q4

TOSC

1

23

45678

PIC18F010/020

DS41142A-page 12 Preliminary 2001 Microchip Technology Inc.

2.7 Effects of SLEEP Mode on the

On-chip Oscillator

When the device exe cutes a SLEEP i nstructio n, the onchip clocks and oscillator are turn ed off and the device

is held at the beginning of an instruction cycle (Q1

state). With the oscill ato r of f, the OSC 1 and OS C2 si gnals will stop oscill ating. Since all the transis tor s w itch-

ing currents have been removed, SLEEP mode

achieves the lowest current consumption of the device

(only leakage currents). Enabling any on-chip feature

that will operate during SL EEP will increas e the current

consumed during SLEEP. The user can wake from

SLEEP through external RESET, Watchdog Timer

Reset or through an interrupt.

TABLE 2-3: OSC1 AND OSC2 PIN STATES IN SLEEP MODE

OSC Mode OSC1 Pin OSC2 Pin

Internal Oscillator Floating, external resistor should pull

high

At logic low

RCIO Floating, external resistor should pull

high

Configured as PORTB, RB4

EC Floating At logic low

LP, XT, and HS Feedback inverter disabled, at quiescent

voltage level

Feedback inverter disabled, at quiescent

voltage level

Note: See Table 3-1 in the RESET Section, for time-outs due to SLEEP and MCLR

Reset.

2001 Microchip Technology Inc. Preliminary DS41142A-page 13

PIC18F010/020

2.8 Power-up Delays

Power-up delays are controlled by two timers, so that

no external RESET circuitry is required for most applications. The delays ensure that the device is kept in

RESET until the device power sup ply and clock are st able. For additional information on RESET operation,

see the “RESET” section.

The first timer is the Power-up Timer (PWRT), which

optionally provides a fix ed delay of 72 ms (nominal) on

power-up only (POR and BOR). The second timer is

the Oscillator Start-up Timer OST, intended to keep the

chip in RESET until the crystal oscillator is stable.

2.9 Frequency Calibrations

The 8 MHz frequency is cali brated at the fact ory. Since

the 4 MHz and 1 MHz cloc k outputs are derived digita lly

from the 8 MHz, the accuracy specifications of the 4

MHz and 1 MHz clocks are the same as the 8 MHz.

The 500 kHz and 32 kHz frequencies are not calibrated. The 500 kHz and 32 kHz are nominal frequencies. Their accuracy specifications are shown in the

Specifications section.

2.10 Frequency Tuning in User Mode

In addition to the factory calibration, 8 MHz frequency

can be tuned in the user’s application. This frequency

tuning capabili ty allows user to deviate from the fac tory

calibrated frequency. The user can tune the frequency

by writing to the OSCTUNE register. See Register 2-2

for details of the OSCTUNE register. The tuning range

of the 8 MHz oscillator is ±1 MHz, or ±12.5% nominal.

See the Specifications section for further specification

details.

Since the 4 MHz and 1 MHz are derived from the 8

MHz, the tuning range of the 4 MHz is ±500 kHz nominal, and the tuning range of the 1 MHz is ±125 kHz

nominal. The tuning sensitivity (%F

INTOSC/bit) is con-

stant throughout the frequency selections and tuning

range.

REGISTER 2-2: OSCTUNE REGISTER (ADDRESS 0F9Bh)

Note: Frequency tuning is not available in the

500 kHz and 32 kHz frequencies.

U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

— — TUN5 TUN4 TUN3 TUN2 TUN1 TUN0

bit 7 bit 0

bit 7-6 Unimplemented: Read as ‘0’

bit 5-0

TUN<5:0>: 6-bit Frequency Tuning

011111 = Maximum frequency

011110

•

•

•

000001

000000 = Center frequency. Oscillator module is running at the calibrated frequency.

111111

•

•

•

100000 = Minimum frequency

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

PIC18F010/020

DS41142A-page 14 Preliminary 2001 Microchip Technology Inc.

2.11 Base Frequency Change

There are two methods to change frequency during

normal program operation. One option is to switch frequencies using the internal oscillator only; IRCF<2:0>

in the OSCCON register selects the internal oscillator

frequency. Refer to Register 2-1.

Switching for an external clock to an internal oscillator

and vice versa is also possible. Use the SCS bit in the

OSCCON register to select an external or internal cl ock

source.

2.12 Oscillator Delay Upon Start-up

and Base Frequency Change

When the INTOSC Oscillator Module starts up, an

8-cycle delay of the base frequency is invoked. During

this delay, the FINTOSC output signal is held at ‘0’.

The INTOSC Oscillator Module also allows user to

change frequency during run time. For example, the

frequency can be ch anged from 8 M Hz to 32 kH z, while

the device is operating. When the application requires

a base frequency change, a delay of 8 cycles of the

new base frequency is invoked.

Writing to the OSCTUNE register will not cause any

delay. In applications where the OSCTUNE register is

used to shift the F

INTOSC frequency, the application

should not expect the F

INTOSC frequency to stabilize

immediately. In this case, the frequency m ay shif t gradually toward the n ew v al ue. The time for this freque nc y

shift is less than 8 cycles of the base frequency.

Table 2-4 below, shows examples of when the oscillator delay is invoked.

TABLE 2-4: OSCILLATOR DELAY EXAMPLES

Note: The OSCEN bit in the CONFIG 1H configu-

ration byte must be set to allow clock

switching.

Old Frequency New Frequency

New Base

Frequency

Oscillator Delay Comments

8 MHz 4 MHz or 1 MHz No None The 8 MHz, 4 MHz, and 1 MHz are all

running from the same 8 MHz base

frequency.

500 kHz 32 kHz 32 kHz 250µS nominal Base frequency changes from 500 kHz

to 32 kHz.

4 MHz 32 kHz 32 kHz 250µS nominal Base fr equ enc y ch anges from 8 MHz to

32 kHz.

500 kHz 8 MHz 8 MHz 1µS nominal Base frequency changes from 500 kHz

to 8 MHz.

Off or SLEEP

mode

1 MHz 8 MHz 1µS nominal Upon power-up and wake-up from

SLEEP, there is always oscillator delay.

Off or SLEEP

mode

500 kHz 500 kHz 16µS nominal Upon power-up and wake-up from

SLEEP, there is always oscillator delay.

2001 Microchip Technology Inc. Preliminary DS41142A-page 15

PIC18F010/020

3.0 RESET

The PIC18F010/020 differentiates between various

kinds of RESET:

a) Power-on Reset (POR)

b) MCLR

Reset during normal operation

c) MCLR Reset during SLEEP

d) Watchdog Timer (WDT) Reset (during normal

operation)

e) Programmable Brown-out Reset (BOR)

f) RESET Instruction

g) Stack Full Reset

h) Stack Underflow Reset

Most registers are una ffected b y a RESET. Their status

is unknown on POR and unchanged by all other

RESETS. The other registers are forced to a “RESET

state” on Power-on Reset, MCLR

, WDT Reset, Brown-

out Reset, MCLR

Reset during SLEEP and by the

RESET instruction.

Most registers are not affected by a WDT wake-up,

since this is viewed as the resumption of normal operation. Status bits from the RCON register, RI

, TO, PD,

POR

and BOR, are set or cleared differently in different

RESET situations, as i ndicated in Table 3-2. These bit s

are used in software to determine the nature of the

RESET. See Table 3-3 for a full description of the

RESET states of all registers.

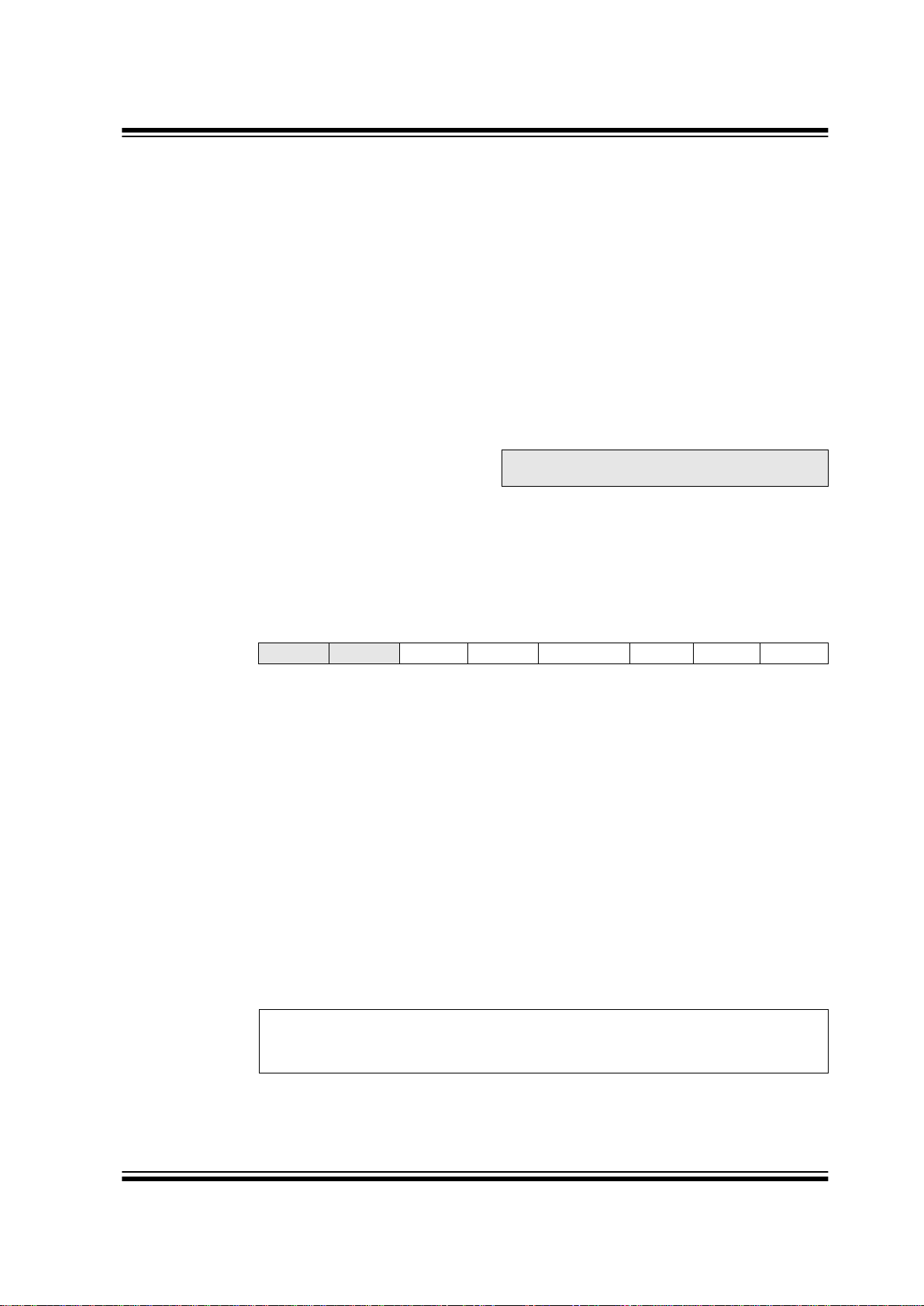

A simplified block diagram of the on-chip RESET circuit

is shown in Figure 3-1.

The Enhanced MCU devices have a MCLR

noise filter

in the MCLR

Reset path. The filter will detect and

ignore small pulses.

FIGURE 3-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

S

R

Q

External Reset

MCLR

WDT

Module

V

DD Rise

Detect

OST/PWRT

On-chip

Internal Osc

(1)

WDT

Time-out

Power-on Reset

OST

10-bit Ripple Counter

PWRT

Chip_Reset

10-bit Ripple Counter

Reset

Enable OST

(2)

Enable PWRT

SLEEP

Note 1: This is a separate oscillator from the internal oscillator of the CLKIN pin.

2: See Table3-1 for time-out situations.

Brown-out

Reset

BOREN

RESET

Instruction

Stack

Pointer

Stack Full/Underflow Reset

VDD

OSC1

PIC18F010/020

DS41142A-page 16 Preliminary 2001 Microchip Technology Inc.

3.1 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when

V

DD rise is detected. To take advantage of the POR c ir-

cuitry, tie the MCLR

pin directly (or through a resistor)

to V

DD, or disable MCLR. This will eliminate external

oscillator components usually needed to create a

Power-on Reset delay. A maximum rise time for V

DD is

specified (parameter D004). For a slow rise time, see

Figure 3-2.

When the device starts normal operation (exits the

RESET condition), device operating parameters (voltage, frequency, temperature,...) must be met to en su re

operation. If these cond itions are not met, the de vice

must be held in RESET until the operating conditions

are met. Brown-out Reset may be used to meet the

voltage start- up condition.

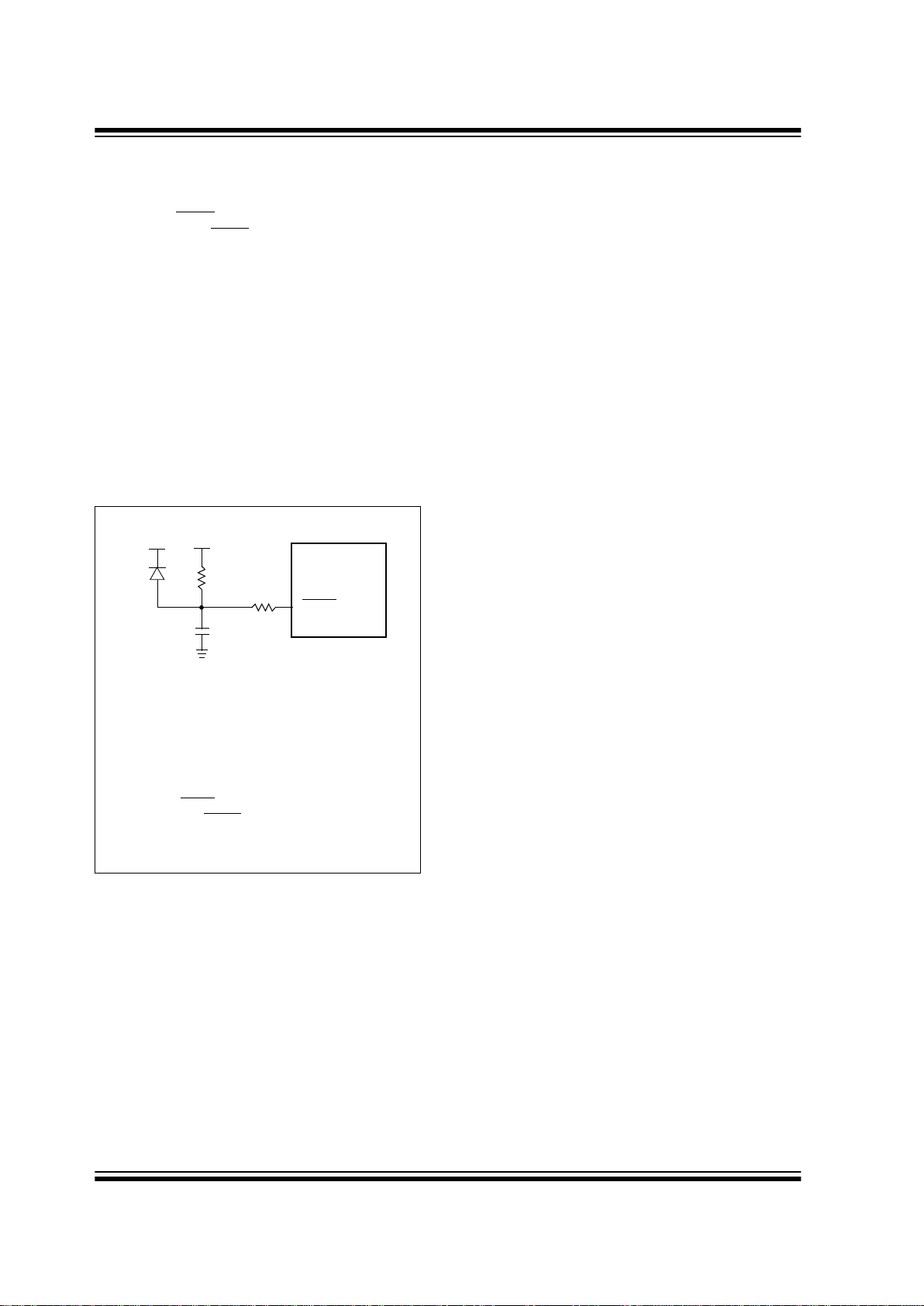

FIGURE 3-2: EXTERNAL POWER-ON

RESET CIRCUIT (FOR

SLOW V

DD POWER-UP)

3.2 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out

(parameter #33) only on power-up from the POR or

BOR, if enabl ed. The Pow er-up Timer o perates on an

internal oscillator . The chi p is kept in RESET as long a s

the PWRT is active. The PWRT’s time delay allows

V

DD to rise to an accep tabl e lev el. A con figurat ion bit i s

provided to enable/disable the PWRT.

The power-up time delay wil l vary from chip-to-ch ip due

to V

DD, temperature and process variation. See DC

parameter #33 for details.

3.3 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024

oscillator cycle (from OSC1 input) delay after the

PWRT delay is over (para meter #32). This ensures th at

the crystal oscillator or resonator has started and

stabilized.

The OST time-out is invoked only for XT, LP and HS

modes and only on Power-on Reset or wake-up from

SLEEP.

3.4 Brown-out Reset (BOR)

A configuration bit, BOREN, can disable (if clear/

programmed), or enable (if set) the Brown-out Reset

circuitry. If VDD falls below parameter D005 for greater

than parameter #35, the brown-out situation will reset

the chip. A RESET may not occur if V

DD falls below

parameter D005 for less than p arameter #35. The chip

will remain in Brown-out Reset until V

DD rises above

BV

DD. The Power- up Timer will then be invok ed and

will keep the chip in RESET an additional time delay

(parameter #33). If V

DD drops below BVDD while the

Power-up Timer is running, the chip will go back into a

Brown-out Reset and the Power-up T im er will be initialized. Once V

DD rises above BVDD, the Power-up Timer

will execute the additional time delay.

Note 1: External Power-on Reset circuit is required only

if the V

DD power-up slope is too slow. T he diode

D helps discharge the capacitor quickly when

V

DD powers down.

2: R < 40k

Ω is recommended to make sure that

the voltage drop across R does not violate the

device’s electrical specification.

3: R1 = 100

Ω to 1kΩ will limit any current flowing

into MCLR

from external capacitor C, in the

event of MCLR/

VPP pin breakdown due to

Electrostatic Discharge (ESD), or Electrical

Overstress (EOS).

C

R1

R

D

V

DD

MCLR

PIC18F010/020

2001 Microchip Technology Inc. Preliminary DS41142A-page 17

PIC18F010/020

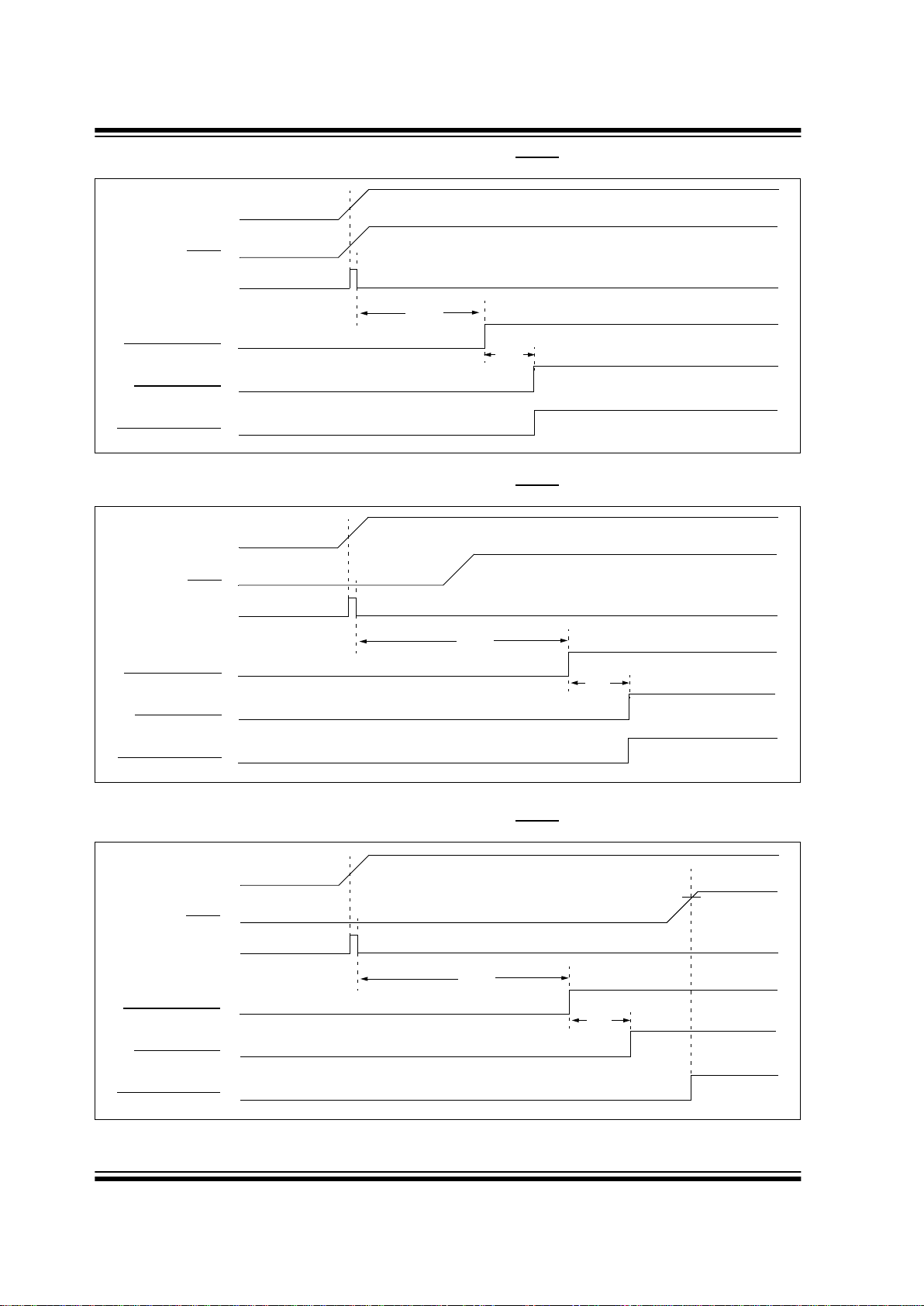

3.5 Time-out Sequence

On power-up, the time-ou t sequenc e is as foll ows: first,

PWRT time-out is invoked af ter the POR time delay has

expired; then, OST is activated. The total time-out will

vary based on oscillator con figura tion and the st atus of

the PWRT. For example, in Internal Oscillator mode

with the PWRT disabled , there will be no time-o ut at all.

Figure 3-3, Figure 3-4, Figure 3-5 and Figure 3-6

depict time-out sequences on power-up.

Since the time-outs occur from the PO R pulse, if MCLR

is kept low long enough, the time-outs will expire.

Bringing MCLR

high will begin execution immediately

(Figure 3-5). This is useful for testing purposes or to

synchronize more than one PIC18F010/020 device

operating in parallel.

Table 3-2 shows the RESET conditions for some

Special Function Registers, while Table 3-3 shows the

RESET conditions for all the registers.

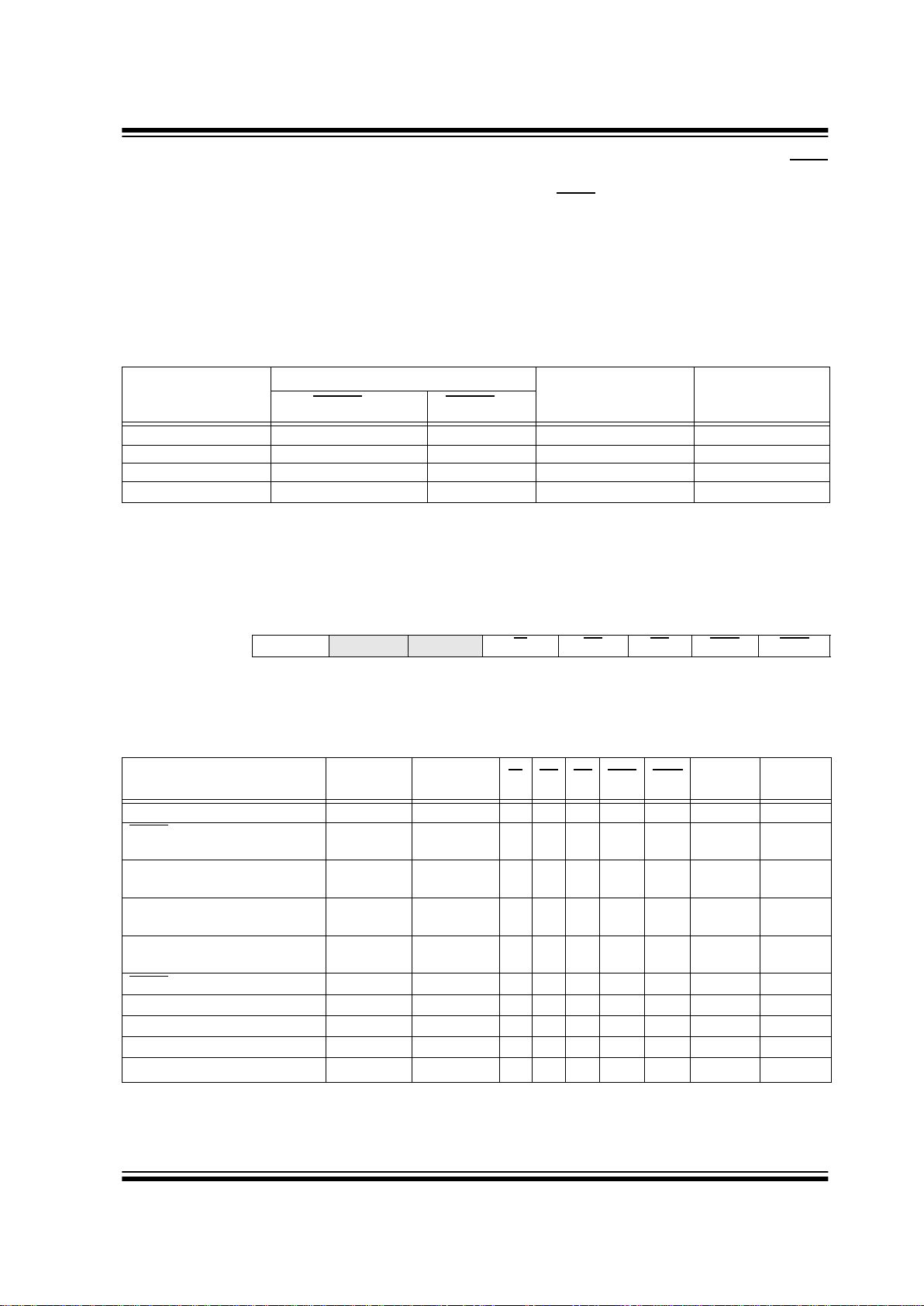

TABLE 3-1: TIME-OUT IN VARIOUS SITUATIONS

REGISTER 3-1: RCON REGISTER BITS AND POSITIONS

TABLE 3-2: STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR

RCON REGISTER

Oscillator

Configuration

Power-up

(1)

Brown-out

(1)

Wake-up from

SLEEP or

Oscillator Switch

PWRTE

= 0 PWRTE = 1

HS, XT, LP 72 ms + 1024Tosc 1024Tosc 72 ms + 1024Tosc 1024Tosc

EC 72 ms — 72 ms —

External Oscillator 72 ms — 72 ms —

Internal Oscillator

(2)

72 ms — 72 ms —

Note 1: 72 ms is the nominal power-up timer delay.

2: 8-cycle delay.

R/W-0 U-0 U-0 R/W-1 R-1 R-1 R/W-1 R/W-1

IPEN — — RI TO PD POR BOR

bit 7 bit 0

Condition

Program

Counter

RCON

Register

RI

TO PD POR BOR STKFUL STKUNF

Power-on Reset 0000h 00-1 1100 1 1 1 0 0 u u

MCLR

Reset during normal

operation

0000h 00-u uuuu u u u u u u u

Software Reset during normal

operation

0000h 0u-0 uuuu 0 u u u u u u

Stack Full Reset during normal

operation

0000h 0u-u uu11 u u u u u 1 u

Stack Underflow Reset during

normal operation

0000h 0u-u uu11 u u u u u u 1

MCLR

Reset during SLEEP 0000h 00-u 10uu u 1 0 u u u u

WDT Reset 0000h 0u-u 01uu 1 0 1 u u u u

WDT Wake-up PC + 2 uu-u 00uu u 0 0 u u u u

Brown-out Reset 0000h 0u-1 11u0 1 1 1 1 0 u u

Interrupt Wake-up from SLEEP

PC + 2

(1)

uu-u 00uu u 1 0 u u u u

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the

interrupt vector (0x000008h or 0x000018h).

PIC18F010/020

DS41142A-page 18 Preliminary 2001 Microchip Technology Inc.

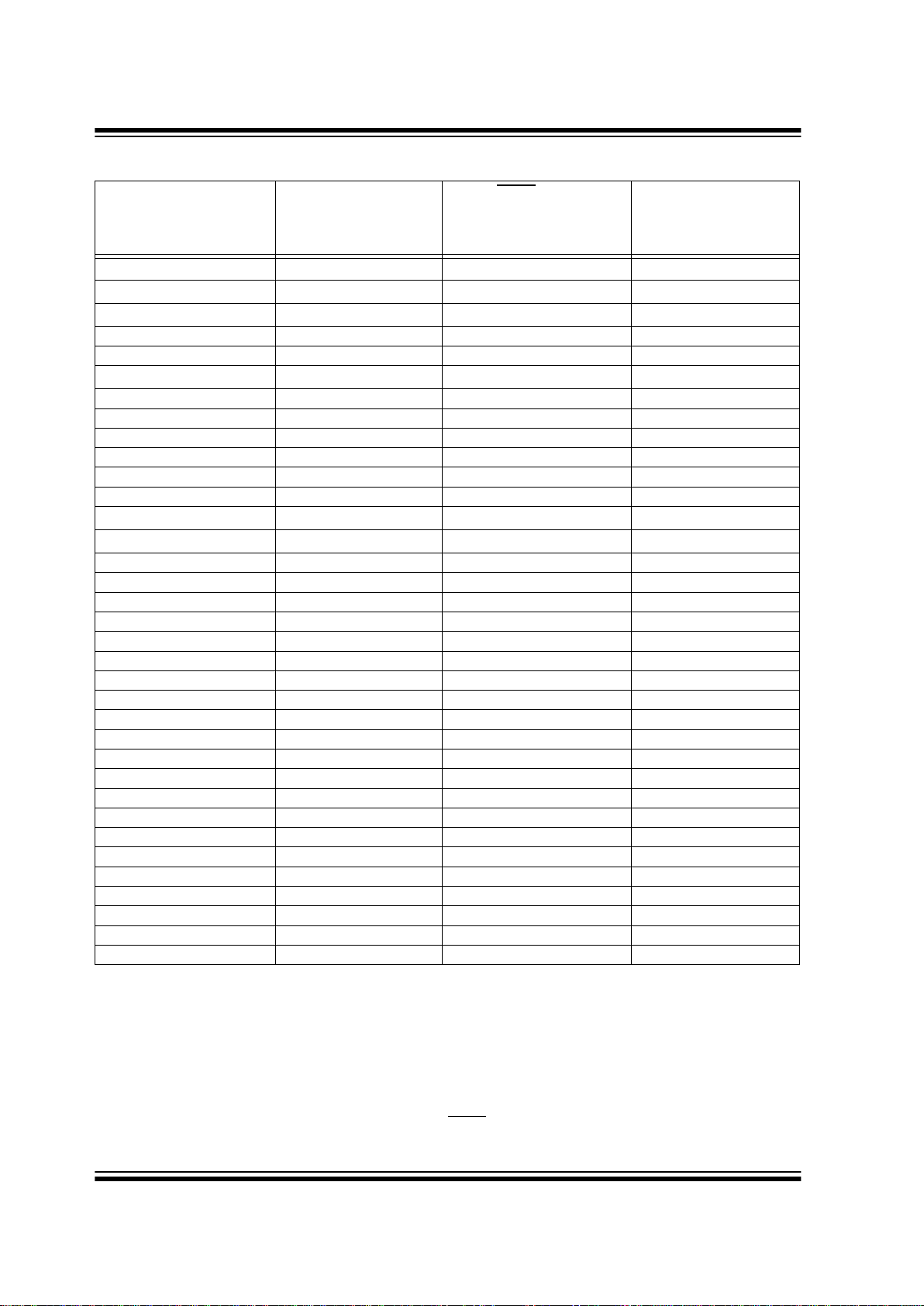

TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS

Register

Power-on Reset,

Brown-out Reset

MCLR

Reset

WDT Reset

Reset Instruction

Stack Reset

Wake-up via WDT

or Interrupt

TOSH 0000 0000 0000 0000

uuuu uuuu

(3)

TOSL 0000 0000 0000 0000

uuuu uuuu

(3)

STKPTR 00-0 0000 00-0 0000

uu-u uuuu

(3)

PCLATU ---0 0000 ---0 0000 ---u uuuu

PCLATH 0000 0000 0000 0000 uuuu uuuu

PCL 0000 0000 0000 0000

PC + 2

(2)

TBLPTRU ---0 00-- ---0 00-- ---u uu--

TBLPTRH ---- 0000 ---- 0000 ---- uuuu

TBLPTRL 0000 0000 0000 0000 uuuu uuuu

TABLAT 0000 0000 0000 0000 uuuu uuuu

PRODH xxxx xxxx uuuu uuuu uuuu uuuu

PRODL xxxx xxxx uuuu uuuu uuuu uuuu

INTCON 0000 000x 0000 000u

uuuu uuuu

(1)

INTCON2 11-- -1-1 11-- -1-1

uu-- -u-u

(1)

INDF0 N/A N/A N/A

POSTINC0 N/A N/A N/A

POSTDEC0 N/A N/A N/A

PREINC0 N/A N/A N/A

PLUSW0 N/A N/A N/A

FSR0H ---- 0000 ---- 0000 ---- uuuu

FSR0L xxxx xxxx uuuu uuuu uuuu uuuu

WREG xxxx xxxx uuuu uuuu uuuu uuuu

INDF1 N/A N/A N/A

POSTINC1 N/A N/A N/A

POSTDEC1 N/A N/A N/A

PREINC1 N/A N/A N/A

PLUSW1 N/A N/A N/A

FSR1H ---- 0000 ---- 0000 ---- uuuu

FSR1L xxxx xxxx uuuu uuuu uuuu uuuu

BSR ---- 0000 ---- 0000 ---- uuuu

INDF2 N/A N/A N/A

POSTINC2 N/A N/A N/A

POSTDEC2 N/A N/A N/A

PREINC2 N/A N/A N/A

PLUSW2 N/A N/A N/A

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as ’0’, q = value depends on condition

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an inte rrupt a nd the GIEL or GIEH bit is set, the PC is lo aded with the i nterrupt

vector (0008h or 0018h).

3: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are

updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table3-2 for RESET value for specific condition.

5: The long write enable is only reset on a POR or MCLR

Reset.

2001 Microchip Technology Inc. Preliminary DS41142A-page 19

PIC18F010/020

FSR2H ---- 0000 ---- 0000 ---- uuuu

FSR2L xxxx xxxx uuuu uuuu uuuu uuuu

ST ATUS ---x xxxx ---u uuuu ---u uuuu

TMR0H 0000 0000 0000 0000 uuuu uuuu

TMR0L xxxx xxxx uuuu uuuu uuuu uuuu

T0CON 1111 1111 1111 1111 uuuu uuuu

OSCCON -000 00-0 -uuu uu-u -uuu uu-u

LVDCON --00 0101 --00 0101 --uu uuuu

WDTCON ---- ---0 ---- ---0 ---- ---u

RCON

(4,5)

0--1 11qq 0--q qquu u--u qquu

IPR2 ---- 1111 ---- 1111 ---- uuuu

PIR2 ---- 0000 ---- 0000

---- uuuu

(1)

PIE2 ---- 0000 ---- 0000 ---- uuuu

TRISB --11 1111 --11 1111 --uu uuuu

LATB --xx xxxx --uu uuuu --uu uuuu

PORTB --xx xxxx --uu uuuu --uu uuuu

PSPCON ---- --00 ---- --00 ---- --uu

EEADR xxxx xxxx uuuu uuuu uuuu uuuu

EEDATA xxxx xxxx uuuu uuuu uuuu uuuu

EECON2 ---- ---- ---- ---- ---- ---EECON1 x--0 x000 u--0 u000 u--u uuuu

OSCTUNE --00 0000 --qq qqqq --uu uuuu

WPUB --11 1111 --11 1111 --uu uuuu

IOCB --00 0000 --00 0000 --uu uuuu

TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Register

Power-on Reset,

Brown-out Reset

MCLR

Reset

WDT Reset

Reset Instruction

Stack Reset

Wake-up via WDT

or Interrupt

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as ’0’, q = value depends on condition

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an inte rrupt a nd the GIEL or GIEH bit is set, the PC is lo aded with the i nterrupt

vector (0008h or 0018h).

3: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are

updated with the current value of the PC. The STKPTR is modified to point to the next location in the hard-

ware stack.

4: See Table3-2 for RESET value for specific condition.

5: The long write enable is only reset on a POR or MCLR

Reset.

PIC18F010/020

DS41142A-page 20 Preliminary 2001 Microchip Technology Inc.

FIGURE 3-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

FIGURE 3-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR

NOT TIED TO VDD): CASE 1

FIGURE 3-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR

NOT TIED TO VDD): CASE 2

TPWRT

TOST

VDD

MCLR

INTERNAL POR

PWRT TIME-OUT

OST TIME-OUT

INTERNAL RESET

VDD

INTERNAL RESET

TPWRT

TOST

VDD

MCLR

INTERNAL POR

PWRT TIME-OUT

OST TIME-OUT

INTERNAL RESET

VDD

MCLR

INTERNAL POR

PWRT TIME-OUT

OST TIME-OUT

INTERNAL RESET

TPWRT

TOST

2001 Microchip Technology Inc. Preliminary DS41142A-page 21

PIC18F010/020

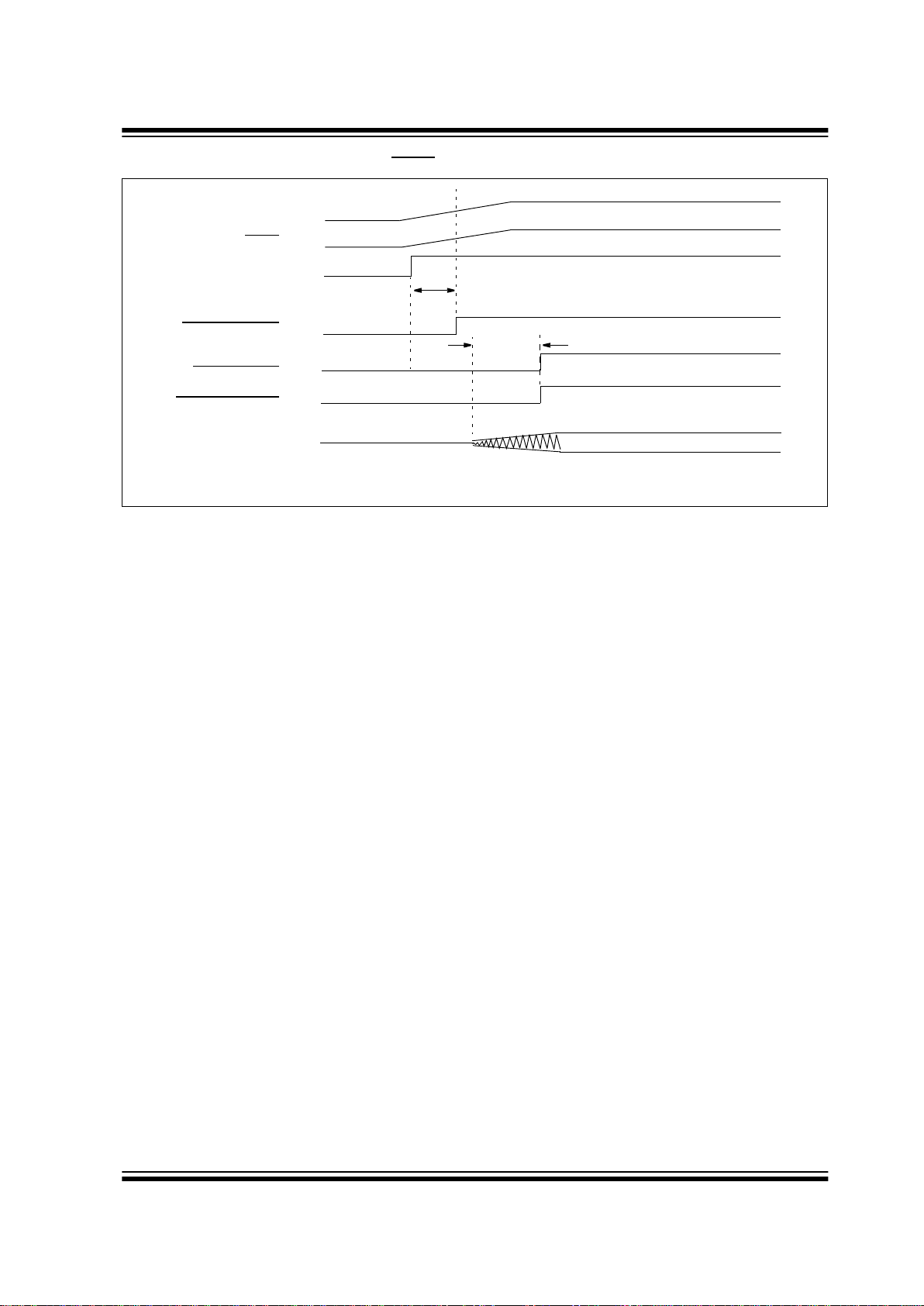

FIGURE 3-6: SLOW RISE TIME (MCLR TIED TO VDD)

VDD

MCLR

INTERNAL POR

PWRT TIME-OUT

OST TIME-OUT

INTERNAL RES ET

0V

1V

5V

T

PWRT

TOST

OSCILLATOR

Note: For slow starting crystals, OST can start beyond PWRT.

PIC18F010/020

DS41142A-page 22 Preliminary 2001 Microchip Technology Inc.

NOTES:

2001 Microchip Technology Inc. Preliminary DS41142A-page 23

PIC18F010/020

4.0 MEMORY ORGANIZATION

There are three memory blocks in PIC18F010/020

Enhanced MCU devices. These memory blocks are:

• Program Memory

• Data Memory

• EEPROM Data Memory

The EEPROM Data Memory is described in detail in

Section 5.0.

4.1 Program Memory Organization

The PIC18F010/020 devices have a 21-bit program

counter. Bits 12 through 16 are implemented as ‘0’

internally; therefore, accessing locations 0x01000

through 0x1FFFF actually mirror what is present in program memory from 0x0000 through 0x0FFF. The

PIC18F010 device reads all zeros (NOP) from 0x0800

through 0x 0FFF.

PIC18F020 has 4 Kbytes of FLASH program memory,

while PIC18F010 has 2 Kbytes of FLASH program

memory . This means the PIC18F020 can st ore up to 2K

of single word instructions, and the PICF18010 can

store up to 1K of single word instructions.

The RESET vector address is at 0000h and the interrupt vector addresses are at 0008h and 0018h. 0008h

is the high priority interru pt and 0018h is the low pri ority

interrupt vector.

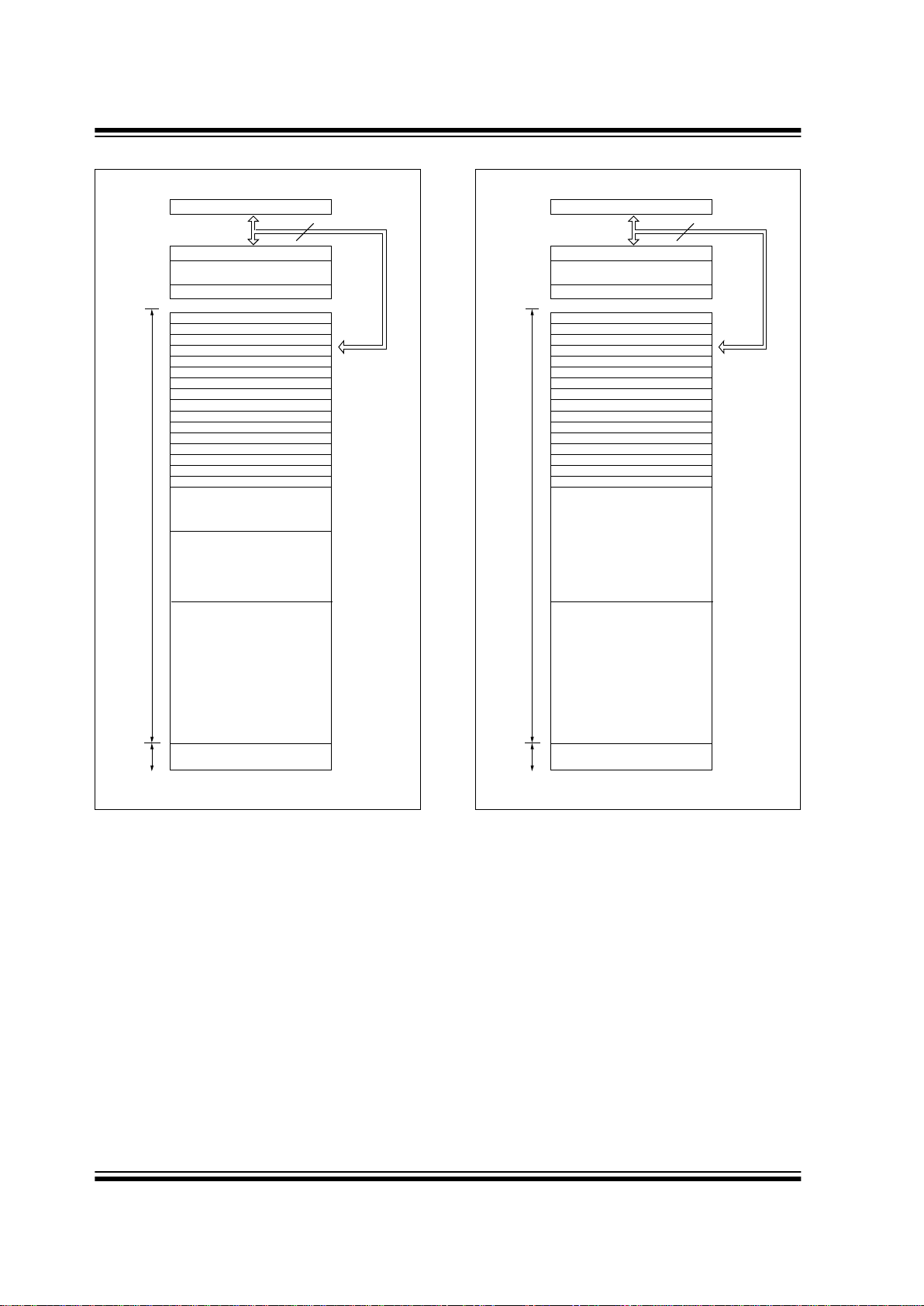

Figure 4-1 shows the Program Memory Map for

PIC18F010 and Figure4-2 shows the Program Memory Map for PIC18F020 devices.

PIC18F010/020

DS41142A-page 24 Preliminary 2001 Microchip Technology Inc.

FIGURE 4-1: PIC18F010 MEMORY FIGURE 4-2: PIC18F020 MEMORY

PC<20:0>

Stack Level 1

•

Stack Level 31

RESET Vector LSb

High Priority Interrupt Vector LSb

•

•

User Memory

Space

21

000000h

000008h

000018h

200000h

200003h

1FFFFFh

Low Priority Interrupt Vector LSb

RESET Vector MSb

000001h

High Priority Interrupt Vector MSb

Low Priority Interrupt Vector MSb

000019h

000009h

User ID Locations

User FLASH

001000h

000FFFh

Mirror

0007FFh

000800h

Read ‘0’s

PC<20:0>

Stack Level 1

•

Stack Level 31

RESET Vector LSb

High Priority Interrupt Vector LSb

•

•

User Memory

Space

21

000000h

000008h

000018h

200000h

200003h

1FFFFFh

Low Priority Interrupt Vector LSb

RESET Vector MSb

000001h

High Priority Interrupt Vector MSb

Low Priority Interrupt Vector MSb

000019h

000009h

User ID Locations

User FLASH

001000h

000FFFh

Mirror

Program Memory

2001 Microchip Technology Inc. Preliminary DS41142A-page 25

PIC18F010/020

4.2 Return Address Stack

The return address s tack allows any co mb in ation of up

to 31 program calls and interrupts to occur. The PC

(Program Counter) is pushed onto the stack when a

PUSH, CALL, or RCALL instruction is executed, or an

interrupt is acknowledged. The PC value is pulled off

the stack on a POP, RETURN, RETLW, or a RETFIE

instruction. PCLATU and PCLATH are not affected by

any of the return instructions.

The stack operates as a 31-word by 21-bit RAM with a

5-bit stack pointer. Although there are 21 bits in the

TOS latch, bits 12 through 16 are not physically implemented in the stack and are read as zeros. The stack

pointer initializes to 0x00 after all RESETS, and there

is no RAM associated with stack pointer 0x00. This is

only a RESET value. During a CALL type instruction

causing a push onto the stack, the stack pointer is first

incremented and the RAM location pointed to by the

stack pointer i s written wi th the conte nts of th e PC. During a RETURN type instruction causing a pop from the

stack, the contents of the RAM location pointed to by

the STKPTR is transferred to the PC and then, the

stack pointer is decremented.

The stack space is not part of either program or data

space. The stac k p oi nte r i s r ead ab l e a n d wr i tabl e, a nd

the address on the top of the stac k is readab le and writable through SFR registers. Data can also be pushed

to, or popped from the stack, using the top-of-stack

SFRs. Status bits indicate if the stack pointer is at, or

beyond, the 31 levels provided.

4.2.1 TOP-OF-STACK ACCESS

The top of the stack is readable and writable. Three

register locations, TOSH and TOSL hold the contents

of the stack location pointed to by the STKPTR register.

This allows users to impl ement a softw are stack, if ne cessary . After a CALL, RCALL or interrupt, the sof tware

can read the pushed value by reading the TOSH and

TOSL registers. T hes e values can be place d o n a us er

defined software stack. At return time, the sof tware can

replace the TOSH and TOSL and do a return.

The user must disable the global interrupt enable bits

during this time to prevent inadvertent stack operations.

4.2.2 RETURN STACK POINTER

(STKPTR)

The STKPTR register contains the stack pointer va lu e,

the STKFUL (stack full) status bit, and the STKUNF

(stack underflow) status bits. Register 4-1 shows the

STKPTR register. The value of the stack pointer can be

0 through 31. The stack pointer increments when values are pushed onto the stack and decrements when

values are popped off the stack. At RESET, the stack

pointer value will be 0. The user may read and write the

stack pointer valu e. This featu re can be us ed by a Rea l

Time Operating System for return stack maintenance.

After the PC is pu shed ont o the s tac k 31 tim es (wi thout

popping any values off the stack), the STKFUL bit is

set. The STKFUL bit can o nly be cle ared in sof tware or

by a POR.

The action that takes place when the stack becomes

full depends on the state of the STVREN (Stack Overflow Reset Enable) configuration bit. Refer to

Section 12.0 for a description of the device configuration bits. If STVREN is set (default), the 31st push will

push the (PC + 2) value onto the st ack, set the STKFUL

bit, and reset the device. The STKFUL bit will remain

set and the stack pointer will be set to 0.

If STVREN is cleared, the STKFUL bit will be set on the

31st push and the stack pointer will increment to 31.

The 32nd push and beyond will be lost while STKPTR

remains at 31, and the 31st push is maintained.

When the stack has been popped enough times to

unload the stac k, the next pop will ret urn a value of zero

to the PC and sets the STKUNF bit, while the stack

pointer remains at 0. The STKUNF bit will remain set

until cleared in software or a POR occurs.

Note: Do not push data onto the stack in bits 12

through 16. This data will be lost. Bits 12

through 16 are always read as ‘0’.

Note: Returning a value of zero to the PC on an

underflow, has the effect of vectoring the

program to the RESET vector, where the

stack condition s can be verifi ed and appropriate actions can be taken.

PIC18F010/020

DS41142A-page 26 Preliminary 2001 Microchip Technology Inc.

REGISTER 4-1: STKPTR - STACK POINTER REGISTER

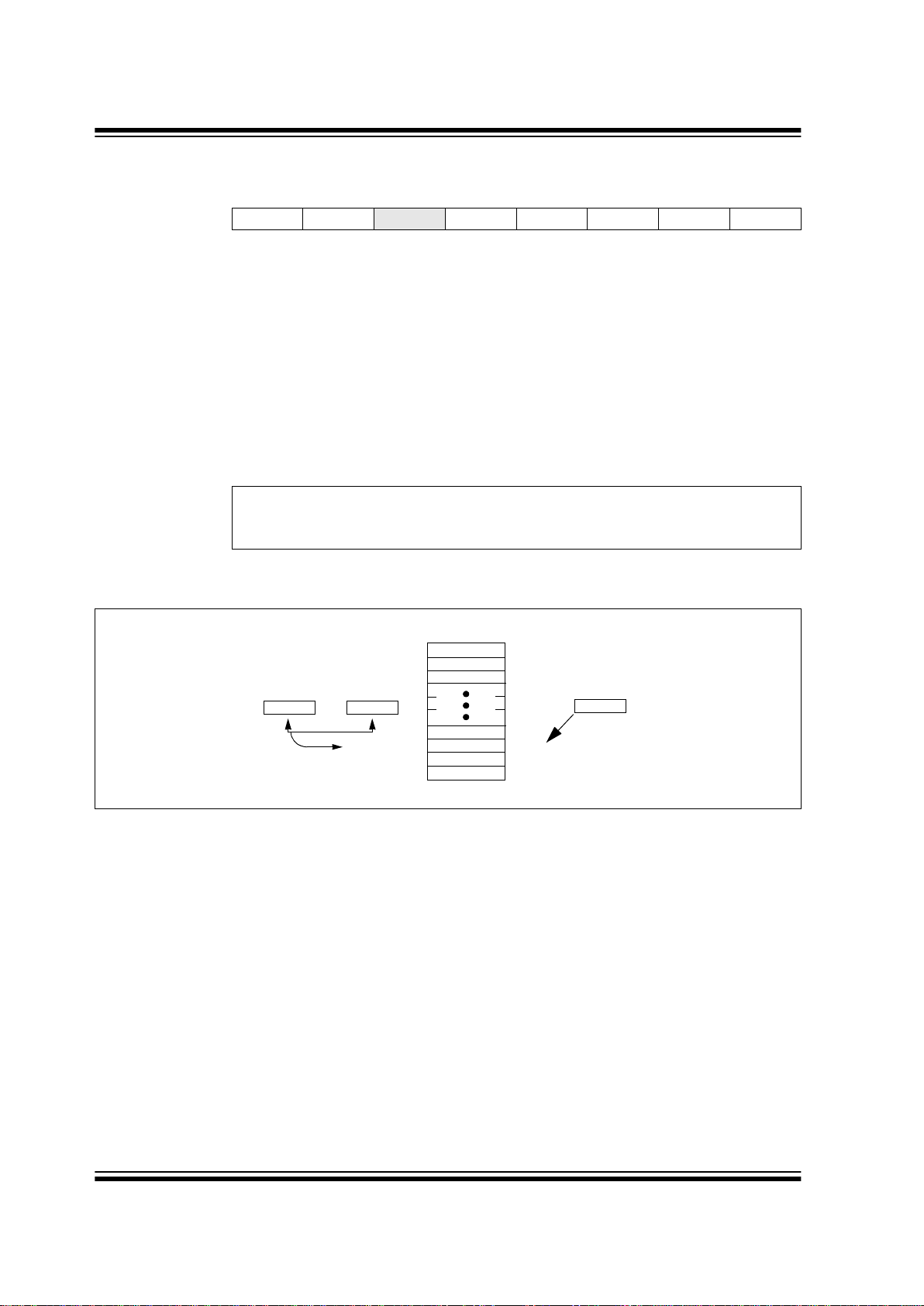

FIGURE 4-3: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

R/C-0 R/C-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

STKFUL STKUNF

— SP4 SP3 SP2 SP1 SP0

bit7 bit0

bit 7

(1)

STKFUL: Stack Full Flag bit

1 = Stack became full or overflowed

0 = Stack has not become full or overflowed

bit 6

(1)

STKUNF: Stack Underflow Flag bit

1 = Stack underflow occurred

0 = Stack underflow did not occur

bit 5 Unimplemented: Read as ‘0’

bit 4-0 SP4:SP0: Stack Pointer Location bits

Note 1: Bit 7 and bit 6 can only be cleared in user software, or by a POR.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

00011

0x0A34

11111

11110

11101

00010

00001

00000

00010

Return Address Stack

Top-of-Stack

0x0D58

TOSLTOSH

0x340x1A

STKPTR<4:0>

0x0000

2001 Microchip Technology Inc. Preliminary DS41142A-page 27

PIC18F010/020

4.2.3 PUSH AND POP INSTRUCTIONS

Since the Top-of-Stack (T OS) is readable and writabl e,

the ability to push valu es onto the stack and pull va lues

off the sta ck, withou t disturbi ng normal program exec ution, is a desirable optio n. To push the current PC value

onto the stack, a PUSH instruction can be executed.

This will i ncrem ent th e stack point er and load the cu rrent PC value onto the stack. TOSU, TOSH and TOSL

can then be modified to place a return address on the

stack.

The ability to pull the TOS value off of the stack and

replace it with the value that was previously pushed

onto the stack, without disturbing normal execution, is

achieved by using the POP inst ruction. T he POP instru ction discards the current TOS by decrementing the

stack pointer. The previous value pushed onto the

stack then becomes the TOS value.

4.2.4 STACK FULL/UNDERFLOW RESETS

These RESETS are enabled by programming the

STVREN configuration bit. When the STVREN bit is

disabled, a full or underflow condition will set th e appropriate STKFUL or STKUNF bit, but not cause a device

RESET. When the STVREN bit is enabled, a full or

underflow condition wil l set the appropriate STK FUL or

STKUNF bit and then cause a device RESET. The

STKFUL or STKUNF bits are only cleared by the user

software or a POR Reset.

4.3 Fast Register Stack

A "fast interrupt return " option is available fo r interrupts .

A Fast Register Stack is provided for the STATUS,

WREG and BSR registers and are only one in depth.

The stack is n ot read able o r writ abl e and is lo ade d with

the current value of the corresponding register when

the processor vecto rs for an in terrupt. The va lues in the

registers are then loaded back into the working registers, if th e fast return instruction is used to return

from the interrupt.

A low or high priority interrupt source will push values

into the stack registers. If both low and high priority

interrupts are enabled, the stack registers cannot be

used reliably for low priority interrupts. If a high priority

interrupt occurs while servicing a low priority interrupt,

the stack registe r values stored by the low priority interrupt will be overwritten.

If high priority int errupts are not dis abled during low priority interrupts, users must save the key registers in

software during a low priority interrupt.

If no interrupts are used, the fast register stack can be

used to restore the STATUS, WREG and BSR register s

at the end of a subroutine call. To use the fast register

stack for a subroutine call, a fast call instruction

must be executed.

Example 4-1 sho ws a source code exam ple that uses

the fast register stack.

EXAMPLE 4-1: FAST REGISTER STACK

CODE EXAMPLE

4.4 PCL, PCLATH and PCLATU

The program counter ( PC) spe ci fie s th e ad dre ss of th e

instruction to fetch for execution. The PC is 21-bits

wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called

the PCH register. This register contains the PC<11:8>

bits and is not directly readable or writable. Updates to

the PCH register may be performed through the

PCLATH register. The upper byte is called PCU. This

register contains th e PC<20: 17> bit s an d is not direc tly

readable or writable. Updates to the PCU register may

be performed through the PCLATU register.

The PC addresses bytes in the program memory. To

prevent the PC from becoming misaligned with word

instructions, the LSB of the PCL is fixed to a value of

’0’. The PC increments by 2 to address sequential

instructions in the program memory.

The CALL, RCALL, GOTO and program branch

instructions write to the program counter directly. For

these instructions, the contents of PCLATH and

PCLATU are not transferred to the program counter.

The contents of PCLATH and PCLATU will be transferred to the program counter by an operation that

writes PCL. Similarly, the upper two bytes of the program counter will be transferred to PCLATH and

PCLA TU, by an operation that reads PCL. Thi s is useful

for computed offsets to the PC (see Section4.8.1).

Note: Bits 12 through 16 are not implemented in

the PC and PCLAT.

CALL SUB1, FAST ;STATUS, WREG, BSR

;SAVED IN FAST REGISTER

;STACK

•

•

SUB1 •

•

•

RETURN FAST ;RESTORE VALUES SAVED

;IN FAST REGISTER STACK

PIC18F010/020

DS41142A-page 28 Preliminary 2001 Microchip Technology Inc.

4.5 Clocking Scheme/Instruction

Cycle

The clock input (from OSC1) is internally divided by

four to generate four non-overlapping quadrature

clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the

instruction is fetched from the program memory and

latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1

through Q4. The clocks and instruction execution flow

are shown in Figure4-4.

FIGURE 4-4: CLOCK/INSTRUCTION CYCLE

4.6 Instruction Flow/Pipelining

An “Instruction Cycle” consists of four Q cycles (Q1,

Q2, Q3 and Q4). The instruc ti on fe tch and ex ec ute a r e

pipelined su ch that fetch takes one instruction cyc le,

while decode and execute takes another instruction

cycle. However, due to the pipelining, each instruction

effectively executes in one cycle. If an instruction

causes the program counter to change (e.g. GOTO),

then two cycles are re quired to com plete the instruc tion

(Example 4-2).

A fetch cycle begins with the program counter (PC)

incrementing in Q1.

In the execution cy cle, the fetched instruction i s latched

into the “Instruction Register" (IR) in cycle Q1. This

instruction is then decoded and executed during the

Q2, Q3, and Q4 cycles. Dat a memory is read during Q2

(operand read) and written during Q4 (destination

write).

EXAMPLE 4-2: INSTRUCTION PIPELINE FLOW

Q1

Q2 Q3 Q4

Q1

Q2 Q3 Q4

Q1

Q2 Q3 Q4

OSC1

Q1

Q2

Q3

Q4

PC

OSC2/CLKOUT

(Internal Oscillator

PC PC+2 PC+4

Fetch INST (PC)

Execute INST (PC-2) Fetch INST (PC+2)

Execute INST (PC) Fetch INST (PC+4)

Execute INST (PC+2)

Internal

phase

clock

mode)

All instructions are single cycle, except for any program branches. These take two cycles, since the fetch

instruction is “flushed” from the pipeline, while the new instruction is being fetched and then executed.

TCY0TCY1TCY2TCY3TCY4TCY5

1. MOVLW 55h

Fetch 1 Execute 1

2. MOVWF PORTB

Fetch 2 Execute 2

3. BRA SUB_1

Fetch 3 Execute 3

4. BSF PORTA, BIT3 (Forced NOP)

Fetch 4 Flush

5. Instruction @ address SUB_1

Fetch SUB_1 Execute SUB_1

2001 Microchip Technology Inc. Preliminary DS41142A-page 29

PIC18F010/020

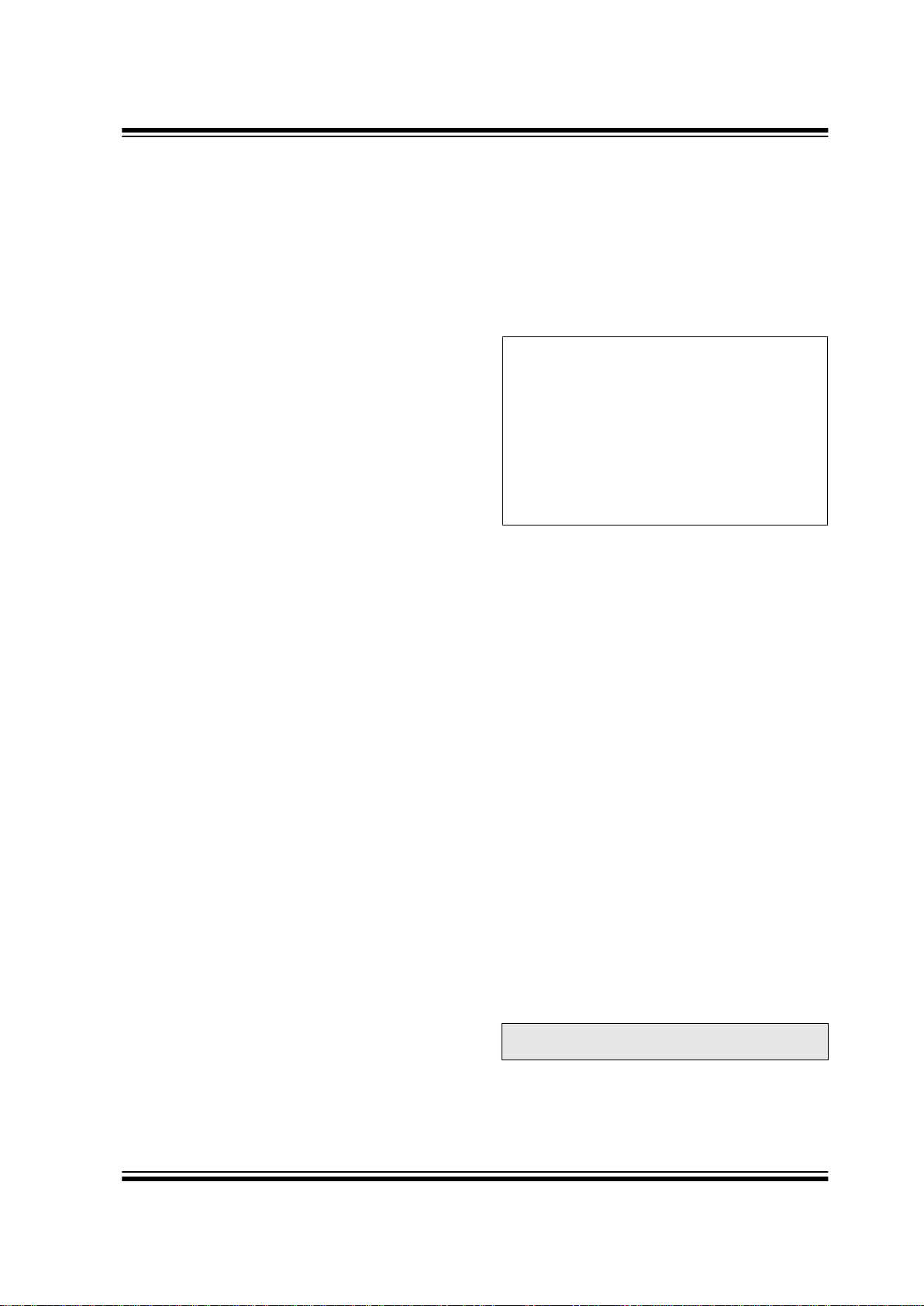

4.7 Instructions in Program Memory

The program memory is addressed in bytes. Instructions are stored as two bytes or four bytes in program

memory. The least significant byte of an instruction

word is always stored in a program memory location

with an even address (LSB = ’0’). Figure 4-5 shows an

example of how instructi on words are stored in the program memory. To maintain alignment with instruction

boundaries, the PC increments in steps of 2 and the

LSB will always read ’0’ (see Section 4 .4).

The CALL and GOTO ins tructions have an absol ute program memory address embedded into the instruction.

Since instructions are always stored on word boundaries, the data contained in the instruction is a word

address. The word address is written to PC<20:1>,

which accesses the desired byte address in program

memory. Instruction #2 in Figure 4-5 shows how the

instruction "GOTO 000006h’ is encoded in the program

memory. Program branch instruc tio ns , w hich e nc ode a

relative address offset, operate in the same manner.

The offset value stored in a branch instruction represents the number of single word instructions that the

PC will be offset by. Section 13.0 provides further

details of the instruction set.

FIGURE 4-5: INSTRUCTIONS IN PROGRAM MEMORY

Word Address

LSB = 1 LSB = 0 ↓

Program Memory

Byte Locations

→

000000h

000002h

000004h

000006h

Instruction 1: MOVLW 055h 0Fh 55h 000008h

Instruction 2: GOTO 000006h EFh 03h 00000Ah

F0h 00h 00000Ch

Instruction 3: MOVFF 123h, 456h C1h 23h 00000Eh

F4h 56h 000010h

000012h

000014h

PIC18F010/020

DS41142A-page 30 Preliminary 2001 Microchip Technology Inc.

4.7.1 TWO-WORD INSTRUCTIONS

The PIC18F010/020 devices have 4 two-word instructions: MOVFF, CALL, GOTO and LFSR. The second

word of these instructions has the 4 MSB’s set to 1’s

and is a special kind of NOP instruction. The lower 12

bits of the second word contain data to be used by the

instruction. If the first word of the instruction is executed, the data in the second word is accessed. If the

second word of the in struction is executed by itself (firs t

word was skipped), it will exec ute as a NOP. This action

is necessary when the two-word inst ruction is prec eded

by a conditional in struct ion that cha nges t he PC. A program example tha t demonstrate s this conc ept is show n

in Example 4-3. Refer to Section 13.0 for further deta ils

of the instruction set.

EXAMPLE 4-3: TWO-WORD INSTRUCTIONS

4.8 Lookup Tables

Lookup tables are implemented two ways. These are:

• Computed GOTO

• Table Reads

4.8.1 COMPUTED GOTO

A computed GOTO is accomplish ed b y a dding an offset

to the program counter (ADDWF PCL).

A lookup table can be formed with an ADDWF PCL

instruction and a group of RETLW 0xnn instructions.

WREG is loaded with an o ffset into t he table, befo re executing a call to that table. The fi rst instruction of the c alled

routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW 0xnn instructions, that returns the value 0xnn to th e ca llin g fun ctio n.

The offset value (va lue in WREG) specifie s the number

of bytes that the program counter should advance.

In this method, only one data byte may be stored in

each instruction location and room on the return

address stack is required.

4.8.2 TABLE READS/TABLE WRITES

A better method of storing data in program memory

allows 2 bytes of data to be stored in each instruction

location.

Lookup table data may be stored 2 bytes per program

word by using ta ble read s and writes . The t abl e point er

(TBLPTR) specifies the byte address and the table

latch (TABLAT) contains the data that is read from, or

written to, program memo ry. Data is transferred to/from

program memory one byte at a time.

A description of the Table Read/Table Write operation

is shown in Se ction 6.0.

CASE 1:

Object Code Source Code

0110 0110 0000 0000 TSTFSZ REG1 ; is RAM location 0?

1100 0001 0010 0011 MOVFF REG1, REG2 ; No, execute 2-word instruction

1111 0100 0101 0110 ; 2nd operand holds address of REG2

0010 0100 0000 0000 ADDWF REG3 ; continue code

CASE 2:

Object Code Source Code

0110 0110 0000 0000 TSTFSZ REG1 ; is RAM location 0?

1100 0001 0010 0011 MOVFF REG1, REG2 ; Yes

1111 0100 0101 0110 ; 2nd operand becomes NOP

0010 0100 0000 0000 ADDWF REG3 ; continue code

2001 Microchip Technology Inc. Preliminary DS41142A-page 31

PIC18F010/020

4.9 Data Memory Organization

The data memory is impleme nted as st atic RAM . Each

register in the data memory has a 12-bit address,

allowing up to 4096 bytes of data memory. Figure 4-6

and Figure 4-7 show the data memory organization for

the PIC18F010/020 devices.

Banking is required to all ow m ore th an 2 56 b yte s to be

accessed. The data memory map is divided into 2

banks that contai n 25 6 by tes ea ch . The low e r 4 bi t s of

the Bank Select Register (BSR<3:0>) select which

bank will be ac cessed. The upper 4 bits for the BSR

are not impl emented.

The data memory contains Special Function Registers

(SFR) and General Purpose Registers (GPR). The

SFRs are used for control and status of the controller

and peripheral functio ns, while GPRs are us ed for data

storage and scratch pad operations in the user’s application. The SFRs start at the last location of Bank 15

(0xFFF) and grow downwards. GPRs start at the first

location of Bank 0 and grow upwards. Any read of an

unimplemented location will read as ’0’s.

The entire data memory may be accessed directly or

indirectly . Direct ad dressing ma y require t he use of th e

BSR register. Indirect addressing requires the use of

the File Select Register (FSR). Each FSR holds a 12bit address v alue that can be used to access any location in the Data Memory map, without banking.

The instruction set and architecture allow operations

across all banks. This may be accomplished by indirect addressing, or by the u se of the MOVFF instruction.

The MOVFF instruction is a two-word/two-cycle instruction, that moves a value from one register to another.

To ensure that commonly used registers (SFRs and

select GPRs) can be accessed in a single cycle,

regardless of the current BSR values, an Access Bank

is implemented. A segment of Bank 0 and a segment

of Bank 15 comp rise the Access RAM. Section 4.10

provides a detailed description of the Access RAM.

4.9.1 GENERAL PURPOSE REGISTER

FILE

The register file can be ac cess ed eithe r dire ctly o r indirectly. Indirect addressing operates through the File

Select Registers (FSR). The operation of indirect

addressing is shown in Section 4.12.

Enhanced MCU devices may have banked memory in

the GPR area. GPRs are not initialized by a Power-on

Reset and are unchanged on all other RESETs.

Data RAM is available for use as GPR registers by all

instructions. Bank 15 (0xF80 to 0xFFF) co ntains SFRs.

Bank 0 contains GPR registers.

4.9.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers

used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these

registers is given in Figure 4-7 and Figure 4-8.

The SFRs can be classified into two sets: those associated with the “core” function and those related to the

peripheral functions. Those registers related to the

“core” are described in this s ec tio n, while those related

to the operation of the peripheral features are

described in the section of that periphe ral fea t ure.

The SFRs are typica lly d istrib uted a mong the per ipherals whose functions they control.

The unused SFR locations will be unimplemented and

read as '0's. See Figure4-7 for addresses for the

SFRs.

Note: Only 2 banks are implemented, Bank 0 and

Bank 15.

PIC18F010/020

DS41142A-page 32 Preliminary 2001 Microchip Technology Inc.

FIGURE 4-6: DATA MEMORY MAP PIC18F010/020

Bank 0

Bank 14

Bank 15

Data Memory Map

BSR<3:0>

= 0000b

= 0001b

= 1111b

080h

07Fh

F80h

FFFh

00h

7Fh

80h

FFh

Access Bank

When a = 0,

the BSR is ignored and the

Access Bank is used.

The first 128 bytes are

General Purpose RAM

(from Bank 0).

The second 128 bytes are

Special Functio n Reg ist ers

(from Bank 15).

When a = 1,

the BSR is used to specify

the RAM location that the

instructi on uses.

F7Fh

F00h

EFFh

100h

0FFh

000h

Access GPR

FFh

00h

FFh

00h

GPR

Access SFR

SFR

Access SFR

Access GPR

Bank 1

to

Unused

Read ’00h’

= 1110b

= 0010b

2001 Microchip Technology Inc. Preliminary DS41142A-page 33

PIC18F010/020

FIGURE 4-7: SPECIAL FUNCTION REGISTER MAP (F80h-FFFh)

FFFh FDFh INDF2 FBFh F9Fh

FFEh TOSH FDEh POSTINC2 FBEh F9Eh

FFDh TOSL FDDh POSTDEC2 FBDh F9Dh

FFCh STKPTR FDCh PREINC2 FBCh F9Ch reserved

FFBh PCLATU FDBh PLUSW2 FBBh F9Bh OSCTUNE

FFAh PCLATH FDAh FSR2H FBAh F9Ah

FF9h PCL FD9h FSR2L FB9h reserved F99h

FF8h TBLPTRU FD8h STATUS FB8h reserved F98h

FF7h TBLPTRH FD7h TMR0H FB7h reserved F97h

FF6h TBLPTRL FD6h TMR0L FB6h F96h

FF5h TABLAT FD5h T0CON FB5h F95h

FF4h PRODH FD4h reserved FB4h F94h

FF3h PRODL FD3h OSCCON FB3h F93h TRISB

FF2h INTCON FD2h LVDCON FB2h F92h

FF1h INTCON2 FD1h WDTCON FB1h F91h

FF0h INTCON3 FD0h RCON FB0h F90h

FEFh INDF0 FCFh FAFh F8Fh

FEEh POSTINC0 FCEh FAEh F8Eh

FEDh POSTDEC0 FCDh FADh F8Dh

FECh PREINC0 FCCh FACh F8Ch

FEBh PLUSW0 FCBh FABh F8Bh

FEAh FSR0H FCAh FAAh EEADRH F8Ah LATB

FE9h FSR0L FC9h FA9h EEADR F89h

FE8h WREG FC8h FA8h EEDATA F88h

FE7h INDF1 FC7h FA7h EECON2 F87h

FE6h POSTINC1 FC6h FA6h EECON1 F86h

FE5h POSTDEC1 FC5h FA5h F85h

FE4h PREINC1 FC4h FA4h F84h

FE3h PLUSW1 FC3h FA3h F83h

FE2h FSR1H FC2h FA2h IPR2 F82h

FE1h FSR1L FC1h FA1h PIR2 F81h PORTB

FE0h BSR FC0h FA0h PIE2 F80h

Note: Shading indicates addresses within Access Bank. Blank areas indicate reserved register space that may or

may not be implemented in this device.

PIC18F010/020

DS41142A-page 34 Preliminary 2001 Microchip Technology Inc.

FIGURE 4-8: SPECIAL FUNCTION REGISTER MAP (F00h-F7Fh)

F7Fh F5Fh F3Fh F1Fh

F7Eh F5Eh F3Eh F1Eh

F7Dh F5Dh F3Dh F1Dh

F7Ch F5Ch F3Ch F1Ch

F7Bh F5Bh F3Bh F1Bh

F7Ah F5Ah F3Ah F1Ah

F79h WPUB F59h F39h F19h

F78h IOCB F58h F38h F18h

F77h F57h F37h F17h

F76h F56h F36h F16h

F75h F55h F35h F15h

F74h F54h F34h F14h

F73h F53h F33h F13h

F72h F52h F32h F12h

F71h F51h F31h F11h

F70h F50h F30h F10h

F6Fh F4Fh F2Fh F0Fh

F6Eh F4Eh F2Eh F0Eh

F6Dh F4Dh F2Dh F0Dh

F6Ch F4Ch F2Ch F0Ch

F6Bh F4Bh F2Bh F0Bh

F6Ah F4Ah F2Ah F0Ah

F69h F49h F29h F09h

F68h F48h F28h F08h

F67h F47h F27h F07h

F66h F46h F26h F06h

F65h F45h F25h F05h

F64h F44h F24h F04h

F63h F43h F23h F03h

F62h F42h F22h F02h

F61h F41h F21h F01h

F60h F40h F20h F00h

Note: Shading indicates addresses within Access Bank. Blank areas indicate reserved register space that may or

may not be implemented in this device.

2001 Microchip Technology Inc. Preliminary DS41142A-page 35

PIC18F010/020

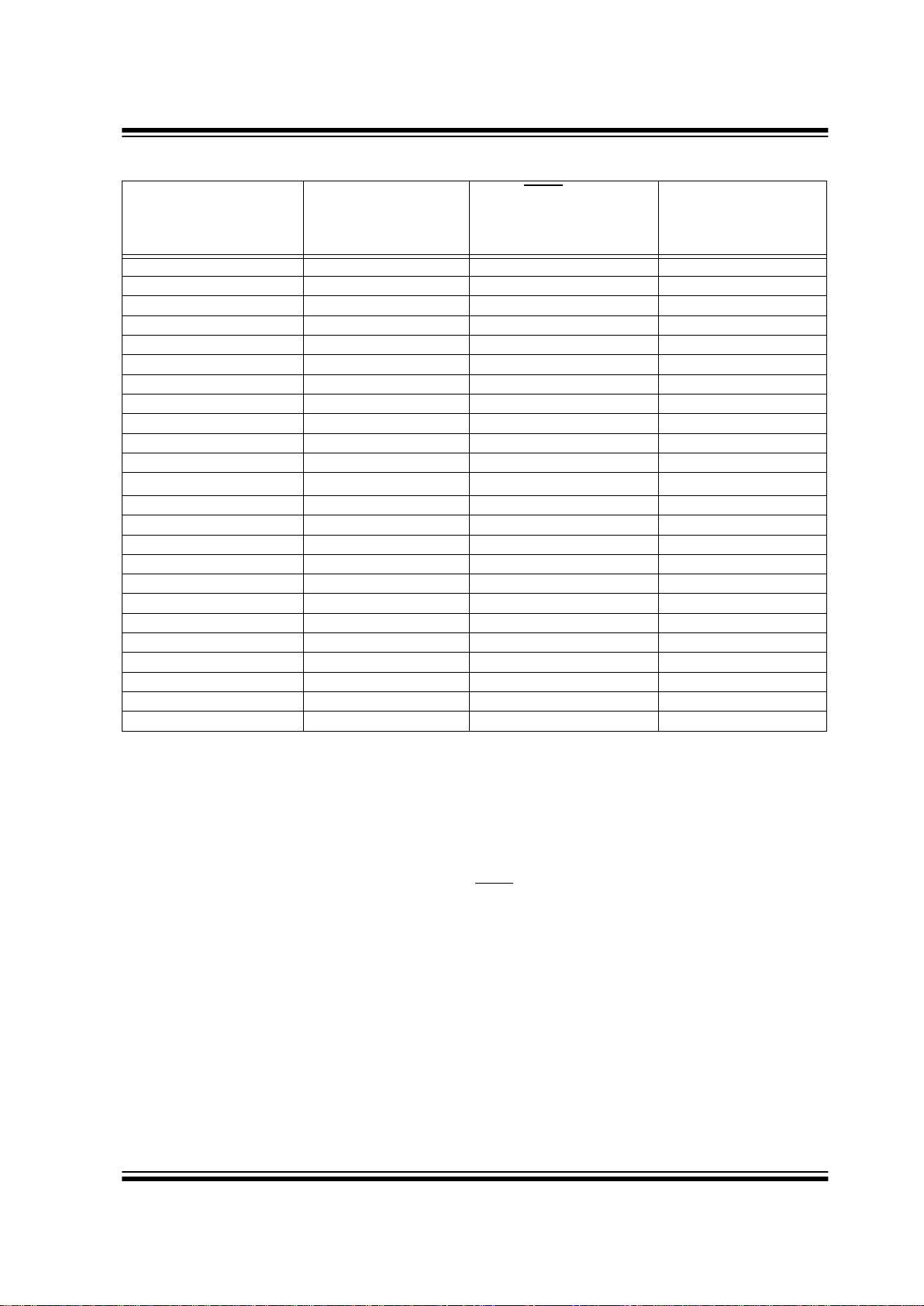

TABLE 4-1: REGISTER FILE SUMMARY (PIC18F010/020)

File Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Value o n

POR,

BOR

Value on

All Other

RESETS

(Note 1)

FFEh TOSH Top-of-Stack High Byte (TOS<11:8>)

---- 0000 ---- 0000

FFDh TOSL Top-of-Stack Low Byte (TOS<7:0>) 0000 0000 0000 0000

FFCh STKPTR STKOVF STKUNF — Return Stack Pointer 00-0 0000 00-0 0000

FFBh PCLATU — — bit21

(3)

Holding Register for PC<20 :18> — — --00 00-- --00 00--

FFAh PCLATH — — — — Holding Register for PC<11:8> ---- 0000 ---- 0000

FF9h PCL PC Low Byte (PC<7:0>) 0000 0000 0000 0000

FF8h TBLPTRU — — bit21

(2)

Program Memory Table Pointer

Upper Byte (TBLPTR<20:18>)

— — ---0 0000 ---0 0000

FF7h TBLPTRH — — — — Program Memory Table Pointer High Byte

(TBLPTR<11:8>)

0000 0000 0000 0000

FF6h TBLPTRL Program Memory Table Pointer Low Byte (TBLPTR<7:0>) 0000 0000 0000 0000

FF5h TABLAT Program Memory Table Latch 0000 0000 0000 0000

FF4h PRODH Product Register High Byte xxxx xxxx uuuu uuuu

FF3h PRODL Product Register Low Byte xxxx xxxx uuuu uuuu

FF2h INTCON GIE/GIEH PEIE/GIEL T0IE INT0E RBIE T0IF INT0F RBIF 0000 000x 0000 000u

FF1h INTCON2 RBPU INTEDG0 — — — T0IP — RBIP 11-- -1-1 11-- -1-1

FEFh INDF0 Uses contents of FSR0 to address data memory - value of FSR0 not changed (not a physical register) N/A N/A

FEEh POSTINC0 Uses contents of FSR0 to address data memory - value of FSR0 post-incremented (not a physical register) N/A N/A

FEDh POSTDEC0 Uses contents of FSR0 to address data memory - value of FSR0 post-decremented (not a physical register) N/A N/A

FECh PREINC0 Uses contents of FSR0 to address data memory - value of FSR0 pre-incremented (not a physical register) N/A N/A

FEBh PLUSW0 Uses contents of FSR0 to address data memory - value of FSR0 pre-incremented (not a physical register) -

value of FSR0 offset by W

N/A N/A

FEAh FSR0H

— — — — Indirect Data Memory Address Pointer 0 High ---- 0000 ---- 0000

FE9h FSR0L

Indirect Data Memory Address Pointer 0 Low Byte

xxxx xxxx uuuu uuuu

FE8h WREG