TC500/A/510/514

Precision Analog Front Ends

Features

• Precision (up to 17-bits) A/D Converter "Front End"

• 3-Pin Control Interface to Microprocessor

• Flexible: User Can Trade-off Conversion Speed

for Resolution

• Single Supply Operation (TC510/TC514)

• 4 Input, Differential Analog MUX (TC514)

• Automatic Input Voltage Polarity Detection

• Low Power Dissipation:

- (TC500/TC500A):10mΩ

- (TC510/TC514):18mΩ

• Wide Analog Input Range: ±4.2V (TC500A/TC510)

• Directly Accepts Bipolar and Differential

Input Signals

Applications

• Precision Analog Signal Processor

• PrecisionSensor Interface

• High Accuracy DC Measurements

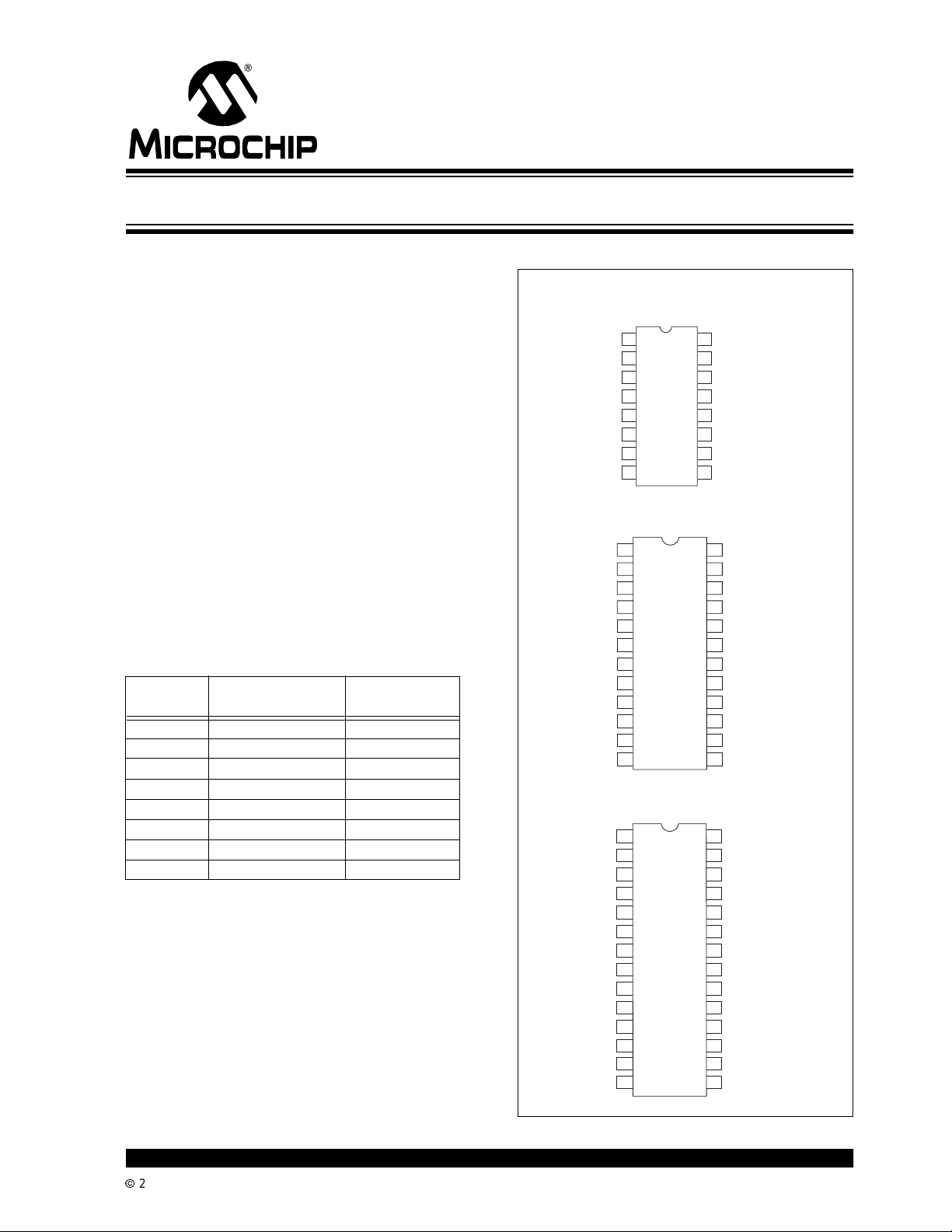

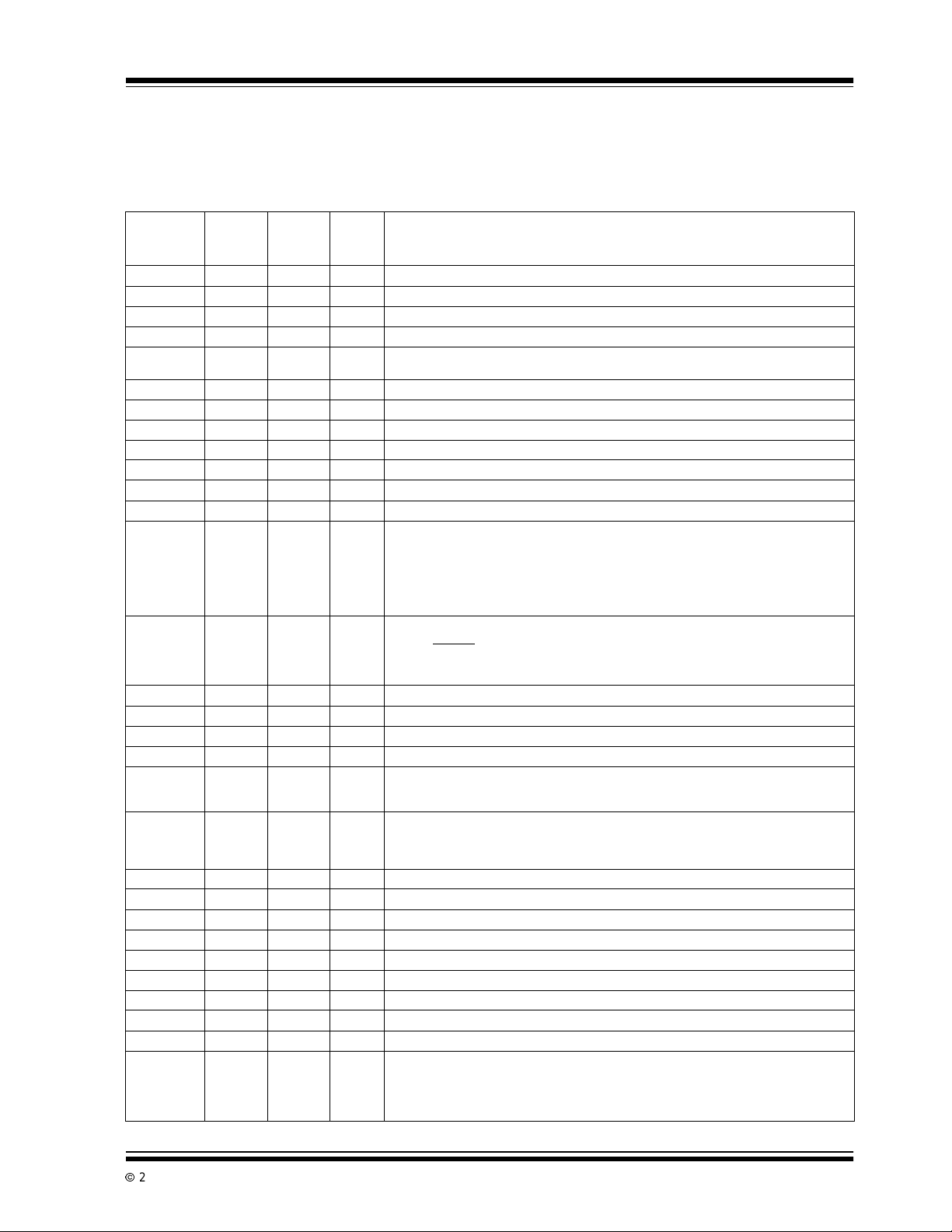

Device Selection Table

Part

Number

Package

TC500ACOE 16-Pin SOIC (Wide) 0°C to +70°C

TC500ACPE 16-Pin PDIP (Narrow) 0°C to +70°C

TC500COE 16-Pin SOIC (Wide) 0°C to +70°C

TC500CPE 16-Pin PDIP (Narrow) 0°C to +70°C

TC510COG 24-Pin SOIC (Wide) 0°C to +70°C

TC510CPF 24-Pin PDIP (Narrow) 0°C to +70°C

TC514COI 28-Pin SOIC (Wide) 0°C to +70°C

TC514CPJ 28-Pin PDIP (Narrow) 0°C to +70°C

Temperature

Range

Package Types

1

C

INT

V

2

SS

C

3

AZ

4

BUF

ACOM

5

C

–

6

REF

C

+

7

REF

V

8

REF

-

V

1

OUT

C

2

INT

C

3

AZ

BUF

4

ACOM

C

V

ACOM

C

V

C

REF

REF

REF

V

REF

V

OUT

C

C

REF

REF

V

REF

REF

CH4-

CH3-

CH2-

CH1-

N/C

N/C

N/C

INT

C

AZ

BUF

N/C

5

-

6

7

+

8

+

9

-

10

11

12

-

1

2

3

4

5

6

-

+

7

-

8

+

9

10

11

12

13

14

16-Pin SOIC

16 Pin-PDIP

TC500/

TC500A

COE

TC500/

TC500A

CPE

24-Pin SOIC

24-Pin PDIP

TC510COG

TC510CPF

28-Pin SOIC

28-Pin PDIP

TC514COI

TC514CPJ

V

16

DD

15

DGND

14

CMPTR OUT

13

B

A

12

VIN+

11

V

10

IN

V

9

REF

24

CAP-

23

DGND

22

CAP+

21

V

20

OSC

19

CMPTR OUT

18

A

17

B

16

V

15

V

14

N/C

13

N/C

28

CAP-

27

DGND

26

CAP+

V

25

24

OSC

23

CMPTR OUT

22

A

21

B

20

A0

19

A1

18

CH1+

17

CH2+

16

CH3+

CH4+

15

–

DD

IN

IN

DD

+

+

-

2002 Microchip TechnologyInc. DS21428B-page 1

TC500/A/510/514

)

General Description

TheTC500/A/510/514 family are precision analog front

ends that implement dual slope A/D converters having

a maximum resolution of 17-bits plus sign. As a minimum, each device contains the integrator, zero crossing comparator and processor i nterface logic. The

TC500 is the base (16-bit max) device and requires

both positive and negative power supplies. The

TC500A is identical to t he TC500 with the exception

that it has improved linearity, allowing it to operate to a

maximumresolutionof17-bits.The TC510 adds an onboard negative power supply converter for single supply operation. The TC514 adds both a negative power

supply converter and a 4 input differential analog

multiplexer.

Each device has the same processor control interface

consistingof3 wires: control inputs(A and B)and zerocrossing comparator output (CMPTR). The processor

manipulates A, B to sequence the TC5XX through four

phases of conversion: Auto Zero, Integrate, De-integrate and IntegratorZero. During the Auto Zero phase,

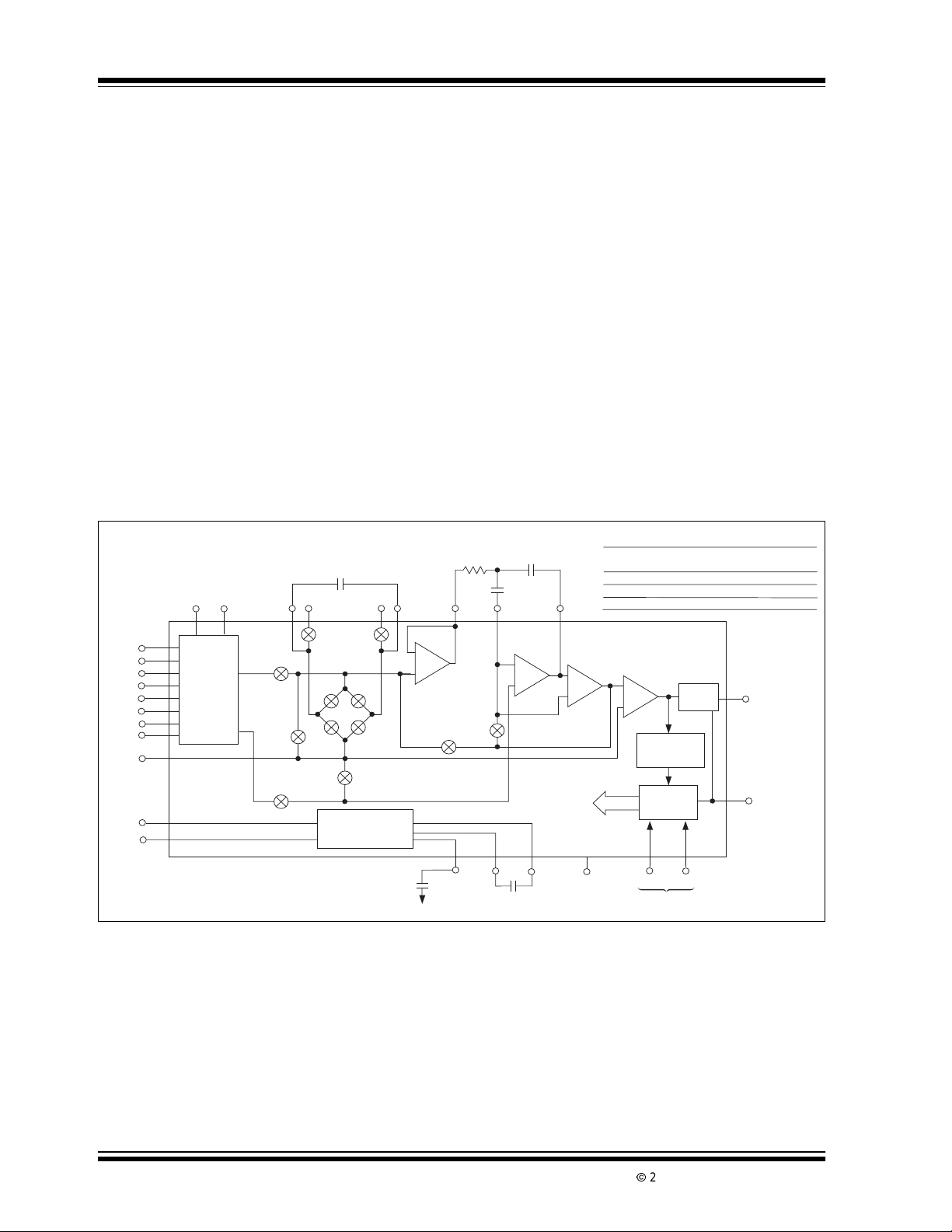

Typical Application

C

REF

V

REF

SW

R

-

SW

RI

-

SW

RI

SW

1

DC-TO-DC

Converter

C

REF

Buffer

-

+

CH1+

CH2+

CH3+

CH4+

CH1CH2CH3CH4-

ACOM

V

OSC

+

A1

A0

DIF.

MUX

(TC514)

SS

V

REF

SW

SW

SW

+

I

Z

I

REF

SW

R

SW

-

RI

SWRI+

(TC510 & TC514)

C

-

SW

offset voltages in the TC5XX are corrected by a closed

loop feedback mechanism.The input voltage is applied

to the integrator during the I ntegrate phase. This

causes an integrator output dv/dt directly proportional

to the magnitude of the input voltage. The higher the

input voltage, the greater the magnitude of the voltage

stored on the integrator during this phase. At the start

of the De-integrate phase, an external voltage reference is applied to the integratorand, at the same time,

the external host processor starts i ts on-board timer.

The processor maintains t his state until a transition

occurson the CMPTR output,atwhichtimetheprocessor halts its timer. The resultingtimer count is the converted analog data. Integrator Zero (the final phase of

conversion) removes any residue remaining in the

integrator in preparationfor the next conversion.

The TC500/A/510/514 offer high resolution (up to 17bits), superior 50Hz/60Hz noise r ejection, low power

operation, minimum I/O connections, low input bias

currents and lower cost compared to other converter

technologies having similarconversion speeds.

Control Logic

TC500

TC500A

TC510

TC514

Polarity

Detection

Phase

Decoding

Logic

Converter Sate

Level

Shift

R

INT

C

BUF

SW

IZ

V

OUT

C

INT

AZ

C

AZ

Integrator

–

+

Z

Analog

Switch

Control

Signals

CAP-

CAP+

A B

0 0 Zero Integrator Output

0 1 Auto-Zero

1 0 Signal Integrate

1 1 Deintegrate

C

INT

CMPTR 1

+

–

CMPTR 2

–

+

CMPTR

Output

DGND

DS21428B-page 2

1.0µF

V

SS

C

-

OUT

1.0µF

(TC500

TC500A

BA

Control Logic

2002 Microchip TechnologyInc.

TC500/A/510/514

1.0 ELECTRICAL

CHARACTERISTICS

Absolute Maximum Ratings*

TC510/TC514 Positive Supply Voltage

(V

to GND) .........................................+10.5V

DD

TC500/TC500A Supply Voltage

(V

to VSS) ..............................................+18V

DD

TC500/TC500A Positive Supply Voltage

(V

to GND) ............................................+12V

DD

TC500/TC500A Negative Supply Voltage

(V

to GND)................................................-8V

SS

Analog Input Voltage(V

Logic Input Voltage...............VDD+0.3Vto GND - 0.3V

Voltage on OSC:

........................... -0.3V to (V

Ambient Operating Temperature Range:

................................................................0°C to +70°C

StorageTemperature Range: .............-65°C to +150°C

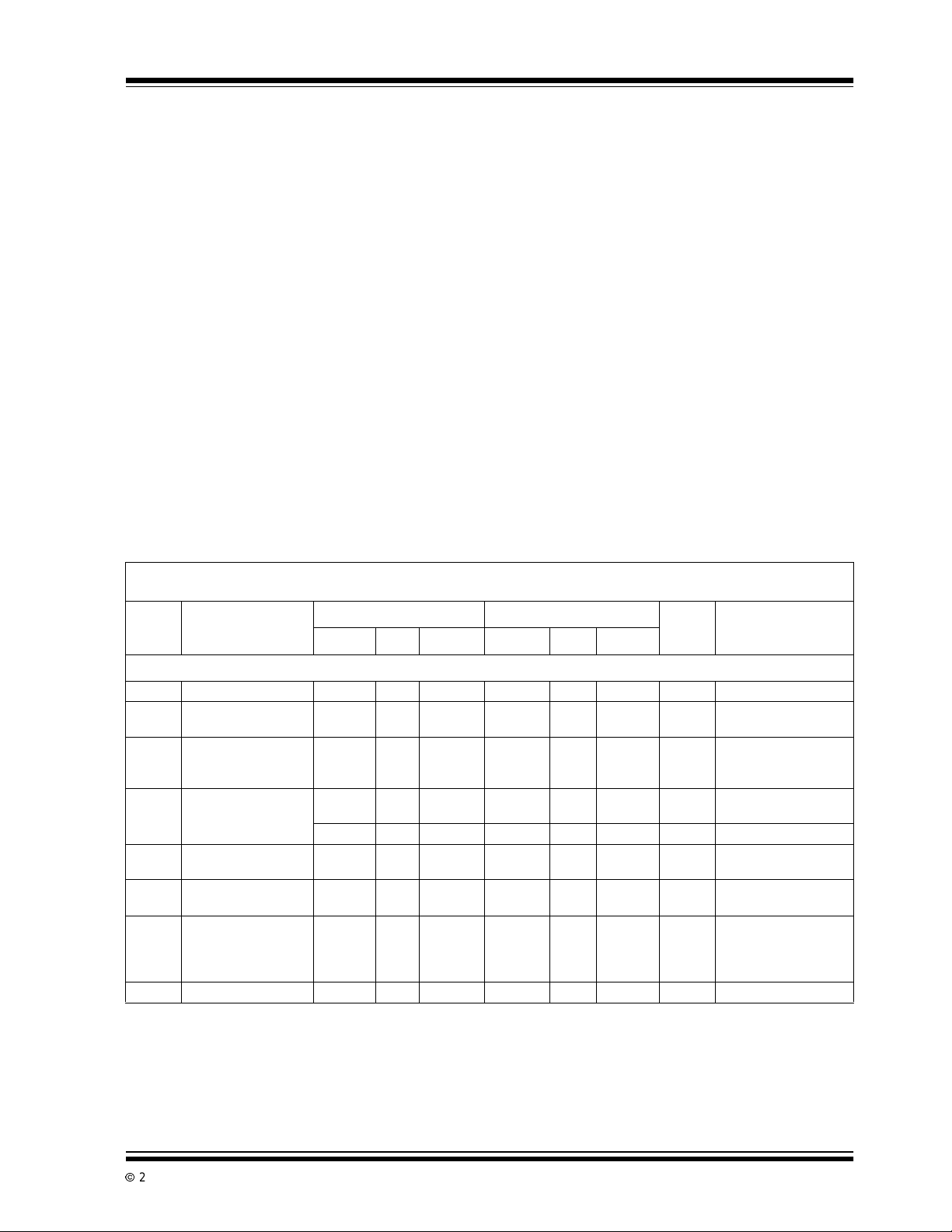

TC500/A/510/514 ELE CTRI CAL SPECIFICATIONS

+orVIN-) ............VDDto V

IN

+0.3V)for VDD<5.5V

DD

SS

*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to t he

device. These are stress ratings only and functional

operation of the device at these or any other conditions

above those indicated in the operation sections of the

specifications is not implied. Exposure to Absolute

Maximum Rating conditions for extended periods may

affect device reliability.

Electrical Characteristics: TC510/TC514: VDD= +5V, TC500/TC500A: VSS= ±5V unless otherwise specified.

C

AZ=CREF

Symbol Parameter

Analog

ZSE Zero Scale Error

ENL End Point Linearity ——0.005—0.015

NL Best Case Straight

ZS

TC

SYE Full-Scale Symmetry

FS

TC

I

IN

Note 1: Integrate time ≥ 66msec, auto zero time ≥ 66msec, V

=0.47µF.

=+25°C TA=0°Cto70°C

T

A

Min Typ Max Min Typ Max

Resolution 60 — — — —— µVNote1

—

with Auto Zero Phase

Line Linearity

Zero-Scale Temp.

Coefficient

Error (Roll-Over Error)

Full-Scale Tempera-

ture Coefficient

Input Current — 6 — — —— pAVIN=0V

2: End point linearity at ±1/4, ±1 /2, ±3/4 F.S. after full-scale adjustment.

3: Roll-overerrorisrelated to C

—

— 0.003 0.008 —

— — 0.005 — — — % F.S. TC500A

——— — 12µV/°C Over Operating

—0.01— — 0.03 — % F.S. Note 3

——— — 10 — ppm/°C Over Operating

—

—

INT,CREF,CAZ

0.005

0.003

0.010

(peak) ≈ 4V.

INT

characteristics.

—

—

—

—

0.005

0.003

0.015

0.010

0.012

0.009

0.060

0.045

— — % F.S. TC500/510/514,

Unit Test Conditions

% F.S. TC500/510/514

TC500A

%F.S.

%F.S.

TC500/510/514,

Note 1, Note 2,

TC500A

Note 1, Note 2

Temperature Range

Temperature Range;

External Reference

TC = 0 ppm/°C

2002 Microchip TechnologyInc. DS21428B-page 3

TC500/A/510/514

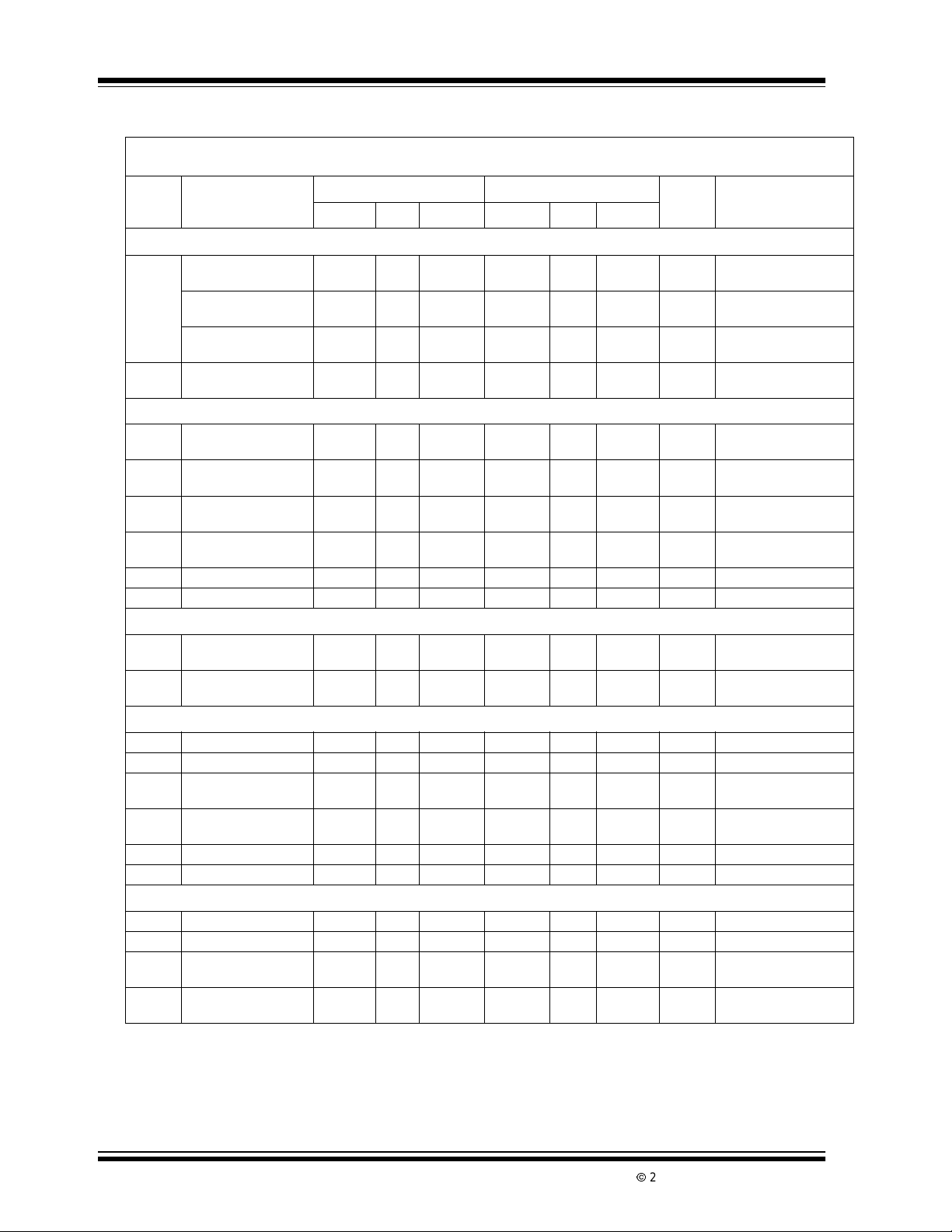

TC500/A/510/514 ELE CTRICAL SPECIFICATIONS (CONTINUED)

Electrical Characteristics: TC510/TC514: VDD= +5V, TC500/TC500A: VSS= ±5V unless otherwise specified.

C

AZ=CREF

Symbol Parameter

Analog (Continued)

V

CMR

V

REF

Digital

V

OH

V

OL

V

IH

V

IL

I

L

t

D

Multiplexer (TC514 Only)

R

DSON

Power (TC510/TC514 Only)

I

S

P

D

V

DD

R

OUT

I

OUT

Power (TC500/TC500A Only)

I

S

P

D

V

DD

V

SS

Note 1: Integrate time ≥ 66msec, auto zero time ≥ 66msec, V

=0.47µF.

=+25°C TA=0°Cto70°C

T

A

Min Typ Max Min Typ Max

Common Mode

VSS+1.5 — VDD–1.5 VSS+1.5 — VDD–1.5 V

Voltage Range

Integrator Output

+0.9 — VDD–0.9 VSS+0.9 — VSS+0.9 V

V

SS

Swing

Analog Input Signal-

+1.5 — VDD–1.5 VSS+1.5 — VSS+1.5 V ACOM= GND = 0V

V

SS

Range

Voltage Reference

VSS+1 — VDD–1 VSS+1 — VDD–1 V V

Range

Comparator Logic 1,

4 — —4——VI

Output High

Comparator Logic 0,

— — 0.4 — — 0.4 V I

OutputLow

Logic1, InputHigh

3.5 — —3.5——V

Voltage

Logic0, InputLow

— — 1——1V

Voltage

LogicInputCurrent — — ——0.3 µALogic1or0

Comparator Delay — 2 — — 3 — µsec

Maximum Input

-2.5 — 2.5 -2.5 — 2.5 V V

Voltage

Drain/Source ON

—610 ———kΩ VDD=5V

Resistance

SupplyCurrent — 1.8 2.4 — — 3.5 mA VDD=5V,A=1,B=1

Power Dissipation — 18 — — — — mW VDD=5V

Positive Supply Oper-

4.5 — 5.5 4.5 — 5.5 V

ating Voltage Range

Operating Source

—6085 — —100Ω I

Resistance

Oscillator Frequency — 100 — — — — kHz (Note3)

Maximum Current Out — — -10 — — -10 mA VDD=5V

Supply Current — 1 1.5 — — 2.5 mA VS=±5V,A=B=1

Power Dissipation — 10 — — — — mW VDD=5V,VSS=-5V

Positive Supply Oper-

4.5 — 7.5 4.5 — 7.5 V

ating Range

Negative Supply

-4.5 — -7.5 - 4.5 — -7.5 V

Operating Range

(peak) ≈ 4V.

2: End point linearity at ±1/4, ±1 /2, ±3/4 F.S. after full-scale adjustment.

3: Roll-overerrorisrelated to C

INT,CREF,CAZ

characteristics.

INT

Unit Test Conditions

REF-VREF

SOURCE

SINK

DD

OUT

+

=400µA

=2.1mA

=5V

=10mA

DS21428B-page 4

2002 Microchip TechnologyInc.

2.0 PIN DESCRIPTIONS

ThedescriptionsofthepinsarelistedinTable2-1.

TABLE 2-1: PIN FUNCTION TABLE

TC500/A/510/514

PinNumber

(TC500,

TC500A)

122C

2 Not Used Not Used V

333C

Pin

Number

(TC510)

Pin

Number

(TC514)

Symbol Description

Integrator output. Integrator capacitor connection.

INT

Negative power supply input(TC500/TC500A only).

SS

Auto Zero input. The Auto Zero capacitor connection.

AZ

4 4 4 BUF Buffer output. The Integrator capacitor connection.

5 5 5 ACOM This pin is grounded in most applications. It is recommended that ACOM and the

666C

777C

888V

999V

10 15 Not Used V

11 16 Not Used V

input common pin (Ve

- Input.Negative reference capacitor connection.

REF

+ Input. Positive reference capacitor connection.

REF

- Input. External voltage reference (-) connection.

REF

+ Input. External voltage reference (+) connection.

REF

- Negative analog input.

IN

+ Positive analog input.

IN

-orCHn-) be within the analog common mode range (CMR).

n

12 18 22 A Input. Converter phase control MSB. (See input B.)

13 17 21 B Input. Converter phase control LSB. The states of A, B place the TC5XX in one of

four required phases. A conversion is complete when all four phases have been

executed:

Phasecontrol input pins: AB = 00: IntegratorZero

01: Auto Zero

10: Integrate

11: De-integrate

14 19 23 CMPTR

Zerocrossing comparatoroutput. CMPTR is HIGH during the Integration phase

OUT

when a positive

voltage is being integrated. A HIGH-to-LOW transition on CMPTR signals the processorthat the De-integrate phase is completed. CMPTR is undefinedduring the

AutoZerophase.Itshouldbe monitored to time theIntegrator Zero phase.

input voltage is being integratedand is LOW when a negative input

15 23 27 DGND Input. Digital ground.

16 21 25 V

Input.Power supply positive connection.

DD

22 26 CAP+ Input. Negative power supply converter capacitor (+) connection.

24 28 CAP- Input. Negative power supply converter capacitor (-) connection.

11V

- Output. Negative power supply converter output and reservoir capacitor connection.

OUT

This output can be used to power other devices in the circuit requiringa negative

biasvoltage.

20 24 OSC Oscillator control input. The negative powersupplyconverter normally runs at a fre-

quency of 100kHz. The converter oscillator frequencycanbe sloweddown

(to reduce quiescent current) by connecting an external capacitor between this pin

and V

(see Section9.0, Typical Characteristics Curves).

DD

18 CH1+ Positiveanalog input pin. MUX channel 1.

13 CH1- Negative analog input pin. MUX channel 1.

17 CH2+ Positiveanalog input pin. MUX channel 2.

12 CH2- Negative analog input pin. MUX channel 2.

16 CH3+ Positiveanalog input pin. MUX channel 3.

11 CH3- Negative analog inputpin. MUX channel3.

15 CH4+ Positiveanalog input pin. MUX channel 4.

10 CH4- Negative analog input pin. MUX channel 4

20 A0 Multiplexer inputchannel select input LSB (see A1).

19 A1 Multiplexer input channel select input MSB.

Phasecontrol input pins: A1, A0 = 00 = Channel1

01 = Channel 2

10 = Channel 3

11 = Channel4

2002 Microchip TechnologyInc. DS21428B-page 5

TC500/A/510/514

T

3.0 DETAILED DESCRIPTION

3.1 Dual Slope Conversion Principles

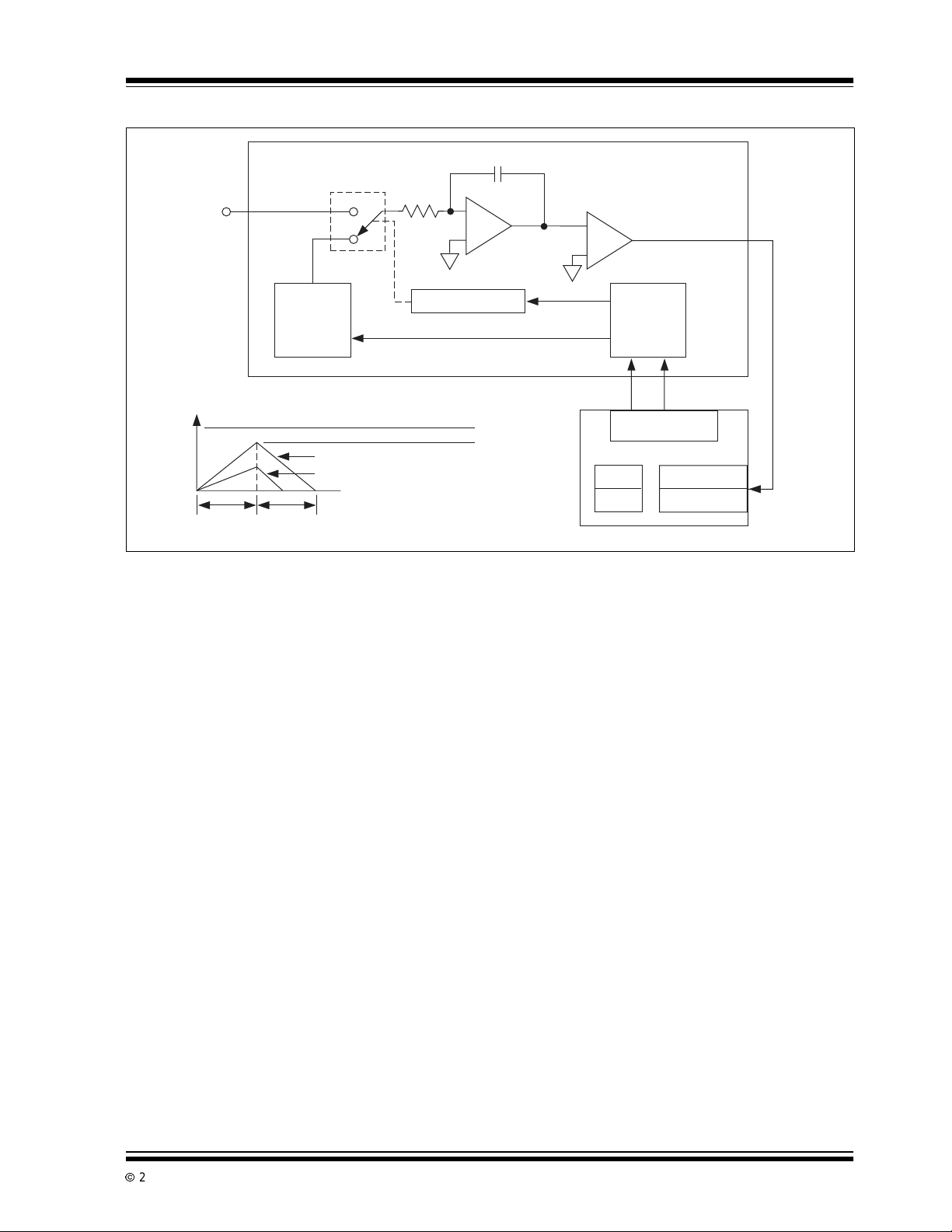

Actual data conversion is accomplishedin t wo phases:

input signal Integrationand reference voltage

De-integration.

The integratoroutputisinitializedt o 0Vprior to the start

of Integration. During Integration, analog switch S1

connects V

tained for a fixed time period (T

V

causes t he integrator output to depart 0V at a rate

IN

determined by the magnitude of V

determined by the polarity of V

phase is initiated immediately at the expiration of T

DuringDe-integration, S1 connectsa reference voltage

(having a polarity opposite that of V

input. At the same time, an external precision timer i s

started. The De-integration phase is maintained until

the comparator output changes state, indicating the

integratorhas returned to its starting point of 0V. When

thisoccurs,the precisiontimerisstopped.TheDe-integration time period (T

sion timer, is directly proportional to the magnitude of

the applied input voltage (see Figure 3-3).

A simple mathematical equation relates the Input Signal, Reference Voltage and Integration time:

EQUATION 3-1:

Where:

V

= Reference Voltage

REF

= Signal Integration time (fixed)

T

INT

t

DEINT

For a constant VIN:

EQUATION 3-2:

The dual slope converter accuracy is unrelated to the

integrating resistor and capacitor values as long as

they are stable during a measurement cycle.

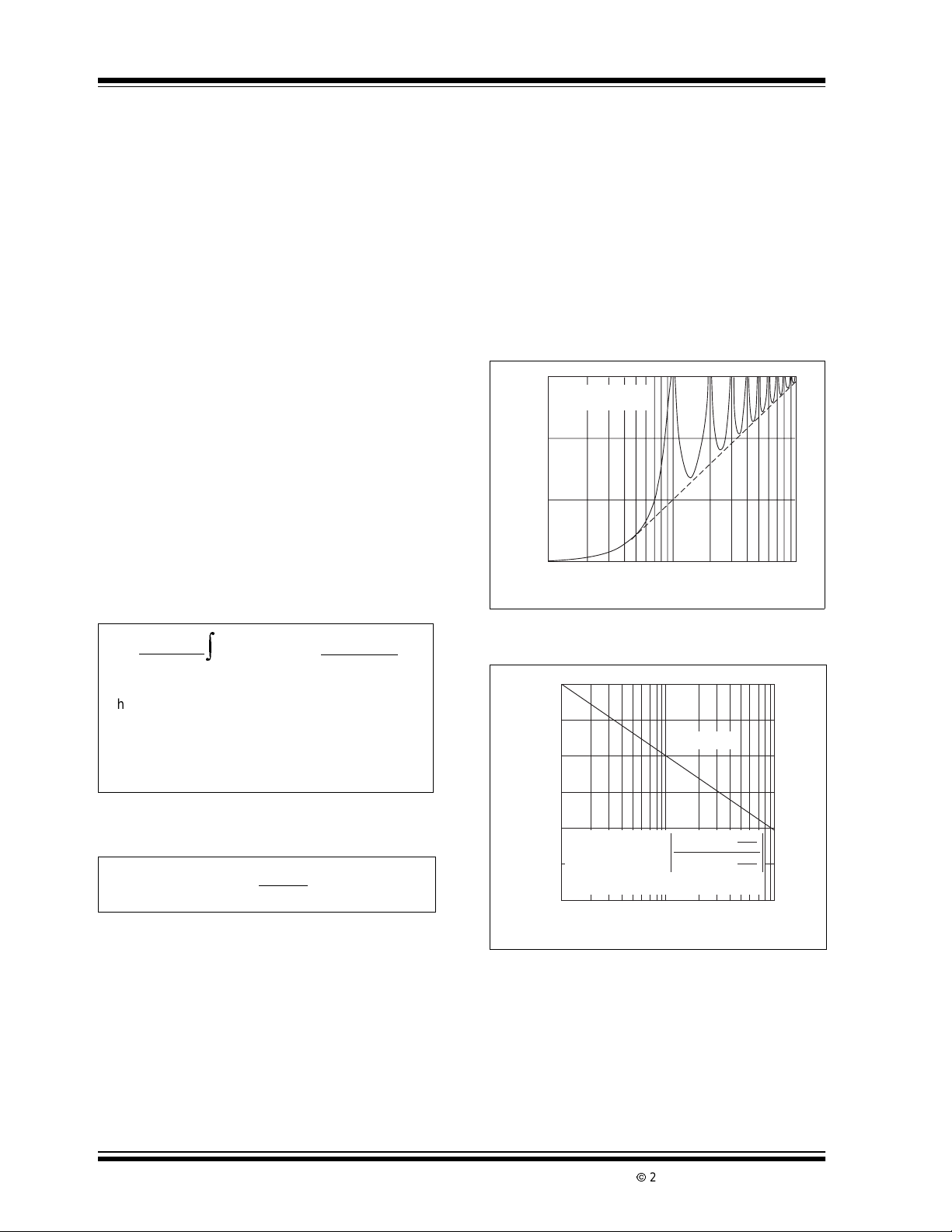

An inherent benefit is noise immunity. Input noise

spikes are i ntegrated (averaged to zero) during the

integration periods. Integrating ADCs are immune to

the large conversion errors that plague successive

approximation converters in high noise environments.

Integrating converters provide inherent noise rejection

with at least a 20dB/decade attenuation rate. Interference signals with frequencies at integral multiples of

to the integrator input where it is main-

R

INTCINT

IN

),as measured by the preci-

DEINT

T

1

INT

∫

V

IN

0

). The application of

INT

and a direction

IN

. The De-integration

IN

) to the integrator

IN

V

(T)DT =

REFTDEINT

R

INT

INTCINT

= Reference Voltage Integrationtime(variable)

T

REF

DEINT

T

INT

VIN=V

the integration period are, theoretically, completely

removed, since the average value of a sine wave of

frequency (1/T) averaged over a period (T) is zero.

Integrating converters often establish the integration

period to reject 50/60Hz line frequency interference

signals. The abilityto reject such signals is shown by a

normal mode rejection plot (Figure 3-1). Normal mode

rejection is limited in practice to 50 to 65dB, since the

line frequency can deviate by a few tenths of a percent

(Figure3-2).

FIGURE 3-1: INTEGRATING

CONVERTER NORMAL

.

30

Measurment

T =

Period

20

10

Normal Mode Rejection (dB)

0

0.1/T 1/T 10/

MODE REJECTION

Input Frequency

FIGURE 3-2: LINE FREQUENCY

DEVIATION

80

70

60

t = 0.1 sec

50

40

Normal Mode

REJECTION

30

DEV = Deviation from 60Hz

Normal Mode Rejeciton (dB)

t = Integration Period

20

= 20 LOG

SIN 60 t (1 ± )

0.01 0.1

DEV

p

100

DEV

p

60 t (1 ± )

100

1.0

Line Frequency Deviation from 60 Hz (%)

DS21428B-page 6

2002 Microchip TechnologyInc.

FIGURE 3-3: BASIC DUAL SLOPE CONVERTER

C

INT

Analog

Input (V

R

INT

)

IN

S1

Integrator

–

+

±

REF

VOLTAGE

Switch Driver

Polarity Control

TC500/A/510/514

TC510

V

INT

Phase

Control

–

+

Comparator

Control

Logic

AB

CMPTR Out

Output

Integrator

T

INT

T

DEINT

V

V

IN

IN

≈ V

REF

≈ 1/2 V

REF

V

SUPPLY

V

INT

Microcomputer

ROM

RAM

I/O

Timer

Counter

2002 Microchip TechnologyInc. DS21428B-page 7

TC500/A/510/514

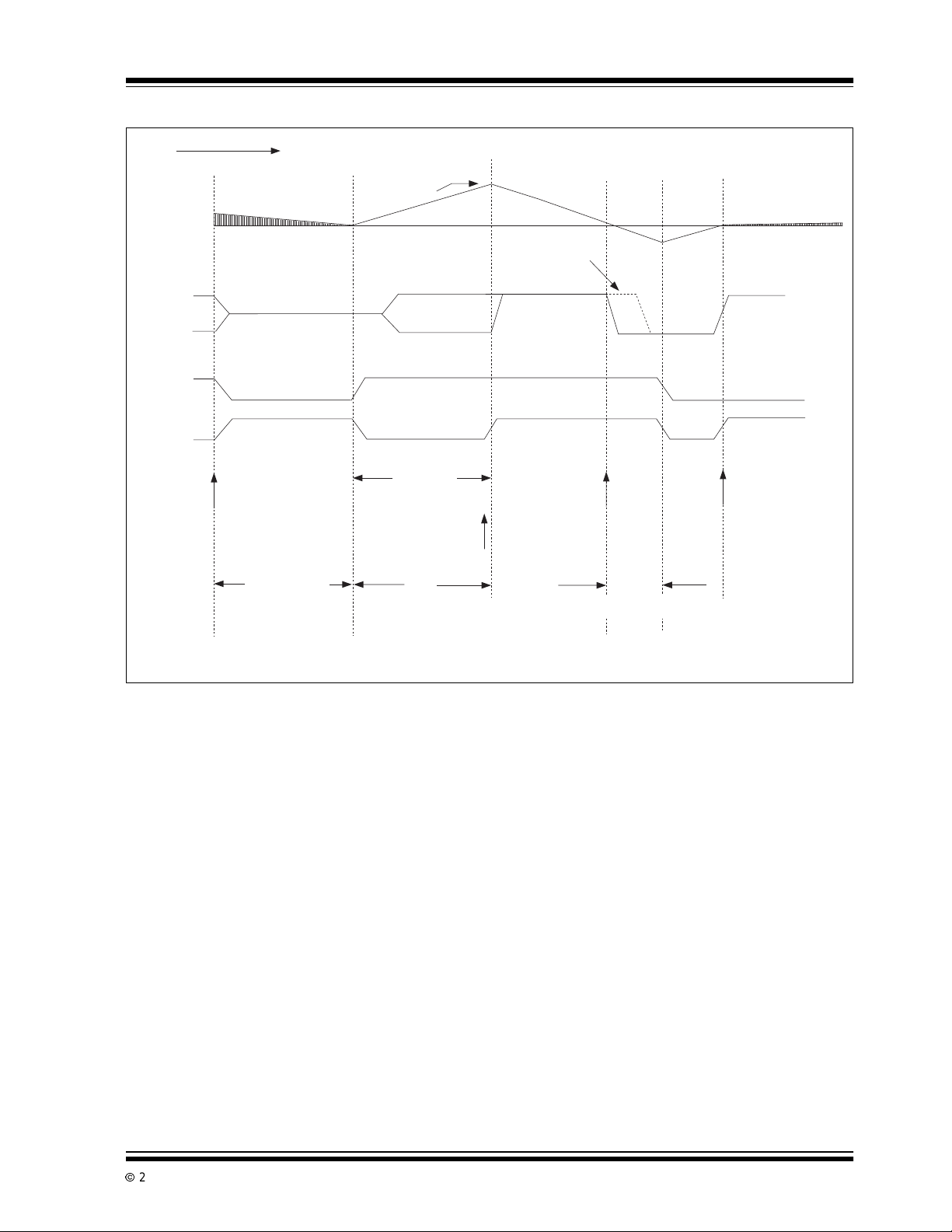

4.0 TC500/A/510/514 CONVERTER

OPERATION

The TC500/A/510/514 incorporates an Auto Zero and

IntegratorphaseinadditiontotheinputsignalIntegrate

and reference De-integrate phases. The addition of

these phases reduce system errors, calibration steps

and shorten overrange recovery time. A typical measurement cycle uses all four phases in the following

order:

1. Auto Zero

2. Input signal integration

3. Reference deintegration

4. Integrator output zero

The internal analog switch status for each of these

phases is summarized in Table 4-1. This table

references the Typical Application.

TABLE 4-1: INTERNAL ANALOG GATE STATUS

Conversion Phase SW

Auto Zero (A = 0, B = 1) Closed Closed Closed

Input Signal Integration (A = 1, B = 0) Closed

Reference Voltage De-integration

(A =1, B = 1)

Integrator Output Zero (A = 0, B = 0) Closed Closed Closed

Note: *Assumes a positive polarity input signal. SW

SWR+SWR-SWZSW

I

Closed* Closed

–

would be closed for a negative i nput signal.

RI

R

SW

SW

1

IZ

4.1 Auto Zero Phase (AZ)

During this phase, errors due to buffer, integrator and

comparator offset voltages are nulled out by charging

C

(auto zero capacitor) with a compensating er ror

AZ

voltage.

The externalinputsignal is disconnectedfromtheinter-

nal circuitry by opening the two SW

internal input points connect to analog common. The

referencecapacitoris charged to the reference voltage

potentialthroughSW

the integrator and comparator, charges the C

itor with a voltage to compensate for buffer amplifier,

integrator and comparator offset voltages.

.A feedbackloop,closedaround

R

switches. The

I

capac-

AZ

4.2 Analog Input Signal Integration

Phase (INT)

The TC5XX integratesthe differential voltage between

the (V

must be within the device's Common mode range

V

software at the end of this phase: CMPTR = 1 for

positive polarity; CMPTR = 0 for negative polarity.

+) and (VIN–) inputs. The differential voltage

IN

. The input signal polarityisnormally checked via

CMR

4.3 Reference Voltage De-integration

Phase (D

The previously charged reference capacitor is connected with the proper polarity to ramp the integrator

output back to zero. An externally-provided, precision

timer is used to measure the duration of this phase.

The resulting time measurement is proportional to the

magnitude of the applied input voltage.

INT

)

4.4 Integrator Output Zero Phase (IZ)

This phase ensuresthe integrator output is at 0V when

the Auto Zero phase is entered and that only system

offsetvoltagesare compensated.Thisphaseisused at

the end of the reference voltage de-integration phase

and MUST be usedfor ALL TC5XX applicationshaving

resolutionsof 12-bits or more. If t his phase is not used,

the value of the Auto Zero capacitor (C

about 2 to 3 times thevalue of the Integrationcapacitor

(C

) to reduce the effectsofchargesharing.TheInte-

INT

grator Output Zero phase should be programmed to

operate until the output of the comparator returns

"HIGH". The overall timing system is shown in

Figure 4-1.

)mustbe

AZ

DS21428B-page 8

2002 Microchip TechnologyInc.

TC500/A/510/514

FIGURE 4-1: TYPICAL DUAL SLOPE A/D CONVERTER SYSTEM TIMING

T

TIME

Converter Status

Integrator

Voltage

V

INT

Auto-Zero

0

Integrate

Full Scale Input

Reference

De-integrate

Comparator Delay

Overshoot Integrator

Output

Zero

Comparator

Output

A

AB Inputs

B

Controller

Operation

Notes:

Undefined

A = 0

B = 1

Begin Conversion with

Auto-Zero Phase

Typically = T

(Positive Input Shown)

The length of this phase is chosen almost arbitrarily

but needs to be long enough to null out worst case errors

(see text).

INT

0 For Negative Input

1 For Postive Input

A = 1

B = 0

Time Input

Integration

Phase

Sample Input Polarity

T

INT

Capture

De-integration

Time

A = 1

B = 1

A = 0

B = 0

I

ntegrator

Output

Zero Phase

Complete

Comparator Delay +

Processor Latency

Ready for Next

Conversion

(Auto-Zero is

Idle State)

Minimizing

Overshoot

will Minimize

I.O.Z. Time

2002 Microchip TechnologyInc. DS21428B-page 9

Loading...

Loading...