Page 1

SAMA5D3

X

PLAINED

SAMA5D3 XPLAINED

SAMA5D3 Xplained Evaluation Kit User’s Guide

Scope

This user guide introduces the Microchip SAMA5D3 Xplained evaluation kit and describes the development and debugging capabilities for applications running on a SAMA5D36 Arm®-based microprocessor unit (MPU).

This guide provides details on the SAMA5D3 Xplained evaluation kit. It is made up of four main sections:

• Section 1. “Evaluation Kit Specifications” describes the evaluation kit content and its main features.

• Section 2. “Power-Up” provides instructions to power up the SAMA5D3 Xplained board.

• Section 3. “Hardware Introduction” provides an overview of the SAMA5D3 Xplained board.

• Section 4. “Board Components” describes the SAMA5D3 Xplained board components.

Contents

• Boards

- One SAMA5D3 Xplained board

•Cables

- One Micro-AB type USB cable

• A welcome letter

Related Items

• SAMA5D3 Series Data Sheet

• SAMA5D3 Xplained Getting Started

2019 Microchip Technology Inc. DS50002884A-page 1

Page 2

SAMA5D3 XPLAINED

WARNING

WARNING

WARNING

Electrostatic

sensitive

device

1. Evaluation Kit Specifications

Table 1-1: Evaluation Kit Specifications

Characteristic Specifications

Temperature

Relative Humidity 0 to 90% (non-condensing)

RoHS status Compliant

Ordering code ATSAMA5D3-XPLD

1.1 Electrostatic Warning

Operating 0°C to +70°C

Storage -40°C to +85°C

ESD-Sensitive Electronic Equipment!

The evaluation kit is shipped in a protective anti-static package. The board system must not be subject to high electrostatic potentials.

We strongly recommend using a grounding strap or similar ESD protective device when handling

the board in hostile ESD environments (offices with synthetic carpet, for example). Avoid touching

the component pins or any other metallic element on the board.

1.2 Power Supply Warning

Hardware Power Supply Limitation

Using a power adapter greater than 5Vcc (e.g. the 12Vcc power adapters from other kits such as

Arduino kits) may damage the board.

Hardware Power Budget

Using the USB as the main power source (max. 500 mA) is acceptable only with the use of the onboard peripherals and low-power LCD extension.

When external peripheral or add-on boards need to be powered, we recommend the use of an external power adapter connected to a J2 DC Jack (can provide up to 1.2A on the 3.3V node).

DS50002884A-page 2 2019 Microchip Technology Inc.

Page 3

SAMA5D3 XPLAINED

WARNING

2. Power-Up

Several power source options are available to power up the SAMA5D3 Xplained board.

The board can be:

• USB-powered through the USB Micro-AB connector (J6 connector - default configuration)

• Powered through an external AC-to-DC adapter connected via a 2.1 mm center-positive plug into the optional power jack of the

board. The recommended output voltage range of the power adapter is 5V at 2A.

• Powered through the Arduino shield

Unlike Arduino Uno boards, the SAMA5D3 Xplained board runs at 3.3V. The maximum voltage that

the I/O pins can tolerate is 3.3V. Providing higher voltages (e.g. 5V) to an I/O pin could damage the

board.

2.1 Power up the Board

Unpack the board, taking care to avoid electrostatic discharge. Simply connect the USB Micro-AB cable to the connector (J6).Then, connect the other end of the cable to a free USB port of your PC.

Table 2-1: Electrical Characteristics

Electrical Parameter Values

Input voltage 5 VCC

Maximum input voltage 6 VCC

Max DC 3.3V current available 1.2A

I/O Voltage 3.3V only

2.2 Sample Code and Technical Support

After booting up the board, you can run sample code or your own application on the board. You can download sample code and get technical support from the Microchip website.

®

software and demos can be found on the website Linux4SAM.

Linux

2019 Microchip Technology Inc. DS50002884A-page 3

Page 4

SAMA5D3 XPLAINED

3. Hardware Introduction

3.1 Introduction

The SAMA5D3 Xplained board is a fully-featured evaluation platform for Microchip SAMA5D3 series MPUs. It allows users to extensively

evaluate, prototype and create application-specific designs.

3.2 Equipment List

The SAMA5D3 Xplained board is built around the integration of a Cortex®-A5-based MPU (BGA 324 package) with external memory, dual

Ethernet physical layer transceiver, two SD/MMC interfaces, two host USB ports and one device USB port, one 24-bit RGB LCD interface

and one debug interface.

Seven headers, compatible with Arduino R3, are available for various shield connections.

DS50002884A-page 4 2019 Microchip Technology Inc.

Page 5

3.3 Board features

Table 3-1: Board Specifications

Characteristics Specifications

PCB characteristics 125 x 75 x 20mm (10-layers)

SAMA5D3 XPLAINED

Processor

Processor clock sources

Memory

Optional on-board memory

SD/MMC

USB

Display interface

Ethernet

Debug port

Expansion connectors

Board supply voltage

Battery On-board optional power Cap for CMOS backup

User interface

SAMA5D36 (324-ball BGA package) ARM Cortex-A5 Processor with ARM

v7-A Thumb2

12-MHz crystal oscillator

32.768-kHz crystal oscillator

2 x 1Gb DDR2 (16M x 16 bits x 8 banks)

1 x 2Gb SLC NAND Flash (256M x 8 bits)

One Serial EEPROM SPI

One 1-Wire EEPROM

One 8-bit SD card connector

One optional 4-bit Micro-SD card connector

Two USB Hosts with power switch

One Micro-AB USB device

One LCD interface connector, LCD TFT Controller with overlay, alphablending, rotation, scaling and color space conversion

One Gigabit Ethernet PHY (GRMII 10/100/1000)

One Ethernet PHY (RMII 10/100)

One JTAG interface connector

One serial DBGU interface (3.3V level)

Arduino R3 compatible set of headers

The SAMA5D36 GPIO,TWI, SPI, USART, UART, Audio and ISI interfaces

are accessible through these headers.

5V from USB or power jack or Arduino shield

On-board power regulation is performed by a Power Management Unit

(PMU)

Reset, wake-up and free user push button

One red user/power LED and one blue user LED

®

instruction set, core frequency up to 536 MHz.

2019 Microchip Technology Inc. DS50002884A-page 5

Page 6

SAMA5D3 XPLAINED

ATSAMA5D36

CU

1401 A

XXXXXXXXXX

ARM

J15 PIO Expansion

1Gb DDR2 Memory

1Gb DDR2 Memory

2Gb Nand Flash Memory

System Buttons

JTAG Interface

LCD Connector

Ethernet 10/100

GigaBit Ethernet

J18 PIO Expansion

Free User Push Button

ADC Inputs and CAN Interfaces

Debug Interface

SAMA5D36

Voltages and Reset Interface

ADC Inputs Expansion

Optional Supply Input

USB A Device

Supply Input

SPI Interface

J20 PIO Expansion

J19 PIO Expansion

XX

USB Host Interfaces

A

4. Board Components

4.1 Board Overview

The full-featured SAMA5D3 Xplained board integrates several peripherals and interface connectors, as shown in Figure 4-1.

Figure 4-1: SAMA5D3 Xplained Board Overview

ctor

DS50002884A-page 6 2019 Microchip Technology Inc.

Page 7

SAMA5D3 XPLAINED

The SAMA5D3 Xplained board is equipped with the interface connectors described in Table 4-1.

Table 4-1: SAMA5D3 Xplained Board Interface Connectors

Header Interfaces to

J2 Main power supply

J6 USB-A device. Supports USB device using a Micro-AB connector

J7 (upper) USB-B Host. Supports USB host using a type A connector

J7 (lower) USB-C™ Host. Supports USB host using a type A connector

J23 Serial DBGU 3.3V level

J24 JTAG, 20-pin IDC connector

J10 SD/MMC connector

J11 Micro-SD connector

J12 Gigabit Ethernet ETH0

J13 Ethernet ETH1

J22

C41 Optional SuperCap

Expansion connector with all LCD controller signals for display module connection (QTouch

display with Touch Screen and backlight

®

, TFT LCD

J14–J21 Expansion connectors with Arduino R3 compatible PIO signals

– Various test points located on the board

2019 Microchip Technology Inc. DS50002884A-page 7

Page 8

SAMA5D3 XPLAINED

JTAG

DBGU

JTAG & DBGU

SERIAL

DATA

Micro SD

CARD

10/100/1000

FAST ETHERNET

10/100

ETHERNET

SD

CARD

LCD

Connector

FLASH

ETH0

ETH1

PIO A,...EPIO A,...E

Single

PMU

Solution

5V INPUT

SAMA5D36

CORTEX®-A5 PROCESSOR

2Gb

DDR2

SDRAM

2Gb

NAND

FLASH

USB

DEVICE

USB

Host

x2

ANALOG Reference

VBAT

USER

LEDS

PIO

Expansion Headers

Power rails

USB A,B,C

Reset

Force PwrOn

Push

Buttons

EBI

5V & 3V3

(Up to 4Gb)

(Up to 4Gb)

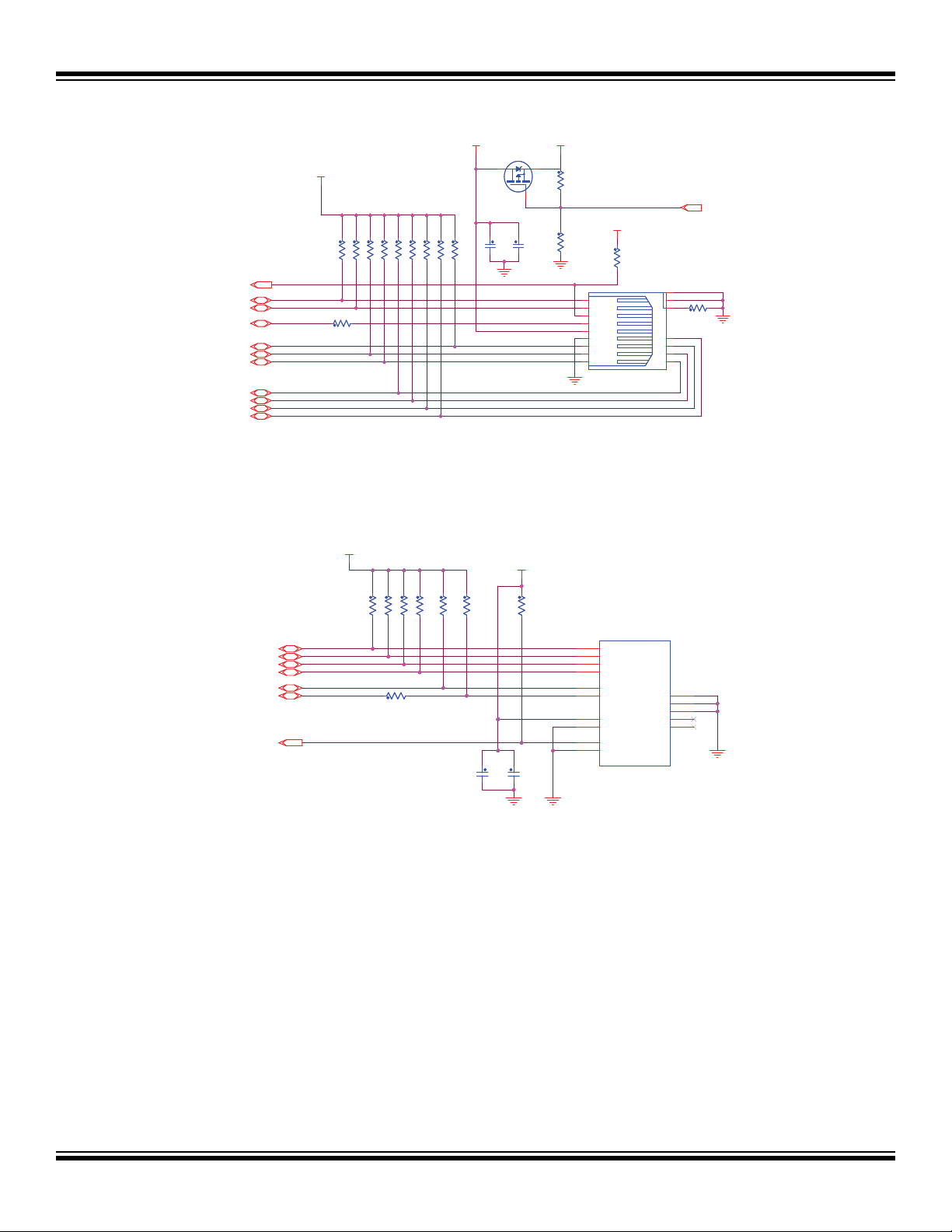

4.2 Function Blocks

Figure 4-2: Evaluation Kit Architecture

4.2.1 Processor

The SAMA5D3 Xplained board is built around the SAMA5D36, a Cortex-A5 application processor which combines high-performance computing device with low-power consumption and a wide range of communication peripherals. It features a combination of user interface

functionalities and high data rate IOs, including LCD controller, touchscreen, camera interface, Gigabit and 10/100 Ethernet ports, highspeed USB and SDIO.

The ARM Cortex-A5 supports the latest generation of DDR2 and NAND Flash memory interfaces for program and data storage. An internal

166-MHz multi-layer bus architecture associated with 24 DMA channels and two 64-Kbyte SRAM blocks, sustains the high bandwidth

required by the processor and the high-speed peripherals.

4.2.2 Clock Circuitry

The SAMA5D3 Xplained evaluation board features four clock sources:

• Two clocks are alternatives for the SAMA5D3 series processor main clock

• Two crystal oscillators are used for the GETH and Ethernet MII/RMII chip

Table 4-2: Main Components Associated with the Clock Systems

Quantity Description Component Assignment

1 Crystal for internal clock, 12 MHz Y1

1 Crystal for RTC clock, 32.768 kHz Y2

1 Oscillator for ethernet clock RGMII, 25 MHz Y3

1 Oscillator for ethernet clock RMII, 25 MHz Y4

DS50002884A-page 8 2019 Microchip Technology Inc.

Page 9

SAMA5D3 XPLAINED

WARNING

WARNING

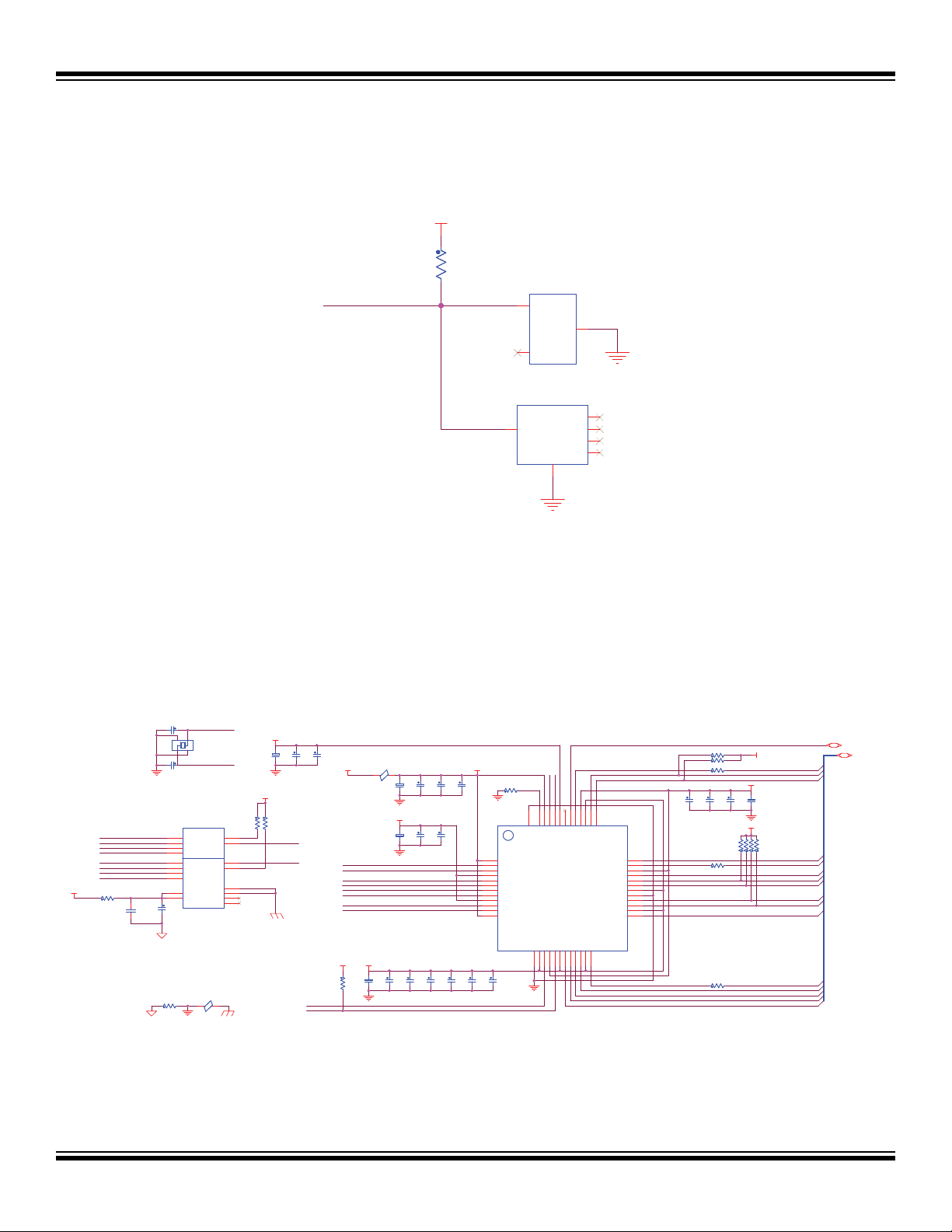

4.2.3 Power Supplies

The on-board power supply generation is based on the Active-Semi® Power Management Unit (PMU) featuring a 3-channel (3.3V / 1.8V

/1.2V or 1.0V) topology. For maximum efficiency, these supply channels are generated by three integrated step-down converters.

In addition to these 3 DCDC channels, 4 LDO channels with low noise and high PSRR performance are available for the application. These

channels are disabled at startup by default and can be turned on and adjusted under software control through an I²C link. They are also

used to supply the 2.5V VDDFUSE and the 3.3V VDDANA power inputs of the processor.

The power supply sequencing of the three primary channels is controlled by the PMU itself in full compliance with the SAMAD3 requirements. The turn-on sequence is: 3.3V first, then 1.8V and finally 1.2V.

There is a known error on the ACT8865 I²C implementation. The port must be shut off after configuration or problems may occur with devices using the same I²C channel, e.g., TM43xx LCD display.

Refer to the ACT8865 data sheet at http://www.active-semi.com/ for more details.

This evaluation kit was equipped with an engineering version of ACT8865 PMIC known as

ACT8865QI303-T. The singularity of this engineering version is that OUT4 and OUT5 outputs, normally enabled at power-up, are disabled at power-up. Consequently, VDDANA and VDDFUSE

power inputs of the processor are OFF when the external reset pin (NRST) is released. They must

therefore be turned on by software in the very first execution steps of the application. In particular,

VDDFUSE is needed to switch SAMA5D3 devices in Secure mode.

The engineering version ACT8865QI303-T of the active semi PMIC is end-of-life (EOL) and replaced

by ACT8865QI305-T devices that have OUT4 and OUT5 enabled by default at power-up. Refer to

the following application note:

https://active-semi.com/wp-content/uploads/ActiveSemi_-ACT8865QI305T_versus_ACT8865QI303-T.pdf

Table 4-3 summarizes the power specifications.

Table 4-3: Supply Group Configuration

Nominal Name Power Domains Power Source

The slow clock oscillator, the internal

3.0V VDDBU

3.3V VDDIOP0 A part of peripheral I/O lines

3.3V VDDIOP1 A part of peripheral I/O lines

3.3V VDDUTMII The three USB interfaces

3.3V VDDOSC The main oscillator cells

3.3V VDDANA The analog-to-digital converter

1.2V VDDCORE

32K RC, the internal 12 MHz RC and a part

of the system controller

The core, including the processor, the

embedded memories and the peripherals

Optional on-board battery

PMU

2019 Microchip Technology Inc. DS50002884A-page 9

Page 10

SAMA5D3 XPLAINED

BP2

BP1

5V_MAIN

VDDCORE

VDDIOP1

VDDIOP0

VDDANA

VDDPLLA

VDDOSC

VDDIODDR

VDDIOM

AVDDL_PLL

DVDDL

AVDDL

FUSE_2V5

5V_MAIN

3V3

3V3

VDDUTMIC

3V3

TWCK_PMIC[7]

TWD_PMIC[7]

NRST

[5,9,10,11]

SHDN[5]

PC31

[7]

WKUP

[5]

PE30

[7]

(1V2)

(1V8)

(3V3)

(3V3)

(2V5)

RESETWAKUP or

Force Power ON

Auto

PWRON

(option)

PC27

PC26

C10

100nF

C10

100nF

L9 2.2uHL9 2.2uH

R14

50K

R14

50K

C21

2.2uF

C21

2.2uF

BP2BP2

C4

1uFC41uF

C13

10uF

C13

10uF

R16 0RR16 0R

C23

2.2uF

C23

2.2uF

R17 2R2R17 2R2

C20

100nF

C20

100nF

MN1 ACT8865MN1 ACT8865

GNDP129GNDA

2

INL45

5

VP1

31

INL67

6

GNDP2

28

VP2

26

GNDP314EXPAD

33

VP3

16

NC2

25

VDDREF

23

nRST0

11

nIRQ

12

nPBSTAT

13

VSEL

20

NC1

18

PWRHLD

10

PWREN

17

SCL

21

SDA

22

REFBP

32

nPBIN

9

SW1

30

OUT1

1

OUT2

24

SW2

27

SW3

15

OUT3

19

OUT4

3

OUT5

4

OUT6

7

OUT7

8

C2

4.7uFC24.7uF

JP1

DNP(JUMPER)

JP1

DNP(JUMPER)

1

2

Q1

IRLML2502Q1IRLML2502

1

3

2

C5

1uFC51uF

R19

100K 1%

R19

100K 1%

C1

4.7uFC14.7uF

R150RR15

0R

L11

180ohm at 100MHz

L11

180ohm at 100MHz

1 2

L8

180ohm at 100MHz

L8

180ohm at 100MHz

1

2

C18

47nF

C18

47nF

C22

2.2uF

C22

2.2uF

JP3 DNP(JUMPER)JP3 DNP(JUMPER)

1

2

R11 0RR11 0R

TP2

SMD

TP2

SMD

C26

4.7uF

C26

4.7uF

C6

1uFC61uF

R6

1.5K 1%R61.5K 1%

L5

2.2uHL52.2uH

JP4

DNP(JUMPER)

JP4

DNP(JUMPER)

1

2

C25

100nF

C25

100nF

L6

10uH60mAL610uH60mA

C3

4.7uFC34.7uF

JP2

DNP(JUMPER)

JP2

DNP(JUMPER)

1

2

R7

1.5K 1%R71.5K 1%

C11

4.7uF

C11

4.7uF

R5 2R2R5 2R2

R8

10KR810K

R41RR4

1R

C17

100nF

C17

100nF

C9

10uFC910uF

L7 2.2uHL7 2.2uH

C19

100nF

C19

100nF

L12

10uH60mA

L12

10uH60mA

C7

4.7uFC74.7uF

R186 0RR186 0R

L3

180ohm at 100MHz

L3

180ohm at 100MHz

1 2

L1

180ohm at 100MHz

L1

180ohm at 100MHz

1 2

R12 49.9K

L10

180ohm at 100MHz

L10

180ohm at 100MHz

1 2

C15

10uF

C15

10uF

TP1

SMD

TP1

SMD

C14

100nF

C14

100nF

R18 1KR18 1K

C130

10nF

C130

10nF

C16

10uF

C16

10uF

C8

10uFC810uF

R9 DNP(0R)R9 DNP(0R)

C24

2.2uF

C24

2.2uF

R13 0RR13 0R

R10 2R2R10 2R2

L4

10uH60mAL410uH60mA

L2

180ohm at 100MHz

L2

180ohm at 100MHz

1 2

BP1BP1

C12

10uF

C12

10uF

Table 4-3: Supply Group Configuration (Continued)

Nominal Name Power Domains Power Source

1.2V VDDUTMIC The USB UTMI + core

1.2V VDDPLLA The PLLA cell

1.8V VDDIODDR DDR2 interface I/O lines

1.8V VDDIOM

3.0V to

3.3V

ADVREF ADC reference voltage J15 header

NAND, NOR Flash and SMC interface I/O

lines

2.5V VDDFUSE Fuse box for programming PMU

Note: Jumper footprints are available on-board to measure power consumption on main power lines. By default, the jumpers are not

implemented. They are short-circuited by a thin PCB wire. To use this functionality, open the short circuit and mount a 2-pin

jumper.

Figure 4-3: Board Power Management Schematic

PMU

DS50002884A-page 10 2019 Microchip Technology Inc.

Page 11

SAMA5D3 XPLAINED

5V_MAIN

Vbus[5]

5V_Ext[11]

R175 0RR175 0R

J2

DNP(DC JACK)

J2

DNP(DC JACK)

3

1

2

R176 DNP(0R)R176 DNP(0R)

D4

P4SMAJ5.0A

D4

P4SMAJ5.0A

1 2

R3 DNP(0R)R3 DNP(0R)

R1 0RR1 0R

R2 DNP(0R)R2 DNP(0R)

R177 DNP(0R)R177 DNP(0R)

TDI

TMS

TCK

TDO

NTRST

NRST

VDDBU

3V3

3V3

TMS

[11]

TCK

[11]

TDO

[11]

TDI

[11]

NRST[4,9,10,11]

NTRST

[11]

VBat

[11]

(Super)-Capacitor

energy storage

Place TP4 to Bottom

Populate R185 if

no Super Cap (C41)

R25 10KR25 10K

R185

1.5K 1%

R185

1.5K 1%

D1

BAT54CLT1

D1

1 2

3

TP4

SMD

TP4

SMD

C27

10nF

C27

10nF

C28

100nF

C28

100nF

C41

DNP(0.2F/3V3)

C41

DNP(0.2F/3V3)

TDO

M11

TMS

N10

TCK

P9

NTRST

P11

TDI

R8

JTAGSEL

T9

BMS

U9

TST

U15

NRST

V9

VDDBU

V15

R23

1.5K 1%

R23

1.5K 1%

R21

100K 1%

R21

100K 1%

R22

DNP(100K)

R22

DNP(100K)

R20 100RR20 100R

4.2.3.1 Power Options

Several power options are available to configure the SAMA5D3 Xplained board powering scheme.

The power sources are selected by a set of 0R resistors.

The USB-powered operation is the default configuration. The power source is the USB device port (J6) connected to a PC or a mini-AB

5V DC supply. The USB supply is sufficient to power the board in most applications if USB host ports are not used. If USB host ports are

used, it is recommended to use a DC supply source.

Schematic diagrams of various power options are illustrated in Figure 4-4.

Figure 4-4: Input Powering Scheme Option Schematic

Note: USB-powered operation is a good “single cable” solution because it combines powering and board control through a unique

cable. Consequently, it eliminates the need for other wires and batteries. This power option is suitable for most projects that

only require 5 volts at up to 500 mA.

4.2.3.2 Mains Power Adapter

A mains power supply adapter can be used to provide power to the board. A regulated 5V DC supply of typically 2A is required but a

current range of 3A is recommended if the USB ports and expansion headers are likely to be used. It needs a 2.1 mm plug with a centerhot configuration.

If you are using the USB host ports or expansion board Arduino shields, a higher current is required. To supply the full 500 mA per port,

a mains power adapter must be used.

4.2.3.3 VBAT

By default, VDDBU is delivered through the 3.3V node. An optional SuperCap (C41), used for real-time clock backup, is provided. The

board does not come equipped with the SuperCap. When the SuperCap is not installed, an R185 must be installed. You must make sure

that the R185 is removed prior to installing the SuperCap.

Figure 4-5: VBAT Powering Scheme Option Schematic

4.2.4 Reset Circuitry

The reset sources for the SAMA5D3 Xplained board are:

2019 Microchip Technology Inc. DS50002884A-page 11

Page 12

SAMA5D3 XPLAINED

DDR_A8

DDR_D9

DDR_D10

DDR_D11

DDR_D12

DDR_D13

DDR_D15

DDR_D14

DDR_A1

DDR_A9

DDR_A2

DDR_D2

DDR_A10

DDR_A3

DDR_A11

DDR_A4

DDR_A12

DDR_A5

DDR_D1

DDR_VREF

DDR_D0

DDR_A6

DDR_D4

DDR_D3

DDR_A7

DDR_D6

DDR_D5

DDR_D7

DDR_D8

DDR_A0

DDR_A8

DDR_D27

DDR_D26

DDR_D25

DDR_D31

DDR_D29

DDR_D28

DDR_D30

DDR_A1

DDR_A9

DDR_A2

DDR_A10

DDR_D18

DDR_A3

DDR_A11

DDR_A4

DDR_A12

DDR_A5

DDR_VREF

DDR_D17

DDR_D16

DDR_A6

DDR_D19

DDR_D20

DDR_D22

DDR_A7

DDR_D23

DDR_D21

DDR_D24

DDR_A0

DDR_DQM0

DDR_DQS1

DDR_DQS0

DDR_CS

DDR_BA0

DDR_BA1

DDR_BA2

DDR_CKE

DDR_WE

DDR_CLK

DDR_RAS

DDR_CLKN

DDR_CAS

DDR_DQM2

DDR_DQS2

DDR_DQS3

DDR_CS

DDR_BA0

DDR_BA1

DDR_BA2

DDR_WE

DDR_CKE

DDR_RAS

DDR_CLK

DDR_CAS

DDR_CLKN

DDR_A13

DDR_DQM1

DDR_DQM3

DDR_A13

VDDIODDR

VDDIODDR

VDDIODDR

VDDIODDR

DDR_A[0..13]

DDR_D[0..31]

C98

100nF

C98

100nF

C73 100nFC73 100nF

C100

100nF

C100

100nF

C68 100nFC68 100nF

R39 4.7KR39 4.7K

C93 100nFC93 100nF

C90 100nFC90 100nF

C69 100nFC69 100nF

R41 4.7KR41 4.7K

C91 100nFC91 100nF

C70 100nFC70 100nF

C97 100nFC97 100nF

MT47H64M16HR

DDR2 SDRAM

MN5

MT47H64M16HR

DDR2 SDRAM

MN5

A0

M8

A1

M3

A2

M7

A3

N2

A4

N8

A5

N3

A6

N7

A7

P2

A8

P8

A9

P3

A10

M2

BA0

L2

ODT

K9

DQ0

G8

DQ1

G2

DQ2

H7

DQ3

H3

DQ4

H1

DQ5

H9

DQ6

F1

DQ7

F9

UDQS

B7

UDQS

A8

LDM

F3

VDD

J9

VDD

M9

VDDL

J1

VREF

J2

VDDQ

E9

VSS

A3

VSS

E3

VDDQ

A9

VDD

E1

RFU1

A2

RFU2

E2

CKE

K2

CK

J8

CK

K8

CAS

L7

RAS

K7

WE

K3

CS

L8

VDDQ

C3

VDDQ

C7

VDDQ

C9

VSSQ

D8

VSSQ

E7

VSSQ

F2

VSSQ

F8

VDD

A1

VSS

J3

A11

P7

BA1

L3

A12

R2

BA2

L1

VSS

N1

VSSDL

J7

VSSQ

B2

RFU3

R3

DQ8

C8

DQ9

C2

DQ10

D7

DQ11

D3

DQ12

D1

DQ13

D9

DQ14

B1

DQ15

B9

VDD

R1

VDDQ

G1

VDDQ

G7

VDDQ

G9

VSS

P9

VSSQ

D2

VSSQ

A7

VSSQ

B8

VSSQ

H2

VSSQ

H8

VDDQ

G3

VDDQ

C1

UDM

B3

LDQS

E8

LDQS

F7

RFU4

R7

A13

R8

R40 4.7KR40 4.7K

C79 100nFC79 100nF

R36

DNP(1K)

R36

DNP(1K)

C71 100nFC71 100nF

R42 4.7KR42 4.7K

MT47H64M16HR

DDR2 SDRAM

MN4

MT47H64M16HR

DDR2 SDRAM

MN4

A0

M8

A1

M3

A2

M7

A3

N2

A4

N8

A5

N3

A6

N7

A7

P2

A8

P8

A9

P3

A10

M2

BA0

L2

ODT

K9

DQ0

G8

DQ1

G2

DQ2

H7

DQ3

H3

DQ4

H1

DQ5

H9

DQ6

F1

DQ7

F9

UDQS

B7

UDQS

A8

LDM

F3

VDD

J9

VDD

M9

VDDL

J1

VREF

J2

VDDQ

E9

VSS

A3

VSS

E3

VDDQ

A9

VDD

E1

RFU1

A2

RFU2

E2

CKE

K2

CK

J8

CK

K8

CAS

L7

RAS

K7

WE

K3

CS

L8

VDDQ

C3

VDDQ

C7

VDDQ

C9

VSSQ

D8

VSSQ

E7

VSSQ

F2

VSSQ

F8

VDD

A1

VSS

J3

A11

P7

BA1

L3

A12

R2

BA2

L1

VSS

N1

VSSDL

J7

VSSQ

B2

RFU3

R3

DQ8

C8

DQ9

C2

DQ10

D7

DQ11

D3

DQ12

D1

DQ13

D9

DQ14

B1

DQ15

B9

VDD

R1

VDDQ

G1

VDDQ

G7

VDDQ

G9

VSS

P9

VSSQ

D2

VSSQ

A7

VSSQ

B8

VSSQ

H2

VSSQ

H8

VDDQ

G3

VDDQ

C1

UDM

B3

LDQS

E8

LDQS

F7

RFU4

R7

A13

R8

C94 100nFC94 100nF

C78 100nFC78 100nF

C74 100nFC74 100nFR380RR38

0R

C95 100nFC95 100nF

C75 100nFC75 100nF

C96 100nFC96 100nF

R37 0RR37 0R

C88 100nFC88 100nF

C80 100nFC80 100nF

C89 100nFC89 100nF

C82 100nFC82 100nF

R35 DNP(1K)R35 DNP(1K)

C66 100nFC66 100nF

C83 100nFC83 100nF

C81 100nFC81 100nF

C84 100nFC84 100nF

C76 100nFC76 100nF

C86 100nFC86 100nFC85 100nFC85 100nF

C77 100nFC77 100nF

C67 100nFC67 100nF

C87 100nFC87 100nF

C92 100nFC92 100nF

C72 100nFC72 100nF

DDR_VREF

VDDIODDR

R46

1.5K 1%

R46

1.5K 1%

R451RR45

1R

R47

1.5K 1%

R47

1.5K 1%

C101

4.7uF

C101

4.7uF

TP3

SMD

TP3

SMD

L16

10uH60mA

L16

10uH60mA

C102

100nF

C102

100nF

C104

100nF

C104

100nF

C103

4.7uF

C103

4.7uF

• Power-on reset from the Power Management Unit (PMU),

• Reset Push button BP2,

• JTAG reset from an in-circuit emulator (through JTAG interface)

4.2.5 Memory Organization

The SAMA5D3x-series processor features a DDR2/SDRAM memory interface and an External Bus Interface (EBI) to interface with a wide

range of external memories and to almost any kind of parallel peripherals.

The memory devices that equip the SAMA5D3 Xplained evaluation kit are as follows:

• Two DDR2/SDRAM (MT47H64M16HR) used as main system memory (256 MByte). The board includes 2 Gbits of on-board soldered DDR2 (double data rate) SDRAM. The footprints can also host two DDR2 (MT47H128M16RT) from Micron

MBytes of DDR2 memory. The memory bus is 32 bits wide and operates with a frequency of up to 166 MHz (See Figure 4-6).

• One NAND Flash (MT29F2G08ABAEAWP) connected to the processor. The default size is 256 Mbytes. The footprint can also host

a 4-Gbit Micron chip for a total of 512 MBytes of NAND Flash memory (See Figure 4-7).

Figure 4-6: DDR2 Schematic

®

for a total of 512

DS50002884A-page 12 2019 Microchip Technology Inc.

Page 13

Figure 4-7: NAND Flash Schematic

NRD

NWE

M_EBI_D2

M_EBI_D4

M_EBI_D3

M_EBI_D6

M_EBI_D7

M_EBI_D5

M_EBI_D0

M_EBI_D1

NANDRDY

PE21

PE22

NCS3

VDDIOM

VDDIOM

(NANDCE)

(NANDCLE)

(NANDALE)

C105

100nF

C105

100nF

R48

100K 1%

R48

100K 1%

R50

100K 1%

R50

100K 1%

JP5

JUMPER

JP5

JUMPER

1

2

R49

100K 1%

R49

100K 1%

MN6

MT29F2G08ABAEAWP

MN6

MT29F2G08ABAEAWP

WE

18

N.C6

6

VCC

37

CE

9

RE

8

N.C11

20

WP

19

N.C5

5

N.C1

1

N.C2

2

N.C3

3

N.C4

4

DNU1

21

DNU2

22

N.C12

23

N.C13

24

R/B

7

I/O8_N.C

26

I/O9_N.C

27

I/O10_N.C

28

I/O0

29

VCC_N.C

34

N.C14

35

VSS

36

DNU3

38

VCC_N.C

39

VCC

12

VSS

13

ALE

17

N.C8

11

N.C7

10

N.C9

14

N.C10

15

CLE

16

VSS_N.C

25

I/O11_N.C

33

I/O1

30

I/O3

32

I/O2

31

I/O15_N.C

47

I/O14_N.C

46

I/O13_N.C

45

I/O7

44

I/O6

43

I/O5

42

I/O4

41

I/O12_N.C

40

VSS_N.C

48

C106

100nF

C106

100nF

The following memory part numbers are recommended:

Table 4-4: Recommended Memories

Part Number Supplier Size Type

MT47H128M16 Micron 2 Gb (

16 M x 16 x 8 banks) DDR2 - BGA

SAMA5D3 XPLAINED

MT47H128M32 Micron 4 Gb (32

M x 16 x 8 banks) DDR2 - BGA

MT29F2G08 Micron 2 Gb NAND Flash - TSOP

MT29F4G08 Micron 4 Gb NAND Flash - TSOP

4.2.6 SD/MMC Interface

The SAMA5D3 Xplained board features two high-speed Multimedia Card Interfaces (MCI).

• The first interface is used as an 8-bit interface (MCI0), connected to a SD/MMC card slot (J10) located on the bottom side of the

PCB.

• The second interface is used as a 4-bit interface (MCI1), connected to an optional Micro-SD card connector (J11) located on the top

side of the PCB.

The MCI0 SD card power line is enabled by default. It is PIO-controlled through a MOSFET transistor.

Note: The power source is VCC (3.3 volts).

4.2.6.1 J10 SD Card Slot

When a card is inserted into the SD/MMC connector, the Card Detect pin (PE0) is tied to ground.

2019 Microchip Technology Inc. DS50002884A-page 13

Page 14

SAMA5D3 XPLAINED

VDDIOP1

VDD_MCI0

VDDIOP1

VDDIOM

PD1[7]

PE2 [7]

PD9[7]

PD0

[7]

PD4[7]

PD3[7]

PE0[7]

PD6[7]

PD7[7]

PD8[7]

PD5[7]

PD2[7]

(MCI0_CD)

(MCI0_WP)

(MCI0_DA1)

(MCI0_DA0)

(MCI0_CK)

(MCI0_CDA)

(MCI0_DA3)

(MCI0_DA2)

(MCI0_DA4)

(MCI0_DA5)

(MCI0_DA7)

(MCI0_DA6)

C108

10uF

C108

10uF

R55

DNP(4.7K)

R55

DNP(4.7K)

R12268K R12268K

R182 22RR182 22R

R12768K R12768K

J10

7SDMM-B0-2211

J10

7SDMM-B0-2211

8

5

7

6

4

3

2

1

9

14

15

16

13

12

11

10

R5410K R5410K

R12468K R12468K

R53

100K 1%

R53

100K 1%

R57 0RR57 0R

R12668K R12668K

R12168K R12168K

Q3

IRLML6402

Q3

IRLML6402

1

3

2

R12368K R12368K

R56

10K

R56

10K

R12868K R12868K

C109

100nF

C109

100nF

R12568K R12568K

Figure 4-8: J10 SD Card Schematic

4.2.6.2 J11 SD Card Slot (optional)

When a card is inserted into the Micro SD connector, the Card Detect pin is tied to ground. This is detected on pin PE1 of the main processor.

Figure 4-9: J11 Micro SD Card Schematic

VDDIOP1

VDDIOM

R12968K R12968K

R13268K R13268K

R5810K R5810K

R112DNP(68K) R112DNP(68K)

C110

C110

10uF

10uF

C111

C111

100nF

100nF

R59

R59

10K

10K

7

DAT0

8

DAT1

1

DAT2

2

DAT3

3

CMD

5

CLK

4

VDD

6

VSS

9

CD

10

PGND

J11

J11

PGND

PGND

PGND

DNP(MCTF-0403)

DNP(MCTF-0403)

11

12

13

14

NC

15

NC

R13068K R13068K

R13168K R13168K

PB20[7]

PB21[7]

PB22[7]

PB23[7]

PB19[7]

PB24

[7]

PE1[7]

(MCI1_DA0)

(MCI1_DA1)

(MCI1_DA2)

(MCI1_DA3)

(MCI1_CDA)

(MCI1_CK)

(MCI1_CD)

R183 22RR183 22R

Micro SD CARD INTERFACE - MCI1

4.2.7 Serial Peripheral Interface (SPI)

The SAMA5D3X-series processor features two high-speed Serial Peripheral Interfaces. One port is used to interface with the optional onboard serial DataFlash®.

There are four main signals used in the SPI interface; Clock, Data In, Data Out, and Chip Select.

DS50002884A-page 14 2019 Microchip Technology Inc.

Page 15

Figure 4-10: Optional Serial DataFlash Schematic

VDDIOP1

R52

R52

100K 1%

100K 1%

PD11

PD10

PD12

PD13

(SPI0_MOSI)

(SPI0_MIS0)

(SPI0_SPCK)

(SPI0_CS)

1

2

JP6

JP6

JUMPER

JUMPER

MN8

MN8

5

DQO

2

DQ1

6

C

W/Vpp/DQ2

HOLD/DQ3

1

S

DNP(N25Q032A13ESE40F)

DNP(N25Q032A13ESE40F)

VCC

GND

8

3

7

4

SAMA5D3 XPLAINED

VDDIOP1

C107

C107

100nF

100nF

2019 Microchip Technology Inc. DS50002884A-page 15

Page 16

SAMA5D3 XPLAINED

PB3

PB2

PB1

PB0

PB4

PB5

PB6

PB7

ETH0_A+

ETH0_A-

ETH0_BETH0_C+

ETH0_C-

ETH0_D+

ETH0_D-

PB16

PB11

PB13

PB9

PB17

PB10

ETH0_LED2

XI

XO

ETH0_LED1

XI

XO

PB18

PB8

ETH0_B+

VDDIOP1

DVDDL

AVDDL

AVDDH

AVDDL_PLL

VDDIOP1

VDDIOP1

VDDIOP1

VDDIOP1

PB[0..31]

[7,8,10,11]

NRST [4,5,10,11]

G125CK

GTX0

GTX1

GTX2

GTX3

GRX0

GRX1

GRX2

GRX3

GTXCK

GTX_CTL

GRXCK

GRX_CTL

GMDC

GMDIO

INT_GETHR

10Base-T/100Base-TX/1000BASE-T

R64

4.7K

R64

4.7K

R68 22RR68 22R

+

C127

10uF

+

C127

10uF

C112 20pFC112 20pF

R61 1KR61 1K

C120

10nF

C120

10nF

R67

4.7K

R67

4.7K

C136

10nF

C136

10nF

+

C113

10uF

+

C113

10uF

Y3

25MHzY325MHz

1

23

4

C121

10nF

C121

10nF

C135

10nF

C135

10nF

C129

10nF

C129

10nF

+

C126

10uF

+

C126

10uF

C116 20pFC116 20pF

R69

4.7K

R69

4.7K

C119

10nF

C119

10nF

L17

180ohm at 100MHz

L17

180ohm at 100MHz

1 2

C122

10nF

C122

10nF

C115

10nF

C115

10nF

R65

4.7K

R65

4.7K

C134

10nF

C134

10nF

C128

10nF

C128

10nF

C118

10nF

C118

10nF

C114

10nF

C114

10nF

C133

10nF

C133

10nF

C123

10nF

C123

10nF

KSZ9031RNI

48-pin QFN

MN10

KSZ9031RN

KSZ9031RNI

48-pin QFN

MN10

KSZ9031RN

VSS_PS13LED215DVDDH16LED117DVDDL14TXD019TXD120TXD221TXD322DVDDL18DVDDL23GTX_CLK

24

TX_EN

25

DVDDL

26

RXD3

27

VSS

29

DVDDL

30

RXD1

31

RXD0

32

RX_DV

33

DVDDH

34

RX_CLK

35

MDC

36

MDIO

37

INT_N

38

DVDDL

39

DVDDH

40

CLK125_NDO

41

RESET_N

42

LDO_O

43

XO

45

XI

46

AVDDH

47

ISET

48

AVDDH

1

TXRXP_A

2

TXRXM_A

3

TXRXP_B

5

TXRXM_B

6

TXRXP_C

7

TXRXM_C

8

TXRXP_D

10

TXRXM_D

11

AVDDH

12

RXD2

28

AVDDL_PLL

44

P_GND

49

AVDDL

4

AVDDL

9

R66

4.7K

R66

4.7K

R63 12.1K 1%R63 12.1K 1%

C138

10nF

C138

10nF

R60 4.7KR60 4.7K

+

C117

10uF

+

C117

10uF

C137

10nF

C137

10nF

R70 22RR70 22R

+

C132

10uF

+

C132

10uF

R62 22RR62 22R

EARTH_ETH0

ETH0_GND

R73 0RR73 0R

L18 180ohm at 100MHzL18 180ohm at 100MHz

1

2

ETH0_B+

ETH0_B-

ETH0_D+

ETH0_D-

ETH0_A+

ETH0_A-

ETH0_C+

ETH0_C-

ETH0_LED1

ETH0_LED2

AVDDH

VDDIOP1

EARTH_ETH0

ETH0_GND

LINK

ACT

Left Green LED

Right Yellow LED

C124

100nF

C124

100nF

R71470R R71470R

J12

48F-01GY2DPL2NL

J12

48F-01GY2DPL2NL

TD2+

3

TD1+

1

TD1-

2

TD3+

7

TD3-

8

RCT

6

TD2-

4

GRLA

11

GRLC

12

TD4+

9

TD4-

10

TCT

5

YELC

13

YELA

14

GND

15

GND

16

GND

17

GND

18

R72470R R72470R

R111 DNP(0R)R111 DNP(0R)

C125

DNP(10uF 0805)

C125

DNP(10uF 0805)

4.2.8 Optional 1-Wire EEPROM

The SAMA5D3 Xplained board can use a 1-Wire device as “soft label” to store data such as chip type, manufacturer’s name, production

date, etc.

Figure 4-11: Optional One-Wire EEPROM Schematic

VDDIOM

R51

R51

1.5K

1.5K

MN11

PE23

MN11

1

IO

2

NC

DNP(DS28E05)

DNP(DS28E05)

2

IO

GND

MN7

MN7

NC1

NC2

NC3

NC4

GND

1

DNP(DS2431)

DNP(DS2431)

3

3

4

5

6

4.2.9 10/100/100 Ethernet Port

The SAMA5D3 Xplained board features a MICREL PHY device (KSZ9031RN) operating at 10/100/1000 Mb/s. The board supports the

RGMII Interface mode. The Ethernet interface consists of four pairs of low-voltage differential pair signals designated from GRX± and

GTX± plus Control signals for link activity indicators. These signals are routed to the 10/100/1000BASE-T RJ45 connector (J12).

For monitoring and control purposes, LEDs are integrated in the RJ45 connectors to indicate activity, link, and speed status information

for the corresponding ports.

For more information about the Ethernet controller device, refer to the MICREL KSZ9031RN data sheet.

Figure 4-12: Gigabit Ethernet Schematic

DS50002884A-page 16 2019 Microchip Technology Inc.

Page 17

SAMA5D3 XPLAINED

4.2.10 Ethernet 10/100 Port

The SAMA5D3 Xplained board features a MICREL PHY device (KSZ8081RNB) operating at 10/100 Mb/s. The board supports RMII interface modes. The Ethernet interface consists of two pairs of low-voltage differential pair signals designated from GRX± and GTX± plus

Control signals for link activity indicators. These signals are routed to the 10/100BASE-T RJ45 connector (J13).

For monitoring and control purposes, an LED functionality is added on the RJ45 connectors to indicate activity, link, and speed status

information for the corresponding ports.

For more information about the Ethernet controller device, refer to the MICREL KSZ8081RNB controller manufacturer's data sheet.

Figure 4-13: RMII Ethernet Schematic

VDDIOP1 VDDIOP0

L19

L19

1 2

+

+

C144

C144

10uF

10uF

+

+

C146

C146

10uF

10uF

R741KR74

1K

VDDIOP0

180ohm at 100MHz

180ohm at 100MHz

NRST [4,5,9,11]

EARTH_ETH1

VDDIOP0

13

14

15

16

R79 470RR79 470R

R80 470RR80 470R

1

TX+

1

TX+

2

TX-

2

TX-

3

RX+

3

RX+

6

RX-

6

RX-

4

4

5

5

7

7

8

8

12

R81 0RR81 0R

10Base-T/100Base-TX

MN9

J1313F-64GYD2PL2NL

J1313F-64GYD2PL2NL

TD+

TD+

1

CT

CT

4

TD-

TD-

2

RD+

RD+

3

CT

CT

5

RD-

RD-

6

C139

C139

100nF

NC

NC

7

8

9

180ohm at 100MHz

180ohm at 100MHz

100nF

GND_ETH1

EARTH_ETH1

75 75

75 75

75

75

1nF

1nF

75

75

Left Green LED Right yellow LED

Left Green LED Right yellow LED

10

11

VDDIOP0

+

+

C148

C148

10uF

10uF

L20

L20

1 2

EARTH_ETH1GND_ETH1

C140

C140

100nF

100nF

ETH1_LED0

TX-

RX+

RX-

ACT

LINK

ETH1_LED0

ETH1_LED1ETH1_LED1

C147 20pFC147 20pF

C149

C149

20pF

20pF

23

VDDIOP0

R77

R77

10K

10K

1

4

25MHzY425MHz

Y4

R78

R78

10K

10K

ETH1_XI

ETH1_XO

TX+TX+

TX-

RX+

RX-

C141 2.2uFC141 2.2uF

C142 100nFC142 100nF

7

TXP

6

TXM

5

RXP

4

RXM

2

VDD_1V2

1

GND

33

PADDLE

22

TXC

26

TXD2

27

TXD3

R766.49k/1% R766.49k/1% C143

10

REXT

ETH1_XO

8

XO

ETH1_XI

9

XI

30

LED0/NWAYEN

31

LED1/SPEED

RXC/B-CAST_OFF

TXD1

TXD0

TXEN

RXD3/PHYAD0

RXD2/PHYAD1

RXD1/PHYAD2

RXD0/DUPLEX

RXDV/CONFIG2

RXER/ISO

CRS/CONFIG1

COL/CONFIG0

MDIO

INTRP/NAND

VDDA_3V3

VDDIO

RESET

KSZ8081RNB

KSZ8081RNB

MN9

19

25

24

23

13

14

15

16

18

20

29

28

12

MDC

11

21

E1_AVDDT

3

C143

100nF

100nF

17

C145

C145

100nF

100nF

32

4.2.11 Indicators

Two LEDs are available on the SAMA5D3 Xplained board. Both can be software-controlled by the user.

• The red LED indicates that power is applied to the board (by default). It can be controlled via software.

• The blue LED is mainly controlled by one GPIO line.

R751KR75

1K

R114

R114

R115

R115

R113

R113

10K

10K

10K

10K

10K

10K

R116

R116

R120

R120

R117

R117

R118

R118

R119

R119

10K

10K

10K

10K

10K

10K

10K

10K

10K

10K

ETH1_PC7 [7]

ETH1_PC1 [7]

ETH1_PC0 [7]

ETH1_PC4 [7]

ETH1_PC3 [7]

ETH1_PC2 [7]

ETH1_PC5 [7]

ETH1_PC6 [7]

ETH1_PC8 [7]

ETH1_PC9 [7]

PB12 [7]

Figure 4-14: LED Indicators Schematic

R32

PE[0..31][4,7,8,11]

PE23

PE24

1

Q2

Q2

IRLML2502

IRLML2502

R32

R33 100K 1%R33 100K 1%

32

470R

470R

R34

R34

470R

470R

2019 Microchip Technology Inc. DS50002884A-page 17

D2

BLUED2BLUE

D3

REDD3RED

3V3

LED

Page 18

SAMA5D3 XPLAINED

HHSDPC

HHSDMA

HHSDPA

HHSDMB

HHSDPB

HHSDMC

HHSDMC

HHSDPC

HHSDMB

HHSDPB

5V_USBB

5V_USBC

5V_USBB

5V_USBC

GNDUTMI

GNDUTMI

EARTH_USB

5V_MAIN

EARTH_USB

EARTH_USB_A

PE5 [7]

Vbus[4]

PE9

[7,11]

PE4 [7]

PE3 [7]

OVCUR_USB

USB A DEVICE INTERFACE

(VBUS_SENSE)

J7_USB_A_Up J7_USB_B_Down

EN5V_USBC

EN5V_USBB

C60

10pF

C60

10pF

32.768K

R27

200K

R27

200K

20pF20pF

p

p

MN3

SP2526A-2E

MN3

SP2526A-2E

ENA

1

FLGA

2

ENB

4

OUTA

8

GNG6FLGB

3

IN

7

OUTB

5

J6

UBAF-1015P

J6

UBAF-1015P

MN2H

SAMA5D3x_BGA324

MN2H

SAMA5D3x_BGA324

GNDCORE_1

A

A

GNDCORE_2

GNDIODDR_1

GNDIODDR_2

GNDIODDR_3

GNDIODDR_4

GNDIODDR_5

GNDIOP_1

GNDIOM_1

GNDANA

L4

ADVREF

VDDANA

GNDIOP_2

GNDCORE_3

GNDFUSE

GNDPLL

GNDUTMI_1

R12

VDDPLLA

VBG

R11

GNDCORE_4

GNDOSC

GNDBU

GNDCORE_5

GNDIOM_2

GNDIOP_3

VDDOSC

VDDUTMII

XIN32

U16

XOUT

V8

VDDUTMIC

XOUT32

V16

GNDCORE_6

GNDIOP_4

HHSDMA

V10

HHSDPA

U10

HHSDMC

V14

HHSDPC

U14

HHSDPB

U12

HHSDMB

V12

DIBN

U6

DIBP

V6

C61

100nF

C61

100nF

L21 180ohm at 100MHzL21 180ohm at 100MHz

1

2

20

20pF

12MHz

C64

100nF

C64

100nF

R30

5.62K 1%

R30

5.62K 1%

L13

180ohm at 100MHz

L13

180ohm at 100MHz

1 2

C62

10uF

C62

10uF

C63

100nF

C63

100nF

L15

180ohm at 100MHz

L15

180ohm at 100MHz

1 2

A

B

J7

Dual USB A

A

B

J7

Dual USB A

5

8

6

7

9

10

1

2

3

4

11

12

R31 0RR31 0R

20pF20pF

p

p

L14

180ohm at 100MHz

L14

180ohm at 100MHz

1 2

C65

10uF

C65

10uF

R26 100K 1%R26 100K 1%

EARTH_USB_A

VBUS

DM

DP

ID

GND

VBUS

DM

DP

ID

GND

1

2

3

4

5

76

8

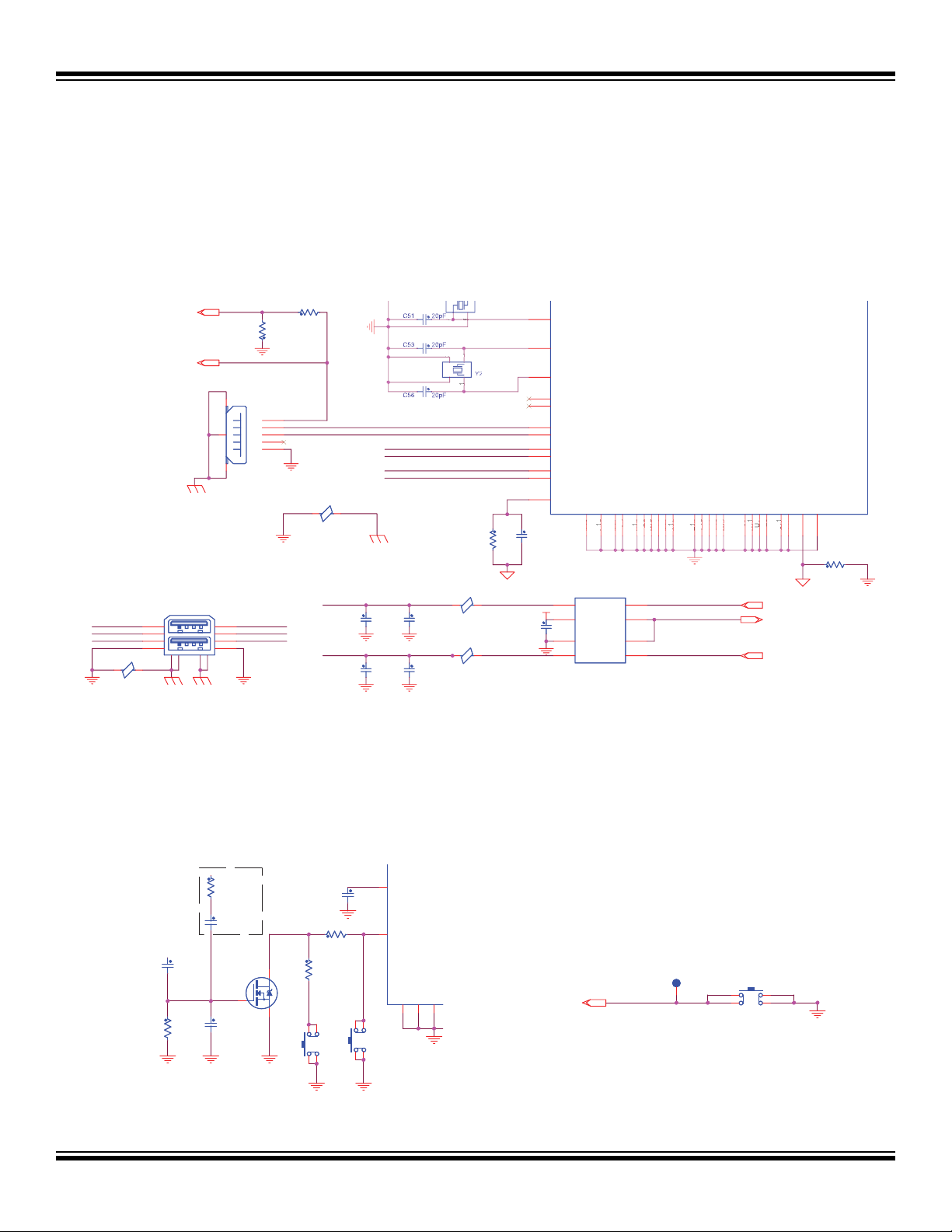

4.2.12 USB

The SAMA5D3 Xplained board features three USB communication ports:

• Port A: High-speed (EHCI) and full-speed (OHCI) host multiplexed with high-speed USB device Micro-AB connector (J6)

• Port B: High-speed (EHCI) and full-speed (OHCI) host, standard type A connector (J7 upper port)

• Port C: Full-speed OHCI host, standard type A connector (J7 lower port)

The two USB host ports are equipped with 500-mA high-side power switch for self-powered and bus-powered applications.

The USB device port A (J6) features a VBUS insert detection function through the ladder-type resistors R26 and R27.

Figure 4-15: USB Interface Schematic

Y

pF

4.2.13 Push Button Switches

The following push button switches are available:

• One board reset button (BP2). When pressed and released, this push button causes a Power-on Reset of the whole board.

• One wake-up push button that brings the processor out of Low-Power mode (BP1)

• One user push button (BP3)

Figure 4-16: Push Button Schematic

C25

C25

100nF

100nF

R19

R19

C130

C130

10nF

100K 1%

100K 1%

WAKUP or Force Power ON

DS50002884A-page 18 2019 Microchip Technology Inc.

10nF

R14

R14

50K

50K

C20

C20

100nF

100nF

IRLML2502

IRLML2502

Auto

PWRON

(option)

Q1

Q1

3

1

2

R12 49.9K

R150RR15

0R

BP1

BP1BP1

C18

C18

47nF

47nF

BP2

BP2BP2

32

REFBP

9

nPBIN

RESET

GNDP129GNDA2GNDP2

28

TP5

TP5

SMD

SMD

[7,11]

PE29

Place TP5 to Bottom

USER BUTTON

BP3BP3

Page 19

SAMA5D3 XPLAINED

4.2.14 LCD

The SAMA5D36 processor drives 24 bits of Data and Control signals to the LCD interface. Other signals are used to control the LCD and

are also routed to the J22 connector: TWI, SPI, 2 GPIOs for interrupt, ID for 1-Wire EEPROM (ID_SYS) and power supply lines.

4.2.14.1 LCD Connector

One 1.27 mm pitch 50-pin header is provided to gain access to the LCD signals.

Figure 4-17: LCD Expansion Header Interface Schematic

3V3

5V_MAIN

DNP(0R)

DNP(0R)

R92

R92

See

Errata section

NRST

PE6

PD20

PD12

PD21

PD11

PD22

PD10

PD23

PD16

PA28

TWCK_LCD[7]

TWD_LCD[7]

(RST_LCD)

(AD0)

(SPI0_SPCK)

(AD1)

(SPI0_MOSI)

(AD2)

(SPI0_MISO)

(AD3)

(SPI0_NPCS3)

(LCDPCK)

R93 0RR93 0R

R94 0RR94 0R

R99 DNP(0R)R99 DNP(0R)

R95 DNP(0R)R95 DNP(0R)

R96 22RR96 22R

DNP(0R)

DNP(0R)

R100

R100

R97 22RR97 22R

R98

R98

DNP(0R)

DNP(0R)

R101 22RR101 22R

DNP(0R)

DNP(0R)

R102

R102

R103 22RR103 22R

R184 22RR184 22R

TWCK_LCD

TWD_LCD

LCD Connector

(LCDPWM)

PA24

(IRQ2)

PE8

IRQ1)

PE7

TWCK_LCD

TWD_LCD

(LCDDISP)

PA25

(LCDDEN)

PA29

PA27

(LCDHSYNC)

(LCDVSYNC)

PA26

(LCDDAT23)

PE28

(LCDDAT22)

PE27

(LCDDAT21)

PC15

(LCDDAT20)

PC10

(LCDDAT19)

PC11

(LCDDAT18)

PC12

(LCDDAT17)

PC13

(LCDDAT16)

PC14

(LCDDAT15)

PA15

(LCDDAT14)

PA14

(LCDDAT13)

PA13

(LCDDAT12)

PA12

PA11

(LCDDAT11)

PA10

(LCDDAT10)

PA9

(LCDDAT9)

PA8

(LCDDAT8)

PA7

(LCDDAT7)

PA6

(LCDDAT6)

PA5

(LCDDAT5)

PA4

(LCDDAT4)

PA3

(LCDDAT3)

PA2

(LCDDAT2)

(LCDDAT1)

PA1

(LCDDAT0)

PA0

PE23

(ID_SYS)

J22J22

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

FP520T1-50SR04

52

51

4.2.14.2 LCD Power

To operate correctly with various LCD modules, regardless of the processor, two voltage lines are available: 3V3 by default and 5V_MAIN,

both selected by 0R resistors R92 and R93.

4.2.15 Debug JTAG/ICE and DBGU

4.2.15.1 Debug JTAG/ICE

A 2x10-pin JTAG header is implemented on the SAMA5D3 Xplained board to enable the software development and debugging of the

board by using various JTAG emulators. The interface signals have a voltage level of 3.3V.

2019 Microchip Technology Inc. DS50002884A-page 19

Page 20

SAMA5D3 XPLAINED

Figure 4-18: JTAG/ICE Interface Schematic

JTAG

3V3

J24J24

2

6

8

10

12

14

16

18

20

R104

R104

100K 1%

100K 1%

1

34

TDI

5

TMS

7

TCK

9

11

13

15

17

19

RTCK

TDO

R109 0RR109 0R

R110 0RR110 0R

R105

R105

100K 1%

100K 1%

VDDIOP0

R106

R106

100K 1%

100K 1%

R107

R107

100K 1%

100K 1%

R108 0RR108 0R

NTRST [5]

TDI [5]

TMS [5]

TCK [5]

TDO [5]

NRST [4,5,9,10]

4.2.15.2 DBGU

The SAMA5D3 Xplained board has a dedicated serial port for debugging, which is accessible through the 6-pin male header J23. Various

interfaces can be used as USB/Serial DBGU port bridge, such as FTDI TTL-232R-3V3 USB to TTL serial cable or basic breakout board

for the 232/USB converter.

These interfaces are available on the following websites:

• Adafruit: http://www.adafruit.com/products/284

•Sparkfun: https://www.sparkfun.com/products/9873

Figure 4-19: DBGU Interface Schematic

5V_MAIN

3V33V3

R189

R190

R171DNP(0R)

R172DNP(0R)

68K

68K

PE13

[7]

PB31

[7]

PB30

PE14

R173 0R

(TXD)

(RXD)

R174 0R

J23

1

2

3

4

5

6

DEBUG

P101-1*06SGF-116A-NX

R171 and R172 are optional (not implemented) resistors that can be used for power selection. Power can be delivered either by the

SAMA5D3 Xplained board or by the debug interface tool. To avoid a contention between your debug interface (e.g. FTDI) and the onboard power system, be careful during the installation of one of these resistors.

4.2.16 Expansion Ports

Five 8-pin, one 10-pin, one 6-pin and one 2x18-pin headers (J14 to J21) are implemented on the board to enable the PIO connection of

various expansion cards that could be developed by users or by other sources. Due to multiplexing, different signals can be provided on

each pin. These connectors are mechanically- and footprint- compatible with the Arduino R3 shields. As the SAMA5D3 signals have a

voltage level of 3.3V, 5-V level shields must not be used on the SAMA5D3 Xplained.

In addition to its standard IO functionality, the SAMA5D3 processor can provide alternate functions to external IO lines available on the

J14 to J21 headers.

These alternate functions are:

• UARTs: UART0, UART1

• USARTs: USART0, USART1, USART2, USART3

• SPI: SPI1

DS50002884A-page 20 2019 Microchip Technology Inc.

Page 21

SAMA5D3 XPLAINED

• I²C: TWI0, TWI1

• Timer capture and compare: TIOA, TIOB

• Clock out: PCK0, PCK1, PCK2

• PWMs: PWML0, PWMH0, PWML1, PWMH1

• DIGITAL AUDIO: TD0, TK0, TF0, RD0, RK0, RF0

• ISI: ISI[D0:D11], ISI_HSYNC, ISI_VSYNC, ISI_PCK

• CAN: CAN-RX0, CANTX0, CANRX1, CAN_TX1

• Analog: AD[0:11], ADTRG, ADREF

• GPIO: MISC

• RESET

• VBAT

Refer to the SAMA5D3 series data sheet for further details on the PIO multiplexing and alternate function selection.

2019 Microchip Technology Inc. DS50002884A-page 21

Page 22

SAMA5D3 XPLAINED

4.2.16.1 Functions Available Through the Arduino Headers

The following tables illustrate the functionalities provided by the SAMA5D3 Xplained board. They show the pins used to implement each

functionality.

Note: Some pins are multiplexed for different functionalities, which means that only one at a time can be active for each pin.

Table 4-5: Function by PIO (Part 1)

PIO NAME PCK ISI SSC CAN SPI

PC16 -- -- TK0 -- --

PC17 -- -- TF0 -- --

PC18 -- -- TD0 -- --

PC20/PD28 -- -- RF0 -- --

PC21/PD29 -- -- RD0 -- --

PC19/PD30 PCK0 -- RK0 -- --

PD30/PC15 PCK0/PCK2 -- -- -- --

PD31 PCK1 -- -- -- --

PB14------CANRX1--

PD14 -- -- -- CANRX0 --

PB15 -- -- -- CANTX1 --

PD15 -- -- -- CANTX0 --

PC22/PC1 -- -- -- -- SPI1_MISO

PC24/PC0 -- -- -- -- SPI1_SPCK

PC23/PC2 -- -- -- -- SPI1_MOSI

PC25 -- -- -- -- SPI1_NPCS0

PC26/PA30 -- ISI_D11/VSYNC -- -- SPI1_NPCS1

PC27/PA31 -- ISI_D10/HSYNC -- -- SPI1_NPCS2

PC28 -- ISI_D9 -- -- SPI1_NPCS3

PC29 -- ISI_D8 -- -- --

PA23 -- ISI_D7 -- -- --

PA22 -- ISI_D6 -- -- --

PA21 -- ISI_D5 -- -- --

PA20 -- ISI_D4 -- -- --

PA19 -- ISI_D3 -- -- --

PA18 -- ISI_D2 -- -- --

PA17 -- ISI_D1 -- -- --

PA16 -- ISI_D0 -- -- --

PC30 -- ISI_PCK -- -- --

PA30 -- ISI_VSYNC -- -- --

PA31 -- ISI_HSYNC -- -- --

DS50002884A-page 22 2019 Microchip Technology Inc.

Page 23

SAMA5D3 XPLAINED

Table 4-6: Function by PIO (Part 2)

PIO NAME TWI UART/USART ANALOG MISC

3V3/5V -- -- -- 3V3/5V

nRTS -- -- -- nRTS

GND ------GND

AREF -- -- AREF --

5V -- -- -- 5V

PC18 -- -- AD0 --

PD21 -- -- AD1 --

PD22 -- -- AD2 --

PD23 -- -- AD3 --

PD24 -- -- AD4 --

PD25 -- -- AD5 --

PD26 -- -- AD6 --

PD27 -- -- AD7 --

PC20/PD28 -- -- AD8 --

PC21/PD29 -- -- AD9 --

PC19/PD30 -- -- AD10 --

PD31 -- -- AD11 --

PD19/PB15 -- -- ADTRG --

PA1 9 TWC K2 - - -- --

PA18 TWD2 -- -- --

PC26 TWD1 -- -- --

PA30 TWD0 URXD1 -- --

PA31 TWCK0 UTXD1 -- --

PC26/PA30 TWD0/TWD1 URXD1 -- --

PC27/PA31 TWCK0/TWCK1 URTD1 -- --

PC30 -- UTXD0 -- --

PC29 -- URXD0 -- PWMFI2

PD14 -- SCK0 -- --

PD15 -- CTS0 -- --

PD18 -- TXD0 -- --

PD17 -- RXD0 -- --

PB25 -- SCK1 -- --

PB26 -- CTS1 -- --

PB29 -- TXD1 -- --

PB28 -- RXD1 -- --

2019 Microchip Technology Inc. DS50002884A-page 23

Page 24

SAMA5D3 XPLAINED

Table 4-6: Function by PIO (Part 2) (Continued)

PIO NAME TWI UART/USART ANALOG MISC

PB27 -- RTS1 -- PWMH1

PE20 -- SCK2 -- --

PE23 -- CTS2 -- --

PE26 -- TXD2 -- --

PE25 -- RXD2 -- --

PE24 -- RTS2 -- --

PE15 -- SCK3 -- --

PE16 -- CTS3 -- --

PE19 -- TXD3 -- --

PE18 -- RXD3 -- --

PE17 -- RTS3 -- --

PC22/PC1 -- -- -- GPIO

PC23/PC2 -- -- -- GPIO

PC24/PC0 -- -- -- GPIO

PC9 ------GPIO

PE9 -- -- -- GPIO

PE10 -- -- -- GPIO

PE11 -- -- -- GPIO

PE12 -- -- -- GPIO

PE16 -- -- -- GPIO

PE31 ------IRQ/PWML1

PC28 -- -- -- PWMFI0

PA20 -- -- -- PWMH0

PA22 -- -- -- PWMH1

PA21 -- -- -- PWML0

PA23 -- -- -- PWML1

PE29 -- -- -- TCLK2

PC5 ------TCLK4

PC8 ------TCLK5

PC3 ------TIOA4

PC6 ------TIOA5

PC4 ------TIOB4

PC7 ------TIOB5

DS50002884A-page 24 2019 Microchip Technology Inc.

Page 25

4.2.16.2 J15 Header

Figure 4-20: J15 Header

SAMA5D3 XPLAINED

Table 4-7: J15 Header IOs

Silkscreen PIO Function 1 Function 2 Function 3 PIO Function 4 Function 5

SCL0 PA31 TWCK0 UTXD1 ISI_HSYNC -- -- --

SDA0 PA30 TWD0 URXD1 ISI_VSYNC -- -- --

ARFE -- -- -- -- -- -- --

GND--------------

13 PC24 SPI1_SPCK -- -- PC0 ETX0 TIOA3

12 PC22 SPI1_MISO -- -- PC1 ETX1 TIOB3

11 PC23 SPI1_MOSI -- -- PC2 ERX0 TCLK3

10 PC25 SPI1_NPCS0 -- -- -- -- --

9 PC3 ERX1 TIOA4 -- -- -- --

8 PC4 ETXEN TIOB4 -- -- -- --

2019 Microchip Technology Inc. DS50002884A-page 25

Page 26

SAMA5D3 XPLAINED

4.2.16.3 J18 Header

Figure 4-21: J18 Header

Table 4-8: J18 Header IOs

Silkscreen PIO Function 1 Function 2 Function 3

7 PC5 ECRSDV TCLK4 --

6 PC6 ERXER TIOA5 --

5 PC7 EREFCK TIOB5 --

4 PC28 SPI1_NPCS3 PWMFI0 ISI_D9

3 PC8 EMDC TCLK5 --

2 PC9 EMDIO -- --

1 PC30 UTXD0 ISI_PCK --

0 PC29 URXD0 PWMFI2 ISI_D8

DS50002884A-page 26 2019 Microchip Technology Inc.

Page 27

4.2.16.4 J20 Header

Figure 4-22: J20 Header

SAMA5D3 XPLAINED

Table 4-9: J20 Header IOs

Silkscreen PIO Function 1 Function 2 Function 3 PIO Function 4 Function 5 Function 6

TXD3 14 PE19 A19 TXD3 -- -- -- -- --

RXD3 15 PE18 A18 RXD3 -- -- -- -- --

TXD1 16 PB29 TXD1 -- -- -- -- -- --

RXD1 17 PB28 RXD1 -- -- -- -- -- --

TXD0 18 PD18 TXD0 -- -- -- -- -- --

RXD0 19 PD17 RXD0 -- -- -- -- -- --

SDA 20 PC26 SPI1_NPCS1 TXWD1 ISI_D11 PA30 TWD0 URXD1 ISI_VSYNC

SCL 21 PC27 SPI1_NPCS2 TWCK1 ISI_D10 PA31 TWCK0 UTXD1 ISI_HSYNC

2019 Microchip Technology Inc. DS50002884A-page 27

Page 28

SAMA5D3 XPLAINED

4.2.16.5 J19 Header

Figure 4-23: J19 Header

Table 4-10: J19 Header IOs

Silkscreen PIO Function 1 Function 2 Function 3 PIO Function 4 Function 5

PD30 PD30 AD10 PCK0 -- PC15 PCI2_CK PCK2

PC17 PC17 TF0 -- -- -- -- --

PB26 PB26 CTS1 GRX7 -- -- -- --

PE9 PE9 A9 -- -- -- -- --

PA17 PA17 LCDDAT17 ISI_D1 -- -- -- --

PA19 PA19 LCDDAT19 TWCk2 ISI_D3 -- -- --

PA21 PA21 LCDDAT21 PWML0 ISI_D5 -- -- --

PA23 PA23 LCDDAT23 PWML1 ISI_D7 -- -- --

PE15 PE15 A15 SCK3 -- -- -- --

PE17 PE17 A17 RTS3 -- -- -- --

PE11 PE11 A11 -- -- -- -- --

PE23 PE23 A23 CTS2 -- -- -- --

PE25 PE25 A25 RXD2 -- -- -- --

DS50002884A-page 28 2019 Microchip Technology Inc.

Page 29

SAMA5D3 XPLAINED

Table 4-10: J19 Header IOs (Continued)

Silkscreen PIO Function 1 Function 2 Function 3 PIO Function 4 Function 5

PE13 PE13 A13 -- -- -- -- --

PE29 PE29 NWR1/NBS1 TCLK2 -- -- -- --

PC26 PC26 SPI1_NPCS1 TXWD1 ISI_D11 -- -- --

PC16 PC16 TK0 -- -- -- -- --

PB25 PB25 SCK1 GRX6 -- -- -- --

PB27 PB27 RTS1 PWMH1 -- -- -- --

PE10 PE10 A10 -- -- -- -- --

PA16 PA16 LCDDAT16 ISI_D0 -- -- -- --

PA18 PA18 LCDDAT18 TWD2 ISI_D2 -- -- --

PA20 PA20 LCDDAT20 PWMH0 ISI_D4 -- -- --

PA22 PA22 LCDDAT22 PWMH1 ISI_D6 -- -- --

PE16 PE16 A16 CTS3 -- -- -- --

PE20 PE20 A20 SCK2 -- -- -- --

PE12 PE12 A12 -- -- -- -- --

PE24 PE24 A24 RTS2 -- -- -- --

PE26 PE26 NCS0 TXD2 -- -- -- --

PE14 PE14 A14 -- -- -- -- --

PE31 PE31 IRQ PWML1 -- -- -- --

PB15 PB15 GCOL CANTX1 -- -- -- --

2019 Microchip Technology Inc. DS50002884A-page 29

Page 30

SAMA5D3 XPLAINED

4.2.16.6 J16 Header

Figure 4-24: J16 Header

Table 4-11: J16 Header IOs

Silkscreen PIO Function 1

MISO1 PC22 SPI1_MISO

5V/3V3 -- Power supply

SPCK PC24 SPI1_SPCK

MOSI1 PC23 SPI1_MOSI

RST NRST System reset

GND -- Power ground

DS50002884A-page 30 2019 Microchip Technology Inc.

Page 31

4.2.16.7 J14 Header

Figure 4-25: J14 Header Position

SAMA5D3 XPLAINED

Table 4-12: J14 Header IOs

Silkscreen Function

VBAT VBAT supply

3V3 AREF. Reference voltage for the analog inputs of the SAMA5D36 processor.

RST System reset

Main 3.3V supply - generated by the on-board regulator. Maximum sourced current is

3V3

5V Main 5.0V supply

GND System ground

GND System ground

NC Not connected

1.2A. This regulator also provides the power supply to the SAMA5D36 microcontroller

and components.

2019 Microchip Technology Inc. DS50002884A-page 31

Page 32

SAMA5D3 XPLAINED

4.2.16.8 J17 Header

Figure 4-26: J17 Header

Table 4-13: J17 Header IOs

Silkscreen PIO Function 1 Function 2 Function 3 PIO Function 4 Function 5

A0 PC18 TD0 -- -- PD20 AD0 --

A1 PD21 AD1 -- -- -- -- --

A2 PD22 AD2 -- -- -- -- --

A3 PD23 AD3 -- -- -- -- --

A4 PD24 AD4 -- -- -- -- --

A5 PD25 AD5 -- -- -- -- --

A6 PD26 AD6 -- -- -- -- --

A7 PD27 AD7 -- -- -- -- --

DS50002884A-page 32 2019 Microchip Technology Inc.

Page 33

4.2.16.9 J21 Header

Figure 4-27: J21 Header

SAMA5D3 XPLAINED

Table 4-14: J21 Header IO

Silkscreen PIO Function 1 Function 2 Function 3 PIO Function 4 Function 5

A8 PC20 RF0 -- -- PD28 AD8 --

A9 PC21 RD0 -- -- PD29 AD9 --

A10 PC19 RK0 -- -- PD30 AD10 PCK0

A11 PD31 PCK1 -- -- -- -- --

** PB14 GCRS CANRX1 -- -- -- --

** PD19 ADTRG -- -- PB15 GCOL CANTX1

CANRX0 PD14 SCK0 SPO_NPCS1 CANRX0 -- -- --

CANTX0 PD15 CTS0 SPI0_NPCS2 CANTX0 -- -- --

2019 Microchip Technology Inc. DS50002884A-page 33

Page 34

SAMA5D3 XPLAINED

1 3 5 7 9 11 13 15 17 19

2 4 6 8 10 12 14 16 18 20

4.3 Other Connector Details and PIO Usage Summary

4.3.1 Power Supply

Figure 4-28: Power Supply Connector J2 (Optional)

Table 4-15: Power Supply Connector J2 Signal Description

Pin Mnemonic Signal Description

1 Center +5V

2-- GND

3 -- Floating

4.3.2 JTAG/ICE Connector

Figure 4-29: JTAG Port J24

Table 4-16: JTAG/ICE Connector J24 Signal Descriptions

Pin Mnemonic Signal Description

This is the target reference voltage. It is used to check if the target has

1VT

2V

ref 3.3V power

supply 3.3V power

power, to create the logic-level reference for the input comparators and

to control the output logic levels to the target. It is normally fed from VDD

on the target board and must not have a series resistor.

This pin is not connected in SAM-ICE

with other equipment. Connect to VDD or leave open in target system.

™

. It is reserved for compatibility

JTAG Reset. Output from SAM-ICE to the Reset signal on the target

3

4 GND Common ground.

nTRST Target Reset - Active-low

Output signal that resets the target.

JTAG port. Typically connected to nTRST on the target CPU. This pin is

normally pulled high on the target to avoid unintentional resets when

there is no connection.

DS50002884A-page 34 2019 Microchip Technology Inc.

Page 35

Table 4-16: JTAG/ICE Connector J24 Signal Descriptions (Continued)

Pin Mnemonic Signal Description

TDI Test Data Input - Serial data

5

6 GND Common ground.

7 TMS Test Mode Select.

8 GND Common ground.

9

10 GND Common ground.

11

output line, sampled on the rising

edge of the TCK signal.

TCK Test Clock - Output Timing

signal, for synchronizing test logic

and control register access.

RTCK - Input Return Test Clock

signal from the target.

JTAG data input of target CPU. It is recommended that this pin is pulled

to a defined state on the target board. Typically connected to TDI on

target CPU.

JTAG mode set input of target CPU. This pin should be pulled up on the

target. Typically connected to TMS on target CPU. Output signal that

sequences the target's JTAG state machine, sampled on the rising edge

of the TCK signal.

JTAG Clock signal to target CPU. It is recommended that this pin is

pulled to a defined state on the target board. Typically connected to TCK

on target CPU.

Some targets must synchronize the JTAG inputs to internal clocks. To

fulfill this requirement, a returned and resynchronized TCK can be used

to dynamically control the TCK rate. SAM-ICE supports adaptive

clocking which waits for TCK changes to be echoed correctly before

making further changes. Connect to RTCK if available, otherwise to

GND.

SAMA5D3 XPLAINED

12 GND Common ground.

13

14 GND Common ground

15 nSRST RESET Active-Low Reset signal. Target CPU Reset signal.

16 GND Common ground

17 RFU This pin is not connected.

18 GND Common ground

19 RFU This pin is not connected.

20 GND Common ground

TDO JTAG Test Data Output Serial data input from the target.

JTAG data output from target CPU. Typically connected to TDO on target

CPU.

4.3.3 USB Type-A Dual Port

Figure 4-30: USB Type-A Dual Port J19

2019 Microchip Technology Inc. DS50002884A-page 35

Page 36

SAMA5D3 XPLAINED

-

Table 4-17: USB Type-A Dual Port J19 Signal Descriptions

Pin Mnemonic Signal Description

A1 Vbus - USB_A 5V power

A2 DM - USB_A Data minus

A3 DP - USB_A Data plus

A4 GND Common ground

B1 Vbus - USB_A 5V power

B2 DM - USB_A Data minus

B3 DP - USB_A Data plus

B4 GND Common ground

Mechanical

pins

4.3.4 USB Micro-AB

-- Shield

Figure 4-31: USB Host/Device Micro-AB Connector J6

12345

Table 4-18: USB Device Micro-AB Connector J6 Signal Descriptions

Pin Mnemonic Signal Description

1 Vbus 5V power

2 DM Data minus

3 DP Data plus

4 ID On-the-go identification

5 GND Common ground

DS50002884A-page 36 2019 Microchip Technology Inc.

Page 37

4.3.5 DEBUG Connector

Figure 4-32: DEBUG Connector J23

Table 4-19: DEBUG Connector J23 Signal Descriptions

Pin Mnemonic PIO Signal Description

1 -- PE13 --

2 TXD (transmitted data) PB31 RS232 Serial Data Input signal

3 RXD (transmitted data) PB30 RS232 Serial Data Output signal

4 -- -- Power line (5V/3V3)

5 -- PE14 --

6 GND -- Common ground

SAMA5D3 XPLAINED

4.3.6 SD/MMC Plus MCI0

Figure 4-33: SD/MMC Socket J10

Table 4-20: SD/MMC Socket J10 Signal Descriptions

Pin Mnemonic PIO Signal Description

1 DAT3 PD4 Data bit

2 CMD PD0 Command line

3 VSS -- Command line

4 VCC -- Supply voltage 3.3V

5 CLK PD9 Clock / command line

6 CD PE0 Card detect

7 DAT0 PD1 Data bit

8 DAT1 PD2 Data bit

9 DAT2 PD3 Data bit

10 DAT4 PD5 Data bit

11 DAT5 PD6 Data bit

12 DAT6 PD7 Data bit

13 DAT7 PD8 Data bit

2019 Microchip Technology Inc. DS50002884A-page 37

Page 38

SAMA5D3 XPLAINED

Table 4-20: SD/MMC Socket J10 Signal Descriptions

Pin Mnemonic PIO Signal Description

14 WP R57 Protect

15 VSS -- Common ground

16 VSS -- Common ground

4.3.7 MicroSD MCI1

Figure 4-34: MicroSD Socket J11

Table 4-21: MicroSD Socket J11 Signal Descriptions

Pin Mnemonic PIO Signal Description

1 DAT2 PB22 Data bit 2

2 CD/DAT3 PB23 Card detect / data bit 3

3 CMD PB19 Command line

4 VCC -- Supply voltage 3.3V

5 CLK PB24 Clock / command line

6 VSS -- Common ground

7 DAT0 PB20 Data bit 0

8 DAT1 PB21 Data bit 1

9 SW1 -- Not used, grounded

10 CARD DETECT PE1 Card detect

4.3.8 Gigabit Ethernet ETH0 RJ45 Socket J12

Figure 4-35: Gigabit Ethernet RJ45 Socket J12

1 2 3 4 5 6 7 8

RJ-45

DS50002884A-page 38 2019 Microchip Technology Inc.

Page 39

4.3.9 Ethernet ETH1 RJ45 Socket J13

Figure 4-36: Ethernet RJ45 Socket J13

4.3.10 LCD Socket J22

Figure 4-37: LCD Socket J22

SAMA5D3 XPLAINED

1 2 3 4 5 6 7 8

RJ-45

Table 4-22: LCD Socket J22 Signal Descriptions

PIN Signal Display Module Interface Function MCU Interface Function

Extension module identification (connected

1 ID_SYS

2 GND GND GND

3 D0 Data line Data line

4 D1 Data line Data line

5 D2 Data line Data line

6 D3 Data line Data line

7 GND GND GND

8 D4 Data line Data line

9 D5 Data line Data line

10 D6 Data line Data line

11 D7 Data line Data line

12 GND GND GND

13 D8 Data line Data line

14 D9 Data line Data line

to 1-wire EEPROM available on LCD display

module)

Extension module identification

15 D10 Data line Data line

16 D11 Data line Data line

17 GND GND GND

18 D12 Data line Data line

2019 Microchip Technology Inc. DS50002884A-page 39

Page 40

SAMA5D3 XPLAINED

Table 4-22: LCD Socket J22 Signal Descriptions (Continued)

PIN Signal Display Module Interface Function MCU Interface Function

19 D13 Data line Data line

20 D14 Data line Data line

21 D15 Data line Data line

22 GND GND GND

23 D16 Data line Data line

24 D17 Data line Data line

25 D18 Data line Data line

26 D19 Data line Data line

27 GND GND GND

28 D20 Data line Data line

29 D21 Data line Data line

30 D22 Data line Data line

31 D23 Data line Data line

32 GND GND GND

33 PCLK Pixel clock --

34 VSYNC/CS Vertical sync Chip select

35 HSYNC/WE Horizontal sync Write enable

36

37

38

39

40

(1)

(1)

(1)

(1)

DATA_ENABLE/

RE

SPI_SCK

SPI_MOSI

SPI_MISO

SPI_CS

(1)

(1)

(1)

(1)

Data enable Read enable

-- SPI_SCK

(1)

-- SPI_MOSI

-- SPI_MISO

-- SPI_CS

(1)

(1)

(1)

41 ENABLE Display Enable signal Display Enable signal

®

42 TWI_SDA I2C data line (maXTouch

) I2C data line (maXTouch)

43 TWI_SCL I2C clock line (maXTouch) I2C clock line (maXTouch)

44 IRQ1 maXTouch interrupt line maXTouch interrupt line

45 IRQ2 Interrupt line for other I2C devices Interrupt line for other I2C devices

46 PWM Backlight control Backlight control

47 RESET Reset for both display and maXTouch Reset for both display and maXTouch

48 VCC 3.3V or 5V supply (0R) 3.3V supply

49 VCC 3.3V or 5V supply (0R) 3.3V supply

50 GND GND GND

Note 1: See Section 5. “Errata”.

DS50002884A-page 40 2019 Microchip Technology Inc.

Page 41

SAMA5D3 XPLAINED

4.3.11 PIO Usage

Most signals can also be configured as simple inputs or outputs from the processor.

Table 4-23: PIO A Pin Assignment and Signal Description

Power Rail PIO Signal Signal Signal Main Board Function Extended Function

VDDIOP0 PA0 LCDDAT0 – – – LCDDAT0

VDDIOP0 PA1 LCDDAT1 – – – LCDDAT1

VDDIOP0 PA2 LCDDAT2 – – – LCDDAT2

VDDIOP0 PA3 LCDDAT3 – – – LCDDAT3

VDDIOP0 PA4 LCDDAT4 – – – LCDDAT4

VDDIOP0 PA5 LCDDAT5 – – – LCDDAT5

VDDIOP0 PA6 LCDDAT6 – – – LCDDAT6

VDDIOP0 PA7 LCDDAT7 – – – LCDDAT7

VDDIOP0 PA8 LCDDAT8 – – – LCDDAT8

VDDIOP0 PA9 LCDDAT9 – – – LCDDAT9

VDDIOP0 PA10 LCDDAT10 – – – LCDDAT10

VDDIOP0 PA11 LCDDAT11 – – – LCDDAT11

VDDIOP0 PA12 LCDDAT12 – – – LCDDAT12

VDDIOP0 PA13 LCDDAT13 – – – LCDDAT13

VDDIOP0 PA14 LCDDAT14 – – – LCDDAT14

VDDIOP0 PA15 LCDDAT15 – – – LCDDAT15

VDDIOP0 PA16 LCDDAT16 ISI_D0 – – ISI_D0

VDDIOP0 PA17 LCDDAT17 ISI_D1 – – ISI_D1

VDDIOP0 PA18 LCDDAT18 TWD2 ISI_D2 – TWD2/ISI_D2

VDDIOP0 PA19 LCDDAT19 TWCK2 ISI_D3 – TWCK2/ISI_D3

VDDIOP0 PA20 LCDDAT20 PWMH0 ISI_D4 – ISI_D4

VDDIOP0 PA21 LCDDAT21 PWML0 ISI_D5 – ISI_D5

VDDIOP0 PA22 LCDDAT22 PWMH1 ISI_D6 – ISI_D6

VDDIOP0 PA23 LCDDAT23 PWML1 ISI_D7 – ISI_D7

VDDIOP0 PA24 LCDPWM – – – LCDPWM