Page 1

KSZ8061MNX

Evaluation Board

User’s Guide

2016 Microchip Technology Inc. DS50002449A

Page 2

Note the following details of the code protection feature on Microchip devices:

YSTEM

CERTIFIED BY DNV

== ISO/TS 16949 ==

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device

applications and t he lik e is provided only for your convenience

and may be su perseded by upda t es . It is y our responsibility to

ensure that your application meets with your specifications.

MICROCHIP MAKES NO REPRESENTATIONS OR

WARRANTIES OF ANY KIND WHETHER EXPRESS OR

IMPLIED, WRITTEN OR ORAL, STATUTORY OR

OTHERWISE, RELATED TO THE INFORMATION,

INCLUDING BUT NOT LIMITED TO ITS CONDITION,

QUALITY, PERFORMANCE, MERCHANTABILITY OR

FITNESS FOR PURPOSE. Microchip disclaims all liability

arising from this information and its use. Use of Microchip

devices in life supp ort and/or safety ap plications is entir ely at

the buyer’s risk, and the buyer agrees to defend, indemnify and

hold harmless M icrochip from any and all dama ges, claims,

suits, or expenses re sulting from such use. No licens es are

conveyed, implicitly or otherwise, under any Microchip

intellectual property rights unless otherwise stated.

Trademarks

The Microchip name and logo, the Microchip logo, dsPIC,

FlashFlex, flexPWR, JukeBlox, K

LANCheck, MediaLB, MOST, MOST logo, MPLAB,

OptoLyzer , PIC, PICSTART, PIC

SST, SST Logo, SuperFlash and UNI/O are registered

trademarks of Microchip Technology Incorporated in the

U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are

registered trademarks of Microchip Technology Incorporated

in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo,

CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit

Serial Programming, ICSP , Inter-Chip Connectivity, KleerNet,

KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB

Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach,

Omniscient Code Generation, PICDEM, PICDEM.net, PICkit,

PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O,

Total Enduranc e, TSHARC , USBC heck, VariSense,

ViewSpan, WiperLock, Wireless DNA, and ZENA are

trademarks of Microchip Technology Incorporated in the

U.S.A. and other countries.

SQTP is a service mark of Microchip T echnology Incorporated

in the U.S.A.

Silicon Storage Technology is a registered trademark of

Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology

Germany II GmbH & Co. KG, a subsidiary of Microchip

Technology Inc., in other countries.

All other trademarks mentioned herein are property of their

respective companies.

© 2016, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0359-3

EELOQ, KEELOQ logo, Kleer,

32

logo, RightT ouch, S pyNIC,

QUALITY MANAGEMENT S

2016 Microchip Technology Inc. DS50002449A-page 2

Microchip received ISO/TS-16949:2009 certification for its worldwide

headquarters, design and wafer fabrication facilities in Chandler and

Tempe, Arizona; Gresham, Oregon and design centers in California

and India. The Company’s quality system processes and procedures

are for its PIC

devices, Serial EEPROMs, microperipherals, nonvolatile memory and

analog products. In addition, Microchip’s quality system for the design

and manufacture of development systems is ISO 9001:2000 certified.

®

MCUs and dsPIC® DSCs, KEELOQ

®

code hopping

Page 3

Object of Declaration: KSZ8061MNX Evaluation Board

2016 Microchip Technology Inc. DS50002449A-page 3

Page 4

NOTES:

DS50002449A-page 4 2016 Microchip Technology Inc.

Page 5

KSZ8061MNX EVALUATION

BOARD USER’S GUIDE

Table of Contents

Preface ...........................................................................................................................7

Introduction............................................................................................................7

Document Layout .................................................................................................. 7

Conventions Used in This Guide........................................................................... 8

Recommended Reading.............................................................. .. ........................9

The Microchip Web Site........................................................................................ 9

Customer Support....................... ....................................................... ...................9

Revision History .................................................................................................... 9

Chapter 1. Product Overview

1.1 Introduction ...................................................................................................11

Chapter 2. Configuration

2.1 Introduction ...................................................................................................13

2.2 Configur ation Options ....... ............................................................................ 13

2.3 Configur ation Instruct io n s .......... ............. ... .. .......................... ... .. ............. .. .. . 16

2.4 Power ........................................................................................................... 18

2.5 Clocking ........... .......................................... ................................................... 18

2.6 Line Interface Connector Options .................................................................19

2.7 MII Connector ...............................................................................................20

2.8 MII Management Interface (MDIO/MDC) .....................................................20

2.9 10-Pin He ad e r (J 7) ........................................ .. .. .............. .. .. ......................... 20

2.10 Status Indicator LEDs .................................................................................20

2.11 Reset Butt o n s ............... ....................................................... ....................... 21

2.12 Jumpers ......... ............................................................................................. 21

2.13 KSZ8061MNX Strapping Options ....................................... .................... ....22

2.14 MDIO/MDC Software Utility and FTDI Cable .............................................22

Appendix A. Schematic and Layouts

A.1 Introduction ..................................................................................................25

Appendix B. Bill of Materials (BOM)

Worldwide Sales and Service ....................................................................................34

2016 Microchip Technology Inc. DS50002449A-page 5

Page 6

KSZ8061MNX Evaluation Board User’s Guide

NOTES:

DS50002449A-page 6 2016 Microchip Technology Inc.

Page 7

KSZ8061MNX EVALUATION

BOARD USER’S GUIDE

Preface

NOTICE TO CUSTOMERS

All documentation becomes dated, and this manual is no exception. Microchip tools and

documentation are constantly evolving to meet customer needs, so some actual dialogs

and/or tool description s may differ from th ose in this docume nt. Please refer to our web site

(www.microchip.com) to obtain the latest documentation available.

Documents are identified with a “DS” numb er. This number is located on the bottom of each

page, in front of the page number. The numbering convention for the DS number is

“DSXXXXXXXXA”, where “XXXXXXXX” is the document number and “A” is the revision level

of the document.

For the most up-to-date information on development tools, see the MPLAB

Select the Help menu, and then Topics to open a list of available online help files.

INTRODUCTION

®

IDE online help.

This chapter contains general information that will be useful to know before using the

KSZ8061MNX Evaluation Board. Items discussed in this chapter include:

• Document Layout

• Conventions Used in This Guide

• Recommended Reading

• The Microchip Web Site

• Customer Support

• Revision History

DOCUMENT LAYOUT

This document describes how to use the KSZ8061MNX Evaluation Board as a development tool. The document is organized as follows:

• Chapter 1. “Product Overview” – This chapter includes important information

about the KSZ8061MNX Evaluation Board.

• Chapter 2. “Configuration” – This chapter includes a detailed description of

each function of the evaluation boar d and instructions on how to begin us ing the

board.

• Appendix A. “Schematic and Layouts” – Refer to this appendix for board

schematics.

• Appendix B. “Bill of Materials (BOM)” – Refer to this appendix to view the bill of

materials.

2016 Microchip Technology Inc. DS50002449A-page 7

Page 8

KSZ8061MNX Evaluation Board User’s Guide

CONVENTIONS USED IN THIS GUIDE

This manual uses the following docum entat io n conven tion s:

DOCUMENTATION CONVENTIONS

Description Represents Examples

Arial font:

Italic chara c ters Referenced books MPLAB

Emphasized text ...is the only compiler...

Initial caps A window the Output window

A dialog the Settings dialog

A menu selection select Enable Programmer

Quotes A field name in a window or

dialog

Underlined, Italic text with

right angle bracket

Bold characters A dialog button Click OK

N‘Rnnnn A number in verilog format,

Te xt in angle brackets < > A key on the keyboard Press <Enter>, <F1>

Courier New font:

Plain Courier New Sample source code #define START

Italic Courier New A variable argument file.o, where file can be

Square brackets [ ] Optional arguments mcc18 [options] file

Curly brackets and pipe

character: { | }

Ellipses... Replaces r epeated text var_name [,

A menu path File>Save

A tab Click the Power tab

where N is the tota l number of

digits, R is th e radi x and n is a

digit.

Filenames autoexec.bat

File paths c:\mcc18\h

Keywords _asm, _endasm, static

Command-line options -Opa+, -Opa-

Bit values 0, 1

Constants 0xFF, ‘A’

Choice of mut ually exclus ive

arguments; an OR selection

Represents code supplied by

user

®

IDE User’s Guide

“Save project before build”

4‘b0010, 2‘hF1

any valid filename

[options]

errorlevel {0|1}

var_name...]

void main (void)

{ ...

}

DS50002449A-page 8 2016 Microchip Technology Inc.

Page 9

RECOMMENDED READING

This user's guide descr ibe s how to us e K S Z8061 MNX Ev alu ati on Bo ard. Other us eful

documents are listed below. The following Microchip documents are available and

recommended as supplemental r eference resources:

• KSZ8061MNX/KSZ8061MNG Data Sheet

This data sheet provides detailed information regarding the KSZ8061MNX device.

THE MICROCHIP WEB SITE

Microchip provides on line support via our w eb site at www.microchip.com. This web

site is used as a means to m ake files and infor mation easily availabl e to customers.

Accessible by using your favo rite In ternet bro wser, the web site contains the follow in g

information:

• Product Support – Data sheets and errata, application notes and sample

programs, design resources, user’s guides and hardware support documents,

latest software releases and archived software

• General Technical Support – Frequently Asked Questions (FAQs), technical

support requests, online discussion groups, Microchip consultant program

member listing

• Business of Microchip – Product selector and ordering guides, latest Microchip

press releases, listing of seminars and events, listings of Microchip sales offices,

distributors and factory representatives

Preface

CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

• Distributor or Representative

• Local Sales Office

• Field Application Engineer (FAE)

• Technical Support

Customers should contact th eir di str ibutor, representative or field application engineer

(FAE) for support. Local sales office s are al s o av ail ab le to help customers. A list ing of

sales offices and locations is included in the back of this document.

Technical support is available through the web site at:

http://www.microchip.com/support.

REVISION HISTORY

Revision A (March 2016)

• Original Microchip release of this document. This document replaces Micrel document “KSZ8061MNX Evaluation Board User's Guide” version 1.1 (March 2015).

2016 Microchip Technology Inc. DS50002449A-page 9

Page 10

KSZ8061MNX Evaluation Board User’s Guide

NOTES:

DS50002449A-page 10 2016 Microchip Technology Inc.

Page 11

KSZ8061MNX EVALUATION

KSZ8061

Second PHY

(KSZ8081)

RJ-45

Line

Connector

(3 options)

MII Connector

10-Pin

Management

Header (J7)

R1-6

R21-26 R11-16

R221-226R211-216

DC Power

Connector

Tx

Rx

MII

MII

Rx

Tx

Interrupt

Reset

MDIO/MDC

Signal Detect

Magnetics

Magnetics

KSZ8061 3.3V Reg

Select

KSZ8081 3.3V Reg

KSZ8061 Low V Reg

5V

En

RXER Latch,

LED, Reset

Reset

Reset

25 MHz

Xtal

Clocking Options

BOARD USER’S GUIDE

Chapter 1. Product Overview

1.1 INTRODUCTION

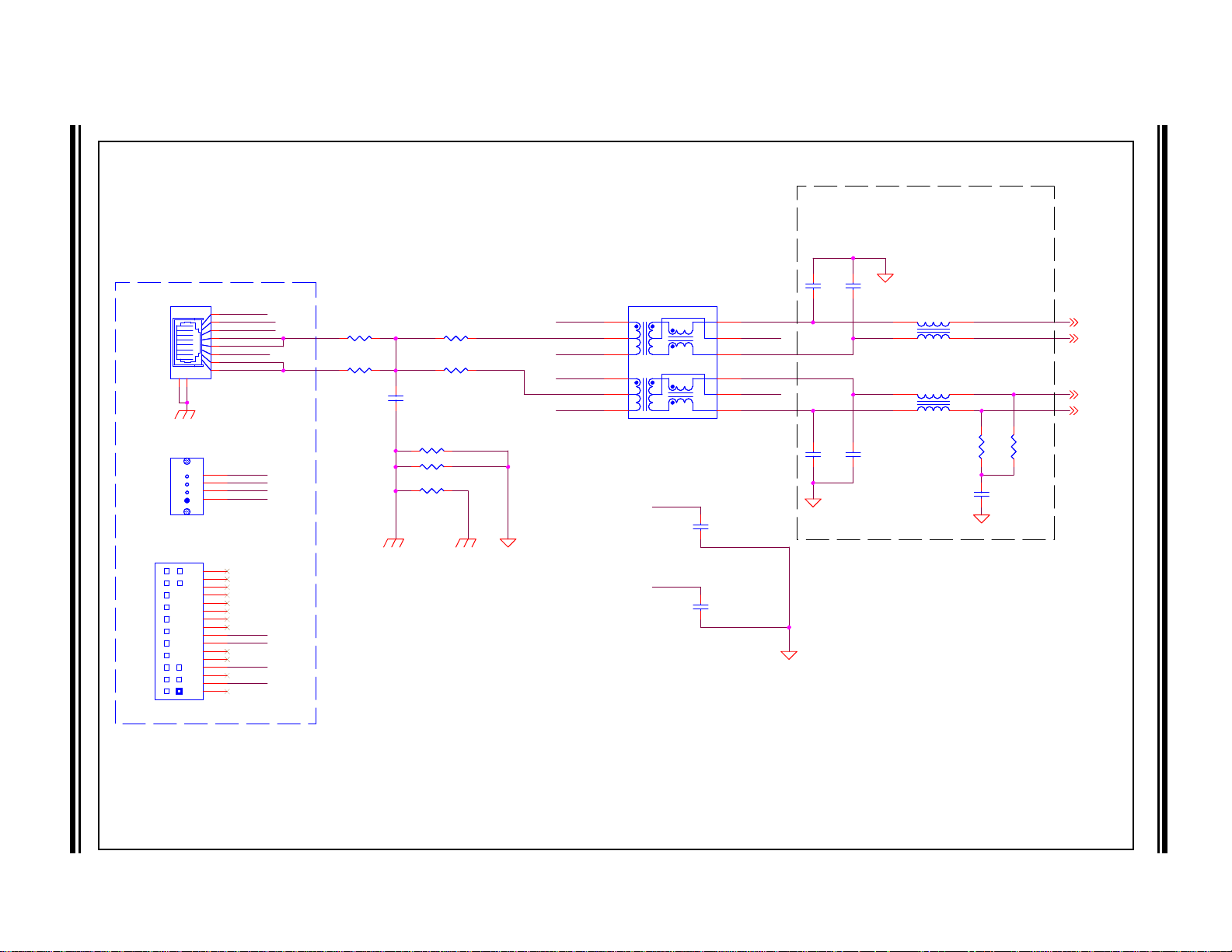

The KSZ8061MNX Evaluation Board is designed to enable functional and performance

testing of the KSZ8061MNX PHY. In addition to the KSZ8061 PHY, there is a second

PHY–a KSZ8081. The KSZ8081 is a standard 10/100 Ethernet PHY. It is used here to

provide a second line interface for simple full-duplex traffic through the KSZ8061. This

board is not intended for evaluation of the KSZ8081. A block diagram of the board is

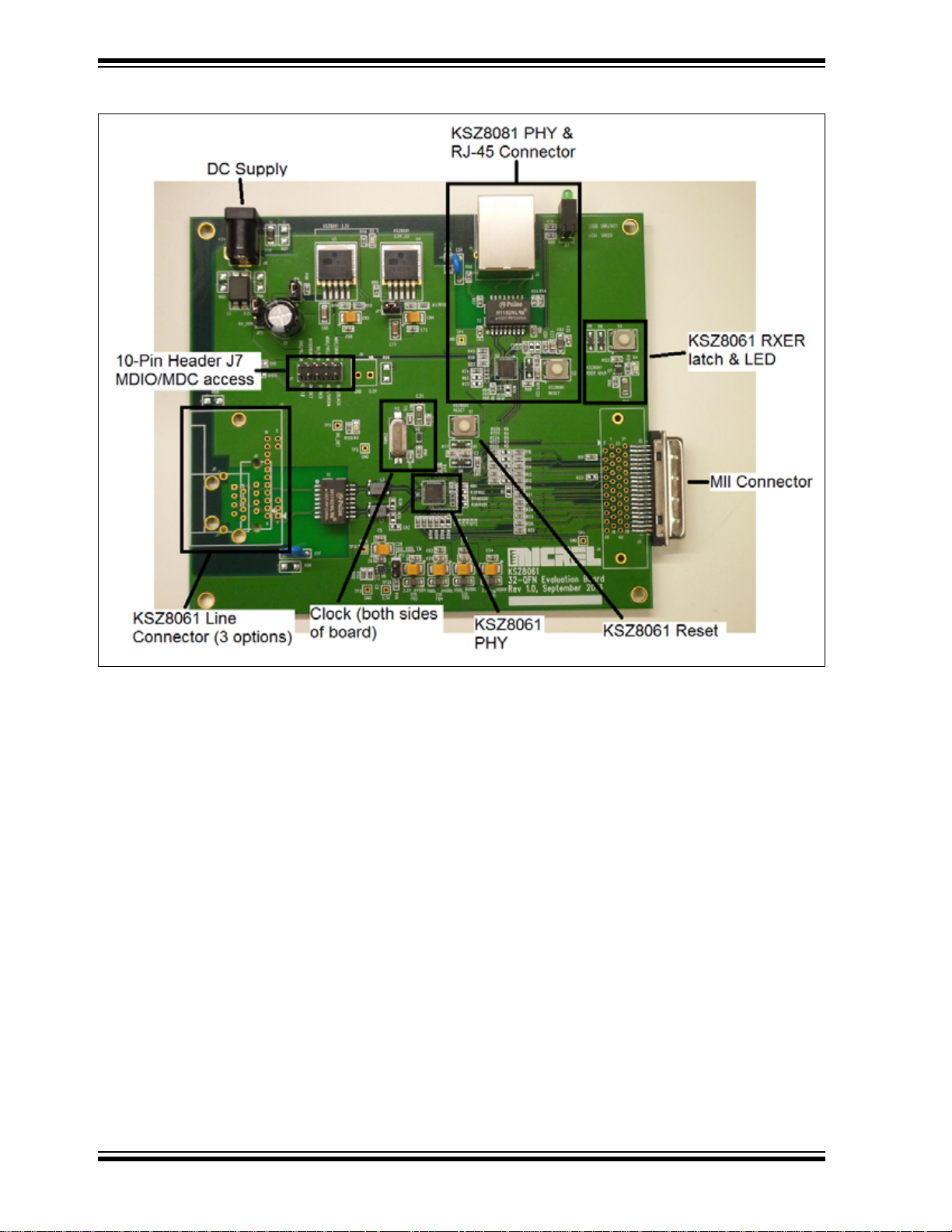

shown in Figure 1-1. Figure 1-2 highlights the board components.

FIGURE 1-1: KSZ8061MNX EVALUATION BOARD BLOCK DIAGRAM

2016 Microchip Technology Inc. DS50002449A-page 11

Page 12

KSZ8061MNX Evaluation Board User’s Guide

FIGURE 1-2: KSZ8061MNX EVALUATION BOARD COMPONENTS

DS50002449A-page 12 2016 Microchip Technology Inc.

Page 13

2.1 INTRODUCTION

This chapter discusses the configuration of the KSZ8061MNX Evaluation Board.

Items discussed in this chapter include:

• Configuration Options

• Configuration Instructions

• Power

• Clocking

• Line Interface Connector Options

• MII Connector

• MII Management Interface (MDIO/MDC)

• 10-Pin Header (J7)

• Status Indicator LEDs

• Reset Buttons

• Jumpers

• KSZ8061MNX Strapping Options

• MDIO/MDC Software Utility and FTDI Cable

KSZ8061MNX EVALUATION

BOARD USER’S GUIDE

Chapter 2. Configuration

2.2 CONFIGURATION OPTIONS

The KSZ8061 line interface is designed to permit the installation of any one of three

different connectors. These are described further in a later section.

The KSZ8061 MII data path can be configured in three different ways. Below are

descriptions and photographs of the configuration options.

1. Two-PHY MII Back-to-Back

The evaluation board has two PHYs: a KSZ8061 (U1) and a KSZ8081 (U2). The

KSZ8081 is an ordinary 10/100 Ethernet PHY , and is on this board to support the

KSZ8061. Their MII buses can be connected together, which allows Ethernet

frames to be passed between the KSZ8061 line interface (J1, J2 or J3) and the

KSZ8081 line interface (J6). Unless otherwise indicated, this is the default board

configuration.

2. MII Loopback

In this configuration, the KSZ8061 receives Ethernet traffic from the line interface. At the MII interface, RX traffic is looped back the TX MII interface, and the

KSZ8061 transmits it back to the line interface. The KSZ8081 PHY is not used.

Do not reference Figure 2-2 for resistor settings.

3. MII Connector

The MII edge connector (J5) allows the KSZ8061MNX Evaluation Board to be

connected to the MAC port of a Microchip switch evaluation board, or to any

other device with an Ethernet MAC interface. Full duplex traffic can pass

between the MII connector and the KSZ8061 line interface (J1, J2 or J3). The

KSZ8081 PHY is not used.

2016 Microchip Technology Inc. DS50002449A-page 13

Page 14

KSZ8061MNX Evaluation Board User’s Guide

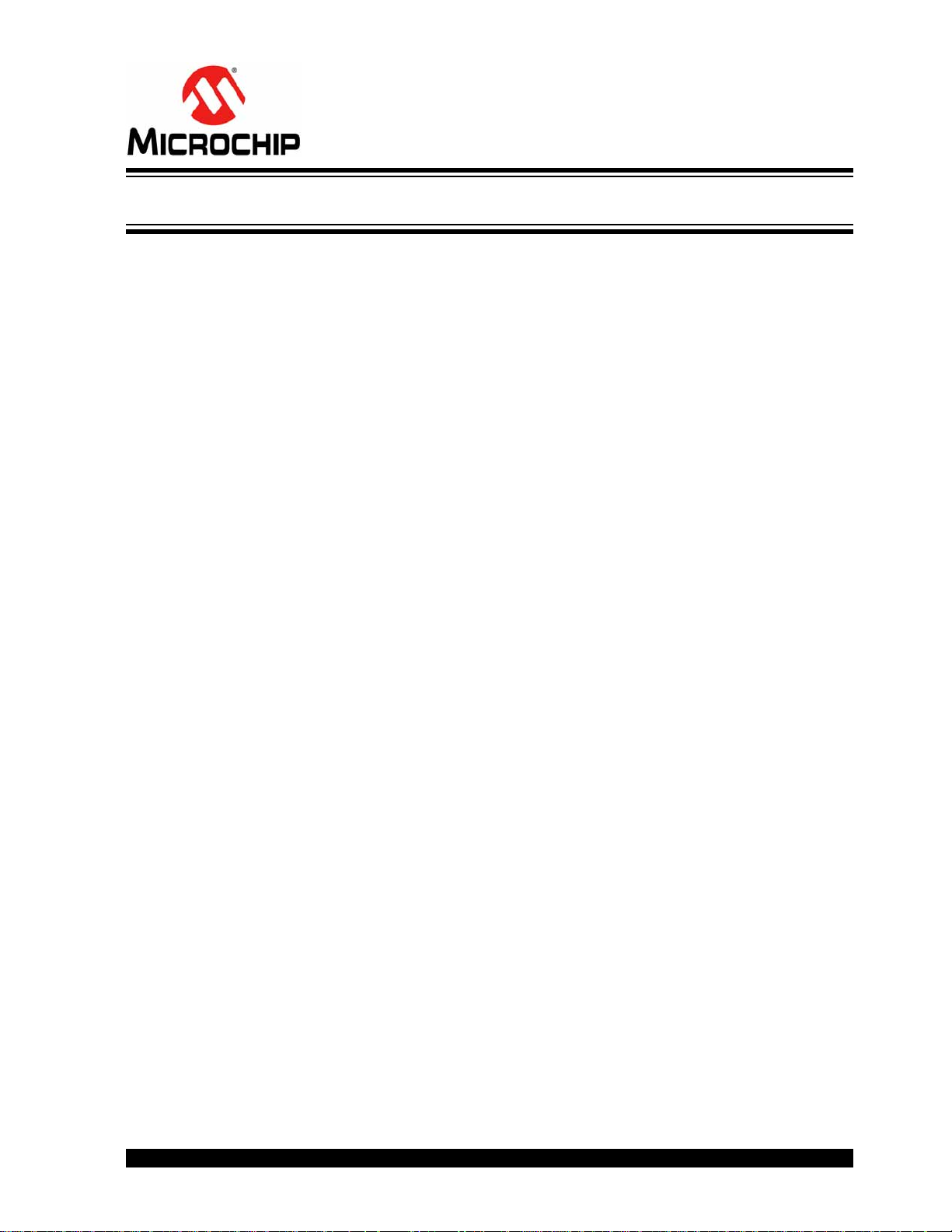

FIGURE 2-1: KSZ8061MNX EVALUATION BOARD IN TWO-PHY MII BACK-TO-BACK MODE

DS50002449A-page 14 2016 Microchip Technology Inc.

Page 15

Configuration

FIGURE 2-2: KSZ8061MNX EVALUATION BOARD IN MII LOOPBACK MODE WITH

USB-TO-MDIO/MDC CABLE ON J7

FIGURE 2-3: KSZ8061MNX EVALUATION BOARD IN MII CONNECTOR MODE, WITH

ETHERNET SWITCH

2016 Microchip Technology Inc. DS50002449A-page 15

Page 16

KSZ8061MNX Evaluation Board User’s Guide

2.3 CONFIGURATION INSTRUCTIONS

These instructions detail how to change between configurations. Figure 2-4 and

Figure 2-5 show the location of the components referenced in the instructions.

1. Two-PHY MII Back-to-Back Configuration. This is the default configuration, so

these steps are only necessary if switching the board back from another

configuration.

a) Place the KSZ8061 in MII Back-to-Back mode: install R40 and R41. Remove

R39.

b) Connect the MII interfaces of the KSZ8061 and KSZ8081: install R212-R216

and R222-226. Note that the MII clocks should not be connected between

the two devices, so do not install R211 and R221.

c) Both PHYs must be clocked from U3. Do not use crystal Y1, by removing

either Y1 or R91 and R92.

d) Remove R1-R6.

e) Power the KSZ8081: install jumper JP1.

f) Optionally, for optimal signal integrity, remove R11-R16 and R21-R26.

2. MII Loopback Config urati on

a) Place the KSZ8061 in MII Back-to-Back mode: install R40 and R41. Remove

R39.

b) Install R1-R6.

c) Remove the KSZ8081 from the MII bus. There are three possible ways to do

this:

- Remove jumper JP1 to remove power from the KSZ8081.

- Remove R211-R216 and R221-R226.

- Put the KSZ8081 in Isolate mode: install R70.

d) The KSZ061 may be clocked by either the external clock (U3) or the crystal

(Y1). When changing between clock sources, the KSZ8061 does not require

any setting changes.

e) Optionally, for optimal signal integrity, remove R11-R16 and R21-R26.

3. MII Connector Configurati on

a) Place the KSZ8061 in Normal mode: remove R39 and R41. Install R40 if

Auto-MDI/MDI-X is desired. Otherwise, remove R40.

b) Install R11-R16 and R21-R26.

c) Remove R1-R6.

d) Remove the KSZ8081 from the MII bus. There are three possible ways to do

this:

- Remove jumper JP1 to remove power from the KSZ8081.

- Remove R211-R216 and R221-R226

- Put the KSZ8081 in Isolate mode: install R70.

e) The KSZ061 may be clocked by either the external clock (U3) or the crystal

(Y1). When changing between clock sources, the KSZ8061 does not require

any setting changes.

f) Connect the KSZ8061 evaluation board to a compatible connector on a

Microchip switch evaluation board, and ensure that the port on the switch

board is configured for MAC interface.

DS50002449A-page 16 2016 Microchip Technology Inc.

Page 17

Configuration

FIGURE 2-4: TOP SIDE COMPONENTS FOR CONFIGURTION CHANGES

FIGURE 2-5: BOTTOM SIDE COMPONENTS FOR CONFIGURATION

CHANGES

2016 Microchip Technology Inc. DS50002449A-page 17

Page 18

KSZ8061MNX Evaluation Board User’s Guide

KSZ8061MNX (U1)

XI

XO

R91 / DNI

R92 / DNI

R62 / 0ȍ

PL135-27 (U3)

Y1

CLK1

XI

KSZ8081MNX (U2)

CLK0

2.4 POWER

The evaluation board requires a DC supply at barrel connector J8. A jumper must be

installed on pins 2-3 of JP3. The voltage requirement is 4.5V to 14V. The current

requirement is 200 mA.

An alternate power connection is available at the 10-pin management header J7. This

is intended to allow the board to be powered from a USB cable such as the FTDI

C232HM-EDHSL-0. When supplying power via header J7, a jumper must be installed

on pins 1-2 of JP3 (labeled “5V_HDR”).

A noise filtering choke is provided on the J8 connector, but not on the J7 power pins.

Therefore, J8 is the preferred power connecto r when tes tin g KSZ80 61 per forma nc e.

2.5 CLOCKING

The KSZ8061 utilizes a 25 MHz reference clock. There are two options for supplying

this clock: crystal or external clock. If the second PHY (KSZ8081, U2) is used, then the

two PHYs must be synchronized and the only clocking option is to clock both PHYs

from the same external clock source.

1. External clock (default configuration). The external clock source is a Microchip

PL135-27 (U 3), wh ich drive s the same 25 MHz cloc k to both PHYs. Wh en usin g

this clock source, the KSZ8061 crystal (Y1) must not be connected from the

KSZ8061. This is done either by removing R91 and R92, or by removing Y1, refer

to Figure 2-6.

FIGURE 2-6: EXTERNAL CLOCK OPTION

2. Crystal. Crystal Y1 can be connected directly to the KSZ8061, which has an

on-chip oscillator. Install resistors R91 and R92, and remove resistor R62. To

fully turn off the external clock (U3), remove R63. This mode can be used only

when the KSZ8061 and KSZ8081 are not used in back-to-back configuration.

DS50002449A-page 18 2016 Microchip Technology Inc.

Page 19

Configuration

KSZ8061MNX (U1)

XI

XO

R91 / 0ȍ

R92 / 0ȍ

R62

DNI

PL135-27 (U3)

Y1

VDD

3.3V

R63 optional

FIGURE 2-7: CRYSTAL CLOCKING OPTION

CAUTION

The silkscreen labels on the bottom of the board for R62, R91 and R92 are incorrect.

The middle resistor is R62. R91 is closer to C9, and R92 is closer to C10. The image

below shows the correct locations of R62, R91, and R92.

2.6 LINE INTERFACE CONNECTOR OPTIONS

The KSZ8081 has a conventional RJ-45 UTP Ethernet connector, but there are three

connector options for the KSZ8061:

1. J1: Ethernet RJ-45

2. J2: TE MQS-4, part number 1379165-1 (Mating receptacle is 1379029-1)

3. J3: Sumitomo TS series 16-pin, part number 6098-6793 (Mating receptacle is

6098-4008)

2016 Microchip Technology Inc. DS50002449A-page 19

Table 2-1 lists the signal connections for each connector. Also refer to the schematic or

PCB layout file since connector pin numbering may not be standardized.

Page 20

KSZ8061MNX Evaluation Board User’s Guide

TABLE 2-1: KSZ8061 CONNECTOR PIN ASSIGNMENTS

Connector Pin Assignment

KSZ8061 Signal

RJ-45 TE 1379165-1

TXP1410

TXM239

RXP327

RXM616

2.7 MII CONNECTOR

The MII edge connector J5 provides external access to the KSZ8061 MII bus and the

MII management interface (MDIO/MDC). This connector is typically used to connect

the KSZ8061 PHY to the MAC interface on a Microchip Ethernet switch evaluation

board. Test traffic can then be sent and received through another port on the switch.

This configuration is shown in Figure 2-3. Note that 5V power is not shared across this

connector, so each board must be powered separately.

To use this interface, it is necessary to have 0-ohm resistors R11-R16 and R21-R26

installed. The KSZ8081 also needs to be isolated from the MII bus. The simplest way

to do this is to remove power from the KSZ8081 by removing jumper JP1. Alternatively,

place the KSZ8081 into Isolate mode by installing R70, or remove resistors R211-R216

and R221-R226.

Sumitomo

6098-6793

2.8 MII MANAGEMENT INTERFACE (MDIO/MDC)

The MII management interface (MDIO/MDC) can be accessed in two ways. The first is

via the MII connector J5, discussed above. This requires the installation of resistors

R31 and R33. Alternatively , these signals are accessible at the 10-pin header J7,

requiring the installation of resistors R27 and R28. These resistor options are provided

for signal integrity optimization. If signal integrity on this interface is not a problem, then

it is acceptable to leave all four resistors installed.

The default MII management addresses (a.k.a. PHY addresses) are b'001 for the

KSZ8061, and b'011 for the KSZ8081.

2.9 10-PIN HEADER (J7)

Header J7 is intended primarily for access to the MII management interface (MDIO and

MDC signals). The header pins are labeled with color codes for connection to the FTDI

C232HM-DDHSL-0 or C232HM-EDHSL-0 USB-to-MPSSE cable. The two pins labeled

“MDIO” are the same board signal. They are duplicated because the FTDI cable separates the serial data input and output signals.

As described in Section 2.4 “Power”, it is possible to power the board through header

J7 instead of the standard power connector J8. The C232HM-EDHSL-0 cable has 5V

available for this purpose. Note that the board cannot be powered from the

C232HM-DDHSL-0 cable which is 3.3V. See Section 2.4 “Power” for more details.

This header also provides access to the KSZ8061 reset input signal, and the interrupt

and signal detect output signals. The reset signal goes only to the KSZ8061, and not

to the KSZ8081 nor to the RXER latch and LED.

DS50002449A-page 20 2016 Microchip Technology Inc.

Page 21

2.10 STATUS INDICATOR LEDS

The board includes the following LEDs:

• D2: KSZ8061 3.3V power indicator LED (red). Note that the KSZ8061 and

KSZ8081 have separate voltage regulators, and that there is no equivalent power

LED for the KSZ8081.

• D3: KSZ8061 SIGD (signa l det ect ) LED (g reen ). SIGD is als o a ccessibl e at J7 pi n 8 .

• D4: KSZ8061 RXER (RX error) latch LED (red). RXER is an MII output signal from

the KSZ8061. If RXER ever goes high, that state is captured and held by latch

(U7). This latch is reset by the press button S3.

• D7: KSZ8081 link status LEDs (green). These are standard link/activity and speed

status LEDs. There are no equivalent link status LEDs for the KSZ8061.

FIGURE 2-8: LOCATION OF LEDS AND RESET BUTTONS

Configuration

2.11 RESET BUTTONS

The board has three push buttons, which are all used for reset purposes:

• S1: Chip reset for KSZ8061 (U1)

• S2: Chip reset for KSZ8081 (U2)

• S3: KSZ8061 RXER latch reset (U7, D4)

2016 Microchip Technology Inc. DS50002449A-page 21

Page 22

KSZ8061MNX Evaluation Board User’s Guide

2.12 JUMPERS

The board has four jumpers:

• JP1: Install to enable the KSZ8081 (U2) 3.3V regulator. Remove to disconnect

power from the KSZ8081. Removing power from the KSZ8081 also isolates it

from the MII bus.

• JP2: When installed, the low voltage regulator (U6) that partially powers the

KSZ8061 is enabled/disabled by the KSZ8061 SIGD signal. When not installed,

the low voltage regulator is always enabled. When the KSZ8061 is properly configured, this feature can be used to achieve ultra-low power standby power.

• JP3: (3-pin) Selects the power source for the board. Normally, install a jumper on

pins 2-3 for power from connector J8. To power the board from header J7 instead,

install the jumper on pins 1-2.

• JP4: Install to enable the KSZ8061 (U1) voltage regulator. Remove to disconnect

power from the KSZ8061.

FIGURE 2-9: LOCATION OF JUMPERS

2.13 KSZ8061MNX STRAPPING OPTIONS

Resistors R36-R44 are used to select optional strapping configurations to the

KSZ8061MNX. When a resistor is not installed, the internal resistor for each pin pulls

it to its default level during reset. Installing a resistor pulls the pin to the opposite logic

level. See the chip data sheet and/or board schematic for details.

DS50002449A-page 22 2016 Microchip Technology Inc.

Page 23

Configuration

TABLE 2-2: STRAPPING RESISTOR OPTIONS FOR PRODUCTION SILICON

Resistor Strapping Function Resistor not Installed Resistor Installed

[R38, R37, R36] PHY Address Address = b’001 Any other address

[R41, R40, R39] Configuration b’000 = Normal MII mode,

Auto-MDI/MDI-X disabled

R42 Quiet-WIRE

R43 NAND Tree Disabled Enabled

R44 Auto Negotiation Disabled Enabled

®

Filtering Enabled Disabled

2.14 MDIO/MDC SOFTWARE UTILITY AND FTDI CABLE

ethutil.exe is a free Windows command line utility from Microchip for access to the

KSZ8061 MII management interface (MDIO/MDC) using the USB cables described in

Section 2.9 “10-Pin Header (J7)”. Contact your Microchip sales representative for

information on how to download this utility and the accompanying user guide. The user

guide provides instructions on installing and using this utility.

When the KSZ8061 and KSZ8081 are both powered and connected to the MII management interface (MDIO/MDC), the ethutil.exe utility will automatically configure itself

for the highest address PHY, which by default is the KSZ8081 at address 3. Use the

“address” command, as shown in Figure 2-10, to switch to the KSZ8061 PHY.

b’010 = Normal mode,

Auto-MDI/MDI-X enabled

b’110 = Back-to-back,

Auto-MDI/MDI-X enabled

FIGURE 2-10: ETHUTIL.EXE UTILITY - OPENING SCREEN AND ADDRESS COMMAND

If the KSZ8081 is removed, disabled or if power is disconnected, then the utility will

automatically configure itself for the KSZ8061 instead of the KSZ8081. This is shown

in Figure 2-11.

2016 Microchip Technology Inc. DS50002449A-page 23

Page 24

KSZ8061MNX Evaluation Board User’s Guide

address 1

r 0

r 1

FIGURE 2-11: ETHUTIL.EXE UTILITY WHEN KSZ8081 MDIO/MDC IS OFF

Commands for ethutil.exe can be saved in ordinary text files and run using the “run”

command. This is a simple form of scripting. It is suggested to have an “address 1"

command as the first line in all script files, to ensure that the commands to go the

KSZ8061 rather than the KSZ8081. Example 2-1 is an example of a file named

script.txt. Figure 2-12 shows how this script file is run.

EXAMPLE 2-1: SCRIPT.TXT

FIGURE 2-12: RUNNING A SCRIPT

DS50002449A-page 24 2016 Microchip Technology Inc.

Page 25

Appendix A. Schematic and Layouts

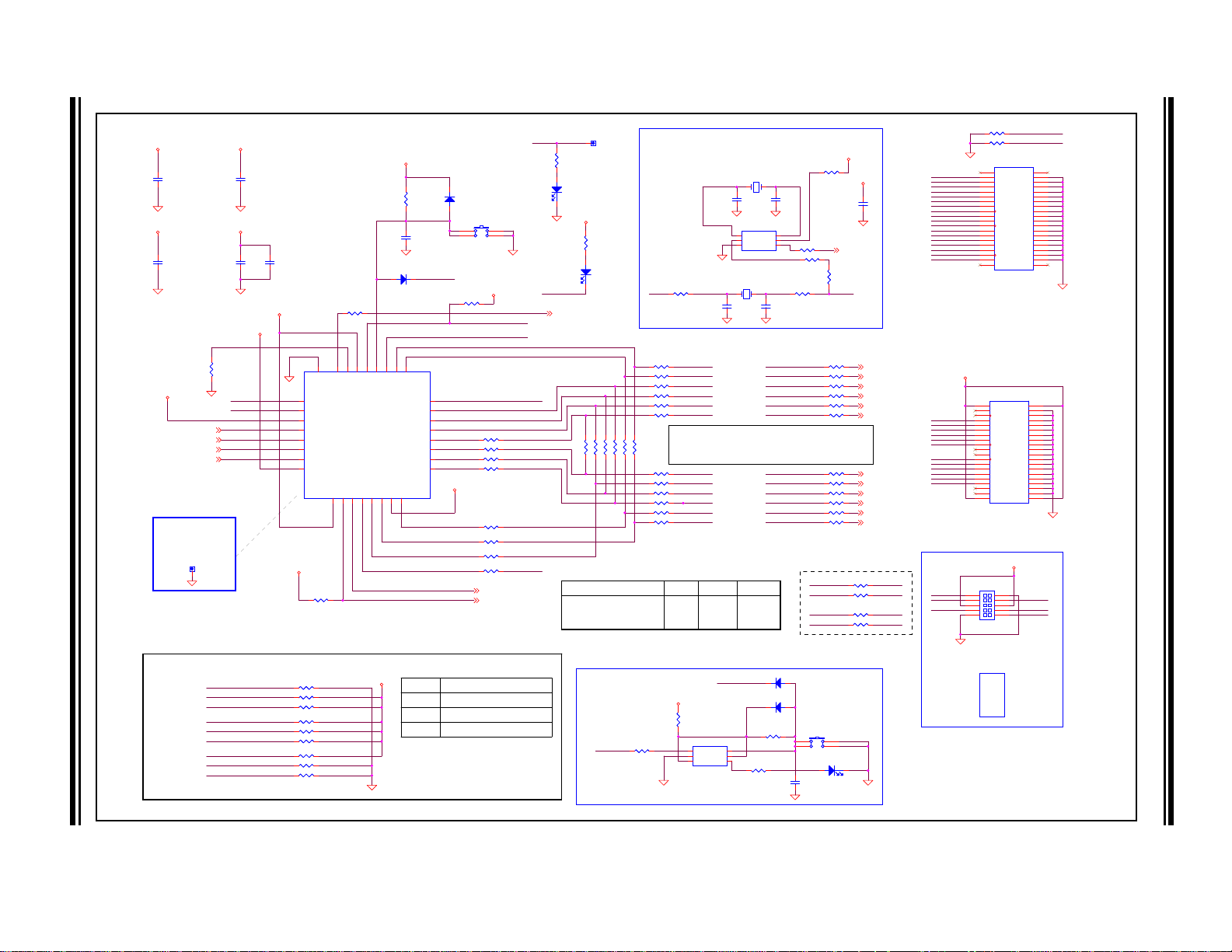

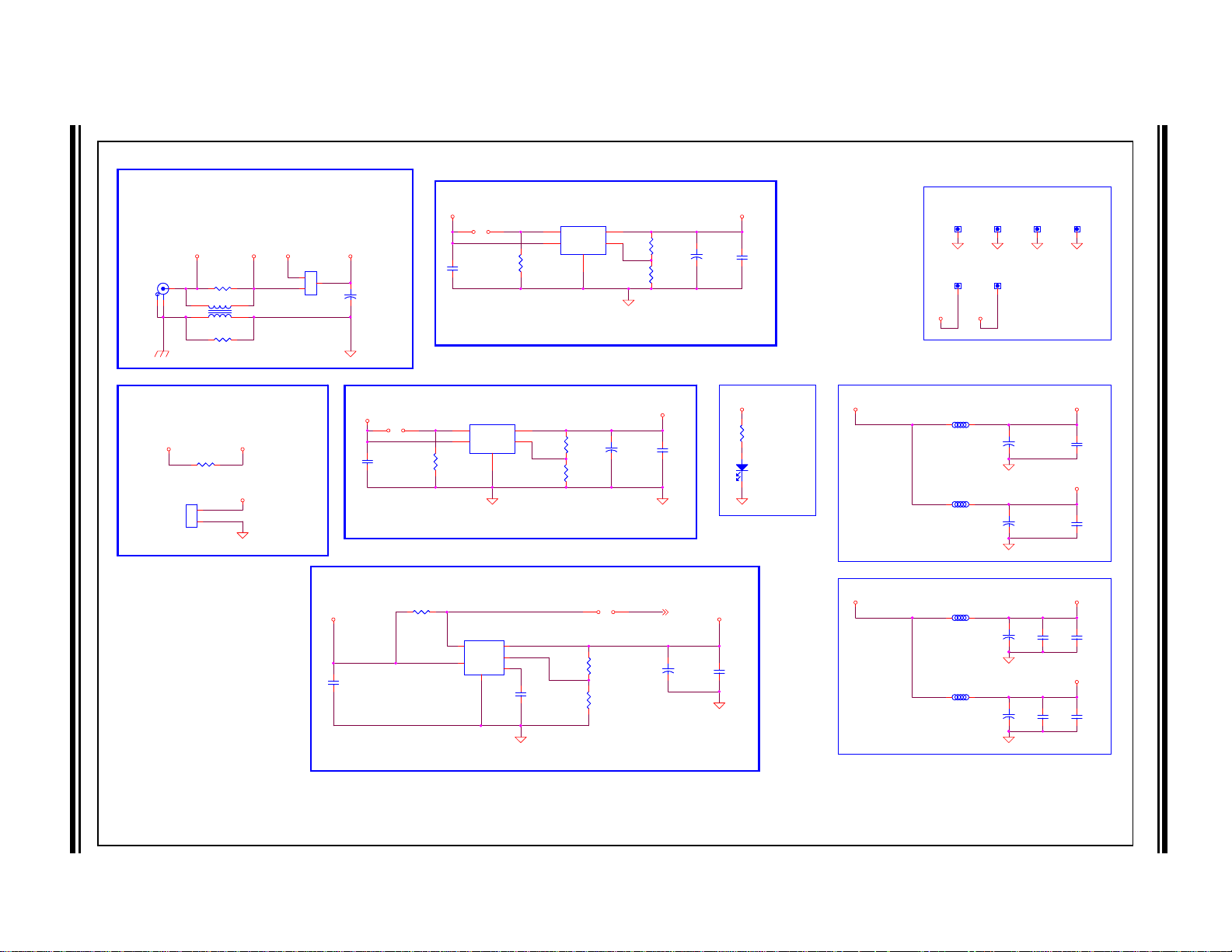

A.1 INTRODUCTION

This appendix contains the following schematics and layouts for the MCP9600

Thermocouple IC Evaluation Board:

• Figure A-1: “Board Schematic 1 of 4”

• Figure A-2: “Board Schematic 2 of 4”

• Figure A-3: “Board Schematic 3 of 4”

• Figure A-4: “Board Schematic 4 of 4”

KSZ8061MNX EVALUATION

BOARD USER’S GUIDE

2016 Microchip Technology Inc. DS50002449A-page 25

Page 26

DS50002449A-page 26 2016 Microchip Technology Inc.

TXC_P1

RXD1_P1

RXD0_P1

RXC_P1

MDIO

RXD3_U1

RXD1_U1

RXD2_U1

RXC_U1

TXER_U1

TXD2_U1

TXD3_U1

MII_TXC

MII_MDC

MII_RXC

RXER_U1

MII_MDIO

MII_RXD2

MII_RXD3

COL

MII_RXDV

MII_RXD1

MII_RXD0

CRS_U1

MII_TXD2

MII_TXD3

MII_TXD0

MII_TXD1

MII_TXEN

INTRP_U1

RXP_U1

RXM_U1

TXP_U1

TXM_U1

TXER_U1

TXD0_U1

RXD2_P1

RXDV_P1

RXER_P1

RXD3_P1

TXEN_U1

INTRP_U1

TXD1_U1

CRS_U1

XI_D1XO_D1

XI_U1

XO_U1

COL

MII_TXEN

TXC_U1

RXC_U1

RXD0_U1

RXD1_U1

RXD2_U1

RXD3_U1

RXDV_U1

RXER_U1

MII_RXD2

CRS_U1

RXDV_U1

RXER_U1

RXD0_U1

SIGD

XO_U1

XI_PLXO_PL

MII_RXC

MII_RXD0

MII_RXD1

MII_RXDV

MII_RXD3

MII_TXC

MII_TXEN

MII_TXD0

MII_TXD1

MII_TXD2

MII_TXD3

XI_U1

RESET_IN

RST#_U1

SIGD_P1

SIGD

RESET_IN

SIGDINTRP_U1

MDIO_H10

MDC_H10

MDIO_H10

MII_TXC

MII_RXC

MII_RXD2

MII_RXD3

MII_RXDV

MII_RXD1

MII_RXD0

MII_TXD2

MII_TXD3

MII_TXD0

MII_TXD1

MII_TXEN

RXER_U1

RESET_IN

MDC

MDC

MDIO MDIO_H10

MDC_H10

MDC

MDIO MII_MDIO

MII_MDC

TXER_U1

TXD3_U1

TXD2_U1

TXD1_U1

TXD0_U1

TXEN_U1

TXC_U1

RXC_U1

RXDV_U1

RXD0_U1

RXD1_U1

RXD2_U1

RXD3_U1

VDDIO

AVDDL

AVDDH

VDDIO

DVDDL

DVDDL

AVDDH

VDDIO

VDDIO

VDDIO

AVDDL

5V_HDR

5.0V

VDDIO

VDDIO

3.3V

3.3V

3.3V

RXP_U1(4)

RXM_U1(4)

TXP_U1(4)

TXM_U1(4)

SIGD (6)

CLK_U2 (5)

MDC (5)

MDIO (5)

PHY_TXD3 (5)

PHY_TXD2 (5)

PHY_TXD1 (5)

PHY_TXD0 (5)

PHY_TXEN (5)

PHY_TXC (5)

PHY_RXD1 (5)

PHY_RXD2 (5)

PHY_RXD3 (5)

PHY_RXDV (5)

PHY_RXC (5)

PHY_RXD0 (5)

CONFIG2

PHYAD0

CONFIG1

CONFIG0

Q-WIRE_DISABLE

PHYAD2

Strapping Options (Refer to data sheet for descriptions)

PHYAD1

AUTO_NEG_DIS

010

MII normal mode; Auto-MDI/MDI-X disabled000

Mode (description)CONFIG[2:0]

MII normal mode; Auto-MDI/MDI-X enabled

NAND_Tree#

KSZ8061

Push

Button

Reset

(32-QFN)

Notes:

1. Place all MII bus resistors on the traces

to U1 to minimize stubs.

2. Place R11-R26 and R211-R226 on opposite

sides of the board - mirror image.

MII Back-to-Back mode is required

for MII loopback, and when connecting

KSZ8061 to KSZ8081.

MII normal mode is used when interfacing

via the MII Connector.

1) PL135-27 (default): Install R62. Remove R91, R92

or

2) Y1: Install R91, R92. Remove R62.

0.1uF at U1 pin 15

0.1uF at U1 pins 9, 30

0.1uF at U1 pin 3

0.1uF at U1 pin 8

Labels for 5x2 Header:

1

3

5

7

9

2

4

6

8

10

GND / BLACK

MDIO / GREEN

5V / RED

SIG_DET

RESET#

MDC / ORANGE

MDIO / YELLOW

5V / RED

INTERRUPT#

GND / BLACK

KSZ8061 Clock Options

RX_ER Flip Flop

Male MII Connector: Connect to switch or SOC/CPU board.

Put KSZ8061 in normal mode.

Unpower KSZ8081 (remove JP1).

Female MII Connector: Connect back-to-back with another PHY.

5V is supplied to the attached board.

Put KSZ8061 in Back-to-Back mode.

Unpower KSZ8081 (remove JP1).

SIG DET

1. KSZ8061 has a Paddle Ground on bottom side of chip.

Refer to datasheet for mechanical dimensions.

Notes:

CLEAR RX_ER FFLOP

GND

Place this GND test

point on bottom side;

Center and connect to

Paddle Ground of U1.

MII Bus Connection

KSZ8061 to KSZ8081

KSZ8061 to MII Connectors J4, J5

KSZ8061 MII loopback

R1 - R6

Remove

Remove

Install

R11 - R26

Optional

Install

Remove

R211 - R226

Install

Optional

Remove

110 MII Back-to-Back; Auto-MDI/MDI-X enabled

Configuration options for KSZ8061MNX

Y1

25MHzY125MHz

C31

0.1uF

C31

0.1uF

R33 33R33 33

D8

BAV16W-7 SOD-123

D8

BAV16W-7 SOD-123

21

R212 0R212 0

R77

10K

R77

10K

C10

15pF

C10

15pF

R213 0R213 0

R22 0R22 0

R7633 R7633

R53 optR53 opt

R5 Opt/0R5 Opt/0

R81 0R81 0

C11

22pF

C11

22pF

R83 33R83 33

R12 0R12 0

D6

BAV16W-7 SOD-123

D6

BAV16W-7 SOD-123

2 1

R214 0R214 0

R16 0R16 0

R78 4.7KR78 4.7K

R122 10KR122 10K

Y2

25MHzY225MHz

R226 0R226 0

C7

2.2uFC72.2uF

R91 Opt/0R91 Opt/0

R620R62

0

R60 0R60 0

R63 0R63 0

C65

0.1uF

C65

0.1uF

R86 33R86 33

R215 0R215 0

R35 1KR35 1K

D1

BAV16W-7 SOD-123

D1

BAV16W-7 SOD-123

2 1

C12

22pF

C12

22pF

R84 33R84 33

C8

0.1uFC80.1uF

R216 0R216 0

R1 Opt/0R1 Opt/0

C73

0.1uF

C73

0.1uF

R2 Opt/0R2 Opt/0

R15 0R15 0

R11 0R11 0

R6 Opt/0R6 Opt/0

J4

Female MII Connector

J4

Female MII Connector

VCC

1

MDIO

2

MDC

3

RXD3

4

RXD2

5

RXD1

6

RXD0

7

RX_DV

8

RX_CLK

9

RX_ER

10

TX_ER

11

TX_CLK

12

TX_EN

13

TXD0

14

TXD1

15

TXD2

16

TXD3

17

COL

18

CRS

19

VCC

20

VCC

21

NC

22

NC

23

NC

24

NC

25

NC

26

NC

27

NC

28

NC

29

NC

30

NC

31

NC

32

NC

33

NC

34

NC

35

NC

36

NC

37

NC

38

NC

39

VCC

40

R123

220

R123

220

R26 0R26 0

C68

0.1uF

C68

0.1uF

R3 Opt/0R3 Opt/0

R221 0R221 0

R23 0R23 0

R21 0R21 0

R610R61

0

R87 33R87 33

R92 Opt/0R92 Opt/0

TP5TP5

R222 0R222 0

R120

220

R120

220

R36 Opt/4.7KR36 Opt/4.7K

C76

0.1uF

C76

0.1uF

R85 33R85 33

R42 4.7KR42 4.7K

TP6TP6

R20 33R20 33

J7

Header 5x2J7Header 5x2

1

3

5

798

6

4

2

10

R24 0R24 0

R37 Opt/4.7KR37 Opt/4.7K

D10

LED - GREEN SMD

D10

LED - GREEN SMD

21

U1

KSZ8061MNX

U1

KSZ8061MNX

XI

1

XO

2

AVDDH

3

TXP

4

TXM

5

RXP

6

RXM

7

AVDDL

8

VDDL9MDIO10MDC11RXER12RXDV13RXD314VDDIO15RXD2

16

RXD1

17

RXD0

18

RXC

19

TXC

20

TXEN

21

TXD0

22

TXD1

23

LED0/TXER

24

TXD225TXD3

26

CRS

27

RESET#

28

INTRP

29

VDDL30REXT

31

SIGDET

32

PAD_GND

33

D9

BAV16W-7 SOD-123

D9

BAV16W-7 SOD-123

21

R14 0R14 0

R28 33R28 33

R82 33R82 33

R27 33R27 33

R44 Opt/4.7KR44 Opt/4.7K

R51 4.7kR51 4.7k

J5

Male MII Connector

J5

Male MII Connector

VCC

1

MDIO

2

MDC

3

RXD3

4

RXD2

5

RXD1

6

RXD0

7

RX_DV

8

RX_CLK

9

RX_ER

10

TX_ER

11

TX_CLK

12

TX_EN

13

TXD0

14

TXD1

15

TXD2

16

TXD3

17

COL

18

CRS

19

VCC

20

VCC

21

NC

22

NC

23

NC

24

NC

25

NC

26

NC

27

NC

28

NC

29

NC

30

NC

31

NC

32

NC

33

NC

34

NC

35

NC

36

NC

37

NC

38

NC

39

VCC

40

R223 0R223 0

D3

LED - GREEN SMD

D3

LED - GREEN SMD

21

U3

Micrel PL135-27

U3

Micrel PL135-27

XIN

1

CLK1

2

GND3CLK0

4

VDD

5

XOUT

6

S1

SW PUSHBUTTON

S1

SW PUSHBUTTON

1 2

3 4

R121 220R121 220

R224 0R224 0

R41 4.7KR41 4.7K

R88 33R88 33

R47

6.04K

R47

6.04K

S3

SW PUSHBUTTON

S3

SW PUSHBUTTON

1 2

3 4

R4 Opt/0R4 Opt/0

R43 Opt/1KR43 Opt/1K

C3

10uFC310uF

R25 0R25 0 R225 0R225 0

D4

LED - RED SMD

D4

LED - RED SMD

2 1

R40 4.7KR40 4.7K

R90 33R90 33

C9

15pFC915pF

R13 0R13 0

R31 33R31 33

R211 0R211 0

R39 Opt/4.7KR39 Opt/4.7K

U7

74LVC1G175U774LVC1G175

CLK

1

GND

2

D3Q

4

VCC

5

CLR#

6

R38 Opt/4.7KR38 Opt/4.7K

FIGURE A-1: BOARD SCHEMATIC 1 OF 4

KSZ8061MNX Evaluation Board User’s Guide

Page 27

2016 Microchip Technology Inc. DS50002449A-page 27

B

RX-_U1

TX+_U1

TX-_U1

RX+_U1

CMT

RX+_U1

RX-_U1

TX+_U1

TX-_U1

TX+_U1

RX-_U1

TX-_U1

RX+_U1

RXP_U1

RXM_U1

CT_RX1

CT_TX1

CMR

TX_P_U1

RX-_U1

RX+_U1

TX-_U1

TX+_U1

TXP_U1

TXM_U1

RX_M_U1

RX_P_U1

TX_M_U1

CT_TX1

CT_RX1

U1_CHASSIS_GND

EXT_GNDU1_CHASSIS_GND

TXP_U1 (3)

RXP_U1 (3)

TXM_U1 (3)

RXM_U1 (3)

Component placement for this schematic page

will allow for flow thru routing of TX and RX

differential pairs on top PCB layer.

Three connector options are provided.

Only one may be mounted at a time.

The footprints are closely spaced so as to minimize trace stubs.

R58 and R96:

Place one near J1/J2/J3

Place the other nearer L1

These components are optional. They are suggested

only for applications requiring maximum noise immunity.

J2

MQS 4 Pos TE 1379165-1

J2

MQS 4 Pos TE 1379165-1

1

2

3

4

C92

opt

C92

opt

R96 optR96 opt

R59 0R59 0

C16

1uF

C16

1uF

R52 75R52 75

T1

TDK TLA-8T104WLF

T1

TDK TLA-8T104WLF

1

2

3

6

8

7

16

15

14

11

10

9

R50 75R50 75

C93

opt

C93

opt

C94

opt

C94

opt

R32

opt

R32

opt

R49 75R49 75

C90

opt

C90

opt

J1

RJ-45 Jack

J1

RJ-45 Jack

8

7

6

5

4

3

2

1

TH1

TH2

C17

1000pF / 2kV

C17

1000pF / 2kV

R34

opt

R34

opt

R58 optR58 opt

C91

opt

C91

opt

C18

1uF

C18

1uF

L2

TDK ACT45

L2

TDK ACT45

1

2

4

3

L3

TDK ACT45

L3

TDK ACT45

1

2

4

3

R48 75R48 75

516

61

J3

Sumitomo 6098-6793

516

61

J3

Sumitomo 6098-6793

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

FIGURE A-2: BOARD SCHEMATIC 2 OF 4

Schematic and Layouts

Page 28

DS50002449A-page 28 2016 Microchip Technology Inc.

PHY_TXD0

PHY_TXD1

PHY_TXD2

PHY_TXD3

RXD3_P2

RXD1_P2

RXD2_P2

RXD0_P2

PHY_TXC

RXDV_P2

RXC_P2

PHY_RXDV

PHY_RXD0

PHY_RXD1

PHY_RXD2

PHY_RXD3

PHY_RXC

RX+_P2

TX+_P2

RX-_P2

LED0_U2

LED1_U2

TX-_P2

RST#_U2

PHY_TXEN

PHY_TXEN

CRS_U2

PHY_TXD0

LED1_U2

LED0_U2

LED1_U2

LED0_U2

RXER_U2

CRS_U2

RXER_U2

RX+_U2

TX+_U2

TX-_U2

RX-_U2

RX-_U2

TX+_U2

RX+_U2

TX-_U2

MDIO

MDC

PHY_TXD2

PHY_TXD1

3.3V_U2

3.3V_U23.3A_U2

3.3V_U2

3.3A_U2

3.3V_U2

3.3V_U2

U2_CHASSIS_GND

U2_CHASSIS_GND EXT_GND

PHY_TXD3 (3)

PHY_TXEN (3)

PHY_TXD0 (3)

PHY_TXD1 (3)

PHY_TXD2 (3)

PHY_RXD3 (3)

PHY_RXD2 (3)

PHY_RXD1 (3)

PHY_RXD0 (3)

PHY_RXDV (3)

PHY_RXC (3)

PHY_TXC (3)

CLK_U2(3)

MDC (3)

MDIO (3)

(32-QFN)

U2

Push

Button

Reset

1. KSZ8081 has a Paddle Ground on bottom side of chip.

Refer to datasheet for mechanical dimensions.

Notes:

Strapping Options (Refer to datasheet for descriptions)

ISO

CONFIG2

CONFIG1

SPEED

DUPLEX

NWAYEN

LED1

SPEED

LINK/ACT

LED0

110

MII normal mode000

Mode (description)CONFIG[2:0]

MII Back-to-Back

MII Back-to-Back mode is required

when connecting KSZ8061 to KSZ8081.

On this board, the KSZ8081 is never used

in MII normal mode.

LEDs

Place R97 nearer to power connector J8.

FB5 should also be placed nearer to J8 than to J6.

PHYAD1

PHYAD2

GND

Place this GND test

point on bottom side;

Center and connect to

Paddle Ground of U2.

R69 4.7KR69 4.7K

R67 33R67 33

R72 Opt/1KR72 Opt/1K

C63

1uF

C63

1uF

C71

2.2uF

C71

2.2uF

R93 Opt/4.7KR93 Opt/4.7K

R57 75R57 75

R79 220R79 220

S2

SW PUSHBUTTON

S2

SW PUSHBUTTON

1 2

3 4

C69

1uF

C69

1uF

C29

1000pF / 2kV

C29

1000pF / 2kV

U2

KSZ8081MNX

U2

KSZ8081MNX

GND

1

VDD_1.2

2

VDDA_3.3

3

RXM

4

RXP

5

TXM

6

TXP

7

XO

8

XI9REXT10MDIO11MDC12RXD313RXD214RXD115RXD0

16

VDDIO

17

RXDV

18

RXC

19

RXER

20

INTRP

21

TXC

22

TXEN

23

TXD0

24

TXD125TXD226TXD3

27

COL

28

CRS

29

LED030LED1

31

RST#

32

GND

33

R80 220R80 220

R45

6.49K

R45

6.49K

J6

RJ-45 Jack

J6

RJ-45 Jack

8

7

6

5

4

3

2

1

TH1

TH2

R97 optR97 opt

R71 Opt/1KR71 Opt/1K

R75

10K

R75

10K

R54 75R54 75

C21

10uF

C21

10uF

R64 33R64 33

R30 33R30 33

R55 75R55 75

TP7TP7

C22

1uF

C22

1uF

R73 Opt/1KR73 Opt/1K

R29 33R29 33

C23

10uF

C23

10uF

C20

0.1uF

C20

0.1uF

T2

TDK TLA-8T104WLF

T2

TDK TLA-8T104WLF

1

2

3

6

8

7

16

15

14

11

10

9

R74 4.7KR74 4.7K

D5

BAV16W-7 SOD-123

D5

BAV16W-7 SOD-123

2 1

R68 4.7KR68 4.7K

FB5

FBEAD

FB5

FBEAD

1 2

R65 33R65 33

C30

0.1uF

C30

0.1uF

R56 75R56 75

FB7

FBEAD

FB7

FBEAD

12

C26

0.1uF

C26

0.1uF

R66 33R66 33

R70 Opt/4.7KR70 Opt/4.7K

C24

1uF

C24

1uF

D7

LEDx2D7LEDx2

1 2

3 4

FIGURE A-3: BOARD SCHEMATIC 3 OF 4

KSZ8061MNX Evaluation Board User’s Guide

Page 29

2016 Microchip Technology Inc. DS50002449A-page 29

VDDL_EN

3.3V

AVDDH

3.3V VDDIO

3.3V

5.0V

AVDDL

DVDDLVDDL

VDDL3.3V

5.0V 3.3V_U2

5.0V

3.3V VDDL

DC_IN_EXT 5V_HDR

EXT_GND

DC_IN

3.3V 3.3V_U2

3.3V

SIGD (3)

GND

Place GND test points evenly across PCB.

GND GNDGND

KSZ8061 Power

3.3V Power for KSZ8061MNX

VOUT = 1.24 X [ 1 + ( R114 / R115 ) ]

VOUT = 1.25 X [ 1 + ( R112 / R113 ) ]

VDDL Power for KSZ8061MNX

Open: Regulator enabled

Closed: Regulator controlled by SIGD pin of KSZ8061

3.3V Power for Second PHY (KSZ8081MNX)

Jumper

Closed: Second PHY (KSZ8081) is powered

Open: Second PHY is unpowered

3.3V VDDL

2.1mm Power

Jack

VOUT = 1.24 X [ 1 + ( R117 / R118 ) ]

Power source options:

DC_IN_EXT (J26) must be used for EMC testing.

5V_HDR (J44) may be used in non-EMC environment.

DC_IN_EXT:

Nominal: 5V

Maximum: 13V or limited by attached MII board

Jumper

Closed: KSZ8061 is powered

Open: KSZ8061 is unpowered

When using terminal block (3.3V only),

1. Remove JP1 and JP4 to disable LDOs U4 and U5.

2. Install R98.

TP1TP1

C5

2.2uFC52.2uF

D2

LED - RED SMD

D2

LED - RED SMD

21

FB4

FBEAD

FB4

FBEAD

1 2

+

C1

220uF / 50V Elect

+

C1

220uF / 50V Elect

JP4 JUMPERJP4 JUMPER

R115

1.50K

R115

1.50K

FB3

FBEAD

FB3

FBEAD

1 2

C6

1uFC61uF

U6

MIC5305_adj / MQF

U6

MIC5305_adj / MQF

EN

1

GND

2

VIN

3

VOUT

4

ADJ

5

BYP

6

+

C28

10uF Tant

+

C28

10uF Tant

JP1 JUMPERJP1 JUMPER

C25

10uF

C25

10uF

JP2 JUMPERJP2 JUMPER

J8

PWRJACK-TH

J8

PWRJACK-TH

1

3

2

R114

2.49K

R114

2.49K

FB1

FBEAD

FB1

FBEAD

1 2

R94 optR94 opt

+

C15

10uF Tant

+

C15

10uF Tant

JP3

3X1

JP3

3X1

1

2

3

TP3TP3

C56

1uF

C56

1uF

R99

4.7K

R99

4.7K

C60

2.2uF / 50V

C60

2.2uF / 50V

R117

2.49K

R117

2.49K

C54

1uF

C54

1uF

C58

1uF

C58

1uF

U5

MIC29302WU / TO-263-5

U5

MIC29302WU / TO-263-5

EN

1

VIN

2

GND

3

VOUT

4

ADJ

5

R116

220

R116

220

R112

1.50K

R112

1.50K

+

C19

10uF Tant

+

C19

10uF Tant

R46

4.7K

R46

4.7K

U4

MIC29302WU / TO-263-5

U4

MIC29302WU / TO-263-5

EN

1

VIN

2

GND

3

VOUT

4

ADJ

5

R98 optR98 opt

R95 optR95 opt

TP2TP2

R89

4.7K

R89

4.7K

+

C13

10uF Tant

+

C13

10uF Tant

TP12TP12

TP4TP4

J9

Term_Block_2

J9

Term_Block_2

1

2

C2

0.1uFC20.1uF

R113

26.7K

R113

26.7K

+

C84

22uF Tant

+

C84

22uF Tant

L1

TDK ZJYS81L1TDK ZJYS81

124

3

C27

10uF

C27

10uF

TP33TP33

FB2

FBEAD

FB2

FBEAD

1 2

C72

1uF

C72

1uF

C77

2.2uF / 50V

C77

2.2uF / 50V

C81

1uF

C81

1uF

+

C14

10uF Tant

+

C14

10uF Tant

R118

1.50K

R118

1.50K

+

C85

22uF Tant

+

C85

22uF Tant

C83

1uF

C83

1uF

FIGURE A-4: BOARD SCHEMATIC 4 OF 4

Schematic and Layouts

Page 30

KSZ8061MNX Evaluation Board User’s Guide

NOTES:

DS50002449A-page 30 2016 Microchip Technology Inc.

Page 31

KSZ8061MNX EVALUATION

BOARD USER’S GUIDE

Appendix B. Bill of Materials (BOM)

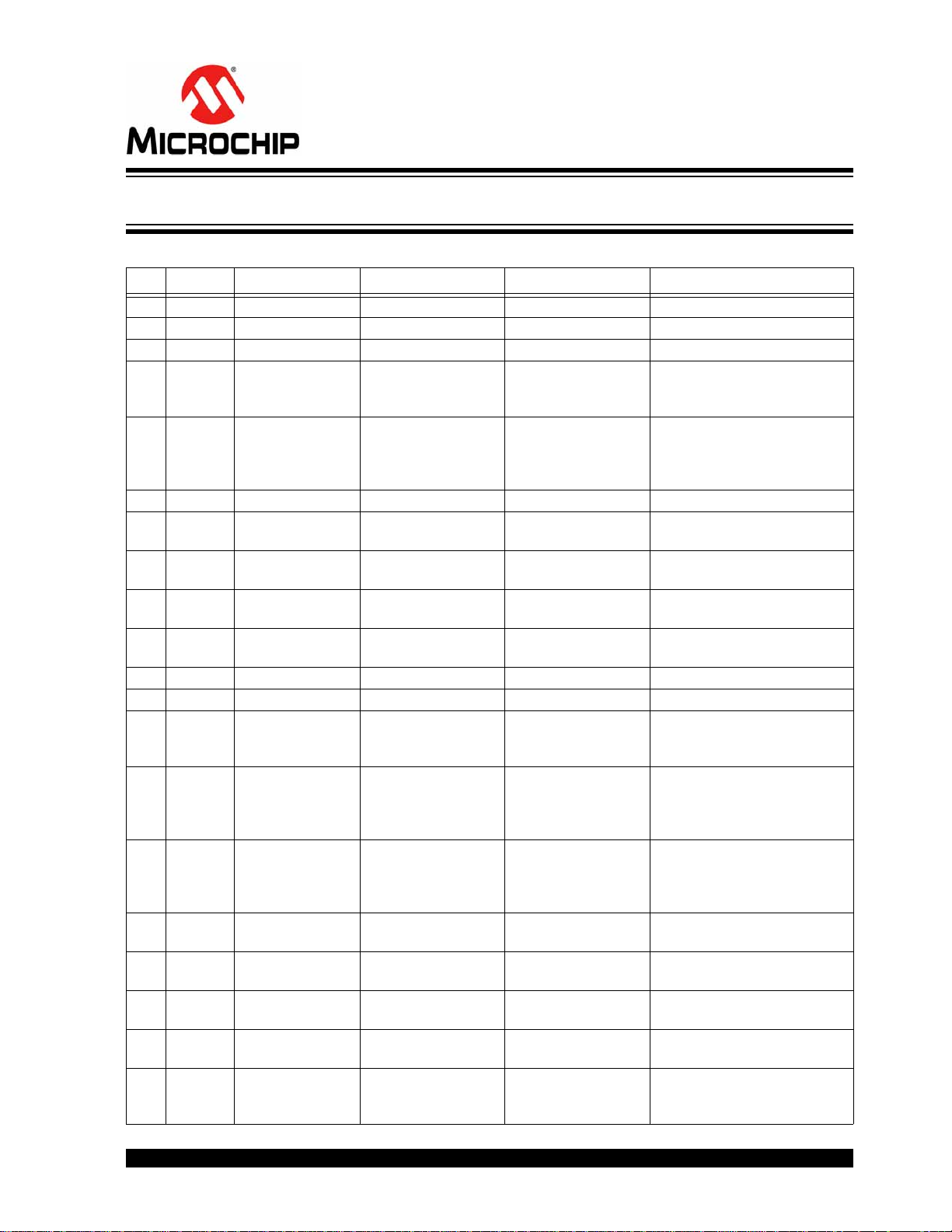

TABLE B-1: BILL OF MATERIALS (BOM)

Item Quantity Reference Description Footprint/Package Manufacturer/Part Number

1 2 C9, C10 15 pF 0603

2 2 C11, C12 22 pF 0603

3 2 C17, C29 1000 pF/2 kV Radial lead, thru hole Vishay S102K33Y5PP63K5R

4 10 C2, C8, C20, C26,

C30, C31, C6 5 ,

C68, C73, C7 6

5 11 C6, C22, C2 4,

C54, C56, C5 8 ,

C63, C69, C7 2 ,

C81, C83

6 2 C16, C18 1 uF 0805

7 3 C5, C7, C71 2.2 uF/10V, ceramic

8 2 C60, C77 2.2 uF/50V, ceramic

9 5 C3, C21, C23,

C25, C27

10 5 C13, C14, C15,

C19, C28

11 2 C84, C85 22 uF Tant 1210 (3528 metric) AVX TAJB226K016RNJ

12 1 C1 220 uF/50V Elect Al Electrolytic Panasonic ECA-1HM221

13 DNI 8 R32, R34, R53,

C90, C91, C9 2 ,

C93, C94

14 3 D1, D5, D6, D8, D9Diode SOD-123 Diodes Inc BAV16W-7

15 DNI 2 D8, D9 Diode SOD-123 Diodes Inc BAV16W-7

16 1 D2 LED - RED SMD LED 0805 Lite-On LTST-C170CKT

17 DNI 1 D4 LED - RED SMD LED 0805 Lite-On LTST-C170CKT

18 1 D3 LED - GREEN SMD LED 0805 Lite-On LTST-C171GKT

19 DNI 1 D10 LED - GREEN SMD LED 0805 Lite-On LTST-C171GKT

20 1 D7 LED, green, stacked

0.1 uF 0402

1 uF 0603

0603 TDK C1608X5R1A225K080AC

0603

1206 Taiyo Yuden

1206

10 uF/10V, ceramic

0805

10 uF Tant 1210 (3528 metric)

opt 0603

pair, right angle, thru

hole

0805 TDK C2012X5R1A106K125AB

Dual LED (thru hole) Lumex SSF-LXH240GGD

UMK316BJ225KD-T

Diodes Inc 1N4148W-7

Micro Commercial

1N4148W-TP

Diodes Inc 1N4148W-7

Micro Commercial

1N4148W-TP

Lumex SML-LXT0805IW -TR

Lumex SML-LXT0805IW -TR

Lumex SML-LX0805SGC-TR

Lumex SML-LX0805SGC-TR

Dialight 553-0122-300F

2016 Microchip Technology Inc. DS50002449A-page 31

Page 32

MCP9600 Thermocouple IC Evaluation Board User’s Guide

TABLE B-1: BILL OF MATERIALS (BOM) (CONTINUED)

Item Quantity Reference Description Footprint/Package Manufacturer/Part Number

21 7 FB1, FB2, FB3,

FB4, FB5, FB7,

R59

22 3 JP1, JP2, JP4 JUMPER Header 2x1, standard 25 mil header pins, 100 mil pitch

23 1 JP3 3X1 Header 3x1, standard 25 mil header pins, 100 mil pitch

24 1 J6 RJ-45 Ja ck RJ45-4P TE 5558342-1

25 DNI 1 J1 RJ-45 Jack RJ45-4P TE 5558342-1

26 DNI 1 J2 MQS 4 Pos TE

27 DNI 1 J3 Sumitomo 6098-6793 6098-6793 Sumitomo 6098-6793

28 DNI 1 J4 Female MII Connec-

29 1 J5 Male MII Connector,

30 1 J7 Header 5x2 HDR 5x2, standard

31 1 J8 DC power connector,

32 DNI 1 J9 Terminal block, 2 term Thru hole Phoenix 1984617

33 1 L1 TDK ZJYS81 ZJYS81 TDK ZJYS81R5

34 2 L2, L3 Common mo de

35 DNI 9 R1, R2, R3, R4,

R5, R6, R6 0, R9 1,

R92

36 26 R11, R12, R13,

R14, R15, R1 6 ,

R21, R22, R2 3 ,

R24, R25, R2 6 ,

R62, R81, R2 11,

R212, R213,

R214, R215,

R216, R221,

R222, R223,

R224, R225, R226

37 14 R20, R29, R30,

R64, R65, R6 6 ,

R67, R82, R8 3 ,

R84, R85, R8 6 ,

R87, R88

38 1 R35 1K 0603

39 DNI 7 R36, R37, R38,

R39, R44, R7 0 ,

R93

40 1 1 R40, R41, R42,

R46, R51, R6 8 ,

R69, R74, R7 8 ,

R89, R99

41 DNI 4 R43, R71, R72,

R73

42 1 R45 6.49K 0603

Ferrite bead, 150

ohms at 600 MHz

1379165-1

tor, SCSI-2, 40-pin

SCSI-2, 40-pin

barrel, 2.1 mm

choke for signals

Opt/0 0603

0 0603

33 0402

Opt/4.7K 0603

4.7K 0603

Opt/1K 0603

3216 metric Steward/Laird

1379165 TE 1379165-1

Thru hole TE 5787170-4

PCB edge mount Goal Ray Industry Co. Ltd

25mil header pins,

100mil pitch

Thru hole CUI PJ-002A

4532 metric 4ld TDK ACT45B-101-2P

HI1206N101R-10

MDS-40MM-3-C2

FCI 67997-410HLF

Switchcraft RAPC722X

DS50002449A-page 32 2016 Microchip Technology Inc.

Page 33

TABLE B-1: BILL OF MATERIALS (BOM) (CONTINUED)

Item Quantity Reference Description Footprint/Package Manufacturer/Part Number

43 1 R47 12.1K 0603

44 8 R48, R49, R50,

R52, R54, R5 5 ,

R56, R57

45 DNI 6 R58, R94, R95,

R96, R97, R9 8

46 1 R63 0 1206

47 DNI 1 R61 0 1206

48 2 R75, R77 10K 0603

49 DNI 1 R122 10K 0603

50 6 R27, R28, R31,

R33, R76, R9 0

51 4 R79, R80, R116,

R120

52 DNI 2 R121, R123 220 0603

53 3 R112, R115, R118 1.50K, 1% 0603

54 1 R113 26.7K, 1% 0603

55 2 R114, R117 2.49K 0603

56 2 S1, S2 SW PUSHBUTTON Switch (push button) Panasonic EVQ-Q2Y03W

57 DNI 1 S3 SW PUSHBUTTON Switch (push button) Panasonic EVQ-Q2Y03W

58 DNI 7 TP1, TP2, TP3,

TP4, TP5, TP12,

TP33

59 DNI 2 TP6, TP7 TestPoint 60 mil hole at U1 and

60 2 T1, T2 TDK TLA-8T104WLF SOIC16 TDK TLA-8T104WLF

61 1 U1 KSZ8061MNX 32-QFN Microchip KSZ8061MNX

62 1 U2 KSZ8061MNX 32-QFN Microchip KSZ8061MNX

63 1 U3 Microchip PL135-27

64 2 U4, U5 MIC29 302WU adj. 3A

65 1 U6 MIC5305YML adj.

66 DNI 1 U7 74LVC1G175 single

67 1 Y1 25 MHz 5x3.2 mm, 2-ld TXC 7A-25.000MAAE

68 1 Y2 25 MHz HC-49/SMD ECS ECS-250-18-5PX-F

75 0603

Opt 1206

33 0603

220 0603

TestPoint Hole for standard 25

mil square header

pins

U2 center ground

pads

Pulse H1102NL

DFN-6L Microchip PL135-27

oscillator 1:2 fanout

buffer

TO-263-5 Microchip MIC29302WU

LDO

6-pin 2x2 mm MLF Micrel MIC5305YML

150 mA LDO

SC70 TI SN74LVC1G175DCK

flip flop w/ async clear

NDK NX5032GA

CTS 445C23 L25M00000

TXC AA-25.000MAGE

Abracon

ABLS-25.000MHZ-B4-F-T

TXC 9C-25.000MAAJ-T

ILSI

HC49USM-FB1F18-25.000

2016 Microchip Technology Inc. DS50002449A-page 33

Page 34

Worldwide Sales and Service

AMERICAS

Corporate Office

2355 West Chandler Blvd.

Chandler, AZ 85224-6199

Tel: 480-792-7200

Fax: 480-792-7277

Te chn ica l Support:

http://www.microchip.com/

support

Web Address:

www.microchip.com

Atlanta

Duluth, GA

Tel: 678-957-9614

Fax: 678-957-1455

Austin, TX

Tel: 512-257-3370

Boston

Westborough, MA

Tel: 774-760-0087

Fax: 774-760-0088

Chicago

Itasca, IL

Tel: 630-285-0071

Fax: 630-285-0075

Cleveland

Independence, OH

Tel: 216-447-0464

Fax: 216-447-0643

Dallas

Addison, TX

Tel: 972-818-7423

Fax: 972-818-2924

Detroit

Novi, MI

Tel: 248-848-4000

Houston, TX

Tel: 281-894-5983

Indianapolis

Noblesville, IN

Tel: 317-773-8323

Fax: 317-773-5453

Los Angeles

Mission Viejo, CA

Tel: 949-462-9523

Fax: 949-462-9608

New Yor k , NY

Tel: 631-435-6000

San Jose, CA

Tel: 408-735-9110

Canada - Toronto

Tel: 905-673-0699

Fax: 905-673-6509

ASIA/PACIFIC

Asia Pacific Office

Suites 3707-14, 37th Floor

Tower 6, The Gateway

Harbour City, Kowloon

Hong Kong

Tel: 852-2943-5100

Fax: 852-2401-3431

Australia - Sydney

Tel: 61-2-9868-6733

Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000

Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511

Fax: 86-28-8665-7889

China - Chongqing

Tel: 86-23-8980-9588

Fax: 86-23-8980-9500

China - Dongguan

Tel: 86-769-8702-9880

China - Hangzhou

Tel: 86-571-8792-8115

Fax: 86-571-8792-8116

China - Hong Kong SAR

Tel: 852-2943-5100

Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460

Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355

Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533

Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829

Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8864-2200

Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300

Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252

Fax: 86-29-8833-7256

ASIA/PACIFIC

China - Xiamen

Tel: 86-592-2388138

Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040

Fax: 86-756-3210049

India - Bangalore

Tel: 91-80-3090-4444

Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631

Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-3019-1500

Japan - Osaka

Tel: 81-6-6152-7160

Fax: 81-6-6152-9310

Japan - Tokyo

Tel: 81-3-6880- 3770

Fax: 81-3-6880-3771

Korea - Daegu

Tel: 82-53-744-4301

Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200

Fax: 82-2-558-5932 or

82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857

Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870

Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065

Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870

Fax: 65-6334-8850

Tai wan - Hsin Chu

Tel: 886-3-5778-366

Fax: 886-3-5770-955

Taiwan - Kaohsiung

Tel: 886-7-213-7828

Taiwan - Taipei

Tel: 886-2-2508-8600

Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351

Fax: 66-2-694-1350

EUROPE

Austria - Wels

Tel: 43-7242-2244-39

Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828

Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Dusseldorf

Tel: 49-2129-3766400

Germany - Karlsruhe

Tel: 49-721-625370

Germany - Munich

Tel: 49-89-627-144-0

Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611

Fax: 39-0331-466781

Italy - Venice

Tel: 39-049-7625286

Netherlands - Drunen

Tel: 31-416-690399

Fax: 31-416-690340

Poland - Wars a w

Tel: 48-22-3325737

Spain - Madrid

Tel: 34-91-708-08-90

Fax: 34-91-708-08-91

Sweden - Stockholm

Tel: 46-8-5090-4654

UK - Wokingham

Tel: 44-118-921-5800

Fax: 44-118-921-5820

07/14/15

DS50002449A-page 34 2016 Microchip Technology Inc.

Loading...

Loading...