Page 1

dsPIC33CH Curiosity

Development Board

User’s Guide

2018 Microchip Technology Inc.

Advance Information

DS50002762A

Page 2

Note the following details of the code protection feature on Microchip devices:

YSTEM

CERTIFIED BY DNV

== ISO/TS 16949 ==

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device

applications and the like is provided only for your convenience

and may be superseded by updates. It is your responsibility to

ensure that your application meets with your specifications.

MICROCHIP MAKES NO REPRESENTATIONS OR

WARRANTIES OF ANY KIND WHETHER EXPRESS OR

IMPLIED, WRITTEN OR ORAL, STATUTORY OR

OTHERWISE, RELATED TO THE INFORMATION,

INCLUDING BUT NOT LIMITED TO ITS CONDITION,

QUALITY, PERFORMANCE, MERCHANTABILITY OR

FITNESS FOR PURPOSE. Microchip disclaims all liability

arising from this information and its use. Use of Microchip

devices in life support and/or safety applications is entirely at

the buyer’s risk, and the buyer agrees to defend, indemnify and

hold harmless Microchip from any and all damages, claims,

suits, or expenses resulting from such use. No licenses are

conveyed, implicitly or otherwise, under any Microchip

intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide

headquarters, design and wafer fabrication facilities in Chandler and

Tempe, Arizona; Gresham, Oregon and design centers in California

and India. The Company’s quality system processes and procedures

are for its PIC

devices, Serial EEPROMs, microperipherals, nonvolatile memory and

analog products. In addition, Microchip’s quality system for the design

and manufacture of development systems is ISO 9001:2000 certified.

®

MCUs and dsPIC® DSCs, KEEL

®

OQ

code hopping

QUALITY MANAGEMENT S

Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, AVR,

AVR logo, AVR Freaks, BeaconThings, BitCloud, CryptoMemory,

CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, K

EELOQ

logo, Kleer, LANCheck, LINK MD, maXStylus,

K

maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB,

OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip

Designer, QTouch, RightTouch, SAM-BA, SpyNIC, SST, SST

Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered

trademarks of Microchip Technology Incorporated in the U.S.A.

and other countries.

ClockWorks, The Embedded Control Solutions Company,

EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS,

mTouch, Precision Edge, and Quiet-Wire are registered

trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any

Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo,

CodeGuard, CryptoAuthentication, CryptoCompanion,

CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average

Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial

Programming, ICSP, Inter-Chip Connectivity, JitterBlocker,

KleerNet, KleerNet logo, Mindi, MiWi, motorBench, MPASM, MPF,

MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach,

Omniscient Code Generation, PICDEM, PICDEM.net, PICkit,

PICtail, PureSilicon, QMatrix, RightTouch logo, REAL ICE, Ripple

Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI,

SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC,

USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and

ZENA are trademarks of Microchip Technology Incorporated in the

U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in

the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip

Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology

Germany II GmbH & Co. KG, a subsidiary of Microchip Technology

Inc., in other countries.

All other trademarks mentioned herein are property of their

respective companies.

© 2018, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-3181-7

EELOQ

,

DS50002762A-page 2

Advance Information

2018 Microchip Technology Inc.

Page 3

dsPIC33CH CURIOSITY DEVELOPMENT

BOARD USER’S GUIDE

Table of Contents

Preface ...........................................................................................................................5

Chapter 1. Introduction................................................................................................11

1.1 Schematics and Bill of Materials (BOM) ....................................................... 12

Chapter 2. Hardware....................................................................................................13

2.1 Powering the Board ...................................................................................... 13

2.1.1 USB Power ................................................................................................ 13

2.1.2 External Power .......................................................................................... 13

2.2 Using the Programmed Demo Firmware ...................................................... 14

2.3 Reprogramming and Debugging the dsPIC33CH128MP508 Device (U1) ...... 14

2.4 Using the Isolated USB-UART Interface ...................................................... 15

2.5 Circuit Details ............................................................................................... 15

2.5.1 Jumpers/Headers/Connectors ................................................................... 15

2.5.2 SMPS Hardware Overcurrent Protection ................................................... 16

2.5.3 SMPS Hardware Overvoltage Protection .................................................. 17

2.5.4 PWM DAC/DC Bias Generator .................................................................. 17

2.5.5 Transient Load Tester Circuit .................................................................... 18

2.6 Low-Side Current Sensing ........................................................................... 19

2.7 High-Side Current Sensing ........................................................................... 20

Appendix A. Schematics.............................................................................................21

Appendix B. Bill of Materials.......................................................................................27

Worldwide Sales and Service ....................................................................................30

2018 Microchip Technology Inc.

Advance Information

DS50000000A-page 3

Page 4

dsPIC33CH Curiosity Development Board User’s Guide

NOTES:

DS50000000A-page 4

Advance Information

2018 Microchip Technology Inc.

Page 5

dsPIC33CH CURIOSITY DEVELOPMENT

BOARD USER’S GUIDE

Preface

NOTICE TO CUSTOMERS

All documentation becomes dated, and this manual is no exception. Microchip tools and

documentation are const antly evolving to meet customer needs, so some actual dialogs and/

or tool descriptions may differ from those in this document. Please refer to our website

(www.microchip.com) to obtain the latest documentation available.

Documents are identified with a “DS” number. This number is located on the bottom of each

page, in front of the page number. The numbering convention for the DS number is

“DSXXXXXXXXA”, where “XXXXXXXX” is the document number and “A” is the revision level

of the document.

For the most up-to-date information on development tools, see the MPLAB

Select the Help menu, and then Topics to open a list of available on-line help files.

INTRODUCTION

®

IDE on-line help.

This preface contains general information that will be useful to know before using the

dsPIC33CH Curiosity Development Board. Topics discussed in this preface include:

• Document Layout

• Conventions Used in this Guide

• Recommended Reading

• Recommended Reading

• The Microchip WebSite

• Development Systems Customer Change Notification Service

• Customer Support

• Document Revision History

DOCUMENT LAYOUT

This user’s guide provides an overview of the dsPIC33CH Curiosity Development

Board. The document is organized as follows:

• Chapter 1. “Introduction” – This chapter introduces the dsPIC33CH Curiosity

Development Board and provides a brief overview of its features.

• Chapter 2. “Hardwa re ” – This chapter describes some of the noteworthy

hardware features of the board.

• Appendix A. “Schematics” – This appendix provides schematic diagrams for

the dsPIC33CH Curiosity Development Board.

• Appendix B. “Bill of Materials (BOM)” – This appendix provides the component

list used in assembling the board.

2018 Microchip Technology Inc.

Advance Information

DS50002762A-page 5

Page 6

dsPIC33CH Curiosity Development Board User’s Guide

CONVENTIONS USED IN THIS GUIDE

This manual uses the following documentation conventions:

DOCUMENTATION CONVENTIONS

Description Represents Examples

Arial font:

Italic characters Referenced books MPLAB

Emphasized text ...is the only compiler...

Initial caps A window the Output window

A dialog the Settings dialog

A menu selection select Enable Programmer

Quotes A field name in a window or

dialog

Underlined, italic text with

right angle bracket

Bold characters A dialog button Click OK

N‘Rnnnn A number in verilog format,

Text in angle brackets < > A key on the keyboard Press <Enter>, <F1>

Courier New font:

Plain Courier New Sample source code #define START

Italic Courier New A variable argument file.o, where file can be

Square brackets [ ] Optional arguments mcc18 [options] file

Curly braces and pipe

character: { | }

Ellipses... Replaces repeated text var_name [,

A menu path File>Save

A tab Click the Power tab

where N is the total number of

digits, R is the radix and n is a

digit.

Filenames autoexec.bat

File paths c:\mcc18\h

Keywords _asm, _endasm, static

Command-line options -Opa+, -Opa-

Bit values 0, 1

Constants 0xFF, ‘A’

Choice of mutually exclusive

arguments; an OR selection

Represents code supplied by

user

“Save project before build”

4‘b0010, 2‘hF1

any valid filename

[options]

errorlevel {0|1}

var_name...]

void main (void)

{ ...

}

®

IDE User’s Guide

DS50002762A-page 6

Advance Information

2018 Microchip Technology Inc.

Page 7

RECOMMENDED READING

This user’s guide describes how to use the dsPIC33CH Curiosity Development Board.

The device-specific data sheets contain current information on programming the specific

microcontroller or Digital Signal Controller (DSC) devices. The following Microchip

documents are available and recommended as supplemental reference resources:

MPLAB® XC16 C Compiler User’s Guide (DS50002071)

This comprehensive guide describes the usage, operation and features of Microchip’s

MPLAB XC16 C compiler (formerly MPLAB C30) for use with 16-bit devices.

MPLAB® X IDE User’s Guide (DS50002027)

This document describes how to set up the MPLAB X IDE software and use it to create

projects and program devices.

dsPIC33CH128MP508 Family Data Sheet (DS70005319)

Refer to this document for detailed information on the dsPIC33CH Dual Core Digital

Signal Controllers (DSCs). Reference information found in this data sheet includes:

• Device memory maps

• Device pinout and packaging details

• Device electrical specifications

• List of peripherals included on the devices

Preface

dsPIC33/PIC24 Family Reference Manual Sections

Family Reference Manual (FRM) sections are available, which explain the operation of

the dsPIC

each device family are discussed in the individual family’s device data sheet.

®

DSC MCU family architecture and peripheral modules. The specifics of

2018 Microchip Technology Inc.

Advance Information

DS50002762A-page 7

Page 8

dsPIC33CH Curiosity Development Board User’s Guide

THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website

is used as a means to make files and information easily available to customers.

Accessible by using your favorite Internet browser, the website contains the following

information:

• Product Support – Data sheets and errata, application notes and sample

programs, design resources, user’s guides and hardware support documents,

latest software releases and archived software

• General Technical Support – Frequently Asked Questions (FAQs), technical

support requests, online discussion groups, Microchip consultant program

member listing

• Business of Microchip – Product selector and ordering guides, latest Microchip

press releases, listing of seminars and events, listings of Microchip sales offices,

distributors and factory representatives

DEVELOPMENT SYSTEMS CUSTOMER CHANGE NOTIFI CATION SERVICE

Microchip’s customer notification service helps keep customers current on Microchip

products. Subscribers will receive e-mail notification whenever there are changes,

updates, revisions or errata related to a specified product family or development tool of

interest.

To register, access the Microchip website at www.microchip.com, click on Customer

Change Notification and follow the registration instructions.

The Development Systems product group categories are:

• Compilers – The latest information on Microchip C compilers and other language

tools. These include the MPLAB

assemblers; MPLINK™ and MPLAB 16-bit object linkers; and MPLIB™ and

MPLAB 16-bit object librarians.

• Emulators – The latest information on the Microchip MPLAB REAL ICE™

in-circuit emulator.

• In-Circuit Debuggers – The latest information on the Microchip in-circuit

debugger, MPLAB ICD 4.

• MPLAB X IDE – The latest information on Microchip MPLAB X IDE, the

Windows

This list is focused on the MPLAB X IDE, MPLAB SIM simulator, MPLAB X IDE

Project Manager and general editing and debugging features.

• Programmers – The latest information on Microchip programmers. These include

the MPLAB PM3 device programmer and the PICkit™ 3 development

programmers.

®

Integrated Development Environment for development systems tools.

®

C compiler; MPASM™ and MPLAB 16-bit

DS50002762A-page 8

Advance Information

2018 Microchip Technology Inc.

Page 9

CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

• Distributor or Representative

• Local Sales Office

• Field Application Engineer (FAE)

• Technical Support

Customers should contact their distributor, representative or field application engineer

(FAE) for support. Local sales offices are also available to help customers. A listing of

sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://support.microchip.com

DOCUMENT REVISION HISTORY

Revision A (June 2018)

This is the initial released version of this document.

Preface

2018 Microchip Technology Inc.

Advance Information

DS50002762A-page 9

Page 10

dsPIC33CH Curiosity Development Board User’s Guide

NOTES:

DS50002762A-page 10

Advance Information

2018 Microchip Technology Inc.

Page 11

dsPIC33CH CURIOSITY DEVELOPMENT

3

5

14

13

11

6

10

10

1

5

4

8

7

9

2

12

BOARD USER’S GUIDE

Chapter 1. Introduction

The dsPIC33CH Curiosity Development Board (DM330028) is intended as a

cost-effective development and demonstration platform for the dsPIC33CH128MP508

family of dual core, high-performance Digital Signal Controllers. Some of the board

hardware features are highlighted in Figure 1-1.

FIGURE 1-1: dsPIC33CH CURIOSITY DEVELOPMENT BOARD

Hardware Features:

1. dsPIC33CH128MP508 dual core, 16-bit DSP target device.

2. Integrated PICkit™-On-Board (PKOB) programmer/debugger.

3. 2x mikroBUS™ interfaces for hardware expansion, compatible with a wide range

of existing click boards™ from MikroElektronika (www.mikroe.com).

4. 1x Red/Green/Blue (RGB) LED.

5. 2x general purpose red indicator LEDs.

6. 3x general purpose push buttons.

7. 1x MCLR

8. 10k potentiometer.

9. Galvanically isolated USB-UART interface, capable of up to 460,800 baud.

10. Female, 100 mil pitch, I/O pin access headers for probing and connecting to all

target microcontroller GPIO pins.

11. Configurable Switch Mode Power Supply (SMPS) test circuit that can be

operated in Buck, Boost, or Buck-Boost modes, using either Voltage mode or

Peak Current mode control.

12. Converter output voltage screw terminal.

13. Configurable load step transient generator.

14. General purpose through-hole and SMT prototyping area.

Reset push button.

2018 Microchip Technology Inc.

Advance Information

DS50002762A-page 11

Page 12

dsPIC33CH Curiosity Development Board User’s Guide

1.1 SCHEMATICS AND BILL OF MATERIALS (BOM)

Schematics and the BOM for the dsPIC33CH Curiosity Development Board are located in

Appendix A. “Schematics” and Appendix B. “Bill of Materials (BOM)”, respectively.

DS50002762A-page 12

Advance Information

2018 Microchip Technology Inc.

Page 13

dsPIC33CH CURIOSITY DEVELOPMENT

Chapter 2. Hardware

2.1 POWERING THE BOARD

2.1.1 USB Power

The board is intended to be primarily powered from the PKOB USB micro-B connector

J20. Power is not sourced through USB connector J16, as it is part of the isolated

USB-UART interface. The official “USB 2.0 Specification” restricts USB applications to

consuming no more than 500 mA of USB V

rated for 500 mA to enforce the USB current restrictions and to help protect the board,

or host, from damage in the event of unintended short circuits or SMPS output

overloads.

When operating the board from USB power, approximately 300 mA of V

available to the SMPS circuit, as about 200 mA of the total should be reserved for use

by the other non-SMPS circuitry on the board (ex: primarily U1, U4, U11, R17,

LED5, etc.).

2.1.2 External Power

BOARD USER’S GUIDE

BUS

power from the host. Polyfuse TH1 is

BUS

current is

An external DC wall cube may optionally be connected if a DC barrel jack is installed

in the unpopulated footprint J17. If an external wall cube is used, it should be well

regulated and rated for 5.0V, ≤1.5A, with center pin positive. Compared to operating

from USB power, powering the board with an external wall cube enables more power

to be sourced by the SMPS circuit on the board. It is not necessary to use an external

power supply for standard operation at lower current levels (e.g., SMPS circuit output

load power of about <1.2W).

When the board is powered through J17, the polyfuse TH1 is bypassed, and therefore,

it is recommended to use a wall cube with internal short circuit and overload protection

(≤1.5A) to minimize the risk of circuit damage in the event of unintended short circuits.

Additionally, if an external wall cube is used, it is recommended to cut a trace (NT2 on

the top of the PCB) and populate D1 with a ≥1A rated Schottky diode (SOD-123). This

will prevent any USB V

into the attached host via J20. USB V

destructive (when limited in current level), but are a USB compliance violation. They

can interfere with the host operation, especially when the host is unpowered. This

scenario can be avoided, however, via D1.

BUS

“backdrive” current from flowing out of the wall cube and

BUS

backdrive currents may not necessarily be

2018 Microchip Technology Inc.

Advance Information

DS50002762A-page 13

Page 14

dsPIC33CH Curiosity Development Board User’s Guide

2.2 USING THE PROGRAMMED DEMO FIRMWARE

The development board comes programmed with some basic demo firmware, which

exercises several of the board hardware features. For details on how to use the

programmed demo firmware, please refer to the documentation associated with the

source code for the demo, which can be obtained from:

www.microchip.com/dspic33chcuriosity

2.3 REPROGRAMMING AND DEBUGGING THE dsPIC33CH128MP508 DEVICE (U1)

The board has a PICkit-On-Board (PKOB) programmer/debugger circuit, which can be

used to program and debug both the Master and Slave cores in the dsPIC33CH128MP508

target device (U1). Alternatively, an external programmer/debugger tool can be connected

to the board via the 6-pin inline connector J2, using a male-male 100 mil pitch 6-pin header.

During simultaneous “dual debug” of both the Master and Slave cores, two debugger

tools are required. During simultaneous dual debug operation, the PKOB circuit can be

used to debug the Master core, while an external programmer/debugger tool should be

connected via the 6-pin 100 mil pitch connector J15 using a male-male header. Two

programmer/debugger tools are only required when performing dual core simultaneous

debug operations. When programming or debugging only a single core (either Master

or Slave) at a time, the on-board PKOB circuit is sufficient.

The PKOB circuit should automatically enumerate and be recognized by the

MPLAB

the USB micro-B connector J20. No custom USB driver installation is necessary as the

PKOB circuit relies on standard OS provided HID drivers, and therefore, driver installation should be fully automatic. When plugged in, the PKOB programmer/debugger

tool can be selected from the MPLAB X project properties page by selecting the device

under: Hardware Tools>Microchip Starter Kits>Starter Kits (PKOB)>dsPIC33CH

Curio…, as shown in Figure 2-1.

®

X IDE v4.10 or later, when the Curiosity Board is connected to the host via

FIGURE 2-1: dsPIC33CH CURIOSITY PKOB TOOL SELECTION

DS50002762A-page 14

Advance Information

2018 Microchip Technology Inc.

Page 15

2.4 USING THE ISOLATED USB-UART INTERFACE

The board implements a galvanically isolated USB-UART interface based around the

MCP2221A chip. The MCP2221A implements the standard Communication Device

Class (CDC) – Abstract Control Model (ACM) protocol, and therefore, can use standard

USB drivers that are provided with modern Windows

systems. Under most operating systems, the USB driver installation will be fully automatic. Under certain older operating systems, or if the device is attached to an older than

Windows 10 machine without an active internet connection, manual installation of the

drivers may be necessary. In this case, the driver package can be downloaded from:

www.microchip.com/mcp2221a

Details on how to access the serial port from Mac and Linux operating systems can also

be found in the associated collateral for the MCP2221A. Under Windows, after

successful USB driver installation, the device will appear as a “COMx” port object,

which standard serial terminal programs can open/read/write to and from.

2.5 CIRCUIT DETAILS

Some of the circuit blocks in the schematics may not have immediately obvious

purpose or method of operation. This section highlights some of these circuit elements

and provides an explanation for their intent and function.

Hardware

®

, Mac® and Linux® operating

2.5.1 Jumpers/Headers/Connectors

J1 – This is an unpopulated 2-pin, 100 mil jumper header, which may optionally be used

to insert a current meter in series with the U1 V

controller current consumption. In order to measure the U1 current, the trace on the

bottom of the PCB, that shorts the two pins of J1, should be cut and a 2-pin jumper

should be soldered into J1.

J2 – This is an unpopulated 6-pin staggered header interface, which can optionally be

used to connect an external programmer/debugger tool to the target microcontroller

U1. Ordinarily, it is not necessary to use J2, since the integrated programmer/debugger

(PKOB) circuit connects to the same U1 program/debug interface pins.

J3 – This is a female header that implements the mikroBUS Interface A, which can be

used to attach hardware daughter boards to expand the functionality of the

development board.

J8 – This is a female header that implements the mikroBUS Interface B, which can be

used to attach hardware daughter boards to expand the functionality of the

development board.

J10 – This jumper sets the -3 dB low-pass filter breakpoint frequency of the RC

network, composed of R54 + C26/C41. When the jumper is open, the low-pass filter

frequency is around 15.9 kHz, but with the jumper capped, it is around 1.4 kHz. When

a sufficiently high-frequency PWM waveform is generated on RC5, the low-pass filter

can smooth it into a near DC value, which is buffered by op amp U8, providing a

software controlled DAC capability.

J11 – This is a female I/O pin access header used for accessing the U1 microcontroller

I/O pins.

J12 – This is a female I/O pin access header used for accessing the U1 microcontroller

I/O pins.

DD

current path to measure the micro-

2018 Microchip Technology Inc.

Advance Information

DS50002762A-page 15

Page 16

dsPIC33CH Curiosity Development Board User’s Guide

J13 – This jumper sets the effective resistor divider feedback ratio for the SMPS output

voltage when it is measured by the U1 ADC. When the SMPS is used to generate relatively low voltages (ex: 0V-6.5V), it is suggested to keep J13 capped to maximize

feedback circuit sensitivity. When the SMPS will be used to generate voltages above

6.5V, J13 should be opened to ensure the feedback voltage stays within the input

sensing range of the ADC.

J14 – This is an unpopulated 2-pin jumper location that can be used to disconnect the

SMPS transient generator circuitry from the output of the SMPS circuit. In order to

disconnect the transient generator circuit, it is suggested to populate J14 with a 2-pin

jumper header and to cut the trace (NT5) on the bottom of the PCB linking the pins

of J14.

J15 – This is an unpopulated 6-pin staggered header interface that can optionally be

used to connect an external programmer/debugger tool to the target microcontroller U1

when performing dual simultaneous debug of both the Master and Slave cores. The

J15 header connects to the Slave debug port, S1PGx3, and is only intended for use

during dual debug operations. For single core debug of either the Master or Slave,

either J2 or the PKOB circuit should be used. The holes for J15 are slightly staggered,

which provides some friction retention force, without requiring physical soldering, when

a straight male-male or right angle male-male header is installed in J15.

J16 – This is a standard female USB micro-B connector, which connects to the

MCP2221A USB-UART converter chip. This USB interface is a data interface only, as

it is galvanically isolated from the rest of the application circuitry and does not supply

power to the rest of the board.

J17 – This is an unpopulated footprint that may optionally be used to install a standard

DC barrel jack for externally powering the board from a regulated 5.0V wall cube.

J18 – This is a female I/O pin access header for accessing certain U1 microcontroller

I/O pins, along with the various power rails implemented on the development board.

J19 – This is an unpopulated 2-pin jumper header, that may optionally be used as an

attachment point for connecting an external frequency response analyzer tool, for

measuring the SMPS control loop phase/gain characteristics. The 20 Ohm load resistor

(R96) is connected directly across the J19 pins.

J20 – This is a standard female USB micro-B connector that is intended to be used to

power the board and provide a USB communication path when using the integrated

programmer/debugger (PKOB) circuit.

J21 – This is a 2-pin screw terminal that provides access to the SMPS V

nets. This is a convenient place for attaching external loads that may be powered by

the SMPS circuit.

OUT

and GND

DS50002762A-page 16

2.5.2 SMPS Hardware Overcurrent Protection

The components, Q11, C22, R67, U10, and the high-side current sense resistors,

R59 + R74, implement a crude form of hardware-based overcurrent protection. In a

normal/real application SMPS design, overcurrent protection is often provided through

the use of comparator(s), which would typically be implemented using the comparators

and DACs inside the microcontroller. However, during initial firmware development, the

code for enabling the DACs + comparators may not have been written and debugged

yet, at the time of, say, accidentally dropping an oscilloscope ground lead onto the

demo board. This could result in an unanticipated random short circuit. In these

scenarios, the hardware overcurrent protection circuit implemented by Q11, U10 and

surrounding components can potentially help protect the circuit from damage.

Advance Information

2018 Microchip Technology Inc.

Page 17

Hardware

During an overcurrent condition, when the current through R59 + R74 starts to exceed

approximately 1.2A (ex: 600 mV sense voltage), the base of Q11 will become forward

biased and it will begin to turn on. This will quickly charge the capacitor C22 to the

Schmitt trigger V

as a Schmitt trigger OR gate). Once the V

(independent of the RC14_S1PWM7H signal), thus turning off the high-side P-channel

MOSFET Q6.

At this point, the current through Q6 will drop to zero, Q11 will turn off, but C22 will

remain charged near the V

R67. The U10 output will not immediately switch back on due to the Schmitt trigger

hysteresis voltage between the V

mately 40% of an RC time constant (between C22 + R67) for the V

reached, which enforces a minimum Q6 off time of roughly 80 µs. This delay is sufficient for the L1 inductor current to drop all the way to zero due to the energy loss in the

diodes D2, D5 and the resistance in the freewheeling current path.

Therefore, even during short-circuit conditions with improperly implemented firmware

control signals, the average current can be maintained at a reasonably safe level. Once

the firmware for enabling and using the internal U1 comparators and DACs has been

developed/debugged, it is expected that the Q11 and related hardware overcurrent

protection components would be omitted, since they would become somewhat

redundant in the final application design.

IH

input logic high threshold of the U10 logic chip (which is configured

IH

level is reached, the U10 output will go high

IH

level until it is eventually bled down to the VIL level through

IH

and VIL input thresholds of U10. It takes approxi-

IL

threshold to be

2.5.3 SMPS Hardware Overvoltage Protection

The components, Q7, C15, R64, R65, R66 and U5, implemented a hardware-based

output overvoltage protection feature in a manner similar to the hardware overcurrent

protection circuit. When a conventional boost converter is operated open loop without

enough load on the output, the output voltage can theoretically rise to an indeterminate

high level, which can potentially avalanche the output Schottky diode, the boost

MOSFET or the output capacitors.

When the output voltage rises above approximately 16V, the output of the resistor

divider (R65 + R66) will become high enough to begin forward biasing the Q7 base and

turning on the transistor. This will quickly discharge C15 from 3.3V down to the V

IL

Schmitt trigger input threshold of the Schmitt AND gate implemented by U5. This overrides the PWM control signal and shuts down Q2 until such time as the output

overvoltage condition has decayed away, and enough time has elapsed for R64 to

charge C15 back up to the V

IH

Schmitt trigger input threshold of U5 (automatically

re-enabling PWM activity on Q2).

In a typical/real SMPS application, the closed-loop output feedback control loop would

normally be responsible for preventing output overvoltage conditions from occurring.

However, during initial firmware development, the closed-loop control algorithms may

not yet be fully implemented and operational (or may be halted from normal operation,

for example, due to hitting a debug breakpoint in the firmware). In these scenarios, the

hardware output overvoltage protection circuitry can help to prevent potential circuit

damage.

2.5.4 PWM DAC/DC Bias Generator

The RC5_S1PWM2L net is intended to be driven with a fixed frequency PWM waveform. The low-pass filter, consisting of R54 + C26 (and C41 when jumper J10 is

capped), averages the PWM waveforms, and for a high PWM frequency, generates an

adjustable DC voltage. Op amp U8 buffers the DC voltage, providing a low-impedance

firmware adjustable DAC, where the output voltage is based on the PWM duty cycle

provided to the circuit.

2018 Microchip Technology Inc.

Advance Information

DS50002762A-page 17

Page 18

dsPIC33CH Curiosity Development Board User’s Guide

2.5.5 Transient Load Tester Circuit

The MOSFET Q8 and surrounding components implement an adjustable

constant-current sink that can be periodically pulsed on for a few milliseconds at a time

to generate momentary SMPS output load transient pulses. During control loop firmware development, it is often desirable to study the control system behavior in

response to large signal step changes.

By monitoring the SMPS output voltage waveforms in response to the load step

transient event, one can get an idea of the real world output voltage undershoot during

the transient and the subsequent overshoot that will occur after the transient load is

rapidly removed. Additionally, the transient response recovery waveform shapes can

also provide hints as to likely control loop stability and approximate phase margin.

Load step transient response curves exhibiting damped sinusoidal oscillating output

voltage, that takes a long time to recover to steady-state DC values, implies a control

loop with low phase margin, while an over damped RC-like recovery waveform implies

higher phase margin.

When the RC13_TRANSIENT logic signal is driven high, the MOSFET Q8 will begin to

turn on through the gate resistor R79. However, as the gate voltage rises, current will

begin to flow through the MOSFET and current sense resistor R94, which will create a

voltage that is sensed by Q9. When the voltage at the base of Q9 is sufficient to turn it

on, it will begin sinking current from the gate of Q8, preventing the gate voltage from

rising further and maintaining MOSFET Q8 in the linear region, where it behaves like a

voltage controlled constant-current sink.

Components, R83 and C40, provide compensation for the MOSFET Q8 gate waveform

to ensure small signal stable regulation of the constant current. The relative sizes of

R79 and R87 set the DC gain of the constant-current regulation control loop.

The value of current sense resistor R94 sets the current limit, but it is made adjustable

by biasing the base of Q9, up or down, via the resistor dividers R84 and R85. When the

S1PWM2L_DAC_ISET DC voltage level is high (e.g., near 3.3V), Q9 will always be

turned on, even with no current through R94 due to the resistor divider output (of

R84 + R85) being higher than the turn-on voltage of the BJT Q9. Conversely, when the

S1PWM2L_DAC_ISET DC voltage is low (e.g., near 0.0V), this decreases the voltage

appearing on the Q9 base, requiring larger currents through R94 before the MOSFET

Q8 gate voltage becomes limited.

Adjusting the PWM waveform duty cycle on RC5_S1PWM2L by +1.0% alters the Q8

constant-current sink value by approximately -12 mA. At 50% PWM duty cycle, the

approximate current sink level is around 390 mA, but will vary somewhat between

boards and at different ambient temperatures, as these will affect the Q9 turn-on

voltage. For exact current sink values, it is necessary to use closed-loop control by

measuring the RA2_TRANSIENTFB current sense voltage with the ADC at run time.

Then, using the resulting value to fine-tune adjust the PWM duty cycle on

RC5_S1PWM2L.

Since Q8 is driven in the linear region during the transient pulse, the instantaneous

power dissipation within the MOSFET can be quite high, potentially up to 15W if the

circuit is configured for 15V output and 1A pulse load current. This power dissipation

level cannot be sustained indefinitely without a substantial heat sink, but for short

pulses (ex: ≤100 ms based on the safe operating area graph in the MCP87130T

MOSFET data sheet), the thermal inertia of the MOSFET die and package allow the

junction temperature to stay below the 150ºC maximum of the device. However, in

between pulses, enough time must be allowed for the die and package to cool back to

room temperature, before the next pulse, in order to ensure reliable operation of the

circuit. It is therefore recommended to control RC13_TRANSIENT, so as to generate

short pulses (ex: ≤10 ms) with long off times between pulses (ex: pulse rate of ~5 Hz).

DS50002762A-page 18

Advance Information

2018 Microchip Technology Inc.

Page 19

In the event of improper firmware control of the RC13_TRANSIENT net (e.g., DC logic

high or high time pulses > 10 ms), Q8 would potentially experience high sustained

power dissipation, and unless protected somehow, would be vulnerable to thermal

failure. To prevent this scenario, components, Q10, R88, C51, R90 and R91, implement a crude maximum on-time restricting sub-circuit, which is intended to limit the Q8

on time to roughly 10 ms maximum.

When RC13_TRANSIENT goes high, C51 begins charging through R88 and will

eventually reach approximately 2x the VBE forward voltage necessary to turn on Q10.

At this point, the output voltage of the resistor dividers, R90 and R91, rises high enough

that Q10 begins turning on, sinking current/voltage away from the gate of Q8 and eventually turning off the MOSFET Q8. When RC13_TRANSIENT is eventually driven logic

low, C51 discharges through R90 and R91, resetting the circuit automatically.

2.6 LOW-SIDE CURRENT SENSING

During Buck mode operation, it is sometimes desirable to be able to measure the

current during the off time of MOSFET Q6 if implementing some form of “peak valley”

or Average Current mode control algorithm. Low-side current sensing during the

MOSFET off time is possible via the current sense resistors, R63, R92 and R93. However, the voltage developed across the current sense resistors will be a negative

voltage with respect to ground. The signal is therefore connected to the inverting input

of one of the PGAs in the microcontroller, which can then be used to invert and amplify

the negative voltage into a positive voltage that can be measured by the ADC or used

by a comparator inside the device.

When supplying a negative input voltage to the PGA, it is important to maintain the I/O

pin voltage within the absolute maximum ratings from the device data sheet, which

allows for negative voltages only within V

Schottky diode D9 and resistor R95 are used to clamp the negative voltages to within

the 0V to -300 mV range. However, it is important to be aware that the inverting inputs

to the PGAs on the device have approximately 10k typical input impedance from the

device data sheet, and therefore, the resistance of R95 will reduce the gain of the

amplifier for a given PGA setting. Such that, in this configuration, the firmware should

not rely on the absolute output voltage of the PGA to reflect the true current through the

sense resistors, unless the overall gain of the complete circuit is directly measured and

factored into the computations in the firmware.

Hardware

SS

to (VSS – 300 mV) range. Therefore,

2018 Microchip Technology Inc.

Advance Information

DS50002762A-page 19

Page 20

dsPIC33CH Curiosity Development Board User’s Guide

RA3_ISENSEH 0.04877 • VIN + 1.626 • IQ6

RA3_ISENSE H – 0.04 877 • V

IN

IQ6

1.626

Rsense = = 0.5 Ohms

1

R59

1

R74

+

–1

ISENSEH_BIASED = (VIN – IQ6 • Rsense)

R102

(R102 + R97)

RA3_ISENSEH =

R98

R52

(VIN – ISENSEH_BIASED)

RA3_ISENSEH =

R98

R52

[]

(VIN – IQ6 • Rsense)(R102)

R102 + R97

V

IN

–

2.7 HIGH-SIDE CURRENT SENSING

The SMPS on-time current can be measured by the voltage developed across the

high-side current sense resistors, R59 and R74. However, the ISENSEH signal is

referenced to the +5V input rail of the SMPS circuit (not to ground), which prevents it

from being measured directly by the ADC or comparators in the microcontroller U1.

Therefore, the ISENSEH voltage signal is level shifted (to be ground referenced) and

amplified by the components, U7A, Q1, R52 and R98, with an effective gain of 3.3.

Components, R97 and R102, add a small DC bias (approximately -71 mV, before level

shifter gain or about +235 mV at RA3_ISENSEH), which appears at the

RA3_ISENSEH microcontroller pin as an intentional offset error in the current

measurement. This intentional DC biasing ensures that the current sense voltage

signal is always within the U1 comparator input sensing range and the internal DAC

reachable range, even when the Q6 current is exactly 0.0 mA with realistic comparator

and DAC offset voltages.

The final output voltage on RA3_ISENSEH is related to the Q6 current approximately,

as shown in Equation 2-1 and Equation 2-2 (where RA3_ISENSEH is the voltage in

volts measurable with the microcontroller ADC; V

may be ~4.6V under load during operation and IQ6 is the current through the MOSFET

Q6 in amps). Equation 2-1 and Equation 2-2 were derived by simplifying and substituting resistor values into Equation 2-3 through Equation 2-6, which in turn, were derived

from the schematic implementation.

IN

is the +5V rail input voltage, which

EQUATION 2-1:

EQUATION 2-2:

EQUATION 2-3:

EQUATION 2-4:

EQUATION 2-5:

EQUATION 2-6:

DS50002762A-page 20

Advance Information

2018 Microchip Technology Inc.

Page 21

dsPIC33CH CURIOSITY DEVELOPMENT

BOARD USER’S GUIDE

Appendix A. Schematics

The schematics for the dsPIC33CH Curiosity Development Board (DM330028) are shown in Figure 1

through Figure 4.

2018 Microchip Technology Inc.

Advance Information

DS50002762A-page 21

Page 22

DS50002762A-page 22

Designed with

Altium.com

RB0_OSCI

Pin 70

Pin 26

Pin 50

820R

0603

1%

R9

820R

0603

1%

R1 0

1 4

2 3

S2

1 4

2 3

S1

10k

1%

R3

10k

1%

R1

3V3

3V3

3V3

3V3

RD5_RGB_RED

RD7_RGB_GREEN

RB14_RGB_BLUE

Pin 51

Pin 71

Pin 25

RE0_LED1

RE1_LED2

12

DNP

J1

Net Tie

NT1

RED

LED1

RED

LED2

U1VDD

U1VDD

2

1

43

GREEN

RED

BLUE

5

6

LED3

LED_RGB

RB4_PGC2

RB3_PGD2

14

23

S4

3V3

VPP/MCLR

V

DD

GND

ICSPCLK

NC

ICSPDAT

1

2

3

4

5

6

HDR-2.54 Male 1x 6 STAGGE RED

DNP

J2

1k

0603

1%

R8

3V3

4.7k

0603

1%

R7

1

2

3 4

5

6

SC-70

1

2

3 4

5

6

SOT-23

Prototyping Area

Current

measureme nt

point

(Local VDD/VSS bypass/decoupling for U1)

MCLR

G eneral Purpose LEDs

RGB LED

Buttons

P otentiometer

8 MHz Oscillator

RE7_S1

RE8_S2

2

1

3

10k

20%

R17

MCLR

MCLR

3V3

Pin 25Pin 26

RD0_RXA

3V3

I2C Pull-ups (DNP)

Note : N ot p opu late d, typic ally insta lle d o n

mikroBUS dau ghter boards instead.

RB8_SCLB

RB9_SDAB

DNP

R

2

1

DNP

R

2

2

mikroBUS™ Interface A

AN

1

RST

2

CS

3

SCK

4

MISO

5

MOSI

6

+3.3V

7

GND

8

PWM

16

INT

15

RX

14

TX

13

SCL

12

SDA

11

+5V

10

GND

9

J3

3V3

RD4_RSTA

RD1_TXA

RD0_RXA

RE13_SDAA

RE12_SCLARD6_MI

SOA

RC3_MOS

IA

RB10_SCKA

RC7_ANA RB15_PWMA

RD2_INTA

RD3_CSA 1k

R14

AN

1

RST

2

CS

3

SCK

4

MISO

5

MOSI

6

+3.3V

7

GND

8

PWM

16

INT

15

RX

14

TX

13

SCL

12

SDA

11

+5V

10

GND

9

J8

mikroBUS™ Interface B

3V3

RB7_CSB

RC6_RSTB

RB9_SDAB

RB8_SCLB

RC11_TXB

RC10_RXB

RC9_MISOB

RB2_ANB

RD8_MOSIB

RC4_PWMB

RB13_INTB

RC8_SCKB

1k

R19

MCLR

Reset

Button

U1VDD

10k

1%

R5

1 4

2 3

S3

RE9_S3

3V3

RD1_TXA

RD2_INTA

RD3_CSA

RD4_RSTA

RD6_MI

SOA

RD8_MOSIB

RE0_LED1

RE1_LED2

RE8_S2

RE9_S3

RA0_POT

RA4_S1MCLR3

RB0_OSCI

RB2_ANB

RB3_PGD2

RB4_PGC2

RB5_S1PGD3

RB6_S1PGC3

RB7_CSB

RB8_SCLB

RB9_SDAB

RB13_INTB

RB15_PWMA

RC12

RC3_MOSIA

RC4_PWMB

RC6_RSTB

RC7_ANA

RC8_SCKB

RC9_MISOB

RC10_RXB

RC11_TXB

Pin 32

Pin 11

Pin 12

Pin 31

Pin 12Pin 11

RB14_RGB_BLUE

RD5_RGB_RED

RD7_RGB_GREEN

RB6_S1PGC3

RB5_S1PGD3

3V3

VPP/MCLR

V

DD

GND

ICSPCLK

NC

ICSPDAT

RA4_S1MCLR3

Slave Debug Only (during dual debug)

1

2

3

4

5

6

HDR-2.54 1x6 S TAGGER ED

J15

100R 06031%

R20

0.1 μF

25V 0603

C4

0.1 μF

25V 0603

C13

0.1 μF

25V

0603

C2

0.1 μF

25V 0603

C3

0.1 μF

25V

0603

C12

1k

0603

1%

R6

1k

0603

1%

R4

1k

0603

1%

R2

4.7k

0603

1%

R99

3V3

RE7_S1

330R

R12

330R

R13

330R

R11

Master and Slave Programming/Debug

(also connects to PKOB circuit output)

0.1 μF

25V

0603

C6

0.1 μF

25V

0603

C7

0.1 μF

25V

0603

C8

0.1 μF

25V

0603

C9

0.1 μF

25V

0603

C1 1

5V

5V

RD14_ISENSEL

RA3_ISENSEH

RA0_POT

RA1_VINSENSE

RA2_TRANSIENTFB

RC1_VOUTFB

RC14_S1PWM7H

RC15_S1PWM7L

RC5_S1PWM2L

RC13_TRANSIENT

RC0_PWMDACFB

1k

0603

1%

R73

RD12_S1PG A2P2

20k

1%

R77

RB1_IBIAS2

RD9

RD11

RD13

RD15

RE2

RE3

RE4

RE5

RE6

RE10

RE11

RE12_S CLA

RE13_S DAA

RE14

RE15

RB10_SCKA

RB11

RB12

RD10

RC2

RE13_SDAA

RE12_SCLA

DNPR

7

8

DNPR

8

1

10 μF

25V

0805

C1 0

270R

1%

R16

16V

1 μF

0603

C5

0.1 μF

25V

0603

C1

STB

1

GND

2

OUT

3

V

DD

4

DSC 6011JI1A-008.0000

X1

RP46/PWM1H/RB14

1

RE0

2

RP47/PWM1L/RB15

3

RE1

4

RP60/PWM4H/RC12

5

RP61/PWM4L/RC13

6

RP62/S1PWM 7H/RC14

7

RP63/S1PWM7L/RC15

8

MCLR

9

PCI22/S1PCI22/RD15

10

V

SS

11

V

DD

12

PCI21/S1ANN1/S1PGA2N2/S1PCI21/RD14

13

S1ANN0/S1PGA1N2/RD13

14

AN12/S1AN10/IBIAS3/RP48/RC0

15

AN0/C MP1 A/RA0

16

RE2

17

AN1/S1AN15/R A1

18

RE3

19

AN2/S1AN16/RA2

20

AN3/IBIAS0/S1AN0/S1CMP1A/S1PGA1P1/RA3

21

RE4

22

AN4/IBIAS1/S1MCLR3/S1AN1/S1CMP2A/S1PGA2P 1/S1PGA3P2/RA 4

23

RE5

24

AV

DD

25

AV

SS

26

S1AN14/S1PGA2P2/RD12

27

AN13/S1AN A1/I S R C0 /R P 49 /R C1

28

AN14/S1ANA0/ISRC1/RP50/R C2

29

R P 5 4 / S 1 AN 11/S1CMP1B/RC 6

30

V

DD

31

V

SS

32

CMP1B/S1AN8/S1CMP3B/RP51/RC3

33

OSCI/CLKI/AN5/RP32/S1AN5/RB0

34

OSC O /C LK O /AN6/IB IAS 2/R P 33 /S1AN4 /R B 1

35

S1AN17/S1PGA1P2/R D11

36

S1PGA3N2/RE6

37

ISRC 3/S1AN13/S1CMP2B/RD10

38

RE7

39

AN15/ISRC2/RP55/S1AN12/RC7

40

DACOUT/AN7/CMP1D/RP 34/INT0/S1MCLR 2/S1AN3/S1ANC0/S1ANC1/S1CMP1D/S1CMP2D/S1CMP3D/RB2

41

RE8

42

PGD2/AN8/RP35/S1PGD2/S1AN18/S1CM P3A /S1 P GA3 P 1/ R B3

43

RE9

44

PGC2/RP36/

S1PGC2/S1AN9/

S1PWM 5

L/RB4

45

RP56/ASDA1/SCK2/S1ASDA1/S1SCK1/RC 8

46

RP57/ASCL1/SDI2/S1ASC L1/S1SDI1/RC9

47

PCI20/S1PCI20/R D9

48

SDO2/PCI19/S1SDO1/S1PCI19/RD8

49

V

SS

50

V

DD

51

RP71/S1PWM8H/RD7

52

RP70/S1PWM6H/RD6

53

RP69/S1PWM6L/

RD5

54

PGD3/RP37/SDA2/S1PGD3/RB5

55

PGC3/RP38/

SCL2

/S1PGC3/RB6

56

RE10

57

TDO/AN9/RP39/S1MCLR1/S1AN6/S1PWM5H/RB7

58

RE11

59

PGD1/AN10/R P40/SC L1/S1PGD1/S1AN7/S

1SCL1

/RB 8

60

PGC1/AN11

/RP41/

SDA1/S1PGC1/S1SDA1/RB9

61

ASC L2 /RE 1 2

62

RP52/S1PWM2H/R C4

63

ASDA2/ RE 13

64

RP53/S1PWM2L/RC5

65

RP58/S1PWM 1H/RC10

66

RP59/S1PWM 1L/RC11

67

RP68/S1PWM3H/RD4

68

RP67/S1PWM3L/RD3

69

V

SS

70

V

DD

71

RP66/S1PWM8L/RD2

72

RP65/S1PWM4H/RD1

73

RP64/S1PWM4L/ RD0

74

TMS/RP42/PWM3H/RB10

75

TCK/RP43/PWM3L/RB11

76

RE14

77

TDI/RP44/PWM2H/RB12

78

RE15

79

RP45/PWM2L/RB13

80

U1

dsPIC33CH128MP508

FIGURE A-1: dsPIC33CH CURIOSITY BOARD SCHEMATIC REV. 1.0 (SHEET ONE OF FOUR)

dsPIC33CH Curiosity Development Board User’s Guide

Advance Information

2018 Microchip Technology Inc.

Page 23

2018 Microchip Technology Inc.

Designed with

Altium.com

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

22

2123

24

25

26

27

28

29

30

31

32

33

34

35

36

HDR-2.54 Fem ale 2x18

J11

3V3

I/O Pin Access Headers

16V

1 μF

0603

C30

Isolated USB-UART Interface

100k

R76

ID

4

V

BUS

1

GND

5

D-

2

D

+

3

0

USB micro-B TH/SMT

J16

U9D_P

U9D_N

U9D_P

U9D_N

V

DD

1

GP0

2

GP1

3

RST

4

UART RX

5

UART TX

6

GP2

7

GP3

8

SDA

9

SCL

10

V

USB

11

D-

12

D+

13

V

SS

14

MCP2221A

U9

U9_VDD

U9_VDD

16V1 μF

0603

C31

U9_GND

U9_GND

U9_GND

U9_GND

U9_VDD

U9_GND

U9_GND

3V3

1k

0603

1%

R75

RC10_RXB

RC11_TXB

460.8 kBaud max

DNP

2

3

1

J17

If insta lling J17, use regu lated 5V (5.5V max)

is

olate

d wall cube with center pin positive.

Also recommende d to cut NT2 and populate

D1 to prevent V

BUS

backd rive cu rrent.

VBUS5

0.1 μF

25V

C33

0.1 μF

25V 0603

C29

0.1 μF

25V 0603

C32

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

22

21

23

24

25

26

27

28

29

30

31

32

33

34

35

36

HDR-2.54 Fem ale 2x18

J12

1

2

3

4

5

6

7

8

9

10

HDR-2.54 Fem ale 2x5

J18

3V3

Power S

tatus (Green)

LED5

5V

Power Supply

470R

0603

1%

R18

2.2 μF

10V

0603

C23

2.2 μF

10V

0603

C39

V

OUT

1

V

OUT

2

GND3EN

4

NC

5

V

IN

6

MI

C5528

3V3

U12DNP

D1

Net Tie

0.5 mm

NT2

5V

DNP

D7

Net Tie

0.5 mm

NT3

V

DD1

1

A1

2

A2

3

GND14GND2

5

B2

6

B1

7

V

DD2

8

SI8422AB-D-IS

U11

V

OUT

5V

RA

2_TRANSIE NTFB

RA3_ISENSEH

3V3

RE4 RA4_S1MCLR3

RE5

RE3RA1_VINSENSE

RE2RA0_POTRC2

RC3_MOS

IA

RC4_PWMB

RC6_RSTB

RC7_ANA

RC8_SCKB

RC9_MISOB

RC10_RXBRC11_TXB

RC14_S1PWM7H

RC15_S 1PWM7L

RC5_S1PWM2L

RC 13_ T RANS I ENT

RC0_PWMDACFB

RC12

RB0_OSCI

RB2_ANB

RB3_PGD2

RB4_PGC2

RB5_S1PGD3RB6_S1PGC3

RB7_CSB

RB8_SCLB

RB9_SDAB

RB13_INTB

RB15_PWMA

RB14_RGB_BLUE

RB1_IBIAS2

RB10_SCKA

RB11

RB12

RE0_LED1

RE1_LED2

RE8_S2

RE9_S3

RE7_S1

RE6

RE10

RE11

RE12_SCLA RE13_SDAA

RE14

RE15

RD0_RXA

RD1_TXA RD2_INTA

RD3_CSA RD4_RSTA

RD6_MISOA

RD8_MOSIB

RD5_RGB_RED

RD7_RGB_GREEN

RD14_ISENSEL

RD10

RD12_S1PG A2P2

RD9

RD11

RD13

RD15

MC

LR

U1VDD

RC1_VOUTFB

Isolation

5V

FIGURE A-2: dsPIC33CH CURIOSITY BOARD LAYOUT SCHEMATIC REV. 1.0 (SHEET TWO OF FOUR)

Advance Information

DS50002762A-page 23

Schematics

Page 24

DS50002762A-page 24

Designed with

Altium.com

1k

0603

1%

R54

100R

0603

1%

R56

RC15_S1PWM7L

3V3

TP LOOP Black

DNP

TP5

1

2

J10

Pole at ~ 15.9 kHz (J10 Open)

Pole at ~ 1.45 kHz (J10 Closed)

10 μF

25V

0805

C34

10 μF

25V

0805

C35

R S X 10 1 MM- 3 0T R

D5

10 μF

25V

0805

C36

4.7k

1%

R70

4.7k

1%

R80

Resistor Gain (J13 Closed) = 0.5481 (1.470 mV/ADC LSB at 12-bit, 3.3 V

REF

)

1k

1%

R57

VOUT_FB

1

2

J13

1k

0603

1%

R72

Resistor Gain (J13 Open) = 0.1754 (4.592 mV/ADC LSB at 12-bit, 3.3 V

REF

)

3V3

100R

0603

1%

R55

1k

0603

1%

R85

470R

0603

1%

R83

1k

0603

1%

R79

1

3

2

MMBT3904

Q9

100R

0603 1%

R87

S1PWM2L_DAC_ISET

V

OUT

0.010 μF 25V

0603

C40

2.2k

0603

1%

R84

S1PWM2L DAC/DC Bias Generator/RC Filter

On-time restrictor

sub-circ uit

Adjustable constant-current transient load

Note: Q8 is driven in the linear region.

Limit (peak power) * (on-time) product to

maintain peak Q8 juntion temp <150°C.

0.010 μF

25V

0603

C26

4

1,2,3

5,6,7,8

MCP87130T

Q8

1

3

2

MMBT3904

Q10

10k

1%

R88

20k

0603

1%

R90

20k

0603

1%

R91

MMBD 914

D6

10k

1%

R89

Transient Load Tester Circuit

1R

1206

1%

1/4W

R94

1R

1206

1%

1/4W

R9 3

1R

1206

1%

1/4W

R9 2

1R

1206

1%

1/4W

R59

1R

1206

1%

1/4W

R74

10 μF

25V

0805

C42

DNP

C44

DNP

C43

DNP

R86

0603

DNP

C3 8

100R

0603

1%

R9 5

0.1 μF

25V

C25

0.1 μF 25V

0603

C37

0.1 μF

25V

0603

C41

16V

1 μF

0603

C51

100R

0603

1%

R52

330R

1%

R98

DNP

C46

470R

0603

1%

R103

0603

DNP

C52

100R

0603

1%

R61

High-side current sense level shifter

Output voltage feedback circuit

Buck mode low-side o-time current

sense (Note: 0.0V to -300 mV signal,

suggest -8x PGA gain)

For Buck Mode: PWM Q6, D rive Q2 DC OFF

For Boost Mode: Drive Q6 DC OFF (logic high or tr i-state), PW M Q2

For Bu ck/Boost Mode: PWM Q6 and Q2 with same s

ignal

(N ote: Q6 drive should be active- low, Q2 active-high)

Congurable Buck, Boost or Buck/Boost Test Circuit

Inp ut vol tage mo ni tor in g

4

1,2,3

5,6,7,8

MCP87130T

Q2

3V3

0R

0603

R60

+A

3

-A

2

OUTA

1

V

SS

4

V

DD

8

MCP6292

U7A

0.1 μF

25V

0603

C21

0.1 μF 25 V

0603

C24

+A

3

-A

4

OUTA

1

V

SS

2

V

DD

5

MCP6001

U8

5V

5V

5V

5V

330R

1%

R15

5V

1R

1206

1%

1/4W

R6 3

BAT54

D9

+B

5

-B

6

OUTB

7

MCP6292

U7B

BAT54

D8

1

3

2

MMBT3904

Q7

V

OUT

0.010 μF

25V 0603

C15

10k

1%

R65

270R

1%

R66

0.010 μF

25V

0603

C22

20k

0603

1%

R67

1

2

3

MMBT3906

Q11

5V

1k

0603

1%

R68

DNP

C45

DNP

R71

DNP

R69

Hardware overcurrent

protection (useful during

firmware dev elopment)

Output overv oltage protection (useful

during firmware development)

ISENSE H

10 μF

25V

0805

C47

V

OUT

GND

2

I03Y

4

Vcc

5

I2

6

I1

1

NC7SZ58P6X

U10

5V

Con figu red as : S chm itt OR

Configured as : Schmitt AND

3

1

2

RZM001P02T2L

Q1

GND

2

I0

3

Y

4

V

CC

5

I2

6

I1

1

NC7SZ5 7P6X

U5

3V3

3V3

ISENSE H_BIASED

RD14_ISENSEL

RA3_ISENSEH

RA1_VINSENSE

RA2_TRANSIENTFB

12

DNP

J19

5V

RC14_S 1PWM7H

820R

1%

R58

RC5_S1PWM2L

S1P W M 2 L_ DA C _ I S E T

RC13_T RANSIE NT

RC0_PWMDACFB

V

OUT

Net Tie

NT5

1

2

DNP

J14

RS X101MM-30TR

D2

10 μF

25V

0805

C53

10 μF

25V

0805

C55

10k

1%

R82

5V

1 2

TERMINAL 1x2

J21

V

OUT

20R

0805

1%

R96

10k

1%

R102

150R

0603

1%

R97

ISENSE H_BIASED

ISENSE H

10k

1%

R64

RC1_VOUTFB

0.010 μF

25V

0603

C54

100 μF

25V

C57

Low ESR

Scre w

3

1

2

BSS308 PE

Q6

33 μH

L1

_J10

_J13

270R

1%

R62

Designed with

Altium.com

FIGURE A-3: dsPIC33CH CURIOSITY BOARD LAYOUT SCHEMATIC REV. 1.0 (SHEET THREE OF FOUR)

dsPIC33CH Curiosity Development Board User’s Guide

Advance Information

2018 Microchip Technology Inc.

Page 25

2018 Microchip Technology Inc.

Designed with

Altium.com

1

3

2

MMBT3904

Q5

330R

1%

R32

100k

1%

R45

4.7k

1%

R31

D_P

D_N

D_N

D_P

3.16k

1%

R27

1k

1%

R25

VDD_S E NS E

VPP_SE NSE

VPP_SE NSE

VDD_SENSE

10k

1%

R49

100R

1%

R47

MCLR

4.7k

1%

R37

10k

1%

R48

PKEE_CS

PKEE_WP

PKEE_SCK

PKEE_MIS O

PKEE_MIS O

PKEE_CS

10k

1%

R50

PKEE_SCK

PKEE_MOSI

PKEE_MOSI

PKEE_WP

10k

1%

R24

PKSCK

PKMISO

PKMOSI

330R

1%

R29

330R

1%

R36

PKMOSI

PKMISO

PKSCK

RB3_PGD2

RB4_PGC2

PK_PGC

PK_PGD

3V3

3V3

3V3

3V3 3V3

3V3

3V3 3V3 3V3

10k

1%

R33

3V3

+t

500 mA Polyfuse

1210

TH1

100R

1%

R2 8

10k

1%

R35

10k

1%

R38

3V3

1

3

2

MMBT3904

Q4

10k

1%

R46

1

2

3

MMBT3906

Q3

10k

1%

R44

3V3

100k

1%

R42

3V3

2

31

DNP

X2

DNP

R41

DNP

R39

3V3 3V3

RC11_T XB

RC10_R XB

DNP

R40

DNP

R43

1k

0603

1%

R30

1k

0603

1%

R34

3.57k

0603

1%

R26

ID

4

V

BUS

1

GND

5

D-

2

D+

3

0

USB MICRO-B FEMALE

J20

PICkit™ On-Board

Target ICSP™ Signals

PKOB Serial EEPROM (25LC256)

3V3

PKOB USB Interface

1

2

3

4

5

6

J9

PK_PGD

PK_PGC

3V3

VPP/MCLR

V

DD

GND

ICSPCLK

NC

ICSPDAT

Bumpon Hemisphere Black

PAD1 PAD2 PAD3 PAD4

PKVBUS

10 μF

25V

0805

C14

3V3

DSC6011JI1A-012.0000

10k

1%

R51

4.7k

1%

R23

4.7k

1%

R53

1

2

3

MMBT3906

Q12

0.1 μF

25V

0603

C49

20k

0603

1%

R101

0.1 μF

25V

0603

C50

20k

0603

1%

R100

PKVBUS

16V

1 μF

0603

C48

(with V

BUS

inrush slew rate limiting)

VBUS5

0.1 μF

25V

C16

0.1 μF

25V

C17

0.1 μF

25V

C18

0.1 μF

25V

C19

0.1 μF

25V

0603

C27

0.1 μF

25V

0603

C28

0.1 μF

25V

0603

C20

CS

1

SO

2

WP

3

V

SS

4

SI

5

SCK

6

HOLD

7

V

CC

8

25LC256-I/SN

U6

PMD5/CN63/RE5

1

SCL3/ PMD6/ CN64/RE 6

2

SDA3/PMD7/CN65/R E7

3

C1IND/ RP21/ PMA5/ CN8/R G6

4

C1INC/RP26/PMA4/CN9/RG7

5

C2IND/RP 19/PMA 3/CN10/RG8

6

MCLR

7

RP27/ PMA2/ C2INC/C N11/RG9

8

Vss

9

V

DD

10

PGEC 3/AN5/C1INA/ V

BUSON

/RP18/CN7/RB 5

11

PGED3/AN4/C1INB/USBOEN/R P28/CN6/R B4

12

AN3/C 2I NA / V PI O/C N5/ R B 3

13

AN2/C2INB/VMI O/R P13/CN4/R B2

14

PGEC1/AN1/V

REF

-/RP1/CN3/RB 1

15

PGED1/AN0/V

REF

+/RP0/PMA6/CN2/RB0

16

PGEC 2/AN6/RP6/CN24/R B6

17

PGED2/AN7/RP7/R CV/CN25/RB7

18

AV

DD

19

AVss

20

AN8/RP8/CN26/RB 8

21

AN9/RP9/PMA7/C N27/RB9

22

TMS/CV

REF

/AN10/PMA13/CN28/RB10

23

TDO/AN11/PMA12/CN29/RB11

24

Vss

25

V

DD

26

TCK/AN12/PMA11/CTED2/CN30/RB12

27

TDI/AN13/PMA10/ CTE D1/CN31/RB13

28

AN14/CTPLS/R P14/ PMA1/CN32/RB14

29

AN15/RP29/RE FO/PM A0/CN12/RB15

30

SDA2/R P10/P MA9/CN17/ RF4

31

SCL2/RP17/PMA8/CN18/RF5

32

R P 1 6 /U S B I D/C N7 1 /R F 3

33

V

BUS

34

V

USB

35

D-/ R G 3

36

D+/R G 2

37

V

DD

38

OSCI/CLKI/CN23/RC12

39

OSCO/CLKO/CN22/RC15

40

Vss

41

RTCC/DMLN/ RP2/CN53/RD8

42

DPLN/SDA1/RP 4/CN54/RD 9

43

SCL1/RP3/PMCS2/CN55/RD10

44

RP12/PMCS1/CN56/RD11

45

DMH/R P11/INT0/ CN49/RD0

46

SOSCI/C3IND/CN1/RC13

47

SOSC O/T 1CK/C3INC/R PI37/C N0/RC14

48

VCPCON/RP24/CN50/RD1

49

DPH/ R P2 3/C N51 /R D 2

50

RP22/PMBE/CN52/RD3

51

RP25/P MWR /CN13/RD4

52

RP20/PMRD/CN14/RD5

53

C3INB/CN15/RD6

54

C3INA/CN16/RD7

55

V

CAP/VDDCORE

56

ENVREG

57

V

BUSST

/V

CMPST1

/CN68/RF0

58

V

CMPST2

/CN69/RF1

59

PMD0/CN58/RE0

60

PMD1/CN59/RE1

61

PMD2/CN60/RE2

62

PMD3/CN61/RE3

63

PMD4/CN62/RE4

64

U4

3

1

2

DMP2100U

Q13

STB

1

GND2OUT

3

V

DD

4

12.00 MHz

X3

PIC24FJ256GB106-I/PT

Advance Information

DS50002762A-page 25

FIGURE A-4: dsPIC33CH CURIOSITY BOARD LAYOUT SCHEMATIC REV. 1.0 (SHEET FOUR OF FOUR)

Schematics

Page 26

dsPIC33CH Curiosity Development Board User’s Guide

NOTES:

DS50002762A-page 26

Advance Information

2018 Microchip Technology Inc.

Page 27

dsPIC33CH CURIOSITY DEVELOPMENT

BOARD USER’S GUIDE

Appendix B. Bill of Materials (BOM)

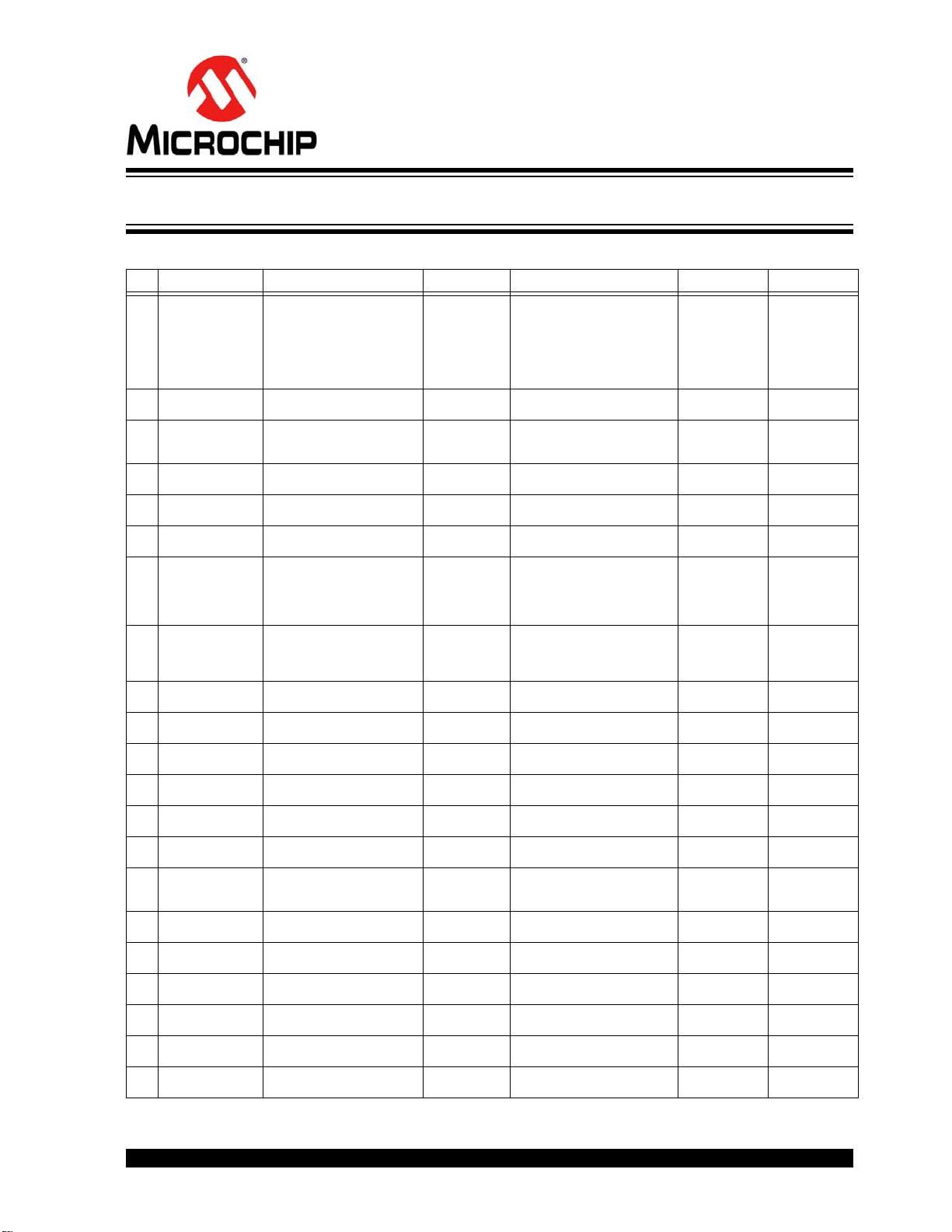

T ABL E B-1: dsPIC33CH CURIO SITY DEVE LOPMENT BOARD BILL OF MATE RIALS

Qty. Designator Description Mfg. 1 Mfg. 1 Part # Mfg. 2 Mfg. 2 Part #

28 C1, C2, C3, C4, C6,

C7, C8, C9, C11,

C12, C13, C16, C17,

C18, C19, C20, C21,

C24, C25, C27, C28,

C29, C32, C33, C37,

C41, C49, C50

5 C5, C30, C31, C48,

C51

9 C 10, C14, C34,

C35, C36, C42,

C47, C53, C55

5 C 15, C22, C26,

C40, C54

2 C23, C39 Capacitor Ceramic, 2.2 µF, 10V,

1 C57 Capacitor Aluminum, 100 µF,

19 R1, R3, R5, R24,

R33, R35, R38, R44,

R46, R48, R49, R50,

R51, R64, R65, R82,

R88, R89, R102

17 R2, R4, R6, R8, R14,

R19, R25, R30, R34,

R54, R57, R68, R72,

R73, R75, R79, R85

8 R7, R23, R31, R37,

R53, R70, R80, R99

3 R9, R10, R58 Resistor TKF, 820R, 1%,

8 R11, R12, R13, R15,

R29, R32, R36, R98

3 R 16, R62, R66 Resistor TKF, 270R, 1%,

1 R17 Resistor, Variable, 10K, 20%, THAlps Electric

3 R 18, R83, R103 Resistor TKF, 470R, 1%,

9 R 20, R28, R47,

R52, R55, R56,

R61, R87, R95

1 R26 Resistor, SMD, 3.57 kOhm, 1%,

1 R27 Resistor TKF, 3.16k, 1%,

3 R 42, R45, R76 Resistor TKF, 100k, 1%,

6 R 59, R63, R74,

R92, R93, R94

1 R60 Resistor TKF, 0R, 1/10W, SMD,

6 R 67, R77, R90,

R91, R100, R101

Capacitor Ceramic, 0.1 µF, 25V,

10%, X7R, SMD, 0603

Capacitor Ceramic, 1 µF, 16V,

10%, X7R, SMD, 0603

Capacitor Ceramic, 10 µF, 25V,

10%, X5R, SMD, 0805

Capacitor Ceramic, 0.010 µF,

25V, 10%, X7R, SMD, 0603

10%, X7R, SMD, 0603

20%, 25V, Low-ESR, Radial

Resistor TKF, 10k, 1%,

1/10W, SMD, 0603

Resistor TKF, 1k, 1%, 1/10W,

SMD, 0603

Resistor TKF, 4.7k, 1%, 1/10W,

SMD, 0603

1/10W, SMD, 0603

Resistor TKF, 330R, 1%,

1/10W, SMD, 0603

1/10W, SMD, 0603

1/10W, SMD, 0603

Resistor TKF, 100R, 1%,

1/10W, SMD, 0603

1/10W, 0603

1/10W, SMD, 0603

1/10W, SMD, 0603

Resistor TKF, 1R, 1%, 1/4W,

SMD, 1206

0603

Resistor TKF, 20k, 1%, 1/10W,

SMD, 0603

Murata

Electronics

Taiyo Yuden

Co., Ltd.

Murata

Electronics

Yageo

Corporation

Murata

Electronics

KEMET ESY107M025AE3AA

Panasonic® ECG

Panasonic ECG

ROHM

Semiconductor

Stackpole

Electronics, Inc.

Panasonic ECG

Panasonic ECG

Co., Ltd.

Panasonic ECG

Panasonic ECG

Vishay/Da le CRCW06033K57FKEA

Panasonic ECG

Panasonic ECG

ROHM

Semiconductor

Panasonic ECG

Panasonic ECG

GRM188R71E104KA01D Wurth Elektronik 885012206071

®

EMK107B7105KA-T Wurth Elektronik 885012206052

GRM21BR61E106KA73L

CC0603KRX7R8BB103 Wurth Elektronik 885012206065

GRM188R71A225KE15D Wurth Elektronik 885012206027

ERJ-3EKF1002V

ERJ-3EKF1001V

MCR03EZPFX4701

RMCF0603FT820R

ERJ-3EKF3300V

ERJ-3EKF2700V

RK09K1130A5R

ERJ-3EKF4700V

ERJ-3EKF1000V

ERJ-3EKF3161V

ERJ-3EKF1003V

MCR18EZHFL1R00

ERJ-3GSY0R00V

ERJ-3EKF2002V

2018 Microchip Technology Inc.

Advance Information

DS50002762A-page 27

Page 28

dsPIC33CH Curiosity Development Board User’s Guide

T ABL E B-1: dsPIC33CH CURIOS ITY DEVE LOPMENT BOARD BILL OF MATER IALS (CON TINUED )

Qty. Designator Description Mfg. 1 Mfg. 1 Part # Mfg. 2 Mfg. 2 Part #

1 R84 Resistor TKF, 2.2k, 1%, 1/10W,

1 R96 Resistor TKF, 20R, 1%, 1/8W,

1 R97 Resistor TKF, 150R, 1%,

1 L1 Inductor, 33 µH, 1.7A, 0.120R, THBourns®, Inc. RLB0914-330KL Wurth Elektronik 7447471330

SMD, 0603

SMD, 0805

1/10W, SMD, 0603

Panasonic ECG

ROHM

Semiconductor

Stackpole

Electronics, Inc.

ERJ-3EKF2201V

MCR10EZHF20R0

RMCF0603FT150R

2 D2, D5 Diode Schottky, 30V, 1A, PMDU ROHM

1 D6 Diode Rectifier,

2 D8, D9 Diode Schottky, BAT54,

2 LED1, LED2 Diode LED Red, 2V, 20 mA,

1 LED3 Diode LED Tri Red, Green, Blue Cree, Inc. CLX6D-FKB-CMPQSGKBB7A363

1 LED5 Diode LED Green, 2.2V, 25 mA,

3 Q3, Q11, Q12 Transistor BJT PNP,

5 Q4, Q5, Q7, Q9,

Q10

1 Q1 MOSFET P-CH, 20V, 0.1A,

1 Q6 MOSFET P-CH, 30V, 2A,

1 Q13 MOSFET P-CH, 20V, 4.3A,

2 Q2, Q8 MOSFET N-CH, 25V,

4 J3, J8 Connector Header-2.54 Female,

2 J10, J13 Connector Header-2.54 Ma le,

2 _J10, _J13 Mechanical Hardware Jumper

2 J11, J12 Connector Header-2.54 Female,

2 J16, J20 Connector USB 2.0 micro-B

1 J18 Connector Header-2.54 Female,

1 J21 Connector Screw Terminal,

4 S1, S2, S3, S4 Switch Tact, SPST, 12V, 50 mA,

4 PA D1, PAD 2, PA D3 ,

PAD 4

1 TH1 PTC Resettable, 0.50A, 16V,

1 U11 Digital ISO, 2.5KV,

MMBD914LT1G, 1V, 10 mA,

100V, SMD, SOT-23-3

800 mV, 200m A, 30V,

SOT-23-3

104 mcd, Diffuse, SMD, 0805

15 mcd, Clear, SMD, 0603

MMBT3906, -40V, -200 mA,

300 mW, SOT-23-3

Transistor BJT NPN,

MMBT3904, 40V, 200 mA,

310 mW, SOT-23-3

SOT-723-3

SOT-23

SOT-23

MCP87130T-U/LC

1x8, 0.100" (2.54 mm), Tin,

Through-Hole

1x2, Gold, 5.84MH, TH, Vertical

Cap, 2.54 mm, 1x2

2x18, 0.100" Pitch, Gold, TH

Female, TH/SMD, R/A

2x5, 0.100", Gold, TH

5 mm, 1x2, Female, 1226AWG, 18A, TH, R/A

PTS645SM43SMTR92 LFS,

SMD

Mechanical Hardware Rubber

Pad, Bumpon Hemisphere,

0.44" x 0.20", Black

Chip, 1210

General Purpose, 8-SOIC

Semiconductor

ON

Semiconductor

Diodes

Incorporated

OSRAM Opto

Semiconductors

GmbH.

Kingbright

Electronics Co.,

Ltd.

Diodes

Incorporated

Diodes

Incorporated

ROHM

Semiconductor

Infineon

Technologies AG

Diodes

Incorporated

Microchip

Technology Inc.

Sullins