Page 1

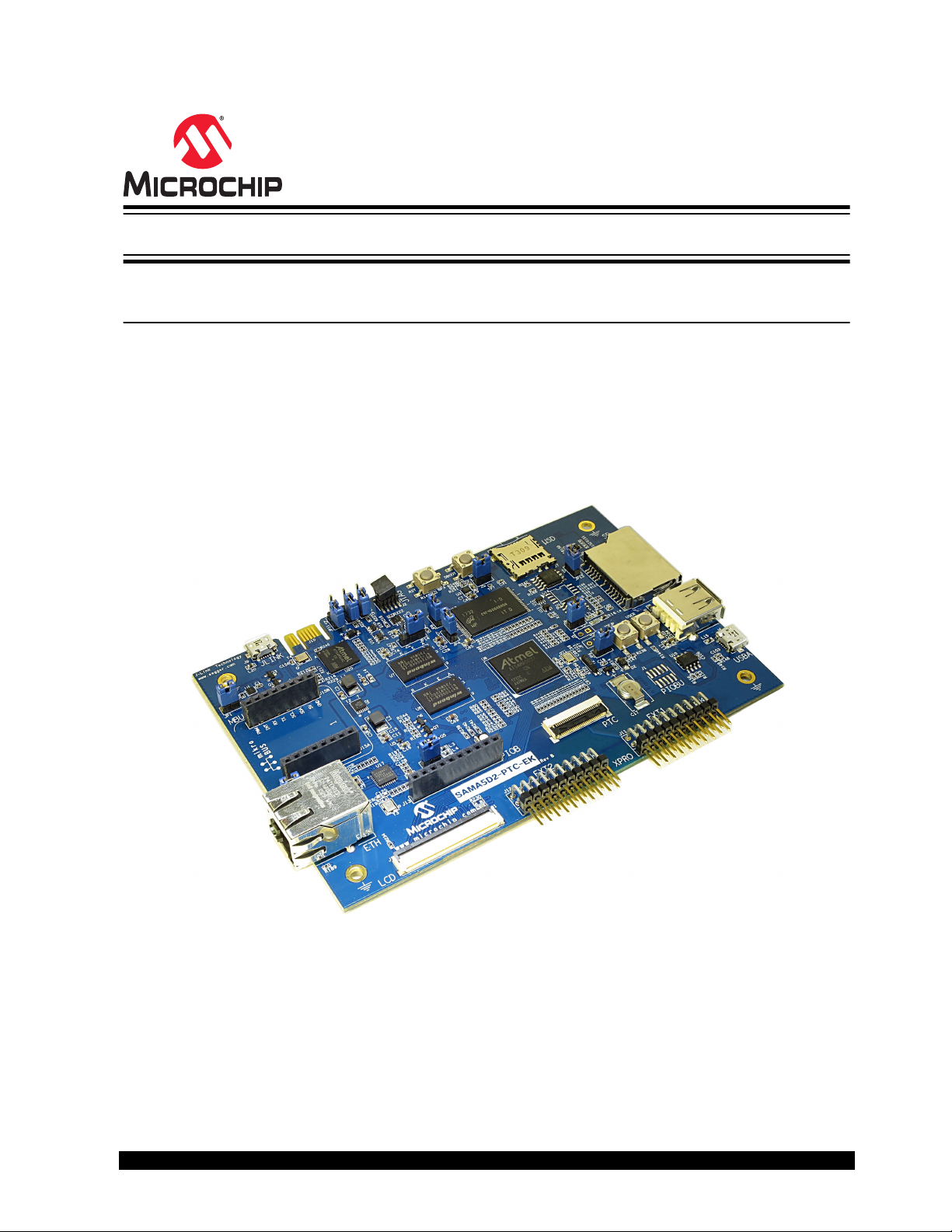

SAMA5D2-PTC-EK

SAMA5D2-PTC-EK User's Guide

Scope

This user's guide describes how to use the SAMA5D2 PTC Evaluation Kit (SAMA5D2-PTC-EK).

The SAMA5D2-PTC-EK is used to evaluate the capabilities of the Peripheral Touch Controller (PTC) designed for the

SAMA5D2 series of embedded MPUs. Refer to the Configuration Summary table in the SAMA5D2 Series Datasheet

for the list of MPUs featuring PTC.

© 2019 Microchip Technology Inc.

DS50002709B-page 1

Page 2

SAMA5D2-PTC-EK

Table of Contents

Scope............................................................................................................................................................. 1

1. Introduction............................................................................................................................................. 3

1.1. Document Layout......................................................................................................................... 3

1.2. Recommended Reading...............................................................................................................3

2. Product Overview....................................................................................................................................4

2.1. SAMA5D2-PTC-EK Features....................................................................................................... 4

2.2. SAMA5D2-PTC-EK Content.........................................................................................................5

2.3. Evaluation Kit Specifications........................................................................................................ 5

2.4. Power Sources............................................................................................................................. 5

3. Board Components................................................................................................................................. 6

3.1. Board Overview............................................................................................................................6

3.2. Function Blocks............................................................................................................................ 9

3.3. External Interfaces..................................................................................................................... 30

3.4. Debugging Capabilities.............................................................................................................. 34

3.5. PIO Usage on Expansion Connectors........................................................................................39

4. Installation and Operation..................................................................................................................... 47

4.1. System and Configuration Requirements...................................................................................47

4.2. Board Setup............................................................................................................................... 47

5. Appendix A. Schematics and Layouts...................................................................................................48

6. Revision History.................................................................................................................................... 61

6.1. DS50002709B - 09/2019............................................................................................................61

6.2. DS50002709A - 12/2017............................................................................................................61

The Microchip Website.................................................................................................................................62

Product Change Notification Service............................................................................................................62

Customer Support........................................................................................................................................ 62

Microchip Devices Code Protection Feature................................................................................................ 62

Legal Notice................................................................................................................................................. 62

Trademarks.................................................................................................................................................. 63

Quality Management System....................................................................................................................... 63

Worldwide Sales and Service.......................................................................................................................64

© 2019 Microchip Technology Inc.

DS50002709B-page 2

Page 3

1. Introduction

1.1 Document Layout

The document is organized as follows:

• Chapter 1. "Introduction"

• Chapter 2. "Product Overview" – Important information about the SAMA5D2-PTC-EK board

• Chapter 3. "Board Components" – Specifications of the SAMA5D2-PTC-EK and high-level description of the

major components and interfaces

• Chapter 4. "Installation and Operation" – Instructions on how to get started with the SAMA5D2-PTC-EK

• Appendix A. "Schematics and Layouts" – SAMA5D2-PTC-EK schematics and layout diagrams

1.2 Recommended Reading

The following Microchip document is available and recommended as a supplemental reference resource:

• SAMA5D2 Series Datasheet. Lit. Number DS60001476

SAMA5D2-PTC-EK

Introduction

© 2019 Microchip Technology Inc.

DS50002709B-page 3

Page 4

2. Product Overview

2.1 SAMA5D2-PTC-EK Features

The SAMA5D2-PTC-EK follows the Microchip MPU strategy for low cost evaluation kits with maximum reuse

capability, and is built on the SAMA5D2 Xplained Ultra (XULT) hardware and software ecosystem. This board is

mainly dedicated to evaluating the Peripheral Touch Controller capabilities.

Table 2-1. SAMA5D2-PTC-EK Features

Characteristics Specifications Components

SAMA5D2-PTC-EK

Product Overview

Processor

Clock speed

Memory

Display One LCD interface connector RGB, 18 bits

SD/MMC

USB

Ethernet One ETH PHY Micrel KSZ8081RN

Debug port

SAMA5D27-CU (289-ball BGA) 14x14mm body,

0.8mm pitch

MPU: 24 MHz, 32.768 KHz

PHY: Crystal 25 MHz

Two 16-bit, 2-Gbit DDR2

One 4-Gbit Nand Flash

One QSPI Flash

One Serial Data Flash (optional)

One EEPROM

One standard SD card interface

One microSD card interface

One USB host type A

One USB device type Micro-AB

One USB HSIC

One J-Link-OB/J-Link-CDC

One JTAG interface

–

–

Winbond W972GG6KB-25

Micron MT29F4G08

Microchip SST26VF064B

Microchip SST26VF032B

Microchip 24AA02E48

With 3.3V/1.8V power switch

–

With 5V power switch

–

Connector not mounted

Embedded J-Link-OB and J-Link-CDC

(ATSAM3U4C TFBGA100)

One RGB (Red, Green, Blue) LED

Board monitor

Expansion

Board supply From USB A and USB J-Link-OB 5VDC

Backup power supply SuperCap ELNA DSK-3R3H204T614-H2L

© 2019 Microchip Technology Inc.

Four push button switches

One set of XPRO WINGS connectors

One ITO FLEX connector

One Port B connector

One PIOBU connector

One mikroBUS™ connector

–

DisableBoot, Reset, WakeUp, User

Free

Dedicated PTC QTouch

Optional

Optional

Optional

–

®

DS50002709B-page 4

Page 5

2.2 SAMA5D2-PTC-EK Content

The SAMA5D2-PTC-EK evaluation kit includes the following:

• The SAMA5D2-PTC-EK board

• A USB cable

2.3 Evaluation Kit Specifications

Table 2-2. Evaluation Kit Specifications

Characteristic Specification

Board SAMA5D2-PTC-EK

Board supply voltage USB-powered

Temperature Operating: 0°C to +70°C

Storage: –40°C to +85°C

Relative humidity 0 to 90% (non-condensing)

Main board dimensions 135 × 90 × 20 mm

SAMA5D2-PTC-EK

Product Overview

RoHS status Compliant

Board identification SAMA5D2 Peripheral Touch Controller Evaluation Kit

2.4 Power Sources

Several options are available to power up the SAMA5D2-PTC-EK board:

• USB powering through the USB Micro-AB connector (J4 - default configuration)

• Powering through the USB Micro-AB connector on the J-Link-OB Embedded Debugger interface (J9)

Table 2-3. Electrical Characteristics

Electrical Parameter Value

Input voltage 5VCC

Maximum input voltage 6VCC

Maximum 3.3VDC current available 1.2A

I/O voltage 3.3V only

© 2019 Microchip Technology Inc.

DS50002709B-page 5

Page 6

3. Board Components

This section covers the specifications of the SAMA5D2-PTC-EK and provides a high-level description of the board's

major components and interfaces. This document is not intended to provide detailed documentation about the

processor or about any other component used on the board. It is expected that the user will refer to the appropriate

documents of these devices to access detailed information.

3.1 Board Overview

The fully-featured SAMA5D2-PTC-EK board integrates multiple peripherals and interface connectors, as shown in the

figure below.

SAMA5D2-PTC-EK

Board Components

3.1.1 Default Jumper Settings

The figure below shows the default jumper settings. Jumpers in red are configuration items and current measurement

points. Jumpers in blue are not populated.

© 2019 Microchip Technology Inc.

DS50002709B-page 6

Page 7

Figure 3-1. Default Jumper Settings

SAMA5D2-PTC-EK

Board Components

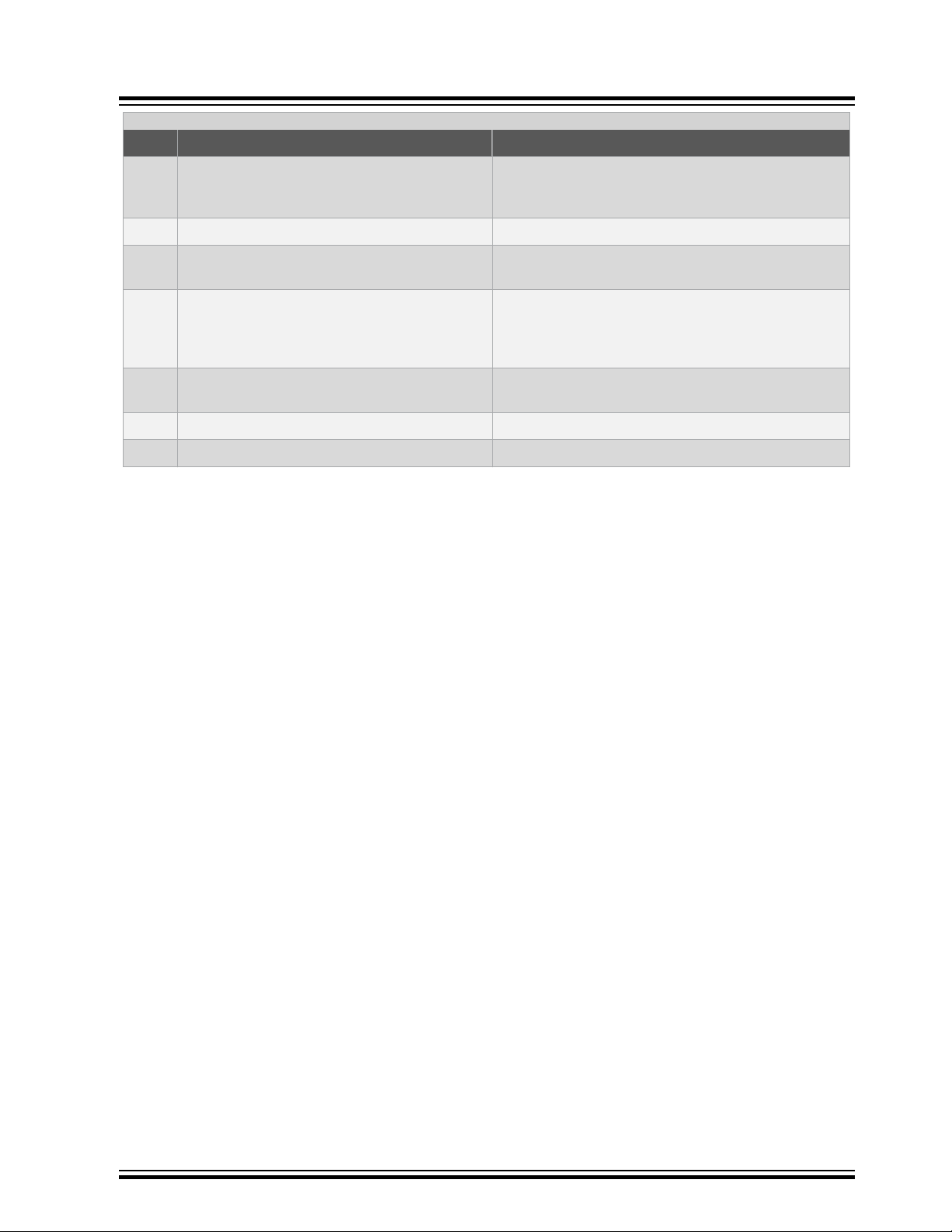

The following table describes the functionality of the jumpers.

Table 3-1. SAMA5D2-PTC-EK Jumper Settings

Jumper Default Function

JP1 Closed VDD_MAIN_5V current measurement

JP2 Closed VDDOSC, VDDUTMII, VDDANA, VDDAUDIOPLL current measurement

JP3 Closed VDDISC + VDDIOP0/1/2 current measurement

JP4 Closed VDDIODDR_MPU current measurement

JP5 Closed VDDCORE current measurement

JP6 Closed VDDBU current measurement

JP7 Open PIOBU1, PIOBU7

JP8 Closed Disables NAND_CS (open=disable)

JP9 Open Enables JTAG-CDC (closed=disable)

JP10 Open Enables JTAG-OB (closed=disable)

© 2019 Microchip Technology Inc.

DS50002709B-page 7

Page 8

...........continued

WARNING

Jumper Default Function

Erases SAM3U Flash Code (closed = erase)

SAMA5D2-PTC-EK

Board Components

JP11 Open

JP12 Closed Powers mikroBUS extension (3.3V)

JP13 Open Disables QSPI

1-2 Enables 3.3V J-Link-OB, connected to shutdown circuitry

JP14

2-3 Enables 3.3V J-Link-OB, always ON

3.1.2 Connectors on Board

The following table describes the interface connectors on the SAMA5D2-PTC-EK.

Table 3-2. SAMA5D2-PTC-EK Board Interface Connectors

Connector Interfaces to

J1 PIOBU, tamper and analog comparator connector (not populated)

J2 JTAG, 10-pin IDC connector

J3 USB Host B. Supports USB host using a type A connector

J4 USB A Device. Supports USB device using a type Micro-AB connector

J5 USB-C™ HSIC header (not populated)

J6 Standard SDMMC connector

This jumper is reserved for factory configuration

and should never be used by the end user.

J7 microSD connector

J8 Ethernet 10/100 RJ45

J9 USB-A Micro-AB, J-Link-OB port

J10 PCB connector for factory-programming the J-Link-OB/SAM3U

J11, J12 Xplained Pro expansion connectors (PTC-dedicated add-on boards)

J13 PIOs PortB connector

J14 ITO connector

J15 A&B mikroBUS connector

J16 Expansion TFT LCD connector for display module

© 2019 Microchip Technology Inc.

DS50002709B-page 8

Page 9

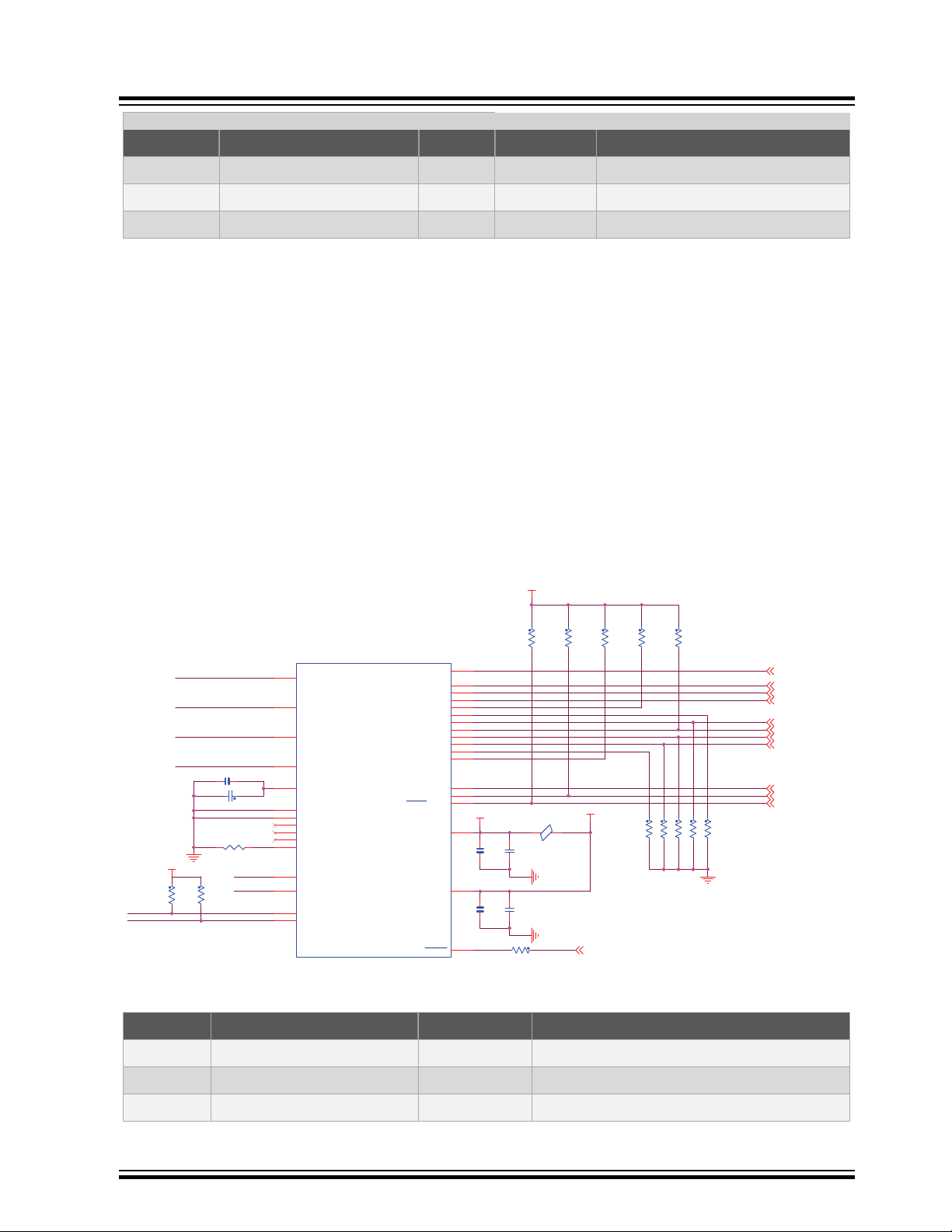

3.2 Function Blocks

POWER

MONITOR

J-Link Power

5V/3.3V

USB

Connector

Function Select

System Supplies

POWER

REGULATORS

SHDN

UART

MPU JTAG

Interface

JTAG

Switch

JTAG

LCD (18 bits)

TWI/SPI

RJ45

USB A&B

SDHC0

SDHC1

SAMA5D2-PTC-EK

Push

Button

FPC Connector

DEBUG

Interface

Reset, Wkup

DisBoot, User

3.3V, 2.5V,1.8V, 1.2V

VDDBU

GPIO

USB

Detection

ETH

PHY

PTC

QSPI

Flash

DDR2

SDRAM

DDR2

SDRAM

Power

Cap

Serial

EEPROM

NAND

Flash

PIOBU Connector

MikroBUS

Interface

ITO Connector

XPRO (1&2)

PTC Interface

GPIO

PortB[0-7]

Power

Switch

VBUS

5V

5V

5V

USB-B

Connector

USB-A

Connector

SPI

Flash

LEDs

J-Link-OB

J-Link-CDC

SAMA5D27

RGB

LEDs

Tri

State

SD Card

Connector

uSD

Connector

J-Link-OB

JTAG Interface

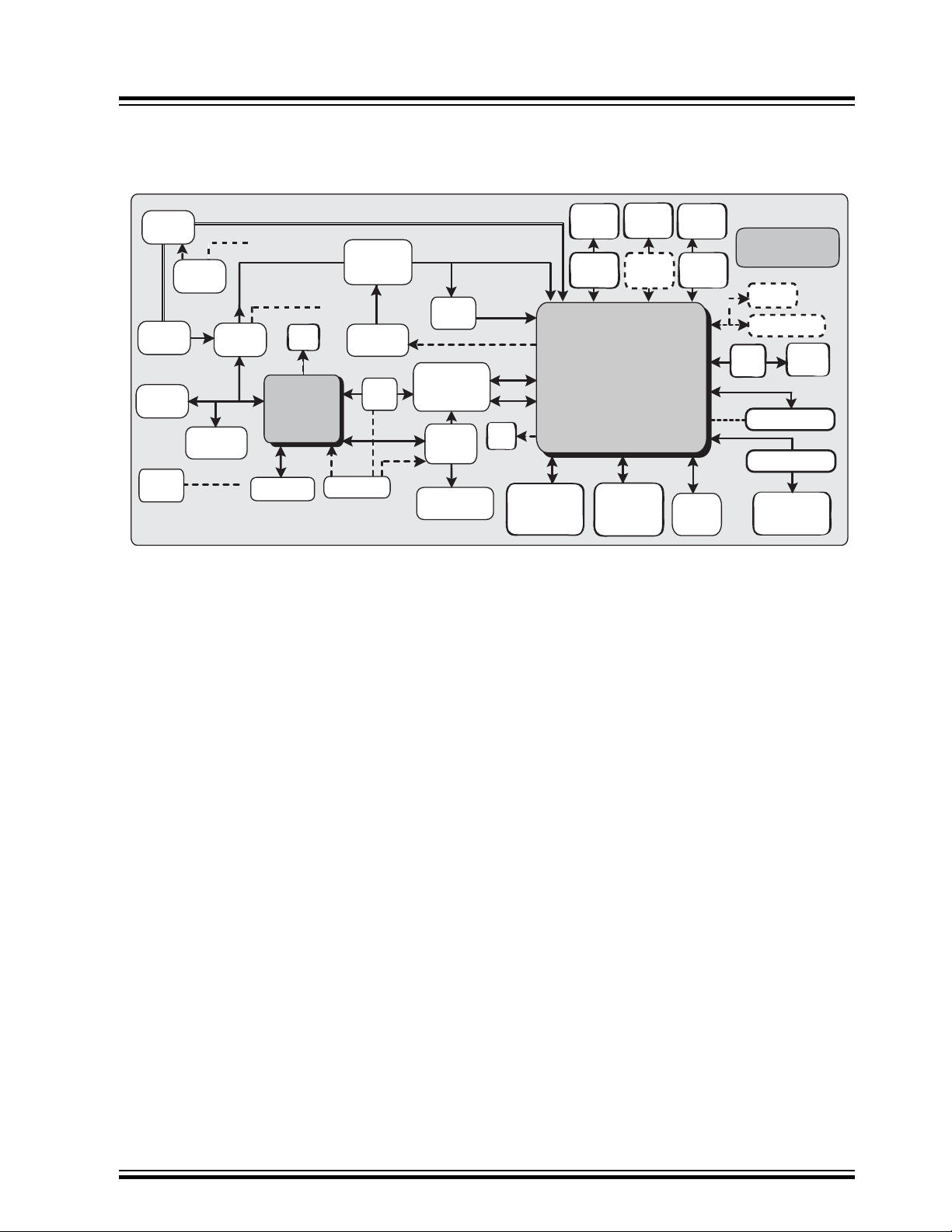

Figure 3-2. SAMA5D2-PTC-EK Block Diagram

SAMA5D2-PTC-EK

Board Components

3.2.1 Processor

The SAMA5D2 Series is a high-performance, power-efficient embedded MPU based on the ARM® Cortex®-A5

processor.

Please refer to the SAMA5D2 Series datasheet for more information.

3.2.2 Power Supply Topology and Power Distribution

3.2.2.1 Input Power Options

Two options are available to power the SAMA5D2-PTC-EK board. The USB-powered operation is the default

configuration and comes from the USB device ports (J4-J9) connected to a PC or a 5VDC supply. Such USB power

source is sufficient to supply the board in most applications. It is important to note that when the USB-powered

operation is used, the USB port down the way has a limited powering capability. If the USB-B Host port (J3) is

required to provide full powering capabilities to the target application, it is recommended to use an external DC

supply instead of a USB power source.

The following figure is a schematic of the power options.

© 2019 Microchip Technology Inc.

DS50002709B-page 9

Page 10

Figure 3-3. Input Powering

VDD_MAIN_5V

GND_POWER

GND_POWER

GND_POWER

GND_POWER

GND_POWER

VBUS_USBA

VBUS_JLINK

U1A

DMP2160UFD

1

2

6

7

C1

100nF

C0402

U4A

DMP2160UFD

1

2

6

7

R5 100K

R0402

R6 DNP

R0402

U1B

DMP2160UFD

4

5

3

8

JP1

Header 1X2

1

2

C12

100nF

C0402

R1

10K

R0402

U4B

DMP2160UFD

4

5

3

8

R2

100K

R0402

JPR1

Jumper

C2

100nF

C0402

CAUTION

Note: USB-powered operation eliminates additional wires and batteries. It is the preferred mode of operation for any

project that requires only a 5V source at up to 500 mA.

Jumper JP1 is used to perform MAIN_5V current measurements on the SAMA5D2-PTC-EK board.

3.2.2.2 Power Supply Requirements and Restrictions

Detailed information on the device power supplies is provided in tables “SAMA5D2 Power Supplies” and “Power

Supply Connections” in the SAMA5D2 Series datasheet.

SAMA5D2-PTC-EK

Board Components

3.2.2.3 Power-up and Power-down Considerations

Power-up and power-down considerations are described in section “Power Considerations” of the SAMA5D2 Series

datasheet.

The power-up and power-down sequences provided in the SAMA5D2 Series datasheet must be respected

for reliable operation of the device.

3.2.2.4 Power Management

The board power management uses three types of regulators:

• One dual synchronous step-down DC-DC regulator (U2 MIC2230) generates the 3.3V/800mA and 1.8V/800mA

power lines and utilizes a high-efficiency, fixed-frequency (2.5 MHz), current-mode PWM control architecture

that requires a minimum number of external components.

• One ultra low-dropout linear regulator (U3 MIC47053) generates the 1.25V/500mA from the 1.8V source.

• One high-performance single 2.5V/150mA is used as a VDDFUSE generator (U5 MIC5366).

The main regulators are enabled through a Field Effect Transistor (FET) scheme. The processor can assert SHDN (a

VDDBU-powered I/O) to shut down the regulators to enter Backup mode. All regulators on the board are also shut

down by the action of the SHDN signal.

A 3.3V battery (supercap) is implemented to permanently maintain VDDBU voltage (note: jumper JP6 must be in

place). The board can be woken up by action on the PB4 button, which drives the WKUP signal (also a VDDBUpowered I/O).

The figure below shows the power management scheme.

© 2019 Microchip Technology Inc.

DS50002709B-page 10

Page 11

Figure 3-4. Board Power Management

EN_1

EN_VDD_1V25

STARTB

STARTB

FPWM#

FPWM#

EN_1

EN_VDD_1V25

VDD_MAIN_5V

GND_POWER

GND_POWER

VDD_3V3

VDD_1V8

VDD_MAIN_5V

VDD_1V8

VDD_1V25

VDD_MAIN_5V

GND_POWER

GND_POWER

GND_POWER

VDD_MAIN_5V

VDD_3V3

VDD_MAIN_5V

GND_POWER

VDD_3V3

GND_POWER

GND_POWER

VDD_3V3

GND_POWER

GND_POWERGND_POWER

GND_POWER

SHDN

C4

10uF

C0603

U2

MIC2230-GSYML

MLF3x3mm

AVIN

3

EN1

11

FPWM#

7

SW1

8

OUT1

12

AGND5PGND

6

OUT2

1

SW2

4

PGOOD

10

EN2

2

VIN

9

EPAD

13

R249 4.7K

R0402

R13

39K

R0402

C6

10uF

C0603

R3

100K

R0402

R251

10K

R0402

R12

220K

R0402

C10 390pF

C0402

C7

100nF

C0402

L2 LQH43CN2R2M03L

L1812

C3

10uF

C0603

R248

20K

R0402

R10

DNP

R0402

R11

100K

R0402

C13

4.7nF

C0402

R250

3.3K

R0402

L1 LQH43CN2R2M03L

L1812

C5

1uF

C0603

Q1

BSS138

SOT23_123

1

3

2

R4

10K

R0402

C9

1uF

C0603

D1

PMEG6010CEGWX

sod123

Q2

BSS138

SOT23_123

1

3

2

C8

100nF

C0402

R9

100K

R0402

C11

10uF

C0603

Q3

BSS138

SOT23_123

1

3

2

U3

MIC47053YMT

BIAS

1

GND

2

IN1

3

IN2

4

ADJ

6

OUT

5

EPAD

9

PGOOD

7

EN

8

Q4

BC847C

SOT-23

1

32

R8 100K

R0402

C14

2.2uF

C0603

NRST

SAMA5D2-PTC-EK

Board Components

3.2.2.5 Supply Group Configuration

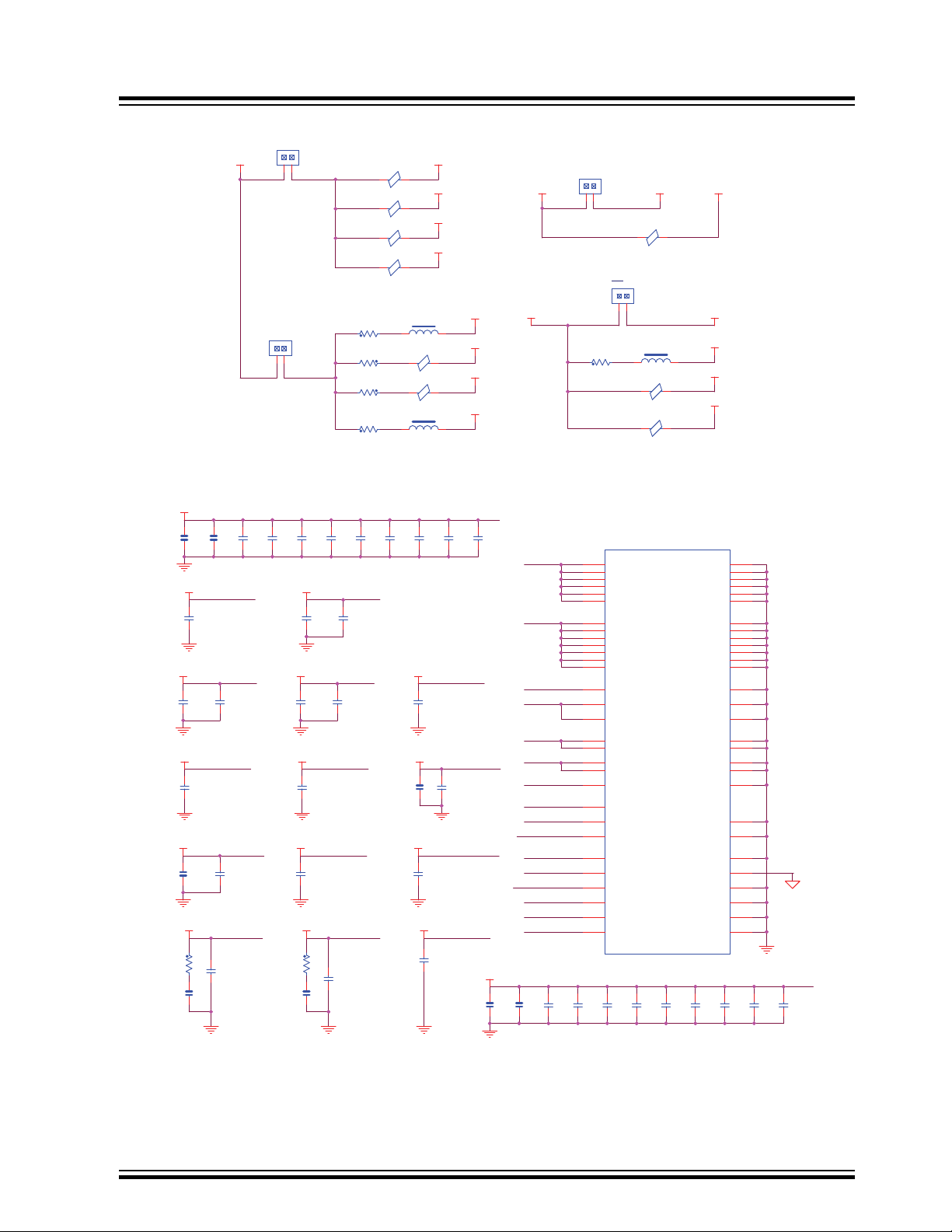

The main regulators provide all power supplies required by the SAMA5D2 device:

© 2019 Microchip Technology Inc.

• 1.25V VDDCORE, VDDPLLA, VDDUTMIC, VDDHSIC

• 1.8V VDDIODDR, VDDSDHC1V8

• 2.5V VDDFUSE

• 3.3V VDDIOP0, VDDIOP1, VDDIOP2, VDDISC

• 3.3V VDDOSC, VDDUTMI, VDDANA, VDDAUDIOPLL

• 3.3V VDDBU

DS50002709B-page 11

Page 12

Figure 3-5. Power Lines Distribution

For DDR2 For MPU

VDDHSIC

V

DD_3V3

VDD_1V25

VDDCORE

VDDIOP0

VDDIOP2

VDDIOP1

VDDPLLA

VDDUTMIC

VDDIODDR

VDDAUDIOPLL

VDDANA

VDDOSC

VDDUTMII

VDDISC

VDD_1V8 VDDSDHC1V8

L3

BLM18PG181SN1D

R0603

1 2

R16

2R2

R0603

R15

2R2

R0603

R17

0R

R0603

L7

MLZ1608N100L

L0603

L11

BLM18PG181SN1D

R0603

1 2

L10

BLM18PG181SN1D

R0603

1

2

JP5

Header 1X2

1

2

R18

0R

R0603

L4

BLM18PG181SN1D

R0603

1 2

L14

BLM18PG181SN1D

1

2

L9

MLZ1608N100L

L0603

JP4

Header 1X2

1

2

L13

BLM18PG181SN1D

R0603

1 2

L6

BLM18PG181SN1D

R0603

1

2

L8

MLZ1608N100L

L0603

R19

2R2

R0603

L5

BLM18PG181SN1D

R0603

1 2

L12

BLM18PG181SN1D

R0603

1 2

JP3

Header 1X2

1

2

JP2

Header 1X2

1

2

(3V3)

(1V2)

(1V8)

(3V3)

)3

V3(

)3V3()3V3

(

)5V2(

)

2V1(

(3V3)

(3V3)

(3V3)

(3V3)

(3V3)

(3V3)

(3V3)

(3V3)

(3V3)

(1V8)

(1V2)

(1V2)

(1V2)

(1V2)

(2V5)

(3V3)

(1V2)

)3

V3(

)2V1(

(3V3)

(3V3)

(3V3 or 1V8)

(3V3 or 1V8)

VDDBU

VDDCORE

VDDPLLA

VDDIOP0

VDDIOP1

VDDIOP2

VDDHSIC

VDDUTMIC

VDDUTMII

VDDSDHC

VDDPLLA

VDDOSC

VDDISC

VDDFUSE

VDDAUDIOPLL

VDDBU

VDDIODDR

VDDANA

VDDANA

VDDIOP0

VDDIOP1

VDDIOP2

VDDHSIC

VDDFUSE

VDDUTMII

VDDSDHC

VDDOSC VDDISC

VDDUTMIC

VDDCORE

VDDIODDR

VDDAUDIOPLL

GND_POWER

VDDBU

GND_POWER

GND_POWER

VDDCORE

GND_POWER

VDDIODDR

VDDANA

GND_POWER

VDDIOP0

GND_POWER

VDDIOP1

GND_POWER

VDDIOP2

GND_POWER

VDDHSIC

GND_POWER

VDDFUSE

GND_POWER

VDDUTMII

GND_POWER

VDDSDHC

GND_POWER

VDDPLLA

GND_POWER

VDDOSC

VDDISC

GND_POWER

GND_POWER

VDDUTMIC

GND_POWER

GNDUTMII

GND_POWER

VDDAUDIOPLL

C35

100nF

C0402

C51

1nF

C0402

C54

4.7uF

C0805

C31

100nF

C0402

C25

4.7uF

C0805

C61

1nF

C0402

C56

100nF

C0402

C37

100nF

C0402

C59

1nF

C0402

C20

10uF

C0603

C19

10uF

C0603

C21

100nF

C0402

C42

100nF

C0402

C40

100nF

C0402

C52

1nF

C0402

C50

100nF

C0402

C48

100nF

C0402

C26

100nF

C0402

C53

100nF

C0402

C28

10uF

C0603

C30

100nF

C0402

C34

100nF

C0402

C60

1nF

C0402

C46

100nF

C0402

C41

4.7uF

C0805

C49

100nF

C0402

C27

10uF

C0603

C44

100nF

C0402

R20

1R-1%

R0603

C29

100nF

C0402

C36

100nF

C0402

R21

1R-1%

R0603

C24

4.7uF

C0805

C47

100nF

C0402

C32

100nF

C0402

ATSAMA5D27C-CN

U6G

bga289p8

GNDADC

K5

GNDANA

L3

GNDBU

N6

GNDCORE_1

E7

GNDCORE_2

E9

GNDCORE_3

H4

GNDCORE_4

K12

GNDCORE_5

M5

GNDCORE_6

M9

GNDDDR_1

D14

GNDDDR_2

E11

GNDDDR_3

E12

GNDDDR_4

E14

GNDDDR_5

H14

GNDDDR_6

J14

GNDDDR_7

L14

GNDDPLL

T5

GNDAUDIOPLL

T4

GNDIOP0_1

F6

GNDIOP0_2

G7

GNDIOP1_1

M13

GNDIOP1_2

P14

GNDIOP2

F9

GNDISC

G4

GNDOSC

T6

GNDPLLA

U5

GNDSDMMC

R11

GNDUTMII

P9

GNDUTMIC

R7

VDDADC

L5

VDDANA

K3

VDDBU

N7

VDDCORE_1

D7

VDDCORE_2

D9

VDDCORE_3

H3

VDDCORE_4

K13

VDDCORE_5

N5

VDDCORE_6

N9

VDDDDR_1

D11

VDDDDR_2

D12

VDDDDR_3

D15

VDDDDR_4

E15

VDDDDR_5

H15

VDDDDR_6

J15

VDDDDR_7

L15

VDDAUDIOPLL

T3

VDDFUSE

M12

VDDHSIC

R9

VDDIOP0_1

E6

VDDIOP0_2

F7

VDDIOP1_1

N13

VDDIOP1_2

R14

VDDIOP2

F10

VDDISC

F4

VDDOSC

T7

VDDPLLA

U4

VDDSDMMC

P11

VDDUTMII

P8

VDDUTMIC

P7

C55

100nF

C0402

C23

100nF

C0402

C43

100nF

C0402

C38

100nF

C0402

C58

1nF

C0402

C57

100nF

C0402

C33

100nF

C0402

C39

100nF

C0402

C45

100nF

C0402

C22

100nF

C0402

Figure 3-6. Processor Power Lines Supplies

SAMA5D2-PTC-EK

Board Components

© 2019 Microchip Technology Inc.

DS50002709B-page 12

Page 13

3.2.2.6 VDDFUSE

VDD_3V3

GND_POWER

VDDFUSE

EN_1 12

C16

1uF

C0603

U5

MIC5366-2.5YMT

MLF1x1mm

VIN

4

GND

2

VOUT

1

EN

3

EPAD

5

C15

1uF

C0603

(Super)-Capa citor

energy storage

VDDBU

GND_POWER

GND_POWER

VDD_3V3

C18

100nF

C0402

JP6

Header 1X2

1

2

+

C17

0.2F/3.3V

c117x68

D2

PMEG6010CEGWX

sod123

R14 100R-1%

R0402

D3

BAT54C

SOT23_123

3

1

2

STARTB

GND_POWER

VDD_MAIN_5V

VDD_3V3

NRST

R13

39K

R0402

R12

220K

R0402

R11

100K

R0402

D1

PMEG6010CEGWX

sod123

Q3

BSS138

SOT23_123

1

3

2

Q4

BC847C

SOT-23

1

32

C14

2.2uF

C0603

PowerGood VDD_1V25

The SAMA5D2-PTC-EK board embeds a 2.5V regulator for fuse box programming.

Figure 3-7. VDDFUSE Regulator

3.2.2.7 Backup Power Supply

The SAMA5D2-PTC-EK board requires a power source in order to permanently power the backup part of the

SAMA5D2 device (refer to SAMA5D2 Series datasheet). The super capacitor C17 sustains such permanent power to

VDDBU when all system power sources are off.

Figure 3-8. VDDBU Powering Options

SAMA5D2-PTC-EK

Board Components

3.2.3 Reset Circuitry

3.2.4 Shutdown Circuitry

The reset sources for the SAMA5D2-PTC-EK board are:

• Power-on Reset from the power management unit,

• Push button reset BP3,

• JTAG or J-Link-OB reset from an in-circuit emulator.

Figure 3-9. Main Reset Control

The SHDN signal, output of Shutdown Controller (SHDN), drives the shutdown request to the power supply. This

output signal is supplied by VDDBU, which is present in Backup mode.

The Shutdown Controller manages the main power supply and is connected to the ENABLE input pin of the DC/DC

converter providing the main power supplies of the system.

© 2019 Microchip Technology Inc.

DS50002709B-page 13

Page 14

Figure 3-10. Shutdown Controller

STARTB

EN_1

VDD_MAIN_5V

GND_POWER GND_POWER

VDD_3V3

GND_POWER

SHDN

R3

100K

R0402

Q1

BSS138

SOT23_123

1

3

2

R4

10K

R0402

Q2

BSS138

SOT23_123

1

3

2

C8

100nF

C0402

WAKE UP

RESET

DIS BOOT

GND_POWER

VDDBU

DISABLE_BOOT

NRST

WKUP

R146 100R-1%

r0402

BP3 Tact Switch

FSM2JSML

R147 100R-1%

r0402

R238 10K

R0402

BP2 Tact Switch

FSM2JSML

R145 100R-1%

r0402

BP4 Tact Switch

FSM2JSML

USER BUTTON

PA10_USER_BT

R144 0R

R0402

BP1 Tact Switch

FSM2JSML

GND_POWER

XIN

XOUT

XOUT32

XIN32

GND_POWERGND_POWER

GND_POWER

GND_POWER

R122

DNP

R0402

C98

20pF

C0402

C97

20pF

C0402

R123 DNP

R0402

C96

20pF

C0402

Y1

24MHz CL=10pF

x4s32x25

1 4

32

C99

20pF

C0402

Y2

32.768KHz CL=12.5pF

X4S70X15

1

23

4

3.2.5 Push Button Switches

The SAMA5D2-PTC-EK features four push buttons:

• One board reset push button (BP3). When pressed and released, it causes a power-on reset of the board.

• One wakeup push button (BP4) connected to the SAMA5D2 WKUP pin, used to exit the processor from LowPower mode.

• One disable boot push button (BP2) used to devalidate the boot memories (refer to 3.2.8.3 CS Disable).

Figure 3-11. System Push Buttons

SAMA5D2-PTC-EK

Board Components

• One user push button (BP1) connected to PIO PB10.

Figure 3-12. User Push Button

3.2.6 Clock Circuitry

The embedded microcontroller generates its necessary clocks based on two crystal oscillators: one slow clock

(SLCK) oscillator running at 32.768 KHz and one main clock oscillator running at 24 MHz.

The SAMA5D2-PTC-EK board includes four clock sources:

• The two clocks mentioned above are alternatives for the SAMA5D2 processor (24 MHz, 32.768 kHz)

• One crystal oscillator for the Ethernet RMII chip (25 MHz)

• One crystal oscillator for the J-Link-OB microcontroller (12 MHz)

Figure 3-13. MPU Clock Circuitry

© 2019 Microchip Technology Inc.

DS50002709B-page 14

Page 15

3.2.7 Memory

DDR_VREFDDR_VREF

DDR_DQM0

DDR_DQM1

DDR_DQM2

DDR_DQM3

DDR_DQS0-

DDR_DQS0+

DDR_DQS1+

DDR_DQS1-

DDR_DQS2+

DDR_DQS2DDR_DQS3+

DDR_DQS3-

DDR_BA1

DDR_BA0

DDR_BA1

DDR_BA0

DDR_WE DDR_WE

DDR_CSDDR_CS

DDR_CLK-

DDR_CLK+

DDR_CLK-

DDR_CLK+

DDR_CKE DDR_CKE

DDR_CAS

DDR_RAS

DDR_CAS

DDR_RAS

DDR_D16

DDR_D17

DDR_D18

DDR_D19

DDR_D20

DDR_D21

DDR_D22

DDR_D23

DDR_D24

DDR_D25

DDR_D26

DDR_D27

DDR_D28

DDR_D29

DDR_D30

DDR_D31

DDR_D0

DDR_D1

DDR_D2

DDR_D3

DDR_D4

DDR_D5

DDR_D6

DDR_D7

DDR_D8

DDR_D9

DDR_D10

DDR_D11

DDR_D12

DDR_D13

DDR_D14

DDR_D15

DDR_A0

DDR_A1

DDR_A2

DDR_A3

DDR_A4

DDR_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_A0

DDR_A1

DDR_A2

DDR_A3

DDR_A4

DDR_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_BA2 DDR_BA2

DDR_A13DDR_A13

GND_POWER

VDD_1V8

GND_POWER

VDD_1V8

GND_POWER

GND_POWER

VDD_1V8

GND_POWER

VDD_1V8

GND_POWER

C94

100nF

C0402

R29 DNP R0402

C95

1nF

C0402

U8

W972GG6KB-25

bga84-32-1509e

A0

M8

A1

M3

A2

M7

A3

N2

A4

N8

A5

N3

A6

N7

A7

P2

A8

P8

A9

P3

A10

M2

A11

P7

A12

R2

A13

R8

BA0

L2

BA1

L3

BA2

L1

CKE

K2

CK_P

J8

CK_N

K8

RAS

K7

CAS

L7

WE

K3

CS

L8

DQ0

G8

DQ1

G2

DQ2

H7

DQ3

H3

DQ4

H1

DQ5

H9

DQ6

F1

DQ7

F9

DQ8

C8

DQ9

C2

DQ10

D7

DQ11

D3

DQ12

D1

DQ13

D9

DQ14

B1

DQ15

B9

LDQS_P

F7

NU/LDQS_N

E8

UDQS_P

B7

NU/UDQS_N

A8

LDM

F3

UDM

B3

ODT

K9

NC1

A2

NC2

E2

NC3

R3

NC4

R7

VDD1

A1

VDD2

E1

VDD3

J9

VDD4

M9

VDD5

R1

VDDQ1

A9

VDDQ2

C1

VDDQ3

C3

VDDQ4

C7

VDDQ5

C9

VDDQ6

E9

VDDQ7

G1

VDDQ8

G3

VDDQ9

G7

VDDQ10

G9

VDDL

J1

VREF

J2

VSS1

A3

VSS2

E3

VSS3

J3

VSS4

N1

VSS5

P9

VSSQ1

A7

VSSQ2

B2

VSSQ3

B8

VSSQ4

D2

VSSQ5

D8

VSSQ6

E7

VSSQ7

F2

VSSQ8

F8

VSSQ9

H2

VSSQ10

H8

VSSDL

J7

U7

W972GG6KB-25

bga84-32-1509e

A0

M8

A1

M3

A2

M7

A3

N2

A4

N8

A5

N3

A6

N7

A7

P2

A8

P8

A9

P3

A10

M2

A11

P7

A12

R2

A13

R8

BA0

L2

BA1

L3

BA2

L1

CKE

K2

CK_P

J8

CK_N

K8

RAS

K7

CAS

L7

WE

K3

CS

L8

DQ0

G8

DQ1

G2

DQ2

H7

DQ3

H3

DQ4

H1

DQ5

H9

DQ6

F1

DQ7

F9

DQ8

C8

DQ9

C2

DQ10

D7

DQ11

D3

DQ12

D1

DQ13

D9

DQ14

B1

DQ15

B9

LDQS_P

F7

NU/LDQS_N

E8

UDQS_P

B7

NU/UDQS_N

A8

LDM

F3

UDM

B3

ODT

K9

NC1

A2

NC2

E2

NC3

R3

NC4

R7

VDD1

A1

VDD2

E1

VDD3

J9

VDD4

M9

VDD5

R1

VDDQ1

A9

VDDQ2

C1

VDDQ3

C3

VDDQ4

C7

VDDQ5

C9

VDDQ6

E9

VDDQ7

G1

VDDQ8

G3

VDDQ9

G7

VDDQ10

G9

VDDL

J1

VREF

J2

VSS1

A3

VSS2

E3

VSS3

J3

VSS4

N1

VSS5

P9

VSSQ1

A7

VSSQ2

B2

VSSQ3

B8

VSSQ4

D2

VSSQ5

D8

VSSQ6

E7

VSSQ7

F2

VSSQ8

F8

VSSQ9

H2

VSSQ10

H8

VSSDL

J7

C72

100nF

C0402

R32 0R

R0402

C75

1nF

C0402

R31

DNP R0402

R30 0R

R0402

3.2.7.1 Memory Organization

The SAMA5D2 features a DDR/SDR memory interface and an External Bus Interface (EBI) to enable interfacing to a

wide range of external memories and to almost any kind of parallel peripheral.

This section describes the memory devices mounted on the SAMA5D2-PTC-EK board:

• Two DDR2 SDRAMs

• One NAND Flash

• One QSPI Flash

• One SPI Flash (optional)

• One serial EEPROM

Additional memory can be added to the board by:

• Installing an SD or MMC card in the SD/MMC0 or SD/MMC1 slot,

• Using the USB-B port.

Support is dependent upon driver support in the OS.

3.2.7.2 DDR2/SDRAMs

Two DDR2/SDRAMs (W972GG6KB-25-2 Gbits = 16 Mbits x 16 x 8 banks) are used as main system memory,

totalling 4 Gbits of SDRAM on the board. The memory bus is 32 bits wide and operates with a frequency of up to 166

MHz.

The figure below illustrates the implementation for the DDR2 memories.

Figure 3-14. DDR2 SDRAMs

SAMA5D2-PTC-EK

Board Components

3.2.7.3 DDR_CAL Analog Input

One specific analog input, DDR_CAL, is used to calibrate all DDR I/Os.

© 2019 Microchip Technology Inc.

DS50002709B-page 15

Page 16

Table 3-3. Calibration Cell DDR_CAL Value

DDR_D0

DDR_D1

DDR_D2

DDR_D3

DDR_D4

DDR_D5

DDR_D6

DDR_D7

DDR_D8

DDR_D9

DDR_D10

DDR_D11

DDR_D12

DDR_D13

DDR_D14

DDR_D15

DDR_D16

DDR_D17

DDR_D18

DDR_D19

DDR_D20

DDR_D21

DDR_D22

DDR_D23

DDR_D24

DDR_D25

DDR_D26

DDR_D27

DDR_D28

DDR_D29

DDR_D30

DDR_D31

DDR_DQM0

DDR_DQM1

DDR_DQM2

DDR_DQM3

DDR_DQS0+

DDR_DQS0-

DDR_DQS1+

DDR_DQS1-

DDR_DQS2+

DDR_DQS2-

DDR_DQS3+

DDR_DQS3-

DDR_A0

DDR_A1

DDR_A2

DDR_A3

DDR_A4

DDR_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_BA0

DDR_BA1

DDR_RAS

DDR_CAS

DDR_BA2

DDR_CS

DDR_WE

DDR_VREF

DDR_RESETN

DDR_CLK+

DDR_CLKDDR_CKE

GND_POWER

GND_POWER

GND_POWER

VDDIODDR

R23

100K

R0402

R24

21K-1%

R0402

R25

100K

R0402

C64

22pF

C0402

ATSAMA5D27C-CN

U6E

bga289p8

DDR_A0

F12

DDR_A1

C17

DDR_A10

C15

DDR_A11

A16

DDR_A12

A17

DDR_A13

G11

DDR_A2

B17

DDR_A3

B16

DDR_A4

C16

DDR_A5

G14

DDR_A6

F14

DDR_A7

F11

DDR_A8

C14

DDR_A9

D13

DDR_BA0

H12

DDR_BA1

H13

DDR_BA2

F17

DDR_CAL

E13

DDR_CAS

G12

DDR_CKE

F16

DDR_CLK

E17

DDR_CLKN

D17

DDR_CS

G13

DDR_D0

B12

DDR_D1

A12

DDR_D10

H17

DDR_D11

K17

DDR_D12

K16

DDR_D13

J13

DDR_D14

K14

DDR_D15

K15

DDR_D16

B8

DDR_D17

B9

DDR_D18

C9

DDR_D19

A9

DDR_D2

C12

DDR_D20

A10

DDR_D21

D10

DDR_D22

B11

DDR_D23

A11

DDR_D24

J12

DDR_D25

H10

DDR_D26

J11

DDR_D27

K11

DDR_D28

L13

DDR_D29

L11

DDR_D3

A13

DDR_D30

L12

DDR_D31

M17

DDR_D4

A14

DDR_D5

C13

DDR_D6

A15

DDR_D7

B15

DDR_D8

G17

DDR_D9

G16

DDR_DQM0

C11

DDR_DQM1

G15

DDR_DQM2

C8

DDR_DQM3

H11

DDR_DQS0

B13

DDR_DQS1

J17

DDR_DQS2

C10

DDR_DQS3

L17

DDR_DQSN0

B14

DDR_DQSN1

J16

DDR_DQSN2

B10

DDR_DQSN3

L16

DDR_RAS

F13

DDR_RESETN

E16

DDR_VREFCM

D16

DDR_VREFB0

H16

DDR_WE

F15

C62

100nF

C0402

C63

100nF

C0402

CAUTION

Memory Resistor value

LPDDR2/LPDDR3 24K

DDR3L 23K

DDR3 22K

DDR2/LPDDR1 21K

Figure 3-15. DDR Signals and CAL Analog Input

SAMA5D2-PTC-EK

Board Components

3.2.7.4 NAND Flash

The SAMA5D2-PTC-EK has native support for NAND Flash memory through its NAND Flash Controller. The board

implements one MT29F4G08ABA 4Gb x 16 NAND Flash connected to Chip Select three (NCS3) of the

microcontroller.

The figure below illustrates the NAND Flash memory implementation.

© 2019 Microchip Technology Inc.

The NAND Flash interface is shared with the SDMMC1 and QSPI interfaces.

DS50002709B-page 16

Page 17

NAND_WPn

3V3_NAND

VDD_3V3 3V3_NAND

3V3_NAND

NAND_CLE_PB1

NAND_ALE_PB0

NAND_REn_PB2

NAND_WEn_PA30

NAND_RDY_PC8

NAND_IO5_PA27

NAND_IO6_PA28

NAND_IO7_PA29

NAND_IO0_PA22

NAND_IO1_PA23

NAND_IO2_PA24

NAND_IO3_PA25

NAND_IO4_PA26

NAND_CS_PA31

R175

100K

MT29F4G08ABADAWP

U13

NC1

1

NC2

2

NC3

3

NC4

4

NC5

5

NC6

6

R/B#

7

CE#

9

NC7

10

VCC_1

12

VSS_1

13

NC9

14

NC10

15

CLE

16

ALE

17

NC21

47

VSS_4

48

RE#

8

NC8

11

WE#

18

WP#

19

DNU2

20

DNU1

21

NC11

22

NC12

23

NC13

24

VSS_2

25

NC14

26

NC15

27

NC16

28

DQ0

29

DQ1

30

DQ2

31

DQ3

32

NC17

33

VCC_2

34

DNU3

35

VSS_3

36

VCC_3

37

DNU4

38

VCC_4

39

NC18

40

DQ4

41

DQ5

42

DQ6

43

DQ7

44

NC19

45

NC20

46

R177

DNP

R174 0R

C113

100nF

R180

100K

C112

100nF

JP8

Header 1X2

1

2

C114

100nF

R179 0R

C115

100nF

R176

10K

SAMA5D2-PTC-EK

Figure 3-16. NAND Flash

Table 3-4. NAND Flash Signal Descriptions

PIO Signal Name Shared PIO Signal Description

Board Components

PA22 NAND_D0 SDMMC1-QSPI Data 0

PA23 NAND_D1 QSPI Data 1

PA24 NAND_D2 QSPI Data 2

PA25 NAND_D3 QSPI Data 3

PA26 NAND_D4 QSPI Data 4

PA27 NAND_D5 QSPI Data 5

PA28 NAND_D6 SDMMC1 Data 6

PA29 NAND_D7 – Data 7

PA30 NANDWE SDMMC1 –

PA31 NCS3 – Chip Select

PB00 NANDALE – –

PB01 NANDCLE – –

PB02 NANDOE – –

PC08 NANRDY – –

3.2.7.5 NAND Flash CS Disable

On-board jumper JP8 controls the selection (CS#) of the NAND Flash memory.

3.2.8 Additional Memories

3.2.8.1 Serial Flash

The SAMA5D2 includes two high-speed Serial Peripheral Interface (SPI) controllers. The SPI is a full duplex

synchronous bus supporting a single master and multiple slave devices. The SPI bus consists of the following items:

• a serial clock line (generated by the master)

• a data output line from the master

• a data input line to the master

• one or more active low Chip Select signals (output from the master)

© 2019 Microchip Technology Inc.

DS50002709B-page 17

Page 18

One SPI port is used to interface with the on-board serial Flash.

SPI0_CS0_PA17

GND_POWER

VDD_3V3

SPI0_MOSI_PA15

SPI0_MISO_PA16

SPI0_SPCK_PA14

C119

100nF

C0402

U16

SST26VF032B-104I/SM

soic8jg

HOLD

7

GND

4

VCC

8

CS

1

SCK

6

SI

5

SO

2

WP

3

QSPI0_CS_PA23

VDD_3V3

GND_POWER

VDD_3V3

VDD_3V3

QSPI0_IO0_PA24

QSPI0_IO1_PA25

QSPI0_IO2_PA26

QSPI0_IO3_PA27 QSPI0_SCK_PA22

U14

SST26VF064B-104I/SM

soic8jg

SI/SIO0

5

SO/SIO1

2

SIO2

3

SIO37SCLK

6

CS#

1

GND

4

VCC

8

C120

100nF

C0402

R186

10K

R0402

R187

10K

R0402

JP13

Header 1X2

1

2

R242

10K

The following figure illustrates the implementation of an SPI Flash memory.

Figure 3-17. Serial Flash

Note: The serial Flash is optional and not mounted on board.

3.2.8.2 QSPI Serial Flash

The SAMA5D2 provides two Quad Serial Peripheral Interfaces (QSPI).

A QSPI is a synchronous serial data link that provides communication with external devices in Master mode.

The QSPI can be used in SPI mode to interface with serial peripherals (such as ADCs, DACs, LCD controllers, CAN

controllers and sensors), or in Serial Memory mode to interface with serial Flash memories.

The QSPI allows the system to execute code directly from a serial Flash memory (XIP, or Execute In place,

technology) without code shadowing to RAM. The serial Flash memory mapping is seen in the system as other

memories (ROM, SRAM, DRAM, etc.).

With the support of the Quad SPI protocol, the QSPI allows the system to use high-performance serial Flash

memories which are small and inexpensive, instead of larger and more expensive parallel Flash memories.

The figure below illustrates the implementation of a QSPI Flash memory.

Figure 3-18. QSPI Serial Flash

SAMA5D2-PTC-EK

Board Components

A jumper (JP13) is used to disable the QSPI Flash.

Table 3-5. SPI and QSPI Signal Descriptions

PIO Signal Name Shared PIO Signal Description

PA14 SPI0_SPCK – SPI clock

PA15 SPI0_MOSI – Master out - Slave in

PA16 SPI0_MISO – Master in - Slave out

PA17 SPI0_NPCS0 – Chip Select

– – – –

PA22 QSPI0_SCK SDMMC1-NAND Flash QSPI clock

PA23 QSPI0_CS NAND Flash Chip Select

© 2019 Microchip Technology Inc.

DS50002709B-page 18

Page 19

...........continued

BOOT_DIS

QSPI Flash CS

SPI Flash CS

QSPI0_CS_PA23

SPI0_CS0_PA17

GND_POWER

GND_POWER

VDD_3V3

SPI0_NPCS0_PA17

QSPI0_NPCS_PA23

DISABLE_BOOT

C116

100nF

VCC

GND

U11

NL17SZ126DFT2G

1

2

3

4

5

VCC

GND

U12

NL17SZ126DFT2G

1

2

3

4

5

R184

10K

C117

100nF

R185

10K

R178

10K

CAUTION

PIO Signal Name Shared PIO Signal Description

PA24 QSPI0_IO0 NAND Flash Data0

PA25 QSPI0_IO1 NAND Flash Data1

PA26 QSPI0_IO2 NAND Flash Data2

PA27 QSPI0_IO3 NAND Flash Data3

3.2.8.3 CS Disable

On-board push button PB2 controls the selection (CS#) of the bootable memory components (QSPI and serial Flash)

using a non-inverting 3-state buffer.

Figure 3-19. CS Disable

SAMA5D2-PTC-EK

Board Components

The rule of operation is:

• PB2 (DISABLE_BOOT) and PB3 (RESET) pressed = booting from QSPI or optional serial Flash is disabled.

Refer to the SAMA5D2 Series datasheet for more information on standard boot strategies and sequencing.

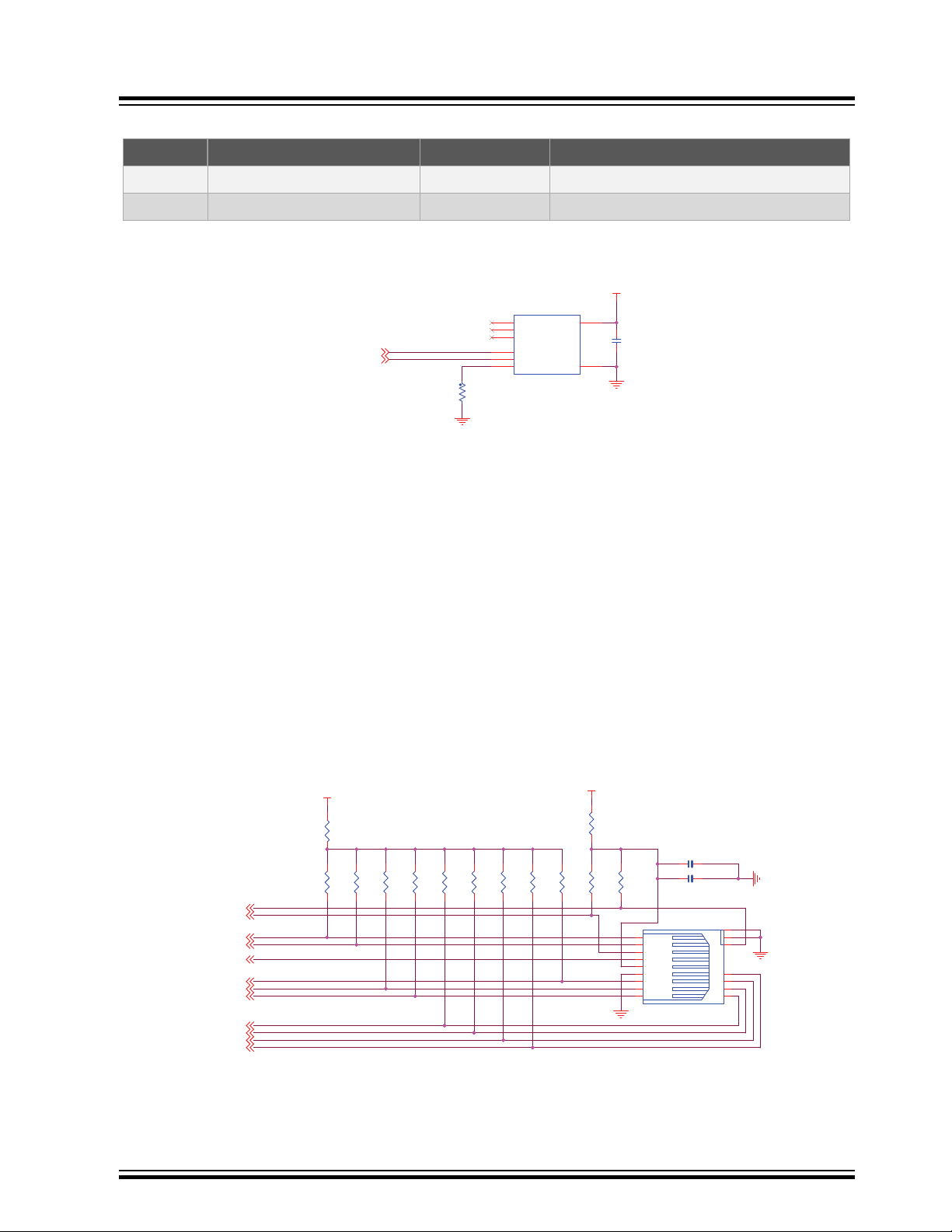

3.2.8.4 Serial EEPROM with Unique MAC Address

The SAMA5D2-PTC-EK board embeds one Microchip 24AA02E48 I²C serial EEPROM connected on the TWI1

interface.

The TWI interface is I2C-compatible and similarly uses only two lines, namely serial data (SDA) and serial clock

(SCL). According to the standard, the TWI clock rate is limited to 400 kHz in Fast mode and 100 kHz in Normal

mode, but configurable baud rate generator permits the output data rate to be adapted to a wide range of core clock

frequencies. The TWI is used in Master mode.

The 24AA02E48 features 2048 bits of Serial Electrically-Erasable Programmable Read-Only Memory (EEPROM)

organized as 256 words of eight bits each and is accessed via an I2C-compatible (2-wire) serial interface. In addition,

the 24AA02E48 incorporates an easy and inexpensive method to obtain a globally unique MAC or EUI address

(EUI-48™).

The EUI-48 addresses can be assigned as the actual physical address of a system hardware device or node, or it

can be assigned to a software instance. These addresses are factory-programmed by Microchip and guaranteed

unique. They are permanently write-protected in an extended memory block located outside the standard 2-Kbit

memory array.

The EEPROM device is used as a “software label” to store board information such as chip type,

© 2019 Microchip Technology Inc.

manufacturer name and production date, using the last two 16-byte blocks in memory. The information

contained in these blocks should not be modified.

DS50002709B-page 19

Page 20

Table 3-6. EEPROM PIOs Signal Descriptions

TWD1

TWCK1

GND_POWER

VDD_3V3

GND_POWER

TWD1_PC6

TWCK1_PC7

C118

100nF

C0402

R188

10K

R0402

U15

24AA02E48

8MA2

A0

1

A1

2

A2

3

GND

4

SDA

5

SCL

6

WP

7

VCC

8

(MCI0_C D)

(MCI0_WP)

(MCI0_DA1)

(MCI0_DA0)

(MCI0_CK)

(MCI0_CD A)

(MCI0_DA3)

(MCI0_DA2)

(MCI0_DA4)

(MCI0_DA5)

(MCI0_DA7)

(MCI0_DA6)

GND_POWER

GND_POWER

VDDSDHC

VDD_3V3

SDMMC0_CK_PA0

SDMMC0_CMD_PA1

SDMMC0_DAT1_PA3

SDMMC0_DAT2_PA4

SDMMC0_DAT3_PA5

SDMMC0_DAT4_PA6

SDMMC0_DAT5_PA7

SDMMC0_DAT6_PA8

SDMMC0_DAT7_PA9

SDMMC0_WP_PA12

SDMMC0_CD_PA13

SDMMC0_DAT0_PA2

R154

0R

R0402

R169

10k

R0402

R167

68k

R0603

R173

10k

R0402

C110 10uF

C0603

R161

68k

R0603

R155

68k

R0603

R163

68k

R0603

J6

7SDMM-B0-2211

con_kingconn_7sdmm_2211

8

5

7

6

4

3

2

1

9

14

15

16

13

12

11

10

R165

68k

R0603

R171

0R

R0402

R157

68k

R0603

R172

10k

R0402

C111 100nF

C0402

R158

68k

R0603

R159

68k

R0603

PIO Signal Name Shared Signal Description

PC6 TWD1 XPRO TWI Data

PC7 TWCL1 XPRO TWI Clock

The figure below illustrates the implementation for the EEPROM.

Figure 3-20. EEPROM 24AA02E48

3.2.9 Secure Digital Multimedia Card (SDMMC) Interface

The SD (Secure Digital) Card is a non-volatile memory card format used as a mass storage memory in mobile

devices.

SAMA5D2-PTC-EK

Board Components

3.2.9.1 Secure Digital Multimedia Card (SDMMC) Controller

The SAMA5D2-PTC-EK board has two Secure Digital Multimedia Card (SDMMC) interfaces that support the

MultiMedia Card (e.MMC) Specification V4.41, the SD Memory Card Specification V3.0, and the SDIO V3.0

specification. It is compliant with the SD Host Controller Standard V3.0 Specification.

• The SDMMC0 interface is connected to a standard SD card interface.

• The SDMMC1 interface is connected to a microSD card interface.

3.2.9.2 SDMMC0 Card Connector

A standard MMC/SD card connector, connected to SDMMC0, is mounted on the top side of the board. The SDMMC0

communication is based on a 12-pin interface (clock, command, data (8) and power lines (2)). A card detection switch

is included.

The figure below illustrates the implementation for the SDMMC0 interface.

Figure 3-21. SDMMC0 Standard SD Socket

© 2019 Microchip Technology Inc.

DS50002709B-page 20

Page 21

Figure 3-22. Standard SD Socket J6 Location

SAMA5D2-PTC-EK

Board Components

The table below describes the pin assignment of SD/MMC connector J6.

Table 3-7. Standard SD Socket J6 Pin Assignment

Pin No Signal Name Signal Description

1 MCI0_DA3 SDMMC0_DAT3_PA5

2 MCI0_CDA SDMMC0_CMD_PA1

3 GND GND

4 VCC VDDSDHC (3.3V or 1.8V)

5 MCI0_CK SDMMC0_CK_PA0

6 MCI0_CD SDMMC0_CD_PA13 (card detect)

7 MCI0_DA0 SDMMC0_DAT0_PA2

8 MCI0_DA1 SDMMC0_DAT1_PA3

9 MCI0_DA2 SDMMC0_DAT2_PA4

10 MCI0_DA4 SDMMC0_DAT4_PA6

11 MCI0_DA5 SDMMC0_DAT5_PA7

12 MCI0_DA6 SDMMC0_DAT6_PA8

13 MCI0_DA7 SDMMC0_DAT7_PA9

14 MCI0_WP SDMMC0_WP_PA12

© 2019 Microchip Technology Inc.

DS50002709B-page 21

Page 22

...........continued

GND_POWER

GND_POWER

VDD_3V3

VDD_3V3

VDDSDHC1V8

VDDSDHC

SDMMC0_VDDSEL_PA11

U9

ADG849YKSZ-REEL

SC70

S2

6

S1

4

IN

1

GND

3

D

5

VDD

2

R151 DNP

R0402

R150

10k

R0402

R152 DNP

R0402

C107

100nF

C0402

(MCI1_DA1)

(MCI1_DA0)

(MCI1_CK)

(MCI1_CD A)

(MCI1_DA3)

(MCI1_DA2)

(MCI1_C D)

GND_POWER

GND_POWER

VDD_3V3

SDMMC1_CK_PA22

SDMMC1_CD_PA30

SDMMC1_CMD_PA28

SDMMC1_DAT1_PA19

SDMMC1_DAT0_PA18

SDMMC1_DAT2_PA20

SDMMC1_DAT3_PA21

R160

10k

R0402

R162

68k

R0603

R170

10k

R0402

R164

68k

R0603

R166

68k

R0603

R168

68k

R0603

C109

100nF

C0402

C108

10uF

C0603

SW1

SW2

J7

PJS008-2120-0

Micro_SD_PJS008

8

5

7

6

4

3

2

1

9

13

12

11

10

14

Pin No Signal Name Signal Description

15 GND GND

16 GND GND

3.2.9.3 SDMMC0 VDDHC Voltage Switching

The board uses an ADG849 to switch the power line VDDSDHC_3V3 or VDDSDHC_1V8 through the command line

SDMMC0_VDDSEL_PA11.

Figure 3-23. SDMMC0 VDDSDHC Voltage Switching

SAMA5D2-PTC-EK

Board Components

Table 3-8. SDMMC1 Power Command

PIO Signal Name Signal Description

PA11 SDMMC0_VDDSEL Selects 3.3V or 1.8V

3.2.9.4 SDMMC1 Card Connector

A microSD card connector, connected to SDMMC1, is mounted on the top side of the board. The SDMMC1

communication is based on a 9-pin interface (clock, command, card detect, four data and power lines). A card

detection switch is included. The microSD connector can be used to connect any microSD card for mass storage.

Figure 3-24. SDMMC1 microSD Socket

© 2019 Microchip Technology Inc.

DS50002709B-page 22

Page 23

Figure 3-25. microSD Socket J7 Location

SAMA5D2-PTC-EK

Board Components

The table below describes the pin assignment of microSD connector J7.

Table 3-9. microSD Socket J7 Pin Assignment

Pin No Signal Name PIO Shared Signal Description

1 SDMMC1_DAT2 PA20 – Data bit 2

2 SDMMC1_DAT3 PA21 – Data bit 3

3 SDMMC1_CDA PA28 – Command

4 VCC – – 3.3V supply voltage

5 SDMMC1_CK PA22 – Clock

6 GND – – Common ground

7 SDMMC1_DAT0 PA18 – Data bit 0

8 SDMMC1_DAT1 PA19 – Data bit 1

9 SW1 GND – Not used

10 SDMMC1_CD PA30 – Card detection switch

11 GND – – Common ground

© 2019 Microchip Technology Inc.

DS50002709B-page 23

Page 24

...........continued

top/bo t

top/bo t

top/bo t

top/bo t

ETH_LED0

TX+

ETH_XI

ETH_XO

ETH_LED1

TX-

RX+

RX-

GND_POWER

GND_POWER

GND_POWER

GND_POWER

VDDA_3V3

VDD_3V3

VDD_3V3

VDD_3V3

ETH_INT_PB24

ETH_GTXCK_PB14

ETH_GTXEN_PB15

ETH_GRXDV_PB16

ETH_GRXER_PB17

ETH_GRX0_PB18

ETH_GRX1_PB19

ETH_GTX0_PB20

ETH_GTX1_PB21

ETH_GMDC_PB22

ETH_GMDIO_PB23

NRST

R200

10K

R0402

R198

1K

R0402

R202

10K

R0402

U17

KSZ8081RNB

qfn32_1p5h

RXC/B-CAST_OFF

19

CRS/CONFIG1

29

COL/CONFIG0

28

TXD1

25

TXD0

24

TXEN

23

RXD3/PHYAD0

13

RXD2/PHYAD1

14

RXD1/PHYAD2

15

RXD0/DUPLEX

16

RXDV/CONFIG2

18

RXER/ISO

20

MDC

12

MDIO

11

INTRP/NAND

21

VDDA_3V3

3

VDDIO

17

RESET

32

TXP

7

TXM

6

RXP

5

RXM

4

VDD_1V2

2

GND

1

PADDLE

33

TXC

22

TXD2

26

TXD3

27

REXT

10

XO

8

XI

9

LED0/NWAYEN

30

LED1/SPEED

31

R193

10K

R0402

R197

1K

R0402

C130

100nF

C0402

R192

10K

R0402

C128

10uF

C0603

R199

10K

R0402

C129

100nF

C0402

R203

10K

R0402

R204

10K

R0402

C123 2.2uF

C0603

C127

10uF

C0603

C124 100nF

C0402

R205

10K

R0402

L19

BLM18PG181SN1D

R0603

1 2

R206

10K

R0402

R194 6.49K 1%

R0402

R196 0R

R0402

R201

10K

R0402

Pin No Signal Name PIO Shared Signal Description

12 GND – – Common ground

13 GND – – Common ground

14 GND – – Common ground

3.2.10 Communication Interfaces

The SAMA5D2-PTC-EK board is equipped with Ethernet and USB host/device communication interfaces. This

section describes the signals and connectors related to the ETH and USB communication interfaces.

3.2.10.1 Ethernet 10/100 (GMAC) Port

The SAMA5D2-PTC-EK board features a Micrel PHY device (KSZ8081) operating at 10/100 Mb/s. The board

supports RMII interface modes. The Ethernet interface consists of two pairs of low-voltage differential pair signals

designated from GRX± and GTX± plus control signals for link activity indicators. These signals can be used to

connect to a 10/100 Base-T RJ45 connector integrated on the SAMA5D2-PTC-EK board.

An individual 48-bit MAC address (Ethernet hardware address) is allocated to each product. This number is stored in

the Microchip 24AA02E48 I2C serial EEPROM (refer to Serial EEPROM with Unique MAC Address).

Additionally, for monitoring and control purposes, a LED functionality is carried on the RJ45 connectors to indicate

activity, link, and speed status.

For more information about the Ethernet controller device, refer to the Micrel KSZ8081RN controller manufacturer's

datasheet.

Figure 3-26. Ethernet Interface

SAMA5D2-PTC-EK

Board Components

© 2019 Microchip Technology Inc.

Table 3-10. Ethernet PHY 10/100 Signal Descriptions

PIO Signal Name Shared Signal Description

PB14 ETH_GTXCK _ Transmit clock

PB15 ETH_GTXEN _ Transmit enable

PB16 ETH_GRXDV _ Receive data valid

DS50002709B-page 24

Page 25

LINK

ACT

ETH_LED0

TX+

ETH_LED1

RX-

RX+

TX-

EARTH_ETH

EARTH_ETH

GND_ETH

VDD_3V3

R190 510R

R0402

C122

100nF

C0402

C121

100nF

C0402

1

2

3

6

4

5

7

8

75

75

75 75

1nF

TD+

TD-

CT

NC

RD-

CT

TX+

TX-

RX+

RX-

RD+

Left Green LED

Right yellow LED

J8 13F-64GYD2PL2NL

rj45_13f-64gy_P12_4

1

2

7

8

3

6

5

4

9

10

11

12

13

14

15

16

R189 510R

R0402

SAMA5D2-PTC-EK

...........continued

PIO Signal Name Shared Signal Description

PB17 ETH_GRXER _ Receive error

PB18 ETH_GRX0 _ Receive data 0

PB19 ETH_GRX1 _ Receive data 1

PB20 ETH_GTX0 _ Transmit data 0

PB21 ETH_GTX1 _ Transmit data 1

PB22 ETH_GMDC _ Management data clock

PB23 ETH_GMDIO _ Management data in/out

PB24 ETH_GTX_INT _ Interrupt (open drain)

Figure 3-27. Ethernet PHY Connector J8

Board Components

© 2019 Microchip Technology Inc.

DS50002709B-page 25

Page 26

Figure 3-28. Ethernet RJ45 Connector J8 Location

SAMA5D2-PTC-EK

Board Components

The table below describes the pin assignment of Ethernet connector J8.

Table 3-11. Ethernet RJ45 Connector J8 Pin Assignment

Pin No Signal Name Signal Description

1 TX+ Transmit

2 TX- Transmit

3 RX+ Receive

4 Decoupling capacitor –

5 Decoupling capacitor –

6 RX- Receive

7 NC –

8 EARTH / GND Common ground

9 ACT LED LED activity

10 ACT LED LED activity

11 LINK LED LED link connection

12 LINK LED LED link connection

13 EARTH / GND Common ground

14 EARTH / GND Common ground

© 2019 Microchip Technology Inc.

DS50002709B-page 26

Page 27

...........continued

Pin No Signal Name Signal Description

15 NC –

16 NC –

3.2.10.2 USB Host/Device A, B

The USB (Universal Serial Bus) is a hot-pluggable general-purpose high-speed I/O standard for computer

peripherals. The standard defines connector types, cabling, and communication protocols for interconnecting a wide

variety of electronic devices. The USB 2.0 Specification defines data transfer rates as high as 480 Mbps (also known

as High Speed USB). A USB host bus connector uses 4 pins: a power supply pin (5V), a differential pair (D+ and Dpins) and a ground pin.

The SAMA5D2-PTC-EK board features three USB communication ports named USB-A to USB-C:

• USB-A device interface

– One USB device standard micro-AB connector.

– This port has a VBUS detection function made through the R148-R149 resistor bridge.

– The USB-A port is used as a primary power source and as a communication link for the board, and derives

power from the PC over the USB cable. In most cases, this port is limited to 500 mA.

• USB-B (host port B high- and full-speed interface)

– One USB host type A connector.

– The USB-B host port is equipped with a 500 mA high-side power switch to enable powering devices

connected to it.

• UBC-C (High-Speed Inter-Chip/HSIC port)

– One USB high-speed host port with an HSIC interface.

– The port is connected to a single 2-pin jumper.

SAMA5D2-PTC-EK

Board Components

© 2019 Microchip Technology Inc.

DS50002709B-page 27

Page 28

3.2.10.3 USB-A Interface

GND_POWER

EARTH_USB_A

GND_POWER

GND_POWER

VBUS_USBA

USBA_VBUS_5V_PB11

USBA_DP

USBA_DM

C103

20pF

C0402

VBUS

SHD

DM

DP

ID

GND

J4

MicroUSB AB Connector

USBMICRO5_6A

1

2

3

4

5

8

6

11

7

9

10

R149

200K

R0402

R148 100K

R0402

Figure 3-29. USB-A Type Micro-AB Connector J4 Location

SAMA5D2-PTC-EK

Board Components

3.2.10.4 USB-A VBUS Detection

The USB-A port (J4) features a VBUS detection function provided by the R148-R149 resistor bridge.

The figure below shows the USB implementation on the USBA port.

Figure 3-30. USB-A Power and VBUS Detection

Table 3-12. USB-A PIO Signal Descriptions

PIO Signal Name Shared Signal Description

PB11 USBA_VBUS_5V – VBUS insertion detection

© 2019 Microchip Technology Inc.

DS50002709B-page 28

Page 29

3.2.10.5 USB-B Interface

USBB_VBUS_5V

GND_POWER

EARTH_USB_B

USBB_DP

USBB_DM

A

J3

Single USB Type A

USB4_2AL

VBUS

1

DM

2

DP

3

GND

4

SH1

5

SH2

6

The figure below shows the USB implementation on the USB-B port.

Figure 3-31. USB-B Interface

Figure 3-32. USB-B Type A Connector J3 Location

SAMA5D2-PTC-EK

Board Components

Table 3-13. USB-B PIO Signal Descriptions

PIO Signal Name Shared Signal Description

PB12 USBB_EN_5V – Power switch enable (active high)

PB13 USBB_OVCUR – Indicates overcurrent (open drain)

3.2.10.5.1 USB-B Power Switch

The USB-B Host port is equipped with a 500 mA high-side power switch for self-powered and bus-powered

applications. If the client device is bus-powered, the carrier can supply a 5V, 500mA power to the client device. The

USBB_EN_5V_PB12 signal controls the power switch and current limiter, the Micrel MIC2025, which in turn supplies

power to a bus-powered client device. Per the USB specification, bus-powered USB 2.0 devices are limited to a

© 2019 Microchip Technology Inc.

DS50002709B-page 29

Page 30

maximum of 500 mA. The MIC2025 limits the current and indicates an overcurrent with the USBB_OVCUR_PB13

HSIC_DATA

HSIC_STRB

J5

DNP

1

2

signal.

The table below describes the pin assignment of the USB-A and USB-B connectors.

Table 3-14. USB-A and USB-B Connector Signal Descriptions

3.2.10.6 HSIC

High-Speed Inter-Chip (HSIC) is a standard for USB chip-to-chip interconnect with a 2-signal (strobe, data) source

synchronous serial interface using 240 MHz DDR signaling to provide only high-speed 480 Mbps data rate.

The interface operates at high speed, 480 Mbps, and is fully compatible with existing USB software stacks. It meets

all data transfer needs through a single unified USB software stack.

The HSIC interface is not used on the board and is connected to two-point jumper J5 (not mounted).

Figure 3-33. HSIC Interface

SAMA5D2-PTC-EK

Board Components

Pin No Signal Name Signal Description

1 VBUS 5V power

2 DM Data minus

3 DP Data plus

4 ID On-the-go identification

5 GND Common ground

3.3 External Interfaces

3.3.1 LCD TFT Interface

This section describes the signals and connectors related to the LCD interface.

3.3.1.1 LCD Interface

The SAMA5D2-PTC-EK board provides a connector with 18 bits of data and control signals to the LCD interface.

Other signals are used to control the LCD and are available on connector J16: TWI, SPI, two GPIOs for interrupt, 1wire and power supply lines.

This connector is used to connect LCD display series 43xx or 70xx from PDA.

3.3.1.2 LCD Expansion Header

J16 is a 1.27-mm pitch, 50-pin header. It gives access to the LCD signals.

© 2019 Microchip Technology Inc.

DS50002709B-page 30

Page 31

Figure 3-34. LCD Expansion Header Interface

GND_POWER

VDD_3V3VDD_MAIN_5V

LCD_D2_PC10

LCD_D3_PC11

LCD_D4_PC12

LCD_D5_PC13

LCD_D6_PC14

LCD_D7_PC15

LCD_D10_PC16

LCD_D11_PC17

LCD_D12_PC18

LCD_D13_PC19

LCD_D14_PC20

LCD_D15_PC21

LCD_D18_PC22

LCD_D19_PC23

LCD_D20_PC24

LCD_D21_PC25

LCD_D22_PC26

LCD_D23_PC27

LCD_PCLK_PD0

LCD_VSYNC_PC30

LCD_HSYNC_PC31

LCD_DE_PD1

LCD_EN_PC29

LCD_IRQ1_PC9

LCD_IRQ2_PD2

LCD_PWM_PC28

SPI_CS_PB31

SPI_SCK_PB30

SPI_MISO_PB29

SPI_MOSI_PB28

TWI_SCL_PB29

TWI_SDA_PB28

NRST

SPI_CS_PB31

R230

DNP

R0603

R231

0R

R0603

R234

100R-1%

R0402

J16

XF2M-5015-1A

FPC50-0p5mm

ID

1

GND1

2

D0

3

D1

4

D2

5

D3

6

GND2

7

D4

8

D5

9

D6

10

D7

11

GND3

12

D8

13

D9

14

D10

15

D11

16

GND4

17

D12

18

D13

19

D14

20

D15

21

GND5

22

D16

23

D17

24

D18

25

D19

26

GND6

27

D20

28

D21

29

D22

30

D23

31

GND7

32

PCLK/CMD

33

VSYNC/CS

34

HSYNC/WE

35

DE/RE

36

SPI_SCK

37

SPI_MOSI

38

SPI_MISO

39

SPI_CS

40

ENABLE

41

TWI_SDA

42

TWI_SCL

43

IRQ1

44

IRQ2

45

PWM

46

RESET

47

VCC1

48

VCC2

49

GND8

50

SAMA5D2-PTC-EK

Board Components

3.3.1.3 LCD Power

In order to operate correctly with various LCD modules, two voltage lines are available: 3.3V and 5VCC (default). The

selection is made with 0R resistors R230 and R231.

© 2019 Microchip Technology Inc.

DS50002709B-page 31

Page 32

3.3.1.4 LCD Connector JX

Figure 3-35. LCD Connector J16 Location

SAMA5D2-PTC-EK

Board Components

The table below describes the pin assignment of LCD FPC connector J16.

Table 3-15. LCD Connector J16 Signal Descriptions

Pin No Signal PIO Signal RGB Interface Function

1 ID PB31 _ ID LCD module

2 GND – GND GND

3 LCDDAT0 – D0 –

4 LCDDAT1 – D1 –

5 LCDDAT2 PC10 D2 Data line

6 LCDDAT3 PC11 D3 Data line

7 GND – GND GND

8 LCDDAT4 PC12 D4 Data line

9 LCDDAT5 PC13 D5 Data line

10 LCDDAT6 PC14 D6 Data line

11 LCDDAT7 PC15 D7 Data line

12 GND – GND GND

© 2019 Microchip Technology Inc.

DS50002709B-page 32

Page 33

SAMA5D2-PTC-EK

...........continued

Pin No Signal PIO Signal RGB Interface Function

13 LCDDAT8 – D8 –

14 LCDDAT9 – D9 –

15 LCDDAT10 PC16 D10 Data line

16 LCDDAT11 PC17 D11 Data line

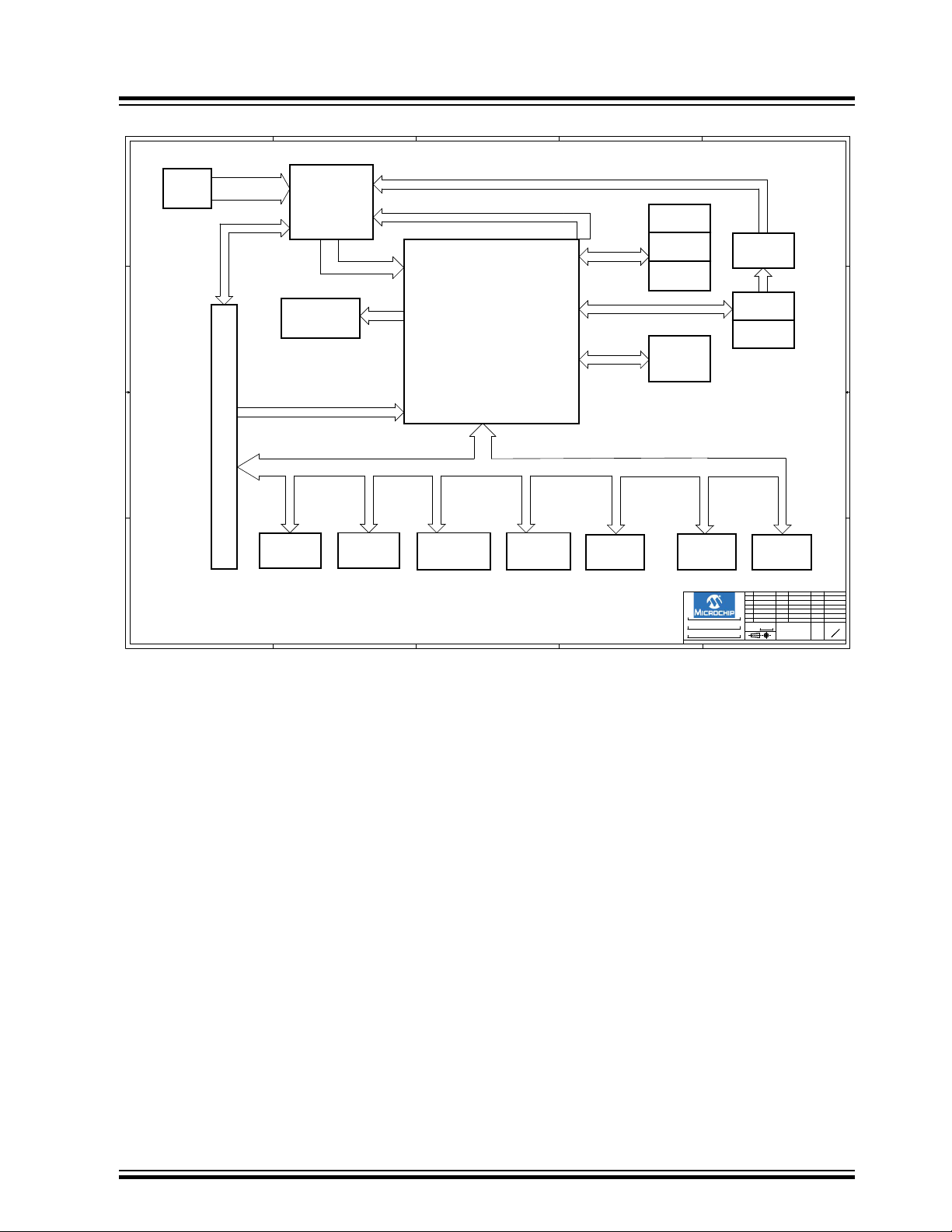

17 GND GND GND GND

18 LCDDAT12 PC18 D12 Data line

19 LCDDAT13 PC19 D13 Data line

20 LCDDAT14 PC20 D14 Data line

21 LCDDAT15 PC21 D15 Data line

22 GND – GND GND

23 LCDDAT16 – D16 –

24 LCDDAT17 – D17 –

25 LCDDAT18 PC22 D18 Data line

Board Components

26 LCDDAT19 PC23 D19 Data line

27 GND – GND GND

28 LCDDAT20 PC24 D20 Data line

29 LCDDAT21 PC25 D21 Data line

30 LCDDAT22 PC26 D22 Data line

31 LCDDAT23 PC27 D23 Data line

32 GND – GND GND

33 LCDPCK PD0 PCLK Pixel clock

34 LCDVSYNC PC30 VSYNC/CS Vertical sync

35 LCDHSYNC PC31 HSYNC/WE Horizontal sync

36 LCDDEN PD1 DATA_ENABLE Data enable

37 SPI_SPCK PB30 SPI_SCK –

38 SPI_MOSI PB28 SPI_MOSI (Shared with TWI)

39 SPI_MISO PB29 SPI_MISO (Shared with TWI)

40 SPI_NPCS0 PB31 SPI_CS –

41 LCDDISP PC29 ENABLE Display enable signal

42 TWD PB28 TWI_SDA I2C data line (maXTouch)

43 TWCK PB29 TWI_SCL I2C clock line (maXTouch)

44 GPIO PC9 IRQ1 maXTouch interrupt line

45 GPIO PD2 IRQ2 Interrupt line for other I2C devices

46 LCDPWM PC28 PWM Backlight control

47 RESET – RESET Reset for both display and maXTouch

© 2019 Microchip Technology Inc.

DS50002709B-page 33

Page 34

...........continued

LED

VDD_3V3

GND_POWER

GND_POWER

GND_POWER

GND_POWER

GND_POWER

LED_RED_PB10

LED_GREEN_PB8

LED_BLUE_PB6

R240 1K

R0402

R182 100R-1%

R0402

R183 100R-1%

R0402

R244

10K

Q7

BSS138

SOT23_123

1

3

2

R181 100R-1%

R0402

D4

CLV1A-FKB-CJ1M1F1BB7R4S3

Red

1

Green

4

Blue

3

Anode

2

R241 1K

R0402

R239 2.2K-1%

R0402

Q5

BSS138

SOT23_123

1

3

2

R243

10K

Q6

BSS138

SOT23_123

1

3

2

Pin No Signal PIO Signal RGB Interface Function

48 Main_5V/3.3V VCC VCC 3.3V or 5V supply (0R)

49 Main_5V/3.3V VCC VCC 3.3V or 5V supply (0R)

50 GND – GND GND

3.3.2 RGB LED

The SAMA5D2-PTC-EK board features one RGB LED which can be controlled by the user. The three LED cathodes

are controlled via GPIO PWM or timer/counter pins.

Figure 3-36. RGB LED Indicators

SAMA5D2-PTC-EK

Board Components

Table 3-16. RGB LED PIOS

3.4 Debugging Capabilities

The SAMA5D2-PTC-EK includes two main debugging interfaces to provide debug-level access to the SAMA5D2:

• One UART through USB J-Link-CDC

• Two JTAG interfaces, one connected directly to the MPU using connector J2 and one through the J-Link-OB

interface USB port J9

3.4.1 Debug JTAG

This section describes the signals and connectors related to the JTAG interface.

A 10-pin JTAG header is provided on the SAMA5D2-PTC-EK board to facilitate software development and debugging

using various JTAG emulators. The interface signals have a voltage level of 3.3V.

© 2019 Microchip Technology Inc.

Signal PIO Function

LED_RED PB10 TIOB3

LED_GREEN PB8 PWML3

LED_BLUE PB6 PWML2

DS50002709B-page 34

Page 35

Figure 3-37. JTAG Interface

GND_POWER

VDD_3V3

VDD_3V3

GND_POWER

NRST

CON_JTAG_Pin2

CON_JTAG_Pin4

CON_JTAG_Pin6

CON_JTAG_Pin8RTCKIN

R140

100K

R0402

R236

10K

R0402

R142

100K

R0402

R143 100R-1% R0402

R141

100K

R0402

R138 DNP

R0402

J2

Header 2X5

FTSH-105-01-F-DV-P-TR

1

2

3

4

5

6

7

8

9

10

Figure 3-38. JTAG Connector J2 Location

SAMA5D2-PTC-EK

Board Components

The table below describes the pin assignment of JTAG connector J2.

Table 3-17. JTAG/ICE Connector J2 Pin Assignment

Pin No Signal Name Signal Description

1 VTref. 3.3V power This is the target reference voltage (main 3.3V).

2 TMS TEST MODE SELECT JTAG mode set input into target CPU

3 GND Common ground

© 2019 Microchip Technology Inc.

DS50002709B-page 35

Page 36

...........continued

Pin No Signal Name Signal Description

TCK TEST CLOCK - Output timing signal, for

4

synchronizing test logic and control register

access

5 GND Common ground

TDO JTAG TEST DATA OUTPUT - Serial data

6

input from the target

RTCK - Input return test clock signal from the

7

target

TDI TEST DATA INPUT - Serial data output line,

8

sampled on the rising edge of the TCK signal

9 GND Common ground

10 nRST RESET Active-low reset signal. Target CPU reset signal.

3.4.2 Embedded Debugger (J-Link-OB) Interface

The SAMA5D2-PTC-EK includes a built-in SEGGER J-Link-On-Board device. The functionality is implemented with

an ATSAM3U4C microcontroller in an LFBGA100 package. The ATSAM3U4C provides the functions of JTAG and a

bridge USB/Serial debug port (CDC). One two-colored LED (D6) mounted near the SAM3 chip (U20) shows the

status of the J-Link-On-Board device.

J-Link-OB-ATSAM3U4C was designed in order to provide an efficient, low-cost, on-board alternative to the standard

J-Link.

The USB J-Link-OB port is used as a secondary power source and as a communication link for the board, and

derives power from the PC over the USB cable. This port is limited in most cases to 500 mA. A single PC USB port is

sufficient to power the board.

SAMA5D2-PTC-EK

Board Components

JTAG clock signal into target CPU

JTAG data output from target CPU

Some targets with a slow system clock must

synchronize the JTAG inputs to internal clocks. In the

present case, such synchronization is unneeded and

TCK is merely looped back into RTCK.

JTAG data input into target CPU

© 2019 Microchip Technology Inc.

DS50002709B-page 36

Page 37

Figure 3-39. J-Link-OB Interface

EDBG_USB_DP

EDBG_USB_DM

ENSPI

ERASE_3U

TDI_3U

TDO_3U

TCK_3U

TMS_3U

NRST_3U

TRSTIN

TRSTOUT

TRESIN

TRESOUT

TDIIN

TMSIN

TCKOUT

TMSOUT