Page 1

PIC24FJ128GA Family

Data Sheet

General Purpose,

16-Bit Flash Microcontrollers

© 2006 Microchip Technology Inc. Advance Information DS39747B

Page 2

Note the following details of the code protection feature on Microchip devices:

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device

applications and the like is provided only for your convenience

and may be superseded by updates. It is your responsibility to

ensure that your application meets with your specifications.

MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED,

WRITTEN OR ORAL, STATUTORY OR OTHERWISE,

RELATED TO THE INFORMATION, INCLUDING BUT NOT

LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE,

MERCHANTABILITY OR FITNESS FOR PURPOSE.

Microchip disclaims all liability arising from this information and

its use. Use of Microchip devices in life support and/or safety

applications is entirely at the buyer’s risk, and the buyer agrees

to defend, indemnify and hold harmless Microchip from any and

all damages, claims, suits, or expenses resulting from such

use. No licenses are conveyed, implicitly or otherwise, under

any Microchip intellectual property rights.

Trademarks

The Microchip name and logo, the Microchip logo, Accuron,

dsPIC, K

EELOQ, microID, MPLAB, PIC, PICmicro, PICSTART,

PRO MATE, PowerSmart, rfPIC and SmartShunt are

registered trademarks of Microchip Technology Incorporated

in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB,

SEEVAL, SmartSensor and The Embedded Control Solutions

Company are registered trademarks of Microchip Technology

Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, dsPICDEM,

dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR,

FanSense, FlexROM, fuzzyLAB, In-Circuit Serial

Programming, ICSP, ICEPIC, Linear Active Thermistor,

MPASM, MPLIB, MPLINK, MPSIM, PICkit, PICDEM,

PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo,

PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select

Mode, Smart Serial, SmartTel, Total Endurance, UNI/O,

WiperLock and Zena are trademarks of Microchip Technology

Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated

in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2006, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received ISO/TS-16949:2002 quality system certification for

its worldwide headquarters, design and wafer fabrication facilities in

Chandler and Tempe, Arizona and Mountain View, California in

October 2003. The Company’s quality system processes and

procedures are for its PICmicro

devices, Serial EEPROMs, microperipherals, nonvolatile memory and

analog products. In addition, Microchip’s quality system for the design

and manufacture of development systems is ISO 9001:2000 certified.

®

8-bit MCUs, KEEL

®

OQ

code hopping

DS39747B-page ii Advance Information © 2006 Microchip Technology Inc.

Page 3

PIC24FJ128GA FAMILY

General Purpose, 16-bit Flash Microcontrollers

High-Performance CPU:

• Modified Harvard Architecture

• Up to 16 MIPS operation @ 32 MHz

• 8 MHz internal oscillator:

- 4x PLL option

- Multiple divide options

• 17-bit x 17-bit Single-Cycle Hardware

Fractional/Integer Multiplier

• 32-bit by 16-bit Hardware Divider

• 16 x 16-bit Working Register Array

• C compiler Optimized Instruction Set Architecture:

- 76 base instructions

- Flexible addressing modes

• Linear Program Memory Addressing up to 12 Mbytes

• Linear Data Memory Addressing up to 64 Kbytes

• Two Address Generation Units for separate Read

and Write Addressing of Data Memory

Special Microcontroller Features:

• Operating Voltage Range of 2.0V to 3.6V

• Flash Program Memory:

- 1000 erase/write cycles, typical

- Flash retention 20 years, typical

• Self-Reprogrammable under Software Control

• Selectable Power Management modes:

- Sleep, Idle and Alternate Clock modes

• Fail-Safe Clock Monitor operation:

- Detects clock failure and switches to on-chip,

low-power RC oscillator

• On-Chip LDO Regulator

• JTAG Boundary Scan and Programming Support

• Power-on Reset (POR), Power-up Timer (PWRT)

and Oscillator Start-up Timer (OST)

• Flexible Watchdog Timer (WDT) with On-Chip,

Low-Power RC Oscillator for reliable operation

• In-Circuit Serial Programming™ (ICSP™) and

In-Circuit Emulation (ICE) via 2 pins

Analog Features:

• 10-bit, up to 16-channel Analog-to-Digital Converter

(A/D):

- 500 ksps conversion rate

- Conversion available during Sleep and Idle

• Dual Analog Comparators with Programmable

Input/Output Configuration

Peripheral Features:

• Two 3-wire/4-wire SPI modules, supporting 4 Frame

modes with 4-level FIFO Buffer

•Two I2C™ modules support Multi-Master/Slave

mode and 7-bit/10-bit Addressing

• Two UART modules:

- Supports RS-232, RS-485 and LIN 1.2

- Supports IrDA

- Auto-Wake-up on Start bit

- Auto-Baud Detect

- 4-level FIFO buffer

• Parallel Master Slave Port (PMP/PSP):

- Supports 8-bit or 16-bit data

- Supports 16 address lines

• Hardware Real-Time Clock/Calendar (RTCC):

- Provides clock, calendar and alarm functions

• Five 16-bit Timers/Counters with Programmable

prescaler

• Five 16-bit Capture Inputs

• Five 16-bit Compare/PWM Outputs

• High-Current Sink/Source on select I/O pins:

18 mA/18 mA

• Configurable Open-Drain Output on Digital I/O pins

• Up to 5 External Interrupt Sources

®

with on-chip hardware endec

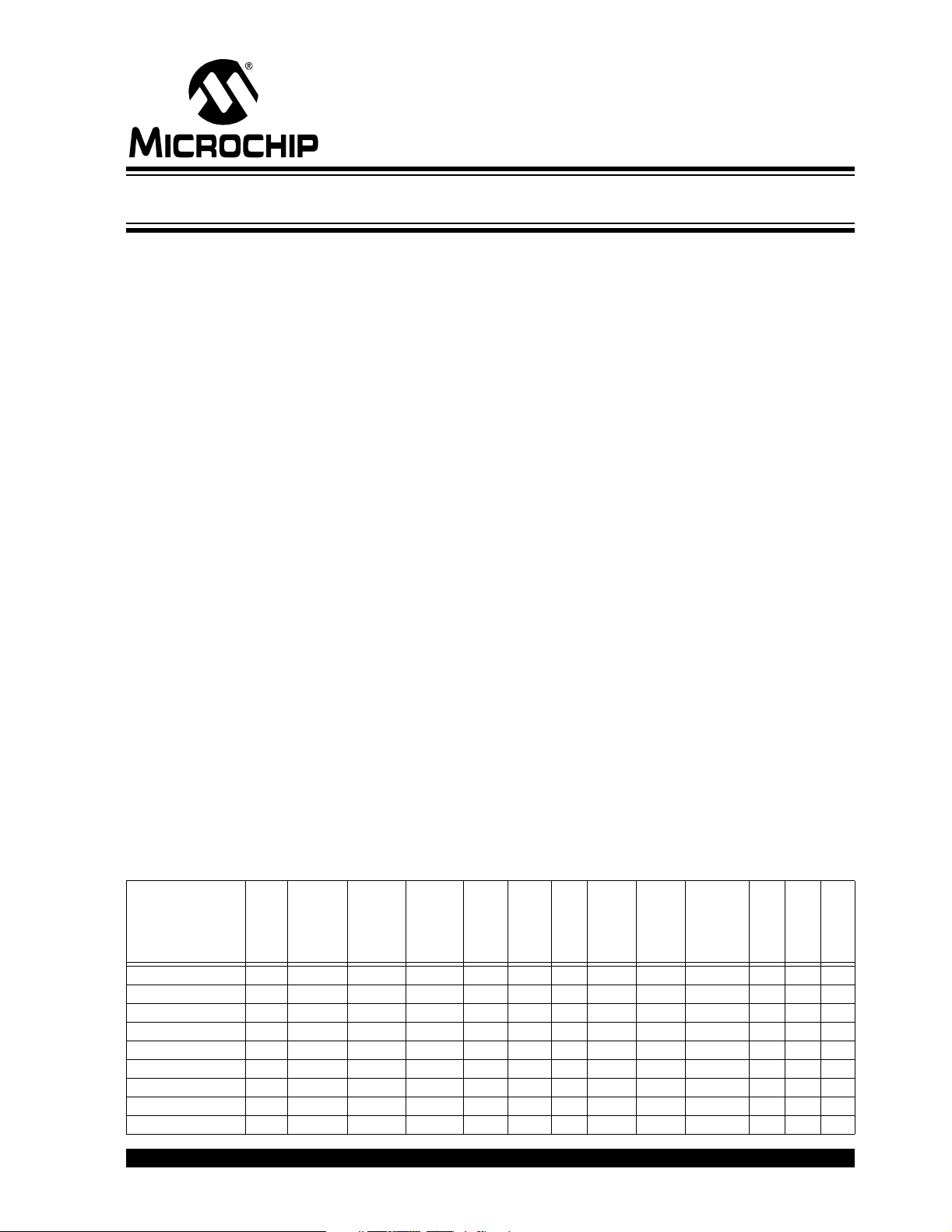

Program

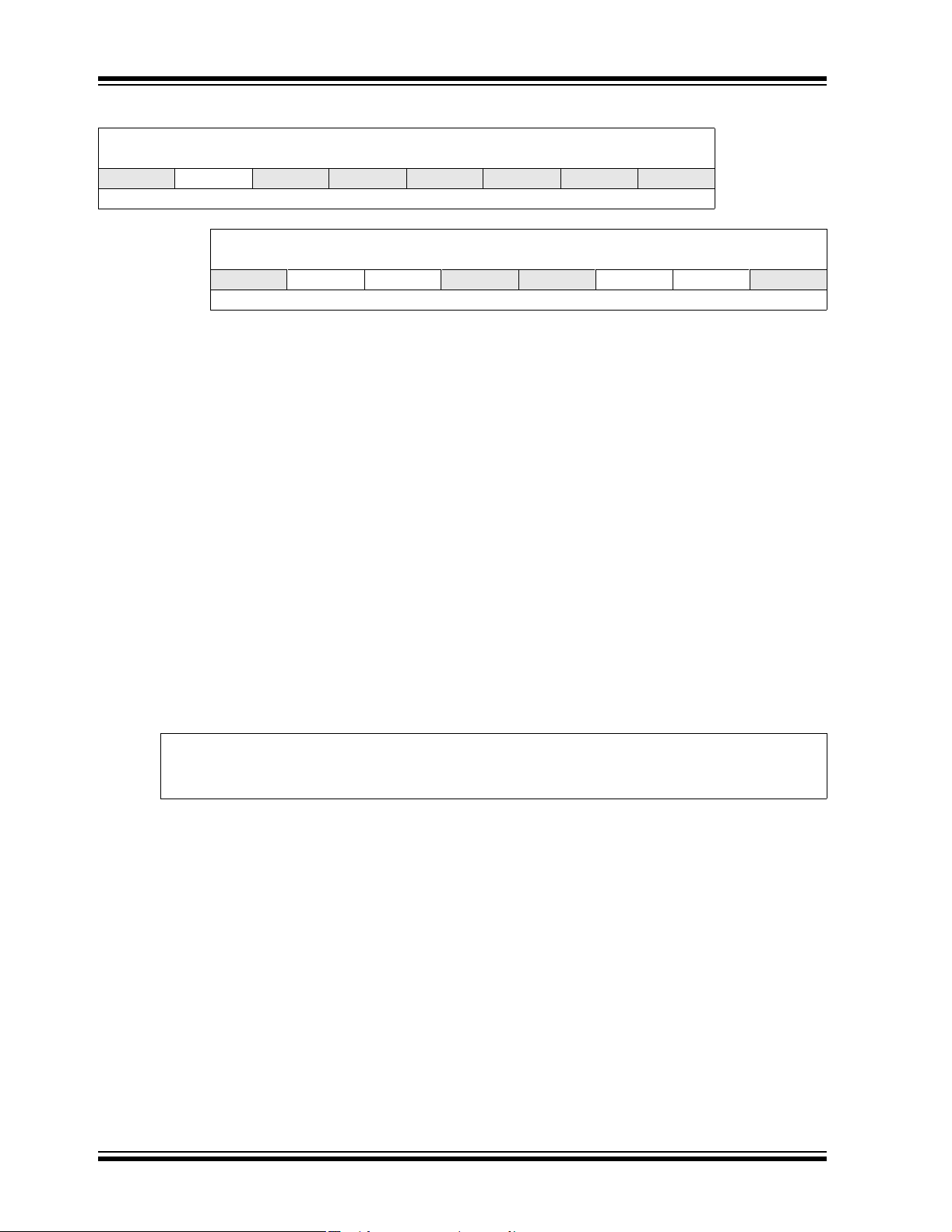

Device Pins

PIC24FJ64GA006 64 64K 8K 5 5 5 2 2 2 16 2 Y Y

PIC24FJ96GA006 64 96K 8K 5 5 5 2 2 2 16 2 Y Y

PIC24FJ128GA006 64 128K 8K 5 5 5 2 2 2 16 2 Y Y

PIC24FJ64GA008 80 64K 8K 5 5 5 2 2 2 16 2 Y Y

PIC24FJ96GA008 80 96K 8K 5 5 5 2 2 2 16 2 Y Y

PIC24FJ128GA008 80 128K 8K 5 5 5 2 2 2 16 2 Y Y

PIC24FJ64GA010 100 64K 8K 5 5 5 2 2 2 16 2 Y Y

PIC24FJ96GA010 100 96K 8K 5 5 5 2 2 2 16 2 Y Y

PIC24FJ128GA010 100 128K 8K 5 5 5 2 2 2 16 2 Y Y

© 2006 Microchip Technology Inc. Advance Information DS39747B-page 1

Memory

(Bytes)

SRAM

(Bytes)

Timers

16-bit

Input

Capture

Compare/

PWM Output

SPI I2C™

UART

10-bit

A/D (ch)

PMP/PSP

Comparators

JTAG

Page 4

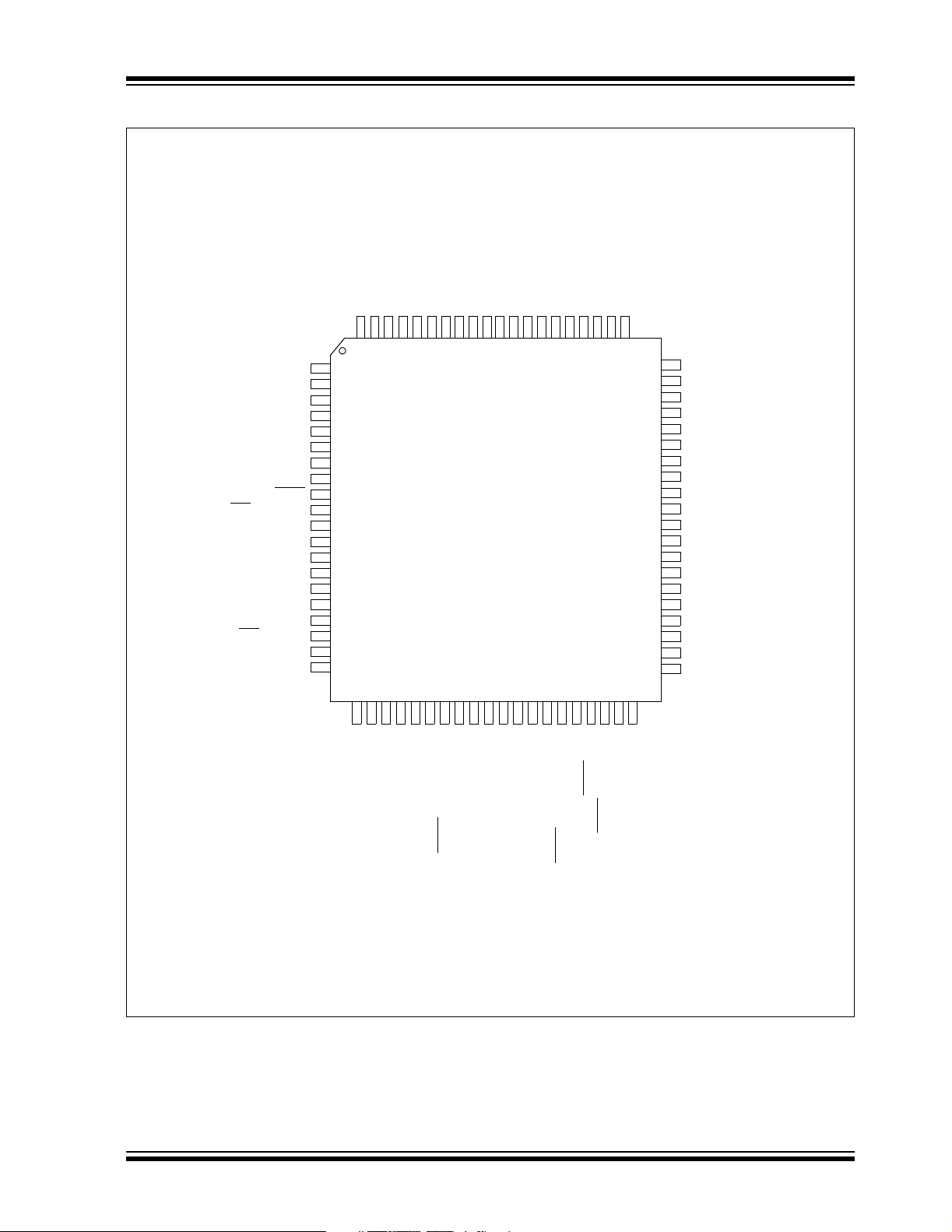

PIC24FJ128GA FAMILY

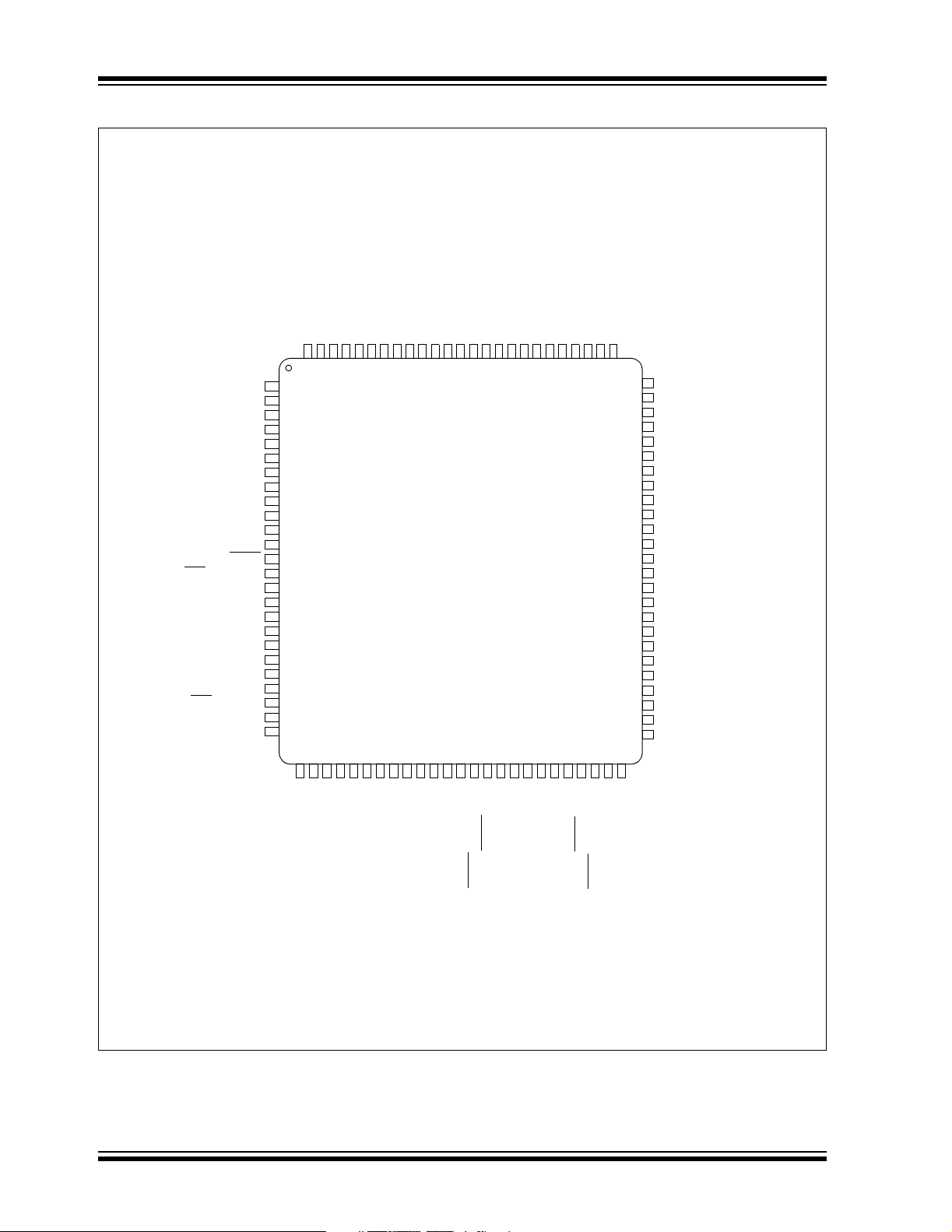

Pin Diagrams

64-Pin TQFP

PMD4/RE4

PMD3/RE3

PMD2/RE2

PMD1/RE1

PMD0/RE0

RF1

64

636261596058575654555352514950

1

2

3

4

5

6

7

8

9

DD

10

11

12

13

14

15

16

PIC24FJXXGA006

PIC24FJXXXGA006

17

18

2244242526272829303132

192021

PMA5/SCK2/CN8/RG6

PMA4/SDI2/CN9/RG7

PMA3/SDO2/CN10/RG8

PMA2/SS2

C2IN-/AN2/SS1

PGC1/EMUC1/V

PGD1/EMUD1/PMA6/V

PMD5/RE5

PMD6/RE6

PMD7/RE7

MCLR

/CN11/RG9

VSS

V

C1IN+/AN5/CN7/RB5

C1IN-/AN4/CN6/RB4

C2IN+/AN3/CN5/RB3

/CN4/RB2

REF-/AN1/CN3/RB1

REF+/AN0/CN2/RB0

RF0

ENVREG

23

CAP/VDDCORE

CN15/RD6

PMRD/CN14/RD5

PMWR/OC5/IC5/CN13/RD4

PMBE/OC4/RD3

OC3/RD2

V

CN16/RD7

OC2/RD1

48

47

46

45

43

42

41

40

39

38

37

36

35

34

33

SOSCO/T1CK/CN0/RC14

SOSCI/CN1/RC13

OC1/RD0

IC4/PMCS1/INT4/RD11

IC3/PMCS2/INT3/RD10

IC2/U1CTS

IC1/RTCC/INT1/RD8

Vss

OSC2/CLKO/RC15

OSC1/CLKI/RC12

V

DD

SCL1/RG2

SDA1/RG3

U1RTS

U1RX/SDI1/RF2

U1TX/SDO1/RF3

//INT2/RD9

/BCLK1/SCK1/INT0/RF6

PGD2/EMUD2/AN7/RB7

PGC2/EMUC2/AN6/OCFA/RB6

AVDD

SS

AV

DD

VSS

V

REF/AN10/RB10

/BCLK2/AN14/RB14

PMA7/C2OUT/AN9/RB9

TDO/PMA12/AN11/RB11

U2CTS/C1OUT/AN8/RB8

TMS/PMA13/CV

TDI/PMA10/AN13/RB13

TCK/PMA11/AN12/RB12

PMA8/U2TX/SCL2/CN18/RF5

PMA9/U2RX/SDA2/CN17/RF4

PMA0/AN15/OCFB/CN12/RB15

PMA1/U2RTS

DS39747B-page 2 Advance Information © 2006 Microchip Technology Inc.

Page 5

Pin Diagrams (Continued)

80-Pin TQFP

PMD4/RE4

PMD3/RE3

PMD2/RE2

PMD1/RE1

PMD0/RE0

PIC24FJ128GA FAMILY

CAP/VDDCORE

PMRD/CN14/RD5

PMWR/OC5/CN13/RD4

CN19/RD13

IC5/RD12

PMBE/OC4/RD3

OC3/RD2

RG0

RG1

RF0

V

ENVREG

RF1

CN16/RD7

CN15/RD6

OC2/RD1

PMD5/RE5

PMD6/RE6

PMD7/RE7

T2CK/RC1

T4CK/RC3

PMA5/SCK2/CN8/RG6

PMA4/SDI2/CN9/RG7

PMA3/SDO2/CN10/RG8

MCLR

PMA2/SS2

C1IN+/AN5/CN7/RB5

C2IN+/AN3/CN5/RB3

C2IN-/AN2/SS1

PGC1/EMUC1/AN1/CN3/RB1

PGD1/EMUD1/AN0/CN2/RB0

/CN11/RG9

VSS

V

TMS/INT1/RE8

TDO/INT2/RE9

C1IN-/AN4/CN6/RB4

/CN4/RB2

DD

TCK/PMA11/AN12/RB12

/BCLK2/AN14/RB14

TDI/PMA10/AN13/RB13

PMA1/U2RTS

6564636162

/BCLK1/RD15

CN20/U1CTS/RD14

CN21/U1RTS

PMA0/AN15/OCFB/CN12/RB15

60

SOSCO/T1CK/CN0/RC14

59

SOSCI/CN1/RC13

58

OC1/RD0

57

IC4/PMCS1/RD11

56

IC3/PMCS2/RD10

55

IC2/RD9

54

IC1/RTCC/RD8

53

SDA2/INT4/RA15

52

SCL2/INT3/RA14

51

VSS

50

OSC2/CLKO/RC15

49

OSC1/CLKI/RC12

48

V

47

46

45

44

43

42

41

40

39

PMA8/U2TX/CN18/RF5

PMA9/U2RX/CN17/RF4

DD

SCL1/RG2

SDA1/RG3

SCK1/INT0/RF6

SDI1/RF7

SDO1/RF8

U1RX/RF2

U1TX/RF3

807978

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

PGD2/EMUD2/AN7/RB7

PGC2/EMUC2/AN6/OCFA/RB6

7574737172

76

77

PIC24FJXXGA008

PIC24FJXXXGA008

26

232425

REF-/RA9

PMA7/V

27

SS

DD

AV

AV

PMA6/VREF+/RA10

U2CTS/C1OUT/AN8/RB8

7069686667

2829303132333435363738

DD

VSS

V

REF/AN10/RB10

C2OUT/AN9/RB9

PMA12/AN11/RB11

PMA13/CV

© 2006 Microchip Technology Inc. Advance Information DS39747B-page 3

Page 6

PIC24FJ128GA FAMILY

Pin Diagrams (Continued))

100-Pin TQFP

RG1

RA6

RG0

RF1

RG15

DD

V

PMD5/RE5

PMD6/RE6

PMD7/RE7

T2CK/RC1

T3CK/RC2

T4CK/RC3

PMA5/SCK2/CN8/RG6

PMA4/SDI2/CN9/RG7

PMA3/SDO2/CN10/RG8

PMA2/SS2

C1IN+/AN5/CN7/RB5

C1IN-/AN4/CN6/RB4

C2IN+/AN3/CN5/RB3

C2IN-/AN2/SS1

PGC1/EMUC1/AN1/CN3/RB1

PGD1/EMUD1/AN0/CN2/RB0

T5CK/RC4

MCLR

/CN11/RG9

SS

V

DD

V

TMS/RA0

INT1/RE8

INT2/RE9

/CN4/RB2

PMD2/RE2

RG13

PMD4/RE4

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

RG12

PMD3/RE3

969897

99

2829303132333435363738

27

RA7

RG14

PMD1/RE1

PMD0/RE0

9294939190898887868584838281807978

95

PIC24FJXXGA010

PIC24FJXXXGA010

ENVREG

RF0

40

39

CN15/RD6

PMRD/CN14/RD5

PMWR/OC5/CN13/RD4

CN19/RD13

IC5/RD12

PMBE/OC4/RD3

OC3/RD2

464748

OC2/RD1

76

77

49

V

SS

75

SOSCO/T1CK/CN0/RC14

74

SOSCI/CN1/RC13

73

OC1/RD0

72

IC4/PMCS1/RD11

71

IC3/PMCS2/RD10

70

IC2/RD9

69

IC1/RTCC/RD8

68

INT4/RA15

67

INT3/RA14

66

VSS

65

OSC2/CLKO/RC15

64

OSC1/CLKI/RC12

63

DD

V

62

TDO/RA5

61

TDI/RA4

60

SDA2/RA3

59

SCL2/RA2

58

SCL1/RG2

57

SDA1/RG3

56

SCK1/INT0/RF6

55

SDI1/RF7

54

SDO1/RF8

53

U1RX/RF2

52

U1TX/RF3

51

50

VCAP/VDDCORE

CN16/RD7

45

44

43

42

41

DD

AVSS

AV

REF-/RA9

PMA7/V

PGD2/EMUD2/AN7/RB7

PGC2/EMUC2/AN6/OCFA/RB6

C1OUT/AN8/RB8

PMA6/VREF+/RA10

C2OUT/AN9/RB9

REF/AN10/RB10

PMA13/CV

DD

VSS

V

TCK/RA1

U2CTS/RF12

/BCLK2/RF13

PMA12/AN11/RB11

PMA11/AN12/RB12

PMA10/AN13/RB13

U2RTS

DD

VSS

V

/RD14

/BCLK1/RD15

PMA1/AN14/RB14

CN20/U1CTS

PMA8/U2TX/CN18/RF5

PMA9/U2RX/CN17/RF4

CN21/U1RTS

PMA0/AN15/OCFB/CN12/RB15

DS39747B-page 4 Advance Information © 2006 Microchip Technology Inc.

Page 7

PIC24FJ128GA FAMILY

Table of Contents

1.0 Device Overview .......................................................................................................................................................................... 7

2.0 CPU............................................................................................................................................................................................ 19

3.0 Memory Organization ................................................................................................................................................................. 25

4.0 Flash Program Memory.............................................................................................................................................................. 45

5.0 Resets ........................................................................................................................................................................................ 51

6.0 Interrupt Controller ..................................................................................................................................................................... 57

7.0 Oscillator Configuration.............................................................................................................................................................. 91

8.0 Power-Saving Features .............................................................................................................................................................. 97

9.0 I/O Ports ..................................................................................................................................................................................... 99

10.0 Timer1 ...................................................................................................................................................................................... 101

11.0 Timer2/3 and Timer4/5 ............................................................................................................................................................ 103

12.0 Input Capture............................................................................................................................................................................ 109

13.0 Output Compare....................................................................................................................................................................... 111

14.0 Serial Peripheral Interface (SPI)............................................................................................................................................... 115

15.0 Inter-Integrated Circuit (I

16.0 Universal Asynchronous Receiver Transmitter (UART) ........................................................................................................... 131

17.0 Parallel Master Port .................................................................................................................................................................. 139

18.0 Real-Time Clock and Calendar ................................................................................................................................................ 149

19.0 Programmable Cyclic Redundancy Check (CRC) Generator .................................................................................................. 161

20.0 10-bit High-Speed A/D Converter............................................................................................................................................. 165

21.0 Comparator Module.................................................................................................................................................................. 173

22.0 Comparator Voltage Reference................................................................................................................................................ 177

23.0 Special Features ...................................................................................................................................................................... 179

24.0 Instruction Set Summary .......................................................................................................................................................... 189

25.0 Development Support............................................................................................................................................................... 197

26.0 Electrical Characteristics .......................................................................................................................................................... 201

27.0 Packaging Information.............................................................................................................................................................. 213

Appendix A: Revision History............................................................................................................................................................. 219

Index ................................................................................................................................................................................................. 221

The Microchip Web Site..................................................................................................................................................................... 225

Customer Change Notification Service .............................................................................................................................................. 225

Customer Support .............................................................................................................................................................................. 225

Reader Response .............................................................................................................................................................................. 226

Product Identification System ............................................................................................................................................................ 227

2

C™) ................................................................................................................................................. 123

© 2006 Microchip Technology Inc. Advance Information DS39747B-page 5

Page 8

PIC24FJ128GA FAMILY

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at docerrors@microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150. We

welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision

of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are

using.

Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

DS39747B-page 6 Advance Information © 2006 Microchip Technology Inc.

Page 9

PIC24FJ128GA FAMILY

1.0 DEVICE OVERVIEW

This document contains device specific information for

the following devices:

• PIC24FJ64GA006

• PIC24FJ64GA008

• PIC24FJ64GA010

• PIC24FJ96GA006

• PIC24FJ96GA008

• PIC24FJ96GA010

• PIC24FJ128GA006

• PIC24FJ128GA008

• PIC24FJ128GA010

This family introduces a new line of Microchip devices:

a 16-bit RISC microcontroller family with a broad

peripheral feature set and enhanced computational

performance. The PIC24FJ128GA family offers a new

migration option for those high-performance applications which may be outgrowing their 8-bit platforms, but

don’t require the numerical processing power of a

digital signal processor.

1.1 Core Features

1.1.1 16-BIT ARCHITECTURE

Central to all PIC24 devices is the 16-bit modified

Harvard architecture, first introduced with Microchip’s

dsPIC® digital signal controllers. The PIC24 CPU core

offers a wide range of enhancements, such as:

• 16-bit data and 24-bit address paths, with the

ability to move information between data and

memory spaces

• Linear addressing of up to 8 Mbytes (program

space) and 64 Kbytes (data)

• A 16-element working register array with built-in

software stack support

• A 17 x 17 hardware multiplier with support for

integer math

• Hardware support for 32 by 16-bit division

• An instruction set that supports multiple

addressing modes and is optimized for high-level

languages such as ‘C’

• Operational performance up to 16 MIPS

1.1.2 POWER-SAVING TECHNOLOGY

All of the devices in the PIC24FJ128GA family incorporate a range of features that can significantly reduce

power consumption during operation. Key items

include:

• On-the-Fly Clock Switching: The device clock

can be changed under software control to the

Timer1 source or the internal low-power RC

oscillator during operation, allowing the user to

incorporate power-saving ideas into their software

designs.

• Doze Mode Operation: When timing-sensitive

applications, such as serial communications,

require the uninterrupted operation of peripherals,

the CPU clock speed can be selectively reduced,

allowing incremental power savings without

missing a beat.

• Instruction-Based Power-Saving Modes: The

microcontroller can suspend all operations, or

selectively shut down its core while leaving its

peripherals active, with a single instruction in

software.

1.1.3 OSCILLATOR OPTIONS AND

FEATURES

All of the devices in the PIC24FJ128GA family offer five

different oscillator options, allowing users a range of

choices in developing application hardware. These

include:

• Two Crystal modes, using crystals or ceramic

resonators.

• Two External Clock modes, offering the option of

a divide-by-2 clock output.

• A Fast Internal Oscillator (FRC) with a nominal

8 MHz output, which can also be divided under

software control to provide clock speeds as low as

31 kHz.

• A Phase Lock Loop (PLL) frequency multiplier,

available to the external oscillator modes and the

FRC oscillator, which allows clock speeds of up to

32 MHz.

• A separate internal RC oscillator (LPRC) with a

fixed 31 kHz output, which provides a low-power

option for timing-insensitive applications.

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor. This

option constantly monitors the main clock source

against a reference signal provided by the internal

oscillator and enables the controller to switch to the

internal oscillator, allowing for continued low-speed

operation or a safe application shutdown.

© 2006 Microchip Technology Inc. Advance Information DS39747B-page 7

Page 10

PIC24FJ128GA FAMILY

1.1.4 EASY MIGRATION

Regardless of the memory size, all devices share the

same rich set of peripherals, allowing for a smooth

migration path as applications grow and evolve.

The consistent pinout scheme used throughout the

entire family also aids in migrating to the next larger

device. This is true when moving between devices with

the same pin count, or even jumping from 64-pin to

80-pin to 100-pin devices.

The PIC24 family is pin-compatible with devices in the

dsPIC33 family, and shares some compatibility with the

pinout schema for PIC18 and dsPIC30. This extends

the ability of applications to grow from the relatively

simple to the powerful and complex, yet still select a

Microchip device.

1.2 Other Special Features

• Communications: The PIC24FJ128GA family

incorporates a range of serial communication

peripherals to handle a range of application

requirements. All devices are equipped with two

independent UARTs with built-in IrDA

encoder/decoders. There are also two independent SPI modules, and two independent I

modules that support both Master and Slave

modes of operation.

• Parallel Master/Enhanced Parallel Slave Port:

One of the general purpose I/O ports can be

reconfigured for enhanced parallel data communications. In this mode, the port can be configured

for both master and slave operations, and

supports 8-bit and 16-bit data transfers with up to

16 external address lines in Master modes.

• Real-Time Clock/Calendar: This module

implements a full-featured clock and calendar with

alarm functions in hardware, freeing up timer

resources and program memory space for use of

the core application.

• 10-Bit A/D Converter: This module incorporates

programmable acquisition time, allowing for a

channel to be selected and a conversion to be

initiated without waiting for a sampling period, as

well as faster sampling speeds.

2

C

1.3 Details on Individual Family Members

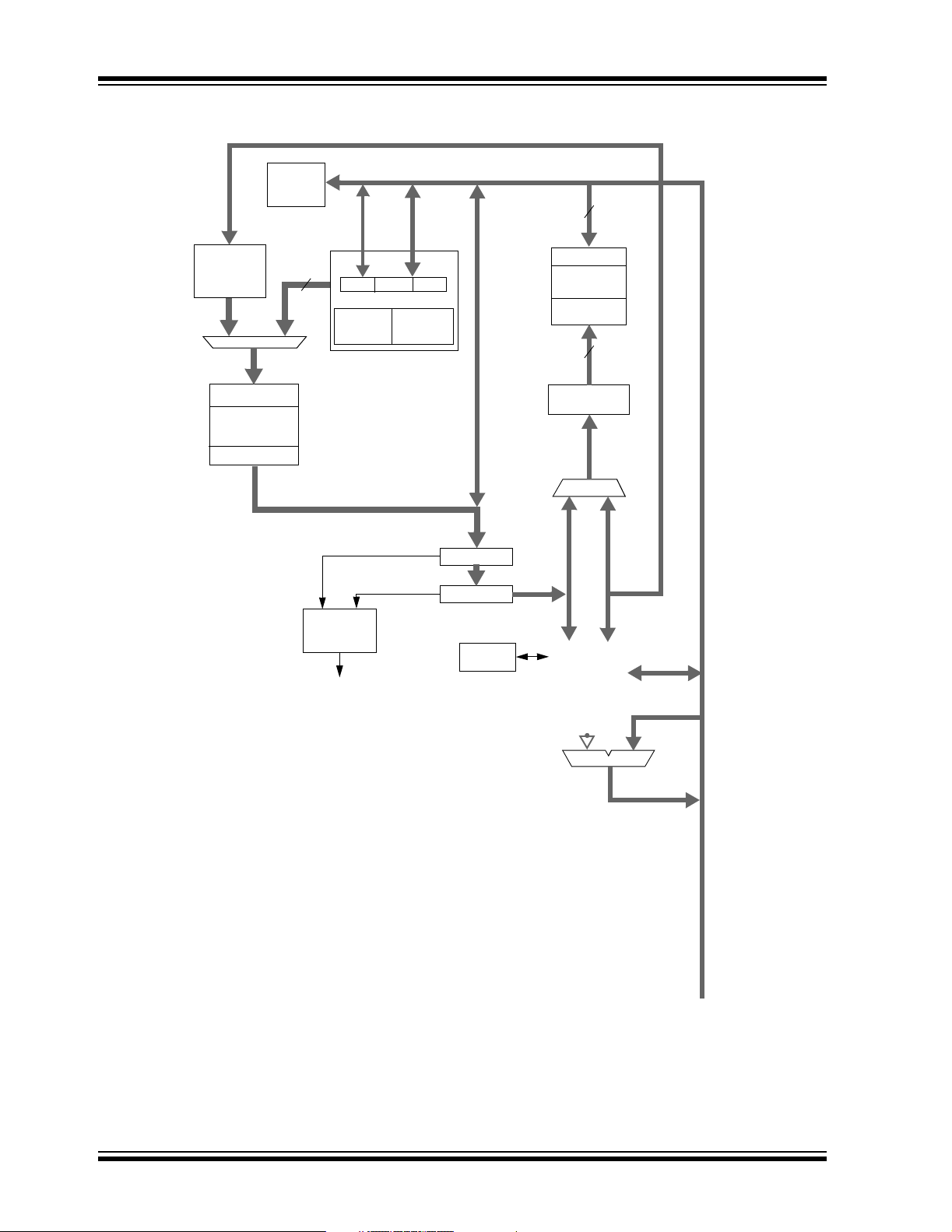

Devices in the PIC24FJ128GA family are available in

64-pin, 80-pin and 100-pin packages. The general

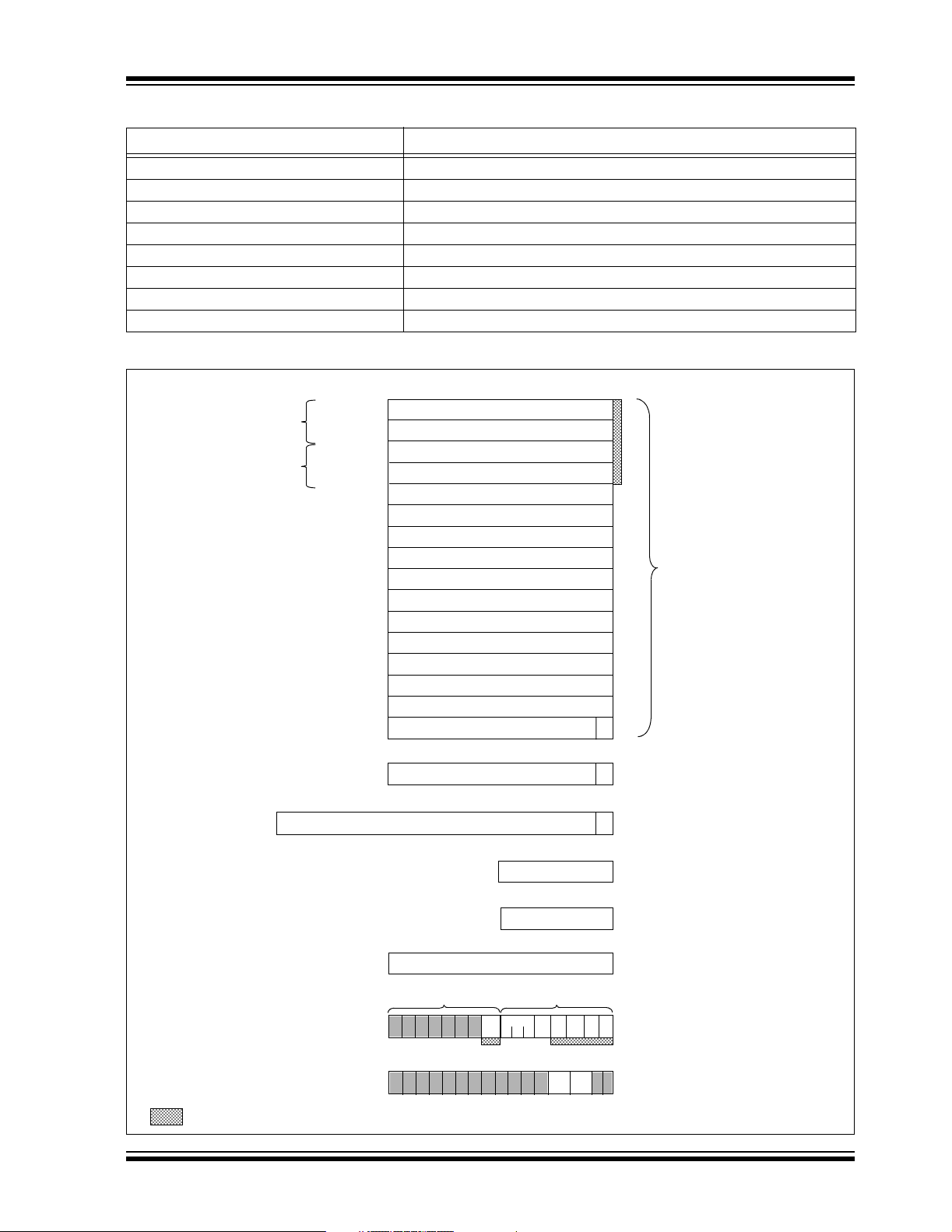

block diagram for all devices is shown in Figure 1-1.

The devices are differentiated from each other in two

ways:

1. Flash program memory (64 Kbytes for

PIC24FJ64GA devices, 96 Kbytes for

PIC24FJ96GA devices and 128 Kbytes for

PIC24FJ128GA devices).

2. Available I/O pins and ports (53 pins on 6 ports

for 64-pin devices, 69 pins on 7 ports for 80-pin

devices and 84 pins on 7 ports for 100-pin

devices).

All other features for devices in this family are identical.

These are summarized in Table 1-1.

A list of the pin features available on the

PIC24FJ128GA family devices, sorted by function, is

shown in Table 1-2. Note that this table shows the pin

location of individual peripheral features and not how

they are multiplexed on the same pin. This information

is provided in the pinout diagrams in the beginning of

the data sheet. Multiplexed features are sorted by the

priority given to a feature, with the highest priority

peripheral being listed first.

DS39747B-page 8 Advance Information © 2006 Microchip Technology Inc.

Page 11

PIC24FJ128GA FAMILY

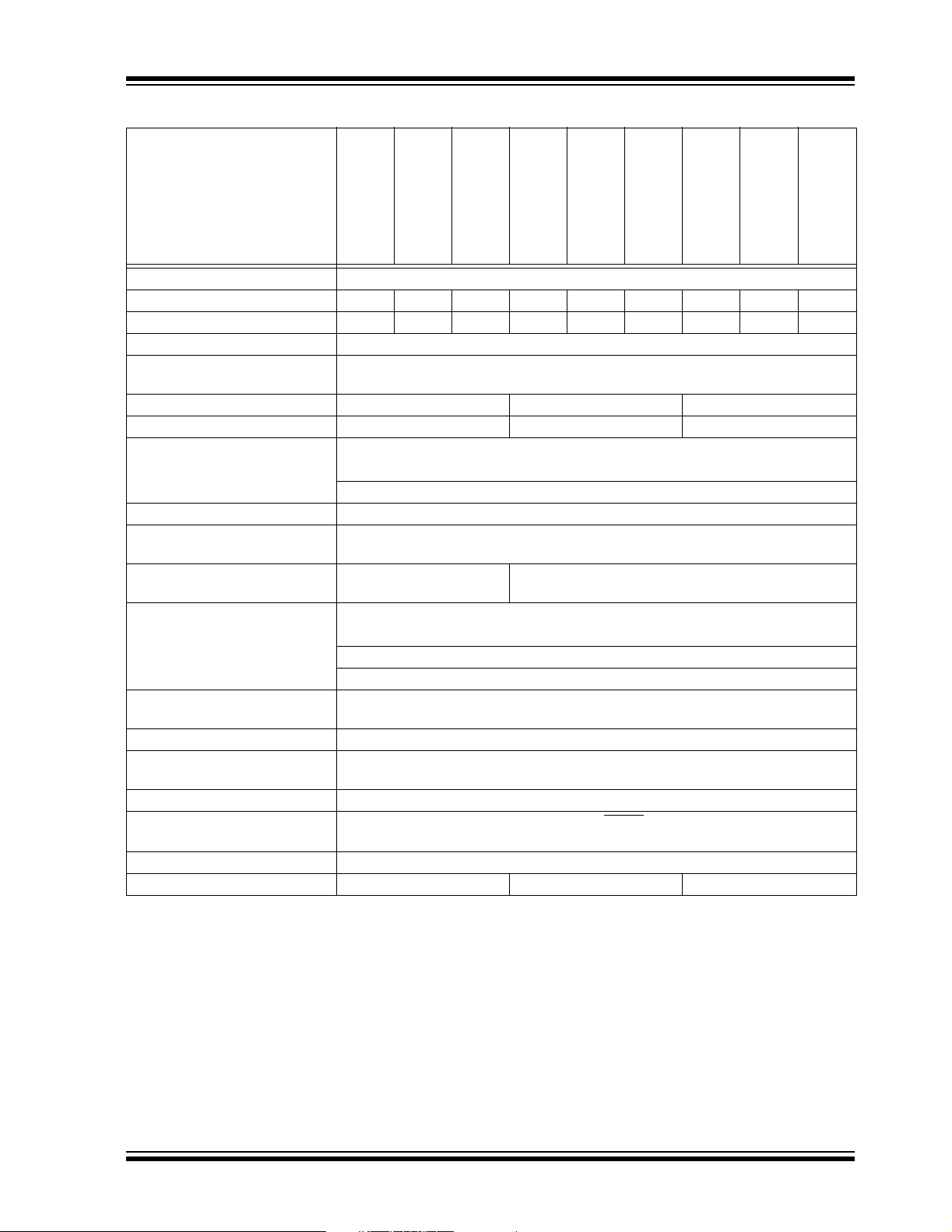

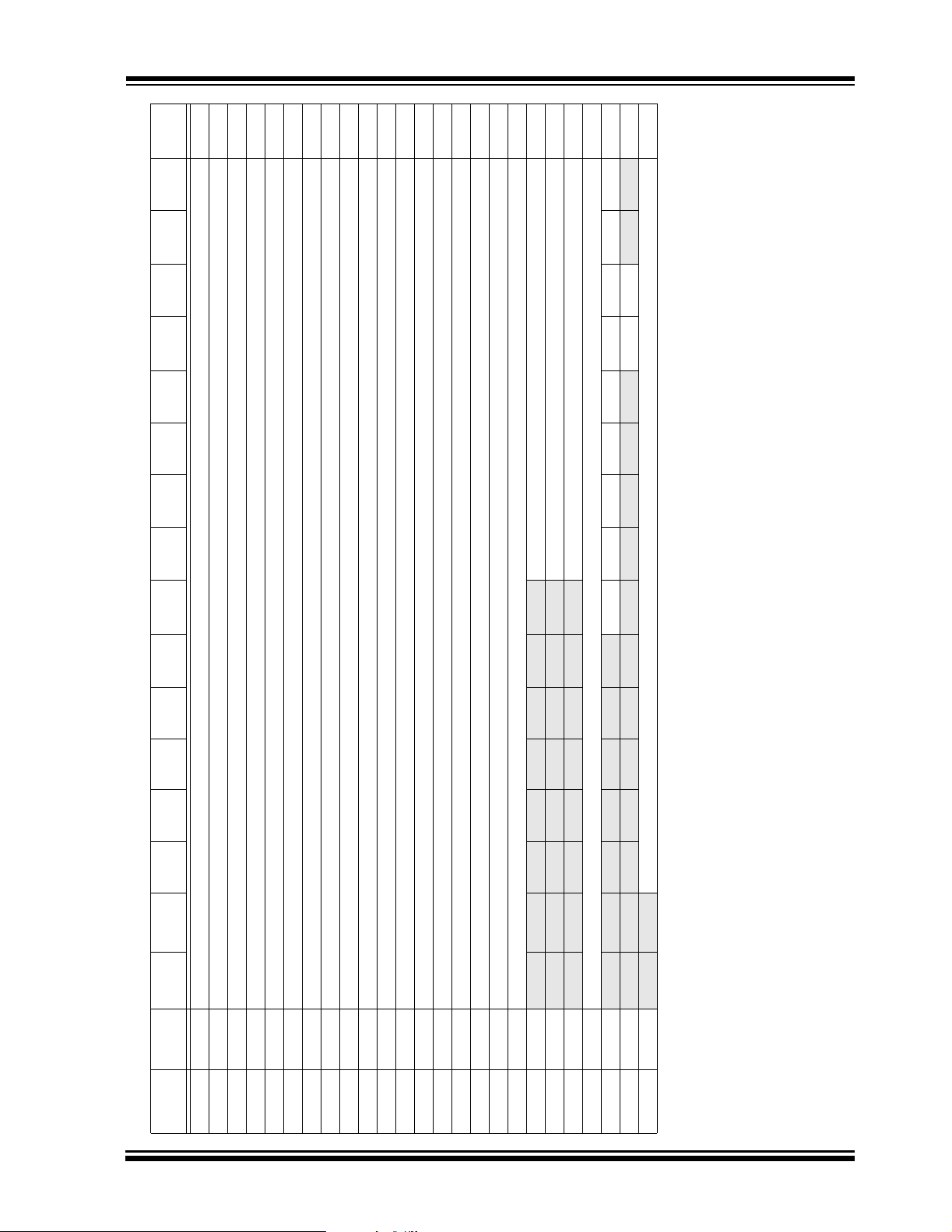

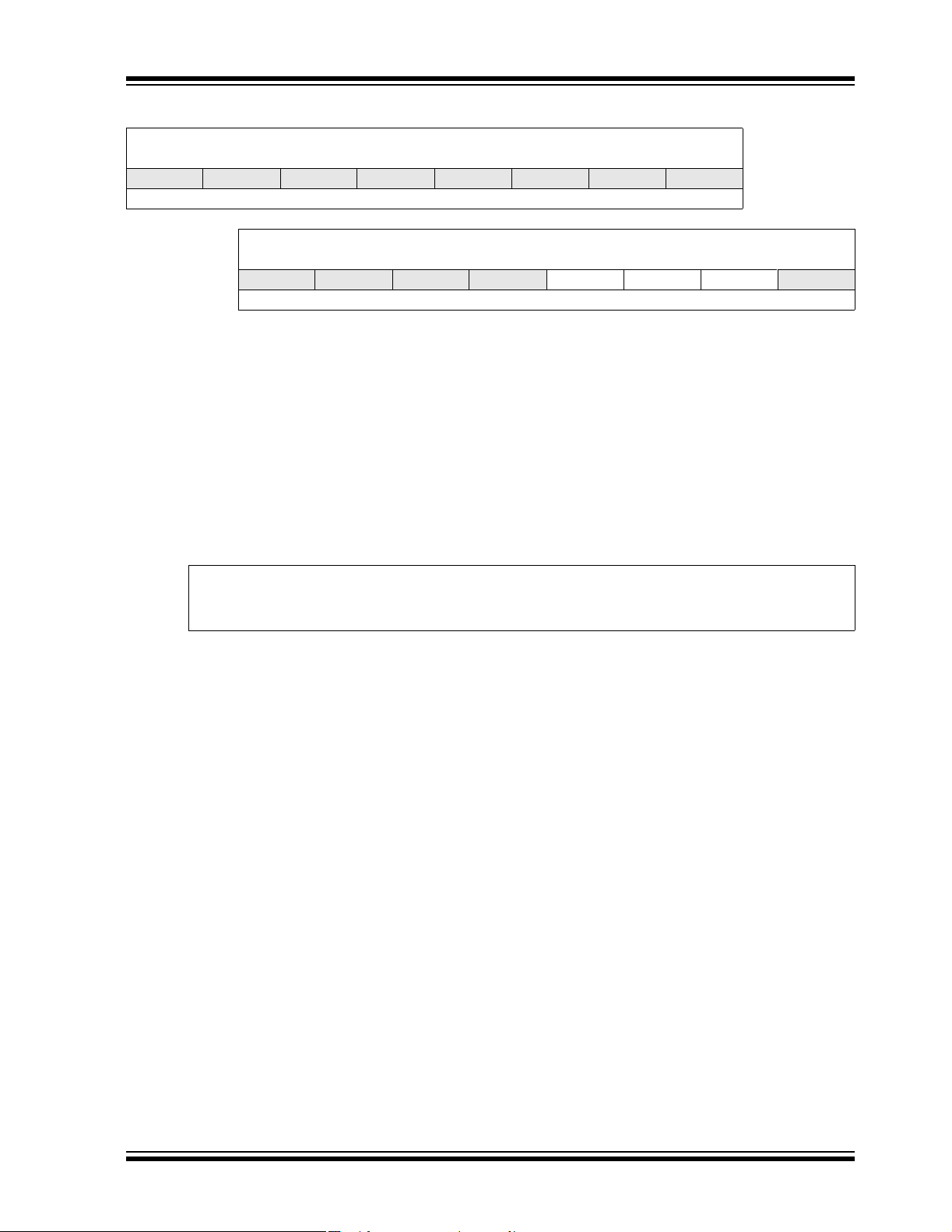

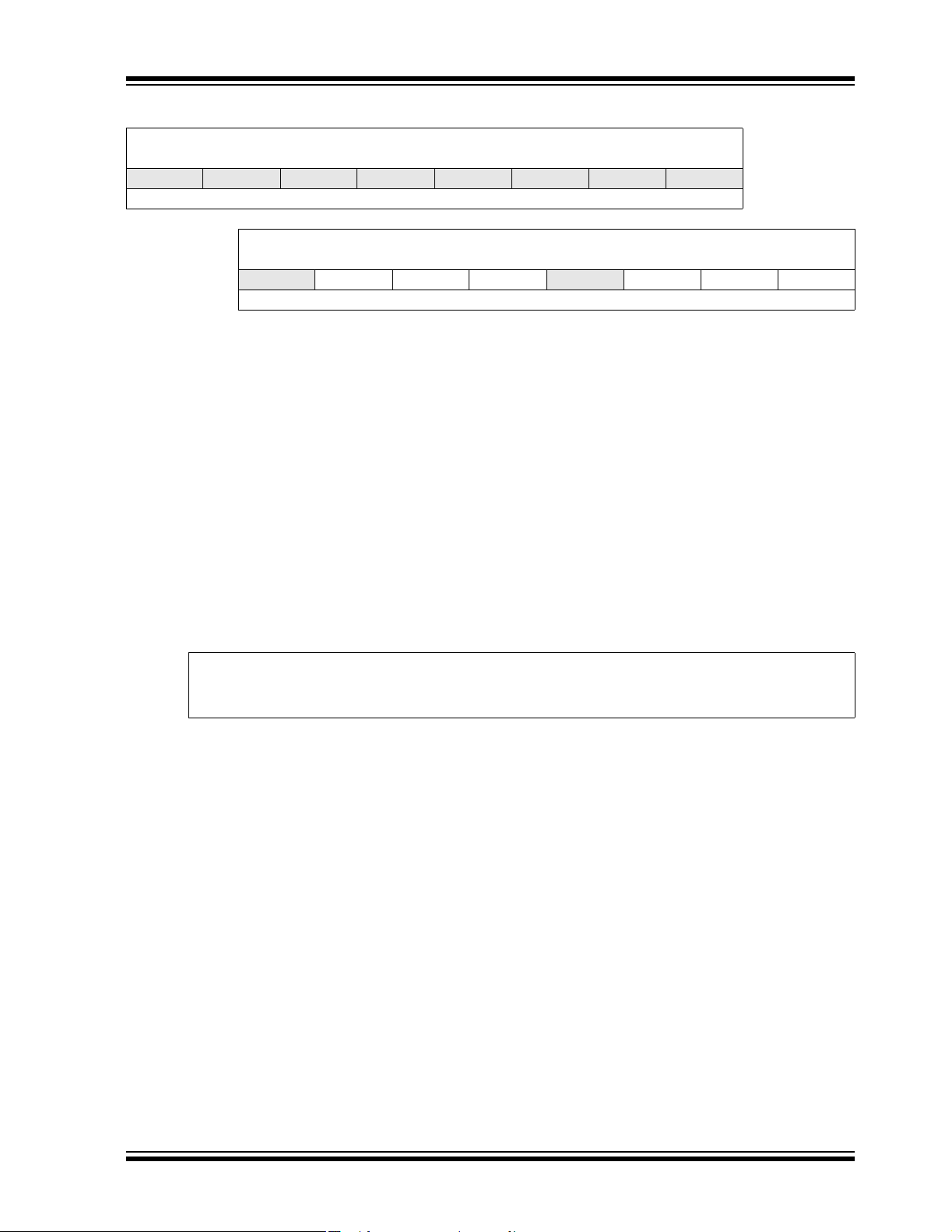

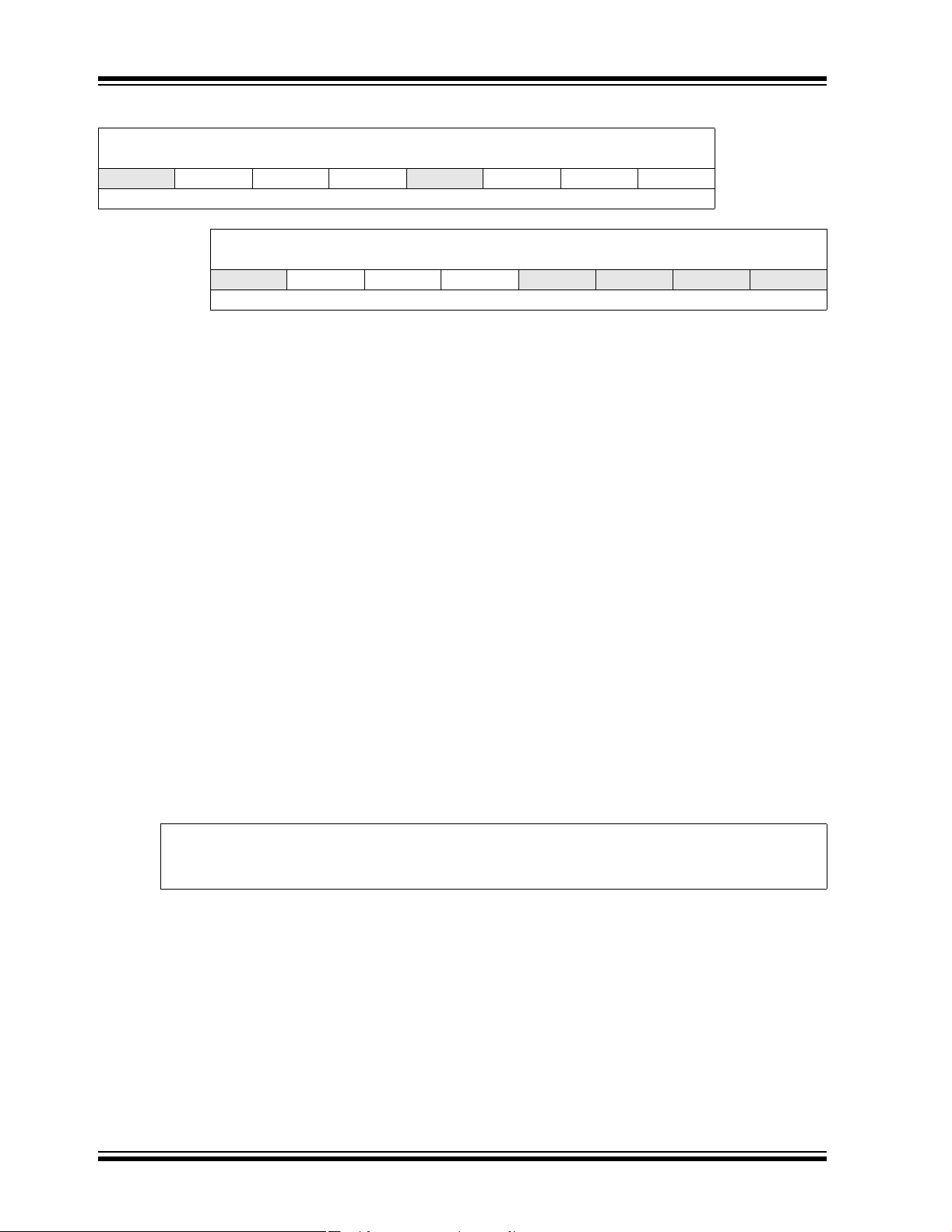

TABLE 1-1: DEVICE FEATURES FOR THE PIC24FJ128GA FAMILY

Features

PIC24FJ64GA006

Operating Frequency DC – 32 MHz

Program Memory (Bytes) 64K 96K 128K 64K 96K 128K 64K 96K 128K

Program Memory (Instructions) 22,016 32,768 44,032 22,016 32,768 44,032 22,016 32,768 44,032

Data Memory (Bytes) 8192

Interrupt Sources

(Soft Vectors/NMI Traps)

I/O Ports Ports B, C, D, E, F, G Ports A, B, C, D, E, F, G Ports A, B, C, D, E, F, G

Total I/O Pins 53 69 84

Timers:

Total number (16-bit) 5

32-bit (from paired 16-bit timers) 2

Input Capture Channels 5

Output Compare/PWM Channels

Input Change Notification

Interrupt

Serial Communications:

Enhanced UART 2

SPI (3-wire/4-wire) 2

2

C™ 2

I

Parallel Communications

(PMP/PSP)

JTAG Boundary Scan Yes

10-bit Analog-to-Digital Module

(input channels)

Analog Comparators 2

Resets (and Delays) POR, BOR, RESET Instruction, MCLR

Instruction Set 76 Base Instructions, Multiple Addressing Mode Variations

Packages 64-pin TQFP 80-pin TQFP 100-pin TQFP

PIC24FJ96GA006

19 22

PIC24FJ128GA006

Repeat Hardware Traps, (PWRT, OST, PLL Lock)

PIC24FJ64GA008

PIC24FJ96GA008

43

(39/4)

5

Yes

16

PIC24FJ128GA008

, WDT; Illegal Opcode,

PIC24FJ64GA010

PIC24FJ96GA010

PIC24FJ128GA010

© 2006 Microchip Technology Inc. Advance Information DS39747B-page 9

Page 12

PIC24FJ128GA FAMILY

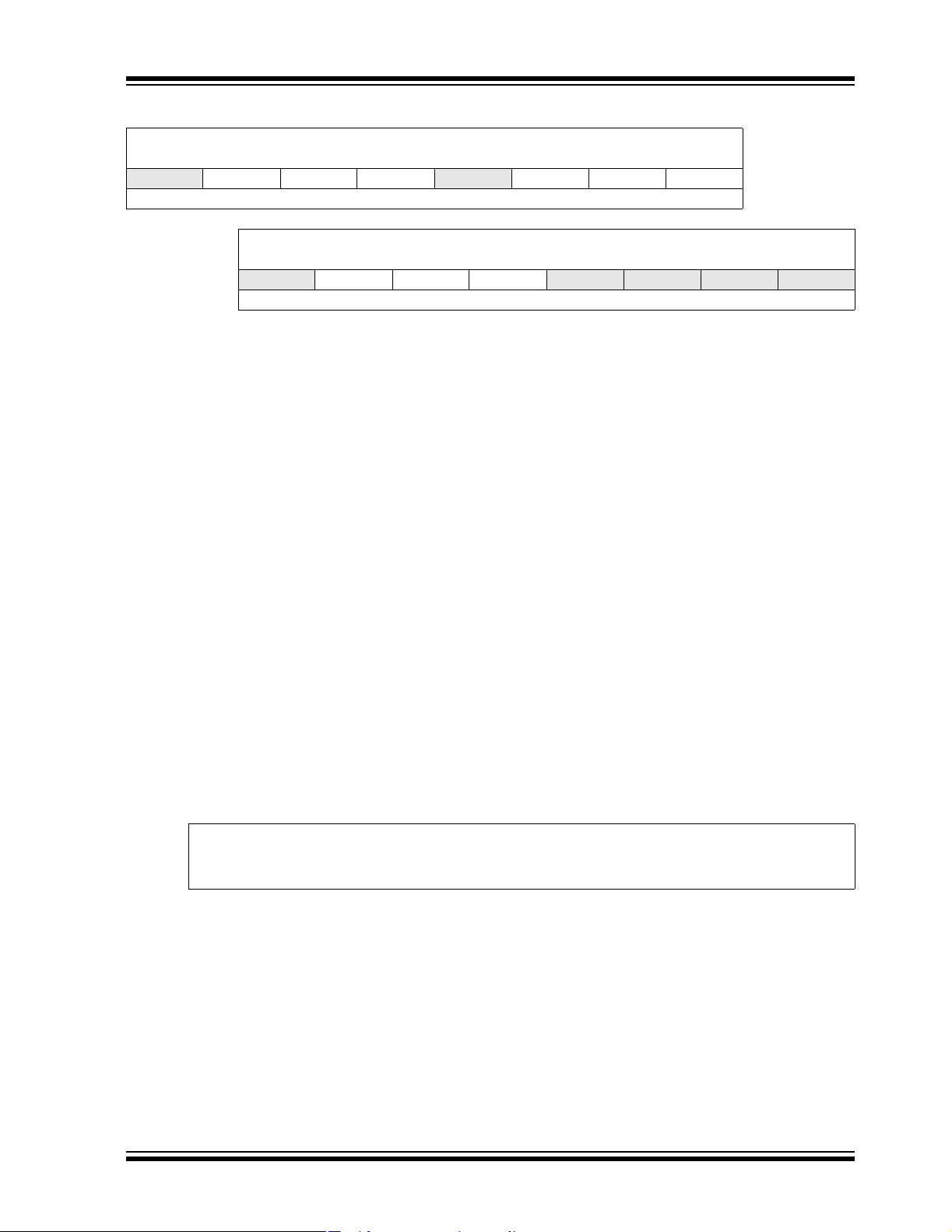

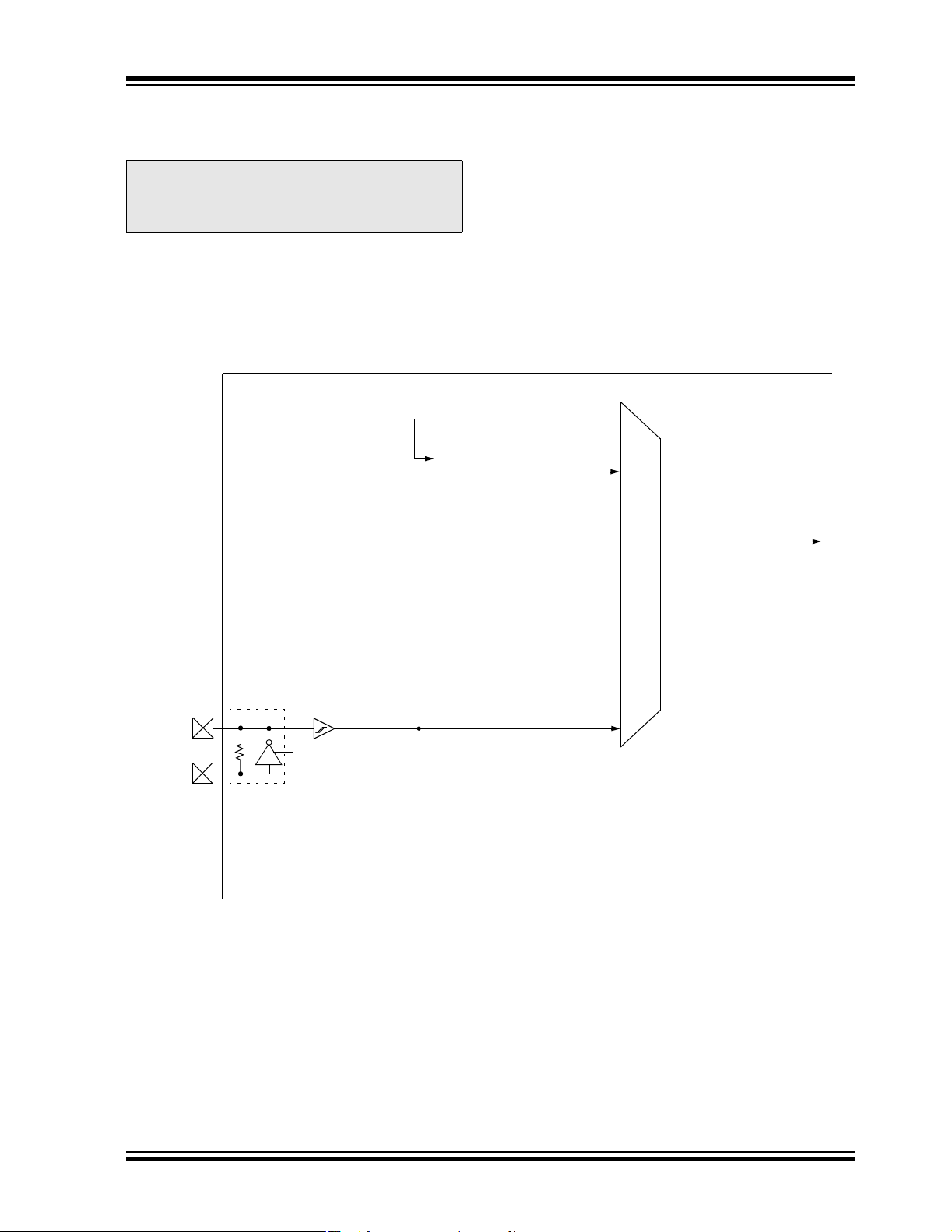

FIGURE 1-1: PIC24FJ128GA FAMILY GENERAL BLOCK DIAGRAM

PSV & Table

Data Access

Control Block

Address Latch

Program Memory

Data Latch

Interrupt

Controller

23

23

Instruction

Decode &

Control

8

PCH PCL

PCU

Program Counter

Stac k

Control

Logic

Address Bus

24

16

Repeat

Control

Logic

Data Bus

16

Inst Latch

Inst Register

Divide

Support

Data Latch

Data RAM

Address

Latch

Read AGU

Write AGU

EA MUX

16

Literal Data

16

16

16

16-bit ALU

16

DS39747B-page 10 Advance Information © 2006 Microchip Technology Inc.

Page 13

PIC24FJ128GA FAMILY

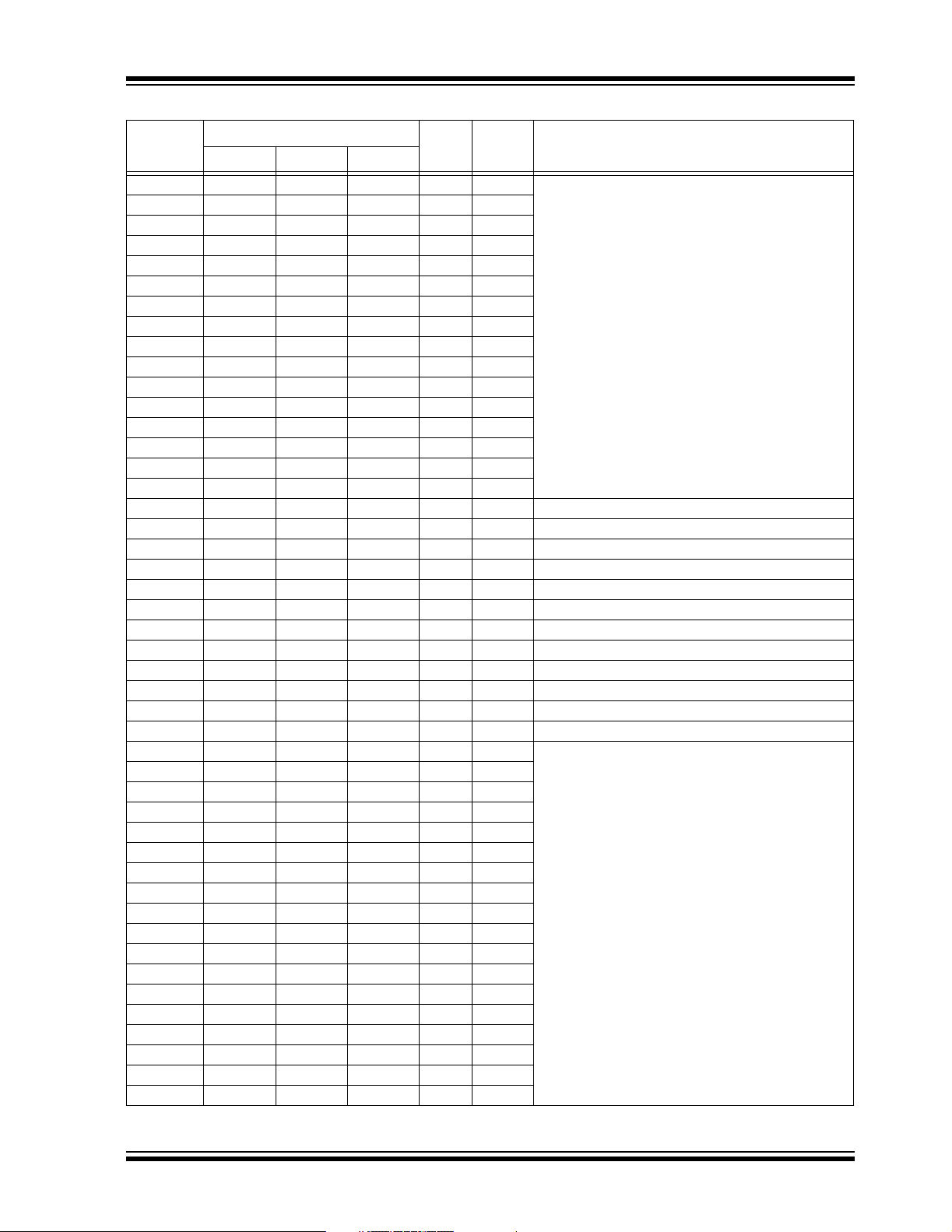

TABLE 1-2: PIC24FJ128GA FAMILY PINOUT DESCRIPTIONS

Function

AN0 16 20 25 I ANA A/D Analog Inputs.

AN1151924IANA

AN2141823IANA

AN3131722IANA

AN4121621IANA

AN5 11 15 20 I ANA

AN6172126IANA

AN7182227IANA

AN8212732IANA

AN9222833IANA

AN10 23 29 34 I ANA

AN11 24 30 35 I ANA

AN12 27 33 41 I ANA

AN13 28 34 42 I ANA

AN14 29 35 43 I ANA

AN15 30 36 44 I ANA

DD 19 25 30 P — Positive Supply for Analog Modules.

AV

SS 20 26 31 P — Ground Reference for Analog Modules.

AV

BCLK1353848O—UART1 IrDA

BCLK2293539O—UART2 IrDA

C1IN- 12 16 21 I ANA Comparator 1 Negative Input.

C1IN+ 11 15 20 I ANA Comparator 1 Positive Input.

C1OUT 21 27 32 O — Comparator 1 Output.

C2IN- 14 18 23 I ANA Comparator 2 Negative Input.

C2IN+ 13 17 22 I ANA Comparator 2 Positive Input.

C2OUT 22 28 33 O — Comparator 2 Output.

CLKI 39 49 63 I ANA Main Clock Input Connection.

CLKO 40 50 64 O — System Clock Output.

CN0 48 60 74 I ST Interrupt-on-Change Inputs.

CN1475973IST

CN2162025IST

CN3151924IST

CN4141823IST

CN5131722IST

CN6121621IST

CN7 11 15 20 I ST

CN8 4 6 10 I ST

CN9 5 7 11 I ST

CN10 6 8 12 I ST

CN11 8 10 14 I ST

CN12303644IST

CN13526681IST

CN14536782IST

CN15546883IST

CN16556984IST

CN17313949IST

Legend: TTL = TTL input buffer ST = Schmitt Trigger input buffer

64-pin 80-pin 100-pin

ANA = Analog level input/output I

Pin Number

I/O

Input

Buffer

®

Baud Clock.

®

Baud Clock.

2

C™ = I2C/SMBus input buffer

Description

© 2006 Microchip Technology Inc. Advance Information DS39747B-page 11

Page 14

PIC24FJ128GA FAMILY

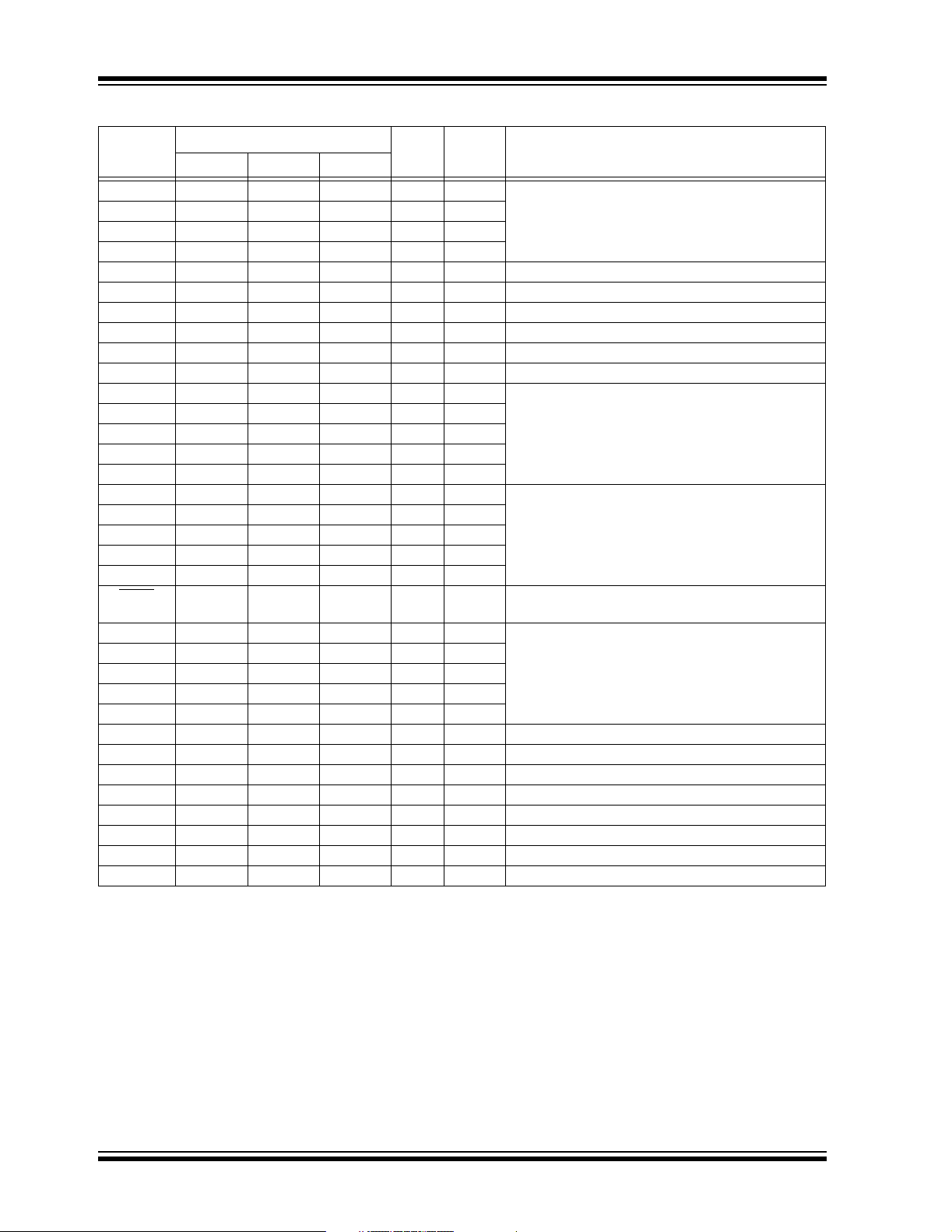

TABLE 1-2: PIC24FJ128GA FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Function

CN18 32 40 50 I ST Interrupt-on-Change Inputs.

CN19 — 65 80 I ST

CN20 — 37 47 I ST

CN21 — 38 48 I ST

REF 23 29 34 O ANA Comparator Voltage Reference Output.

CV

EMUC1 15 19 24 I/O ST In-Circuit Emulator Clock Input/Output.

EMUD1 16 20 25 I/O ST In-Circuit Emulator Data Input/Output.

EMUC2 17 21 26 I/O ST In-Circuit Emulator Clock Input/Output.

EMUD2 18 22 27 I/O ST In-Circuit Emulator Data Input/Output.

ENVREG 57 71 86 I ST Enable for On-Chip Voltage Regulator.

IC1 42 54 68 I ST Input Capture Inputs.

IC2435569IST

IC3445670IST

IC4455771IST

IC5526479IST

INT0 35 45 55 I ST External Interrupt Inputs.

INT1 42 13 18 I ST

INT2 43 14 19 I ST

INT3 44 52 66 I ST

INT4 45 53 67 I ST

MCLR

OC1 46 58 72 O — Output Compare/PWM Outputs.

OC2496176O—

OC3506277O—

OC4516378O—

OC5526681O—

OCFA 17 21 26 I ST Output Compare Fault A Input.

OCFB 30 36 44 I ST Output Compare Fault B Input.

OSC1 39 49 63 I ANA Main Oscillator Input Connection.

OSC2 40 50 64 O ANA Main Oscillator Output Connection.

PGC1 15 19 24 I/O ST In-Circuit Debugger and ICSP™ Programming Clock

PGD1 16 20 25 I/O ST In-Circuit Debugger and ICSP Programming Data.

PGC2 17 21 26 I/O ST In-Circuit Debugger and ICSP™ Programming Clock.

PGD2 18 22 27 I/O ST In-Circuit Debugger and ICSP Programming Data.

Legend: TTL = TTL input buffer ST = Schmitt Trigger input buffer

64-pin 80-pin 100-pin

ANA = Analog level input/output I

Pin Number

I/O

7 9 13 I ST Master Clear (Device Reset) Input. This line is brought

Input

Buffer

low to cause a Reset.

2

C™ = I2C/SMBus input buffer

Description

DS39747B-page 12 Advance Information © 2006 Microchip Technology Inc.

Page 15

PIC24FJ128GA FAMILY

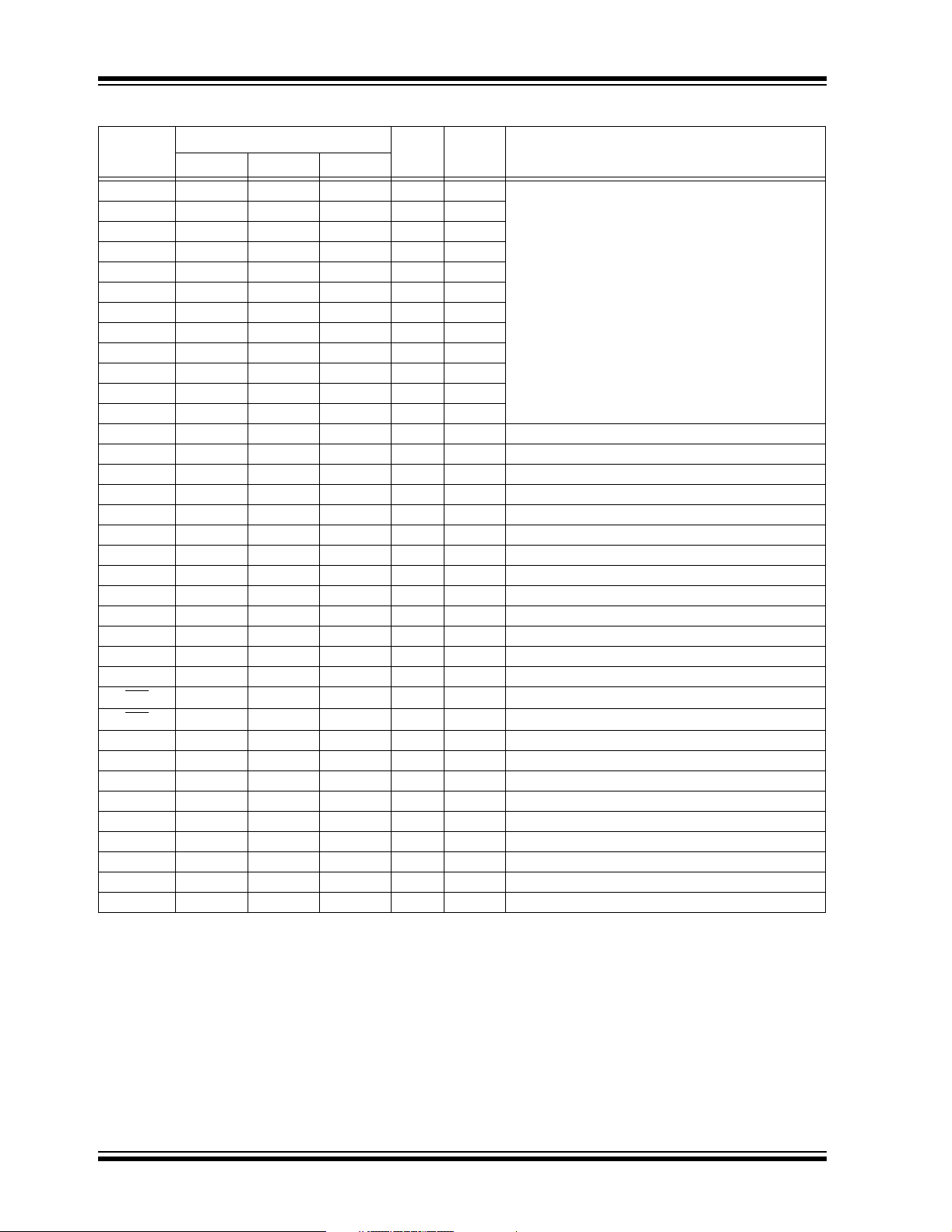

TABLE 1-2: PIC24FJ128GA FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Function

64-pin 80-pin 100-pin

PMA0 30 36 44 I/O ST Parallel Master Port Address Bit 0 Input (Buffered Slave

PMA1 29 35 43 I/O ST

PMA2 8 10 14 O — Parallel Master Port Address (Demultiplexed Master

PMA3 6 8 12 O —

PMA4 5 7 11 O —

PMA5 4 6 10 O —

PMA6 16 24 29 O —

PMA7 22 23 28 O —

PMA8 32 40 50 O —

PMA9 31 39 49 O —

PMA10 28 34 42 O —

PMA11 27 33 41 O —

PMA12 24 30 35 O —

PMA13 23 29 34 O —

PMBE 51 63 78 O — Parallel Master Port Byte Enable Strobe.

PMCS1 45 57 71 O — Parallel Master Port Chip Select 1 Strobe/Address bit 14.

PMCS2 44 56 70 O — Parallel Master Port Chip Select 2 Strobe/Address bit 15.

PMD0 60 76 93 I/O ST Parallel Master Port Data (Demultiplexed Master mode)

PMD1 61 77 94 I/O ST

PMD2 62 78 98 I/O ST

PMD3 63 79 99 I/O ST

PMD4 64 80 100 I/O ST

PMD5 1 1 3 I/O ST

PMD6 2 2 4 I/O ST

PMD7 3 3 5 I/O ST

PMRD 53 67 82 O — Parallel Master Port Read Strobe.

PMWR 52 66 81 O — Parallel Master Port Write Strobe.

Legend: TTL = TTL input buffer ST = Schmitt Trigger input buffer

ANA = Analog level input/output I

Pin Number

I/O

Input

Buffer

modes) and Output (Master modes).

Parallel Master Port Address Bit 1 Input (Buffered Slave

modes) and Output (Master modes).

modes).

or Address/Data (Multiplexed Master modes).

2

C™ = I2C/SMBus input buffer

Description

© 2006 Microchip Technology Inc. Advance Information DS39747B-page 13

Page 16

PIC24FJ128GA FAMILY

TABLE 1-2: PIC24FJ128GA FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Function

64-pin 80-pin 100-pin

RA0 — — 17 I/O ST PORTA Digital I/O.

RA1 — — 38 I/O ST

RA2 — — 58 I/O ST

RA3 — — 59 I/O ST

RA4 — — 60 I/O ST

RA5 — — 61 I/O ST

RA6 — — 91 I/O ST

RA7 — — 92 I/O ST

RA9 — 23 28 I/O ST

RA10 — 24 29 I/O ST

RA14 — 52 66 I/O ST

RA15 — 53 67 I/O ST

RB0 16 20 25 I/O ST PORTB Digital I/O.

RB1151924I/OST

RB2141823I/OST

RB3131722I/OST

RB4121621I/OST

RB5 11 15 20 I/O ST

RB6172126I/OST

RB7182227I/OST

RB8212732I/OST

RB9222833I/OST

RB10 23 29 34 I/O ST

RB11 24 30 35 I/O ST

RB12 27 33 41 I/O ST

RB13 28 34 42 I/O ST

RB14 29 35 43 I/O ST

RB15 30 36 44 I/O ST

RC1 — 4 6 I/O ST PORTC Digital I/O.

RC2 — — 7 I/O ST

RC3 — 5 8 I/O ST

RC4 — — 9 I/O ST

RC12394963I/OST

RC13475973I/OST

RC14486074I/OST

RC15405064I/OST

Legend: TTL = TTL input buffer ST = Schmitt Trigger input buffer

ANA = Analog level input/output I

Pin Number

I/O

Input

Buffer

2

C™ = I2C/SMBus input buffer

Description

DS39747B-page 14 Advance Information © 2006 Microchip Technology Inc.

Page 17

PIC24FJ128GA FAMILY

TABLE 1-2: PIC24FJ128GA FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Function

64-pin 80-pin 100-pin

RD0 46 58 72 I/O ST PORTD Digital I/O.

RD1496176I/OST

RD2506277I/OST

RD3516378I/OST

RD4526681I/OST

RD5536782I/OST

RD6546883I/OST

RD7556984I/OST

RD8425468I/OST

RD9435569I/OST

RD10445670I/OST

RD11 45 57 71 I/O ST

RD12 — 64 79 I/O ST

RD13 — 65 80 I/O ST

RD14 — 37 47 I/O ST

RD15 — 38 48 I/O ST

RE0 60 76 93 I/O ST PORTE Digital I/O.

RE1617794I/OST

RE2627898I/OST

RE3637999I/OST

RE4 64 80 100 I/O ST

RE5 1 1 3 I/O ST

RE6 2 2 4 I/O ST

RE7 3 3 5 I/O ST

RE8 — 13 18 I/O ST

RE9 — 14 19 I/O ST

RF0 58 72 87 I/O ST PORTF Digital I/O.

RF1597388I/OST

RF2344252I/OST

RF3334151I/OST

RF4313949I/OST

RF5324050I/OST

RF6354555I/OST

RF7 — 44 54 I/O ST

RF8 — 43 53 I/O ST

RF12 — — 40 I/O ST

RF13 — — 39 I/O ST

Legend: TTL = TTL input buffer ST = Schmitt Trigger input buffer

ANA = Analog level input/output I

Pin Number

I/O

Input

Buffer

2

C™ = I2C/SMBus input buffer

Description

© 2006 Microchip Technology Inc. Advance Information DS39747B-page 15

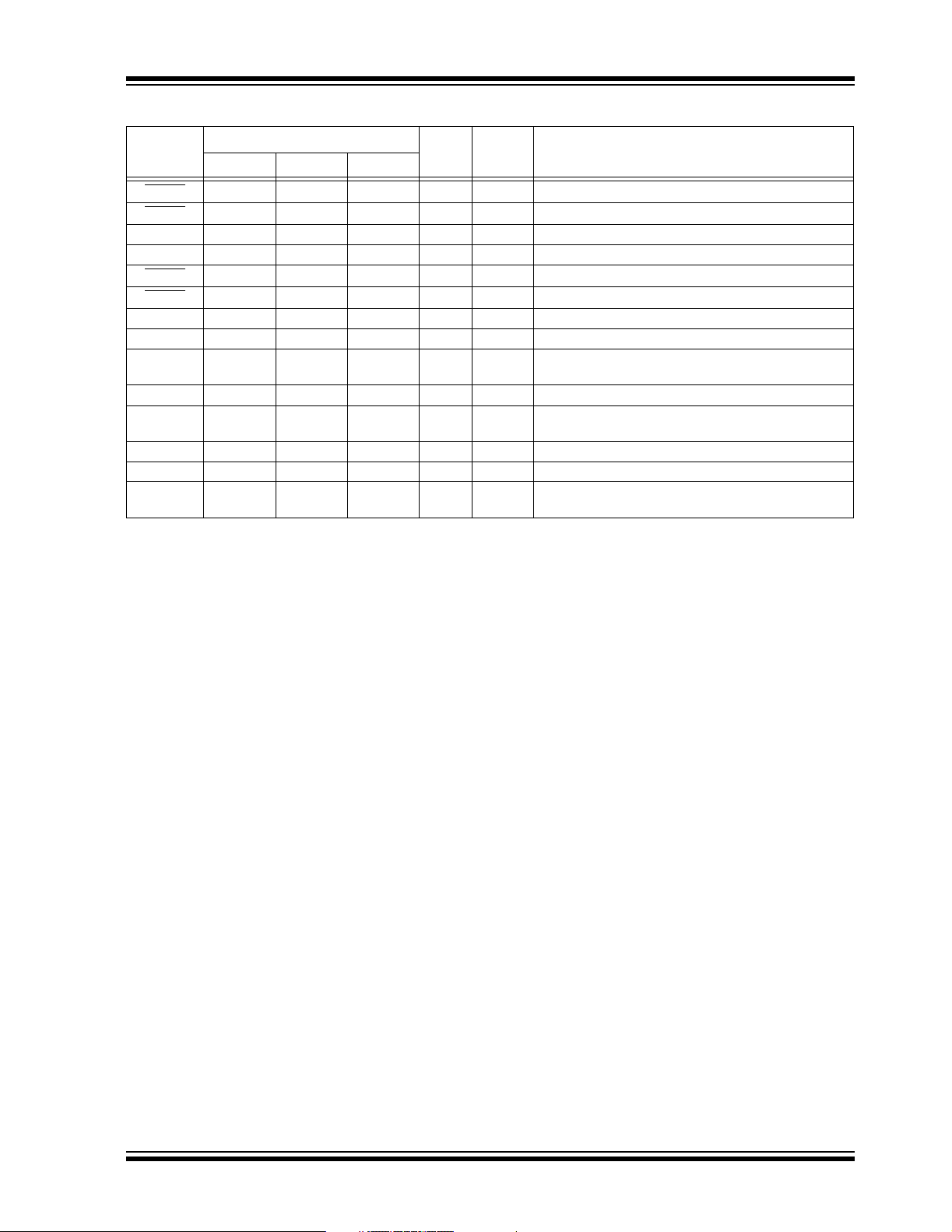

Page 18

PIC24FJ128GA FAMILY

TABLE 1-2: PIC24FJ128GA FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Function

64-pin 80-pin 100-pin

RG0 — 75 90 I/O ST PORTG Digital I/O.

RG1 — 74 89 I/O ST

RG2374757I/OST

RG3364656I/OST

RG6 4 6 10 I/O ST

RG7 5 7 11 I/O ST

RG8 6 8 12 I/O ST

RG9 8 10 14 I/O ST

RG12 — — 96 I/O ST

RG13 — — 97 I/O ST

RG14 — — 95 I/O ST

RG15 — — 1 I/O ST

RTCC 42 54 68 O — Real-Time Clock Alarm Output.

SCK1 35 45 55 O — SPI1 Serial Clock Output.

SCK2 4 6 10 I/O ST SPI2 Serial Clock Output.

SCL1 37 47 57 I/O I

SCL2 32 52 58 I/O I

SDA1 36 46 56 I/O I

SDA2 31 53 59 I/O I

SDI1 34 44 54 I ST SPI1 Serial Data Input.

SDI2 5 7 11 I ST SPI2 Serial Data Input.

SDO1 33 43 53 O — SPI1 Serial Data Output.

SDO2 6 8 12 O — SPI2 Serial Data Output.

SOSCI 47 59 73 I ANA Secondary Oscillator/Timer1 Clock Input.

SOSCO 48 60 74 O ANA Secondary Oscillator/Timer1 Clock Output.

SS1

SS2

T1CK 48 60 74 I ST Timer1 Clock.

T2CK — 4 6 I ST Timer2 External Clock Input.

T3CK — — 7 I ST Timer3 External Clock Input.

T4CK — 5 8 I ST Timer4 External Clock Input.

T5CK — — 9 I ST Timer5 External Clock Input.

TCK 27 33 38 I ST JTAG Test Clock/Programming Clock Input.

TDI 28 34 60 I ST JTAG Test Data/Programming Data Input.

TDO 24 14 61 O — JTAG Test Data Output.

TMS 23 13 17 I ST JTAG Test Mode Select Input.

Legend: TTL = TTL input buffer ST = Schmitt Trigger input buffer

ANA = Analog level input/output I

Pin Number

I/O

14 18 23 I/O ST Slave Select Input/Frame Select Output (SPI1).

8 10 14 I/O ST Slave Select Input/Frame Select Output (SPI2).

Input

Buffer

2

C I2C1 Synchronous Serial Clock Input/Output.

2

C I2C2 Synchronous Serial Clock Input/Output.

2

C I2C1 Data Input/Output.

2

C I2C2 Data Input/Output.

2

C™ = I2C/SMBus input buffer

Description

DS39747B-page 16 Advance Information © 2006 Microchip Technology Inc.

Page 19

PIC24FJ128GA FAMILY

TABLE 1-2: PIC24FJ128GA FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Function

U1CTS 43 37 47 I ST UART1 Clear to Send Input.

U1RTS

U1RX 34 42 52 I ST UART1 Receive.

U1TX 33 41 51 O DIG UART1 Transmit Output.

U2CTS

U2RTS

U2RX 31 39 49 I ST UART 2 Receive Input.

U2TX 32 40 50 O — UART2 Transmit Output.

DD 10, 26, 38 12, 32, 48 2, 16, 37,

V

V

DDCAP 56 70 85

V

DDCORE 56 70 85

V

REF- 15 23 28 I ANA A/D and Comparator Reference Voltage (Low) Input.

REF+ 16 24 29 I ANA A/D and Comparator Reference Voltage (High) Input.

V

SS 9, 25, 41 11, 31, 51 15, 36, 45,

V

Legend: TTL = TTL input buffer ST = Schmitt Trigger input buffer

64-pin 80-pin 100-pin

ANA = Analog level input/output I

Pin Number

I/O

35 38 48 O — UART1 Request to Send Output.

21 27 40 I ST UART2 Clear to Send Input.

29 35 39 O — UART2 Request to Send Output.

46, 62

65, 75

Input

Buffer

P — Positive Supply for Peripheral Digital Logic and I/O pins.

P—

P—

P — Ground Reference for Logic and I/O pins.

External Filter Capacitor Connection (regulator enabled).

Positive Supply for Microcontroller Core Logic (regulator

disabled).

2

C™ = I2C/SMBus input buffer

Description

© 2006 Microchip Technology Inc. Advance Information DS39747B-page 17

Page 20

PIC24FJ128GA FAMILY

NOTES:

DS39747B-page 18 Advance Information © 2006 Microchip Technology Inc.

Page 21

PIC24FJ128GA FAMILY

2.0 CPU

The PIC24 CPU has a 16-bit (data) modified Harvard

architecture with an enhanced instruction set, and a

23-bit instruction word with a variable length opcode

field. The Program Counter (PC) is 24 bits wide and

addresses up to 4M instructions of user program

memory space. A single-cycle instruction prefetch

mechanism is used to help maintain throughput and

provides predictable execution. All instructions execute

in a single cycle, with the exception of instructions that

change the program flow, the double-word move

(MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using

the REPEAT instructions, which are interruptible at any

point.

PIC24 devices have sixteen 16-bit working registers in

the programmer’s model. Each of the working

registers can act as a data, address or address offset

register. The 16th working register (W15) operates as

a software Stack Pointer for interrupts and calls.

The upper 32 Kbytes of the data space memory map

can optionally be mapped into program space at any

16K word boundary defined by the 8-bit Program

Space Visibility Page (PSVPAG) register. The program

to data space mapping feature lets any instruction

access program space as if it were data space.

The Instruction Set Architecture (ISA) has been significantly enhanced beyond that of the PIC18, but maintains an acceptable level of backward compatibility. All

PIC18 instructions and addressing modes are

supported either directly or through simple macros.

Many of the ISA enhancements have been driven by

compiler efficiency needs.

The core supports Inherent (no operand), Relative,

Literal, Memory Direct and three groups of addressing

modes. All modes support Register Direct and various

Register Indirect modes. Each group offers up to 7

addressing modes. Instructions are associated with

predefined addressing modes depending upon their

functional requirements.

For most instructions, the core is capable of executing

a data (or program data) memory read, a working register (data) read, a data memory write and a program

(instruction) memory read per instruction cycle. As a

result, three-parameter instructions can be supported,

allowing trinary operations (that is, A + B = C) to be

executed in a single cycle.

A high-speed 17-bit by 17-bit multiplier has been

included to significantly enhance the core arithmetic

capability and throughput. The multiplier supports

signed, unsigned and mixed mode 16-bit by 16-bit or

8-bit by 8-bit integer multiplication. All multiply

instructions execute in a single cycle.

The 16-bit ALU has been enhanced with integer divide

assist hardware that supports an iterative

non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping mechanism,

and a selection of iterative divide instructions, to

support 32-bit (or 16-bit) divided by 16-bit integer

signed and unsigned division. All divide operations

require 19 cycles to complete but are interruptible at

any cycle boundary.

The PIC24 has a vectored exception scheme with up

to 8 sources of non-maskable traps and up to 118

interrupt sources. Each interrupt source can be

assigned to one of seven priority levels.

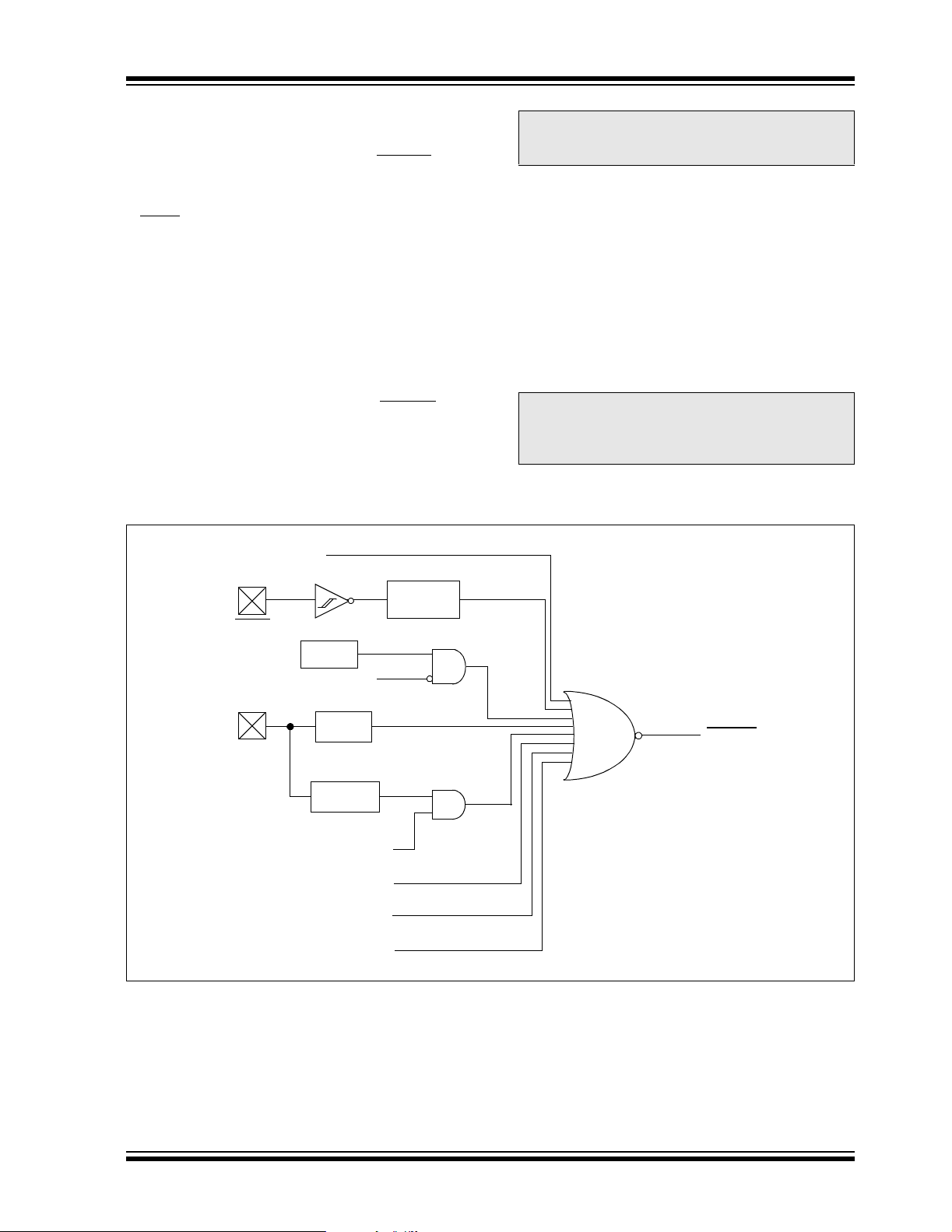

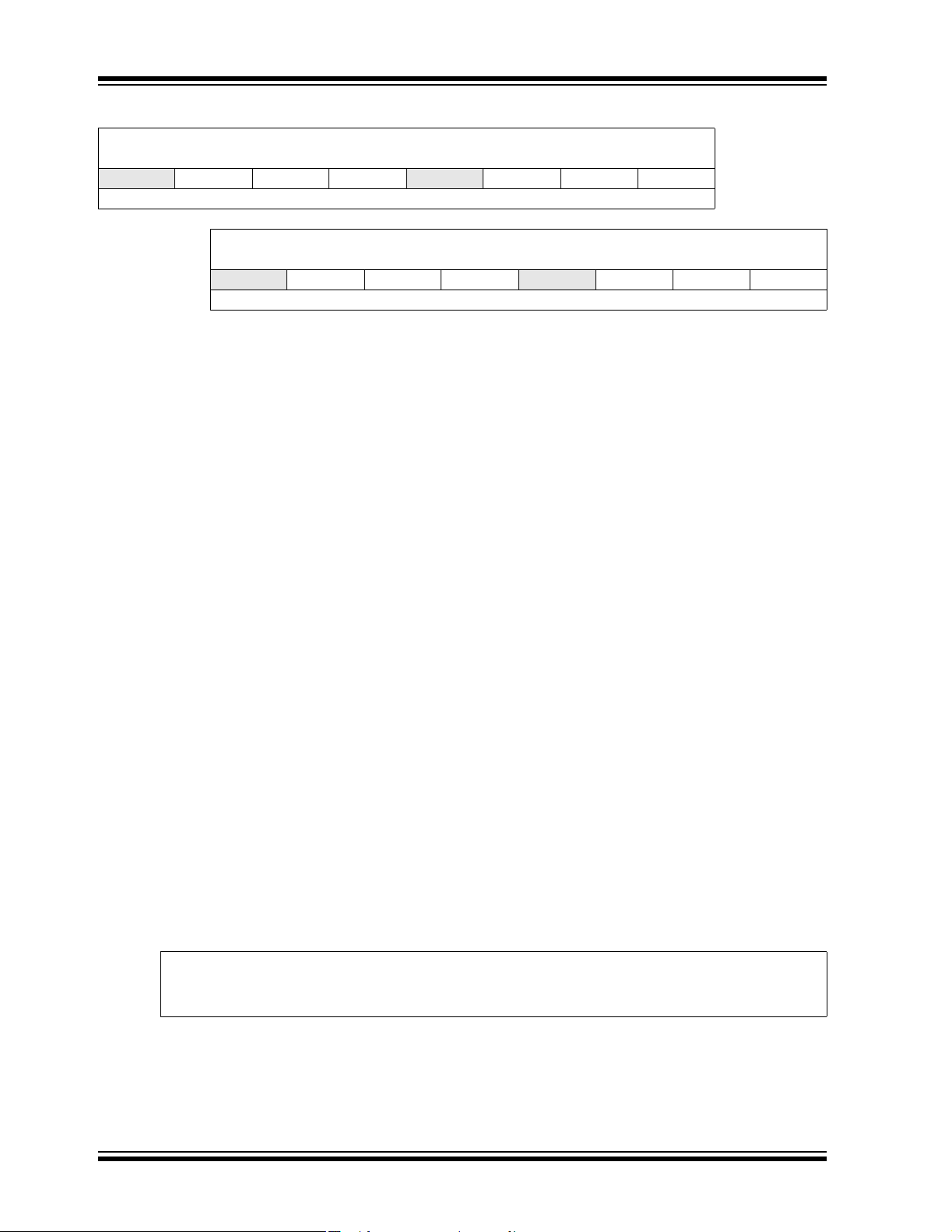

A block diagram of the CPU is shown in Figure 2-1.

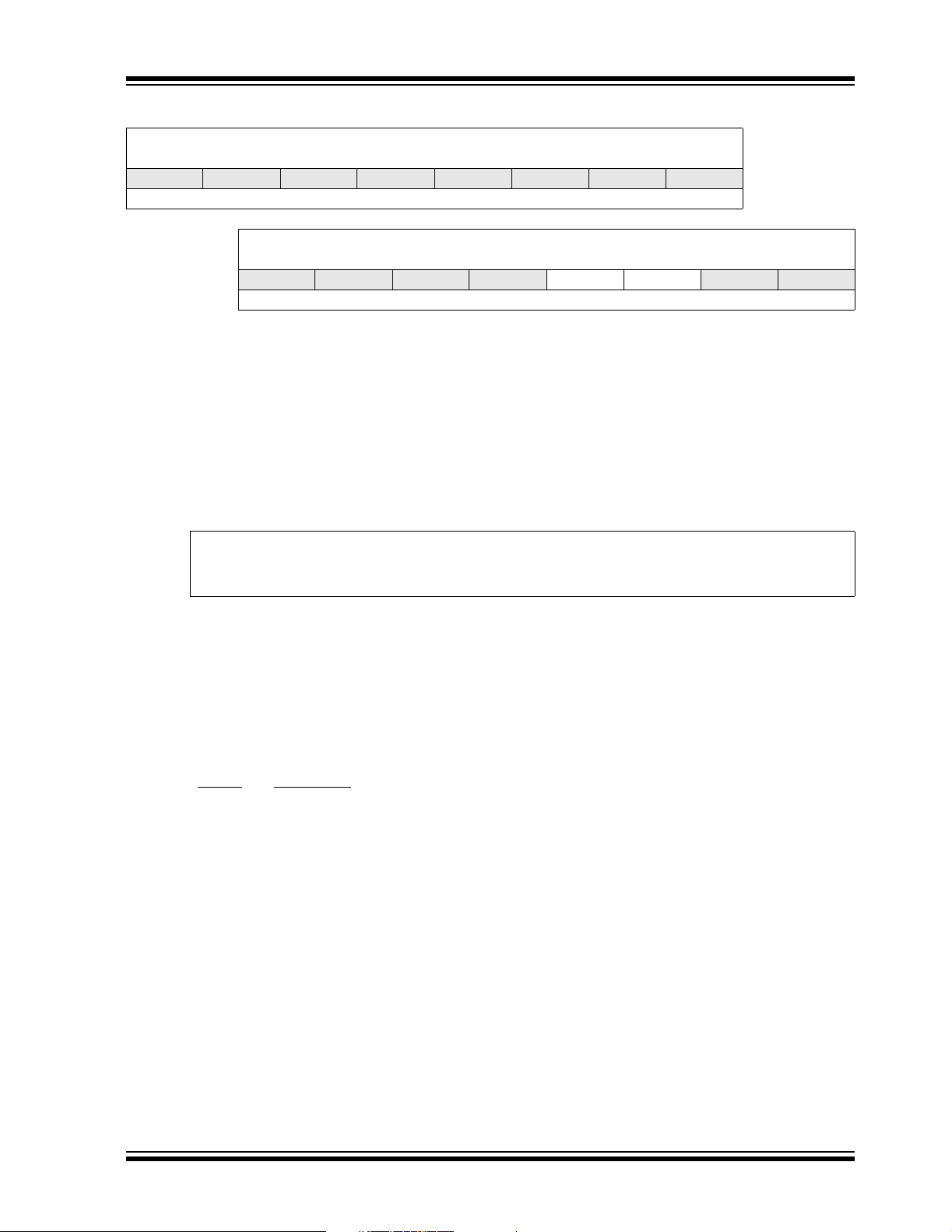

2.1 Programmer’s Model

The programmer’s model for the PIC24 is shown in

Figure 2-2. All registers in the programmer’s model are

memory mapped and can be manipulated directly by

instructions. A description of each register is provided

in Table 2-1. All registers associated with the

programmer’s model are memory mapped.

© 2006 Microchip Technology Inc. Advance Information DS39747B-page 19

Page 22

PIC24FJ128GA FAMILY

FIGURE 2-1: PIC24 CPU CORE BLOCK DIAGRAM

PSV & Table

Data Access

Control Block

Interrupt

Controller

8

23

23

23

PCU

Program Counter

Stac k

Control

Logic

16

PCH PCL

Loop

Control

Logic

Data Bus

16

16

Data Latch

Data RAM

Address

Latch

16

16

Address Latch

Program Memory

Data Latch

Address Bus

24

Instruction

Decode &

Control

Control Signals

to Various Blocks

ROM Latch

Instruction Reg

Hardware

Multiplier

Divide

Support

RAGU

WAGU

EA MUX

16

16

Literal Data

16 x 16

W Register Array

16-Bit ALU

16

16

To Peripheral Modules

DS39747B-page 20 Advance Information © 2006 Microchip Technology Inc.

Page 23

PIC24FJ128GA FAMILY

TABLE 2-1: CPU CORE REGISTERS

Register(s) Name Description

W0 through W15 Working register array

PC 23-bit Program Counter

SR ALU STATUS register

SPLIM Stack Pointer Limit Value register

TBLPAG Table Memory Page Address register

PSVPAG Program Space Visibility Page Address register

RCOUNT Repeat Loop Counter register

CORCON CPU Control Register

FIGURE 2-2: PROGRAMMER’S MODEL

015

Divider Working Registers

Multiplier Registers

W0 (WREG)

W1

W2

W3

W4

W5

W6

W7

W8

W9

W10

W11

W12

W13

W14

W15

Frame Pointer

Stack Pointer

Working/Address

Registers

0

Stack Pointer Limit

0

0

0

——

0

0

Program Counter

Data Table Page Address

0

Program Space Visibility

Page Address

0

REPEAT Loop Counter

STATUS Register (SR)

Core Control Register (CORCON)

SPLIM

22

PC

7

TBLPAG

7

PSVPAG

15

RCOUNT

IPL

210

SRL

NOVZ C

RA

IPL3 PSV

15

SRH

———————

15 0

————————————

Registers or bits shadowed for PUSH.S and POP.S instructions.

© 2006 Microchip Technology Inc. Advance Information DS39747B-page 21

DC

Page 24

PIC24FJ128GA FAMILY

2.2 CPU Control Registers

REGISTER 2-1: SR: CPU STATUS REGISTER

Upper Byte:

U-0 U-0 U-0 U-0 U-0 U-0 U -0 R/W-0

— — — — — — —DC

bit 15 bit 8

Lower Byte:

(1)

R/W-0

(2)

IPL2

bit 7 bit 0

bit 15-9 Unimplemented: Read as ‘0’

bit 8 DC: ALU Half Carry/Borrow bit

1 = A carry-out from the 4th low-order bit (for byte sized data) or 8th low-order bit (for word sized data)

of the result occurred

0 = No carry-out from the 4th or 8th low-order bit of the result has occurred

bit 7-5 IPL2:IPL0: CPU Interrupt Priority Level Status bits

111 = CPU interrupt priority level is 7 (15). User interrupts disabled.

110 = CPU interrupt priority level is 6 (14)

101 = CPU Interrupt Priority Level is 5 (13)

100 = CPU interrupt priority level is 4 (12)

011 = CPU interrupt priority level is 3 (11)

010 = CPU interrupt priority level is 2 (10)

001 = CPU interrupt priority level is 1 (9)

000 = CPU interrupt priority level is 0 (8)

Note 1: The IPL Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

2: The IPL bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU interrupt priority

level. The value in parentheses indicates the IPL when IPL3 = 1.

bit 4 RA: REPEAT Loop Active bit

1 = REPEAT loop in progress

0 = REPEAT loop not in progress

bit 3 N: ALU Negative bit

1 = Result was negative

0 = Result was non-negative (zero or positive)

bit 2 OV: ALU Overflow bit

1 = Overflow occurred for signed (2’s complement) arithmetic in this arithmetic operation

0 = No overflow has occurred

bit 1 Z: ALU Zero bit

1 = An operation which effects the Z bit has set it at some time in the past

0 = The most recent operation which effects the Z bit has cleared it (i.e., a non-zero result)

bit 0 C: ALU Carry/Borrow

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

R/W-0

IPL1

bit

(2)

(1)

R/W-0

IPL0

(2)

(1)

R-0 R/W-0 R/W-0 R/W-0 R/W-0

RA N OV Z C

(2)

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

DS39747B-page 22 Advance Information © 2006 Microchip Technology Inc.

Page 25

PIC24FJ128GA FAMILY

REGISTER 2-2: CORCON: CORE CONTROL REGISTER

Upper Byte:

U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

bit 15 bit 8

Lower Byte:

U-0 U-0 U-0 U-0 R/C-0 R/W-0 U-0 U-0

— — — — IPL3 PSV — —

bit 7 bit 0

bit 15-4 Unimplemented: Read as ‘0’

bit 3 IPL3: CPU Interrupt Priority Level Status bit

1 = CPU interrupt priority level is greater than 7

0 = CPU interrupt priority level is 7 or less

Note: User interrupts are disabled when IPL3 = 1.

bit 2 PSV: Program Space Visibility in Data Space Enable bit

1 = Program space visible in data space

0 = Program space not visible in data space

bit 1-0 Unimplemented: Read as ‘0’

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

2.3 Arithmetic Logic Unit (ALU)

The PIC24 ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless

otherwise mentioned, arithmetic operations are 2’s

complement in nature. Depending on the operation, the

ALU may affect the values of the Carry (C), Zero (Z),

Negative (N), Overflow (OV) and Digit Carry (DC)

Status bits in the SR register. The C and DC Status bits

operate as Borrow

for subtraction operations.

The ALU can perform 8-bit or 16-bit operations,

depending on the mode of the instruction that is used.

Data for the ALU operation can come from the W

register array, or data memory, depending on the

addressing mode of the instruction. Likewise, output

data from the ALU can be written to the W register array

or a data memory location.

and Digit Borrow bits, respectively,

The PIC24 CPU incorporates hardware support for

both multiplication and division. This includes a dedicated hardware multiplier and support hardware for

16-bit divisor division.

2.3.1 MULTIPLIER

The ALU contains a high-speed 17-bit x 17-bit

multiplier. It supports unsigned, signed or mixed sign

operation in several multiplication modes:

1. 16-bit x 16-bit signed

2. 16-bit x 16-bit unsigned

3. 16-bit signed x 5-bit (literal) unsigned

4. 16-bit unsigned x 16-bit unsigned

5. 16-bit unsigned x 5-bit (literal) unsigned

6. 16-bit unsigned x 16-bit signed

7. 8-bit unsigned x 8-bit unsigned

© 2006 Microchip Technology Inc. Advance Information DS39747B-page 23

Page 26

PIC24FJ128GA FAMILY

2.3.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit

signed and unsigned integer divide operation with the

following data sizes:

1. 32-bit signed/16-bit signed divide

2. 32-bit unsigned/16-bit unsigned divide

3. 16-bit signed/16-bit signed divide

4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0

and the remainder in W1. 16-bit signed and unsigned

DIV instructions can specify any W register for both the

16-bit divisor (Wn) and any W register (aligned) pair

(m+1):Wm) for the 32-bit dividend. The divide algo-

(W

rithm takes one cycle per bit of divisor, so both

32-bit/16-bit and 16-bit/16-bit instructions take the

same number of cycles to execute.

2.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24 ALU supports both single-bit and

single-cycle, multi-bit arithmetic and logic shifts.

Multi-bit shifts are implemented using a shifter block,

capable of performing up to a 15-bit arithmetic right

shift, or up to a 15-bit left shift, in a single cycle. All

multi-bit shift instructions only support register direct

addressing for both the operand source and result

destination.

A full summary of instructions that use the shift

operation is provided below in Table 2-2.

TABLE 2-2: INSTRUCTIONS THAT USE THE SINGLE AND MULTI-BIT SHIFT OPERATION

Instruction Description

ASR Arithmetic shift right source register by one bit.

ASRF Arithmetic shift right the content of the register by one bit.

ASRW Arithmetic shift right source register by up to 15 bits, value held in the W register referenced

within instruction.

ASRK Arithmetic shift right source register up to 15 bits. Shift value is literal.

SL Shift left source register by one bit.

SLF Shift left the content of the file register by one bit.

SLW Shift left source register by up to 15 bits, value held in the W register referenced instruction.

SLK Shift left source register up to 15 bits. Shift value is literal.

LSR Logical shift right source register by one bit.

LSRF Logical shift right the content of the register by one bit.

LSRW Logical shift right source register by up to 15 bits, value held in the W register referenced

within instruction.

LSRK Logical shift right source register up to 15 bits. Shift value is literal.

DS39747B-page 24 Advance Information © 2006 Microchip Technology Inc.

Page 27

PIC24FJ128GA FAMILY

3.0 MEMORY ORGANIZATION

As Harvard architecture devices, PIC24 microcontrollers feature separate program and data memory

spaces and busses. This architecture also allows the

direct access of program memory from the data space

during code execution.

3.1 Program Address Space

The program address memory space of

PIC24FJ128GA family devices is 4M instructions. The

space is addressable by a 24-bit value derived from

either the 23-bit Program Counter (PC) during program

execution, or from table operation or data space

remapping, as described in Section 3.3 “Interfacing

Program and Data Memory Spaces”.

User access to the program memory space is restricted

to the lower half of the address range (000000h to

7FFFFFh). The exception is the use of TBLRD/TBLWT

operations, which use TBLPAG<7> to permit access to

the Configuration bits and Device ID sections of the

configuration memory space.

© 2006 Microchip Technology Inc. Advance Information DS39747B-page 25

Page 28

PIC24FJ128GA FAMILY

3.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word

addressable blocks. Although it is treated as 24 bits

wide, it is more appropriate to think of each address of

the program memory as a lower and upper word, with

the upper byte of the upper word being unimplemented.

The lower word always has an even address, while the

upper word has an odd address (Figure 3-2).

Program memory addresses are always word-aligned

on the lower word, and addresses are incremented or

decremented by two during code execution. This

arrangement also provides compatibility with data

memory space addressing and makes it possible to

access data in the program memory space.

3.1.2 HARD MEMORY VECTORS

All PIC24 devices reserve the addresses between

00000h and 000200h for hard coded program execution vectors. A hardware Reset vector is provided to

redirect code execution from the default value of the

PC on device Reset to the actual start of code. A GOTO

instruction is programmed by the user at 000000h, with

the actual address for the start of code at 000002h.

PIC24 devices also have two interrupt vector tables,

located from 000004h to 0000FFh and 000100h to

0001FFh. These vector tables allow each of the many

device interrupt sources to be handled by separate

ISRs. A more detailed discussion of the interrupt vector

tables is provided in Section 6.1 “Interrupt Vector

Tabl e”.

3.1.3 FLASH CONFIGURATION WORDS

In PIC24FJ128GA family devices, the top two words of

on-chip program memory are reserved for configuration information. On device Reset, the configuration

information is copied into the appropriate Configuration

registers. The addresses of the Flash Configuration

Word for devices in the PIC24FJ128GA family are

shown in Table 3-1. Their location in the memory map

is shown with the other memory vectors in Figure 3-1.

The Configuration Words in program memory are a

compact format. The actual Configuration bits are

mapped in several different registers in the configuration memory space. Their order in the Flash Configuration Words do not reflect a corresponding arrangement

in the configuration space. Additional details on the

device Configuration Words are provided in

Section 23.1 “Configuration Bits”.

TABLE 3-1: FLASH CONFIGURATION

WORDS FOR PIC24FJ128GA

FAMILY DEVICES

Program

Device

PIC24FJ64GA 22 00ABFCh:

PIC24FJ96GA 32 00FFFCh:

PIC24FJ128GA 44 0157FCh:

Memory

(K words)

Configuration

Word

Addresses

00ABFEh

00FFFEh

0157FEh

FIGURE 3-2: PROGRAM MEMORY ORGANIZATION

msw

Address (lsw Address)

000001h

000003h

000005h

000007h

DS39747B-page 26 Advance Information © 2006 Microchip Technology Inc.

most significant word

23

00000000

00000000

00000000

00000000

Program Memory

‘Phantom’ Byte

(read as ‘0’)

least significant word

Instruction Width

PC Address

0816

000000h

000002h

000004h

000006h

Page 29

PIC24FJ128GA FAMILY

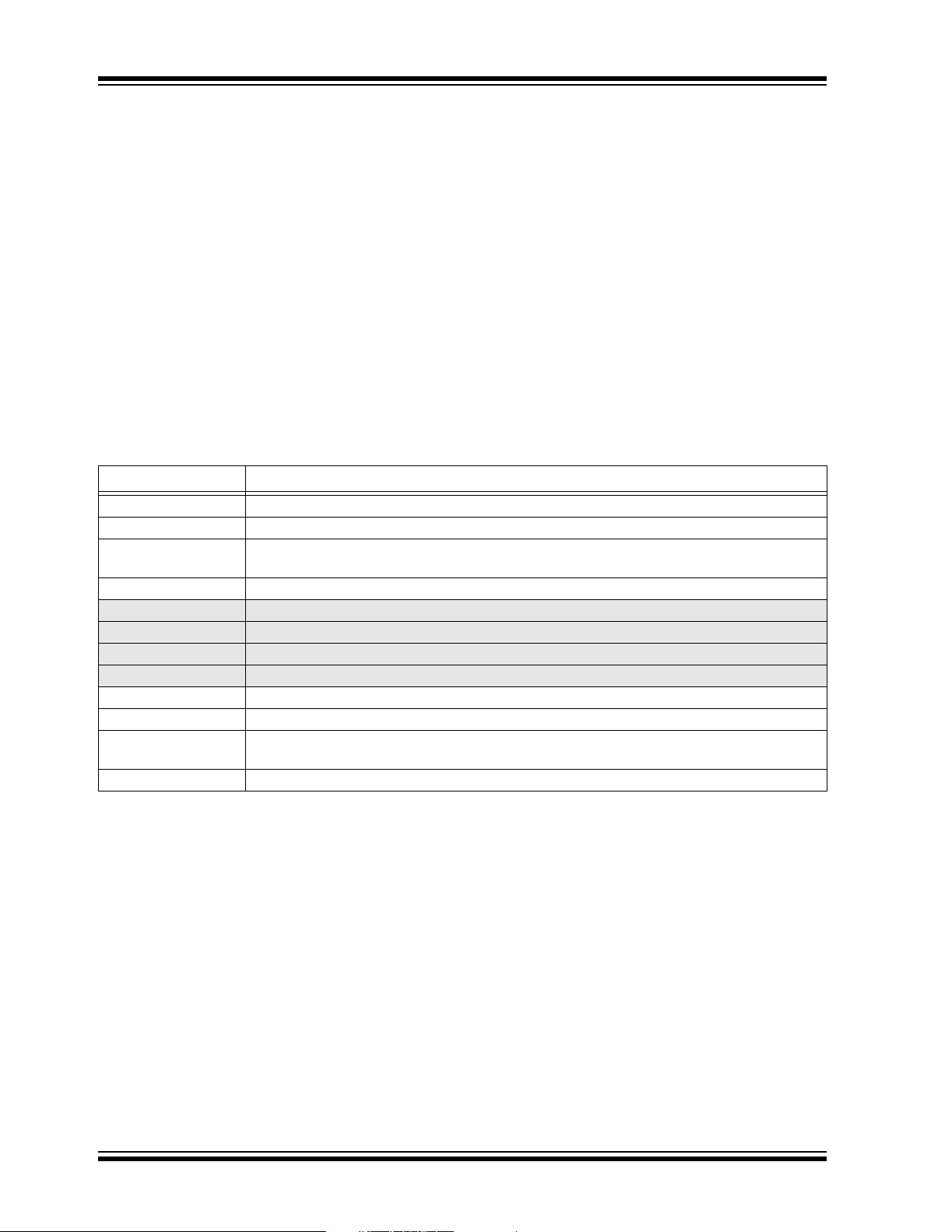

3.2 Data Address Space

The PIC24 core has a separate 16-bit wide data memory space, addressable as a single linear range. The

data space is accessed using two Address Generation

Units (AGUs), one each for read and write operations.

The data space memory map is shown in Figure 3-3.

All Effective Addresses (EAs) in the data memory

space are 16 bits wide, and point to bytes within the

data space. This gives a data space address range of

64 Kbytes, or 32K words. The lower half of the data

memory space (that is, when EA<15> = 0) is used for

implemented memory addresses, while the upper half

(EA<15> = 1) is reserved for the Program Space Visibility area (see Section 3.3.3 “Reading Data from

Program Memory Using Program Space Visibility”).

PIC24FJ128GA family devices implement a total of

8 Kbytes of data memory. Should an EA point to a location outside of this area, an all zero word or byte will be

returned.

3.2.1 DATA SPACE WIDTH

The data memory space is organized in byte addressable, 16-bit wide blocks. Data is aligned in data

memory and registers as 16-bit words, but all data

space EAs resolve to bytes. The Least Significant

Bytes of each word have even addresses, while the

Most Significant Bytes have odd addresses.

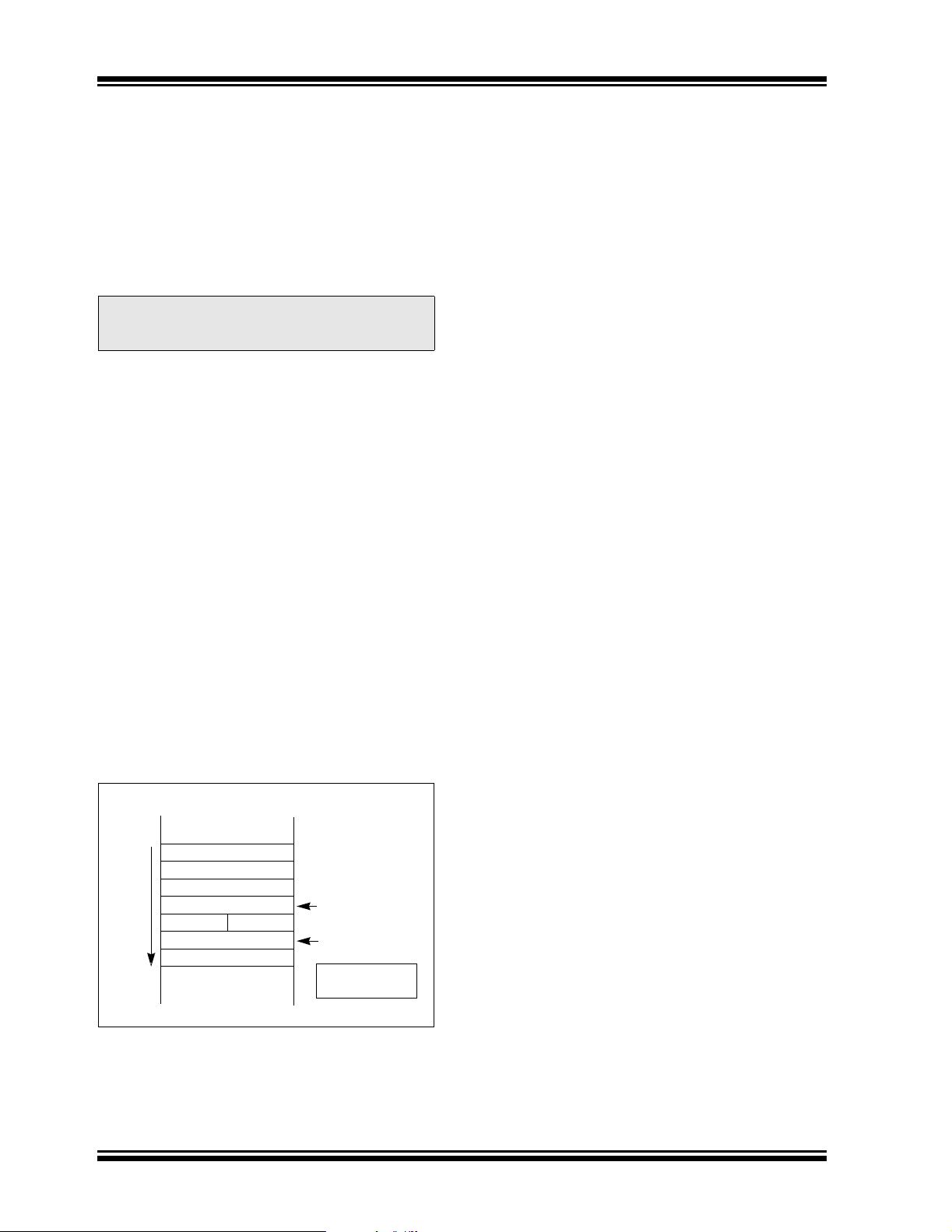

FIGURE 3-3: DATA SPACE MEMORY MAP FOR PIC24FJ128GA FAMILY DEVICES

LSB

Address

0000h

07FEh

0800h

1FFEh

2000h

07FEh

0800h

SFR

Space

Near

Data Space

Implemented

Data RAM

MSB

Address

0001h

07FFh

0801h

1FFFh

2001h

27FFh

2801h

LSBMSB

SFR Space

Data RAM

Unimplemented

Read as ‘0’

7FFFh

8001h

Program Space

Visibility Area

FFFFh

Note: Data memory areas are not shown to scale.

7FFFh

8000h

FFFEh

© 2006 Microchip Technology Inc. Advance Information DS39747B-page 27

Page 30

PIC24FJ128GA FAMILY

3.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PICmicro

devices and improve data space memory usage efficiency, the PIC24 instruction set supports both word

and byte operations. As a consequence of byte accessibility, all effective address calculations are internally

scaled to step through word-aligned memory. For

example, the core recognizes that Post-Modified

Register Indirect Addressing mode [Ws++] will result in

a value of Ws + 1 for byte operations and Ws + 2 for

word operations.

Data byte reads will read the complete word which contains the byte, using the LSb of any EA to determine

which byte to select. The selected byte is placed onto

the LSB of the data path. That is, data memory and registers are organized as two parallel byte-wide entities

with shared (word) address decode but separate write

lines. Data byte writes only write to the corresponding

side of the array or register which matches the byte

address.

All word accesses must be aligned to an even address.

Misaligned word data fetches are not supported, so

care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a

misaligned read or write is attempted, an address error

trap will be generated. If the error occurred on a read,

the instruction underway is completed; if it occurred on

a write, the instruction will be executed but the write will

not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine

state prior to execution of the address Fault.

All byte loads into any W register are loaded into the

Least Significant Byte. The Most Significant Byte is not

modified.

A sign-extend instruction (SE) is provided to allow

users to translate 8-bit signed data to 16-bit signed

®

values. Alternatively, for 16-bit unsigned data, users

can clear the MSB of any W register by executing a

zero-extend (ZE) instruction on the appropriate

address.

Although most instructions are capable of operating on

word or byte data sizes, it should be noted that some

instructions operate only on words.

3.2.3 NEAR DATA SPACE

The 8-Kbyte area between 0000h and 1FFFh is

referred to as the near data space. Locations in this

space are directly addressable via a 13-bit absolute

address field within all memory direct instructions. The

remainder of the data space is addressable indirectly.

Additionally, the whole data space is addressable using

MOV instructions, which support Memory Direct

Addressing with a 16-bit address field.

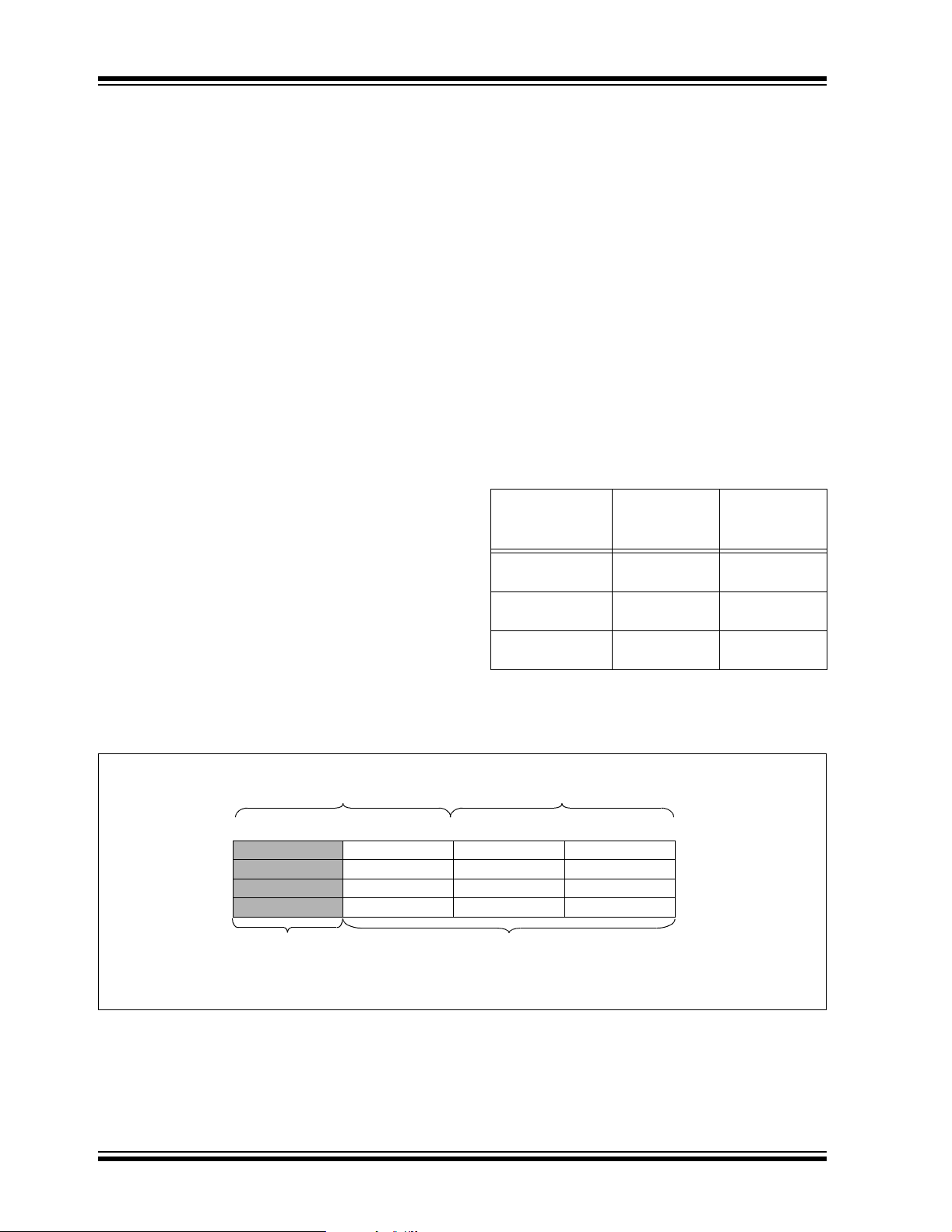

3.2.4 SFR SPACE

The first 2 Kbytes of the near data space, from 0000h

to 07FFh, are primarily occupied with Special Function

Registers (SFRs). These are used by the PIC24 core

and peripheral modules for controlling the operation of

the device.

SFRs are distributed among the modules that they control, and are generally grouped together by module.

Much of the SFR space contains unused addresses;

these are read as ‘0’. A diagram of the SFR space,

showing where SFRs are actually implemented, is

shown in Table 3-2. Each implemented area indicates

a 32-byte region where at least one address is implemented as an SFR. A complete listing of implemented

SFRs, including their addresses, is shown in Tables 3-3

through 3-30.

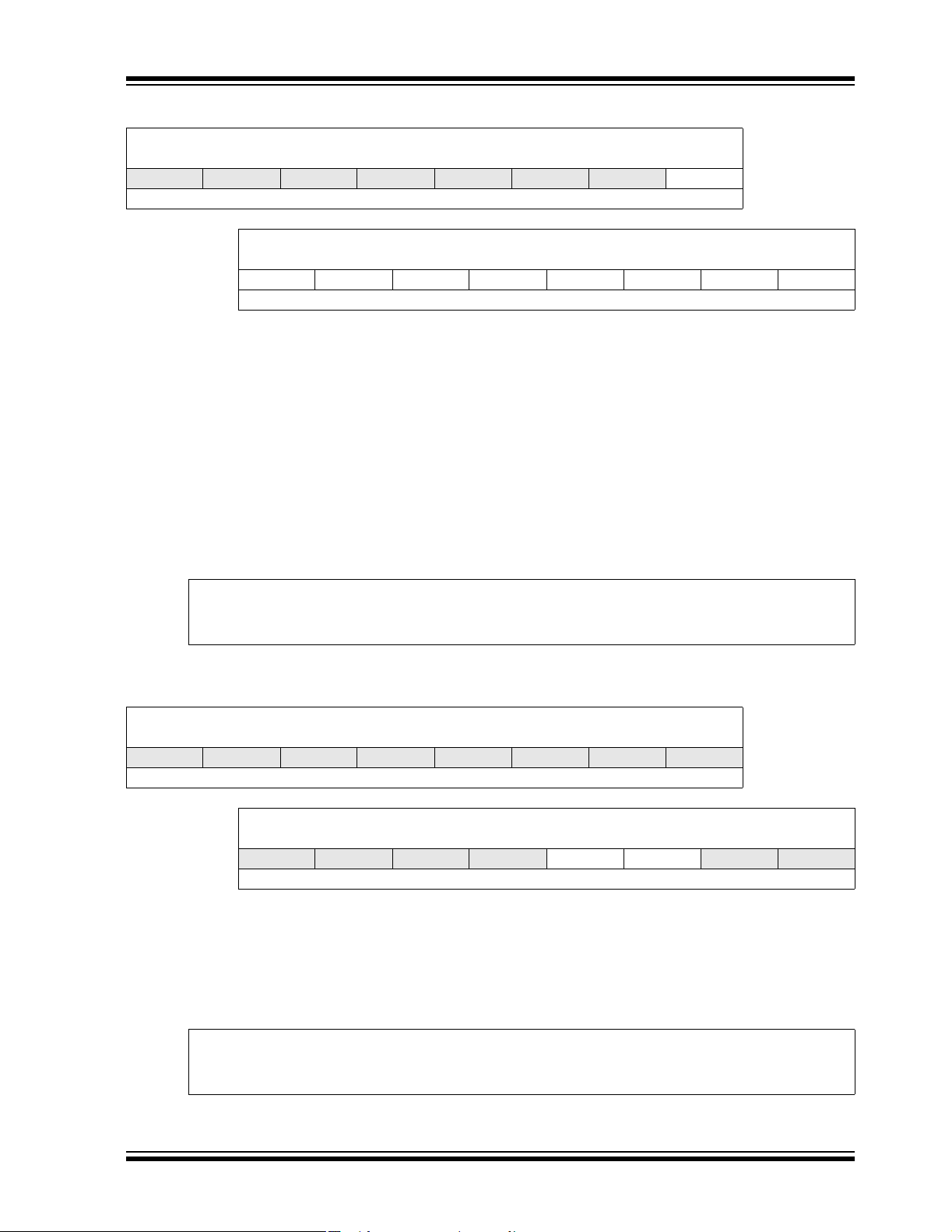

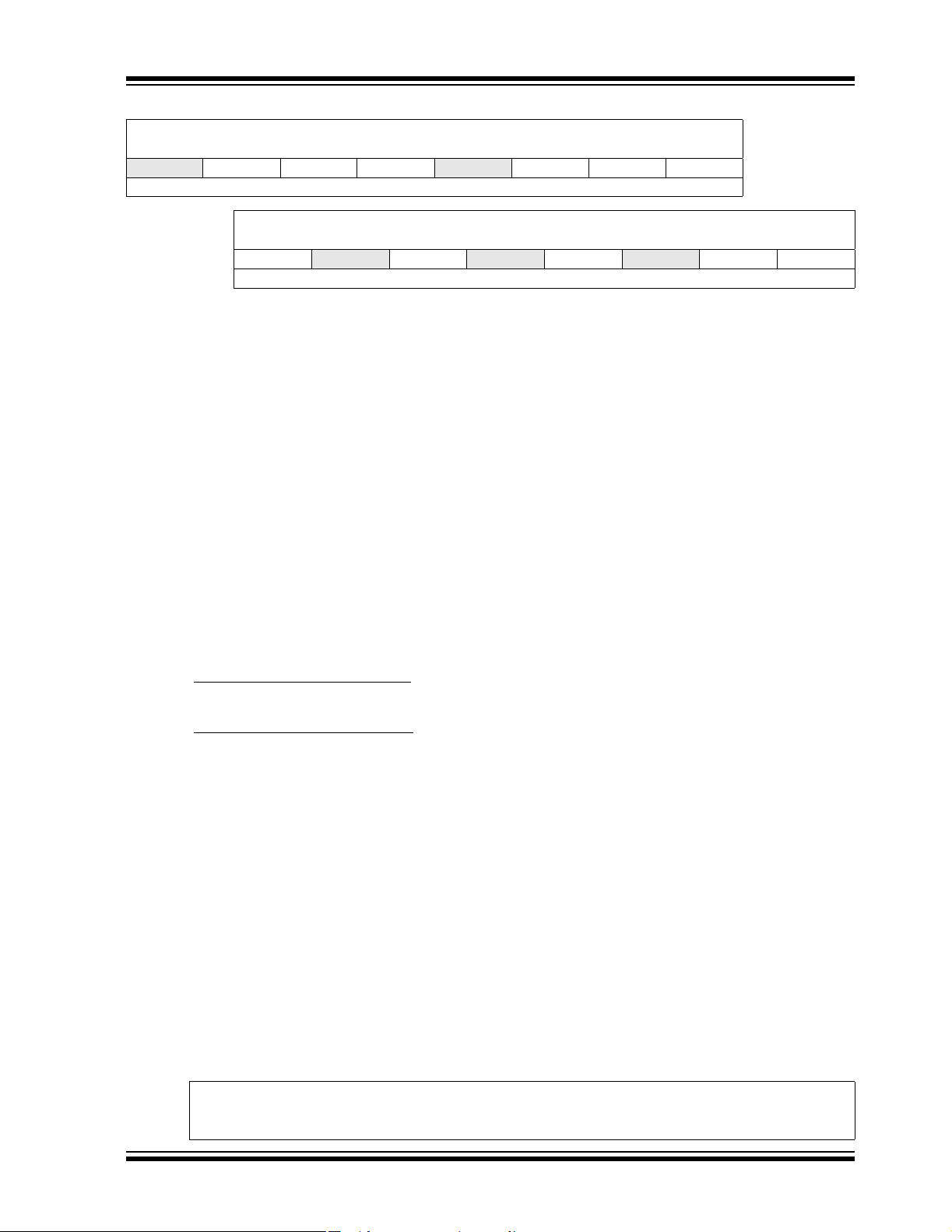

TABLE 3-2: IMPLEMENTED REGIONS OF SFR DATA SPACE

SFR Space Address

xx00 xx20 xx40 xx60 xx80 xxA0 xxC0 xxE0

000h Core ICN Interrupts

100h Timers Capture

2

200h I

300h A/D — — — — I/O

400h

500h

600h PMP RTC/Comp CRC — — — I/O

700h

Legend: — = No implemented SFRs in this block

DS39747B-page 28 Advance Information © 2006 Microchip Technology Inc.

C™ UART SPI — — I/O

— — — — — — — —

— — — — — — — —

— — System NVM/PMD — — — —

— Compare — — —

—

Page 31

PIC24FJ128GA FAMILY

All

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0800

xxxx

0000

0000

0000

0000

xxxx

0000

0000

Resets

xxxx

File Name Addr Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

WREG0 0000 Working Register 0

WREG1 0002 Working Register 1

WREG2 0004 Working Register 2

WREG3 0006 Working Register 3

WREG4 0008 Working Register 4

WREG5 000A Working Register 5

WREG6 000C Working Register 6

WREG7 000E Working Register 7

WREG8 0010 Working Register 8

WREG9 0012 Working Register 9

WREG10 0014 Working Register 10

WREG11 0016 Working Register 11

WREG12 0018 Working Register 12

WREG13 001A Working Register 13

WREG14 001C Working Register 14

WREG15 001E Working Register 15

SPLIM 0020 Stack Pointer Limit

PCL 002E Program Counter, Low Word

PCH 0030 — — — — — — — — Program Counter, High Byte

TBLPAG 0032 — — — — — — — — Table Page Address Pointer

PSVPAG 0034 — — — — — — — — Program Memory Visibility Page Address Pointer

RCOUNT 0036 Repeat Loop Counter

SR 0042 — — — — — — — DC IPL2 IPL1 IPL0 RA N OV Z C

CORCON 0044 — — — — — — — — — — — —IPL3PSV— —

DISICNT 0052 — — Disable Interrupts Counter

TABLE 3-3: CPU CORE REGISTERS MAP

Legend: x = unknown value on Reset, — = unimplemented, read as ‘0’. Reset values are shown in hexadecimal.

© 2006 Microchip Technology Inc. Advance Information DS39747B-page 29

Page 32

PIC24FJ128GA FAMILY

All

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

4444

4440

4444

0044

Resets

4444

0004

4440

4444

0044

4440

0040

0040

0440

0440

0400

4440

File Name Addr Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

INTCON1 0080 NSTDIS — — — — — — — — — — MATHERR ADDRERR STKERR OSCFAIL —

INTCON2 0082 ALTIVT DISI — — — — — — — — — INT4EP INT3EP INT2EP INT1EP INT0EP

IFS0 0084 — — AD1IF U1TXIF U1RXIF SPI1IF SPF1IF T3IF T2IF OC2IF IC2IF — T1IF OC1IF IC1IF INT0IF

IFS1 0086 U2TXIF U2RXIF INT2IF T5IF T4IF OC4IF OC3IF — — — — INT1IF CNIF CMIF MI2C1IF SI2C1IF

IFS2 0088 — —PMPIF— — —OC5IF— IC5IF IC4IF IC3IF — — — SPI2IF SPF2IF

IFS3 008A —RTCIF — — — — — — — INT4IF INT3IF — —MI2C2IFSI2C2IF—

IFS4 008C — — — — — — — — — — — — CRCIF U2ERIF U1ERIF —

IEC0 0094 — — AD1IE U1TXIE U1RXIE SPI1IE SPF1IE T3IE T2IE OC2IE IC2IE — T1IE OC1IE IC1IE INT0IE

IEC1 0096 U2TXIE U2RXIE INT2IE T5IE T4IE OC4IE OC3IE — — — — INT1IE CNIE CMIE MI2C1IE SI2C1IE

IEC2 0098 — —PMPIE— — —OC5IE— IC5IE IC4IE IC3IE — — —SPI2IESPF2IE

IEC3 009A —RTCIE — — — — — — — INT4IE INT3IE — — MI2C2IE SI2C2IE —

IEC4 009C — — — — — — — — — — — — CRCIE U2ERIE U1ERIE —

IPC0 00A4 — T1IP2 T1IP1 T1IP0 — OC1IP2 OC1IP1 OC1IP0 — IC1IP2 IC1IP1 IC1IP0 — INT0IP2 INT0IP1 INT0IP0

IPC1 00A6 — T2IP2 T2IP1 T2IP0 — OC2IP2 OC2IP1 OC2IP0 — IC2IP2 IC2IP1 IC2IP0 — — — —

IPC2 00A8 — U1RXIP2 U1RXIP1 U1RXIP0 — SPI1IP2 SPI1IP1 SPI1IP0 — SPF1IP2 SPF1IP1 SPF1IP0 — T3IP2 T3IP1 T3IP0

IPC3 00AA — — — — — — — — — AD1IP2 AD1IP1 AD1IP0 — U1TXIP2 U1TXIP1 U1TXIP0

IPC4 00AC — CNIP2 CNIP1 CNIP0 — CMIP2 CMIP1 CMI P0 — MI2C1P2 MI2C1P1 MI2C1P0 — SI2C1P2 SI2C1P1 SI2C1P0

IPC5 00AE — — — — — — — — — — — — — INT1IP2 INT1IP1 INT1IP0

IPC6 00B0 — T4IP2 T4IP1 T4IP0 — OC4IP2 OC4IP1 OC4IP0 — OC3IP2 OC3IP1 OC3IP0 — — — —

IPC7 00B2 — U2TXIP2 U2TXIP1 U2TXIP0 — U2RXIP2 U2RXIP1 U2RXIP0 — INT2IP2 INT2IP1 INT2IP0 — T5IP2 T5IP1 T5IP0

IPC8 00B4 — — — — — — — — — SPI2IP2 SPI2IP1 SPI2IP0 — SPF2IP2 SPF2IP1 SPF2IP0

IPC9 00B6 — IC5IP2 IC5IP1 IC5IP0 — IC4IP2 IC4IP1 IC4IP0 — IC3IP2 IC3IP1 IC3IP0 — — — —

IPC10 00B8 — — — — — — — — — OC5IP2 OC5IP1 OC5IP0 — — — —

IPC11 00BA — — — — — — — — — PMPIP2 PMPIP1 PMPIP0 — — — —

IPC12 00BC — — — — — MI2C2P2 MI2C2P1 MI2C2P0 — SI2C2P2 SI2C2P1 SI2C2P0 — — — —

IPC13 00BE — — — — — INT4IP2 INT4IP1 INT4IP0 — INT3IP2 INT3IP1 INT3IP0 — — — —

IPC15 00C2 — — — — — RTCIP2 RTCIP1 RTCIP0 — — — — — — — —

IPC16 00C4 — CRCIP2 CRCIP1 CRCIP0 — U2ERIP2 U2ERIP1 U2ERIP0 — U1ERIP2 U1ERIP1 U1ERIP0 — — — —

TABLE 3-4: INTERRUPT CONTROLLER REGISTER MAP

Legend: — = unimplemented, read as ‘0’. Reset values are shown in hexadecimal.

DS39747B-page 30 Advance Information © 2006 Microchip Technology Inc.

Page 33

PIC24FJ128GA FAMILY

All

0000

0000

0000

Resets

0000

All

xxxx

FFFF

0000

xxxx

xxxx

xxxx

FFFF

FFFF

0000

0000

xxxx

xxxx

xxxx

FFFF

FFFF

0000

Resets

0000

File Name Addr Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

TMR1 0100 Timer1 Register

PR1 0102 Period Register 1

T1CON 0104 TON —TSIDL— — — — — — TGATE TCKPS1 TCKPS0 — TSYNC TCS —

TMR2 0106 Timer2 Register

TMR3HLD 0108 Timer3 Holding Register (For 32-bit timer operations only)

TMR3 010A Timer3 Register

PR2 010C Period Register 2

PR3 010E Period Register 3

T2CON 0110 TON —TSIDL— — — — — — TGATE TCKPS1 TCKPS0 T32 —TCS—

T3CON 0112 TON —TSIDL— — — — — — TGATE TCKPS1 TCKPS0 — —TCS—

TMR4 0114 Timer4 Register

TMR5HLD 0116 Timer5 Holding Register (For 32-bit operations only)

TMR5 0118 Timer5 Register

PR4 011A Period Register 4

PR5 011C Period Register 5

T4CON 011E TON —TSIDL— — — — — — TGATE TCKPS1 TCKPS0 T32 —TCS—

T5CON 0120 TON —TSIDL— — — — — — TGATE TCKPS1 TCKPS0 — —TCS—

File Name Addr Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

CNEN1 0060 CN15IE CN14IE CN13IE CN12IE CN11IE CN10IE CN9IE CN8IE CN7IE CN6IE CN5IE CN4IE CN3IE CN2IE CN1IE CN0IE

CNEN2 0062 — — — — — — — — — — CN21IE CN20IE CN19IE CN18IE CN17IE CN16IE

CNPU1 0068 CN15PUE CN14PUE CN13PUE CN12PUE CN11PUE CN10PUE CN9PUE CN8PUE CN7PUE CN6PUE CN5PUE CN4PUE CN3PUE CN2PUE CN1PUE CN0PUE

CNPU2 006A — — — — — — — — — — CN21PUE CN20PUE CN19PUE CN18PUE CN17PUE CN16PUE

TABLE 3-5: ICN REGISTER MAP

Legend: — = unimplemented, read as ‘0’. Reset values are shown in hexadecimal.

TABLE 3-6: TIMER REGISTER MAP

Legend: x = unknown value on Reset, — = unimplemented, read as ‘0’. Reset values are shown in hexadecimal.

© 2006 Microchip Technology Inc. Advance Information DS39747B-page 31

Page 34

PIC24FJ128GA FAMILY

All

All

xxxx

xxxx

0000

xxxx

xxxx

0000

xxxx

xxxx

0000

xxxx

xxxx

0000

xxxx

xxxx

xxxx

0000

xxxx

0000

xxxx

0000

xxxx

0000

xxxx