PIC18F6X2X/8X2X

Data Sheet

64/80-Pin High Performance,

64-Kbyte Enhanced FLASH

Microcontrollers with A/D

2003 Microchip Technology Inc. Advance Information DS39612A

Note the following details of the code protection feature on Microchip devices:

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protect ion features of our

products. Attempts to break microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device

applications and the like is intended through suggestion only

and may be superseded by updates. It is your responsibility to

ensure that your application meets with your specifications.

No representation or warranty is given and no liability is

assumed by Microchip Technology Incorporated with respect

to the accuracy or use of such information, or infringement of

patents or other intellectual property rights arising from such

use or otherwise. Use of Microchip’s products as critical

components in life support systems is not authorized except

with express written approval by Microchip. No licenses are

conveyed, implicitly or otherwise, under any intellectual

property rights.

Trademarks

The Microchip name and logo, the Microchip logo, dsPIC,

K

EELOQ, MPLAB, PIC, PICmicro, PICSTART , PRO MA TE and

PowerSmart are registered trademarks of Microchip

Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXL AB, PICMASTER, SEEVAL

and The Embedded Control Solutions Company are

registered trademarks of Microchip Technology Incorporated

in the U.S.A.

Accuron, Application Maestro, dsPICDEM, dsPICDEM.net,

ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, InCircuit Serial Programming, ICSP, ICEPIC, microPort,

Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM,

PICC, PICkit, PICDEM, PICDEM.net, PowerCal, PowerInfo,

PowerMate, PowerTool, rfLAB, rfPIC, Select Mode,

SmartSensor, SmartShunt, SmartT el and T otal Endurance are

trademarks of Microchip Technology Incorporated in the

U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark

of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2003, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received QS-9000 quality system

certification for its worldwide headquarters,

design and wafer fabrication facilities in

Chandler and Tempe, Arizona in July 1999

and Mountain View, California in March 2002.

The Company’s quality system processes and

procedures are QS-9000 compliant for its

PICmicro

devices, Serial EEPROMs, microperipherals,

non-volatile memory and analog products. In

addition, Microchip’s quality system for the

design and manufacture of development

systems is ISO 9001 certified.

®

8-bit MCUs, KEELOQ

®

code hopping

DS39612A-page ii Advance Information 2003 Microchip Technology Inc.

PIC18F6X2X/8X2X

64/80-Pin High Performance, 64-Kbyte Enhanced FLASH

Microcontrollers with A/D

High Performance RISC CPU:

• Linear program memory addressing to 64 Kbytes

• Linear data memory addressing to 4 Kbytes

• 1 Kbyte of data EEPROM

• Up to 10 MIPs operation:

- DC - 40 MHz osc./clock input

- 4 MHz - 10 MHz osc./clock input with PLL active

• 16-bit wide instructions, 8-bit wide data path

• Priority levels for interrupts

• 31-level, software accessible hardware stack

• 8 x 8 Single Cycle Hardware Multiplier

Peripheral Features:

• High current sink/so ur ce 25 mA/25 mA

• Four external interrup t pin s

• Timer0 module: 8-bit/16-bit tim er/counter

• Timer1 module: 16-bit timer/counter

• Timer2 module: 8-bit timer/counter

• Timer3 module: 16-bit timer/counter

• Timer4 module: 8-bit timer/counter

• Secondary oscilla to r c lo ck option - Timer1/Timer3

• Two Capture/Compare/PWM (CCP) mo dul es :

- Capture is 16-bit, max. resolution 6.25 ns (T

- Compare is 16-bit, max. resolution 100 ns (T

- PWM output: PWM re sol ution is 1 to 10-bit

• Three Enhanced Capture/Compare/PWM (ECCP)

modules:

- Same Capture/ Compare features as CCP

- One, two, or four PWM ou tp uts

- Selectable polarity

- Programmabl e dead-time

- Auto shutdown on ext er nal event

- Auto Restart

• Master Synchronous Se rial Por t (MSSP) module

with two modes of operation:

- 3-wire SPI™ (supports all 4 SPI modes)

2

C™ Master and Slave mo de

-I

• Two Enhanced USART modules:

- Supports RS-485, R S-2 32, and LIN 1.2

- Auto wake-up on START bit

- Auto baud detec t

• Parallel Slave Port (PSP) module

CY/16)

CY)

External Memory Interface (PIC18F8X2X Devices Only):

• Address capability of up to 2 Mbytes

• 16-bit interface

Analog Features:

• 10-bit, up to 16-channel Analog-to-Digital

Converter (A/D):

- Auto acquisition

- Conversion av ai labl e during SLEEP

• Programmable 16 -level Low Voltage Detection

(LVD) module:

- Supports interrupt on Low Voltage Detection

• Programmable Brown-out Reset (BOR)

• Dual analog comparat or s:

- Programmabl e i nput/output configuration

Special Microcontroller Features:

• 100,000 erase/write cycle Enhanced FLASH

program memory typical

• 1,000,000 erase/write cycle Data EEPROM

memory typical

• 1 second program m in g t ime

• FLASH/Data EEPROM Retention: > 100 years

• Self-reprogramm a bl e under software control

• Power-on Reset (POR) , P ower-up Timer (PWRT)

and Oscillator Start-up Timer (OST)

• Watchdog Timer (WDT) with its own On-Chip

RC Oscillator for reliable operation

• Programmable co de protection

• Power saving SLEEP mode

• Selectable oscillator options including:

- 4X Phase Lock Loop (of primary oscillator)

- Secondary Oscillator (32 kHz) clock inp ut

• In-Circuit Serial Programming™ (ICSP™) via two pins

•MPLAB

®

In-Circuit Debug (ICD 2) via tw o pins

CMOS Technology:

• Low power, high speed FLASH technology

• Fully static design

• Wide operating voltage range (2.0V to 5.5V)

• Industrial and Extended temperature ranges

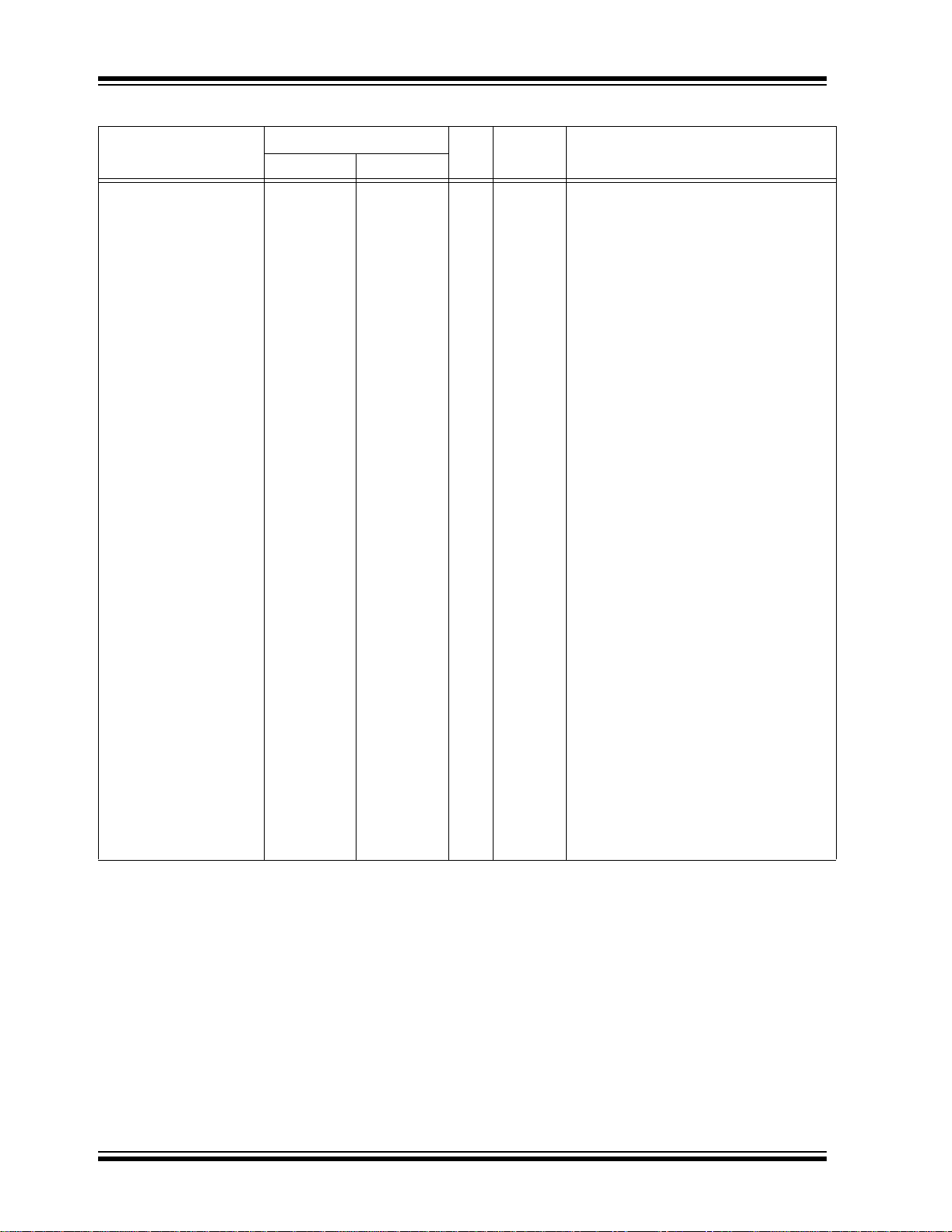

Program Memory Data Memory

Device

PIC18F6525 48K 24576 3840 1024 53 12 2/3 14 Y 2 2/3 N

PIC18F6621 64K 32768 3840 1024 53 12 2/3 14 Y 2 2/3 N

PIC18F8525 48K 24576 3840 1024 69 16 2/3 14 Y 2 2/3 Y

PIC18F8621 64K 32768 3840 1024 69 16 2/3 14 Y 2 2/3 Y

2003 Microchip Technology Inc. Advance Information DS39612A-page 1

Bytes

# Single

Word

Instructions

SRAM

(bytes)

EEPROM

(bytes)

I/O

10-bit

A/D

(ch)

CCP/

ECCP

PWM

MSSP/

SPI/

Master I

2

C

EUSART

Timers

8-bit/16-bit

EMI

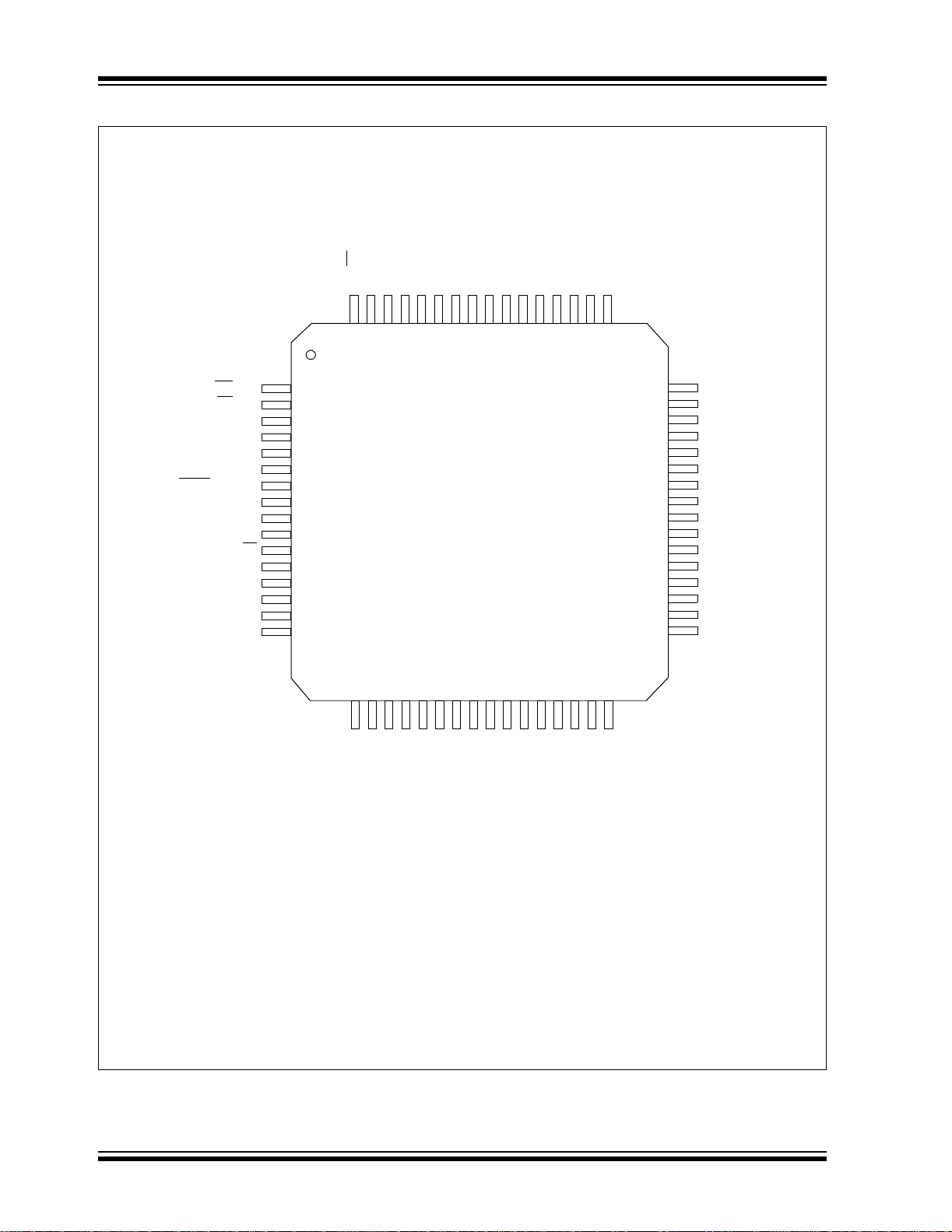

PIC18F6X2X/8X2X

Pin Diagrams

64-Pin TQFP

RE3/P3C

RE2/CS/P2B

(1)

/P2A

(1)

RE4/P3B

RE5/P1C

RE6/P1B

RE7/CCP2

RD0/PSP0

VDDVSS

RD1/PSP1

RD2/PSP2

RD3/PSP3

RD4/PSP4

RD5/PSP5

RD6/PSP6

RD7/PSP7

RE1/WR/P2C

RE0/RD

/P2D

RG0/CCP3/P3A

RG1/TX2/CK2

RG2/RX2/DT2

RG3/CCP4/P3D

/VPP/RG5

MCLR

RG4/CCP5/P1D

V

VDD

RF7/SS

RF6/AN11

RF5/AN10/CV

RF2/AN7/C1OUT

REF

RF4/AN9

RF3/AN8

64

63 62 61

1

2

3

4

5

6

7

SS

8

9

10

11

12

13

14

15

16

17 18 19 20 21 22 23 24 25 26

DD

AV

RF0/AN5

RF1/AN6/C2OUT

PIC18F6525

PIC18F6621

REF-

AVSS

RA2/AN2/V

RA3/AN3/VREF+

RA1/AN1

RA0/AN0

54 53 52 5158 57 56 5560 59

27 28

SS

V

VDD

RA5/AN4/LVDIN

50 49

31

29 30 32

(1)

/P2A

(1)

RA4/T0CKI

RC0/T1OSO/T13CKI

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

RC6/TX1/CK1

RC7/RX1/DT1

RB0/INT0

RB1/INT1

RB2/INT2

RB3/INT3

RB4/KBI0

RB5/KBI1/PGM

RB6/KBI2/PGC

SS

V

OSC2/CLKO/RA6

OSC1/CLKI

V

DD

RB7/KBI3/PGD

RC5/SDO

RC4/SDI/SDA

RC3/SCK/SCL

RC2/CCP1/P1A

RC1/T1OSI/CCP2

Note 1: CCP2/P2A are multiplexed with RC1 when CCP2MX is set, or RE7 when CCP2MX is not set.

DS39612A-page 2 Advance Information 2003 Microchip Technology Inc.

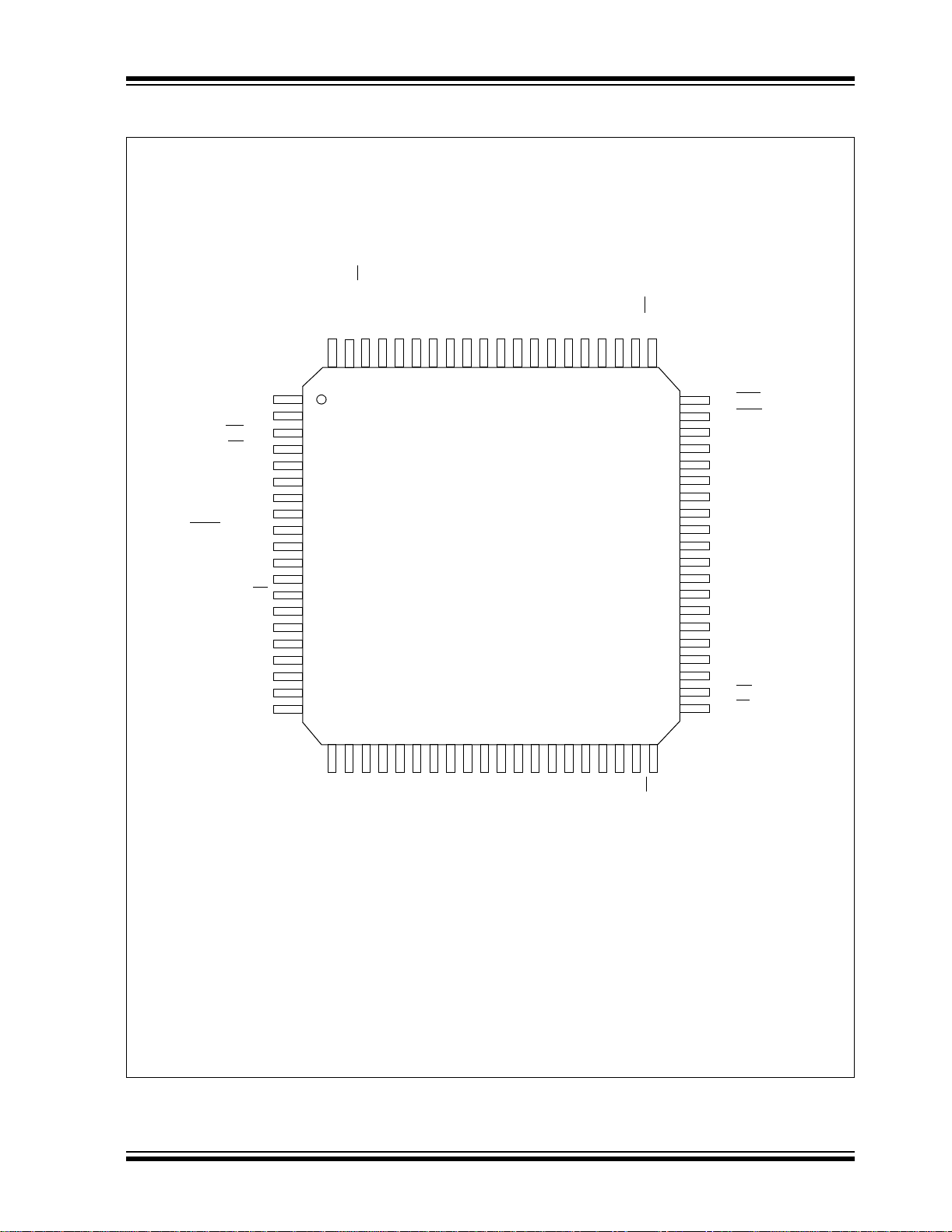

Pin Diagrams (Cont.’d)

80-Pin TQFP

RH2/A18

RH3/A19

RE1/AD9/WR/P2C

RE0/AD8/RD

RG0/CCP3/P3A

RG3/CCP4/P3D

MCLR

RG4/CCP5/P1D

RF5/AN10/CVREF

RF2/AN7/C1OUT

RH7/AN15/P1B

RH6/AN14/P1C

/P2D

RG1/TX2/CK2

RG2/RX2/DT2

/VPP/RG5

V

VDD

RF7/SS

RF6/AN11

RF4/AN9

RF3/AN8

SS

(2)

(2)

(1)

/P2A

(1)

(2)

(2)

RE4/AD12/P3B

(2)

RE5/AD13/P1C

RE6/AD14/P1B

RE7/AD15/CCP2

PIC18F8525

PIC18F8621

RD0/AD0/PSP0

(2)

RE2/AD10/CS/P2B

RE3/AD11/P3C

RH0/A16

RH1/A17

7980

78

77 76 75

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21 22 23 24 25 26 27 28 29 30 31 32

VDDVSS

PIC18F6X2X/8X2X

RD1/AD1/PSP1

RD2/AD2/PSP2

RD3/AD3/PSP3

RD4/AD4/PSP4

RD5/AD5/PSP5

RD6/AD6/PSP6

RD7/AD7/PSP7

RJ0/ALE

RJ1/OE

68 67 66 6572 71 70 6974 73

33 34

35 36

64 63 62 61

37

40

39

38

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

RJ2/WRL

RJ3/WRH

RB0/INT0

RB1/INT1

RB2/INT2

RB3/INT3/CCP2

RB4/KBI0

RB5/KBI1/PGM

RB6/KBI2/PGC

VSS

OSC2/CLKO/RA6

OSC1/CLKI

V

DD

RB7/KBI3/PGD

RC5/SDO

RC4/SDI/SDA

RC3/SCK/SCL

RC2/CCP1/P1A

RJ7/UB

RJ6/LB

(1)

/P2A

(1)

(2)

(2)

RH5/AN13/P3B

RH4/AN12/P3C

RF1/AN6/C2OUT

RF0/AN5

DD

AV

REF-

AVSS

RA2/AN2/V

RA3/AN3/VREF+

RA1/AN1

RA0/AN0

SS

V

(1)

VDD

/P2A

(1)

RA4/T0CKI

RA5/AN4/LVDIN

RC6/TX1/CK1

RC0/T1OSO/T13CKI

RC1/T1OSI/CCP2

RJ5/CE

RJ4/BA0

RC7/RX1/DT1

Note 1: CCP2/P2A are multiplexed with RC1 when CCP2MX is set; with RE7 when CCP2MX is cleared and the device is

configured in Microcontroller mode; or with RB3 when CCP2MX is cleared in all other Program Memory modes.

2: P1B/P1C/P3B /P3C are multiplexed with RE6:RE3 when ECCPMX is set, and with RH7:RH4 when ECCPMX is

not set.

2003 Microchip Technology Inc. Advance Information DS39612A-page 3

PIC18F6X2X/8X2X

Table of Contents

1.0 Device Overview ..........................................................................................................................................................................7

2.0 Oscillator Configurations............................................................................................................................................................ 21

3.0 Reset..........................................................................................................................................................................................31

4.0 Memory Organization.................................................................................................................................................................41

5.0 FLASH Program Memory...................................... ................ ..................................................................................................... 63

6.0 External Memory Interface......................................................................................................................................................... 73

7.0 Data EEPROM Memory................................... ................. ................. ................. ....................................................................... 81

8.0 8 X 8 Hardware Multiplier........................... ................. ................. ................................. .............................................................87

9.0 Interrupts.................................................................................................................................................................................... 89

10.0 I/O Ports................... ................. ...............................................................................................................................................105

11.0 Timer0 Module ......................................................................................................................................................................... 133

12.0 Timer1 Module ......................................................................................................................................................................... 137

13.0 Timer2 Module ......................................................................................................................................................................... 143

14.0 Timer3 Module ......................................................................................................................................................................... 145

15.0 Timer4 Module ......................................................................................................................................................................... 149

16.0 Capture/Compare/PWM (CCP) Modules .................................................................................................................................151

17.0 Enhanced Capture/Compare/PWM (ECCP) Module................................................................................................................159

18.0 Master Synchronous Serial Port (MSSP) Module .................................................................................................................... 175

19.0 Enhanced Universal Synchronous Asynchronous Receiver Transmitter (USART).................................................................. 215

20.0 10-bit Analog-to-Digital Converter (A/D) Module ......................................................................................................................235

21.0 Comparator Module................................................................. ......... .... .. .... ....... .... .... .. .... ......................................................... 243

22.0 Comparator Voltage Reference Module................................................................................................................................... 249

23.0 Low Voltage Detect ..................................................................................................................................................................253

24.0 Special Features of th e CPU.............. ................ ................. ................. .................................................................................... 259

25.0 Instruction Set Summary.......................................................................................................................................................... 277

26.0 Development Support............................................................................................................................................................... 319

27.0 Electrical Characteristics.......................................................................................................................................................... 325

28.0 DC and AC Characteristics Graphs and Tables....................................................................................................................... 359

29.0 Packaging Inform a tio n..... ................. ................ ................. ....................................................................................................... 361

Appendix A: Revision History............................................................................................................................................................. 365

Appendix B: Device Differences......................................................................................................................................................... 365

Appendix C: Conversion Considerations ........................................................... .. ....... .... .. .... .. .... ....................................................... 366

Appendix D: Migration from Mid-Range to Enhanced Devices..........................................................................................................366

Appendix E: Migration from High-End to Enhanced Devices............................................................................................................. 367

Index .................................................................................................................................................................................................. 369

On-Line Support.................................................................... .. .... .... .. ......... .... .. .... ....... .... ...................................................................379

Systems Information and Upgrade Hot Line......................................................................................................................................379

Reader Response.............................................................................................................................................................................. 380

PIC18F6X2X/8X2X Product Identification System............................................................................................................................. 381

DS39612A-page 4 Advance Information 2003 Microchip Technology Inc.

PIC18F6X2X/8X2X

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or c omm ents regarding t his publication, p lease c ontact the M arket ing Co mmunications Department via

E-mail at docerrors@mail.microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150.

We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision

of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

• The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include liter-

ature number) you are using.

Customer Notification System

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

2003 Microchip Technology Inc. Advance Information DS39612A-page 5

PIC18F6X2X/8X2X

NOTES:

DS39612A-page 6 Advance Information 2003 Microchip Technology Inc.

PIC18F6X2X/8X2X

1.0 DEVICE OVERVIEW

This documen t conta i ns dev ic e spec if i c in for m at i on fo r

the following devices:

• PIC18F6525

• PIC18F6621

• PIC18F8525

• PIC18F8621

This family offers the advantages of all

PIC18 microcontrollers - namely, high computational

performance at an economical price - with the

addition of high endurance enhanced FLASH program

memory. The PIC18F6X2X/ 8X2X famil y also provi des

an enhanced range of program memory options and

versatile analog fea tures that mak e it ideal fo r complex,

high performance applications.

1.1 Key Features

1.1.1 EXPANDED MEMORY

The PIC18F6X2X/8X2X family provides ample room

for application code, and includes members with

48 Kbytes or 64 Kbytes of code space.

Other memory features are:

• Data RAM and Data EEPROM: The

PIC18F6X2X/8X2X family also provides plenty of

room for application data. The devices have

3840 bytes of data RAM as well as 1024 bytes of

data EEPROM for lon g term retention of non-volatile

data.

• Memory Endurance: The enhanced FLASH cells

for both program memory and data EEPROM are

rated to last for many thousands of erase/write

cycles - up to 100,000 for program memory, and

1,000,000 for EEPROM. Data retention without

refresh is conservatively estimated to be greater

than 40 years.

1.1.2 EXTERNAL MEMORY INTERFACE

In the unlikely event t hat 64 Kbytes of program memo ry

is inadequate for an application, the PIC18F8X2X

members of the family also implement an external

memory interface. This allows the controller’s internal

program counter to address a memory space of up to

2 MBytes, permitting a level of data access that few

8-bit devices can claim.

With the addition of new operati ng mode s, the ext ernal

memory interface offers many new options, including:

• Operating the microcontr oller entirely f rom external

memory

• Using combinations of on-chip and external

memory, up to the 2-Mbyte limit

• Using external FLASH me mory for reprogrammable

application code or large data tables

• Using external RAM devices for storing large

amounts of variable data

1.1.3 EASY MIGRATION

Regardless of the memory size, all devices share the

same rich set of peripherals, allowing for a smooth

migration path as applications grow and evolve.

The consistent pinout scheme used throughout the

entire family also aids in migrating to the next larger

device. This is true when moving between the 64-pin

members, between the 80-pin members, or even

jumping fr om 64-pin to 80-pin devic es.

1.1.4 OTHER SPECI AL FE A TU RES

• Communications: The PIC18F6X2X/8X2X family

incorporates a range of serial communication

peripherals, including 2 independent enhanced

USARTs and a Master SSP module capable of both

SPI and I2C (Master and Slave) mod es of op era tio n.

Also, for PIC18F6X2X/8X2X devices, one of the

general purpose I/O port s can be recon figured as an

8-bit parallel slave port for direct processor to

processor communi ca tio ns.

• CCP Modules: All devices in the family incorporate

two Capture/Compare/PWM (CCP) modules and

three enhanced CCP modu les to maximize flexibility

in control applications. Up to four different time

bases may be used to perform several different

operations at once. Each of the three ECCPs offer

up to four PWM outputs, allowing for a total of 12

PWMs. The ECCPs also offer many beneficial features, including polarity selection, programmable

dead-time, auto shutdown and restart, and

Half-Bridge and Full-Bridge Output mo des.

• Analog Features: All devices in the family feature

10-bit A/D converters with up to 16 input channels,

as well a s the a bility t o perfor m conver sions du ring

SLEEP mode and auto-acquisition conversions.

Also included are dual analog comparators with

programmable input and output configuration, a

programmable Low Voltage Detect module, and a

2003 Microchip Technology Inc. Advance Information DS39612A-page 7

PIC18F6X2X/8X2X

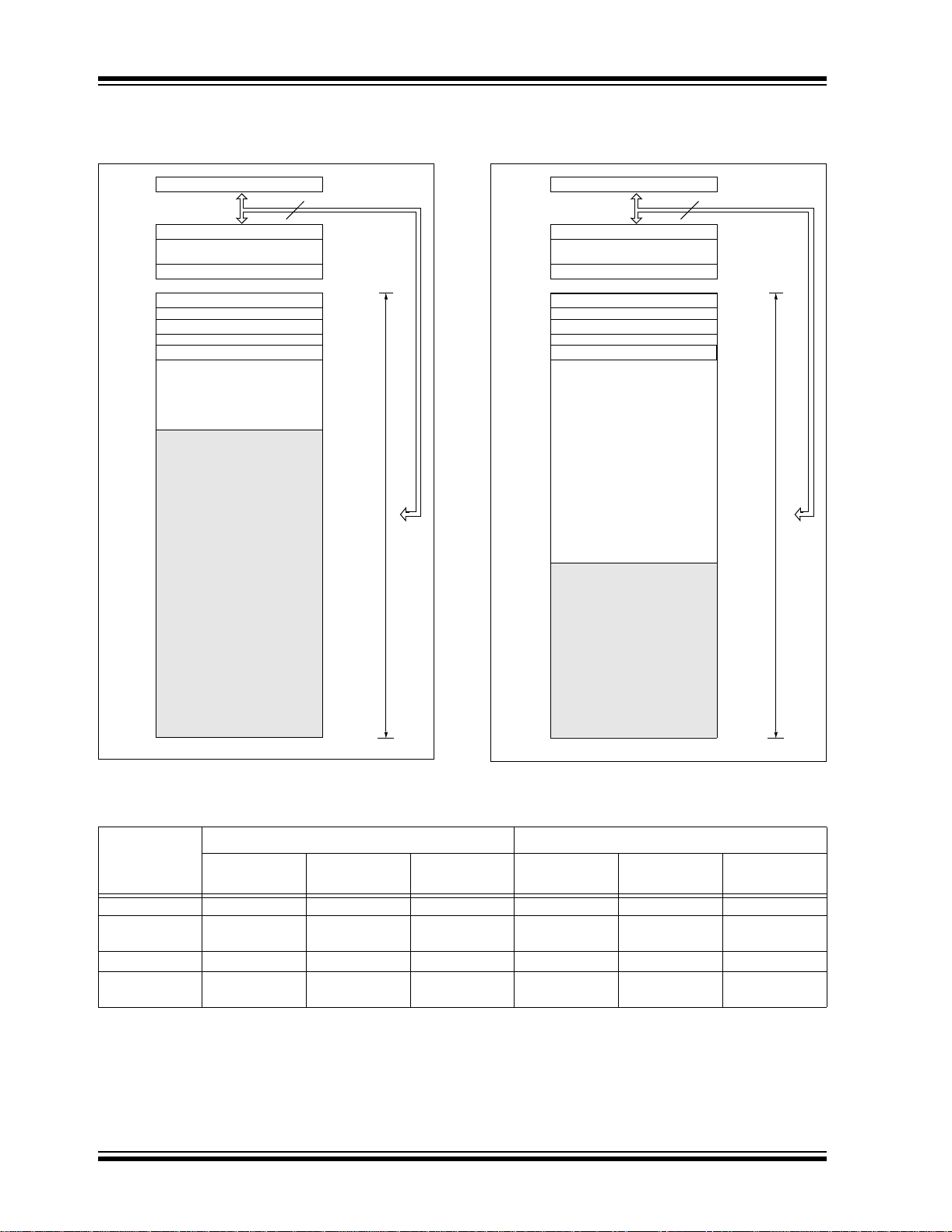

1.2 Details on Individual Family Members

The PIC18F6X2X/8X2X dev ices a re available in 64-pi n

and 80-pin packages. They are differentiated from

each other in four ways:

1. FLASH program memory (48 Kbytes for

PIC18FX525 devices and 64 Kbytes for

PIC18FX621 devices)

2. A/D channels (12 for PIC18F6X2X devices ,

16 for PIC1 8F8X2X)

3. I/O ports (7 on PIC18F6X2X devices, 9 on

PIC18F8X2X)

4. External program memory interface (present

only on PIC18F8X2X devices)

All other features for devic es in the PIC1 8F6X2X/8 X2X

family are identical. These are summarized in

Table 1-1.

Block diagrams of the PIC18F6X2X and PIC18F8X2X

devices are provided in Figure 1-1 and Figure 1-2,

respectively. The pinouts for these device families are

listed in Table 1-2.

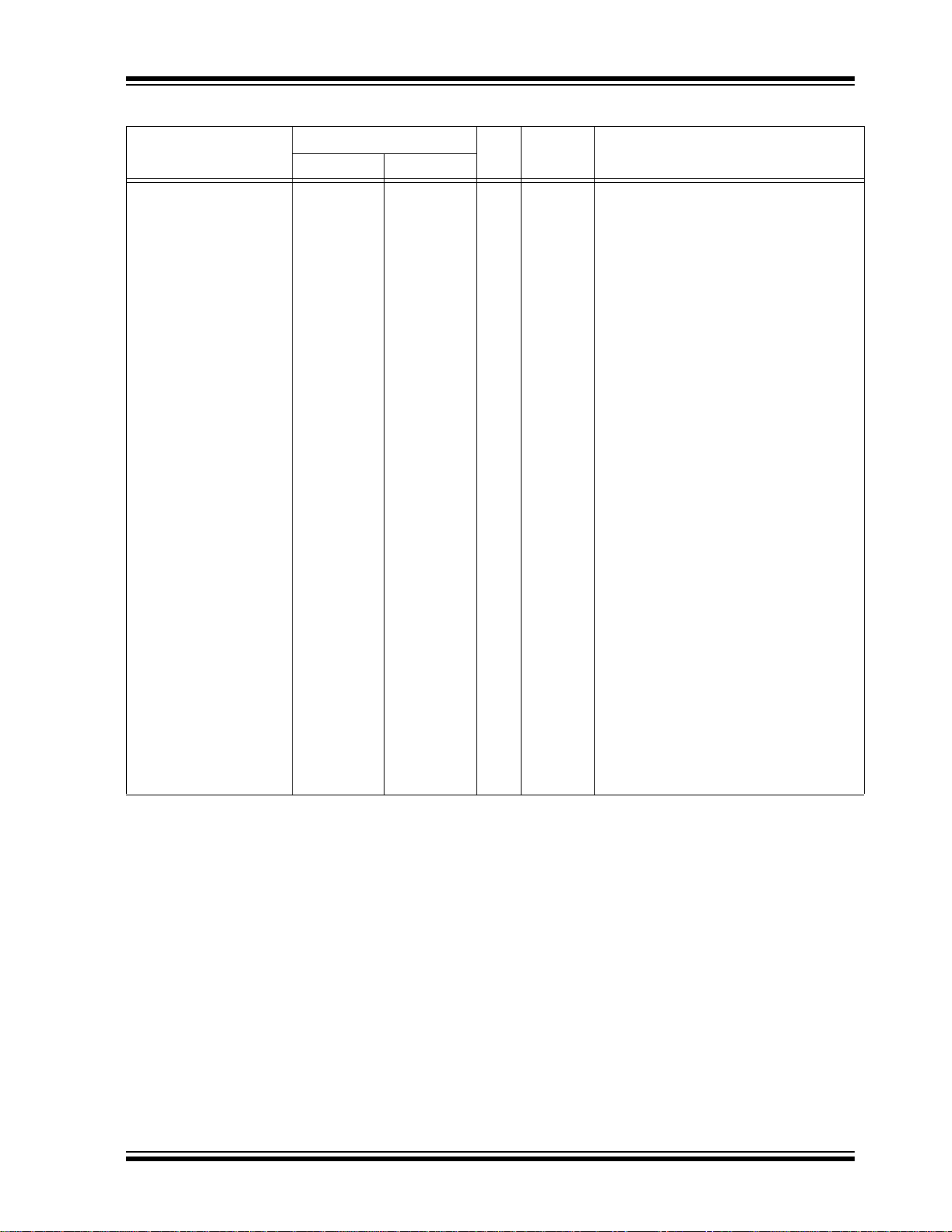

TABLE 1-1: PIC18F6X2X/8X2X DEVICE FEATURES

Features PIC18F6525 PIC18F6621 PIC18F8525 PIC18F8621

Operating Frequency

Program Memory (Bytes) 48K 64K 48K 64 K

Program Memory (Instruction s) 24576 32768 24576 3 276 8

Data Memory (Bytes) 3840 3840 3840 384 0

Data EEPROM Memory (Bytes) 1024 1024 1024 1024

External Memory Interface No No Yes Yes

Interrupt Sources 17 17 17 17

I/O Ports Ports A, B, C, D,

Timers 5 5 5 5

Capture/Compare/PWM Modules 2 2 2 2

Enhanced Capture/Compare/

PWM Module

Serial Communications MSSP,

Parallel Communications PSP PSP PSP PSP

10-bit Analog-to-Digital Module 12 input channels 12 input channels 16 input channels 16 input channels

RESETS (and Delays) POR, BOR,

Programmable Low Voltage

Detect

Programmable Brown-out Reset Yes Yes Y es Yes

Instruction Set 77 Instructions 77 Instructions 77 Instructions 77 Instructions

Package 64-pin TQFP 64-pin TQFP 80-pin TQFP 80-pin TQFP

DC - 40 MHz DC - 40 MHz DC - 40 MHz DC - 40 MHz

Ports A, B, C, D,

E, F, G

3333

Addressable

EUSART (2)

RESET Instruction,

Stack Full,

Stack Underflow

(PWRT, OST)

Yes Yes Yes Yes

E, F, G

MSSP,

Addressable

EUSART (2)

POR, BOR,

RESET Instruction,

Stack Full,

Stack Underflow

(PWRT, OST)

Ports A, B, C, D, E,

F, G, H, J

MSSP,

Addressable

EUSART (2)

POR, BOR,

RESET Instruction,

Stack Full,

Stack Underflow

(PWRT, OST)

Ports A, B, C, D, E,

F, G, H, J

MSSP,

Addressable

EUSART (2)

POR, BOR,

RESET Instruction,

Stack Full,

Stack Underflow

(PWRT, OST)

DS39612A-page 8 Advance Information 2003 Microchip Technology Inc.

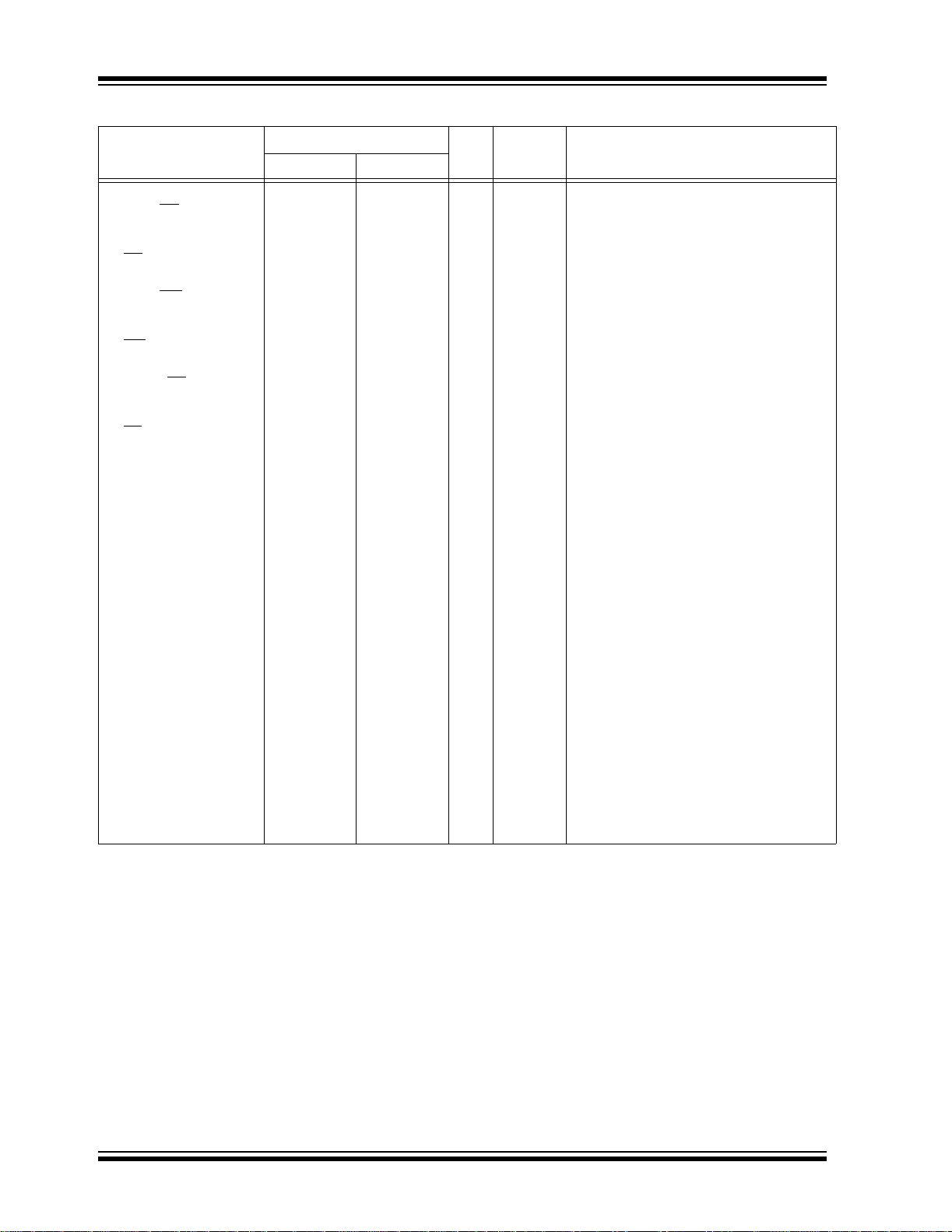

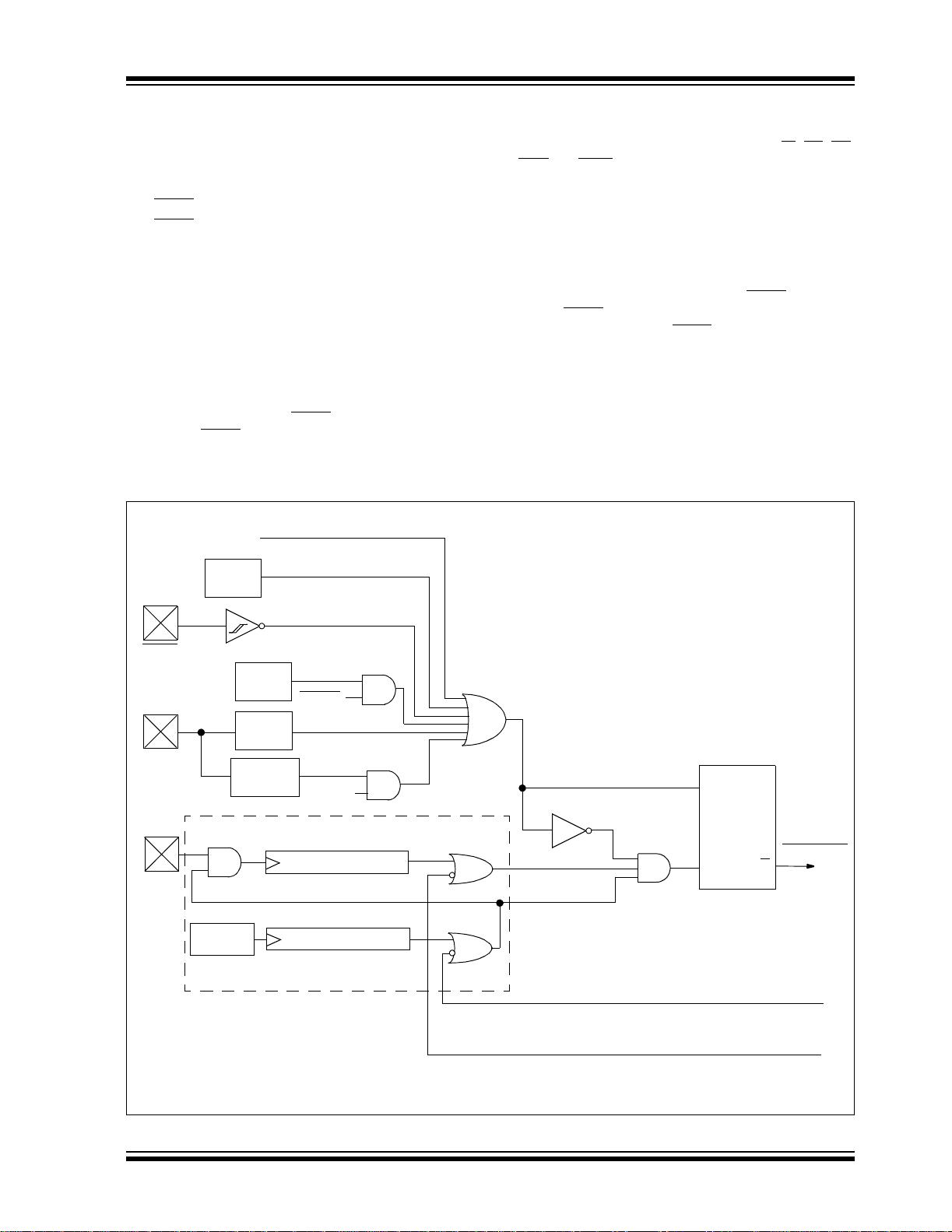

FIGURE 1-1: PIC18F6525/662 1 BLO CK D IA GRA M

PIC18F6X2X/8X2X

2003 Microchip Technology Inc. Advance Information DS39612A-page 9

PIC18F6X2X/8X2X

FIGURE 1-2: PIC18F8525/8621 BLOCK DIAGRAM

Data Bus<8>

PORTA

21

Address Latch

Program Memory

(48/64Kbytes)

Data Latch

OSC2/CLKO

OSC1/CLKI

21

16

Instruction

Decode &

Control

Timing

Generation

Precision

Bandgap

Reference

Table Pointer<21>

inc/dec logic

20

PCLATU

PCU

Program Counter

Table Latch

8

Power-up

Oscillator

Start-up Timer

Power-on

Watchdog

Brown-out

Te st Mod e

8

PCLATH

PCH PCL

31 Level Stack

ROM Latch

IR

Timer

Reset

Timer

Reset

Select

8

4

Decode

BITOP

3

8

Data Latch

Data RAM

(3.8 Kbytes)

Address Latch

12

Address<12>

12 4

FSR0

FSR1

FSR2

inc/dec

logic

8 x 8 Multiply

W

8

8

ALU<8>

8

Bank0, FBSR

PRODLPRODH

RA3/AN3/VREF+

RA4/T0CKI

RA5/AN4 /LVDIN

PORTB

12

8

8

8

PORTC

RB0/INT0

RC0/T1OSO/T13CKI

RC2/CCP1/P1A

RC3/SCK/SCL

RC4/SDI/SDA

RC5/SDO

RC6/TX1/CK1

RC7/RX1/DT1

PORTH

10-bit

LVD

Note 1: CCP2/P2A are multiplexed with RC1 when CCP2MX is set; with RE7 when CCP2MX is cleared and the device is configured in

Microcontroller mode; or with RB3 when CCP2MX is cleared in all other Program Memory modes.

2: P1B/P1C/P3B/P3C are multiplexed with RE6:RE3 when ECCPMX is set, and with RH7:RH4 when ECCPMX is not set.

3: RG5 is multiplexed with MCLR

4: External memory interface pins are multiplexed with PORTD (AD7:AD0), PORTE (AD15:AD8) and PORTH (A19:A16).

Timer2Timer1 Timer3 Timer4Timer0

MSSP

CCP4 CCP5

, and is only available when the MCLR Resets are disabled.

EUSART1Comparator

ADC

EUSART2

PORTJ

RH0:RH3/AD19

RH4/AN12/P3C

RH5/AN13/P3B

RH6/AN14/P1C

RH7/AN15/P1B

RJ0/ALE

RJ1/OE

RJ2/WRL

RJ3/WRH

RJ4/BA0

RJ5/CE

RJ6/LB

RJ7/UB

(4)

(2)

(2)

(2)

(2)

DS39612A-page 10 Advance Information 2003 Microchip Technology Inc.

PIC18F6X2X/8X2X

T ABLE 1-2: PIC18F6X2X/8X2X PINOUT I/O DESCRIPTIONS

Pin Name

Pin Number

PIC18F6X2X PIC18F8X2X

Pin

Type

Buffer

Type

Description

/VPP/RG5

MCLR

MCLR

VPP

RG5

OSC1/CLKI

OSC1

CLKI

OSC2/CLKO/RA6

OSC2

CLKO

RA6

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output

Note 1: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX (CONFIG3H<0>) is not set (all Program

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to V

Memory modes except Microcontroller).

2: Default assignment for CCP2/P2A when CCP2MX is set (all devices).

3: External memory interface functions are only available on PIC18F8X2X devices.

4: Default assignment for P1B/P1C/P3B/P3C for PIC18F8X2X de vices when ECCP MX (CONFIG3H<1>) is set, and for all

PIC18F6X2X devices.

5: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX is not set (Microcontroller mode).

6: PORTH and PORTJ (and their multiplexed functions) are only available on PIC18F8X2X devices.

7: Alternate assignment for P1B/P1C/P3B/P3C for PIC18F8X2X devic es when ECCPM X (CON FIG3H<1>) is not set.

8: AV

DD must be connected to a positive supply and AVSS must be connected to a ground reference for proper operation of

the part in User or ICSP modes. See parameter D001A for details.

79

I

P

I

39 49

IICMOS/ST

40 50

O

O

I/O

ST

—

ST

CMOS

—

—

TTL

Master Clear (input) or programming

voltage (output).

Master Clea r (Res et) inpu t. Thi s pi n is an

active low RESET to the device.

Programming voltage input.

Digital input.

Oscillator crystal or external clock input.

Oscillator crystal input or ex te rn al cl ock

source input. ST buffer when configured

in RC mode; otherwise CMOS.

External clock source input. Always

associated with pin func t io n O SC 1 (see

OSC1/CLKI, OSC2/CLKO pins).

Oscillator crystal or clock out put.

Oscillator crystal output.

Connects to crystal or resonator in

Crystal Oscillator mod e.

In RC mode, OSC2 pin ou tp uts CLKO

which has 1/4 the freque ncy of OSC1

and denotes the instru ct ion cycle rate.

General purpose I/O pin.

DD)

2003 Microchip Technology Inc. Advance Information DS39612A-page 11

PIC18F6X2X/8X2X

TABLE 1-2: PIC18F6X2X/8X2X PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Name

Pin Number

PIC18F6X2X PIC18F8X2X

RA0/AN0

24 30

RA0

AN0

RA1/AN1

23 29

RA1

AN1

RA2/AN2/V

REF-

22 28

RA2

AN2

REF-

V

RA3/AN3/V

REF+

21 27

RA3

AN3

V

REF+

RA4/T0CKI

28 34

RA4

T0CKI

RA5/AN4/LVDIN

27 33

RA5

AN4

LVDIN

RA6 See the OSC2/CLKO/RA6 pin.

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output

Note 1: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX (CONFIG3H<0>) is not set (all Program

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to V

Memory modes except Microcontroller).

2: Default assignment for CCP2/P2A when CCP2MX is set (all devices).

3: External memory interface functions are only available on PIC18F8X2X devices.

4: Default assignment for P1B/P1C/P3B/P3C for PIC18F8X2X devices when ECCPMX (CONFIG3H<1>) is set, and for all

PIC18F6X2X devices.

5: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX is not set (Microc ontroller mode).

6: PORTH and PORTJ (and their multiplexed functions) are only available on PIC18F8X2X devices.

7: Alternate assignment for P1B/P1C/ P3B /P3C for PIC18F8 X2X devic es when ECCPM X (CON FIG3H<1>) is no t set.

8: AV

DD must be connected to a positive supply and AVSS must be connected to a ground reference for proper operation of

the part in User or ICSP modes. See parameter D001A for details.

Pin

Type

I/O

I/O

I/O

I/O

Buffer

Type

TTL

I

Analog

TTL

I

Analog

TTL

I

Analog

I

Analog

TTL

I

Analog

I

Analog

I/OIST/OD

ST

I/O

I

I

TTL

Analog

Analog

Description

PORTA is a bi-directional I/O port.

Digital I/O.

Analog input 0.

Digital I/O.

Analog input 1.

Digital I/O.

Analog input 2.

A/D reference voltage (Low) input.

Digital I/O.

Analog input 3.

A/D reference voltage (High) input.

Digital I/O – Open drain when

configured as output.

Timer0 external clock input.

Digital I/O.

Analog input 4.

Low Voltage Detect input.

DD)

DS39612A-page 12 Advance Information 2003 Microchip Technology Inc.

PIC18F6X2X/8X2X

TABLE 1-2: PIC18F6X2X/8X2X PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Name

Pin Number

PIC18F6X2X PIC18F8X2X

RB0/INT0

48 58

RB0

INT0

RB1/INT1

47 57

RB1

INT1

RB2/INT2

46 56

RB2

INT2

RB3/INT3/CCP2/P2A

45 55

RB3

INT3

(1)

CCP2

(1)

P2A

RB4/KBI0

44 54

RB4

KBI0

RB5/KBI1/PGM

43 53

RB5

KBI1

PGM

RB6/KBI2/PGC

42 52

RB6

KBI2

PGC

RB7/KBI3/PGD

37 47

RB7

KBI3

PGD

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output

Note 1: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX (CONFIG3H<0>) is not set (all Program

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to V

Memory modes except Microcontroller).

2: Default assignment for CCP2/P2A when CCP2MX is set (all devices).

3: External memory interface functions are only available on PIC18F8X2X devices.

4: Default assignment for P1B/P1C/P3B/P3C for PIC18F8X2X de vices when ECCP MX (CONFIG3H<1>) is set, and for all

PIC18F6X2X devices.

5: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX is not set (Microcontroller mode).

6: PORTH and PORTJ (and their multiplexed functions) are only available on PIC18F8X2X devices.

7: Alternate assignment for P1B/P1C/P3B/P3C for PIC18F8X2X devic es when ECCPM X (CON FIG3H<1>) is not set.

8: AV

DD must be connected to a positive supply and AVSS must be connected to a ground reference for proper operation of

the part in User or ICSP modes. See parameter D001A for details.

Pin

Type

I/O

I

I/O

I

I/O

I

I/O

I/O

I/O

O

I/O

I

I/O

I

I/O

I/O

I

I/O

I/O

I

I/O

Buffer

Type

TTL

ST

TTL

ST

TTL

ST

TTL

ST

ST

—

TTL

ST

TTL

ST

ST

TTL

ST

ST

TTL

ST

ST

Description

PORTB is a bi-directional I/O port. PORTB

can be software programmed for internal

weak pull-ups on all inputs.

Digital I/O.

External interrupt 0.

Digital I/O.

External interrupt 1.

Digital I/O.

External interrupt 2.

Digital I/O.

External interrupt 3.

Capture2 input, Compare2 output,

PWM2 output.

Enhanced CCP2 output P2A.

Digital I/O.

Interrupt-on-change pin.

Digital I/O.

Interrupt-on-change pin.

Low voltage ICSP programming

enable pin.

Digital I/O.

Interrupt-on-change pin.

In-Circuit Debugger and

ICSP programming cloc k.

Digital I/O.

Interrupt-on-change pin.

In-Circuit Debugger and

ICSP programming data.

DD)

2003 Microchip Technology Inc. Advance Information DS39612A-page 13

PIC18F6X2X/8X2X

TABLE 1-2: PIC18F6X2X/8X2X PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Name

Pin Number

PIC18F6X2X PIC18F8X2X

RC0/T1OSO/T13CKI

30 36

RC0

T1OSO

T13CKI

RC1/T1OSI/CCP2/P2A

29 35

RC1

T1OSI

(2)

CCP2

(2)

P2A

RC2/CCP1/P1A

33 43

RC2

CCP1

P1A

RC3/SCK/SCL

34 44

RC3

SCK

SCL

RC4/SDI/SDA

35 45

RC4

SDI

SDA

RC5/SDO

36 46

RC5

SDO

RC6/TX1/CK1

31 37

RC6

TX1

CK1

RC7/RX1/DT1

32 38

RC7

RX1

DT1

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to V

Note 1: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX (CONFIG3H<0>) is not set (all Program

Memory modes except Microcontroller).

2: Default assignment for CCP2/P2A when CCP2MX is set (all devices).

3: External memory interface functions are only available on PIC18F8X2X devices.

4: Default assignment for P1B/P1C/P3B/P3C for PIC18F8X2X devices when ECCPMX (CONFIG3H<1>) is set, and for all

PIC18F6X2X devices.

5: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX is not set (Microc ontroller mode).

6: PORTH and PORTJ (and their multiplexed functions) are only available on PIC18F8X2X devices.

7: Alternate assignment for P1B/P1C/ P3B /P3C for PIC18F8 X2X devic es when ECCPM X (CON FIG3H<1>) is no t set.

8: AV

DD must be connected to a positive supply and AVSS must be connected to a ground reference for proper operation of

the part in User or ICSP modes. See parameter D001A for details.

Pin

Type

I/O

O

I

I/O

I

I/O

O

I/O

I/O

O

I/O

I/O

I/O

I/O

I

I/O

I/O

O

I/O

O

I/O

I/O

I

I/O

Buffer

Type

ST

—

ST

ST

CMOS

ST

—

ST

ST

—

ST

ST

ST

ST

ST

ST

ST

—

ST

—

ST

ST

ST

ST

Description

PORTC is a bi-directional I/O port.

Digital I/O.

Timer1 oscillator output.

Timer1/Timer3 external clock input.

Digital I/O.

Timer1 oscillator input.

Capture2 input, Compare2 output,

PWM2 output.

Enhanced CCP2 output P2A.

Digital I/O.

Capture1 input, Compare1 output,

PWM1 output.

Enhanced CCP1 output P1A.

Digital I/O.

Synchronous serial clock input/output for

SPI mode.

Synchronous serial clock input/output for

2

C mode.

I

Digital I/O.

SPI data in.

2

C data I/O.

I

Digital I/O.

SPI data out.

Digital I/O.

USART 1 asynchronous transmit.

USART 1 synchronous clock

(see RX1/DT1).

Digital I/O.

USART 1 asynchronous receive.

USART 1 synchronous data

(see TX1/CK1).

DD)

DS39612A-page 14 Advance Information 2003 Microchip Technology Inc.

PIC18F6X2X/8X2X

TABLE 1-2: PIC18F6X2X/8X2X PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Name

Pin Number

PIC18F6X2X PIC18F8X2X

RD0/AD0/PSP0

RD0

(3)

AD0

58 72

PSP0

RD1/AD1/PSP1

RD1

(3)

AD1

55 69

PSP1

RD2/AD2/PSP2

RD2

(3)

AD2

54 68

PSP2

RD3/AD3/PSP3

RD3

(3)

AD3

53 67

PSP3

RD4/AD4/PSP4

RD4

(3)

AD4

52 66

PSP4

RD5/AD5/PSP5

RD5

(3)

AD5

51 65

PSP5

RD6/AD6/PSP6

RD6

(3)

AD6

50 64

PSP6

RD7/AD7/PSP7

RD7

(3)

AD7

49 63

PSP7

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to V

Note 1: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX (CONFIG3H<0>) is not set (all Program

Memory modes except Microcontroller).

2: Default assignment for CCP2/P2A when CCP2MX is set (all devices).

3: External memory interface functions are only available on PIC18F8X2X devices.

4: Default assignment for P1B/P1C/P3B/P3C for PIC18F8X2X de vices when ECCP MX (CONFIG3H<1>) is set, and for all

PIC18F6X2X devices.

5: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX is not set (Microcontroller mode).

6: PORTH and PORTJ (and their multiplexed functions) are only available on PIC18F8X2X devices.

7: Alternate assignment for P1B/P1C/P3B/P3C for PIC18F8X2X devic es when ECCPM X (CON FIG3H<1>) is not set.

8: AV

DD must be connected to a positive supply and AVSS must be connected to a ground reference for proper operation of

the part in User or ICSP modes. See parameter D001A for details.

Pin

Type

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Buffer

Type

ST

TTL

TTL

ST

TTL

TTL

ST

TTL

TTL

ST

TTL

TTL

ST

TTL

TTL

ST

TTL

TTL

ST

TTL

TTL

ST

TTL

TTL

Description

PORTD is a bi-directional I/O port. These

pins have TTL i nput buffer s wh en external

memory is enabled.

Digital I/O.

External memory addre ss/data 0.

Parallel slave port data.

Digital I/O.

External memory addre ss/data 1.

Parallel slave port data.

Digital I/O.

External memory addre ss/data 2.

Parallel slave port data.

Digital I/O.

External memory addre ss/data 3.

Parallel slave port data.

Digital I/O.

External memory addre ss/data 4.

Parallel slave port data.

Digital I/O.

External memory addre ss/data 5.

Parallel Slave Port data.

Digital I/O.

External memory addre ss/data 6.

Parallel slave port data.

Digital I/O.

External memory addre ss/data 7.

Parallel slave port data.

DD)

2003 Microchip Technology Inc. Advance Information DS39612A-page 15

PIC18F6X2X/8X2X

TABLE 1-2: PIC18F6X2X/8X2X PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Name

Pin Number

PIC18F6X2X PIC18F8X2X

RE0/AD8/RD

RE0

(3)

AD8

/P2D

24

RD

P2D

RE1/AD9/WR/P2C

RE1

(3)

AD9

13

WR

P2C

RE2/AD10/CS

RE2

(3)

AD10

/P2B

64 78

CS

P2B

RE3/AD11/P3C

RE3

(3)

AD11

(4)

P3C

RE4/AD12/P3B

RE4

(3)

AD12

(4)

P3B

RE5/AD13/P1C

RE5

(3)

AD13

(4)

P1C

RE6/AD14/P1B

RE6

(3)

AD14

(4)

P1B

RE7/AD15/CCP2/P2A

RE7

(3)

AD15

(5)

CCP2

(5)

P2A

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output

Note 1: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX (CONFIG3H<0>) is not set (all Program

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to V

Memory modes except Microcontroller).

2: Default assignment for CCP2/P2A when CCP2MX is set (all devices).

3: External memory interface functions are only available on PIC18F8X2X devices.

4: Default assignment for P1B/P1C/P3B/P3C for PIC18F8X2X devices when ECCPMX (CONFIG3H<1>) is set, and for all

PIC18F6X2X devices.

5: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX is not set (Microc ontroller mode).

6: PORTH and PORTJ (and their multiplexed functions) are only available on PIC18F8X2X devices.

7: Alternate assignment for P1B/P1C/ P3B /P3C for PIC18F8 X2X devic es when ECCPM X (CON FIG3H<1>) is no t set.

8: AV

DD must be connected to a positive supply and AVSS must be connected to a ground reference for proper operation of

the part in User or ICSP modes. See parameter D001A for details.

63 77

62 76

61 75

60 74

59 73

Pin

Type

I/O

I/O

I

O

I/O

I/O

I

O

I/O

I/O

I

O

I/O

I/O

O

I/O

I/O

O

I/O

I/O

O

I/O

I/O

O

I/O

I/O

I/O

O

Buffer

Type

ST

TTL

TTL

—

ST

TTL

TTL

ST

ST

TTL

TTL

—

ST

TTL

—

ST

TTL

—

ST

TTL

—

ST

TTL

—

ST

TTL

ST

—

Description

PORTE is a bi-directional I/O port.

Digital I/O.

External memory addre ss/data 8.

Read control for paralle l slave port.

Enhanced CCP2 output P2D.

Digital I/O.

External memory addre ss/data 9.

Write control for parallel slave port.

Enhanced CCP2 output P2C.

Digital I/O.

External memory addre ss/data 10.

Chip select control for parallel slave port.

Enhanced CCP2 output P2B.

Digital I/O.

External memory address/data 11.

Enhanced CCP3 output P3C.

Digital I/O.

External memory addre ss/data 12.

Enhanced CCP3 output P3B.

Digital I/O.

External memory addre ss/data 13.

Enhanced CCP1 output P1C.

Digital I/O.

External memory addre ss/data 14.

Enhanced CCP1 output P1B.

Digital I/O.

External memory addre ss/data 15.

Capture2 input, Compare2 output,

PWM2 output.

Enhanced CCP2 output P2A.

DD)

DS39612A-page 16 Advance Information 2003 Microchip Technology Inc.

PIC18F6X2X/8X2X

TABLE 1-2: PIC18F6X2X/8X2X PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Name

RF0/AN5

RF0

AN5

RF1/AN6/C2OUT

RF1

AN6

C2OUT

RF2/AN7/C1OUT

RF2

AN7

C1OUT

RF3/AN8

RF1

AN8

RF4/AN9

RF1

AN9

RF5/AN10/CV

RF1

AN10

CVREF

RF6/AN11

RF6

AN11

RF7/SS

RF7

SS

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output

Note 1: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX (CONFIG3H<0>) is not set (all Program

REF

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to V

Memory modes except Microcontroller).

2: Default assignment for CCP2/P2A when CCP2MX is set (all devices).

3: External memory interface functions are only available on PIC18F8X2X devices.

4: Default assignment for P1B/P1C/P3B/P3C for PIC18F8X2X de vices when ECCP MX (CONFIG3H<1>) is set, and for all

PIC18F6X2X devices.

5: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX is not set (Microcontroller mode).

6: PORTH and PORTJ (and their multiplexed functions) are only available on PIC18F8X2X devices.

7: Alternate assignment for P1B/P1C/P3B/P3C for PIC18F8X2X devic es when ECCPM X (CON FIG3H<1>) is not set.

8: AV

DD must be connected to a positive supply and AVSS must be connected to a ground reference for proper operation of

the part in User or ICSP modes. See parameter D001A for details.

PIC18F6X2X PIC18F8X2X

Pin Number

18 24

17 23

16 18

15 17

14 16

13 15

12 14

11 13

Pin

Type

I/O

I

I/O

I

O

I/O

I

O

I/O

I

I/O

I

I/O

I

O

I/O

I

I/O

I

Buffer

Type

ST

Analog

ST

Analog

ST

ST

Analog

ST

ST

Analog

ST

Analog

ST

Analog

Analog

ST

Analog

ST

TTL

Description

PORTF is a bi-directional I/O port.

Digital I/O.

Analog input 5.

Digital I/O.

Analog input 6.

Comparator 2 output.

Digital I/O.

Analog input 7.

Comparator 1 output.

Digital I/O.

Analog input 8.

Digital I/O.

Analog input 9.

Digital I/O.

Analog input 10.

Comparator V

Digital I/O.

Analog input 11.

Digital I/O.

SPI slave select input.

REF output.

DD)

2003 Microchip Technology Inc. Advance Information DS39612A-page 17

PIC18F6X2X/8X2X

TABLE 1-2: PIC18F6X2X/8X2X PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Name

RG0/CCP3/P3A

RG0

CCP3

P3A

RG1/TX2/CK2

RG1

TX2

CK2

RG2/RX2/DT2

RG2

RX2

DT2

RG3/CCP4/P3D

RG3

CCP4

P3D

RG4/CCP5/P1D

RG4

CCP5

P1D

RG5 7 9 — — See MCLR

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to V

Note 1: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX (CONFIG3H<0>) is not set (all Program

Memory modes except Microcontroller).

2: Default assignment for CCP2/P2A when CCP2MX is set (all devices).

3: External memory interface functions are only available on PIC18F8X2X devices.

4: Default assignment for P1B/P1C/P3B/P3C for PIC18F8X2X devices when ECCPMX (CONFIG3H<1>) is set, and for all

PIC18F6X2X devices.

5: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX is not set (Microc ontroller mode).

6: PORTH and PORTJ (and their multiplexed functions) are only available on PIC18F8X2X devices.

7: Alternate assignment for P1B/P1C/ P3B /P3C for PIC18F8 X2X devic es when ECCPM X (CON FIG3H<1>) is no t set.

8: AV

DD must be connected to a positive supply and AVSS must be connected to a ground reference for proper operation of

the part in User or ICSP modes. See parameter D001A for details.

PIC18F6X2X PIC18F8X2X

Pin Number

35

46

57

68

810

Pin

Type

I/O

I/O

O

I/O

O

I/O

I/O

I

I/O

I/O

I/O

O

I/O

I/O

O

Buffer

Type

ST

ST

—

ST

—

ST

ST

ST

ST

ST

ST

—

ST

ST

—

Description

PORTG is a bi-directional I/O port.

Digital I/O.

Capture3 input, Compare3 output,

PWM3 output.

Enhanced CCP3 output P3A.

Digital I/O.

USART 2 asynchronous transmit.

USART 2 synchronous clock

(see RX2/DT2).

Digital I/O.

USART 2 asynchronous receive.

USART 2 synchronous data

(see TX2/CK2).

Digital I/O.

Capture4 input, Compare4 output,

PWM4 output.

Enhanced CCP3 output P3D.

Digital I/O.

Capture5 input, Compare5 output,

PWM5 output.

Enhanced CCP1 output P1D.

/VPP/RG5 pin.

DD)

DS39612A-page 18 Advance Information 2003 Microchip Technology Inc.

PIC18F6X2X/8X2X

TABLE 1-2: PIC18F6X2X/8X2X PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Name

RH0/A16

RH0

A16

RH1/A17

RH1

A17

RH2/A18

RH2

A18

RH3/A19

RH3

A19

RH4/AN12/P3C

RH4

AN12

(7)

P3C

RH5/AN13/P3B

RH5

AN13

(7)

P3B

RH6/AN14/P1C

RH6

AN14

(7)

P1C

RH7/AN15/P1B

RH7

AN15

(7)

P1B

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

PIC18F6X2X PIC18F8X2X

Pin Number

—79

—80

—1

—2

—22

—21

—20

—19

Pin

Type

I/O

O

I/O

O

I/O

O

I/O

O

I/O

I

O

I/O

I

O

I/O

I

O

I/O

I

O

Buffer

Type

ST

TTL

ST

TTL

ST

TTL

ST

TTL

ST

Analog

—

ST

Analog

—

ST

Analog

—

ST

Analog

—

Description

PORTH is a bi-directional I/O port

Digital I/O.

External memory address 16.

Digital I/O.

External memory address 17.

Digital I/O.

External memory address 18.

Digital I/O.

External memory address 19.

Digital I/O.

Analog input 12.

Enhanced CCP3 output P3C.

Digital I/O.

Analog input 13.

Enhanced CCP3 output P3B.

Digital I/O.

Analog input 14.

Enhanced CCP1 output P1C.

Digital I/O.

Analog input 15.

Enhanced CCP1 output P1B.

(6)

.

2003 Microchip Technology Inc. Advance Information DS39612A-page 19

PIC18F6X2X/8X2X

TABLE 1-2: PIC18F6X2X/8X2X PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Name

Pin Number

PIC18F6X2X PIC18F8X2X

RJ0/ALE

—62

RJ0

ALE

RJ1/OE

—61

RJ1

OE

RJ2/WRL

—60

RJ2

WRL

RJ3/WRH

—59

RJ3

WRH

RJ4/BA0

—39

RJ4

BA0

RJ5/CE

—40

RJ5

CE

RJ6/LB

—41

RJ6

LB

RJ7/UB

—42

RJ7

UB

SS 9, 25,

V

41, 56

V

DD 10, 26,

38, 57

(8)

AV

SS

(8)

AVDD

Legend: TTL = TTL compatible input CMOS = CMOS compatible input or output

Note 1: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX (CONFIG3H<0>) is not set (all Program

ST = Schmitt Trigger input with CMOS levels Analog = Analog input

I = Input O = Output

P = Power OD = Open Drain (no P diode to V

Memory modes except Microcontroller).

2: Default assignment for CCP2/P2A when CCP2MX is set (all devices).

3: External memory interface functions are only available on PIC18F8X2X devices.

4: Default assignment for P1B/P1C/P3B/P3C for PIC18F8X2X devices when ECCPMX (CONFIG3H<1>) is set, and for all

PIC18F6X2X devices.

5: Alternate assignment for CCP2/P2A in PIC18F8X2X devices when CCP2MX is not set (Microc ontroller mode).

6: PORTH and PORTJ (and their multiplexed functions) are only available on PIC18F8X2X devices.

7: Alternate assignment for P1B/P1C/ P3B /P3C for PIC18F8 X2X devic es when ECCPM X (CON FIG3H<1>) is no t set.

8: AV

DD must be connected to a positive supply and AVSS must be connected to a ground reference for proper operation of

the part in User or ICSP modes. See parameter D001A for details.

20 26 P — Ground reference for analog modul es.

19 25 P — Positive supply for analog modules.

11, 31,

51, 70

12, 32,

48, 71

Pin

Type

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Buffer

Type

PORTJ is a bi-directional I/O port

ST

O

TTL

ST

O

TTL

ST

O

TTL

ST

O

TTL

ST

O

TTL

ST

O

TTL

ST

O

TTL

ST

O

TTL

Digital I/O.

External memory address latch enable.

Digital I/O.

External memory output enable.

Digital I/O.

External memory write low control.

Digital I/O.

External memory write high control.

Digital I/O.

System bus byte addres s 0 control.

Digital I/O

External memory access indicator.

Digital I/O.

External memory low byte select.

Digital I/O.

External memory high byte select.

Description

(6)

P — Ground reference for logic and I/O pins.

P — Po sit iv e supply for logic and I/O pins.

DD)

.

DS39612A-page 20 Advance Information 2003 Microchip Technology Inc.

PIC18F6X2X/8X2X

2.0 OSCILLATOR CONFIGURATIONS

2.1 Oscillator Types

The PIC18F6X2X/8X2X devices can be operated in

twelve different Oscillator modes. The user can program four configuration bits (FOSC3, FOSC2, FOSC1,

OSC0) to select one of these eight modes:

and F

1. LP Low Power Crystal

2. XT Crystal/Resonator

3. HS High Speed Crystal/Resonator

4. RC Ex tern al R esi st or/C apacitor

5. EC External Clock

6. ECIO External Clock with I/O pin

enabled

7. HS+PLL High Speed Crystal/Resonator

with PLL enabled

8. RCIO External Resist or/C apacitor with

I/O pin enabled

9. ECIO+SPLL External Clock with software

controlled PLL

10. ECIO+PLL External Clock with PLL and I/O

pin enabled

11. HS+SPLL High Speed Crystal/Resonator

with software control

12. RC IO E x tern al Resi stor/Capacitor with

I/O pin enabled

2.2 Crystal Oscillator/Ceramic Resonators

In XT , LP, HS, HS+PLL or HS+SPLL Oscillator modes, a

crystal or ceramic resonator is connected to the OSC1

and OSC2 pins to establish oscil lation. Figure 2-1 shows

the pin connections.

The PIC18F6X2X/8X2X oscillator design requires the

use of a parallel cut crysta l.

Note: Use of a series cut crystal may give a fre-

quency out of the crystal manufacturers

specifications.

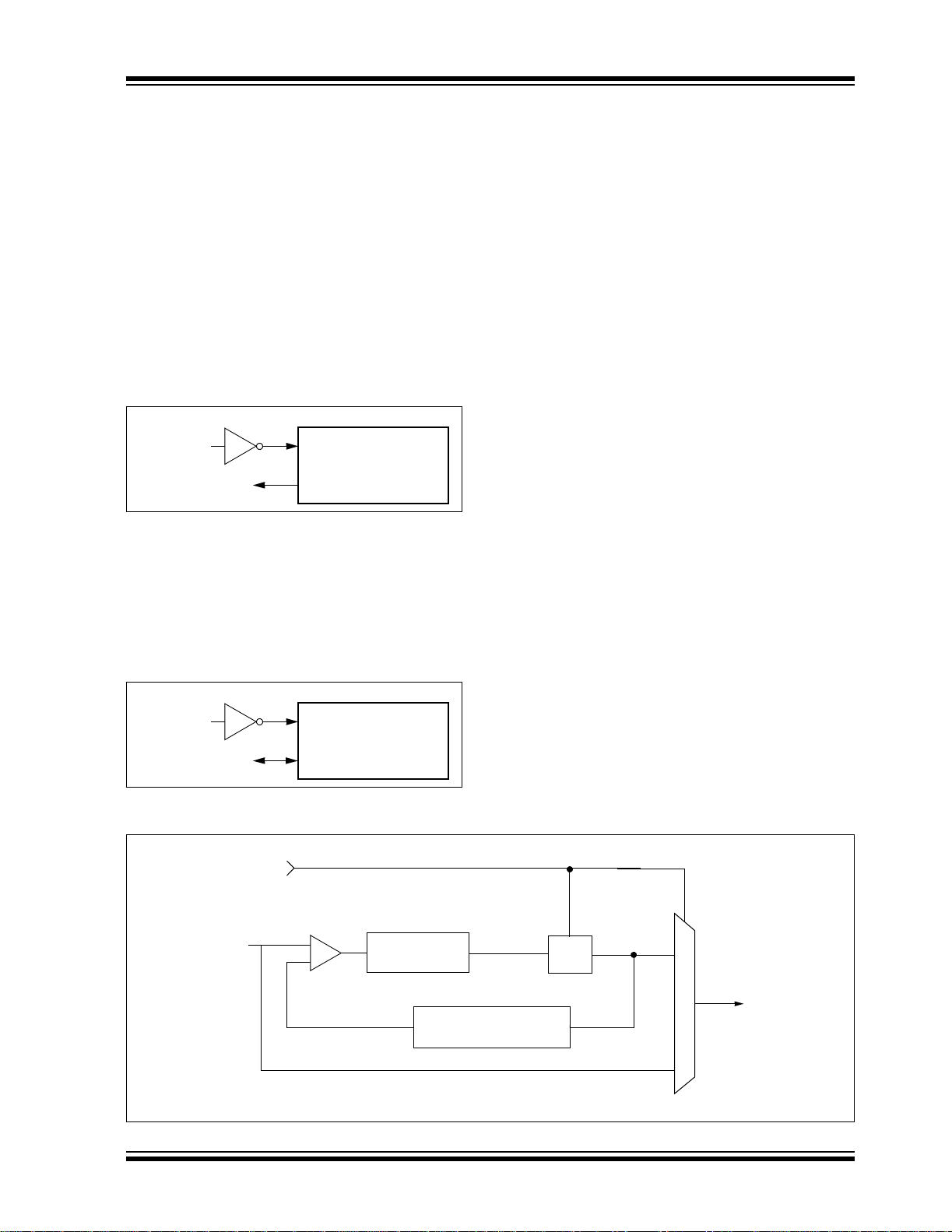

FIGURE 2-1: CRYSTAL/CERAMIC

RESONATOR OPERATION

(HS, XT OR LP

CONFIGURATION)

(1)

C1

(1)

C2

Note 1: See Table 2-1 and Table 2-2 for

2: A series resistor (R

3: R

OSC1

To

Internal

XTAL

(2)

RS

OSC2

recommended values of C1 and C2.

AT strip cut crystals.

F varies with the Oscillator mode chosen.

(3)

RF

PIC18F6X2X/8X2X

S) may be required for

Logic

SLEEP

T ABLE 2-1: CAPACITOR SELECTION FOR

CERAMIC RESONATORS

Ranges Tested:

Mode Freq C1 C2

XT 455 kHz

2.0 MHz

4.0 MHz

HS 8.0 MHz

16.0 MHz

These values are for design guid ance only.

See notes following this table.

Resonators Used:

2.0 MHz Murata Erie CSA2.00MG ± 0.5%

4.0 MHz Murata Erie CSA4.00MG ± 0.5%

8.0 MHz Murata Erie CSA8.00MT ± 0.5%

16.0 MHz Murata Erie CSA16.00MX ± 0.5%

All resonators used did not have bui lt-in capacitors.

Note 1: Higher capacita nce increa ses the st ability

of the oscillator but also increases the

start-up time.

2: When operating below 3V V

using certain ceramic resonators at any

voltage, it may be necessary to use high

gain HS mode, try a lower frequency

resonator, or switch to a crystal oscillator.

3: Since each resonator/crystal has its own

characteristics, the user should consul t the

resonator/crystal manufacturer for appropriate values of external components, or

verify oscillator performance.

68 - 100 pF

15 - 68 pF

15 - 68 pF

10 - 68 pF

10 - 22 pF

68 - 100 pF

15 - 68 pF

15 - 68 pF

10 - 68 pF

10 - 22 pF

DD, or when

2003 Microchip Technology Inc. Advance Information DS39612A-page 21

PIC18F6X2X/8X2X

TABLE 2-2: CAPACITOR SELECTION FOR

CRYSTAL OSCILLATOR

Ranges Tested:

Mode Freq C1 C2

LP 32.0 kHz 33 pF 33 pF

200 kHz 15 pF 15 pF

XT 200 kHz 47-68 pF 47-68 pF

1.0 MHz 15 pF 15 pF

4.0 MHz 15 pF 15 pF

HS 4.0 MHz 15 pF 15 pF

8.0 MHz 15-33 pF 15-33 pF

20.0 MHz 15-33 pF 15-33 pF

25.0 MHz TBD TBD

These values are for de sign guid ance only.

See notes following this table.

Crystals Used

32.0 kHz Epson C-001R32.768K-A ± 20 PPM

200 kHz STD XTL 200.000KHz ± 20 PPM

1.0 MHz ECS ECS-10-13-1 ± 50 PPM

4.0 MHz ECS ECS-40-20-1 ± 50 PPM

8.0 MHz Epson CA-301 8.000M-C ± 30 PPM

20.0 MHz Epson CA-301 20.000M-C ± 30 PPM

Note 1: Higher capacitanc e increase s the stabi lity

of the oscillator but also increases the

start-up time.

2: Rs (see Figure 2-1) may be required in

HS mode, as we ll as XT mode , to avoid

overdriving crystals with low drive level

specification.

3: Since each resonator/crystal has its own

characteristics, the user should consult the

resonator/crystal manufacturer for appropriate values of external components, or

verify oscillator performance.

An external clock sourc e may also be conne cted to th e

OSC1 pin in the HS, XT and LP modes as shown in

Figure 2-2.

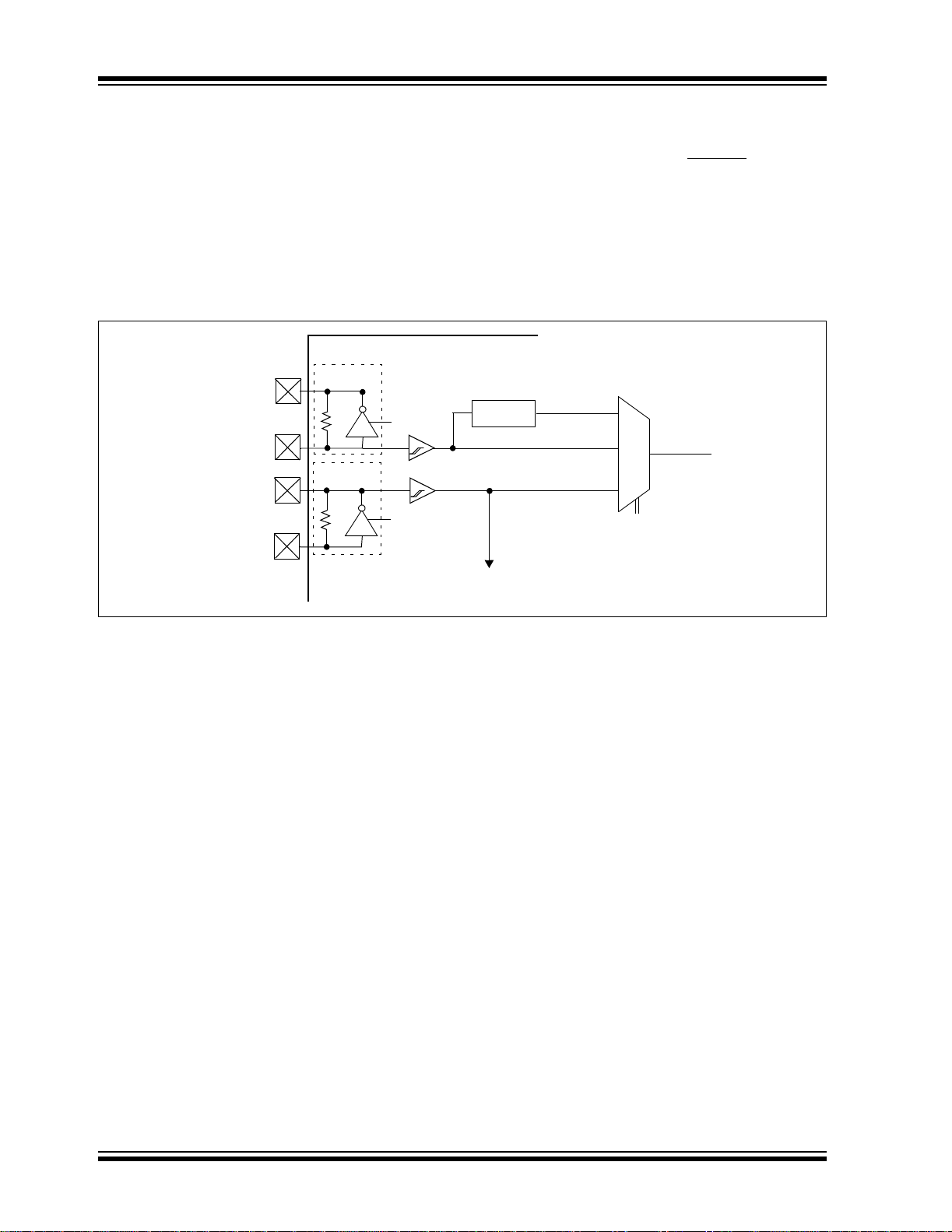

FIGURE 2-2: EXTERNAL CLOCK INPUT

OPERATION (HS, XT OR LP

OSC CONFIGURATION)

Clock from

Ext. System

Open

OSC1

PIC18F6X2X/8X2X

OSC2

2.3 RC Oscillator

For timing insensitive applications, the “RC” and

“RCIO” device options offer additional cost savings.

The RC oscillator frequency is a function of the supply

voltage, the resistor (R

ues and the operating temperature. In addition to this,

the oscillator frequency will vary from uni t to unit due to

normal process parameter variation. Furthermore, the

difference in le ad fram e c apacitance betwee n package

types will also affect the oscillation frequency, especially for low C

EXT values. The user also needs to take

into account variation due to tolerance of external R

and C components used. Figure 2-3 shows how the

R/C combination is connected.

In the RC Oscillator mode, the oscillator frequency

divided by 4 is available on the OSC2 pin. This signal

may be used f or t e st pu r pos es or t o sy nc hr o n iz e ot he r

logic.

FIGURE 2-3: RC OSCILLATOR MODE

VDD

REXT

CEXT

VSS

F

Recommended values: 3 kΩ ≤ REXT ≤ 100 kΩ

The RCIO Oscillator mode functions like the RC mode

except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of

PORTA (RA6).

EXT) and capacitor (CEXT) val-

OSC1

PIC18F6X2X/8X2X

OSC2/CLKO

OSC/4

C

EXT > 20pF

Internal

Clock

DS39612A-page 22 Advance Information 2003 Microchip Technology Inc.

PIC18F6X2X/8X2X

2.4 External Clock Input

The EC, ECIO, EC+PLL and EC+SPLL Oscillator

modes require an external clock source to be connected to the OSC 1 pin. T he feed back device b etwee n

OSC1 and OSC2 is turned off in these modes to save

current. There is a maximum 1.5 µs start-up r equired

after a Power-on Reset or Wak e-up from SLEEP mode.

In the EC Oscillator mode, the oscillator frequency

divided by 4 is available on the OSC2 pin. This signal

may be used f or t e st pu r pos es or t o sy nc hr o n iz e ot he r

logic. Figure 2-4 shows the pin connections for the EC

Oscillator mode.

FIGURE 2-4: EXTERNAL CLOCK INPUT

OPERATION

(EC CONFIGURATION)

Clock from

Ext. System

F

OSC/4

The ECIO Oscillator mode functions like the EC mode

except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of

PORTA (RA6). Figure 2-5 shows the pin connections

for the ECIO Oscillator mode.

FIGURE 2-5: EXTERNAL CLOCK INPUT

Clock from

Ext. System

RA6

OSC1

PIC18F6X2X/8X2X

OSC2

OPERATION

(ECIO CONFIG URATION)

OSC1

PIC18F6X2X/8X2X

I/O (OSC2)

2.5 Phase Locked Loop (PLL)

A phase locked loop circuit is provided as a

programmable option for us ers that want to multip ly the

frequency of the in com in g osc il lat or s ig nal by 4 . For an

input clock frequency of 10 MHz, the internal clock

frequency will b e multipli ed to 40 MHz. This is usefu l for

customers who are concerned with EMI due to high

frequency crystals.

The PLL can only be enabled when the oscillator configuration bits are pro grammed fo r High Spee d Oscill ator or External Clock mode. If they are programmed for

any other mode, the PLL is no t enabled and the s ystem

clock will come directly from OSC1. There are two

types of PLL modes - Software Controlled PLL and

Configuration bits Controlled PLL. In Software Controlled PLL mode, PIC18 F6X2X/8X2X executes at regular clock frequency after all RESET conditi ons. During

execution, the application can enable PLL and switch

to 4x clock frequency operation by setting the PLLEN

bit in the OSCCON register. In Configuration bits Controlled PLL, the PLL operation cann ot be chan ged “onthe-fly”. To enable or disable it, the controller must

either cycle through a Power-on Re set, or switch the

clock source from the main oscillator to the Timer1

oscillator and bac k again ( see Section2.6 for details on

oscillator switching).

The type of PLL is selected by programming

OSC<3:0> configuration bit s in CO NFIG1 H Conf igur a-

F

tion register. The Oscillator mode is specified during

device programming.

A PLL lock timer is used to ensure that the PLL has

locked before device execution starts. The PLL lock

timer has a time-out that is called T

PLL.

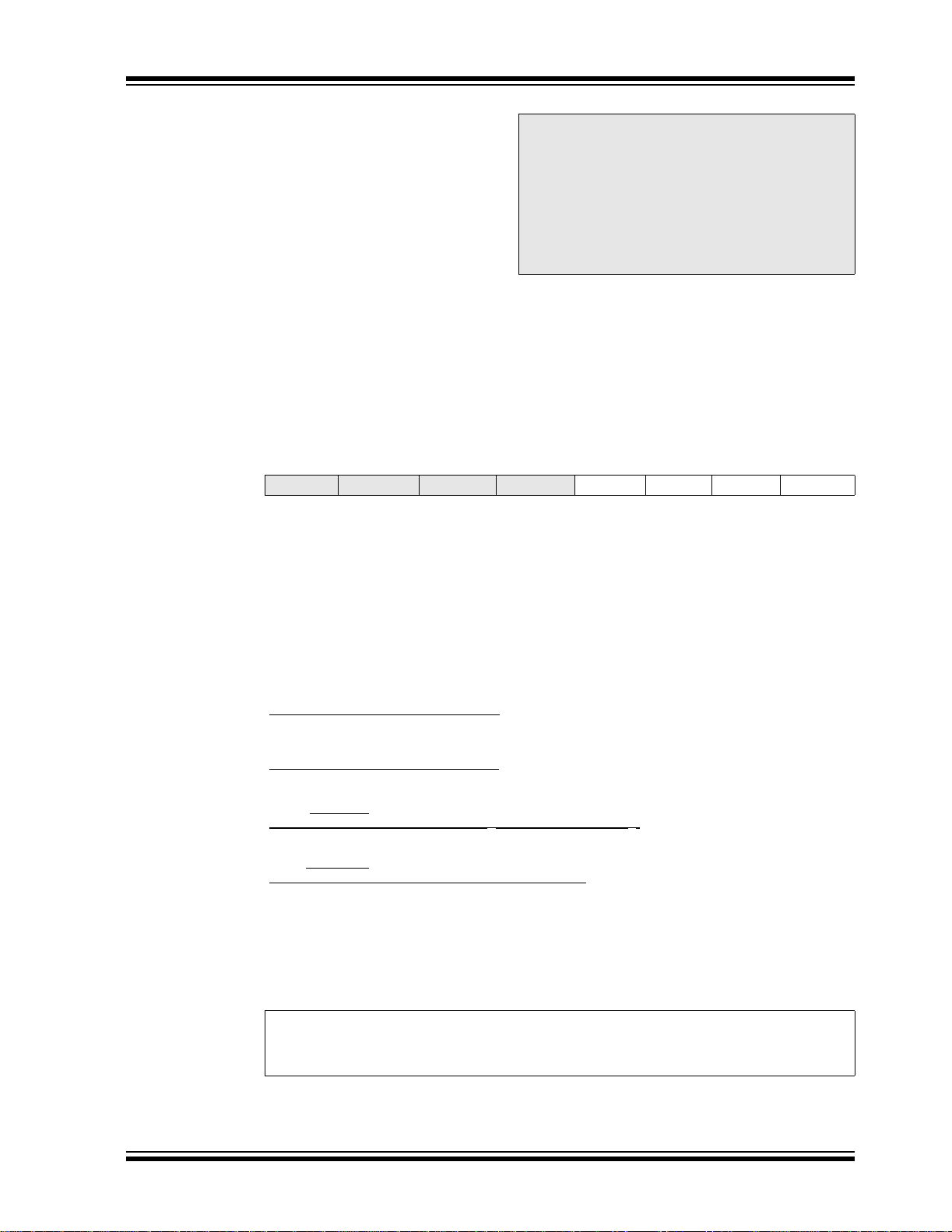

FIGURE 2-6: PLL BLOCK DIAGRAM

PLL Enable

Phase

Comparator

F

IN

FOUT

2003 Microchip Technology Inc. Advance Information DS39612A-page 23

Loop

Filter

Divide by 4

VCO

SYSCLK

MUX

PIC18F6X2X/8X2X

2.6 Oscillator Switching Feature

The PIC18F6X2X/8X2X devices include a feature that

allows the system c lock sour ce to be swit ched from the

main oscillator to an alternate low frequency clock

source. For the PIC18F6X2X/8X2X devices, this

alternate c lock source is th e Timer1 osci llat or. If a low

frequency crystal (32 kHz, for example) has been

attached to the Timer1 oscillator pins and the Timer1

oscillator has been ena bled, the devi ce can swit ch to a

FIGURE 2-7: DEVICE CLOCK SOURCES

PIC18F6X2X/8X2X

OSC2

OSC1

T1OSO

T1OSI

Main Oscillator

SLEEP

Timer1 Oscillator

T1OSCEN

Enable

Oscillator

Low Power Execution mode. Fig ure2-7 shows a block

diagram of the system clock sources. The clock

switching feature is enabled by programming the

Oscillator Switching Enable (OSCSEN

) bit in the

CONFIG1H Configuration register to a ‘0’. Clock

switching is disabled in an erased device. See

Section 12.0 for further details of the Timer1 oscillator.

See Section 24.0 for Configuration register details.

4 x PLL

TOSC

TT1P

TOSC/4

MUX

Clock

Source

TSCLK

Clock Source Option

for Other Modules

DS39612A-page 24 Advance Information 2003 Microchip Technology Inc.

PIC18F6X2X/8X2X

2.6.1 SYSTEM CLOCK SWITCH BIT

The system clock sourc e sw it ching is performed under

software control. The system clock switch bits,

SCS1:SCS0 (OSCCON<1:0>), control the clock

switching. When the SCS0 bit is ‘0’, the system clock

source comes from the main oscillator that is selected

by the F

ration register. When the SCS0 bit is set, the system

clock sourc e will c ome fro m the Timer1 oscill ator. The

SCS0 bit is cleared on all forms of RESET.

When F

mode, SCS1 bit can be u sed to s elect bet ween primar y

oscillator/clock and P LL ou tput . SCS1 b it w ill o nly hav e

an effect on the system clock if the PLL is enabled

(PLLEN = 1) and locked (LOCK = 1), else it will be

forced cleared. When programmed with Configuration

Controlled PLL, SCS1 bit will be forced clear.

OSC configuration bits in CONFIG1H Configu-

OSC bits are programmed for Software PLL

REGISTER 2-1: OSCCON REGISTER

U-0 U-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0

— — — — LOCK PLLEN SCS1 SCS0

bit 7 bit 0

bit 7-4 Unimplemented: Read as ‘0’

bit 3 LOCK: Phase Lock Loop Lock Status bit

1 = Phase lock loop output is stable as system clock

0 = Phase lock loop output is not stable and output cannot be used as system clock

bit 2 PLLEN

bit 1 SCS1: System Clock Switch bit 1

bit 0 SCS0

(1)

: Phase Lock Loop Enable bit

1 = Enable phase lock loop output as system clock

0 = Disable phase lock loop

When PLLEN and LOCK bits are set:

1 = Use PLL output

0 = Use primary oscillator/clock input pin

When PLLEN or LOCK bit is cleared:

Bit is forced clear.

(2)

: System Clock Switch bit 0

When OSCSEN configuration bit = 0 and T1OSCEN bit = 1:

1 = Switch to Timer1 oscillator/clock pin

0 = Use primary oscillator/clock input pin

OSCSEN and T1OSCEN are in other states:

When

Bit is forced clear.

Note: The Timer1 oscillator must be enabled

and operating to switch the system clock

source. The Timer1 oscillator is enabled

by setting the T1OSCEN bit in the Timer1

Control register (T1CON). If the Timer1

oscillator is not enabled, then any write to

the SCS0 bit will be ignored (SCS0 bit

forced cleared) and the main osci llator w ill

continue to be the system clock source.

Note 1: PLLEN bit is forced set when configured for ECIO+PLL and HS+PLL. This bit is

writable for ECIO+SPLL and HS+SPLL modes only; forced cleared for all other

Oscillator modes.

2: The setting of SCS0 = 1 supersedes SCS1 = 1.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

2003 Microchip Technology Inc. Advance Information DS39612A-page 25

PIC18F6X2X/8X2X

2.6.2 OSCILLATOR TRANSITIONS

PIC18F6X2X/8X2X devices con tai n circuit ry to prevent

“glitches” when switching between oscillator sources.

Essentially, the circuitry waits for eight rising edges of

the clock source that the processor is swit ching to. This

ensures that the n ew c lo ck s ourc e is s t able and that its

pulse width will not be less than the shortest pulse

width of the two clock sources.

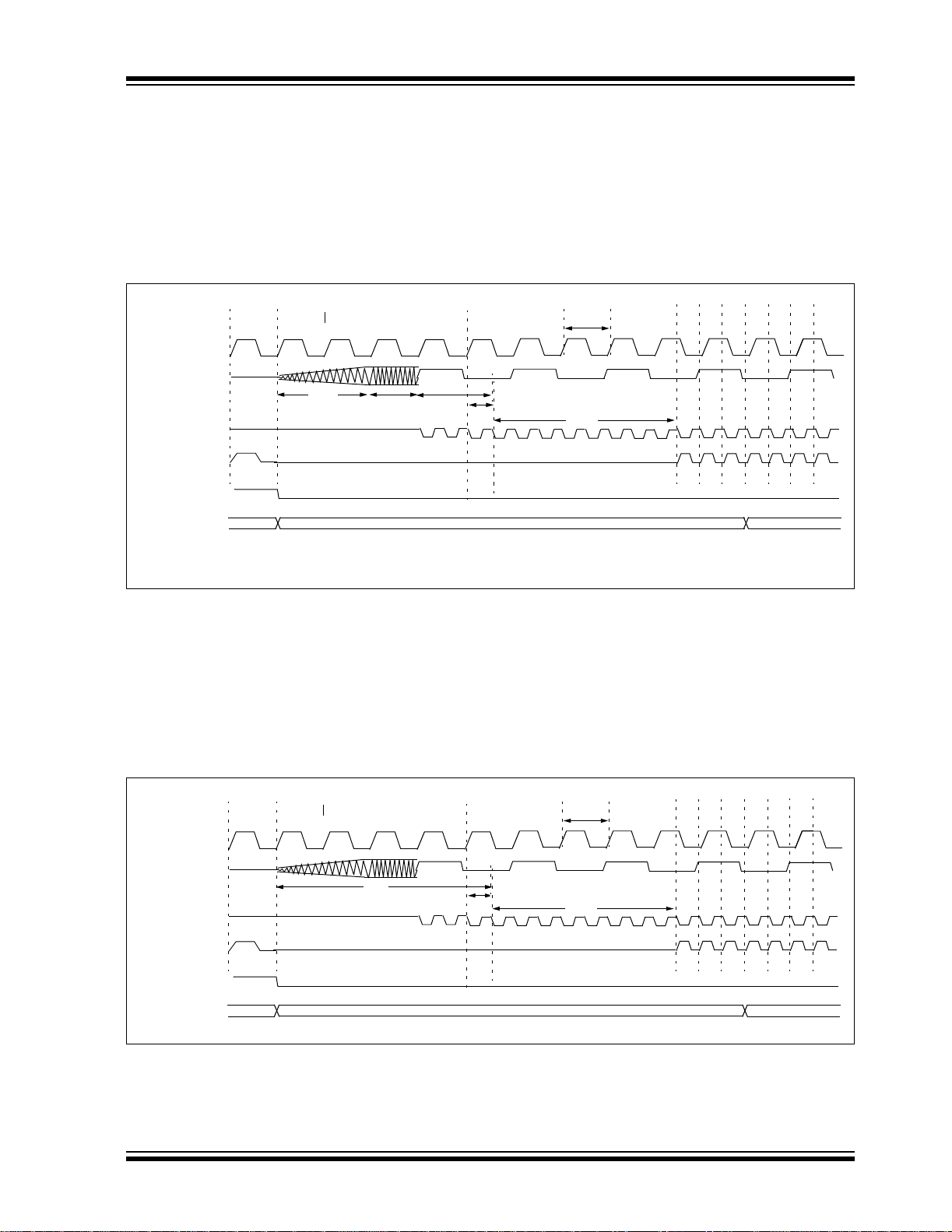

A timing diagram indicating the transition from the main

oscillator to the Timer1 oscillator is s hown in Figure2-8.

The Timer1 oscillator is assumed to be running all the

time. After the SCS0 bit is set, the processor i s frozen at

the next occurring Q1 cycle. After eight synchronization

cycles are counted from the Timer1 oscillator, operation

resumes. No additional delays are required after the

synchronization cycles.

FIGURE 2-8: TIMING DIAGRAM FOR TRANSITION FROM OSC1 TO TIMER1 OSCILLATOR

Q4 Q1

Q1

T1OSI

OSC1

Internal

System

Clock

SCS

(OSCCON<0>)

Program

Counter

Note: T

Q1

TOSC

TDLY

DLY is delay from SCS high to first count of transition circuit.

TT1P

21345678

TSCS

PC + 2PC

Q3Q2Q1Q4Q3Q2

Q2 Q3 Q4 Q1

PC + 4

The sequence of events that takes place when switching from the Timer1 oscillator to the main oscillator will

depend on the mode of the main oscillator. In addition

to eight clock cycles of the main oscillator, additional

delays may take place.

If the main oscillator is configured for an external crystal (HS, XT, LP), then the transition will t ak e pl ac e aft er

an oscillator st art-up time (T

OST) has occurred. A timing

diagram, indicating the transit ion from th e T imer1 os cillator to the main oscillator for HS, XT and LP modes, is

shown in Figure 2-9.

FIGURE 2-9: TIMING FOR TRANSITION BETWEEN TIMER1 AND OSC1 (HS, XT, LP)

Q1 Q2 Q3 Q4 Q1 Q2

T1OSI

OSC1

Internal

System Clock

Program

Counter

Note 1: T

SCS