PIC18F45J10 系列

数据手册

采用纳瓦技术的 28/40/44 引脚

高性能 RISC 单片机

2005 Microchip Technology Inc. 高级信息 DS39682A_CN

请注意以下有关 Microchip 器件代码保护功能的要点:

•Microchip的产品均达到 Microchip 数据手册中所述的技术指标。

•Microchip确信:在正常使用的情况下, Microchip 系列产品是当今市场上同类产品中最安全的产品之一。

• 目前,仍存在着恶意、甚至是非法破坏代码保护功能的行为。就我们所知,所有这些行为都不是以 Microchip 数据手册中规定的

操作规范来使用 Microchip 产品的。这样做的人极可能侵犯了知识产权。

•Microchip愿与那些注重代码完整性的客户合作。

•Microchip或任何其他半导体厂商均无法保证其代码的安全性。代码保护并不意味着我们保证产品是 “牢不可破”的。

代码保护功能处于持续发展中。 Microchip 承诺将不断改进产品的代码保护功能。任何试图破坏 Microchip 代码保护功能的行为均可视

为违反了 《数字器件千年版权法案 (Digital Millennium Copyright Act)》。如果这种行为导致他人在未经授权的情况下,能访问您的

软件或其他受版权保护的成果,您有权依据该法案提起诉讼,从而制止这种行为。

提供本文档的中文版本仅为了便于理解。Microchip

Technology Inc. 及其分公司和相关公司、各级主管与员工及

事务代理机构对译文中可能存在的任何差错不承担任何责任。

建议参考 Microchip Technology Inc. 的英文原版文档。

本出版物中所述的器件应用信息及其他类似内容仅为您提供便

利,它们可能由更新之信息所替代。确保应用符合技术规范,

是您自身应负的责任。Microchip 对这些信息不作任何明示或

暗示、书面或口头、法定或其他形式的声明或担保,包括但不

限于针对其使用情况、质量、性能、适销性或特定用途的适用

性的声明或担保。 Microchip 对因这些信息及使用这些信息而

引起的后果不承担任何责任。未经 Microchip 书面批准,不得

将 Microchip 的产品用作生命维持系统中的关键组件。在

Microchip 知识产权保护下,不得暗中或以其他方式转让任何

许可证。

商标

Microchip 的名称和徽标组合、 Microchip 徽标、 Accuron、

dsPIC、 K

EELOQ、 microID、 MPLAB、 PIC、 PICmicro、

PICSTART、 PRO MATE、 PowerSmart、 rfPIC 和

SmartShunt 均为 Microchip Technology Inc. 在美国和其他国

家或地区的注册商标。

AmpLab、 FilterLab、 Migratable Memory、 MXDEV、

MXLAB、 PICMASTER、 SEEVAL、 SmartSensor 和 The

Embedded Control Solutions Company 均为 Microchip

Technology Inc. 在美国的注册商标。

Analog-for-the-Digital Age、 Application Maestro、

dsPICDEM、 dsPICDEM.net、 dsPICworks、 ECAN、

ECONOMONITOR、 FanSense、 FlexROM、 fuzzyLAB、

In-Circuit Serial Programming、 ICSP、 ICEPIC、 Linear

Active Thermistor、 MPASM、 MPLIB、 MPLINK、 MPSIM、

PICkit、 PICDEM、 PICDEM.net、 PICLAB、 PICtail、

PowerCal、 PowerInfo、 PowerMate、 PowerTool、 Real

ICE、 rfLAB、 rfPICDEM、 Select Mode、 Smart Serial、

SmartTel、 Total Endurance、 UNI/O、 WiperLock 和 Zena

均为 Microchip Technology Inc. 在美国和其他国家或地区的

商标。

SQTP 是 Microchip Technology Inc. 在美国的服务标记。

在此提及的所有其他商标均为各持有公司所有。

© 2005, Microchip Technology Inc. 版权所有。

Microchip

州

10

位单片机、

性存储器和模拟产品方面的质量体系流程均符合

16949:2002

系也已通过了

位于美国亚利桑那州

Mountain View

月通过了

ISO/TS-16949:2002

KEELOQ

。此外,

ISO 9001:2000

的全球总部、设计中心和晶圆生产厂均于

®

跳码器件、串行

Microchip

Chandler和Tem pe

质量体系认证。公司在

EEPROM

在开发系统的设计和生产方面的质量体

认证。

及位于加利福尼亚

PICmicro

、单片机外设、非易失

ISO/TS-

2003

年

®

DS39682A_CN 第 ii 页 高级信息 2005 Microchip Technology Inc.

8

PIC18F45J10 系列

采用纳瓦技术的 28/40/44 引脚

高性能 RISC 单片机

单片机的特殊性能:

• 工作电压范围:2.0V 至 3.6V

• 可接受 5.5V 输入 (仅数字引脚)

• 片上 2.5V 稳压器

• 低功耗的高速 CMOS 闪存技术

• 优化的 C 编译器架构:

- 为优化重入代码而设计的可选的扩展指令集

• 中断优先级

• 8 x 8 单周期硬件乘法器

• 扩展的看门狗定时器 (Watchdog Timer, WDT):

- 可编程周期从 4ms到 131s

• 通过两个引脚进行单电源供电的在线串行编程

(In-Circuit Serial Programming™, ICSP™)

• 通过两个引脚采用三个断点进行在线调试 (In-

Circuit Debug, ICD)

• 功耗管理模式:

- 运行:CPU 打开,外设打开

- 空闲:CPU 关闭,外设打开

- 休眠:CPU 关闭,外设关闭

灵活的振荡器结构:

• 两种晶振模式,频率最高为 40 MHz

• 两种外部时钟模式,频率最高为 40MHz

• 内部 31 kHz 振荡器

• 辅助振荡器使用 Timer1 (工作频率为 32kHz)

• 双速振荡器起振

• 故障保护时钟监视器:

- 当外设时钟停止时可使器件安全关闭

外设特点:

• 高灌 / 拉电流 25 mA/25 mA (PORTB 和 PORTC)

• 3 个可编程外部中断

• 4 个输入电平变化中断

• 一个捕捉 / 比较 /PWM (CCP)模块

• 一个增强型捕捉 / 比较 /PWM (ECCP)模块:

-1路、 2 路或 4 路 PWM 输出

- 可选择的极性

- 可编程的死区时间

- 自动关闭和自动重启

• 2 个主控同步串行端口 (Master Synchronous

Serial Port, MSSP)模块,支持 3 线 SPI (共 4

种模式)和 I

• 一个增强型可寻址 USART 模块:

- 支持 RS-485、 RS-232 和 LIN 1.2

- 起始位自动唤醒

- 自动波特率检测

• 10 位最多 13 路通道的数 / 模转换器模块 (A/D):

- 自动采集功能

- 可在休眠模式下进行转换

- 自动校准功能

• 输入复用的双模拟比较器

2

C™ 主 / 从模式

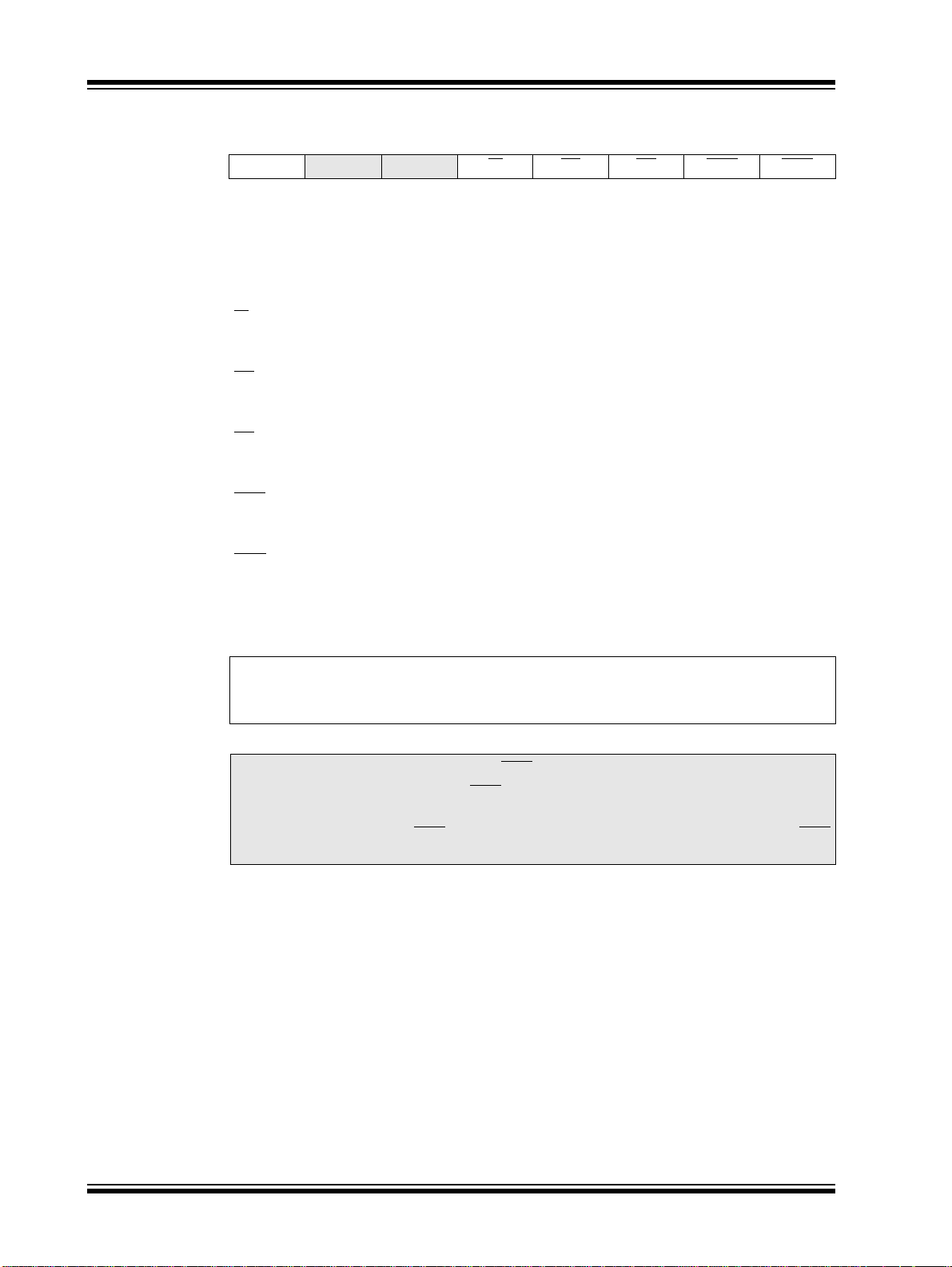

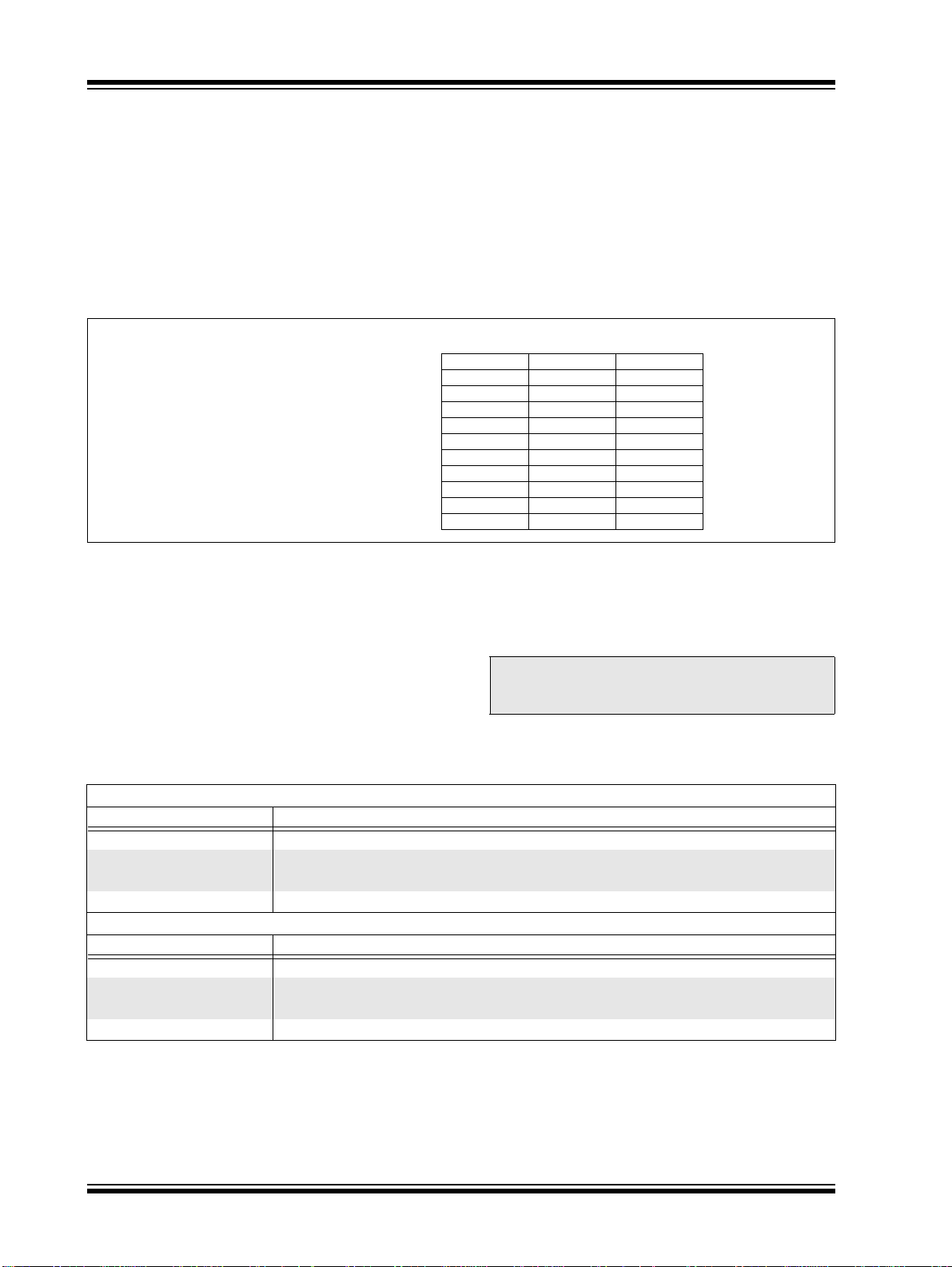

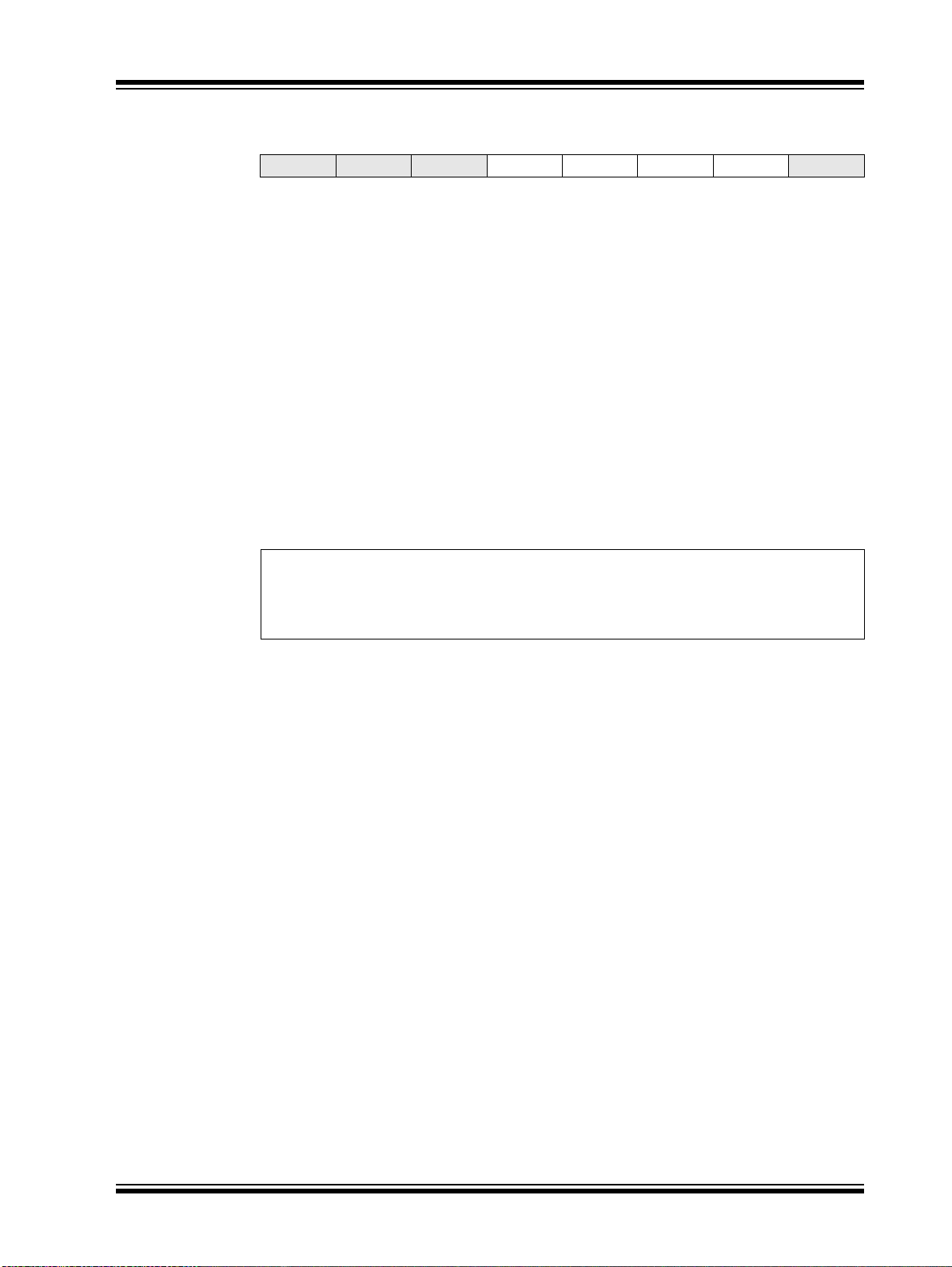

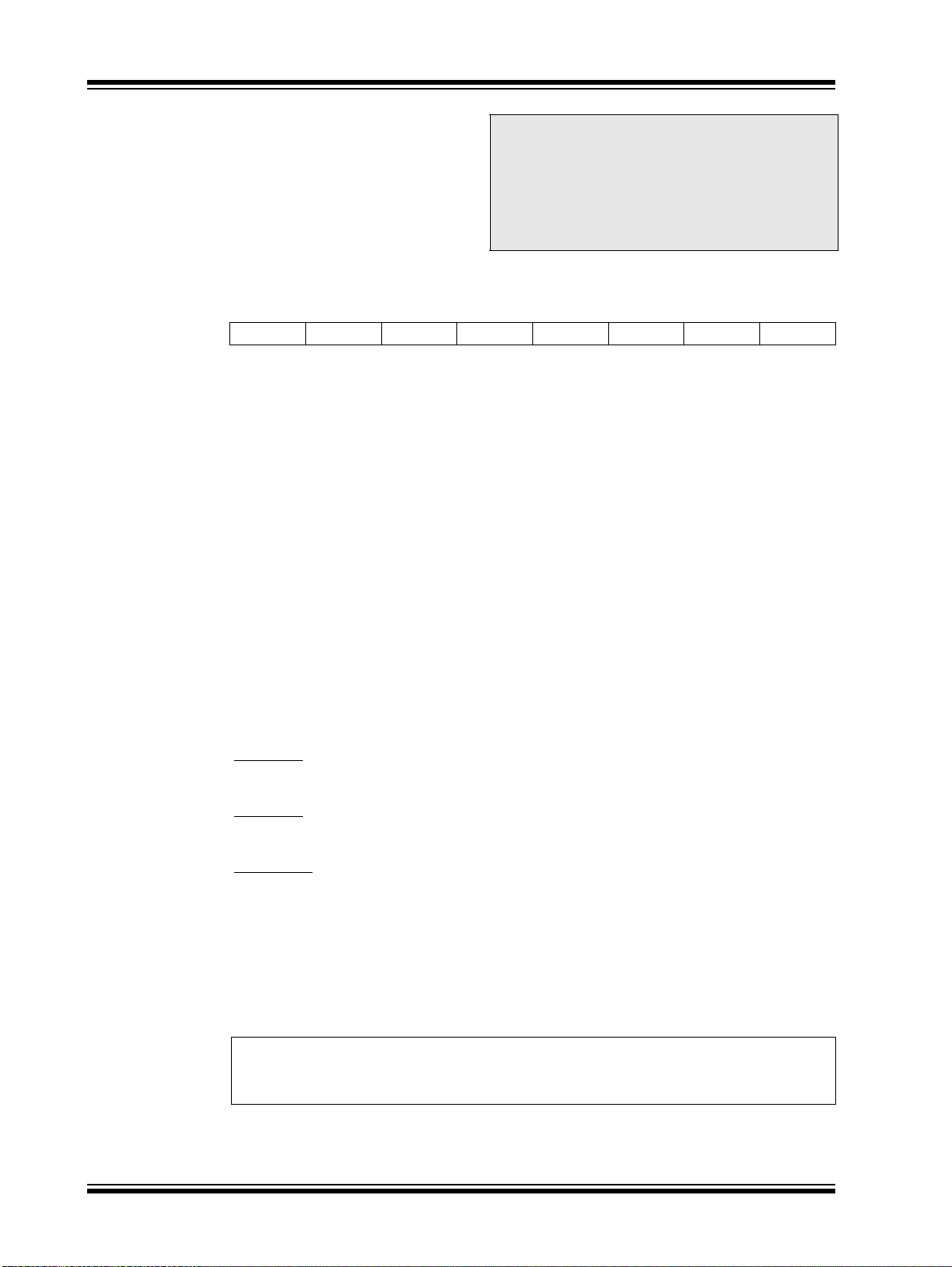

程序存储器

器件

PIC18F24J10 16K 8192 1024 21 10 2/0 1

PIC18F25J10 32K 16384 1024 21 10 2/0 1

PIC18F44J10 16K 8192 1024 32 13 1/1 2

PIC18F45J10 32K 16384 1024 32 13 1/1 2

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 1 页

闪存

(字节)单字指令数

SRAM 数据

存储器

(字节)

I/O

10 位

A/D

(通道数)

CCP/

ECCP

(PWM)

MSSP

主控

SPI

2

C™

I

有有

有有

有有

有有

比较器

EUSART

121/2

121/2

121/2

121/2

8/16 位

定时器

PIC18F45J10 系列

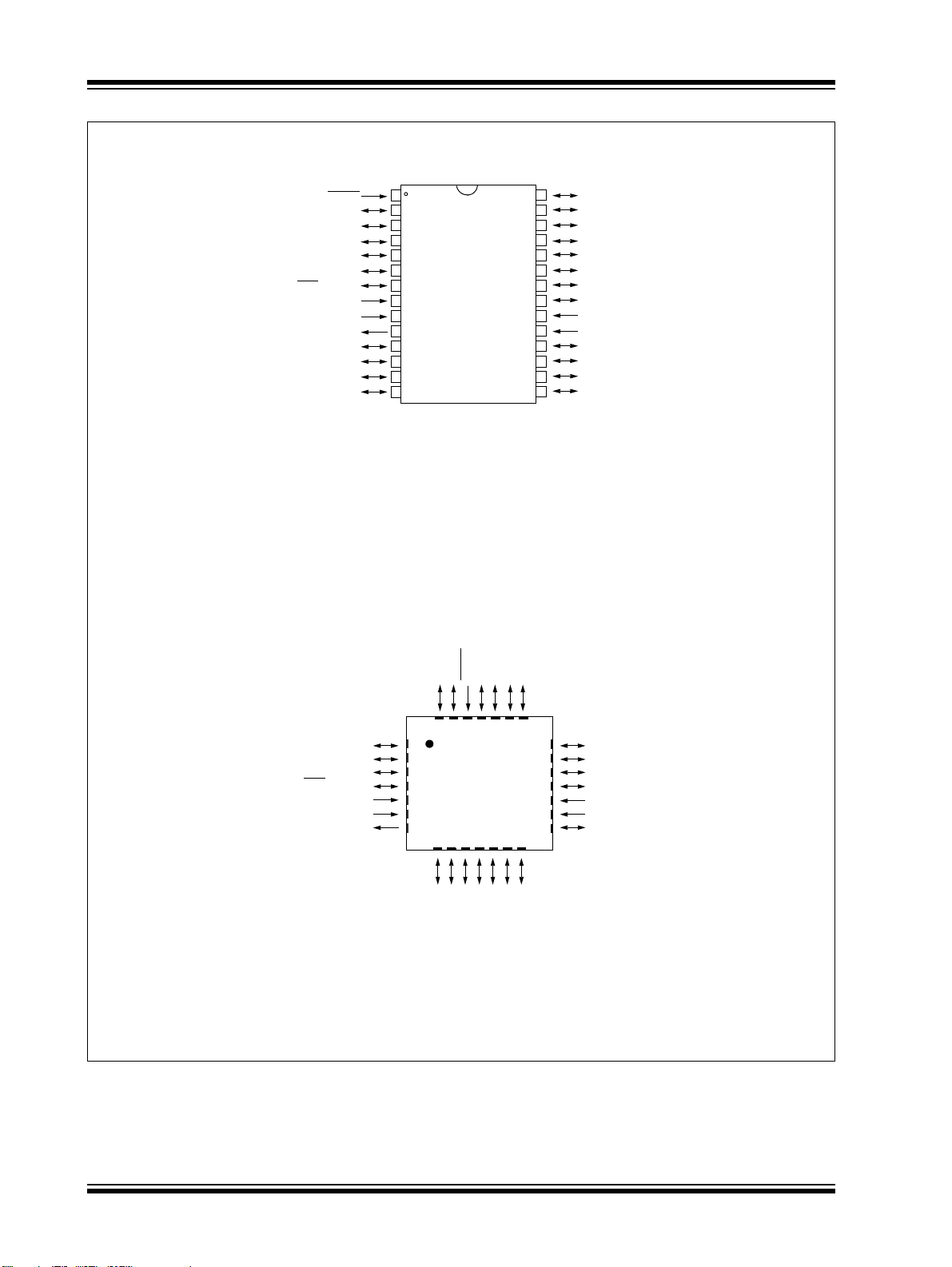

引脚图

28 引脚 SPDIP、SOIC 和 SSOP(300 MIL)

RA2/AN2/V

RA5/AN4/SS1/C2OUT

RC0/T1OSO/T1CKI

RC1/T1OSI/CCP2*

* 引脚功能取决于器件配置。

28 引脚 QFN

MCLR

RA0/AN0

RA1/AN1

REF-/CVREF

RA3/AN3/VREF+

VDDCORE/VCAP

V

OSC1/CLKI

OSC2/CLKO

RC2/CCP1

RC3/SCK1/SCL1

PIC18F25J10

28

27

26

25

24

23

22

21

20

19

18

17

16

15

RB7/KBI3/PGD

RB6/KBI2/PGC

RB5/KBI1/T0CKI/C1OUT

RB4/KBI0/AN11

RB3/AN9/CCP2*

RB2/INT2/AN8

RB1/INT1/AN10

RB0/INT0/FLT0/AN12

V

DD

VSS

RC7/RX/DT

RC6/TX/CK

RC5/SDO1

RC4/SDI1/SDA1

1

2

3

4

5

6

7

SS

8

9

10

11

12

13

14

PIC18F24J10

RA2/AN2/VREF-/CVREF

RA5/AN4/SS1/C2OUT

* 引脚功能取决于器件配置。

RA3/AN3/VREF+

V

DDCORE/VCAP

V

OSC1/CLKI

OSC2/CLKO

RB7/KBI3/PGD

RB6/KBI2/PGC

RB5/KBI1/T0CKI/C1OUT

MCLR

RA0/AN0

RA1/AN1

1

2

3

PIC18F24J10

4

SS

PIC18F25J10

5

6

7

10 11

9

8

RC2/CCP1

RC1/T1OSI/CCP2*

RC0/T1OSO/T1CKI

RB4/KBI0/AN11

22

232425262728

21

20

19

18

17

16

15

12 13 14

RC5/SDO1

RC6/TX/CK

RC4/SDI1/SDA1

RC3/SCK1/SCL1

RB3/AN9/CCP2*

RB2/INT2/AN8

RB1/INT1/AN10

RB0/INT0/FLT0/AN12

V

DD

VSS

RC7/RX/DT

DS39682A_CN 第 2 页 高级信息 2005 Microchip Technology Inc.

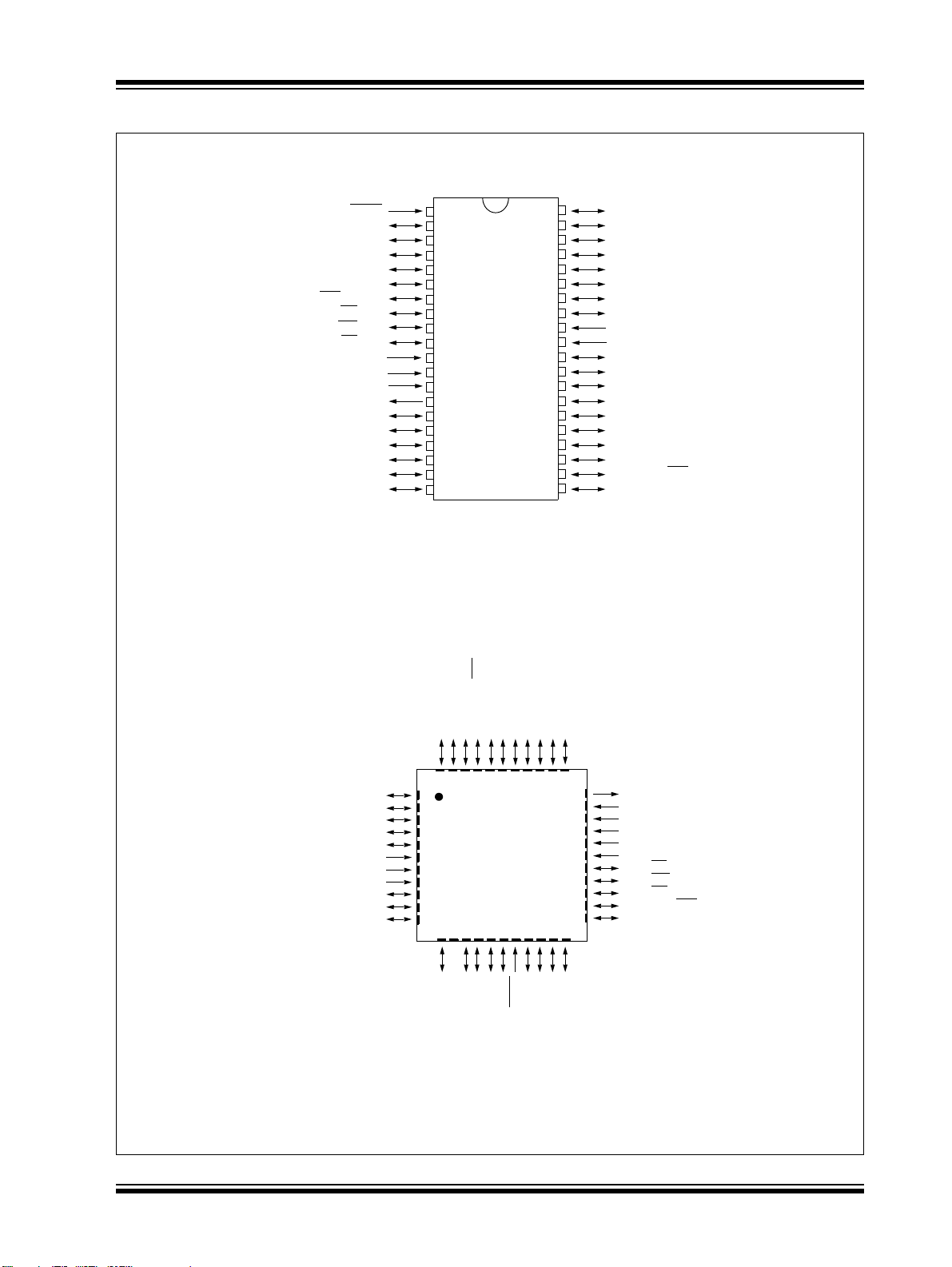

引脚图 (续)

40 引脚 PDIP(600 MIL)

PIC18F45J10 系列

RA2/AN2/V

RA5/AN4/SS1/C2OUT

RC0/T1OSO/T1CKI

RC1/T1OSI/CCP2*

RC3/SCK1/SCL1

RD0/PSP0/SCK2/SCL2

RD1/PSP1/SDI2/SDA2

* 引脚功能取决于器件配置。

44 引脚 QFN

MCLR

RA0/AN0

RA1/AN1

REF-/CVREF

RA3/AN3/VREF+

V

DDCORE/VCAP

RE0/RD

/AN5

RE1/WR

/AN6

/AN7

RE2/CS

V

DD

VSS

OSC1/CLKI

OSC2/CLKO

RC2/CCP1/P1A

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

PIC18F44J10

PIC18F45J10

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

RB7/KBI3/PGD

RB6/KBI2/PGC

RB5/KBI1/T0CKI/C1OUT

RB4/KBI0/AN11

RB3/AN9/CCP2*

RB2/INT2/AN8

RB1/INT1/AN10

RB0/INT0/FLT0/AN12

DD

V

VSS

RD7/PSP7/P1D

RD6/PSP6/P1C

RD5/PSP5/P1B

RD4/PSP4

RC7/RX/DT

RC6/TX/CK

RC5/SDO1

RC4/SDI1/SDA1

RD3/PSP3/SS2

RD2/PSP2/SDO2

RB0/INT0/FLT0/AN12

* 引脚功能取决于器件配置。

RC7/RX/DT

RD4/PSP4

RD5/PSP5/P1B

RD6/PSP6/P1C

RD7/PSP7/P1D

RB1/INT1/AN10

RB2/INT2/AN8

V

AVDD

VDD

RD2/PSP2/SDO2

RD1/PSP1/SDI2/SDA2

RD0/PSP0/SCK2/SCL2

RC3/SCK1/SCL1

RC2/CCP1/P1A

RC1/T1OSI/CCP2*

37

RA0/AN0

363435

RA1/AN1

RC0/T1OSO/T1CKI

33

32

31

30

29

28

27

26

25

24

23

REF-/CVREF-

RA3/AN3/VREF+

RA2/AN2/V

OSC2/CLKO

OSC1/CLKI

V

SS

AVSS

VDD

AVDD

RE2/CS/AN7

RE1/WR

/AN6

RE0/RD

/AN5

RA5/AN4/SS1

V

DDCORE/VCAP

/C2OUT

RC6/TX/CK

RC5/SDO1

RC4/SDI1/SDA1

RD3/PSP3/SS2

414039

42

44

43

1

2

3

4

5

SS

PIC18F44J10

6

PIC18F45J10

7

8

9

10

11

121314

NC

RB3/AN9/CCP2*

RB4/KBI0/AN11

15

16

RB6/KBI2/PGC

RB5/KBI1/T0CKI/C1OUT

38

1819202122

17

MCLR

RB7/KBI3/PGD

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 3 页

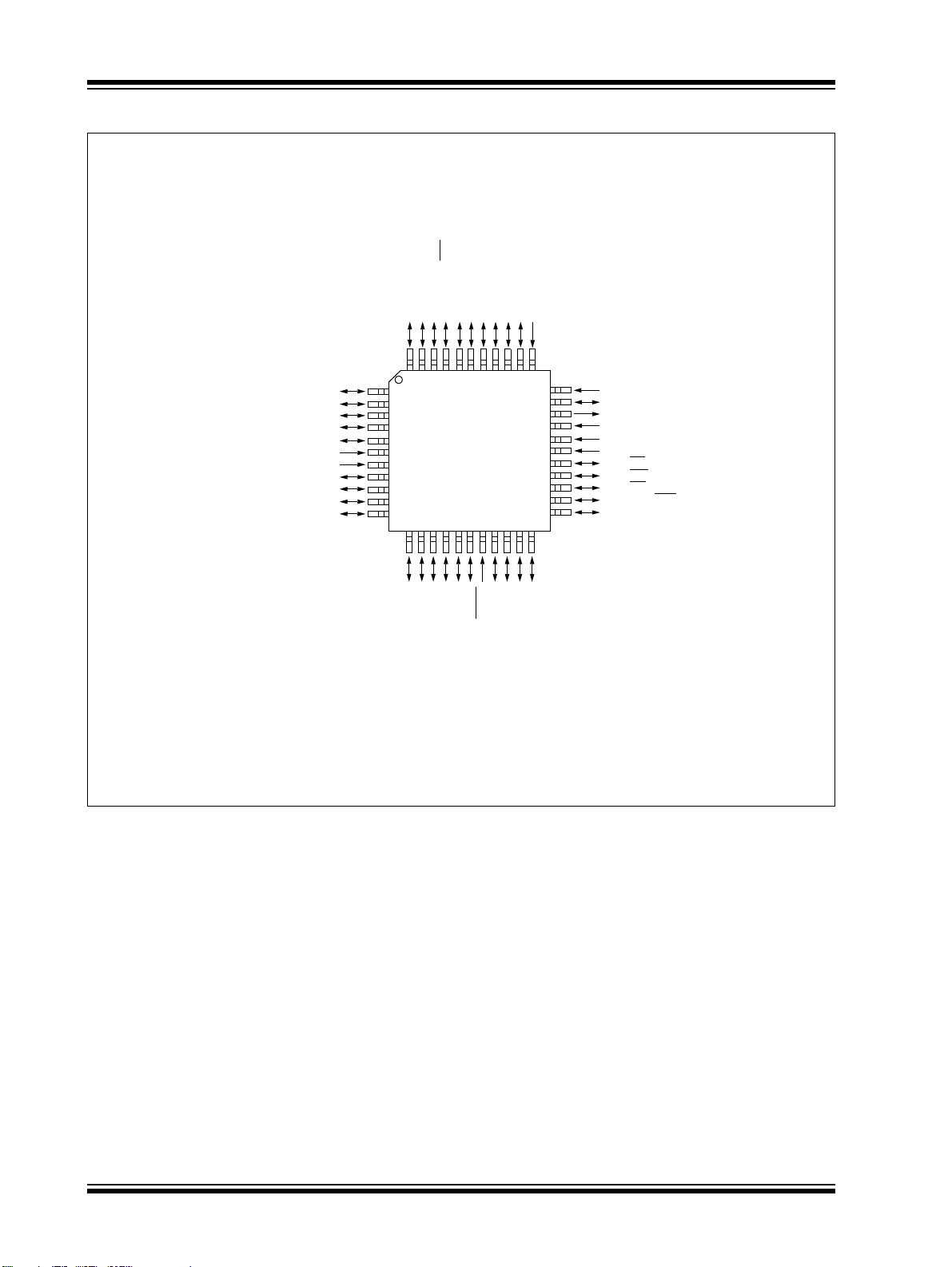

PIC18F45J10 系列

引脚表 (续)

44 引脚 TQFP

RC7/RX/DT

RD4/PSP4

RD5/PSP5/P1B

RD6/PSP6/P1C

RD7/PSP7/P1D

RB0/INT0/FLT0/AN12

RB1/INT1/AN10

RB2/INT2/AN8

RB3/AN9/CCP2*

V

VDD

SS

RC6/TX/CK

RC5/SDO1

44

43

1

2

3

4

5

PIC18F44J10

6

PIC18F45J10

7

8

9

10

11

121314

RC4/SDI1/SDA1

RD3/PSP3/SS2

RD2/PSP2/SDO2

RD1/PSP1/SDI2/SDA2

RD0/PSP0/SCK2/SCL2

RC3/SCK1/SCL1

38

16

17

1819202122

37

414039

42

15

RC2/CCP1/P1A

RC1/T1OSI/CCP2*

NC

363435

33

32

31

30

29

28

27

26

25

24

23

NC

RC0/T1OSO/T1CKI

OSC2/CLKO

OSC1/CLKI

V

SS

VDD

RE2/CS/AN7

/AN6

RE1/WR

RE0/RD

/AN5

RA5/AN4/SS1

V

DDCORE/VCAP

/C2OUT

* 引脚功能取决于器件配置。

NC

NC

RB4/KBI0/AN11

RB6/KBI2/PGC

RB5/KBI1/T0CKI/C1OUT

RB7/KBI3/PGD

MCLR

RA0/AN0

RA1/AN1

REF-/CVREF-

RA3/AN3/VREF+

RA2/AN2/V

DS39682A_CN 第 4 页 高级信息 2005 Microchip Technology Inc.

PIC18F45J10 系列

目录

1.0 器件概述 ....................................................................................................................................................................................... 7

2.0 振荡器配置 ................................................................................................................................................................................. 23

3.0 功耗管理模式.............................................................................................................................................................................. 31

4.0 复位 ............................................................................................................................................................................................ 37

5.0 存储器构成 ................................................................................................................................................................................. 47

6.0 闪存程序存储器 .......................................................................................................................................................................... 67

7.0 8 x 8 硬件乘法器......................................................................................................................................................................... 77

8.0 中断 ............................................................................................................................................................................................ 79

9.0 I/O 端口 ...................................................................................................................................................................................... 93

10.0 Timer0 模块 .............................................................................................................................................................................. 111

11.0 Timer1 模块 .............................................................................................................................................................................. 115

12.0 Timer2 模块 .............................................................................................................................................................................. 121

13.0 捕捉 / 比较 /PWM (CCP)模块............................................................................................................................................... 123

14.0 增强型捕捉 / 比较 /PWM (ECCP)模块 ................................................................................................................................. 131

15.0 主控同步串口 (MSSP)模块 .................................................................................................................................................. 145

16.0 增强型通用同步 / 异步收发器 (EUSART).............................................................................................................................. 187

17.0 10 位模数转换器 (A/D)模块.................................................................................................................................................. 209

18.0 比较器模块 ............................................................................................................................................................................... 219

19.0 比较器参考电压源模块 ............................................................................................................................................................. 225

20.0 CPU 的特殊性能....................................................................................................................................................................... 229

21.0 指令集综述 ............................................................................................................................................................................... 241

22.0 开发支持 ................................................................................................................................................................................... 291

23.0 电气规范 ................................................................................................................................................................................... 297

24.0 DC 和 AC 特性图表 .................................................................................................................................................................. 331

25.0 封装信息 ................................................................................................................................................................................... 333

附录 A:版本历史........................................................................................................................................................................ 343

附录 B: 高档器件系列间的移植................................................................................................................................................... 343

索引................................................................................................................................................................................................... 345

Microchip 网站.................................................................................................................................................................................... 355

客户变更通知服务 .............................................................................................................................................................................. 355

客户支持............................................................................................................................................................................................. 355

读者反馈............................................................................................................................................................................................. 356

PIC18F45J10 系列产品标识体系 ....................................................................................................................................................... 357

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 5 页

PIC18F45J10 系列

致客户

我们旨在提供最佳文档供客户正确使用 Microchip 产品。为此,我们将不断改进出版物的内容和质量,使之更好地满足您的要求。

出版物的质量将随新文档及更新版本的推出而得到提升。

如果您对本出版物有任何问题和建议,请通过电子邮件联系我公司 TRC 经理,电子邮件地址为 CTRC@microchip.com,或将本

数据手册后附的 《读者反馈表》传真到 86-21-5407 5066。我们期待您的反馈。

最新数据手册

欲获得本数据手册的最新版本,请查询我公司的网站:

http://www.microchip.com

查看数据手册中任意一页下边角处的文献编号即可确定其版本。文献编号中数字串后的字母是版本号,例如:DS30000A是 DS30000

的 A 版本。

勘误表

现有器件可能带有一份勘误表,描述了实际运行与数据手册中记载内容之间存在的细微差异以及建议的变通方法。一旦我们了解到

器件 / 文档存在某些差异时,就会发布勘误表。勘误表将注明其所适用的硅片版本和文件版本。

欲了解某一器件是否存在勘误表,请通过以下方式之一查询:

• Microchip 网站:http://www.microchip.com

• 当地 Microchip 销售办事处 (见最后一页)

在联络销售办事处时,请说明您所使用的器件型号、硅片版本和数据手册版本 (包括文献编号)。

客户通知系统

欲及时获知 Microchip 产品的最新信息,请到我公司网站 www.microchip.com 上注册。

DS39682A_CN 第 6 页 高级信息 2005 Microchip Technology Inc.

PIC18F45J10 系列

1.0 器件概述

该文档包含以下器件特定的信息:

• PIC18F24J10 • PIC18LF24J10

• PIC18F25J10 • PIC18LF25J10

• PIC18F44J10 • PIC18LF44J10

• PIC18F45J10 • PIC18LF45J10

PIC18F45J10 系列除了具有 PIC18单片机的传统优点,

即出色的计算性能和经济实惠的价格之外,还引进了一

些增强的功能,使其成为许多高性能、低功耗应用的理

想选择。

1.1 新的内核特性

1.1.1 纳瓦技术

PIC18F45J10 系列的所有器件都具有一系列能显著降

低工作功耗的特性。主要包括以下几项:

• 备用运行模式:通过将 Timer1 或内部振荡器模块

作为单片机时钟源,可使代码执行时的功耗大约降

低 90%。

• 多种空闲模式:单片机还可在其 CPU 内核禁止而

外设工作的情况下运行。处于这些状态时,功耗能

降得更低,只有正常工作需求的 4%。

• 动态模式切换:在器件工作期间可由用户代码调用

该功耗管理模式,允许用户将节能的理念融入到他

们的应用软件设计中。

• 关键模块低功耗: Timer1 和看门狗定时器的功耗

需求最低。 请参见第 23.0 节 “电气规范” 了解具

体数值。

1.1.2 振荡器选项和特性

PIC18F45J10系列的所有器件提供 3种不同的振荡器选

项,包括:

• 一个晶振模式,使用晶振或陶瓷谐振器

• 一个外部时钟模式

• INTRC 时钟源 (约 31 kHz)

除了可用作时钟源外,内部振荡器模块还提供了一个稳

定的参考源,用以实现下列额外的功能以使器件更安全

可靠地工作:

• 故障保护时钟监视器:该部件不停地监视主时钟

源,将其与内部振荡器提供的参考信号作比较。如

果发生了时钟故障,单片机会切换到内部振荡器模

块,使器件可继续低速工作或安全关闭。

• 双速启动:该功能允许在上电复位或从休眠模式唤

醒时将内部振荡器用作时钟源,直到主时钟源可用

为止。

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 7 页

PIC18F45J10 系列

1.2 其他特殊性能

• 通信:PIC18F45J10 系列包含了一系列串行通信

外设,包括一个独立增强型 USART 和 2 个主控

SSP 模块,具备 SPI 和 I2C (主控和从动)两种

工作模式。 此外,一个通用 I/O 端口可以被重新配

置为 8 位并行从动端口,实现处理器到处理器的

直接通信。

• 自编程性:这些器件能在内嵌软件控制下对各自的

程序存储空间进行写操作。通过使用引导加载子程

序,可以创建能够实现现场自我更新的应用程序。

• 扩展指令集:PIC18F45J10 系列在 PIC18 指令集

的基础上进行了扩展,添加了 8 条新指令和变址

寻址模式。此扩展可以使用一个器件配置选项使

能,它是为优化重入代码而特别设计的,这些代码

是使用高级语言 (如 C 语言)开发的。

• 增强型 CCP 模块:在 PWM 模式下,该模块提供

1、 2 或 4 路调制输出来控制半桥和全桥驱动器。

其他功能包括自动关闭 (自动关闭能在中断或其

他条件下禁止 PWM 输出)和自动重启 (自动重

启能在禁止条件被清除时再次激活输出)。

• 增强型可寻址 USART:该串行通信模块可进行标

准的 RS-232 通信并支持 LIN 总线协议。 其他增强

功能包括自动波特率检测和精度更高的 16 位波特

率发生器。

• 10 位 A/D 转换器:该模块实现了可编程采集时

间,从而不必在选择通道和启动转换之间等待一个

采样周期,因而减少了代码开销。

• 扩展的看门狗定时器 (WDT): 该增强的看门狗

定时器添加了 16 位预分频器,扩展了超时周期范

围,该超时周期在整个工作电压和温度范围内保持

稳定。 请参见第 23.0 节 “电气规范”了解超时周

期。

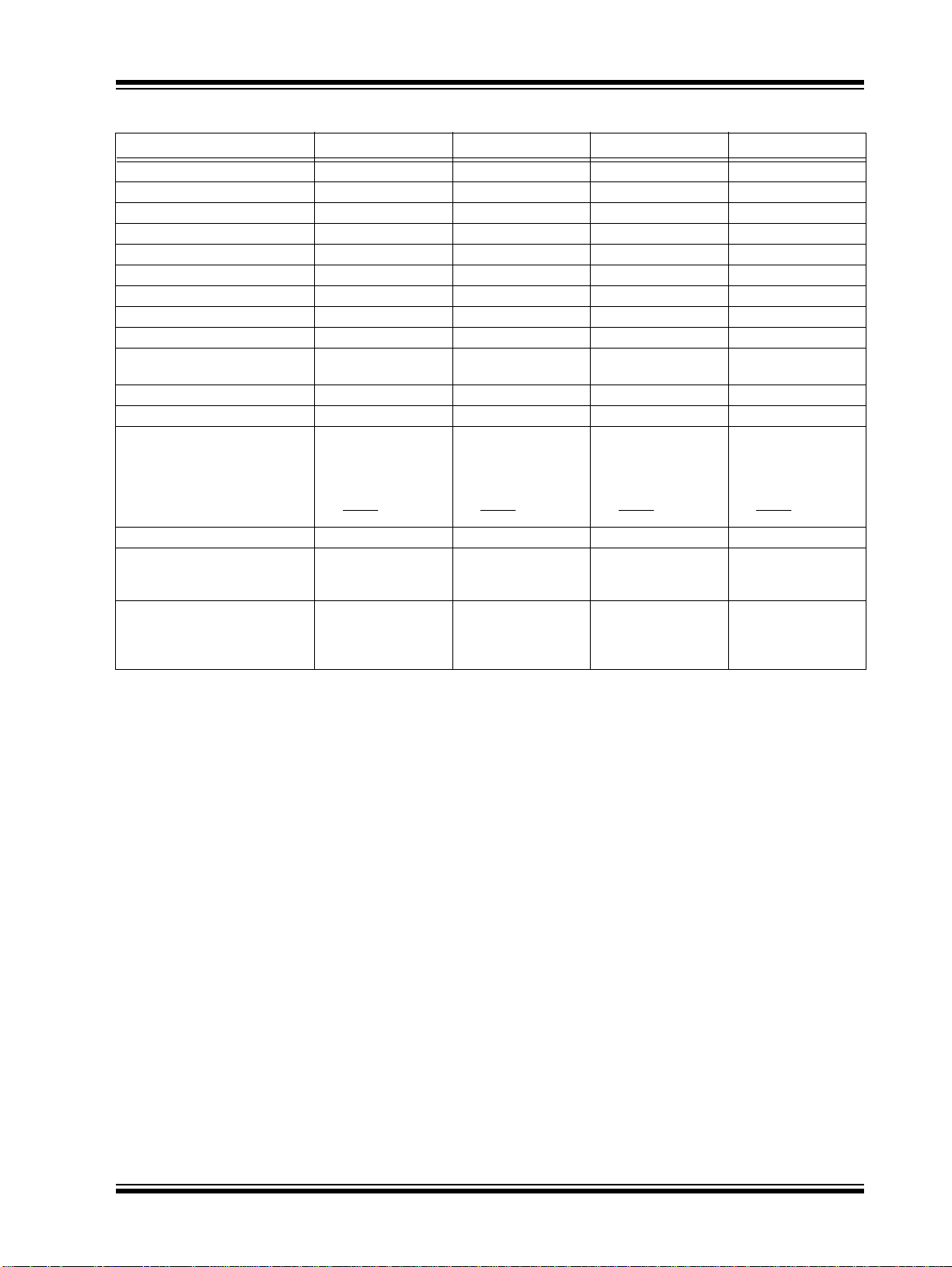

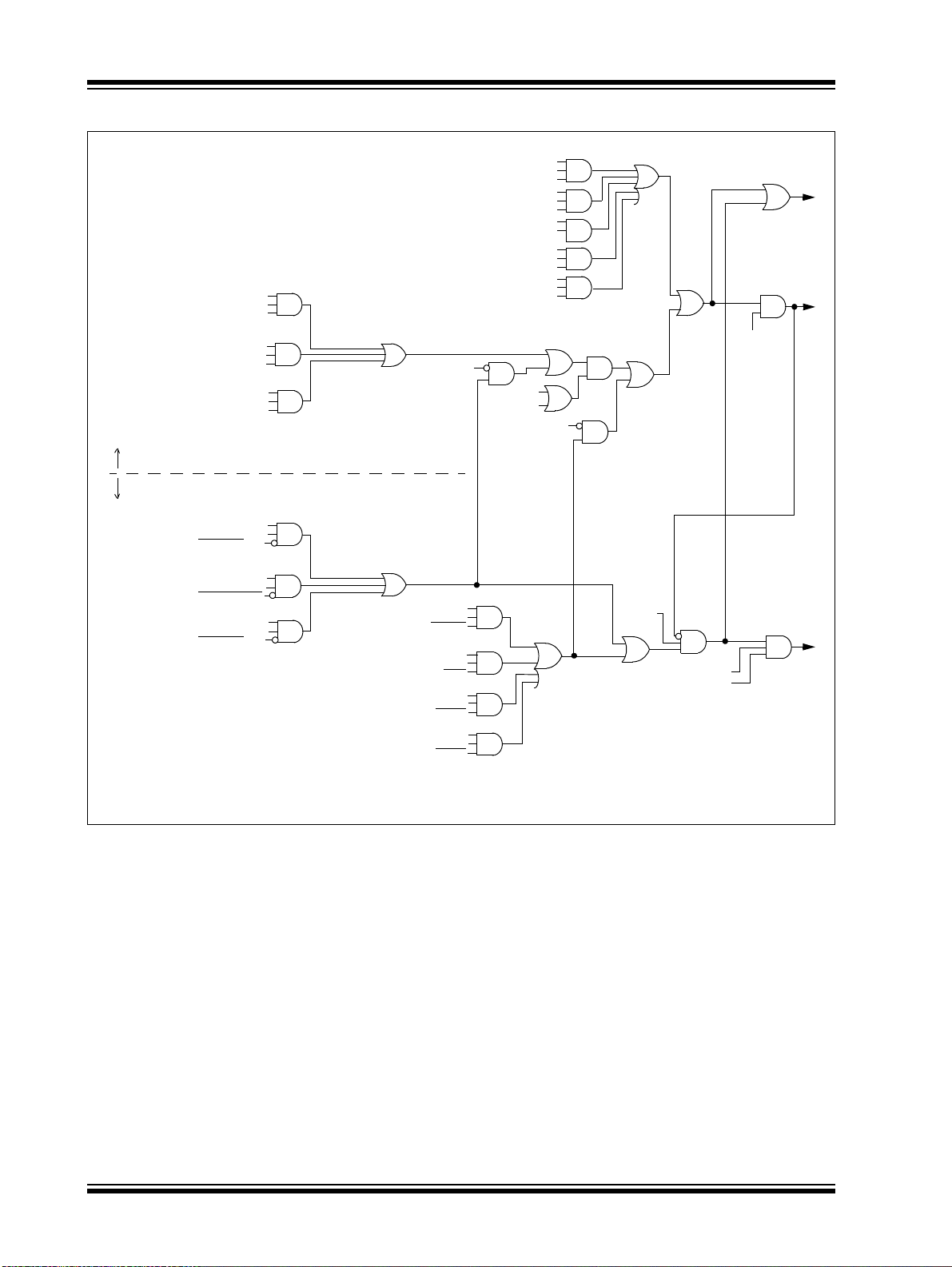

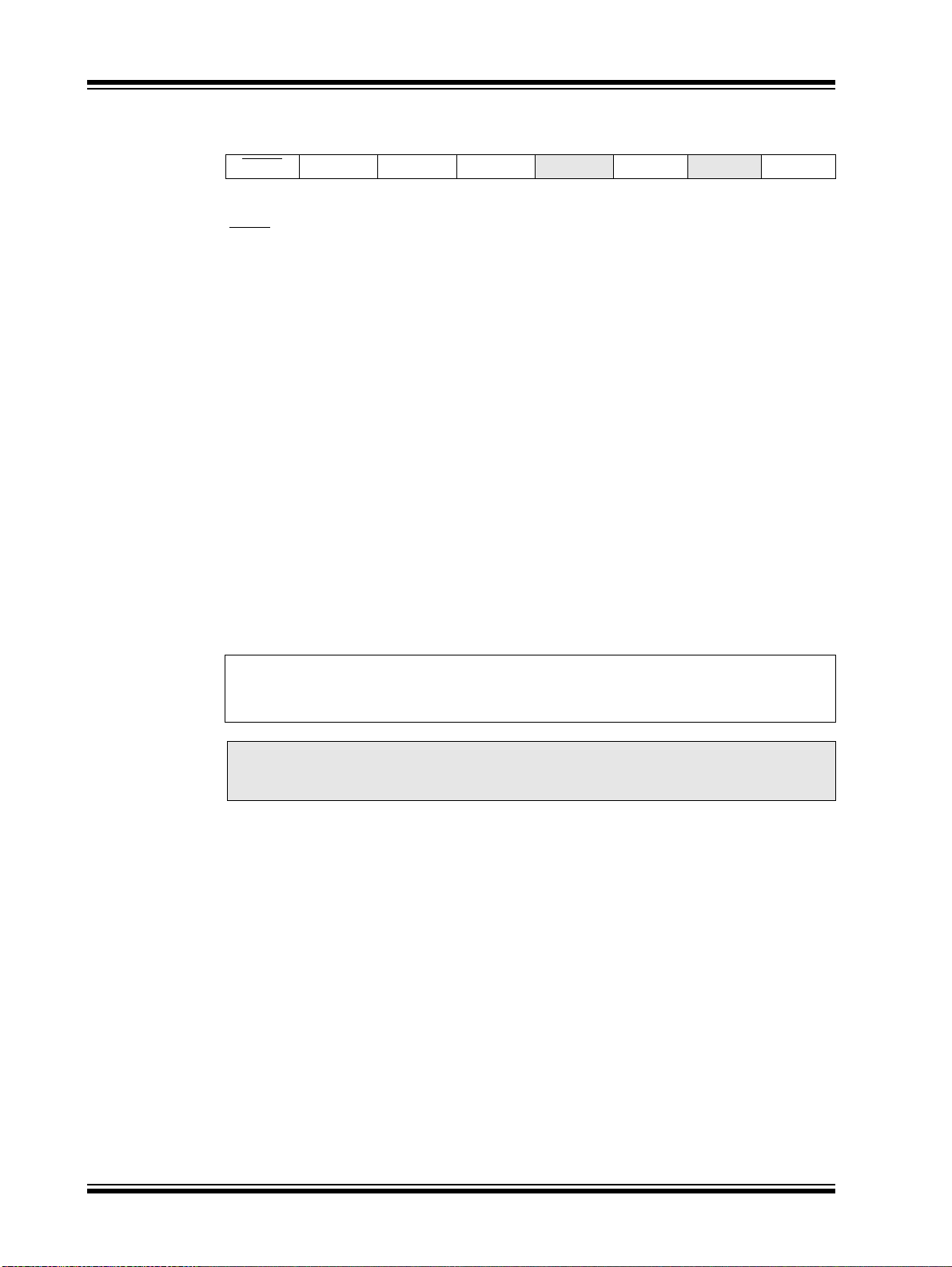

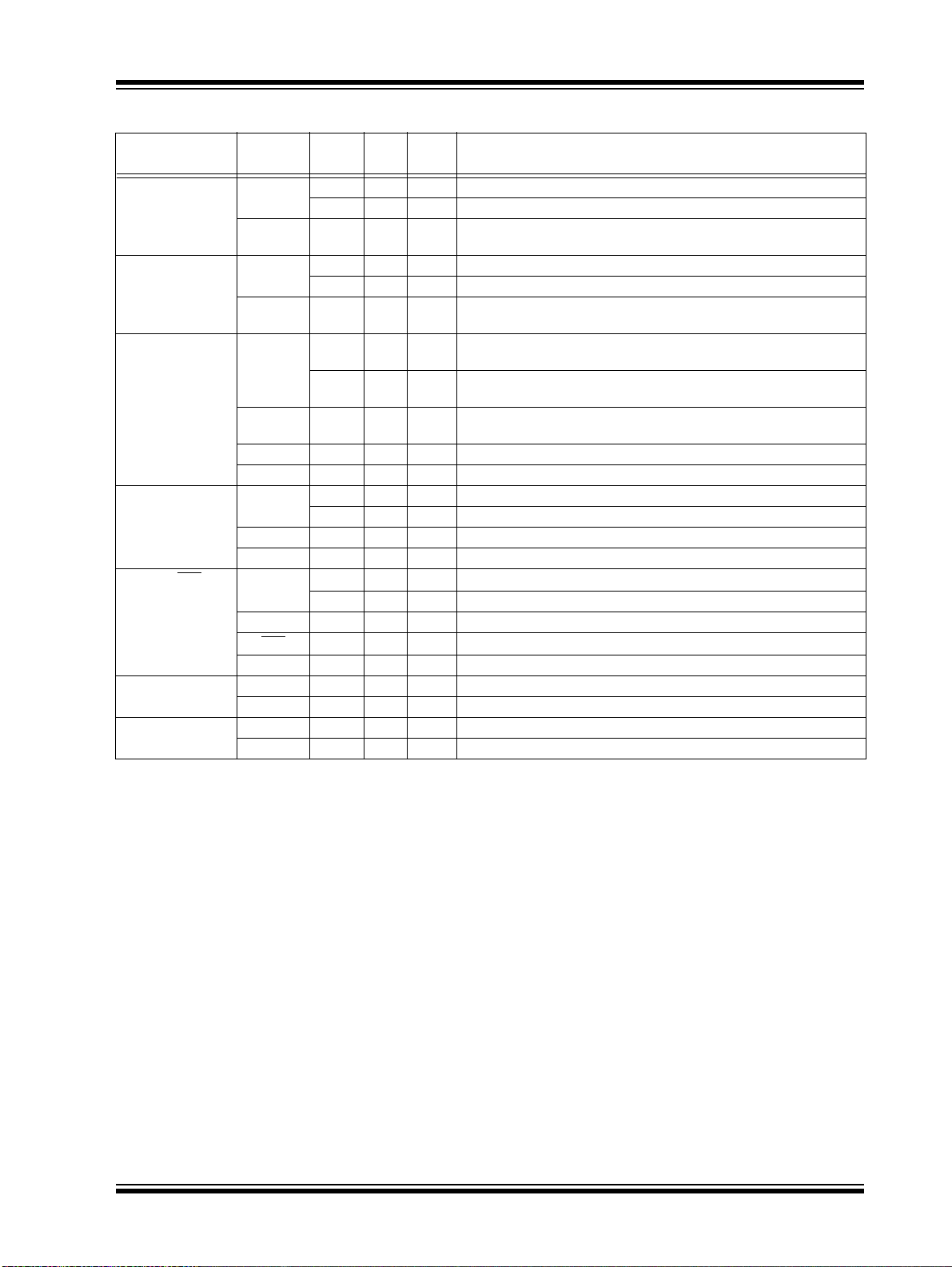

1.3 系列中各产品的具体信息

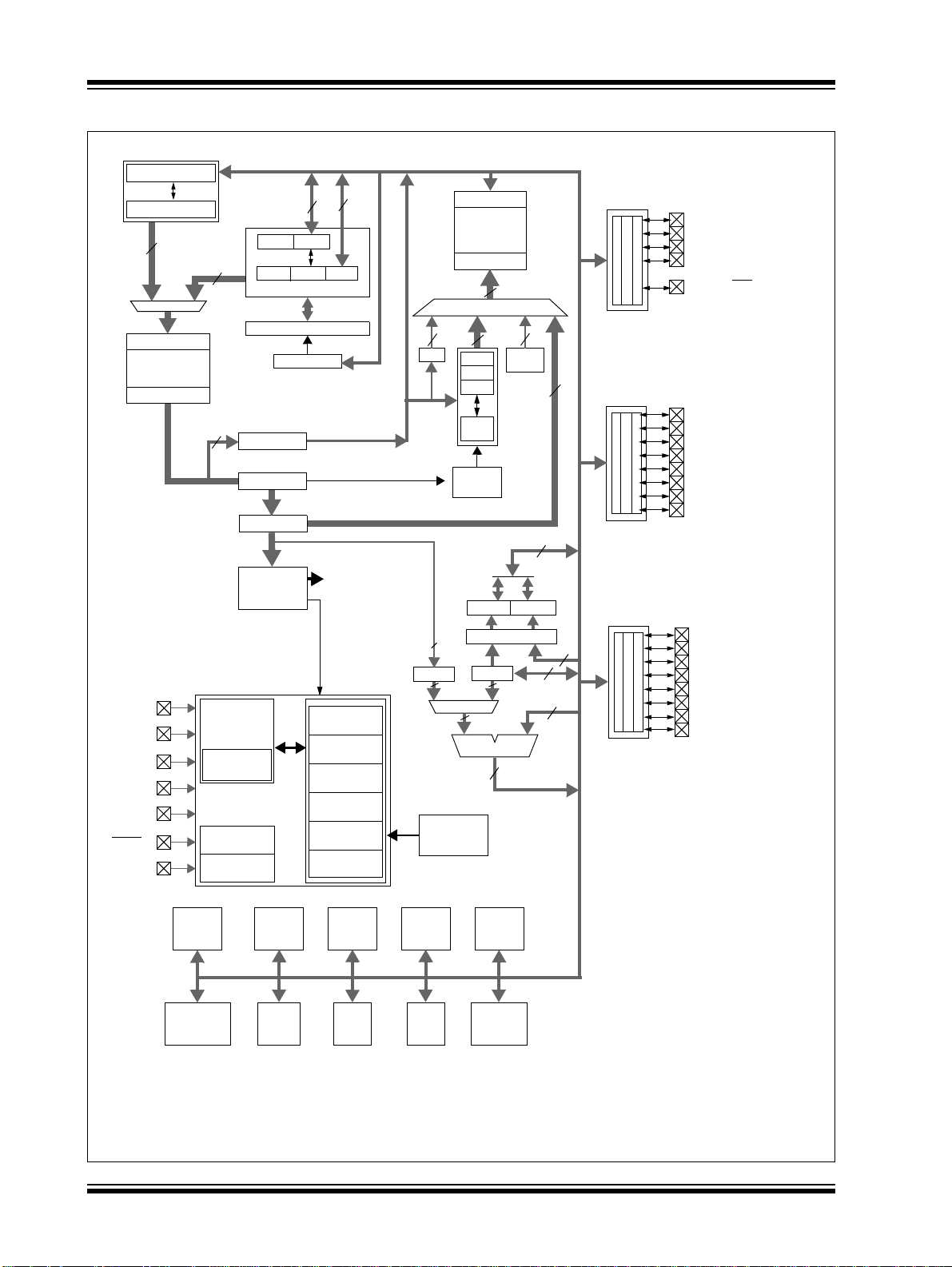

PIC18F45J10 系列器件具有 28 引脚和 40/44 引脚两种

封装形式。图 1-1 和图 1-2 分别为这两类器件的框图。

这两类器件在以下 5 个方面存在差异:

1. 闪存程序存储器 (PIC18F24J10/44J10 器件为

16KB, PIC18F25J10/45J10 为 32KB)。

2. A/D 通道 (28 引脚器件有 10 个, 40/44 引脚

器件有 13 个)。

3. I/O 端口 (28 引脚器件上有 3 个双向端口, 40/

44 引脚器件上有 5 个双向端口)。

4. CCP 和增强型 CCP (28 引脚器件有 2 个标准

的 CCP模块,40/44 引脚器件有1 个标准的CCP

模块和 1 个 ECCP 模块)。

5. 并行从动端口 (只存在于 40/44 引脚器件)。

6. PIC18F24J10/25J10 器件具备 1 个 MSSP 模块,

PIC18F44J10/45J10 器件具备 2 个 MSSP 模块。

7. 器件编号中带 “F”的器件 (如 PIC18F25J10)

DD 最小值可为 2.8 V,而器件编号中带“LF”

的 V

的器件 (如 PIC18LF25J10)能在 2.0-3.6 V 的

DD 范围内工作,但是 VDDCORE 决不能超过

V

VDD。

该系列器件的其他功能都是相同的。表 1-1 汇总了这些

功能。

表 1-2 和表 1-3 列举了所有器件的引脚排列方式。

PIC18F45J10 系列器件具有片内稳压器,可向内核提供

稳定的电平。器件编号中带有“F”的器件(如

PIC18F25J10)使能了稳压器。这些器件能在 2.7-3.6 V

DD 范围内运行,但是要在 VDDCORE 引脚和 VSS 引

的 V

脚之间连接低 ESR 的电容。 器件编号中带 “LF”的器

件(如PIC18LF24J10)没有使能稳压器。 应给VDDCORE

引脚施加 2.0-2.7 V 的电压,而给 VDD 引脚施加 2.0-3.6 V

的电压(VDDCORE 决不能超过 VDD)。请 参 见 第 20.3 节

“片内稳压器”了解内部稳压器的详细信息。

DS39682A_CN 第 8 页 高级信息 2005 Microchip Technology Inc.

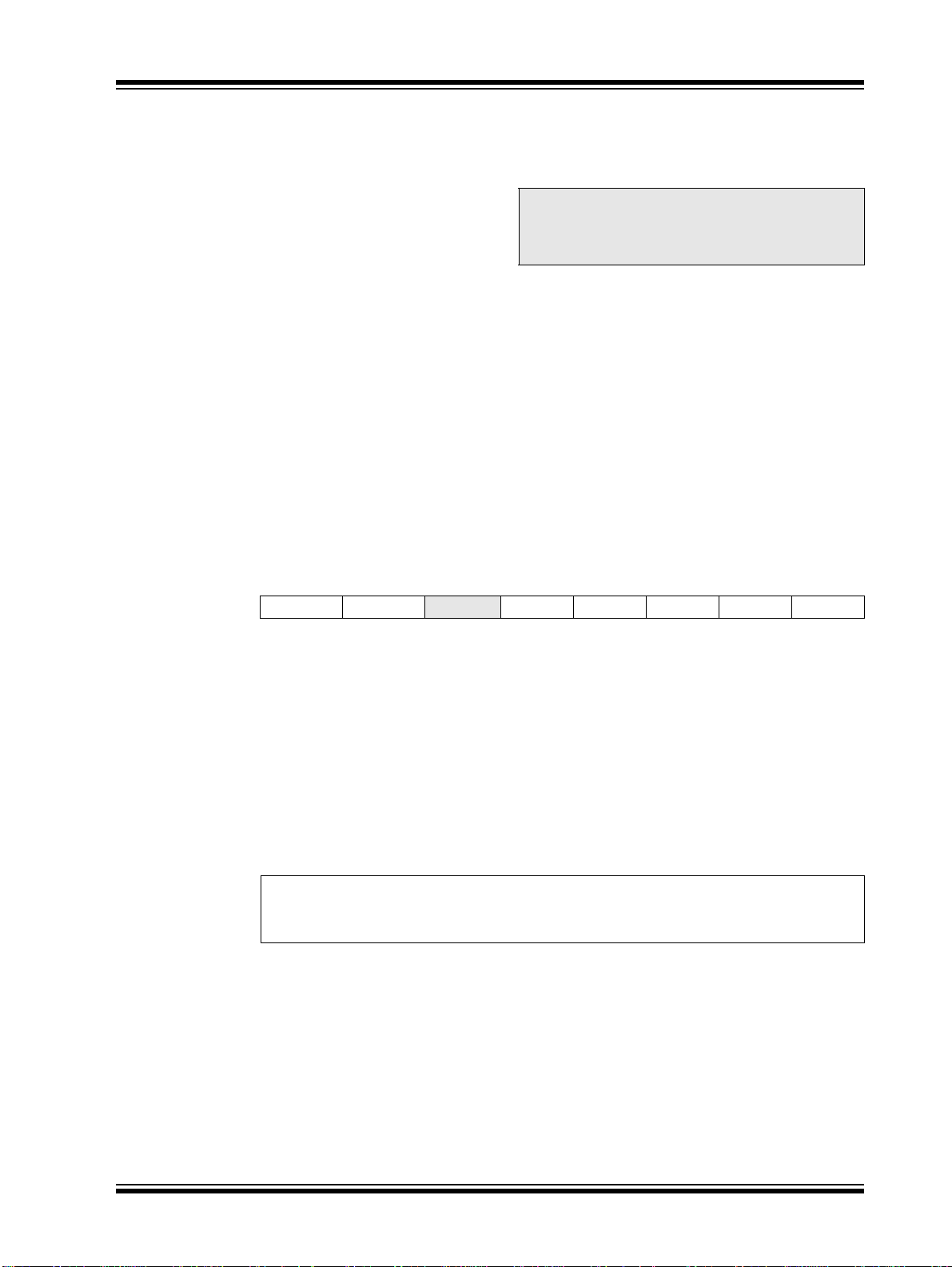

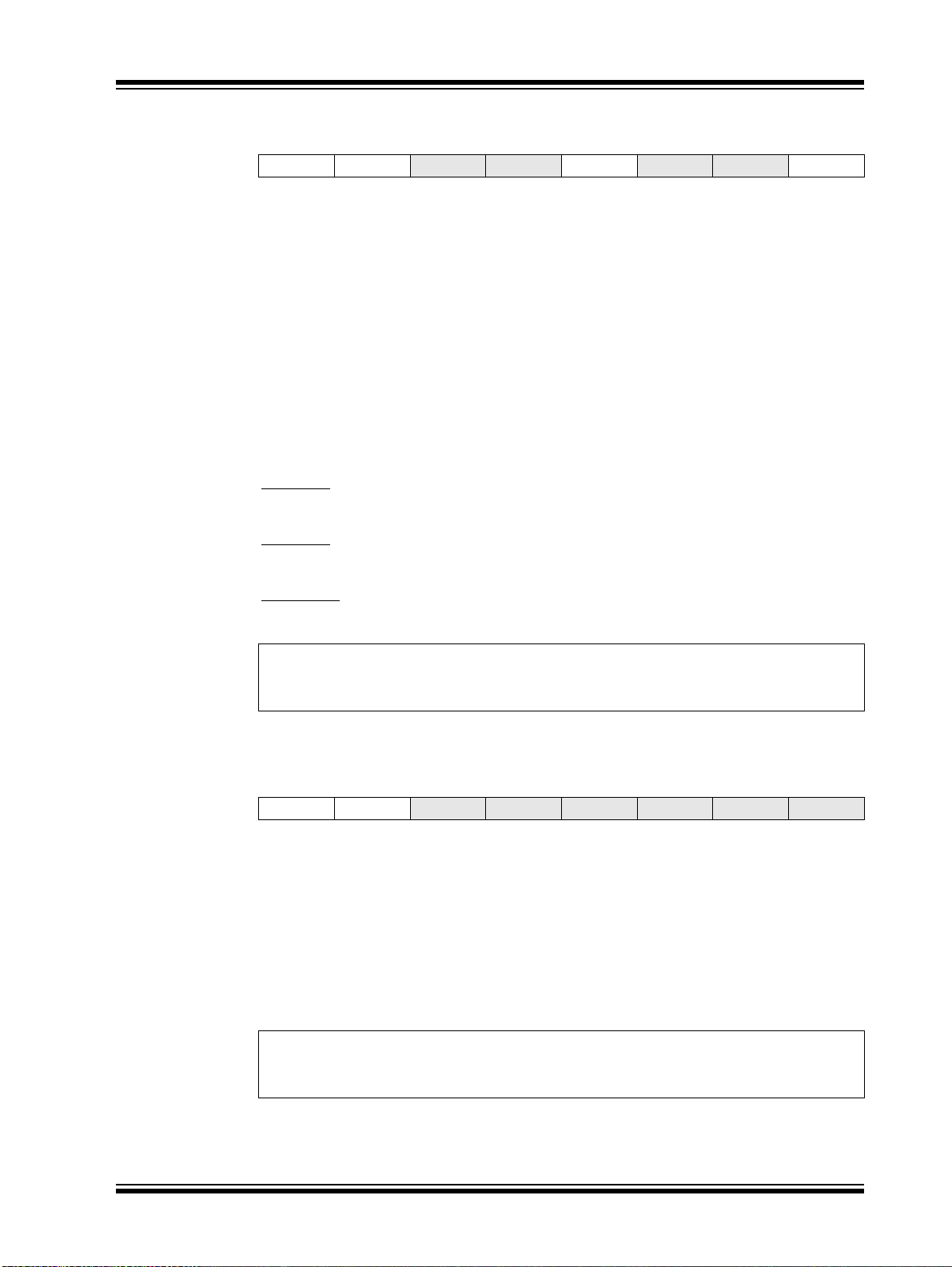

PIC18F45J10 系列

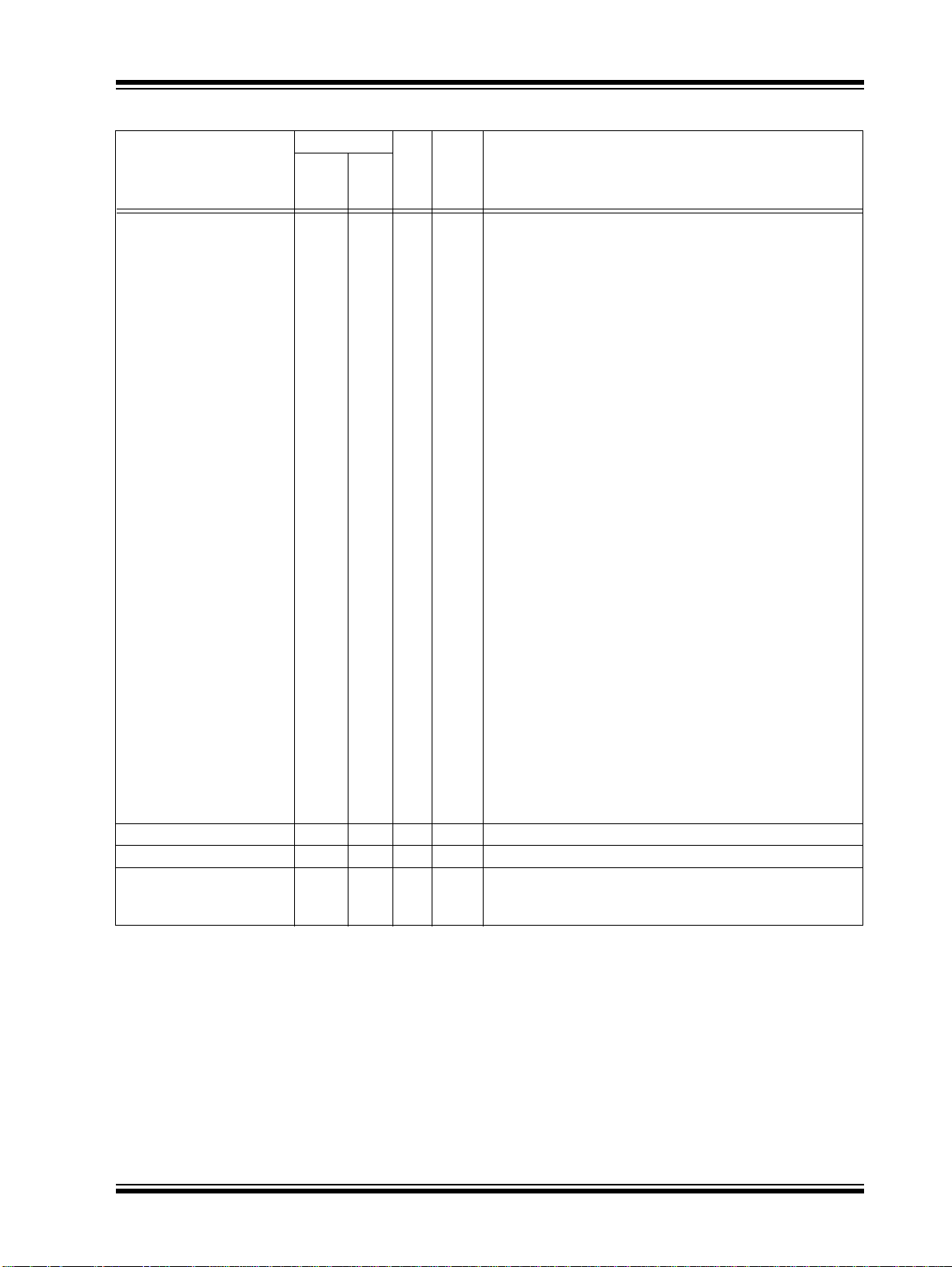

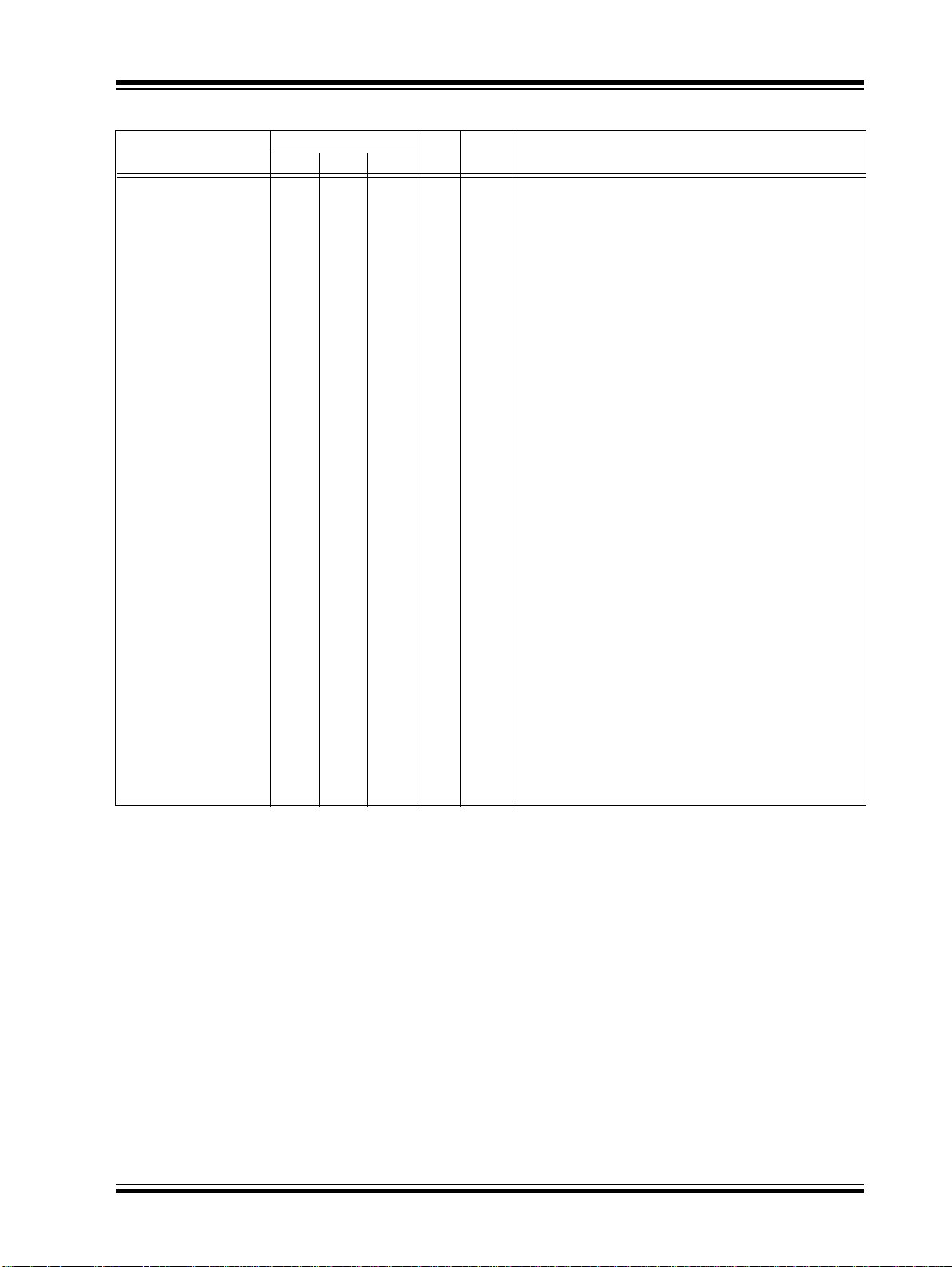

表 1-1: 器件特性

特性

工作频率 DC - 40 MHz DC - 40 MHz DC - 40 MHz DC - 40 MHz

程序存储器 (字节)

程序存储器 (指令)

数据存储器 (字节)

中断源

I/O 端口 端口 A、 B 和 C 端口 A、 B 和 C 端口 A、B、C、D 和 E 端口 A、B、C、D 和 E

定时器

捕捉 / 比较 /PWM 模块

增强型捕捉 / 比较 /PWM 模块

串行通信 MSSP,

并行通信 (PSP) 无无有有

10 位模数转换模块 10 路输入通道 10 路输入通道 13 路输入通道 13 路输入通道

复位 (和延迟) POR, BOR

可编程欠压复位 有 有 有 有

指令集 75 条指令;

封装 28 引脚 SPDIP

注 1: PIC18LF2XJ10/4XJ10 器件不能使用欠压复位。

PIC18F24J10 PIC18F25J10 PIC18F44J10 PIC18F45J10

16384 32768 16384 32768

8192 16384 8192 16384

768 1536 768 1536

19 19 20 20

3333

2211

0011

增强型 USART

(1)

,

RESET 指令,

堆栈满,

堆栈下溢 (PWRT 和

OST),

MCLR

和 WDT

使能了扩展指令集

后总共为 83 条指令

28 引脚 SOIC

28 引脚 SSOP

28 引脚 QFN

MSSP,

增强型 USART

堆栈满,

OST),

和 WDT

(1)

,

POR, BOR

RESET 指令,

堆栈下溢 (PWRT 和

MCLR

75 条指令;

使能了扩展指令集

后总共为 83 条指令

28 引脚 SPDIP

28 引脚 SOIC

28 引脚 SSOP

28 引脚 QFN

MSSP,

增强型 USART

堆栈满,

OST),

和 WDT

(1)

,

POR, BOR

RESET 指令,

堆栈下溢 (PWRT 和

MCLR

75 条指令;

使能了扩展指令集

后总共为 83 条指令

40 引脚 PDIP

44 引脚 QFN

44 引脚 TQFP

MSSP,

增强型 USART

POR, BOR

RESET 指令,

堆栈满,

堆栈下溢 (PWRT 和

OST),

MCLR

75 条指令;

使能了扩展指令集

后总共为 83 条指令

40 引脚 PDIP

44 引脚 QFN

44 引脚 TQFP

(1)

和 WDT

,

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 9 页

PIC18F45J10 系列

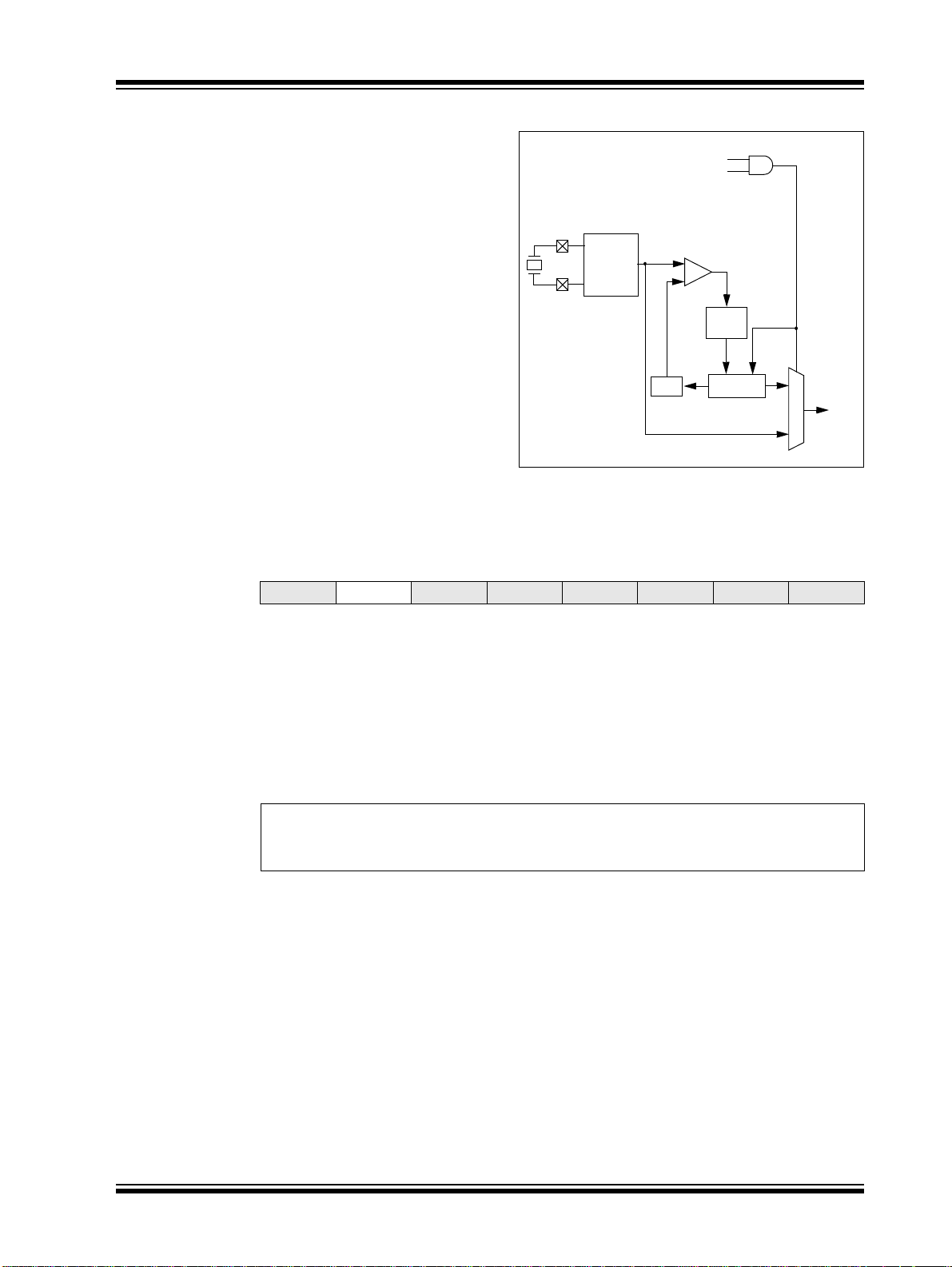

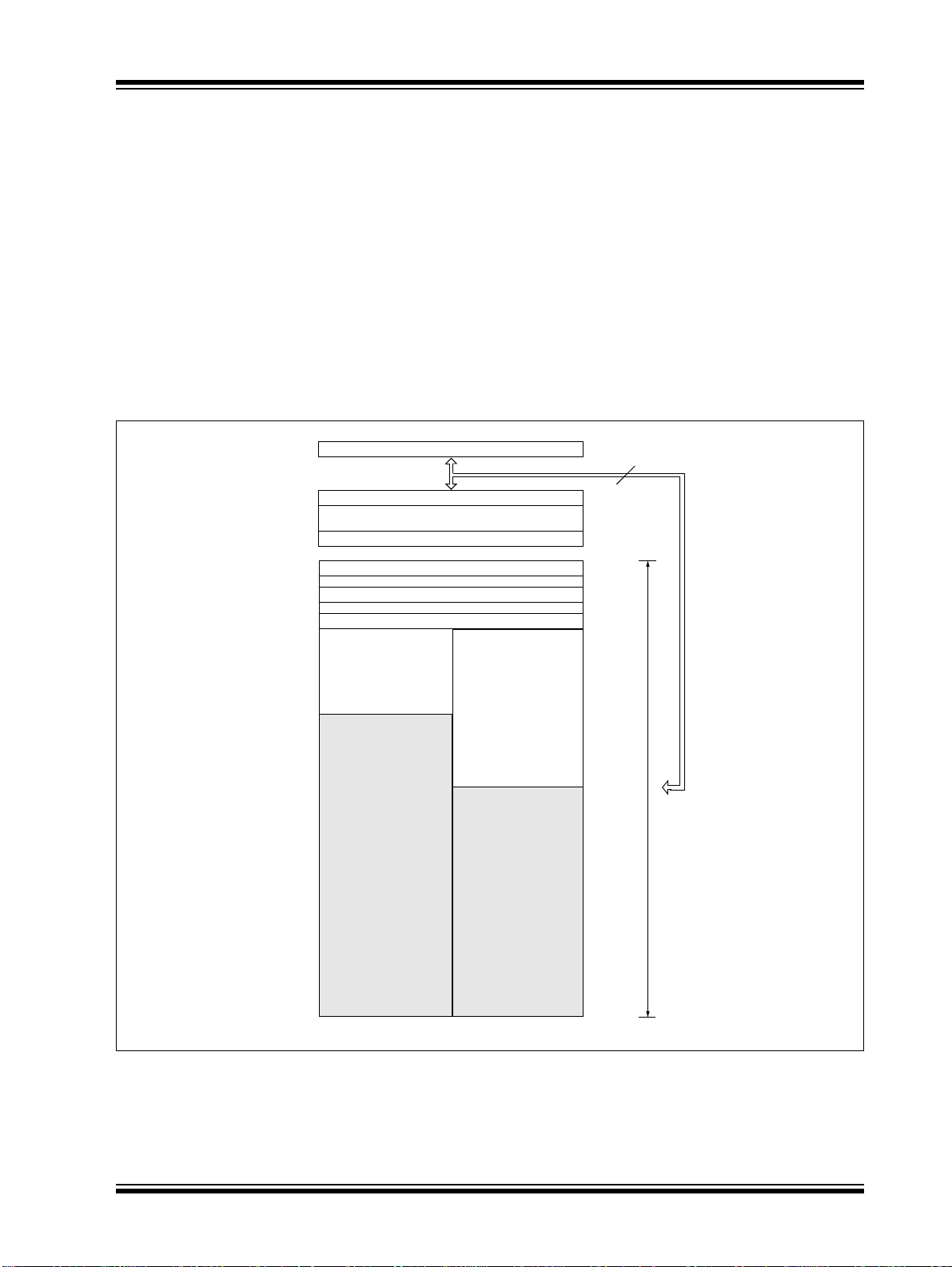

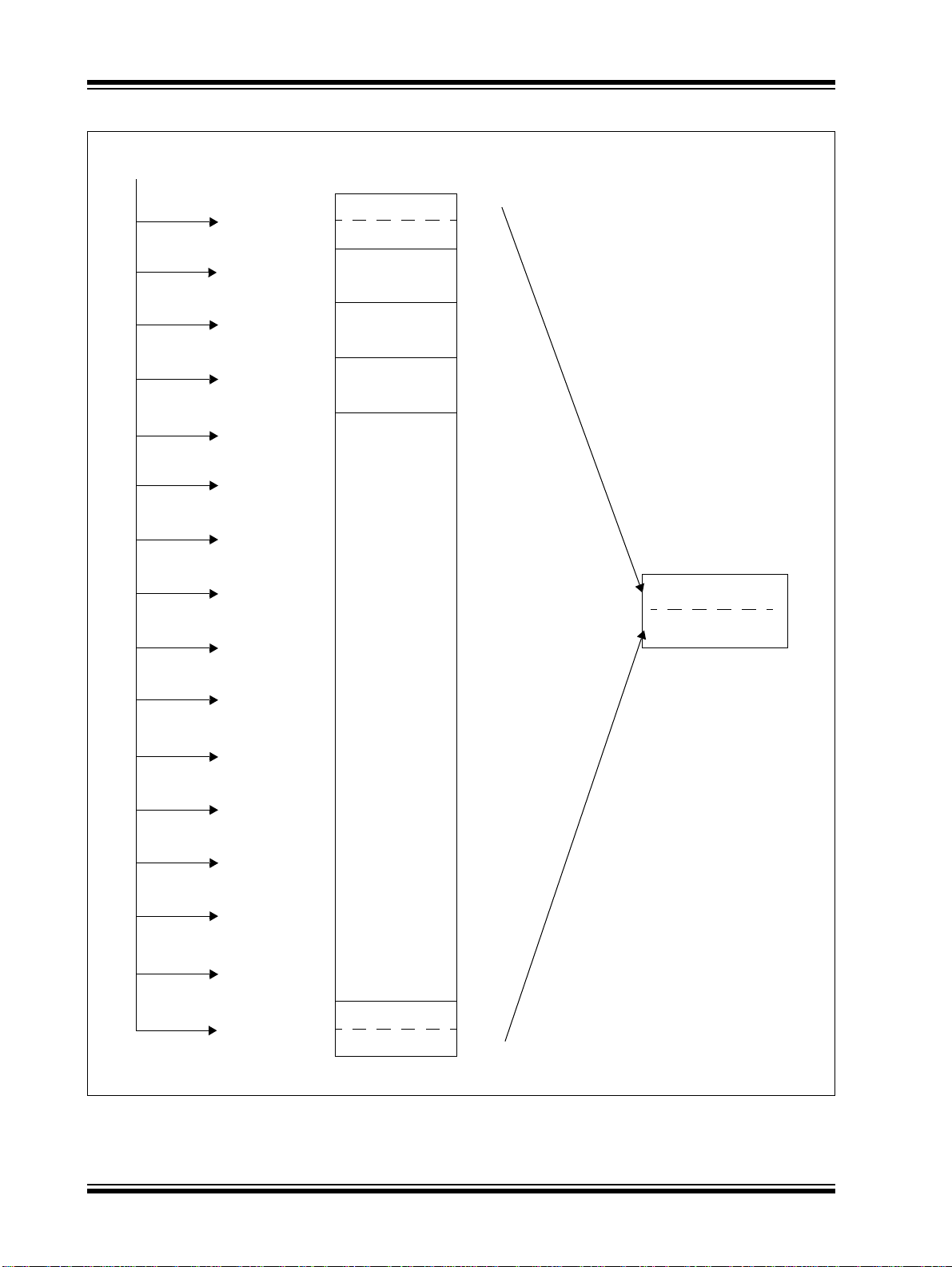

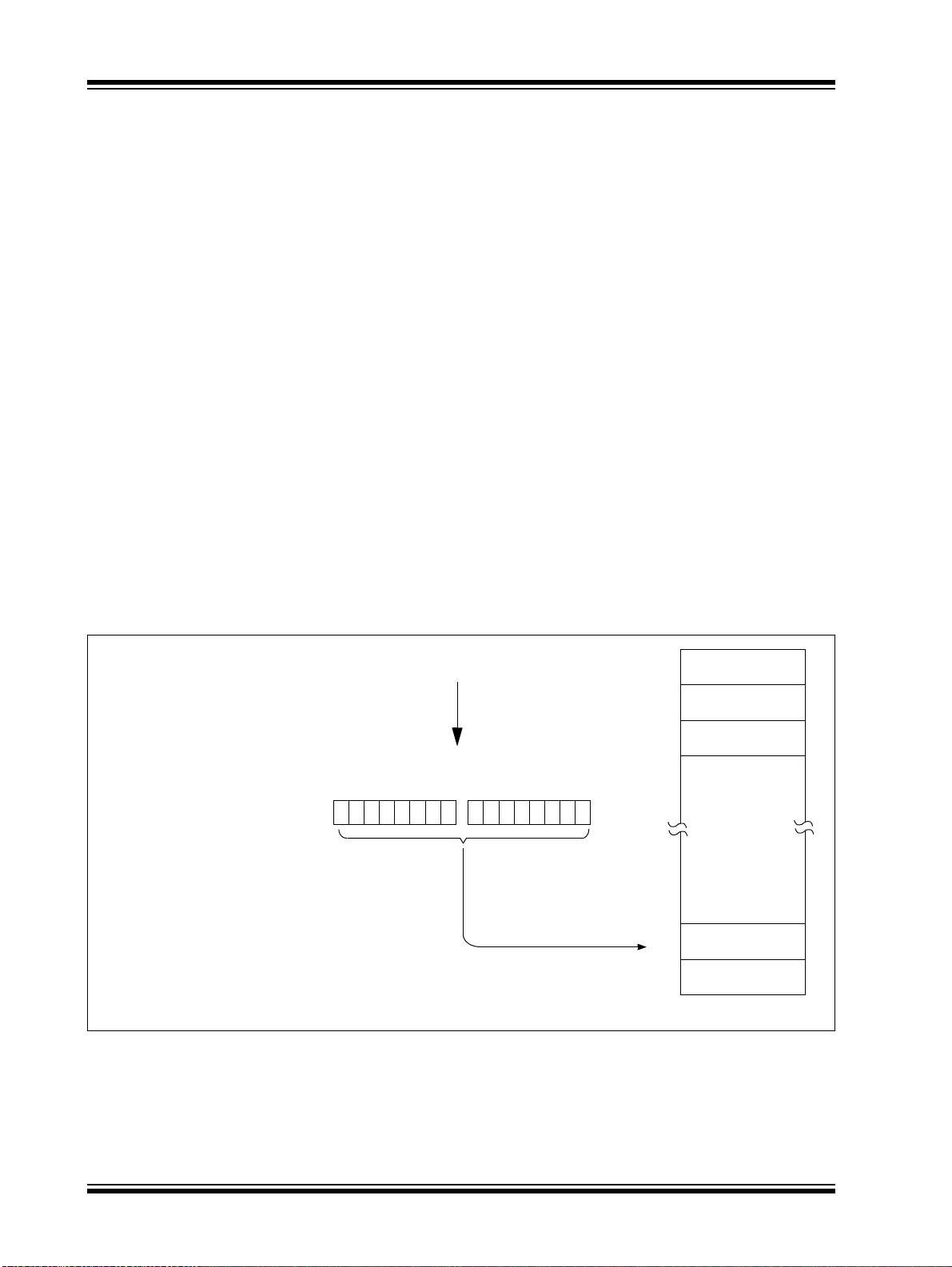

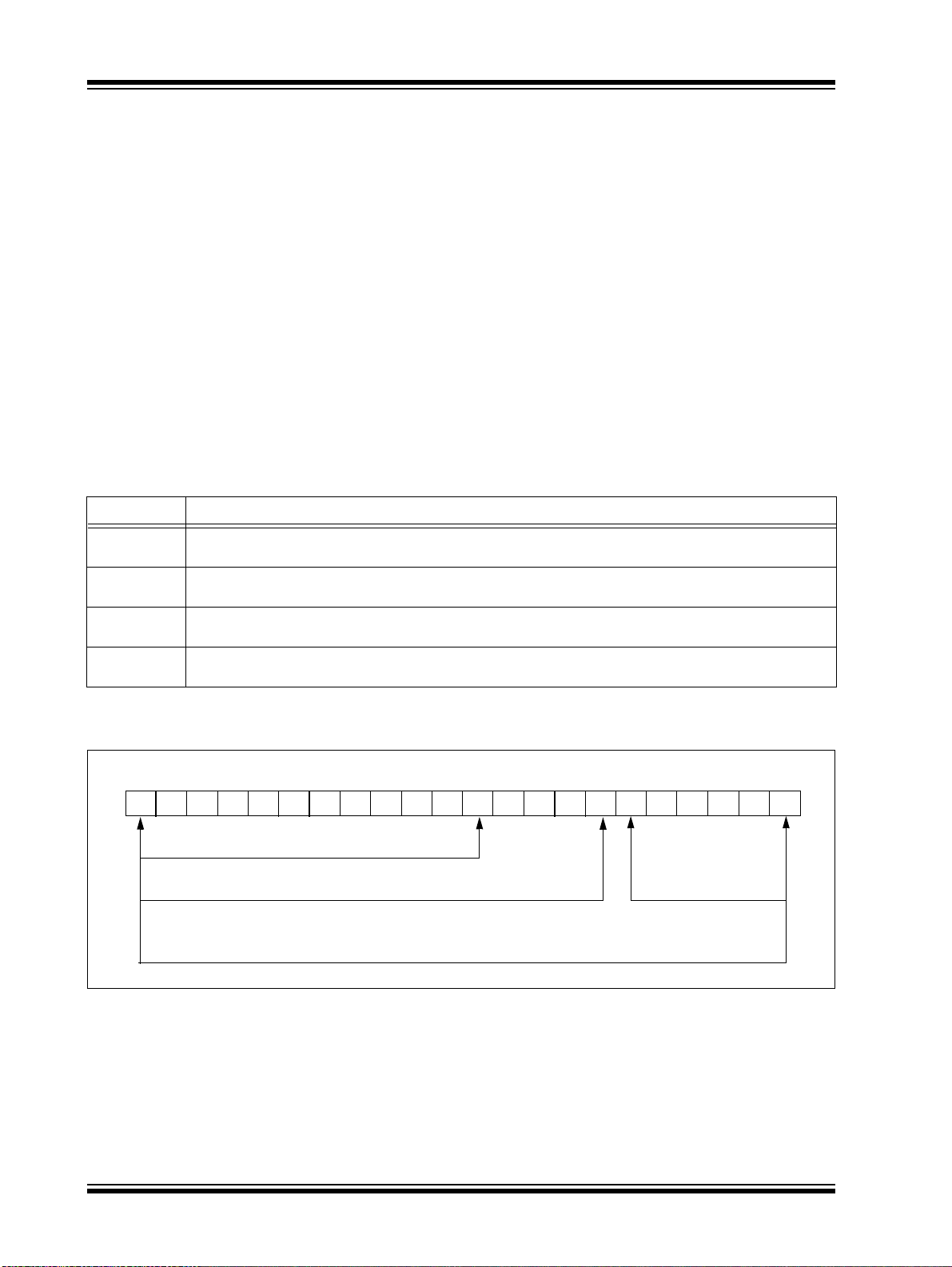

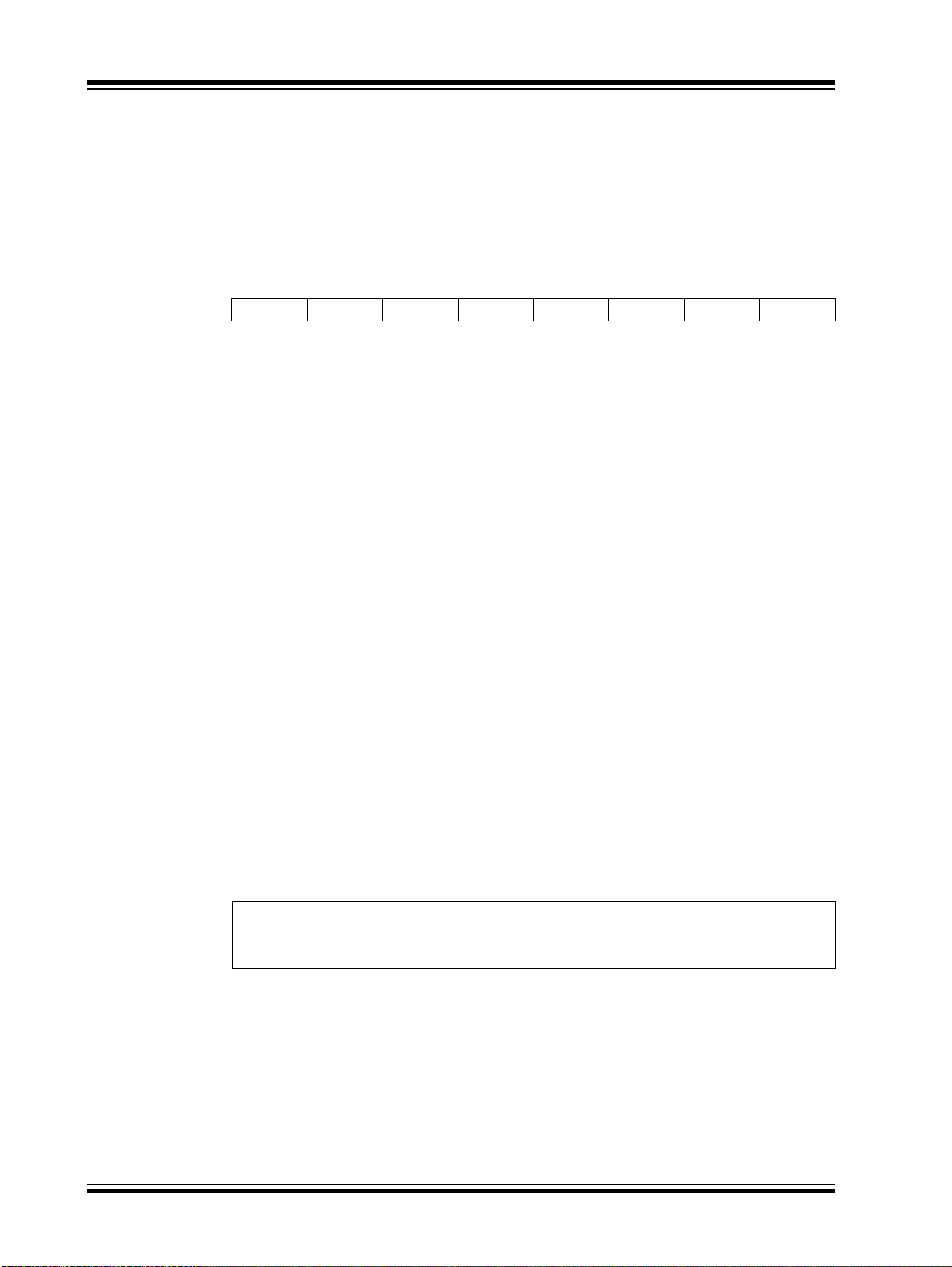

图 1-1: PIC18F24J10/25J10 (28 引脚)框图

表指针 <21>

加 / 减逻辑

地址锁存器

程序存储器

(16/32 KB)

数据锁存器

指令总线 <16>

VDDCORE

OSC1

OSC2

T1OSI

T1OSO

MCLR

V

DD,VSS

数据总线 <8>

8

8

PCLATH

20

8

内部

振荡器

模块

INTRC

振荡器

单电源

编程

在线

调试器

PCLATU

PCU

程序计数器

31 级堆栈

STKPTR

表锁存器

ROM 锁存器

IR

指令

解码和

控制

PCH PCL

状态机

控制信号

上电延时

定时器

振荡器

起振定时器

上电

复位

看门狗

定时器

欠压

复位

故障保护

时钟监视器

BITOP

(2)

21

数据锁存器

数据存储器

(1KB)

地址锁存器

数据地址 <12>

4

BSR

FSR0

FSR1

FSR2

加 / 减

逻辑

地址

译码

3

8

高精度

带隙

参考源

12

12

快速操作

存储区

PRODLPRODH

8 × 8 乘法器

W

8

8

ALU<8>

8

4

12

8

8

8

PORTA

RA0/AN0

RA1/AN1

RA2/AN2/VREF-/CVREF

RA3/AN3/VREF+

RA5/AN4/SS1

PORTB

RB0/INT0/FLT0/AN12

RB1/INT1/AN10

RB2/INT2/AN8

RB3/AN9/CCP2

RB4/KBI0/AN11

RB5/KBI1/T0CKI/C1OUT

RB6/KBI2/PGC

RB7/KBI3/PGD

PORTC

8

RC0/T1OSO/T1CKI

RC1/T1OSI/CCP2

RC2/CCP1

RC3/SCK1/SCL1

RC4/SDI1/SDA1

RC5/SDO1

RC6/TX/CK

RC7/RX/DT

/C2OUT

(1)

(1)

EUSART比较器

10 位

ADC

(2)

BOR

CCP2CCP1

注 1: 当配置位 CCP2MX 置 1 时, CCP2 与 RC1 复用;而当 CCP2MX 清零时, CCP2 与 RB3 复用。

2: PIC18LF2XJ10/4XJ10 器件不能使用欠压复位。

Timer2Timer1Timer0

MSSP

DS39682A_CN 第 10 页 高级信息 2005 Microchip Technology Inc.

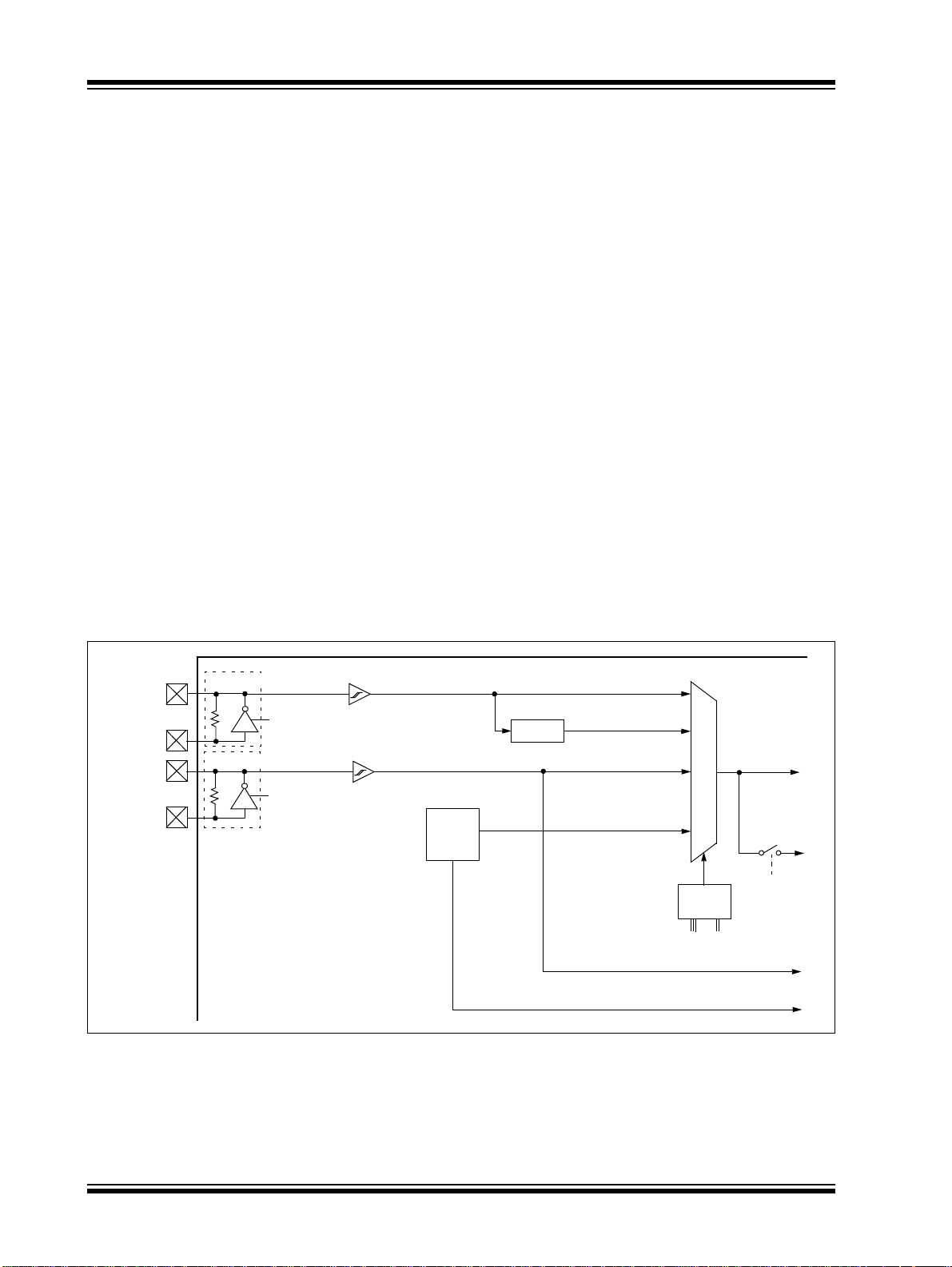

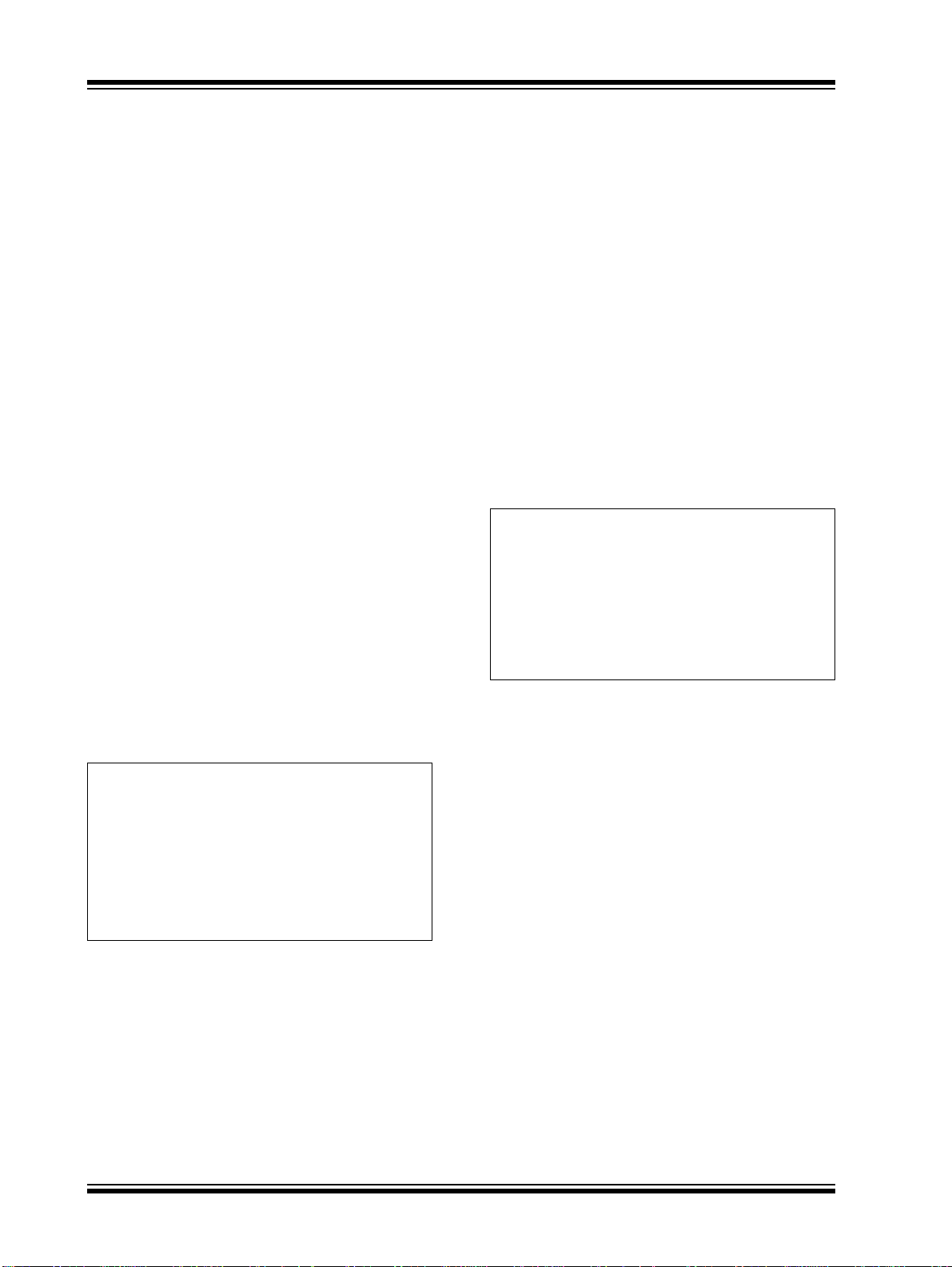

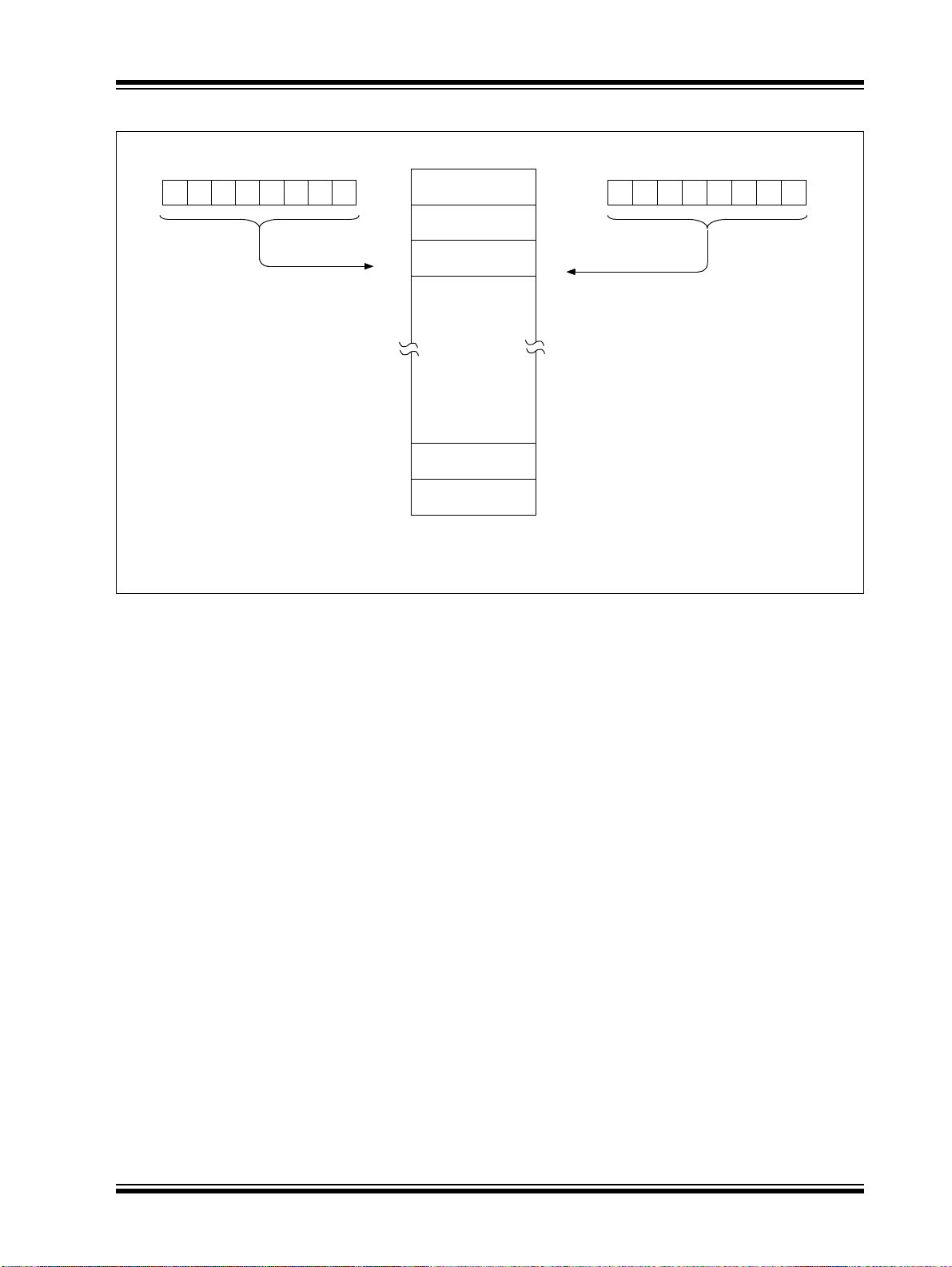

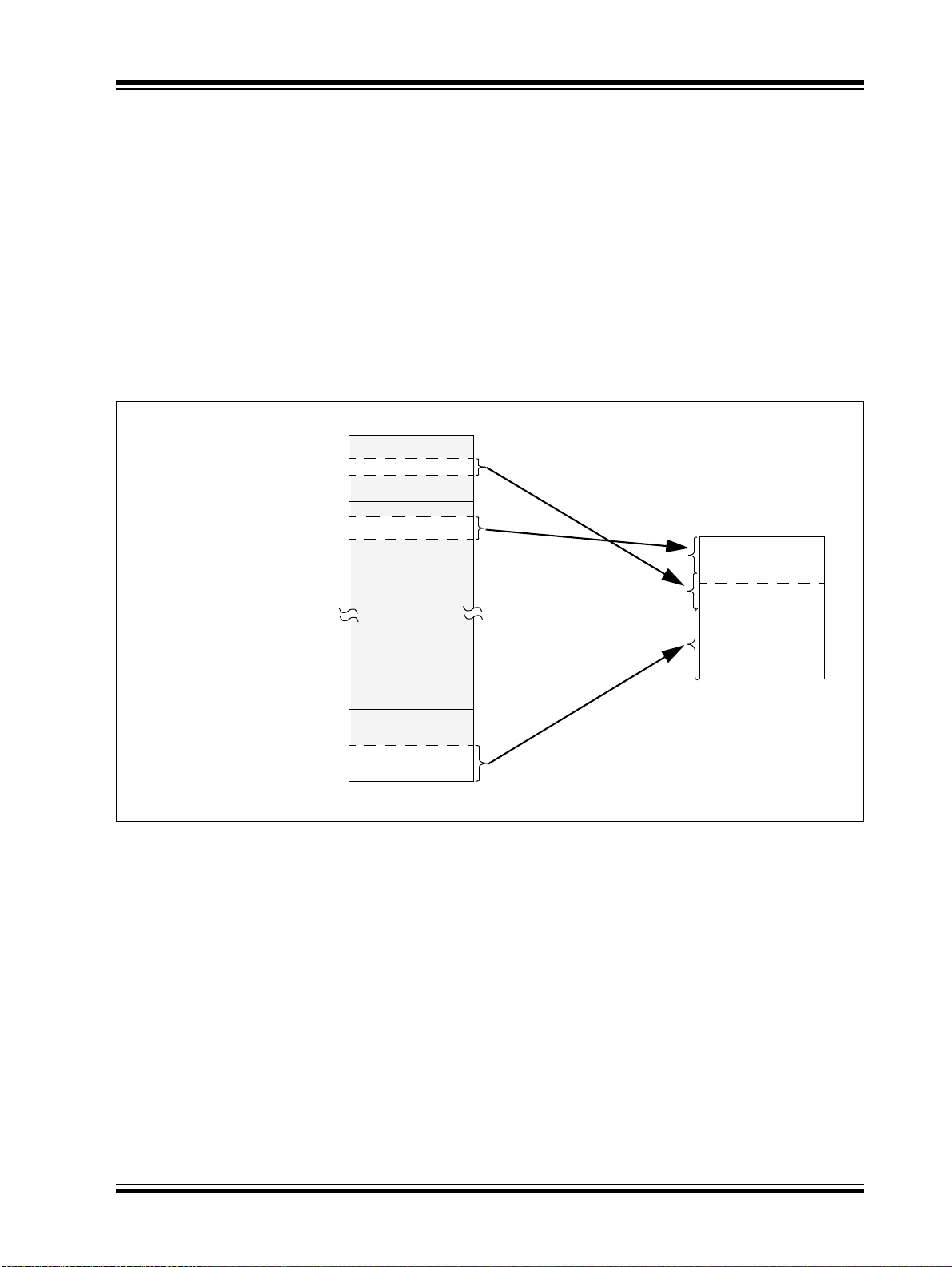

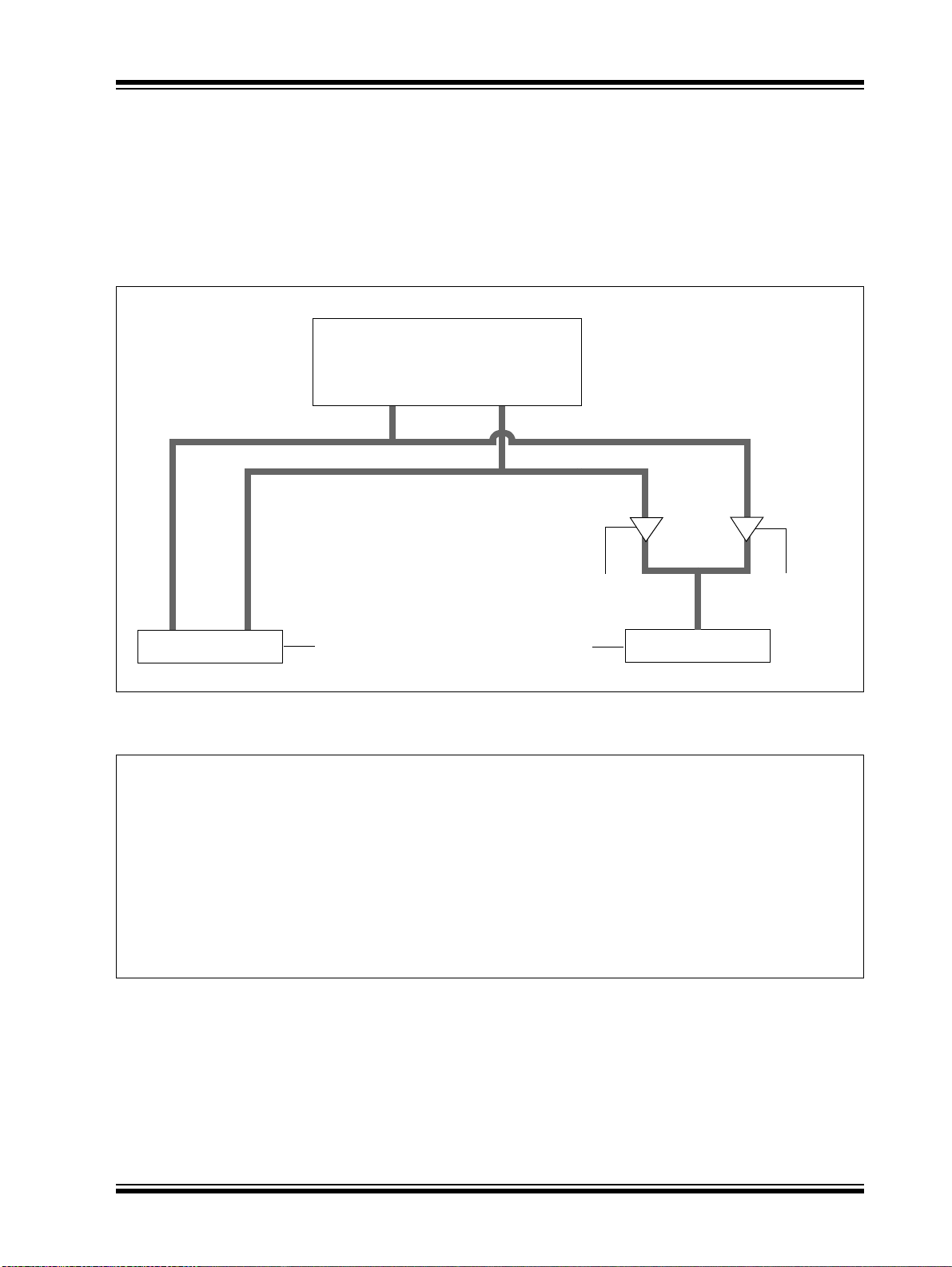

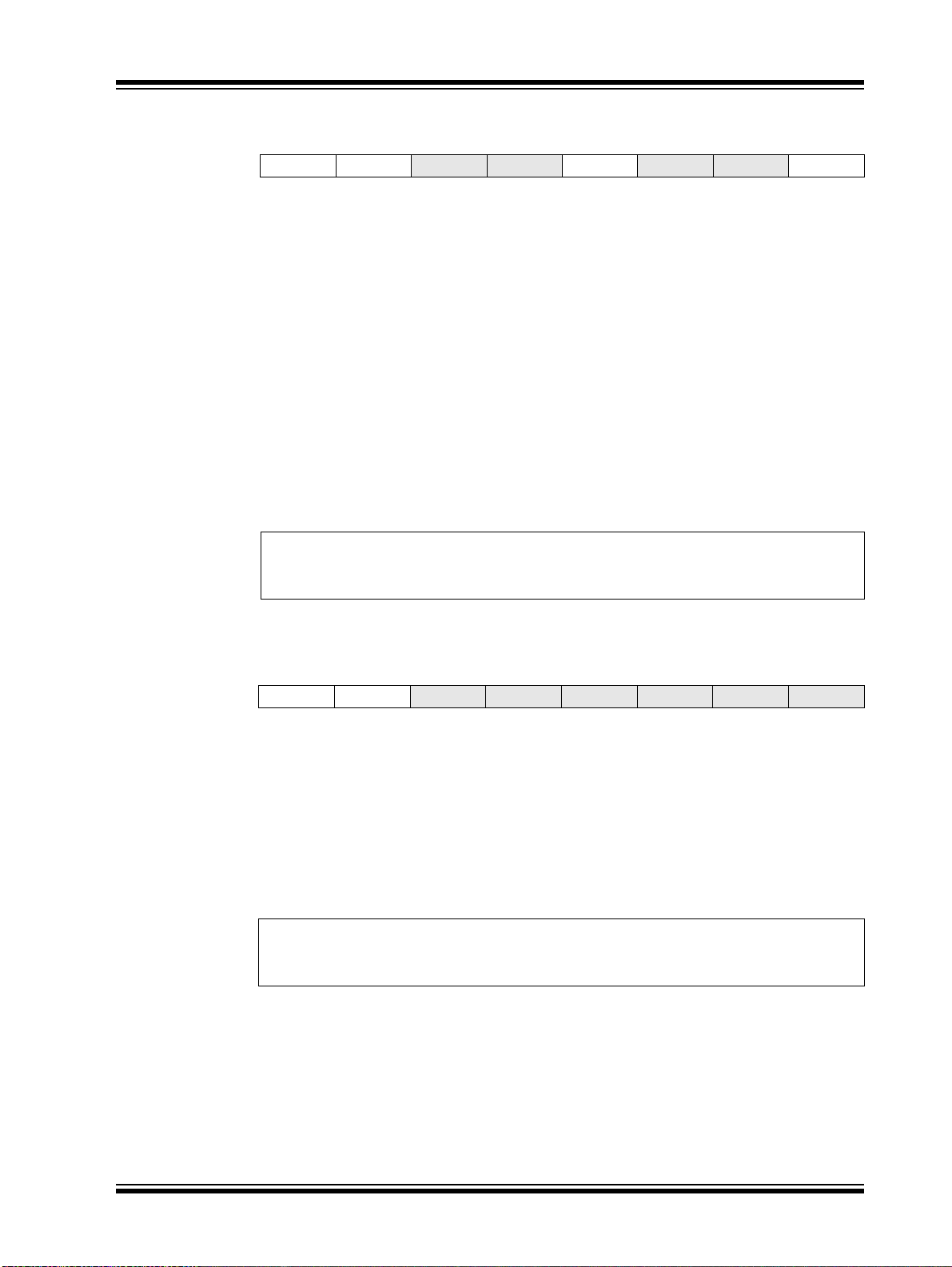

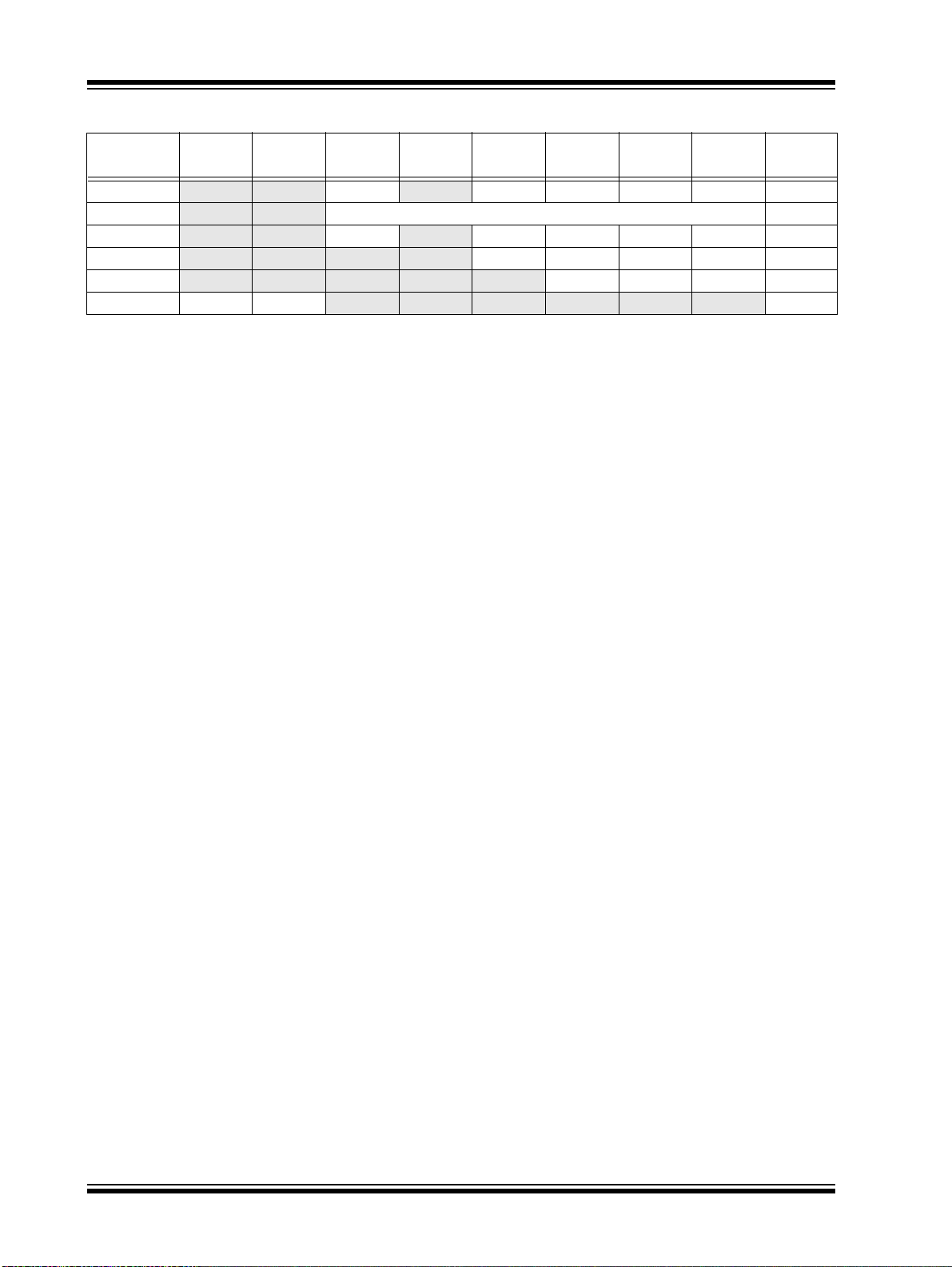

图 1-2: PIC18F44J10/45J10 (40/44 引脚)框图

PIC18F45J10 系列

表指针 <21>

加 / 减逻辑

地址锁存器

程序存储器

(16/32 KB)

数据锁存器

指令总线 <16>

VDDCORE

OSC1

OSC2

T1OSI

T1OSO

MCLR

V

DD,

SS

V

数据总线 <8>

BSR

4

3

8

高精度

带隙

参考源

数据锁存器

数据存储器

(3.9 KB)

地址锁存器

12

数据地址 <12>

12

快速操作

FSR0

存储区

FSR1

FSR2

加 / 减

逻辑

地址

译码

PRODLPRODH

8 × 8 乘法器

W

8

8

ALU<8>

8

4

12

8

8

8

8

8

8

PCLATH

20

8

内部

振荡器

模块

INTRC

振荡器

单电源

编程

在线

调试器

PCLATU

PCU

程序计数器

31 级堆栈

表锁存器

ROM 锁存器

IR

指令

解码和

控制

PCH PCL

STKPTR

起振定时器

欠压

时钟监视器

状态机

控制信号

上电延时

定时器

振荡器

上电

复位

看门狗

定时器

复位

故障保护

BITOP

(2)

21

PORTA

PORTB

PORTC

PORTD

PORTE

RA0/AN0

RA1/AN1

RA2/AN2/VREF-/CVREF

RA3/AN3/VREF+

RA5/AN4/SS1

RB0/INT0/FLT0/AN12

RB1/INT1/AN10

RB2/INT2/AN8

RB3/AN9/CCP2

RB4/KBI0/AN11

RB5/KBI1/T0CKI/C1OUT

RB6/KBI2/PGC

RB7/KBI3/PGD

RC0/T1OSO/T1CKI

RC1/T1OSI/CCP2

RC2/CCP1/P1A

RC3/SCK1/SCL1

RC4/SDI1/SDA1

RC5/SDO1

RC6/TX/CK

RC7/RX/DT

RD0/PSP0/SCK2/SCL2

RD1/PSP1/SDI2/SDA2

RD2/PSP2/SDO2

RD3/PSP3/SS2

RD4/PSP4

RD5/PSP5/P1B

RD6/PSP6/P1C

RD7/PSP7/P1D

RE0/RD/AN5

RE1/WR/AN6

RE2/CS/AN7

/C2OUT

(1)

(1)

EUSART比较器

10 位

ADC

(2)

BOR

CCP2ECCP1

注 1: 当配置位 CCP2MX 置 1 时, CCP2 与 RC1 复用;而当 CCP2MX 清零时, CCP2 与 RB3 复用。

2: PIC18LF2XJ10/4XJ10 器件不能使用欠压复位。

Timer2Timer1Timer0

MSSP

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 11 页

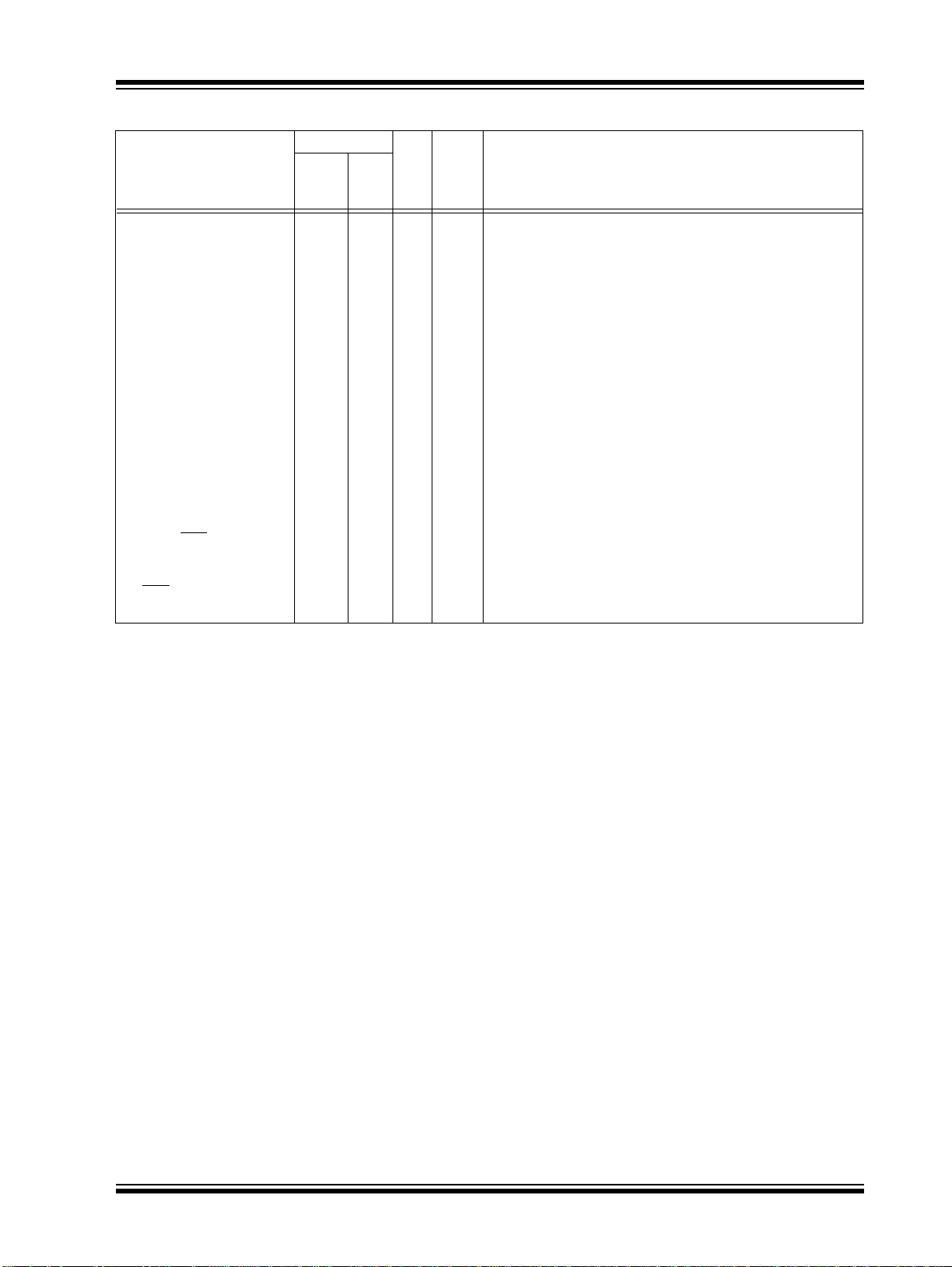

PIC18F45J10 系列

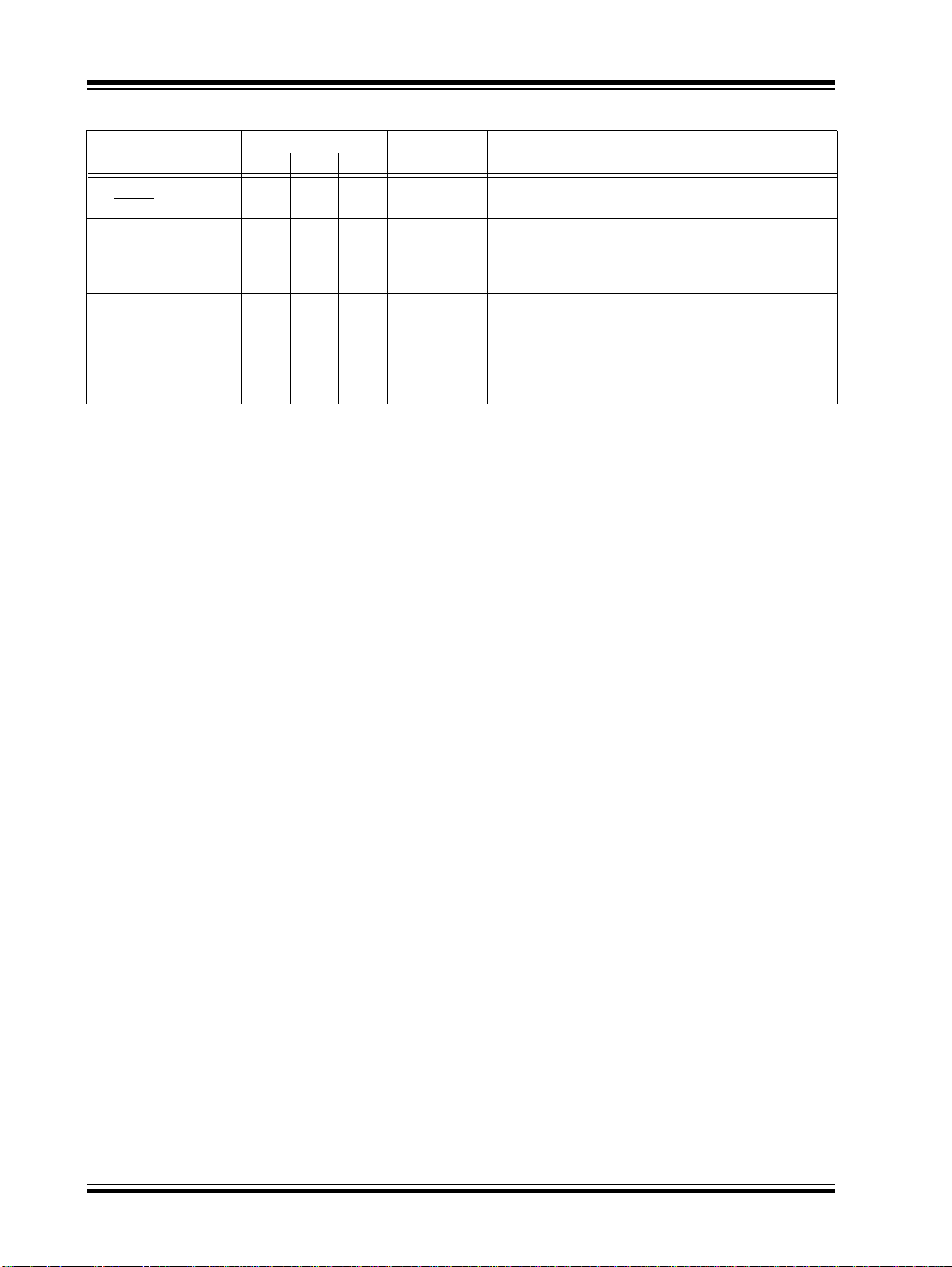

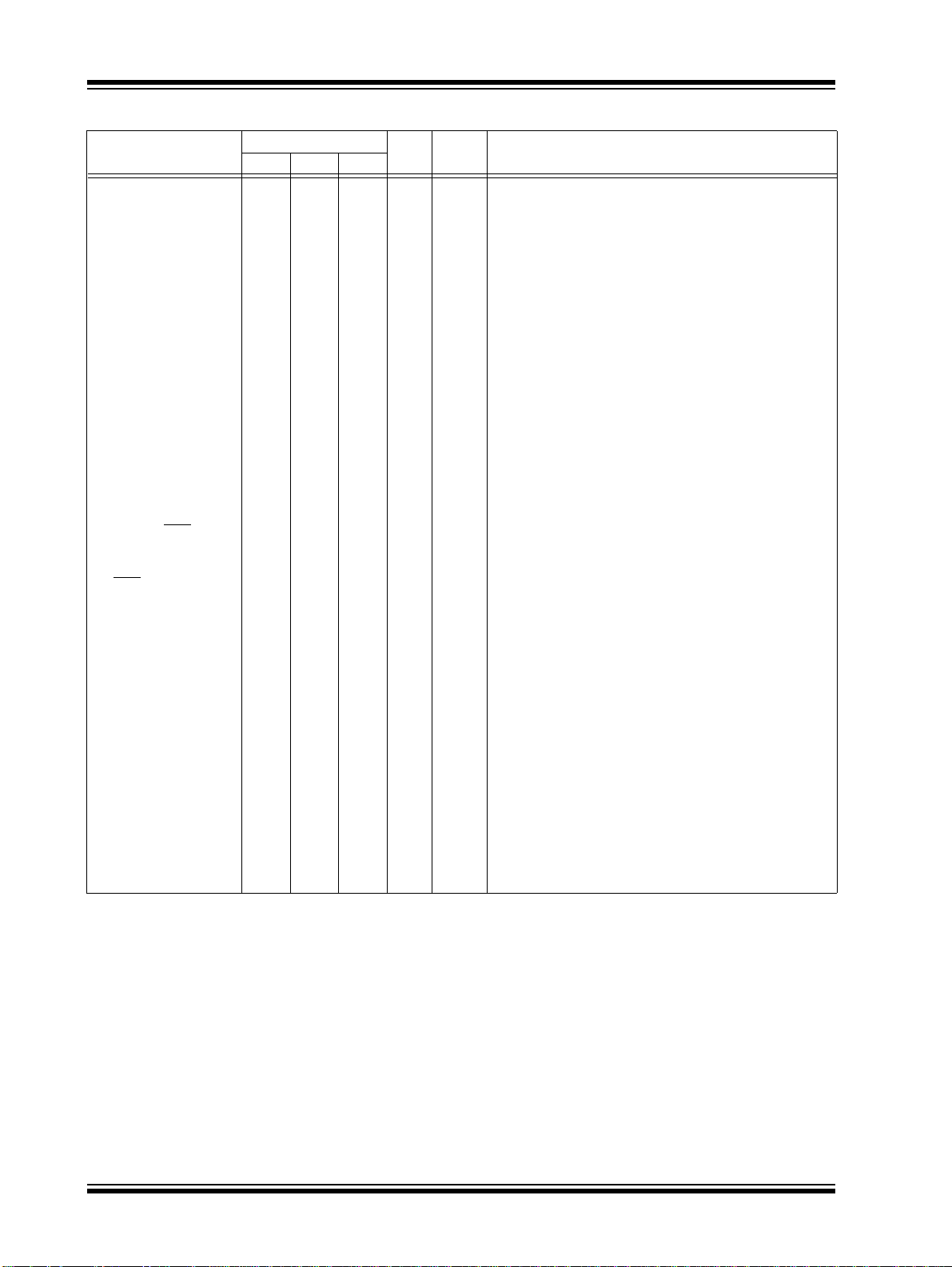

表 1-2: PIC18F24J10/25J10 I/O 引脚排列说明

引脚号

QFN

引脚类型缓冲器

类型

IST

I

I-CMOS

O

-

O

-

说明

主清零 (输入)或编程电压 (输入)。

主清零 (复位)输入。此引脚为低电平时,器件复位。

振荡器晶振或外部时钟输入。

振荡器晶振输入或外部时钟源输入。

外部时钟源输入。总是与 OSC1 引脚功能复用。 请参见

相关的 OSC2/CLKO引脚。

振荡器晶振或时钟输出。

振荡器晶振输出。在晶振模式下,该引脚与晶振或谐振

器相 连。

在 EC 模式下, OSC2 引脚输出 CLKO 振荡信号,该信

号是

OSC1 引脚上振荡信号的 4 分频,该频率等于指令周期的

倒数。

引脚名称

MCLR

MCLR

OSC1/CLKI

OSC1

CLKI

OSC2/CLKO

OSC2

CLKO

图注: TTL = TTL 兼容输入 CMOS = CMOS 兼容输入或输出

ST = CMOS 电平的施密特触发器输入 I=输入

O=输出 P=电源

注 1:当配置位 CCP2MX 置 1 时,对 CCP2 进行默认分配。

2:当配置位 CCP2MX 清零时,对 CCP2 进行其他分配。

SPDIP,

SOIC,

SSOP

126

96

10 7

DS39682A_CN 第 12 页 高级信息 2005 Microchip Technology Inc.

PIC18F45J10 系列

表 1-2: PIC18F24J10/25J10 I/O 引脚排列说明 (续)

引脚号

QFN

引脚类型缓冲器

类型

I/OITTL

模拟

I/OITTL

模拟

I/O

TTL

I

模拟

I

模拟

O

模拟

I/O

TTL

I

模拟

I

模拟

I/O

TTL

I

模拟

I

TTL

O

-

说明

PORTA 是双向 I/O 端口。

数字 I/O。

模拟输入 0。

数字 I/O。

模拟输入 1。

数字 I/O。

模拟输入 2。

A/D 参考电压 (低电平端)输入。

比较器参考电压输出。

数字 I/O。

模拟输入 3。

A/D 参考电压 (高电平端)输入。

数字 I/O。

模拟输入 4。

SPI 从动选择输入。

比较器 2 输出。

引脚名称

RA0/AN0

RA0

AN0

RA1/AN1

RA1

AN1

RA2/AN2/V

RA2

AN2

V

CVREF

RA3/AN3/V

RA3

AN3

V

RA5/AN4/SS1

RA5

AN4

SS1

C2OUT

图注: TTL = TTL 兼容输入 CMOS = CMOS 兼容输入或输出

注 1:当配置位 CCP2MX 置 1 时,对 CCP2 进行默认分配。

REF-/CVREF

REF-

REF+

REF+

/C2OUT

ST = CMOS 电平的施密特触发器输入 I=输入

O=输出 P=电源

2:当配置位 CCP2MX 清零时,对 CCP2 进行其他分配。

SPDIP,

SOIC,

SSOP

227

328

41

52

74

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 13 页

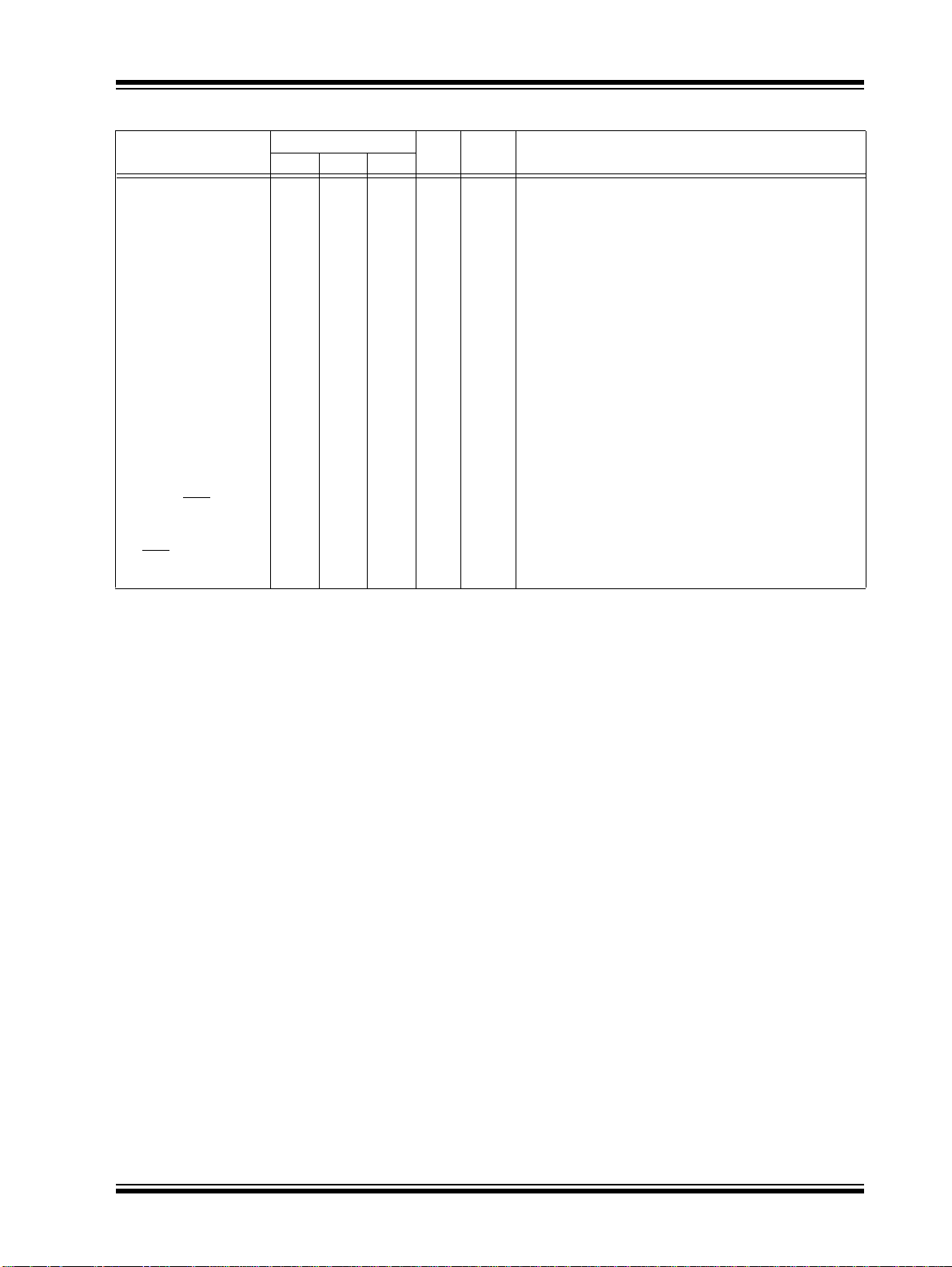

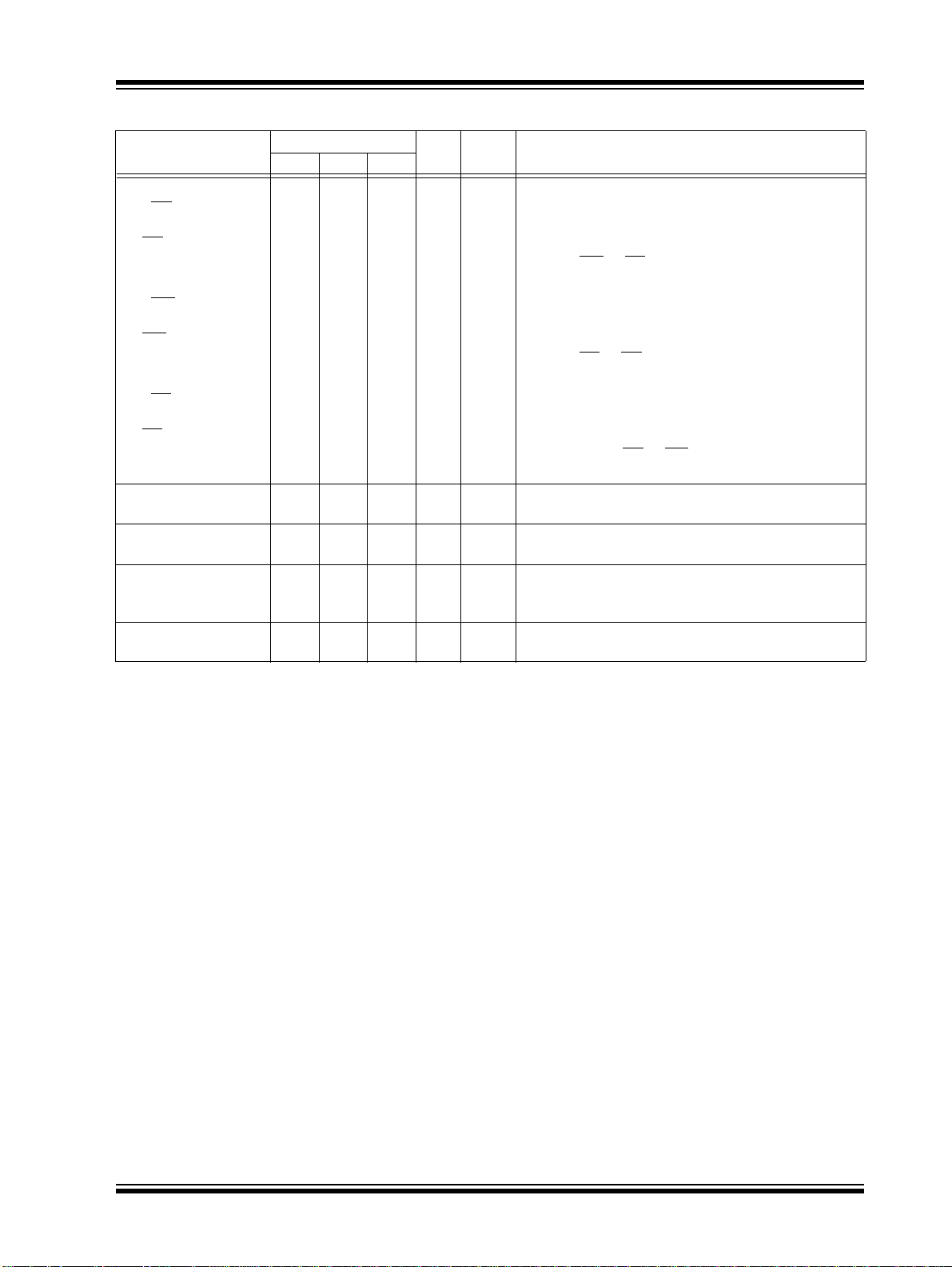

PIC18F45J10 系列

表 1-2: PIC18F24J10/25J10 I/O 引脚排列说明 (续)

引脚号

QFN

引脚类型缓冲器

类型

I/O

TTL

I

ST

I

ST

I

模拟

I/O

TTL

I

ST

I

模拟

I/O

TTL

I

ST

I

模拟

I/O

TTL

I

模拟

I/O

ST

I/O

TTL

I

TTL

I

模拟

I/O

TTL

I

TTL

I

ST

O

-

I/O

TTL

I

TTL

I/O

ST

I/O

TTL

I

TTL

I/O

ST

说明

PORTB 是双向 I/O 端口。 PORTB 在所有的输入端都可以

软件编程为内部弱上拉。

数字 I/O。

外部中断 0。

CCP1 模块 PWM 故障输入。

模拟输入 12。

数字 I/O。

外部中断 1。

模拟输入 10。

数字 I/O。

外部中断 2。

模拟输入 8。

数字 I/O。

模拟输入 9。

捕捉 2 输入 / 比较器 2 输出 /PWM2 输出。

数字 I/O。

电平变化中断引脚。

模拟输入 11 。

数字 I/O。

电平变化中断引脚。

Timer0 外部时钟输入。

比较器 1 输出。

数字 I/O。

电平变化中断引脚。

在线调试器和 ICSP™ 编程时钟引脚。

数字 I/O。

电平变化中断引脚。

在线调试器和 ICSP 编程数据引脚。

引脚名称

RB0/INT0/FLT0/AN12

RB0

INT0

FLT0

AN12

RB1/INT1/AN10

RB1

INT1

AN10

RB2/INT2/AN8

RB2

INT2

AN8

RB3/AN9/CCP2

RB3

AN9

(1)

CCP2

RB4/KBI0/AN11

RB4

KBI0

AN11

RB5/KBI1/T0CKI/C1OUT

RB5

KBI1

T0CKI

C1OUT

RB6/KBI2/PGC

RB6

KBI2

PGC

RB7/KBI3/PGD

RB7

KBI3

PGD

图注: TTL = TTL 兼容输入 CMOS = CMOS 兼容输入或输出

ST = CMOS 电平的施密特触发器输入 I=输入

O=输出 P=电源

注 1:当配置位 CCP2MX 置 1 时,对 CCP2 进行默认分配。

2:当配置位 CCP2MX 清零时,对 CCP2 进行其他分配。

SPDIP,

SOIC,

SSOP

21 18

22 19

23 20

24 21

25 22

26 23

27 24

28 25

DS39682A_CN 第 14 页 高级信息 2005 Microchip Technology Inc.

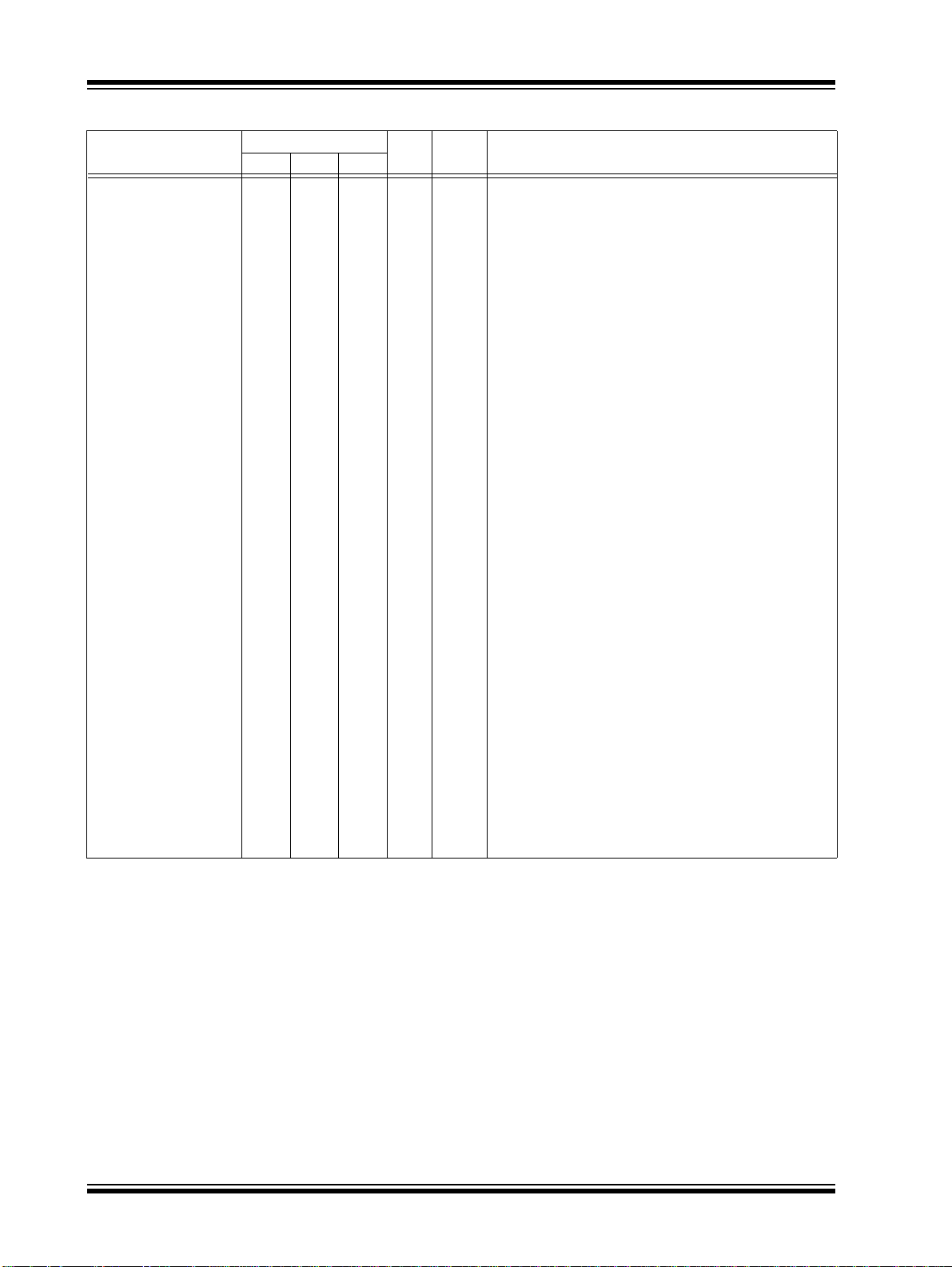

PIC18F45J10 系列

表 1-2: PIC18F24J10/25J10 I/O 引脚排列说明 (续)

引脚号

QFN

引脚类型缓冲器

类型

I/O

ST

O

-

ST

I

I/O

ST

I

模拟

ST

I/O

I/O

I/OSTST

I/O

ST

I/O

ST

I/O

ST

I/O

ST

I

ST

I/O

ST

I/OOST

-

I/O

ST

O

I/O

I/O

I/O

-

ST

ST

I

ST

ST

- 逻辑电路和 I/O 引脚的参考地。

- 逻辑电路和 I/O 引脚的正电源。

P

-

P

-

说明

PORTC 是双向 I/O 端口。

数字 I/O。

Timer1 振荡器输出。

Timer1 外部时钟输入。

数字 I/O。

Timer1 振荡器输入。

捕捉 2 输入 / 比较器 2 输出 /PWM2 输出。

数字 I/O。

捕捉 1 输入 / 比较器 1 输出 /PWM1 输出。

数字 I/O。

SPI 模式的同步串行时钟输入 / 输出。

2

C™ 模式的同步串行时钟输入 / 输出。

I

数字 I/O。

SPI 数据输入。

2

C 数据 I/O。

I

数字 I/O。

SPI 数据输出。

数字 I/O。

EUSART 异步发送。

EUSART 同步时钟 (参见相关 RX/DT 引脚)。

数字 I/O。

EUSART 异步接收。

EUSART 同步数据 (参见相关 TX/CK 引脚)。

逻辑电路和 I/O 引脚的正电源。

逻辑电路和 I/O 引脚的参考地。

引脚名称

RC0/T1OSO/T1CKI

RC0

T1OSO

T1CKI

RC1/T1OSI/CCP2

RC1

T1OSI

(2)

CCP2

RC2/CCP1

RC2

CCP1

RC3/SCK1/SCL1

RC3

SCK1

SCL1

RC4/SDI1/SDA1

RC4

SDI1

SDA1

RC5/SDO1

RC5

SDO1

RC6/TX/CK

RC6

TX

CK

RC7/RX/DT

RC7

RX

DT

SS 8, 19 5, 16 P

V

DD 20 17 P

V

V

DDCORE/VCAP

VDDCORE

VCAP

图注: TTL = TTL 兼容输入 CMOS = CMOS 兼容输入或输出

ST = CMOS 电平的施密特触发器输入 I=输入

O=输出 P=电源

注 1:当配置位 CCP2MX 置 1 时,对 CCP2 进行默认分配。

2:当配置位 CCP2MX 清零时,对 CCP2 进行其他分配。

SPDIP,

SOIC,

SSOP

11 8

12 9

13 10

14 11

15 12

16 13

17 14

18 15

63

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 15 页

PIC18F45J10 系列

表 1-3: PIC18F44J10/45J10 I/O 引脚排列说明

引脚名称

MCLR

MCLR

OSC1/CLKI

OSC1

CLKI

OSC2/CLKO

OSC2

CLKO

图注: TTL = TTL 兼容输入 CMOS = CMOS 兼容输入或输出

ST = CMOS 电平的施密特触发器输入 I=输入

O=输出 P=电源

注 1:当配置位 CCP2MX 置 1 时,对 CCP2 进行默认分配。

2:当配置位 CCP2MX 清零时,对 CCP2 进行其他分配。

引脚号

PDIP QFN TQFP

11818

13 32 30

14 33 31

引脚类型缓冲器

类型

IST

I

I-CMOS

O

O

-

-

说明

主清零 (输入)或编程电压 (输入)。

主清零 (复位)输入。此引脚为低电平时,器件复位。

振荡器晶振或外部时钟输入。

振荡器晶振输入或外部时钟源输入。

外部时钟源输入。总是与 OSC1 引脚功能复用。 参

见相关的 OSC2/CLKO引脚。

振荡器晶振或时钟输出。

振荡器晶振输出。在晶振模式下,该引脚与晶振或

谐振器相连。

在 RC 模式下, OSC2 引脚输出 CLKO 振荡信号,

该信号是 OSC1 引脚上振荡信号的 4 分频,该频率等

于指令周期的倒数。

DS39682A_CN 第 16 页 高级信息 2005 Microchip Technology Inc.

PIC18F45J10 系列

表 1-3: PIC18F44J10/45J10 I/O 引脚排列说明 (续)

引脚名称

RA0/AN0

RA0

AN0

RA1/AN1

RA1

AN1

RA2/AN2/V

RA2

AN2

V

CVREF

RA3/AN3/V

RA3

AN3

V

RA5/AN4/SS1/C2OUT

RA5

AN4

SS1

C2OUT

图注: TTL = TTL 兼容输入 CMOS = CMOS 兼容输入或输出

注 1:当配置位 CCP2MX 置 1 时,对 CCP2 进行默认分配。

REF-/CVREF

REF-

REF+

REF+

ST = CMOS 电平的施密特触发器输入 I=输入

O=输出 P=电源

2:当配置位 CCP2MX 清零时,对 CCP2 进行其他分配。

引脚号

PDIP QFN TQFP

21919

32020

42121

52222

72424

引脚类型缓冲器

类型

I/OITTL

模拟

I/OITTL

模拟

I/O

TTL

I

模拟

I

模拟

O

模拟

I/O

TTL

I

模拟

I

模拟

I/O

TTL

I

模拟

TTL

I

O

-

说明

PORTA 是双向 I/O 端口。

数字 I/O。

模拟输入 0。

数字 I/O。

模拟输入 1。

数字 I/O。

模拟输入 2。

A/D 参考电压 (低电平端)输入。

比较器参考电压输出。

数字 I/O。

模拟输入 3。

A/D 参考电压 (高电平端)输入。

数字 I/O。

模拟输入 4。

SPI 从动选择输入。

比较器 2 输出。

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 17 页

PIC18F45J10 系列

表 1-3: PIC18F44J10/45J10 I/O 引脚排列说明 (续)

引脚名称

RB0/INT0/FLT0/AN12

RB0

INT0

FLT0

AN12

RB1/INT1/AN10

RB1

INT1

AN10

RB2/INT2/AN8

RB2

INT2

AN8

RB3/AN9/CCP2

RB3

AN9

(1)

CCP2

RB4/KBI0/AN11

RB4

KBI0

AN11

RB5/KBI1/C1OUT

RB5

KBI1

C1OUT

RB6/KBI2/PGC

RB6

KBI2

PGC

RB7/KBI3/PGD

RB7

KBI3

PGD

图注: TTL = TTL 兼容输入 CMOS = CMOS 兼容输入或输出

ST = CMOS 电平的施密特触发器输入 I=输入

O=输出 P=电源

注 1:当配置位 CCP2MX 置 1 时,对 CCP2 进行默认分配。

2:当配置位 CCP2MX 清零时,对 CCP2 进行其他分配。

引脚号

PDIP QFN TQFP

33 9 8

34 10 9

35 11 10

36 12 11

37 14 14

38 15 15

39 16 16

40 17 17

引脚类型缓冲器

类型

I/O

TTL

I

ST

I

ST

I

模拟

I/O

TTL

I

ST

I

模拟

I/O

TTL

I

ST

I

模拟

I/O

TTL

I

模拟

I/O

I/O

I/O

I/O

I/O

I/O

I/O

ST

TTL

I

TTL

I

模拟

TTL

I

TTL

O

-

TTL

I

TTL

ST

TTL

I

TTL

ST

说明

PORTB 是双向 I/O 端口。 PORTB 在所有的输入端都

可以软件编程为内部弱上拉。

数字 I/O。

外部中断 0。

增强型 CCP1 模块 PWM 故障输入。

模拟输入 12。

数字 I/O。

外部中断 1。

模拟输入 10。

数字 I/O。

外部中断 2。

模拟输入 8。

数字 I/O。

模拟输入 9。

捕捉 2 输入 / 比较器 2 输出 /PWM2 输出。

数字 I/O。

电平变化中断引脚。

模拟输入 11。

数字 I/O。

电平变化中断引脚。

比较器 1 输出。

数字 I/O。

电平变化中断引脚。

在线调试器和 ICSP™ 编程时钟引脚。

数字 I/O。

电平变化中断引脚。

在线调试器和 ICSP 编程数据引脚。

DS39682A_CN 第 18 页 高级信息 2005 Microchip Technology Inc.

PIC18F45J10 系列

表 1-3: PIC18F44J10/45J10 I/O 引脚排列说明 (续)

引脚名称

RC0/T1OSO/T1CKI

RC0

T1OSO

T1CKI

RC1/T1OSI/CCP2

RC1

T1OSI

(2)

CCP2

RC2/CCP1/P1A

RC2

CCP1

P1A

RC3/SCK1/SCL1

RC3

SCK1

SCL1

RC4/SDI1/SDA1

RC4

SDI1

SDA1

RC5/SDO1

RC5

SDO1

RC6/TX/CK

RC6

TX

CK

RC7/RX/DT

RC7

RX

DT

图注: TTL = TTL 兼容输入 CMOS = CMOS 兼容输入或输出

ST = CMOS 电平的施密特触发器输入 I=输入

O=输出 P=电源

注 1:当配置位 CCP2MX 置 1 时,对 CCP2 进行默认分配。

2:当配置位 CCP2MX 清零时,对 CCP2 进行其他分配。

引脚号

PDIP QFN TQFP

15 34 32

16 35 35

17 36 36

18 37 37

23 42 42

24 43 43

25 44 44

26 1 1

引脚类型缓冲器

类型

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/OOST

I/O

I/O

I/O

I/O

ST

O

O

O

-

I

ST

ST

I

CMOS

ST

ST

ST

-

ST

ST

ST

ST

I

ST

ST

-

ST

-

ST

ST

I

ST

ST

说明

PORTC 是双向 I/O 端口。

数字 I/O。

Timer1 振荡器输出。

Timer1 外部时钟输入。

数字 I/O。

Timer1 振荡器输入。

捕捉 2 输入 / 比较器 2 输出 /PWM2 输出。

数字 I/O。

捕捉 1 输入 / 比较器 1 输出 /PWM1 输出。

增强型 CCP1 输出。

数字 I/O。

SPI 模式的同步串行时钟输入 / 输出。

2

C™ 模式的同步串行时钟输入 / 输出。

I

数字 I/O。

SPI 数据输入。

2

C 数据 I/O。

I

数字 I/O。

SPI 数据输出。

数字 I/O。

EUSART 异步发送。

EUSART 同步时钟 (参见相关 RX/DT 引脚)。

数字 I/O。

EUSART 异步接收。

EUSART 同步数据 (参见相关 TX/CK 引脚)。

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 19 页

PIC18F45J10 系列

表 1-3: PIC18F44J10/45J10 I/O 引脚排列说明 (续)

引脚名称

RD0/PSP0/SCK2/

SCL2

RD0

PSP0

SCK2

SCL2

RD1/PSP1/SDI2/SDA2

RD1

PSP1

SDI2

SDA2

RD2/PSP2/SDO2

RD2

PSP2

SDO2

RD3/PSP3/SS2

RD3

PSP3

SS2

RD4/PSP4

RD4

PSP4

RD5/PSP5/P1B

RD5

PSP5

P1B

RD6/PSP6/P1C

RD6

PSP6

P1C

RD7/PSP7/P1D

RD7

PSP7

P1D

图注: TTL = TTL 兼容输入 CMOS = CMOS 兼容输入或输出

ST = CMOS 电平的施密特触发器输入 I=输入

O=输出 P=电源

注 1:当配置位 CCP2MX 置 1 时,对 CCP2 进行默认分配。

2:当配置位 CCP2MX 清零时,对 CCP2 进行其他分配。

引脚号

PDIP QFN TQFP

19 38 38

20 39 39

21 40 40

22 41 41

27 2 2

28 3 3

29 4 4

30 5 5

引脚类型缓冲器

类型

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/OSTTTL

I/O

I/O

I/O

I/O

I/O

I/O

ST

TTL

ST

ST

ST

TTL

I

ST

ST

ST

TTL

O

O

O

O

-

ST

TTL

I

TTL

ST

TTL

-

ST

TTL

-

ST

TTL

-

说明

PORTD 是双向 I/O 端口或与微处理器连接的并行从动

端口 (Parallel Slave Port, PSP)。当使能 PSP 模块

时,这些引脚具有 TTL 输入缓冲器。

数字 I/O。

并行从动端口数据。

SPI 模式的同步串行时钟输入 / 输出。

2

C™ 模式的同步串行时钟输入 / 输出。

I

数字 I/O。

并行从动端口数据。

SPI 数据输入。

2

C 数据 I/O。

I

数字 I/O。

并行从动端口数据。

SPI 数据输出。

数字 I/O。

并行从动端口数据。

SPI 从动选择输入。

数字 I/O。

并行从动端口数据。

数字 I/O。

并行从动端口数据。

增强型 CCP1 输出。

数字 I/O。

并行从动端口数据。

增强型 CCP1 输出。

数字 I/O。

并行从动端口数据。

增强型 CCP1 输出。

DS39682A_CN 第 20 页 高级信息 2005 Microchip Technology Inc.

PIC18F45J10 系列

表 1-3: PIC18F44J10/45J10 I/O 引脚排列说明 (续)

引脚名称

RE0/RD/AN5

RE0

RD

AN5

RE1/WR

RE2/CS

V

VDD 11, 32 7, 8,

V

NC

图注: TTL = TTL 兼容输入 CMOS = CMOS 兼容输入或输出

注 1:当配置位 CCP2MX 置 1 时,对 CCP2 进行默认分配。

/AN6

RE1

WR

AN6

/AN7

RE2

CS

AN7

SS 12, 31 6, 30,

DDCORE/VCAP

VDDCORE

VCAP

ST = CMOS 电平的施密特触发器输入 I=输入

O=输出 P=电源

2:当配置位 CCP2MX 清零时,对 CCP2 进行其他分配。

引脚号

PDIP QFN TQFP

82525

92626

10 27 27

6, 29 P

31

7, 28 P

28, 29

62323

-

13 12, 13,

33, 34

引脚类型缓冲器

类型

PORTE 是双向 I/O 端口。

I/O

I/O

I/O

ST

I

TTL

I

模拟

ST

I

TTL

I

模拟

ST

I

TTL

I

模拟

- 逻辑电路和 I/O 引脚的参考地。

- 逻辑电路和 I/O 引脚的正电源。

P

P

- - 不连接。

-

-

数字 I/O。

并行从动端口读控制。

(参见 WR

模拟输入 5。

数字 I/O。

并行从动端口写控制

(参见 CS

模拟输入 6。

数字 I/O。

并行从动端口片选控制。

(参见相关的 RD

模拟输入 7。

逻辑电路和 I/O 引脚的正电源。

逻辑电路和 I/O 引脚的参考地。

说明

和 CS 引脚)。

和 RD 引脚)。

和 WR 引脚)。

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 21 页

PIC18F45J10 系列

注:

DS39682A_CN 第 22 页 高级信息 2005 Microchip Technology Inc.

PIC18F45J10 系列

2.0 振荡器配置

2.1 振荡器类型

PIC18F45J10 系列器件可以在五种不同的振荡器模式

下工作:

1. HS 高速晶振 / 谐振器

2. HSPLL 带软件 PLL 控制的高速晶振 /

谐振器

3. EC 带 F

4. ECPLL 带软件 PLL 控制的外部时钟

5. INTRC 31 kHz 内部振荡器

用户可以通过编程FOSC2:FOSC0配置位来选择这其中

的前四种模式。而第五种模式(INTRC)可能要在软件

控制下进入;也可以将它配置为器件复位时的默认模

式。

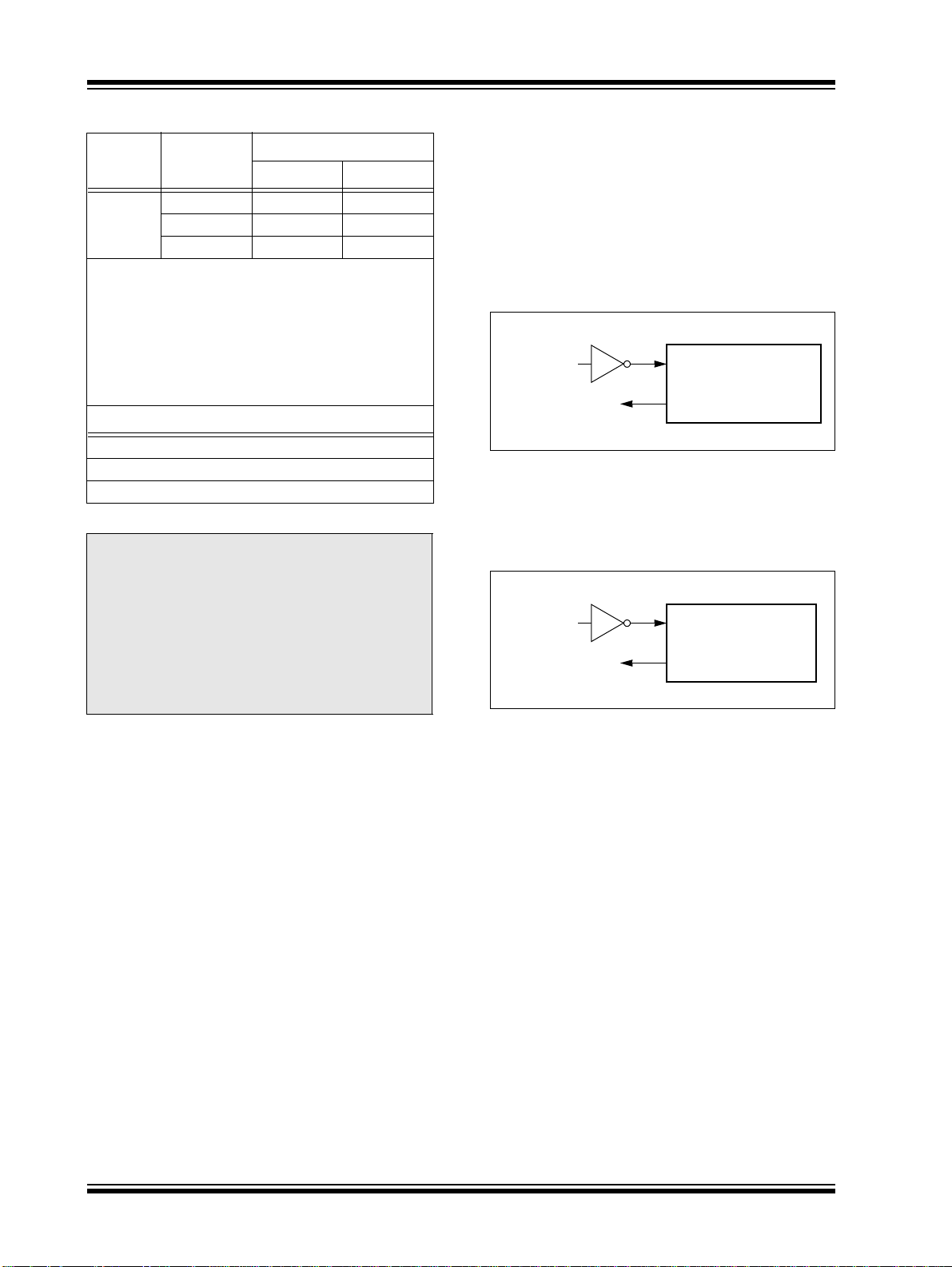

2.2 晶振 / 陶瓷谐振器 (HS 模式)

在 HS 或 HSPLL 振荡器模式中,晶振或陶瓷谐振器与

OSC1 和 OSC2 引脚连接来产生振荡。图 2-1 显示了引

脚连接方式。

振荡器的设计要求使用平行切割的晶体。

注: 使用顺序切割的晶体,会使振荡器产生的

OSC/4 输出的外部时钟

频率不在晶体制造厂商所给的参数范围

内。

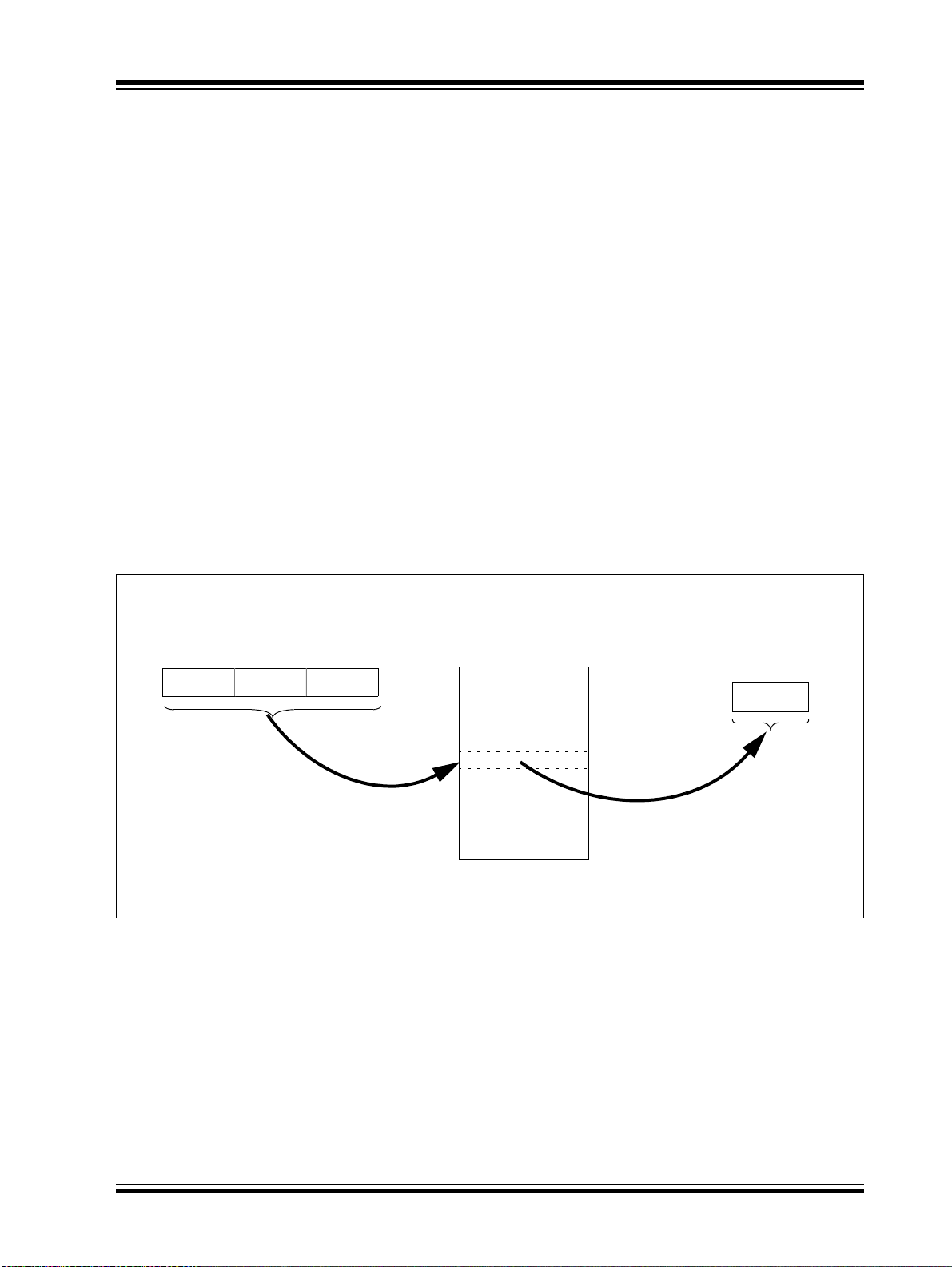

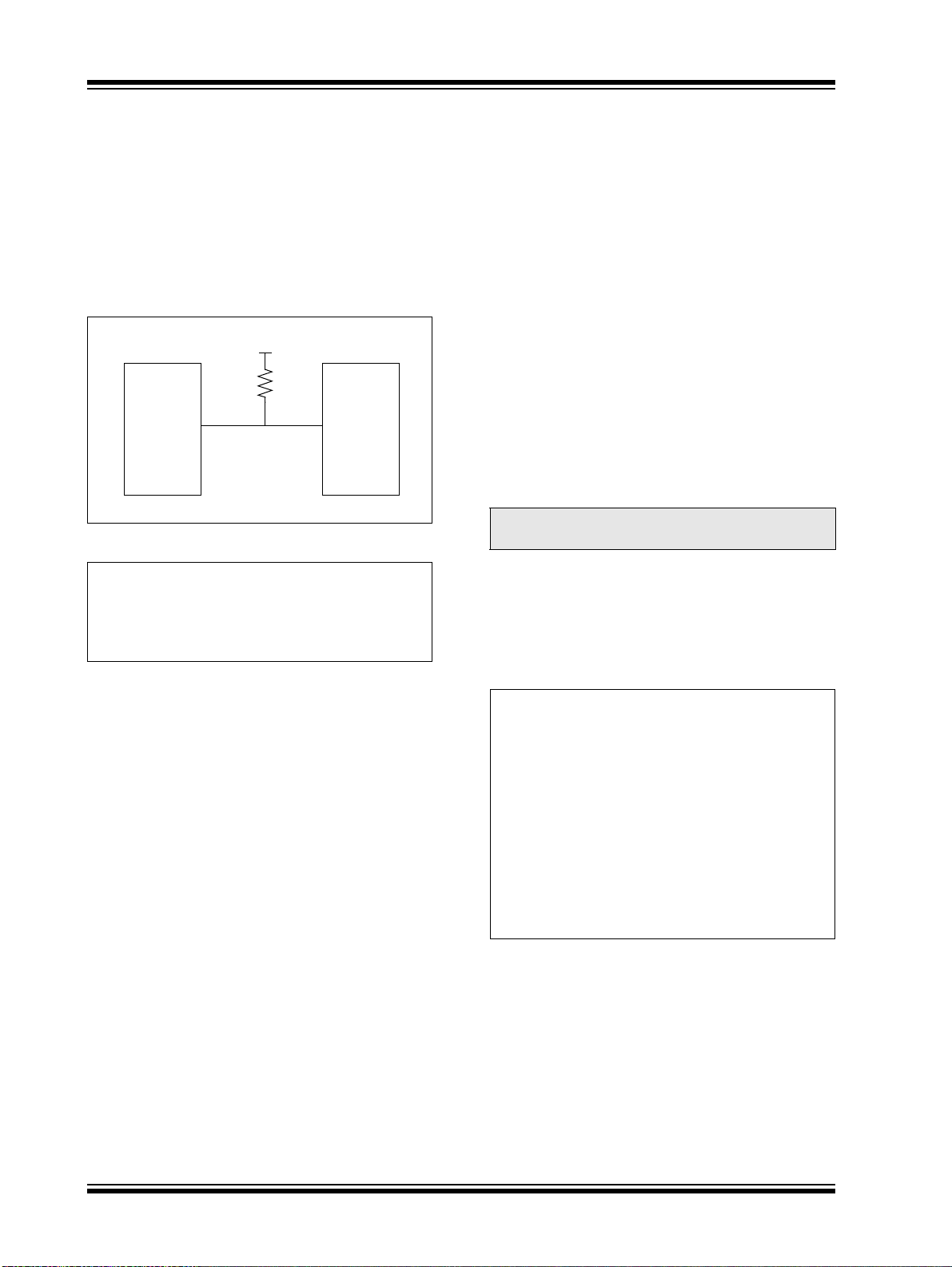

图 2-1:晶振/ 陶瓷谐振器工作原理

(HS 或 HSPLL 配置)

(1)

C1

(1)

C2

注 1: 如需了解 C1 和 C2 的初始值,请参见表 2-1 和

表 2-2。

2: AT 条形切割的晶体可能会需要一个串联电阻

(R

3: R

OSC1

XTAL

OSC2

(2)

RS

S)。

F 的值根据所选择的振荡器模式而定。

RF

(3)

休眠模式

PIC18F45J10

至

内部逻

辑电路

表 2-1: 陶瓷谐振器的电容选择

使用的典型电容值:

模式 频率

HS 8.0 MHz

16.0 MHz

上述电容值仅供设计参考。

已在下列谐振器的基本起振和工作过程中测试了这些

电容。这些值不是最佳值。

要得到合适的振荡器工作状况,可能需要不同的电容

值。用户应在应用的预期 V

器的性能。

欲知更多信息,请参见表 2-2 后的 “注”。

所使用的谐振器:

16.0 MHz

OSC1 OSC2

27 pF

22 pF

DD 和温度范围内测试振荡

4.0 MHz

8.0 MHz

27 pF

22 pF

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 23 页

PIC18F45J10 系列

表 2-2: 晶振的电容选择

振荡器类

型

HS 4 MHz 27 pF 27 pF

上述电容值仅供设计参考。

已在下列晶振的基本起振和运行过程中测试了这些电

容。这些值不是最佳值。

要得到合适的振荡器工作状况,可能需要不同的电容

值。用户应在应用的预期 V

器的性能。

欲知更多信息,请参见本表后的 “注”。

注 1: 较高的电容值可以增加振荡器的稳定性,

2: 因为每种谐振器 / 晶振都有其自身特性,

3: 为避免对低驱动电平规格的晶体造成过驱

4: 请在应用中的预期 V

晶振

频率

8 MHz 22 pF 22 pF

20 MHz 15 pF 15 pF

所使用的晶振:

但同时也会增加起振时间。

用户应当向谐振器 / 晶振制造厂商询问外

部元件的相应值。

动,可能会需要使用电阻 Rs。

振荡器的性能。

已测试的典型电容值:

C1 C2

DD 和温度范围内测试振荡

4 MHz

8 MHz

20 MHz

DD 和温度范围内验证

2.3 外部时钟输入 (EC 模式)

EC 和 ECPLL 振荡器模式需要在 OSC1 引脚连接一个

外部时钟源。在上电复位后或从休眠模式退出后,不需

要振荡器起振时间。

在 EC 振荡器模式下,振荡器频率的 4 分频信号可由

OSC2 引脚输出。此信号可用于测试或同步其他逻辑。

图 2-2 显示了 EC 振荡器模式的引脚连接方式。

图 2-2: 外部时钟输入工作原理

(EC 配置)

来自外部系

统的时钟

OSC/4

F

如图 2-3 所示,在 HS 模式下,OSC1 引脚也可以连接

外部时钟源。在此配置中, OSC2 引脚上的 4 分频输出

不可用。

图 2-3: 外部时钟输入工作原理

来自外部系

统的时钟

开路

OSC1/CLKI

PIC18F45J10

OSC2/CLKO

(HS 振荡器配置)

OSC1

PIC18F45J10

OSC2

(HS 模式)

DS39682A_CN 第 24 页 高级信息 2005 Microchip Technology Inc.

PIC18F45J10 系列

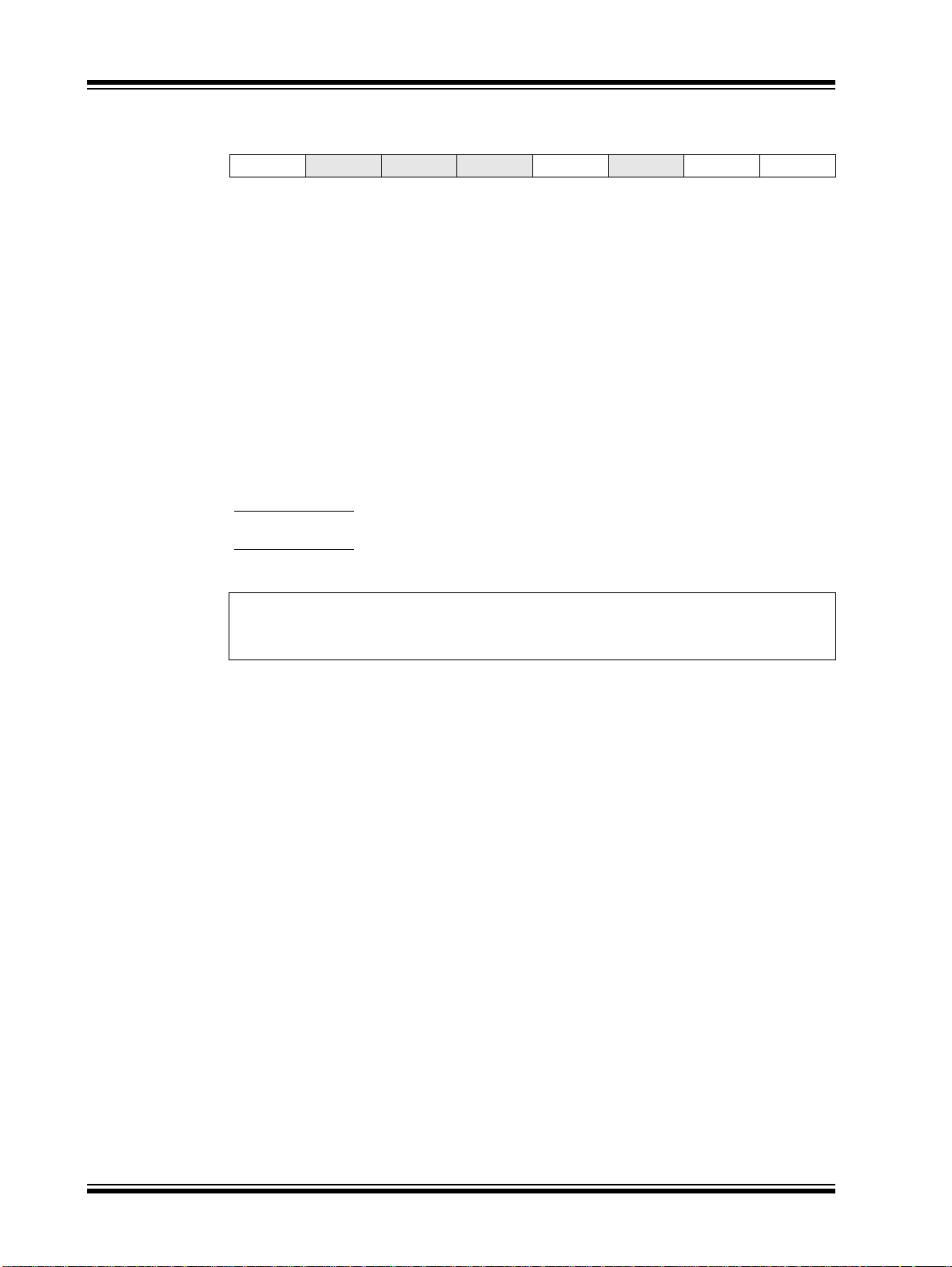

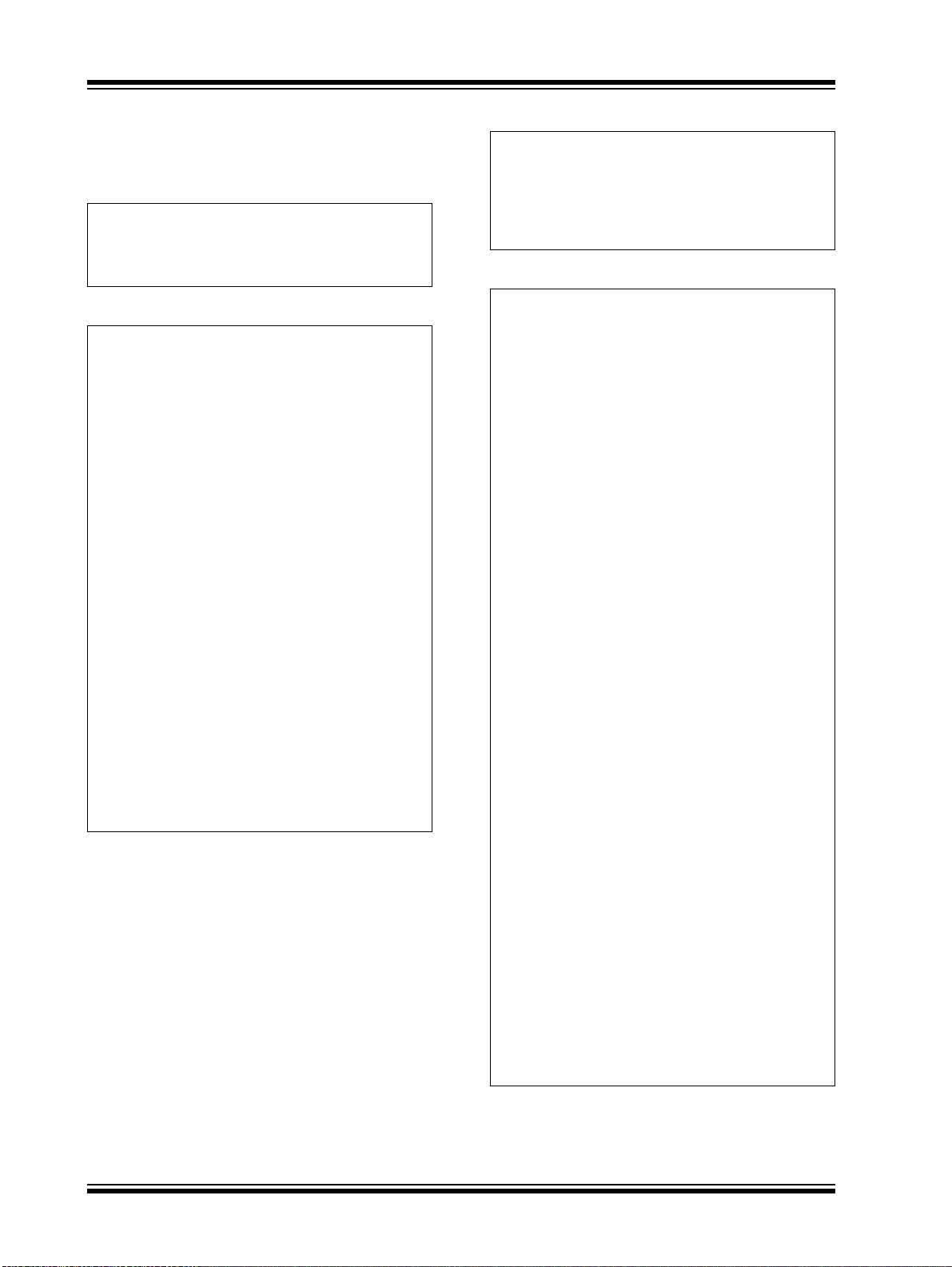

2.4 PLL 倍频器

如果用户希望使用低频晶振电路或通过晶振将器件频率

调节至其最高额定频率,可以选择使用锁相环 (Phase

Locked Loop,PLL)电路。对于担心高频晶振引起 EMI

或需要内部振荡器提供高速时钟的用户而言,这样做可

能会有用。 由于这些原因,提供了 HSPLL 和 ECPLL 模

式。

HSPLL 和 ECPLL 模式使器件能够有选择性地以外部振

荡源的 4 倍速运行以产生最高为 40 MHz 的频率。通过

在 OSCTUNE 寄存器(寄存器 2-1)中将 PLLEN 位置

1 来使能 PLL。

寄存器 2-1: OSCTUNE:PLL 控制寄存器

U-0 R/W-0

- PLLEN

bit 7 bit 0

(1)

(1)

U-0 U-0 U-0 U-0 U-0 U-0

- - - - - -

图 2-4: PLL 框图

HSPLL 或 ECPLL(CONFIG2L)

PLL 使能(OSCTUNE)

OSC2

OSC1

HS 或 EC

模式

IN

F

FOUT

÷4

相位

比较器

环路

滤波器

VCO

系统时钟

MUX

bit 7

bit 6

bit 5-0

未用:读为 0

PLLEN:倍频器 PLL 使能位

(1)

1 =PLL已使能

0 =PLL已禁止

注 1: 用于 ECPLL 和 HSPLL 振荡器配置,否则,此位不可用并读为 0。

未用:读为 0

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 10 = 清零 x = 未知

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 25 页

PIC18F45J10 系列

2.5 内部振荡器电路

PIC18F45J10 系列器件包含内部振荡源(INTRC),它

提供标称频率为 31 kHz 的输出。INTRC 在器件上电时

使能并在器件配置周期期间作为器件时钟源,直至器件

进入工作模式。如果选择 INTRC 作为器件时钟源或者

使能了以下各项之一也会使能 INTRC:

• 故障保护时钟监视器

• 看门狗定时器

• 双速启动

在第 20.0 节“CPU 的特殊性能”中对这些功能进行了

更详细的讨论。

也可以通过将 FOSC2 配置位置 1 把INTRC 配置为器件

启动时的默认时钟源。这将在第 2.6.1 节“振荡器控制

寄存器”中进行讨论。

2.6 时钟源和振荡器切换

PIC18F45J10 系列提供的功能包括允许将器件时钟源

从主振荡器切换到备用时钟源。PIC18F45J10 系列器件

提供了两种备用时钟源。当备用时钟源使能时,各种功

耗管理工作模式都可用。

基本上,这些器件有三种时钟源:

• 主振荡器

• 辅助振荡器

• 内部振荡器

主振荡器包括外部晶振和谐振器模式以及外部时钟模

式。特定的模式由 FOSC2:FOSC0 配置位定义。这些模

式的具体情况已在本章前面的内容中作过介绍。

辅助振荡器是不与 OSC1 或OSC2 引脚连接的外部时钟

源。这些时钟源即使在控制器处于功耗管理模式时仍然

可以继续工作。

PIC18F45J10 系列器件提供 Timer1 振荡器作为辅助振

荡器。此振荡器在所有功耗管理模式中通常是实时时钟

等功能的时基。

大部分情况下,在 RC0/T1OSO/T13CKI 和 RC1/T1OSI

引脚之间接有一个 32.768 kHz 的时钟晶振。在每个引

脚与地之间同时接有负载电容。

第 11.3 节“Timer1 振荡器”中将对 Timer1 振荡器作

更详细的讨论。

除了作为主时钟源之外,内部振荡器还可以作为功耗管

理模式的时钟源。INTRC 源也可以作为几种特殊功能部

件的时钟源,例如 WDT 和故障保护时钟监视器。

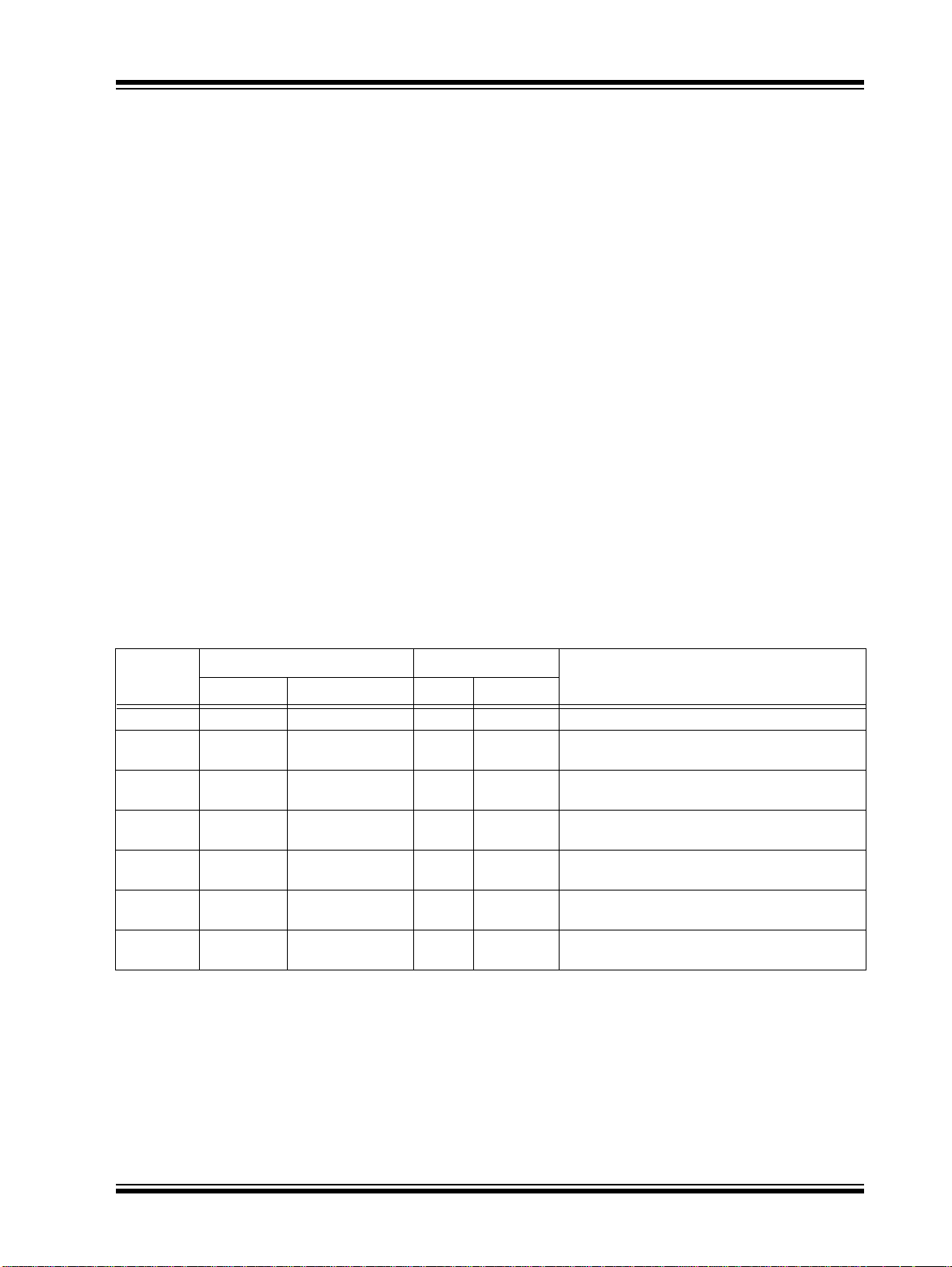

图 2-5 中所示为 PIC18F45J10 系列器件的时钟源。 如

需了解配置寄存器的详细信息,请参见第 20.0节“CPU

的特殊性能”。

图 2-5: PIC18F45J10 系列时钟框图

OSC2

OSC1

T1OSO

T1OSI

主振荡器

辅助振荡器

休眠模式

T1OSCEN

使能

振荡器

PIC18F45J10 系列

4 x PLL

INTRC

时钟源

HS, EC

HSPLL, ECPLL

T1OSC

内部振荡器

FOSC2:FOSC0

供其他模块使用的

时钟源选项

WDT、PWRT、FSCM

和双速启动

时钟

控制

外设

MUX

CPU

IDLEN

OSCCON<1:0>

DS39682A_CN 第 26 页 高级信息 2005 Microchip Technology Inc.

PIC18F45J10 系列

2.6.1 振荡器控制寄存器

OSCCON 寄存器 (寄存器 2-2)控制全功耗模式和功

耗管理模式下器件时钟工作的几个方面。

系统时钟选择位 SCS1:SCS0 用于选择时钟源。可用的

时钟源有主时钟(由 FOSC2:FOSC0 配置位定义)、辅

助时钟 (Timer1 振荡器)和内部振荡器。在写入一个

或多个位后,有一段短的时钟切换间隔,之后,时钟源

发生改变。

OSTS (OSCCON<3>)和 T1RUN (T1CON<6>)位

表明当前由哪个时钟源提供器件时钟。OSTS 位置 1 表

明振荡器起振定时器(OST)延时已结束,且主时钟在

主时钟模式下提供器件时钟。T1RUN 位置 1 表明 Timer1

振荡器在辅助时钟模式下提供器件时钟。在功耗管理模

式下的任何时间,这两个位中都只有一个位会被置 1。

如果这两个位都没有置 1,则当前器件时钟源是

INTRC,或者内部振荡器刚刚起振且尚未稳定。

IDLEN 位决定当执行 SLEEP 指令时,器件是进入休眠

模式还是某种空闲模式。

第 3.0 节“功耗管理模式”中将更详细地讨论 OSCCON

寄存器中的标志位和控制位的使用。

注 1: 要选择辅助时钟源,必须使能 Timer1 振荡

器。通过 将 Timer1 控制寄存器中的

T1OSCEN 位(T1CON<3>)置 1,可以

使能 Timer1 振荡器。如果未使能 Timer1

振荡器,则在执行 SLEEP 指令期间任何选

择辅助时钟源的操作都会被忽略。

2: 建议当Timer1振荡器稳定工作之后再执行

SLEEP指令,否则当 Timer1振荡器起振时

可能会发生很长的延迟。

2.6.1.1 系统时钟选择和 FOSC2 配置位

发生所有形式的复位时,SCS 位都会被清零。在器件的

默认配置中,这意味着将 FOSC1:FOSC0 (也就是 HS

或 EC 模式的一种)定义的主振荡器用作器件复位时的

主时钟源。

复位时的默认时钟配置可以随着FOSC2配置位的改变而

改变。此位的作用是在 SCS1:SCS0 = 00 时选择时钟源。

当 FOSC2 = 1(默认)时,不管何时 SCS1:SCS0 = 00,

都选择由 FOSC1:FOSC0 定义的振荡源。 当FOSC2 = 0

时,不管何时 SCS1:SCS2 = 00,都选择 INTRC 振荡器

作为时钟源。因为在复位时 SCS 位被清零,所以 FOSC2

的设置也会更改复位时的默认振荡器模式。

不管 FOSC2 的设置如何,INTRC 总是会在器件上电时

被使能。它将作为时钟源直到器件已经从存储器中装入

了它的配置值为止。此时 FOSC 配置位被读取并选择了

振荡器的工作模式。

注意主时钟或内部振荡器在任何给定时间都会有两种位

设置选项,取决于 FOSC2 的设置。

2.6.2 振荡器转换

PIC18F45J10 系列器件包含了防止在切换时钟源时发

生时钟 “毛刺”的电路。在时钟切换时,器件时钟会有

短暂的停顿。停顿的长度是旧时钟源的两个周期加上新

时钟源的三到四个周期的和。此公式假设新时钟源是稳

定的。

第 3.1.2 节“进入功耗管理模式”中对时钟转换进行了

更详细的讨论。

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 27 页

PIC18F45J10 系列

寄存器 2-2: OSCCON:振荡器控制寄存器

R/W-0 U-0 U-0 U-0 R-q

IDLEN - - - OSTS - SCS1 SCS0

bit 7 bit 0

bit 7

bit 6-4

bit 3

bit 2

bit 1-0

IDLEN:空闲使能位

1 = 在执行 SLEEP 指令时,器件进入空闲模式

0 = 在执行 SLEEP 指令时,器件进入休眠模式

未用:读为 0

OSTS:振荡器起振延时状态位

1 = 振荡器起振定时器延时已经结束;主振荡器正在运行

0 = 振荡器起振定时器正在进行延时;主振荡器尚未准备就绪

注 1: 当 HS 模式和双速启动都使能时,复位值为 0 ;否则,复位值为 1。

未用:读为 0

SCS1:SCS0:系统时钟选择位

11 = 内部振荡器

10 = 主振荡器

01 = Timer1 振荡器

FOSC2 = 1 时:

当

00 = 主振荡器

当 FOSC2 = 0 时:

00 = 内部振荡器

(1)

(1)

U-0 R/W-0 R/W-0

图注:

U = 未用位,读为 0q = 值由配置确定

-n = 上电复位时的值 R = 可读位 0 = 清零 W = 可写位

2.7 功耗管理模式对各种时钟源的影响

当选择了 PRI_IDLE 模式时,指定的主振荡器会继续运

行而不中断。对于所有其他功耗管理模式,使用 OSC1

引脚的振荡器会被禁止。OSC1 引脚(以及由振荡器使

用 OSC2 引脚)将会停止振荡。

在辅助时钟模式下(SEC_RUN和SEC_IDLE),Timer1

振荡器作为器件时钟源工作。如果需要,Timer1 振荡器

也可以运行在所有功耗管理模式下为 Timer1 或 Timer3

提供时钟源。

在 RC_RUN 和 RC_IDLE 模式下,内部振荡器提供器件

时钟。无论在何种功耗管理模式下,都可以直接使用

31 kHz 的 INTRC 输出来提供时钟或者使能它来支持多

种特殊功能部件 (欲知更多有关 WDT、故障保护时钟

监视器和双速启动的信息,请参见第 20.2 节 “看门狗

定时器 (WDT)”到第 20.5 节 “故障保护时钟监视

器”)。

如果选择了休眠模式,所有的时钟源都会停止。因为消

除了所有的晶体管切换电流,休眠模式能实现最小的器

件电流消耗 (仅泄漏电流)。

在休眠期间使能任何片上功能将会增加休眠时的电流消

耗。需要 INTRC 来支持 WDT 工作。 Timer1 振荡器可

以用来为实时时钟提供时钟源。 不需要器件时钟源的其

他功能部件也可以工作 (即 MSSP 从动器件、 PSP 和

INTn 引脚等)。第 23.2 节 “直流规范:掉电和供电电

流”列出了会明显增加电流消耗的外设。

DS39682A_CN 第 28 页 高级信息 2005 Microchip Technology Inc.

PIC18F45J10 系列

2.8 上电延时

有两个定时器控制上电延迟,这样大部分应用都无需外

接复位电路。上电延迟可以确保在器件电源稳定 (常规

环境下)且主时钟稳定工作之前器件保持复位状态。欲

知有关上电延迟的其他信息,请参见第 4.5 节“上电延

迟定时器 (PWRT)”。

第一个定时器是上电延时定时器 (PWRT),它在上电

时提供一个固定的延迟(表 23-10 中的参数 33)。它 总

是使能的。

第二个定时器是振荡器起振定时器 (OST),旨在使芯

片在晶振稳定之前保持在复位状态 (HS 模式)。 OST

通过计数 1024 个振荡周期实现此延迟,并在延迟后允

许振荡器为器件提供时钟。

在上电复位后,会有一段延迟间隔 T

的参数 38),控制器在这段时间中为执行指令做准备。

CSD (表 23-10 中

表 2-3: 休眠模式下 OSC1 和 OSC2 引脚状态

振荡器模式 OSC1 引脚 OSC2 引脚

EC, ECPLL 悬空,由外部时钟拉高 处于逻辑低电平 (输出时钟的 4 分频信

号)

HS, HSPLL 处于静态电平时,反馈反相器被禁止 处于静态电平时,反馈反相器被禁止

注: 如需了解有关由于休眠和 MCLR

复位引起的延时的信息,请参见第 4.0 节 “复位”中的表 4-2。

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 29 页

PIC18F45J10 系列

注:

DS39682A_CN 第 30 页 高级信息 2005 Microchip Technology Inc.

PIC18F45J10 系列

3.0 功耗管理模式

PIC18F45J10 系列器件提供了只需通过管理 CPU 和外

设的时钟源就可以管理功耗的功能。一般而言,降低时

钟频率和减少由时钟源驱动的电路数目会使功耗降低。

为了在应用中管理功耗,提供了三种主要的工作模式:

• 运行模式

• 空闲模式

• 休眠模式

这些模式定义了器件的哪些部分由时钟源驱动,以及以

多高的时钟速度驱动。运行和空闲模式可以使用三种可

用时钟源 (主时钟源、辅助时钟源或内部振荡器电路)

中的任意一种;而休眠模式则不使用时钟源。

®

功耗管理模式包括几种在以前的 PICmicro

的节省功耗的功能。其中之一就是在其他的 PIC18 器件

上提供的时钟切换功能,允许控制器使用 Timer1 振荡

器代替主振荡器。还包括所有 PICmicro 器件都提供的

休眠模式,在此模式下器件时钟停止。

3.1 选择功耗管理模式

选择功耗管理模式需要考虑两个因素:是否用时钟源驱

动 CPU 以及使用哪个时钟源。IDLEN 位(OSCCON<7>)

控制 CPU 的时钟驱动,而 SCS1:SCS0 位(OSCCON<1:0>)

选择时钟源。表 3-1 总结了各个模式、位设置、时钟源和

受影响的模块。

器件上提供

3.1.1 时钟源

SCS1:SCS0 位可以为功耗管理模式选择三个时钟源中

的一个。它们是:

• 主时钟,由 FOSC1:FOSC0 配置位定义

• 辅助时钟 (Timer1 振荡器)

• 内部振荡器

3.1.2 进入功耗管理模式

从一种功耗管理模式切换到另一种功耗管理模式是通过

装载 OSCCON 寄存器开始的。 SCS1:SCS0 位选择时

钟源并确定使用哪一种运行模式或空闲模式。更改这些

位将导致立即切换到新的时钟源(假定新的时钟源正在

运行)。切换也可能会遇到时钟转换延迟。第 3.1.3 节

“时钟切换和状态指示位”和其后的章节将会讨论这些

问题。

执行SLEEP指令可以触发进入功耗管理空闲模式或休眠

模式。最后实际进入哪个模式由 IDLEN 位的状态决定。

更改功耗管理模式并不总是要求设置所有这些位,这由

当前模式和将要切换到的模式决定。可以通过在发出

SLEEP指令之前 , 更改振荡器选择位或更改 IDLEN 位来

进行模式转换。如果已经正确地配置了 IDLEN 位,则只

需通过执行 SLEEP 指令就能切换到所需的模式。

表 3-1: 功耗管理模式

模式

休眠

PRI_RUN N/A 10

SEC_RUN N/A 01

RC_RUN N/A 11

PRI_IDLE 110

SEC_IDLE 101

RC_IDLE 111

注 1: 仅当执行 SLEEP 指令时, IDLEN 才反映出有效值。

IDLEN<7>

OSCCON 位 模块时钟控制

(1)

SCS1:SCS0<1:0> CPU

0 N/A

关闭 关闭 无——所有时钟被禁止

被时钟

源驱动

被时钟

源驱动

被时钟

源驱动

关闭 被时钟源驱动主时钟——HS, EC

关闭 被时钟源驱动辅助时钟——Timer1 振荡器

关闭 被时钟源驱动内部振荡器

被时钟源驱动主时钟—— HS, EC ;

被时钟源驱动辅助时钟——Timer1 振荡器

被时钟源驱动内部振荡器

外设

可用时钟和振荡器源

这是正常的全功耗运行模式

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 31 页

PIC18F45J10 系列

3.1.3 时钟切换和状态指示位

时钟源切换的延迟时间长度是旧时钟源的 2 个周期与新

时钟源的 3 到 4 个周期的和。此公式假设新时钟源是稳

定的。

OSTS (OSCCON<3>)和 T1RUN (T1CON<6>)两

个位表示当前的时钟源及其状态。通常,在给定功耗管

理模式下,这两个位中只有一个将被置 1。当 OSTS 位

被置 1 时,主时钟提供器件时钟。当 T1RUN 位被置 1

时,Timer1 振荡器提供器件时钟。如果这两个位都不置

1, INTRC 为器件提供时钟。

注: 执行 SLEEP 指令不一定会使器件进入休眠

模式。该指令充当触发条件,根据 IDLEN

位的设置,使控制器进入休眠模式或某种

空闲模式。

3.1.4 多条 SLEEP 命令

用 SLEEP 指令启动的功耗管理模式由执行这条指令时

IDLEN 位的设置决定。如果执行另一条 SLEEP 指令,器

件将进入由那时 IDLEN 位指定的功耗管理模式。如果

IDLEN 位已更改,则器件将进入由新的设置指定的功耗

管理模式。

3.2 运行模式

在运行模式中,内核和外设的时钟均有效。这些模式之

间的差异在于时钟源的不同。

3.2.2 SEC_RUN 模式

SEC_RUN 模式与其他 PIC18 器件提供的“时钟切换”

功能兼容。在此模式下,CPU 和外设由 Timer1 振荡器

提供时钟。这让用户能在仍使用高精度时钟源的情况下

实现较低的功耗。

通过将 SCS1:SCS0 位设置为 01,器件进入 SEC_RUN

模式。器件时钟源切换到 Timer1 振荡器(见图 3-1),

关闭主振荡器, T1RUN 位(T1CON<6>)置 1 并且

OSTS 位清零。

注: Timer1 振荡器应该在进入 SEC_RUN 模式

之前已经开始运行。如果当 SCS1:SCS0位

被设置为“01”时, T1OSCEN 位未置 1,

将不会进入 SEC_RUN 模式。如果 Timer1

振荡器已经被使能,但仍然没有开始运

行,器件时钟将被延迟直到振荡器起振为

止。在这种情况下,最初振荡器运行很不

稳定,并且它的运行结果无法预料。

当从 SEC_RUN 模式转换到 PRI_RUN 模式时,在主时

钟起振期间,外设和 CPU 继续使用 Timer1 振荡器作为

时钟源。当主时钟准备就绪以后,时钟切换回主时钟

(见图 3-2)。当时钟切换完成后, T1RUN 位被清零,

OSTS 位被置 1,主时钟提供器件时钟。唤醒不会影响

IDLEN 和 SCS 位。 Timer1 振荡器继续运行。

3.2.1 PRI_RUN 模式

PRI_RUN 模式是单片机的正常的全功耗工作模式。除

非使能双速启动,这也是器件复位时的默认模式 (详细

信息请参见第 20.4 节 “双速启动”)。在此模式下,

OSTS位置1(参见第 2.6.1节“振荡器控制寄存器”)。

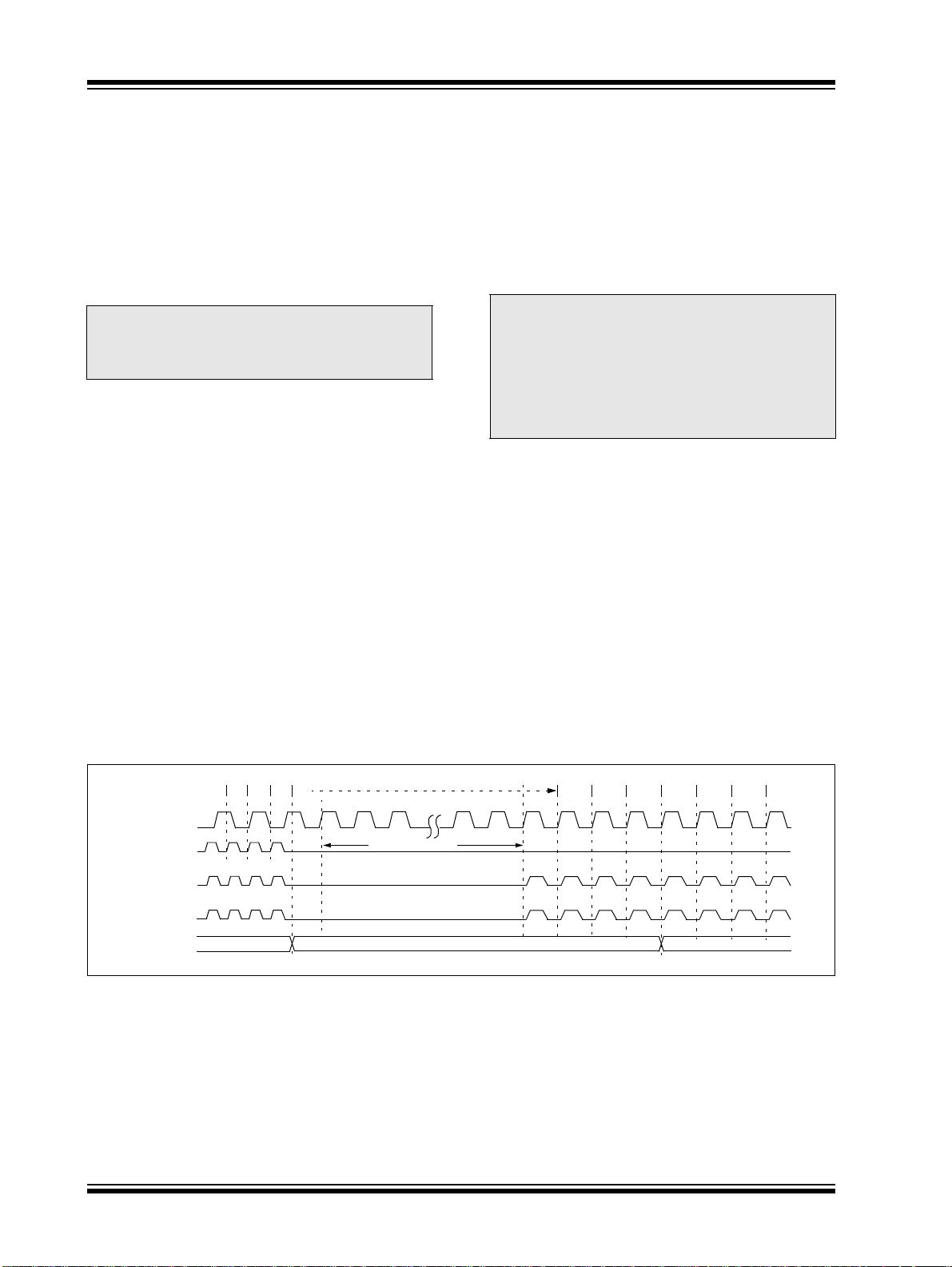

图 3-1:进入SEC_RUN 模式的转换时序

Q4Q3Q2

Q1

123

时钟转换

T1OSI

OSC1

CPU

时钟

外设

时钟

程序

计数器

Q1

Q4Q3Q2 Q1 Q3Q2

n-1

n

PC + 2PC

PC +4

DS39682A_CN 第 32 页 高级信息 2005 Microchip Technology Inc.

PIC18F45J10 系列

3.2.3 RC_RUN 模式

在 RC_RUN 模式下,使用内部振荡器作为 CPU 和外设

的时钟源;主时钟关闭。在所有运行模式之中,此模式

最节约功耗,且仍然执行代码。它非常适用于对时间精

度要求不高或者不是总需要高速时钟的应用。

通过将 SCS 设置为 “11”可以进入此模式。当时钟源

切换到 INTRC (见图 3-2)时,主振荡器关闭, OSTS

位清零。

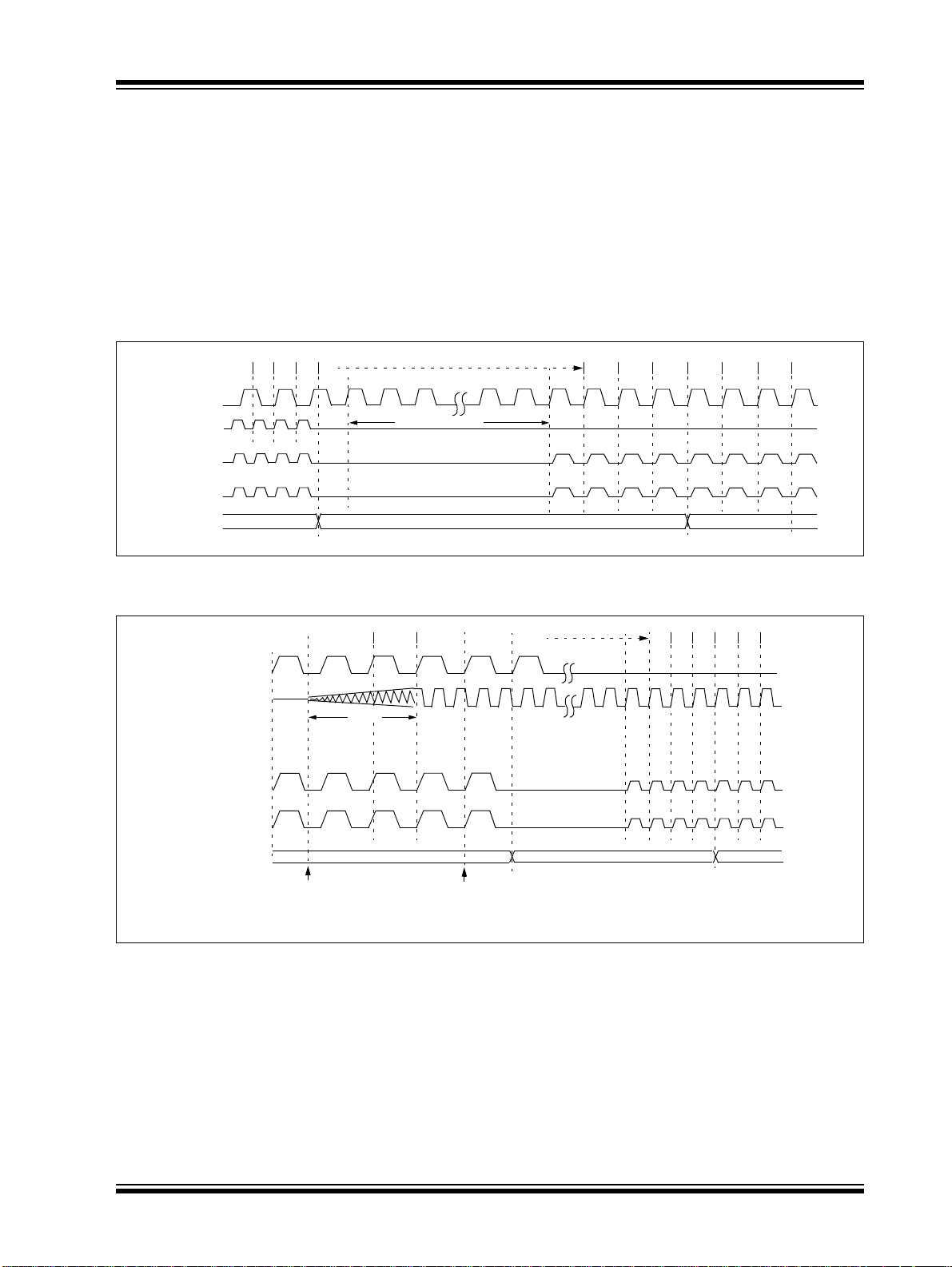

图 3-2:到RC_RUN 模式的转换时序

Q4Q3Q2

Q1

123 n-1n

时钟转换

INTRC

OSC1

CPU

时钟

外设

时钟

程序

计数器

Q1

从 RC_RUN 模式切换到 PRI_RUN 模式时,在主时钟

起振期间外设和器件继续使用 INTRC 作为时钟源。当

主时钟准备就绪以后,时钟开始切换到主时钟 (参见

图 3-3)。当时钟切换完成后,OSTS 位被置 1,主时钟

提供器件时钟。这种切换不会影响 IDLEN 和 SCS 位。

如果使能了 WDT 或故障保护时钟监视器,INTRC 时钟

源将继续运行。

Q4Q3Q2 Q1 Q3Q2

PC + 2PC

PC +4

图 3-3:从RC_RUN 模式到 PRI_RUN 模式的转换时序

Q1

Q4

Q1

INTRC

OSC1

CPU 时钟

外设

时钟

程序

计数器

SCS1:SCS0 位变化

注 1:TOST = 1024 TOSC。这些时间间隔未按比例显示。

TOST

Q2

(1)

PC

Q3

OSTS 位置 1

PC + 2

Q2

Q3 Q4

Q1

Q2

PC +4

Q3

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 33 页

PIC18F45J10 系列

3.3 休眠模式

功耗管理休眠模式与所有其他 PICmicro 器件提供的传

统休眠模式相同。通过清零 IDLEN 位 (器件复位时的

默认状态)并执行 SLEEP 指令进入该模式。 这将关闭

所选的振荡器(图 3-4)。并清零所有的时钟源状态位。

从其他模式进入休眠模式不需要时钟切换,这是因为一

旦单片机进入休眠模式就不需要时钟了。如果选择了

WDT, INTRC 时钟源将继续运行。如果使能了 Timer1

振荡器, INTRC 时钟源也将继续运行。

在休眠模式下发生唤醒事件时(由于中断、复位或 WDT

超时),器件将没有时钟源直到由 SCS1:SCS0 位选定

的时钟源准备就绪为止 (见图 3-5),或者当双速启动

或故障保护监视器被使能时,它会将内部振荡器作为时

钟源 (见第 20.0 节“CPU 的特殊性能”)。在这两种

情况下,当主时钟提供器件时钟时, OSTS 位被置 1。

唤醒不会影响 IDLEN 和 SCS 位。

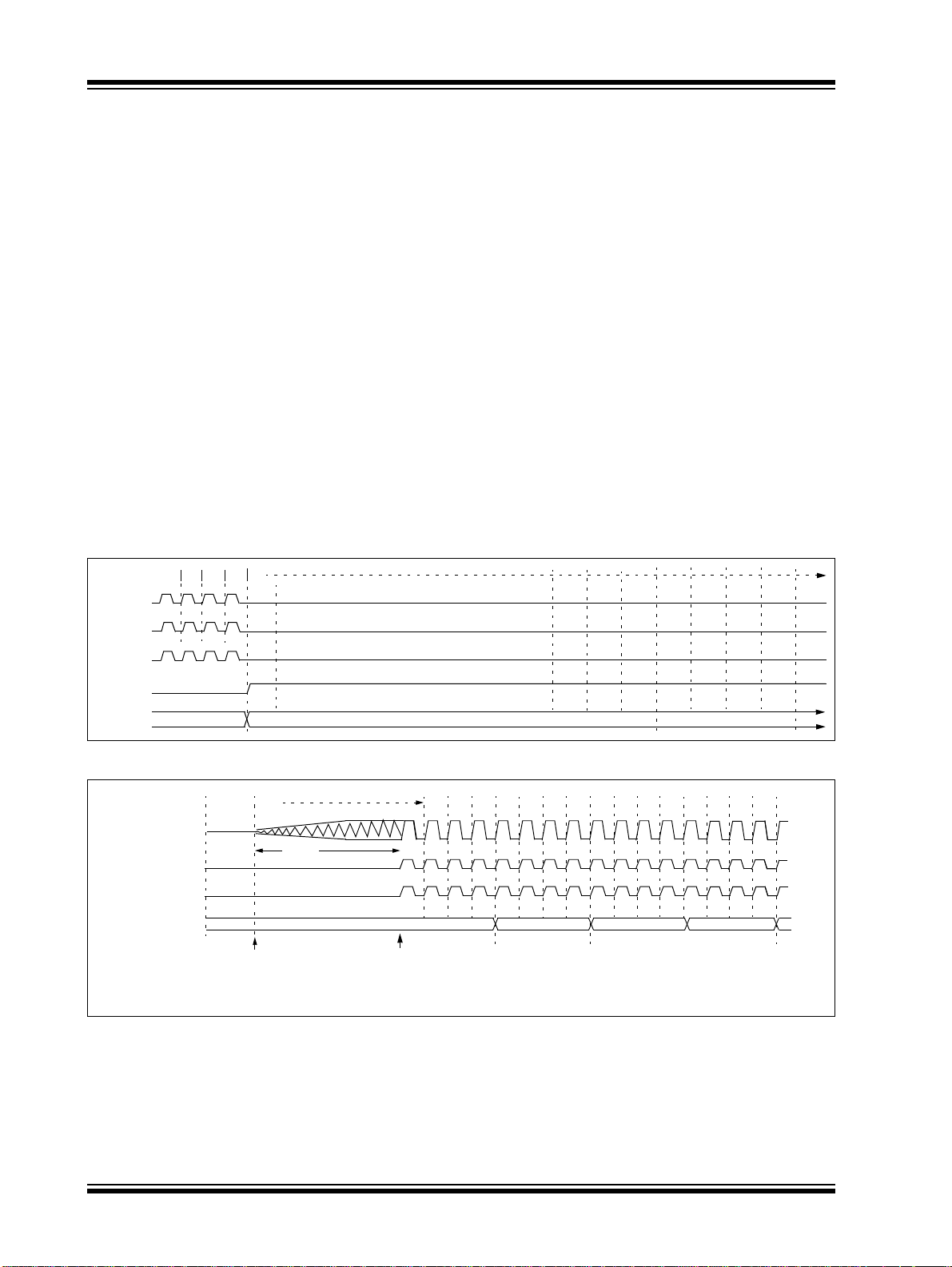

图 3-4: 进入休眠模式的转换时序

Q4Q3Q2

Q1Q1

OSC1

CPU

时钟

外设

时钟

休眠

程序

计数器

3.4 空闲模式

空闲模式允许在外设继续运行的情况下,有选择地关闭

单片机的 CPU。选择某种特定的空闲模式可使用户能进

一步管理功耗。

执行 SLEEP 指令时,如果 IDLEN 位被置 1,外设将使用

SCS1:SCS0 位选定的时钟源;然而,将不会为 CPU 提

供时钟。时钟源状态位不受影响。将 IDLEN 置 1 并执行

SLEEP 指令是一种从给定运行模式切换到其对应空闲模

式的快速方法。

如果选择了 WDT, INTRC 时钟源将继续运行。如果使

能了 Timer1 振荡器, INTRC 时钟源也将继续运行。

由于在空闲模式下 CPU 没有执行指令,只能通过中断、

WDT 超时或复位使器件从空闲模式退出。 当唤醒事件

发生时, CPU 在准备好执行代码前,要延迟一个 T

的时间(表 23-10 中的参数 38)延迟。当 CPU 开始执

行代码时,它将沿用与当前空闲模式相同的时钟源。例

如,当从 RC_IDLE 模式唤醒时,将使用内部振荡器电

路作为 CPU 和外设的时钟源(即 RC_RUN 模式)。唤

醒不会影响 IDLEN 和 SCS 位。

当处于任何空闲模式或休眠模式时, WDT 超时将导致

器件退出到由当前 SCS1:SCS0 位指定的运行模式。

PC + 2PC

CSD

图 3-5: 从休眠模式唤醒的转换时序

Q1 Q2 Q3 Q4 Q1 Q2

OSC1

(1)

TOST

CPU 时钟

外设

时钟

程序

计数器

唤醒事件

注 1:T

DS39682A_CN 第 34 页 高级信息 2005 Microchip Technology Inc.

OST = 1024 TOSC。这些时间间隔未按比例显示。

PC

OSTS 位置 1

Q3 Q4 Q1 Q2

PC + 2

PC +4

Q3 Q4

Q1 Q2 Q3 Q4

PC +6

PIC18F45J10 系列

3.4.1 PRI_IDLE 模式

此模式在三种低功耗空闲模式中是唯一不禁止器件主时

钟的。对于对时间精度要求很高的应用来说,由于时钟

源不需要 “热身”或从其他振荡器切换过来,选用此模

式可以使用更加精确的主时钟源,并以最快的速度恢复

器件运行。

通过置位 IDLEN 位并执行 SLEEP 指令可以从PRI_RUN

模式进入PRI_IDLE模式。如果器件处于其他运行模式,

请先置位 IDLEN,然后将 SCS 位置为 “10”并执行

SLEEP 指令。 虽然 CPU 被禁止,但外设仍继续使用由

FOSC0 控制位指定的主时钟源。 OSTS 位保持置 1(见

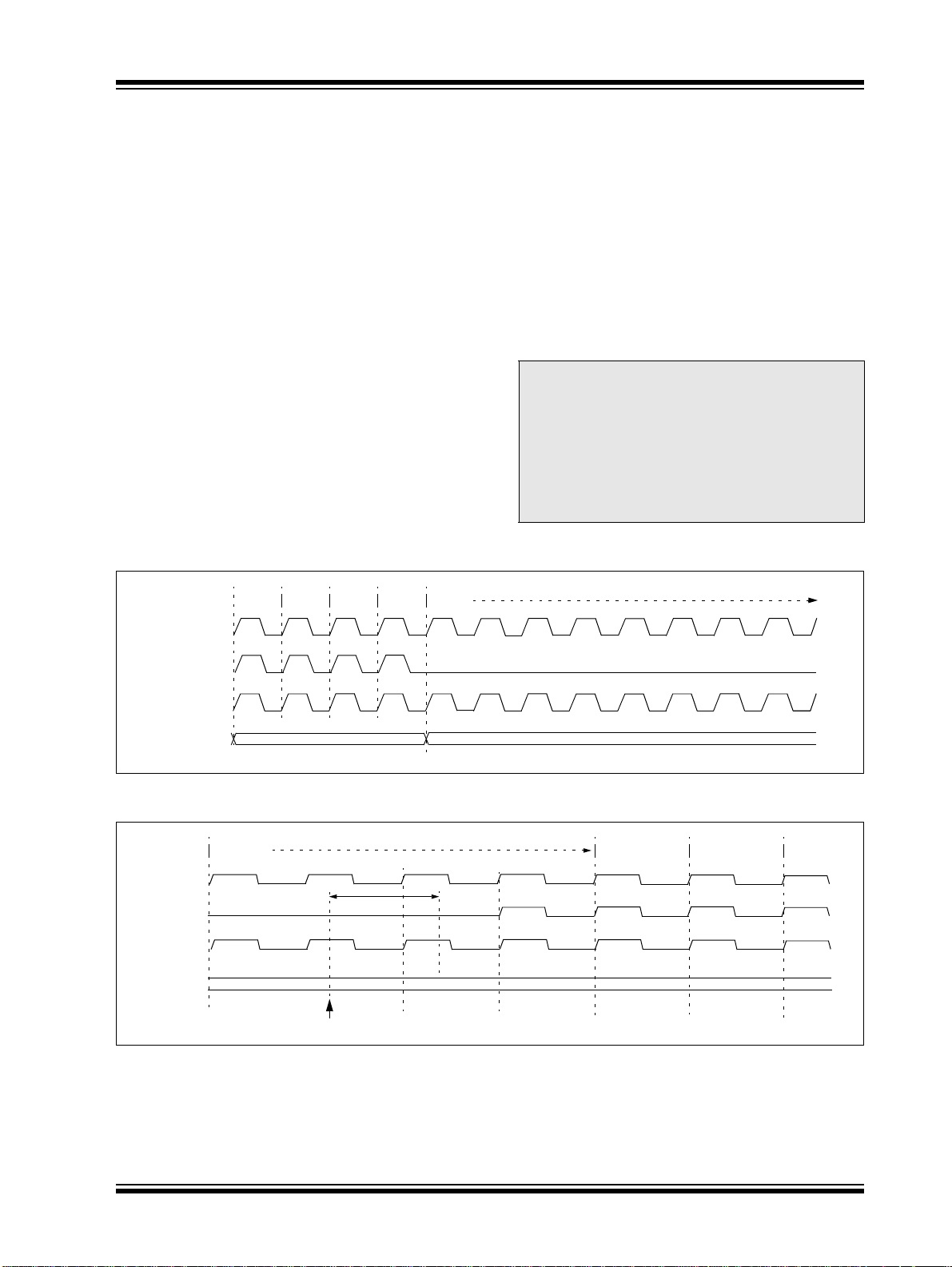

图 3-6)。

当唤醒事件发生时,由主时钟源为 CPU 提供时钟。在唤

醒事件和代码执行开始之间需要一段 T

CSD 间隔的延迟。

这段时间可以使 CPU 做好执行指令的准备。在唤醒之

后,OSTS 位保持置 1。唤醒不会影响 IDLEN 和 SCS 位

(见图 3-7)。

图 3-6: 进入空闲模式的转换时序

3.4.2 SEC_IDLE 模式

在 SEC_IDLE 模式中, CPU 被禁止,但外设继续使用

Timer1 振荡器作为时钟源。通过置位 IDLEN 位并执行

SLEEP 指令可以从 SEC_RUN 进入此模式。如果器件

处于其他运行模式,请先置位 IDLEN,然后 将

SCS1:SCS0 置为 “01”并执行 SLEEP 指令。当时钟

源切换到 Timer1 振荡器时,主振荡器关闭, OSTS 位

清零, T1RUN 位被置 1。

当唤醒事件发生时,外设继续将 Timer1 振荡器作为时

钟源。在唤醒事件后经过一个 T

使用 Timer1 振荡器作为时钟源并开始执行代码。唤醒

不会影响 IDLEN 和 SCS 位; Timer1 振荡器继续运行

(见图 3-7)。

注: Timer1 振荡器应该在进入 SEC_IDLE 模式

之前已经在运行了。如果执行 SLEEP 指令

时 T1OSCEN 位没有被置 1,那么 SLEEP

指令会被忽略并且不会进入 SEC_IDLE 模

式。如果 Timer1 振荡器已经被使能,但还

没有开始运行,外设时钟将被延迟直到振

荡器起振为止。在这种情况下,初始振荡

器运行很不稳定并且它的运行结果无法预

料。

CSD 的时间间隔, CPU

Q1

OSC1

CPU 时钟

外设

时钟

程序

计数器

Q1

Q2

Q3

PC PC + 2

Q4

图 3-7: 从空闲模式唤醒进入运行模式的转换时序

Q1 Q3 Q4

OSC1

CPU 时钟

外设

时钟

程序

计数器

唤醒事件

TCS D

PC

Q2

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 35 页

PIC18F45J10 系列

3.4.3 RC_IDLE 模式

在 RC_IDLE 模式中,CPU 被禁止,但外设继续使用内

部振荡器作为时钟源。该模式允许在器件处于空闲模式

期间对功耗进行控制。

通过将IDLEN位置1并执行SLEEP指令可以从 RC_RUN

模式进入此模式。如果器件处于其他运行模式,请先置

位 IDLEN,然后将 SCS 位清零并执行 SLEEP 指令。当

时钟源切换到 INTRC 时,主振荡器关闭, OSTS 位被

清零。

当唤醒事件发生时,外设继续使用 INTRC 作为时钟源。

唤醒事件发生后经过一个 T

INTRC 作为时钟源并开始执行代码。唤醒不会影响

IDLEN 和 SCS 位。如果使能了 WDT 或故障保护时钟

监视器, INTRC 源将继续运行。

CSD 的时间间隔,CPU 使用

3.5 退出空闲和休眠模式

通过将中断、复位或 WDT 超时作为触发事件,从休眠

模式或任何空闲模式退出。本节将讨论引起从功耗管理

模式退出的触发事件。在每个功耗管理模式的章节中,

还讨论了时钟控制子系统的操作(见第 3.2 节“运行模

式”、第 3.3节“休眠模式”和第 3.4节“空闲模式”)。

3.5.1 通过中断退出

任何可用的中断源可以引起器件从空闲模式或休眠模式

退出,并进入运行模式。要使能此功能,必须通过将

INTCON 或 PIE 寄存器中的相应中断允许位置 1 来使能

该中断源。当相应的中断标志位被置 1 时,启动退出时

序。

当通过中断从空闲或休眠模式退出时,如果 GIE/GIEH

位(INTCON<7>)置 1,程序就会跳转到中断矢量处

执行。否则,代码执行就会继续或恢复,而不发生跳转

(见第 8.0 节 “中断”)。

通过中断从休眠或空闲模式退出时,一个固定的延迟时

间间隔 T

做准备。在此延迟后的第一个时钟周期恢复指令执行。

CSD 是必需的。CPU 需要此延迟来为执行代码

3.5.2 通过 WDT 超时退出

根据 WDT 超时发生时器件所处的不同功耗管理模式,

会引发不同的操作。

如果器件没有执行代码 (在所有空闲模式和休眠模式

下) ,超时将导致从功耗管理模式退出 (见第 3.2 节

“运行模式”和第 3.3 节“休眠模式”)。如果器件正在

执行代码 (在所有运行模式下),超时将导致 WDT 复

位(见第 20.2 节 “看门狗定时器 (WDT)”)。

WDT 定时器和后分频器通过以下任一事件清零:

• 执行 SLEEP 或 CLRWDT 指令

• 当前选定的时钟源失效 (使能故障保护时钟监视

器时)

3.5.3 通过复位退出

通过复位从空闲或休眠模式退出,将自动强制器件使用

INTRC 作为时钟源运行。

3.5.4 在没有振荡器起振延迟的情况下退出

某些从功耗管理模式退出的方式根本不会启动 OST。具

体有两种情形:

• 主时钟源处于不会被停止的 PRI_IDLE 模式;

• 主时钟源处于 EC 模式。

在这两种情况下,主时钟源都不需要振荡器起振延迟,

因为要么它已经在运行了 (在 PRI_IDLE 模式下),要

么根本不需要振荡器起振延迟(在 EC 模式下)。然而,

当退出休眠和空闲模式时,在唤醒事件后的一个固定的

延迟间隔 T

行代码做准备。在此延迟后的第一个时钟周期恢复指令

执行。

CSD 仍然是必需的,CPU 利用这段时间为执

DS39682A_CN 第 36 页 高级信息 2005 Microchip Technology Inc.

PIC18F45J10 系列

4.0 复位

PIC18F45J10 系列器件有以下几种不同的复位方式:

a) 上电复位 (Power-on Reset, POR)

b) 正常工作状态下的 MCLR

c) 功耗管理模式下的 MCLR

d) 看门狗定时器 (WDT)复位 (执行程序期间)

e) 欠压复位 (Brown-on Reset, BOR)

f) RESET 指令

g) 堆栈满复位

h) 堆栈下溢复位

本节将讨论由 MCLR

、POR 和 BOR 产生的各种复位以

及各种起振定时器的操作。堆栈复位事件将在

第 5.1.2.4 节“堆栈满和下溢复位”中讨论。 WDT 复位

将在第 20.2 节 “看门狗定时器 (WDT)” 中讨论。

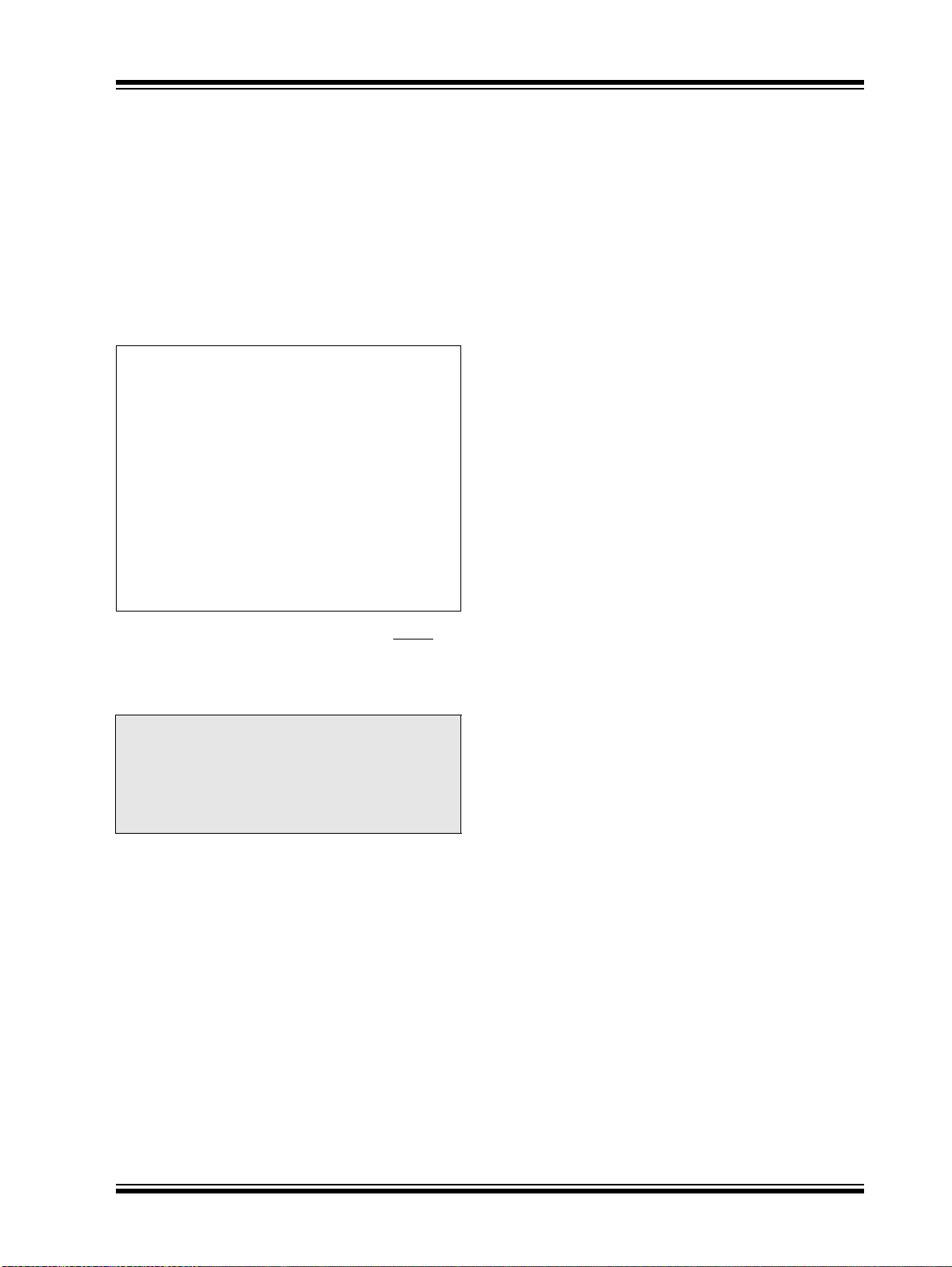

图 4-1 给出了片上复位电路的简化框图。

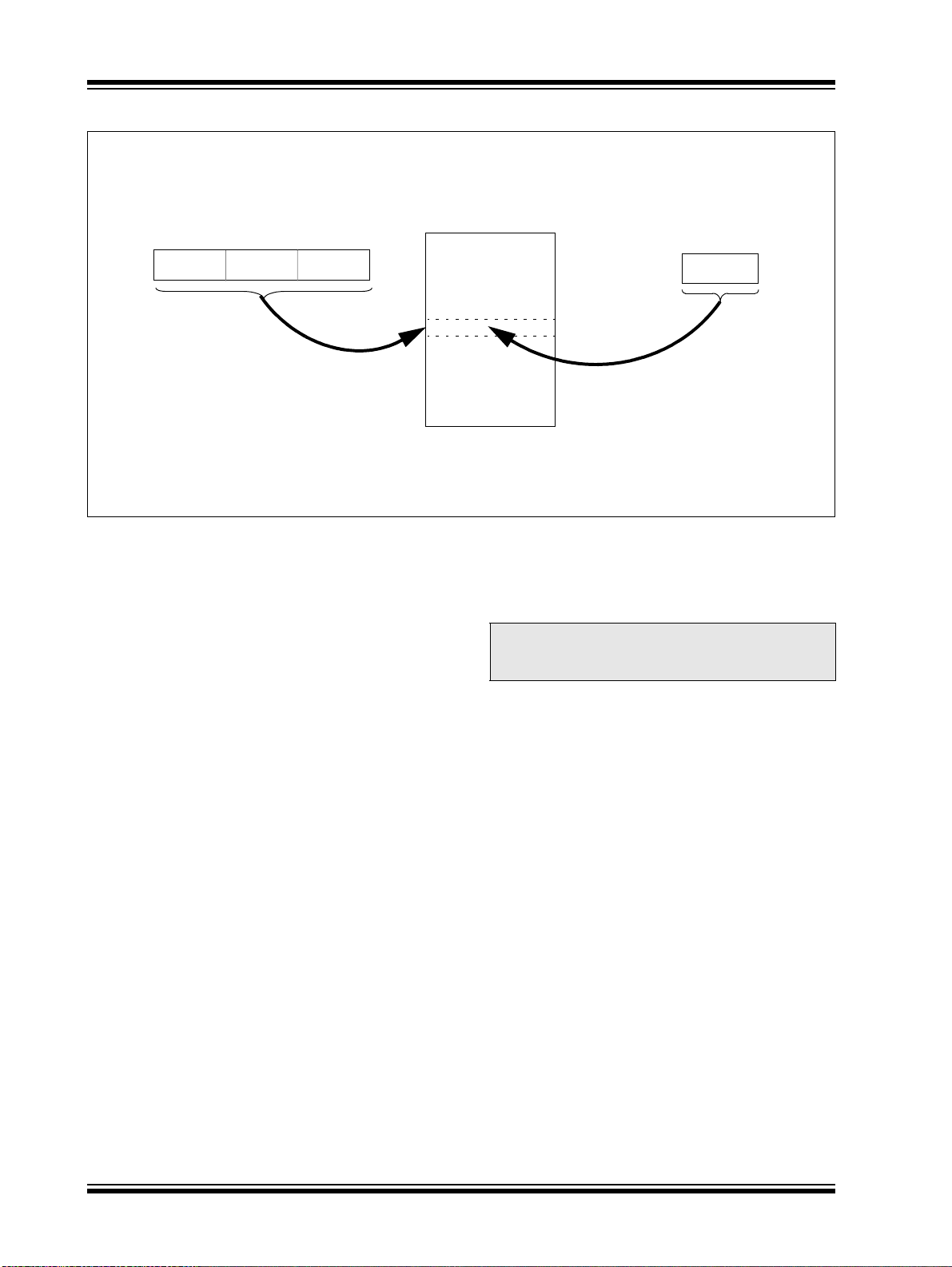

图 4-1: 片上复位电路的简化框图

RESET

指令

堆栈

指针

复位

复位

堆栈满 / 下溢复位

4.1 RCON 寄存器

可通过 RCON 寄存器 (寄存器 4-1)跟踪器件复位事

件。该寄存器的低 5 位表示特定的复位事件是否已经发

生。在大部分情况下,只有复位事件可以将这些位置 1,

而且它们必须在复位事件之后由应用程序清零。将这些

标志位的状态一起读出可以得知刚发生的复位的类型。

第 4.6 节“寄存器的复位状态”对此进行了更详细地说

明。

RCON 寄存器还有一个设置中断优先级的控制位

(IPEN)。中断优先级将在 第 8.0 节“中断”中进行讨

论。

外部复位

MCLR

VDD

注 1: PIC18LF2XJ10/4XJ10 器件不能使用欠压复位。

( )_IDLE

Sleep

WDT

V

沿检测

复位

PWRT

32 µs

INTRC

超时

DD 上升

欠压

(1)

上电复位脉冲

PWRT

11 位脉动计数器

65.5 ms

S

芯片复位

R

Q

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 37 页

PIC18F45J10 系列

寄存器 4-1: RCON:复位控制寄存器

R/W-0 U-0 U-0 R/W-1 R-1 R-1 R/W-0 R/W-0

IPEN

bit 7 bit 0

- -

RI

TO PD POR BOR

bit 7

bit 6-5

bit 4

bit 3

bit 2

bit 1

bit 0

IPEN:中断优先级使能位

1 = 使能中断优先级

0 = 禁止中断优先级 (PIC16CXXX 兼容模式)

未用:读为 0

RI:RESET 指令标志位

1 = 未执行 RESET 指令 (仅由固件置 1)

0 = 执行 RESET 指令导致器件复位 (必须在欠压复位发生之后用软件置 1)

TO:看门狗定时器超时标志位

1 = 通过上电、 CLRWDT 指令或 SLEEP 指令置 1

0 = 发生了 WDT 超时

:掉电检测标志位

PD

1 = 通过上电或 CLRWDT 指令置 1

0 = 通过执行 SLEEP 指令置 1

POR

:上电复位状态位

1 = 未发生上电复位 (仅由固件置 1)

0 = 发生了上电复位 (必须在发生上电复位后由软件置 1)

BOR:欠压复位状态位

1 = 未发生欠压复位 (仅由固件置 1)

0 = 发生了欠压复位 (必须在欠压复位发生之后由软件置 1)

注: PIC18LF2XJ10/4XJ10 器件不能使用欠压复位。

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 10 = 清零 x = 未知

注 1: 建议在检测到上电复位后,将 POR 位置 1,以便检测后续发生的上电复位。

2: 如果禁止了片上稳压器, BOR 则总是保持为 0。欲知更多信息,请参见第 4.4.1 节

“检测 BOR”。

3: 欠压复位是指当 BOR

立即被软件置 1)。

DS39682A_CN 第 38 页 高级信息 2005 Microchip Technology Inc.

为 0且 POR 为 1 时发生的复位(假定在上电复位发生后 POR

PIC18F45J10 系列

4.2 主复位 (MCLR)

MCLR 引脚提供了用外部硬件触发器件复位的方法。保

持该引脚为低电平就能触发此复位。PIC18 扩展的单片

机器件在 MCLR 复位信号传输路径中有一个噪声滤波

器,它可以检测并滤除小的干扰脉冲。

任何内部复位,包括 WDT 复位,都不能将 MCLR

引脚

驱动为低电平。

4.3 上电复位 (POR)

只要 VDD 上升到一定的门限以上,就会在片上产生上电

复位信号。这使得器件在 V

DD 上升到足够其工作时,以

初始化状态启动。

为了使用 POR 电路,可以将 MCLR

引脚通过一个电阻

(1kΩ 到 10 kΩ)连接到 VDD。这样可以省去产生上电

复位延时通常所需的外部 RC 元件。 V

率已指定 (参数 D004)。 对于延缓 V

DD 的最小上升速

DD 上升时间的情

况,请参见图 4-2。

当器件开始正常工作 (即退出复位状态)时,必须满足

特定的工作参数要求 (电压、频率和温度等),才能确

保其正常工作。如果这些条件不满足,那么器件必须保

持在复位状态,直到工作条件满足为止。

上电复位事件由 POR

位(RCON<1>)捕捉。只要发

生上电复位,此位的状态就被置为 0,它不会因任何其

他复位事件发生改变。任何硬件事件都不会将 POR 位

复位为 1。要捕捉多个事件,用户必须在上电复位之后

用软件手动将该位复位为 1。

4.4 欠压复位 (BOR)

(仅 PIC18F2XJ10/4XJ10 器件)

一旦发生欠压复位,上电延时定时器就将芯片保持在复

位状态达 TPWRT (参数 33)时间。如果上电延迟定时

器运行时, V

欠压复位状态并初始化上电延迟定时器。一旦 V

上升到V

DD 电压降到 VBOR 以下,芯片将重新回到

DD 电压

BOR以上,上电延迟定时器将再执行一个延时。

图 4-2: 外部上电复位电路

(用于延缓 V

DD

VDD

注 1: 仅当 VDD 上电很慢时,需要外部上电复位电

V

D

R

R1

C

路。当 V

放电。

2: 建议 R < 40 kΩ,确保电阻 R 两端的压降符合

器件的电气规范。

3: R1

MCLR

Discharge, ESD)或电超载 (Electrical

Overstrss, EOS)导致 MCLR

DD 掉电时,二极管 D 帮助电容迅速

≥ 1kΩ 将限制任何电流从外部电容 C 流入

,以避免由于静电放电 (Electrostatic

DD 上电)

MCLR

PIC18F45J10

引脚击穿。

4.4.1 检测 BOR

BOR 位在发生欠压复位或上电复位事件时总是复位为

0。所以仅通过读 BOR 的状态很难判断 BOR 事件是否

已经发生。更可靠的方法是同时检查 POR

态。假设在上电复位事件之后立即用软件将 POR 位复

位为 1。如果 BOR 为 0 而 POR 为 1,就可以可靠地判

断出已经发生了欠压复位事件。

器件编号中带有 “LF”的器件 (如 PIC18LF25J10)

禁止欠压复位功能。在这种情况下,不能使用 BOR

来确定欠压复位事件。上电复位事件仍然会清零 BOR

位。

和 BOR 的状

位

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 39 页

PIC18F45J10 系列

4.5 上电延时定时器 (PWRT)

PIC18F45J10 系列器件加入了片上上电延时定时器

(PWRT)以帮助稳定上电复位过程。 PWRT 总是使能

的。主要功能是确保在执行代码之前,器件的电压是稳

定的。

PIC18F45J10 系列器件的上电延时定时器(PWRT)是

一个 11 位计数器,使用 INTRC 时钟源作为时钟输入。

这就产生大约 2048 x 32 µs = 65.6ms的延迟时间。当

PWRT 计数时,器件保持在复位状态。

上电延迟时间取决于 INTRC 时钟,并且由于温度和工

艺的变化,不同芯片的延迟时间各不相同。 欲知详细信

息,参见 DC 参数 33。

4.5.1 延时序列

如果使能 PWRT,在 POR 脉冲被清零后触发 PWRT 延

时。总延时会根据 PWRT 的状态而有所不同。 图 4-3、

图 4-4、图 4-5 和图 4-6 都说明了在使能上电延时定时

器时的上电延时序列。

由于延时是由上电复位脉冲引起的,因此若 MCLR

保持足够长时间的低电平,延时将结束。将 MCLR 引脚

的电平拉高后程序将立即执行 (图 4-5)。 这对于测试

或同步多个并行工作的 PIC18F 器件来说是非常有用

的。

图 4-3: 上电延时序列 (MCLR 连接到 VDD, VDD 上升时间 < TPWRT)

VDD

MCLR

内部 POR

TPWRT

PWRT

延时

引脚

内部复位

图 4-4: 上电延时序列 (MCLR

VDD

MCLR

内部 POR

PWRT

延时

内部复位

不连接到 VDD): 情 形 1

TPWRT

DS39682A_CN 第 40 页 高级信息 2005 Microchip Technology Inc.

PIC18F45J10 系列

图 4-5: 上电延时序列 (MCLR 不连接到 VDD): 情 形 2

VDD

MCLR

内部 POR

TPWRT

PWRT

延时

内部复位

图 4-6: VDD 缓慢上升时的上电延时序列 (MCLR

MCLR

内部 POR

PWRT

内部复位

VDD

延时

0V

PWRT

T

1V

连接到 VDD, VDD 上升时间 > TPWRT)

3.3V

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 41 页

PIC18F45J10 系列

4.6 寄存器的复位状态

大多数寄存器不受复位的影响。在上电复位时这些寄存

器的状态未知,而在其他复位时它们的状态不变。而其

他寄存器则根据不同的复位类型被强制置为相应的“复

位状态”。

大多数寄存器不受 WDT 唤醒的影响,这是因为 WDT 唤

醒被视为恢复正常工作。如表 4-1 所示,RCON 寄存器

的状态位 RI

情况下置 1 和清零的状态也各不相同。可在软件中使用

这些状态位判断复位的性质。

、TO、 PD、 POR 和 BOR,在不同的复位

表 4-2 说明了所有特殊功能寄存器的复位状态。这些复

位被分为上电和欠压复位、主复位和 WDT 复位以及

WDT 唤醒复位。

表 4-1: RCON 寄存器的状态位、它们的含义以及初始化状态

条 件 程序计数器

上电复位

RESET 指令

欠压

功耗管理运行模式期间的 MCLR

功耗管理空闲模式和休眠模式期

间时的 MCLR

全功耗或功耗管理运行模式期间

的 WDT 超时

全功耗运行期间的 MCLR

堆栈满复位 (STVREN = 1)

堆栈下溢复位 (STVREN = 1)

堆栈下溢错误 (不是真正的复

位, STVREN = 0)

功耗管理空闲或休眠模式期间的

WDT 超时

中断使器件从功耗管理模式退出

图注: u = 不变

注 1: 当芯片被中断唤醒且 GIEH 或 GIEL 位置 1 时, PC 装入中断矢量 (0008h 或 0018h)。

2: PIC18LF2XJ10/4XJ10 器件不能使用欠压复位。

0000h 11100 0 0

0000h 0uuuu u u

0000h 111u0 u u

0000h u1uuu u u

0000h u10uu u u

0000h u0uuu u u

0000h uuuuu u u

0000h uuuuu 1 u

0000h uuuuu u 1

0000h uuuuu u 1

PC + 2 u00uu u u

PC + 2 uu0uu u u

(1)

RI

RCON 寄存器 STKPTR 寄存器

TO PD POR BOR

(2)

STKFUL STKUNF

DS39682A_CN 第 42 页 高级信息 2005 Microchip Technology Inc.

PIC18F45J10 系列

表 4-2: 所有寄存器的初始化状态

复位

MCLR

寄存器 适用器件

上电复位,

欠压复位

WDT 复位

RESET 指令

堆栈复位

TOSU PIC18F2XJ10 PIC18F4XJ10 ---0 0000 ---0 0000 ---0 uuuu

TOSH PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

TOSL PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

STKPTR PIC18F2XJ10 PIC18F4XJ10 00-0 0000 uu-0 0000 uu-u uuuu

PCLATU PIC18F2XJ10 PIC18F4XJ10 ---0 0000 ---0 0000 ---u uuuu

PCLATH PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

PCL PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 PC + 2

TBLPTRU PIC18F2XJ10 PIC18F4XJ10 --00 0000 --00 0000 --uu uuuu

TBLPTRH PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

TBLPTRL PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

TABLAT PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

PRODH PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

PRODL PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

INTCON PIC18F2XJ10 PIC18F4XJ10 0000 000x 0000 000u uuuu uuuu

INTCON2 PIC18F2XJ10 PIC18F4XJ10 1111 -1-1 1111 -1-1 uuuu -u-u

INTCON3 PIC18F2XJ10 PIC18F4XJ10 11-0 0-00 11-0 0-00 uu-u u-uu

INDF0 PIC18F2XJ10 PIC18F4XJ10 N/A N/A N/A

POSTINC0 PIC18F2XJ10 PIC18F4XJ10 N/A N/A N/A

POSTDEC0 PIC18F2XJ10 PIC18F4XJ10 N/A N/A N/A

PREINC0 PIC18F2XJ10 PIC18F4XJ10 N/A N/A N/A

PLUSW0 PIC18F2XJ10 PIC18F4XJ10 N/A N/A N/A

FSR0H PIC18F2XJ10 PIC18F4XJ10 ---- xxxx ---- uuuu ---- uuuu

FSR0L PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

WREG PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

INDF1 PIC18F2XJ10 PIC18F4XJ10 N/A N/A N/A

POSTINC1 PIC18F2XJ10 PIC18F4XJ10 N/A N/A N/A

POSTDEC1 PIC18F2XJ10 PIC18F4XJ10 N/A N/A N/A

PREINC1 PIC18F2XJ10 PIC18F4XJ10 N/A N/A N/A

PLUSW1 PIC18F2XJ10 PIC18F4XJ10 N/A N/A N/A

FSR1H PIC18F2XJ10 PIC18F4XJ10 ---- xxxx ---- uuuu ---- uuuu

FSR1L PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

BSR PIC18F2XJ10 PIC18F4XJ10 ---- 0000 ---- 0000 ---- uuuu

图注: u = 不变, x = 未知,- = 未用 (读为 0), q = 取值视具体情况而定。

阴影单元表示条件不适用于指定器件。

注 1: 当芯片被中断唤醒且 GIEL 或 GIEH 位被置 1 时,用 PC 的当前值更新 TOSU、 TOSH 和 TOSL。将

STKPTR 修改为指向硬件堆栈的下一个单元。

2: 当芯片被中断唤醒且 GIEL 或 GIEH 位被置 1 时, PC 装入中断矢量地址 (0008h 或 0018h)。

3: INTCONx 或 PIRx 寄存器中的一位或多位会受到影响 (用以唤醒器件)。

4: 关于特定条件下的复位值,请参见表 4-1。

通过 WDT

或中断唤醒器件

(1)

(1)

(1)

(1)

(2)

(3)

(3)

(3)

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 43 页

PIC18F45J10 系列

表 4-2: 所有寄存器的初始化状态

寄存器 适用器件

INDF2 PIC18F2XJ10 PIC18F4XJ10 N/A N/A N/A

POSTINC2 PIC18F2XJ10 PIC18F4XJ10 N/A N/A N/A

POSTDEC2 PIC18F2XJ10 PIC18F4XJ10 N/A N/A N/A

PREINC2 PIC18F2XJ10 PIC18F4XJ10 N/A N/A N/A

PLUSW2 PIC18F2XJ10 PIC18F4XJ10 N/A N/A N/A

FSR2H PIC18F2XJ10 PIC18F4XJ10 ---- xxxx ---- uuuu ---- uuuu

FSR2L PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

STATUS PIC18F2XJ10 PIC18F4XJ10 ---x xxxx ---u uuuu ---u uuuu

TMR0H PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

TMR0L PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

T0CON PIC18F2XJ10 PIC18F4XJ10 1111 1111 1111 1111 uuuu uuuu

OSCCON PIC18F2XJ10 PIC18F4XJ10 0--- q-00 0--- q-00 u--- q-uu

WDTCON PIC18F2XJ10 PIC18F4XJ10 ---- ---0 ---- ---0 ---- ---u

(4)

RCON

TMR1H PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

TMR1L PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

T1CON PIC18F2XJ10 PIC18F4XJ10 0000 0000 u0uu uuuu uuuu uuuu

TMR2 PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

PR2 PIC18F2XJ10 PIC18F4XJ10 1111 1111 1111 1111 1111 1111

T2CON PIC18F2XJ10 PIC18F4XJ10 -000 0000 -000 0000 -uuu uuuu

SSP1BUF PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

SSP1ADD PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

SSP1STAT PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

SSP1CON1 PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

SSP1CON2 PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

ADRESH PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

ADRESL PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

ADCON0 PIC18F2XJ10 PIC18F4XJ10 0-00 0000 0-00 0000 u-uu uuuu

ADCON1 PIC18F2XJ10 PIC18F4XJ10 --00 0qqq --00 0qqq --uu uqqq

ADCON2 PIC18F2XJ10 PIC18F4XJ10 0-00 0000 0-00 0000 u-uu uuuu

图注: u = 不变, x = 未知,- = 未用 (读为 0), q = 取值视具体情况而定。

注 1: 当芯片被中断唤醒且 GIEL 或 GIEH 位被置 1 时,用 PC 的当前值更新 TOSU、 TOSH 和 TOSL。将

2: 当芯片被中断唤醒且 GIEL 或 GIEH 位被置 1 时, PC 装入中断矢量地址 (0008h 或 0018h)。

3: INTCONx 或 PIRx 寄存器中的一位或多位会受到影响 (用以唤醒器件)。

4: 关于特定条件下的复位值,请参见表 4-1。

PIC18F2XJ10 PIC18F4XJ10 0--1 11q0 0--q qquu u--u qquu

阴影单元表示条件不适用于指定器件。

STKPTR 修改为指向硬件堆栈的下一个单元。

(续)

上电复位,

欠压复位

复位

MCLR

WDT 复位

RESET 指令

堆栈复位

通过 WDT

或中断唤醒器件

DS39682A_CN 第 44 页 高级信息 2005 Microchip Technology Inc.

PIC18F45J10 系列

表 4-2: 所有寄存器的初始化状态

寄存器 适用器件

CCPR1H PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

CCPR1L PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

CCP1CON PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

CCPR2H PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

CCPR2L PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

CCP2CON PIC18F2XJ10 PIC18F4XJ10 --00 0000 --00 0000 --uu uuuu

BAUDCON PIC18F2XJ10 PIC18F4XJ10 01-0 0-00 01-0 0-00 uu-u u-uu

ECCP1DEL PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

ECCP1AS PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

CVRCON PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

CMCON PIC18F2XJ10 PIC18F4XJ10 0000 0111 0000 0111 uuuu uuuu

SPBRGH PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

SPBRG PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

RCREG PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

TXREG PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

TXSTA PIC18F2XJ10 PIC18F4XJ10 0000 0010 0000 0010 uuuu uuuu

RCSTA PIC18F2XJ10 PIC18F4XJ10 0000 000x 0000 000x uuuu uuuu

EECON2 PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

EECON1 PIC18F2XJ10 PIC18F4XJ10 ---0 x00- ---0 x00- ---u uuu-

IPR3 PIC18F2XJ10 PIC18F4XJ10 11-- ---- 11-- ---- uu-- ----

PIR3 PIC18F2XJ10 PIC18F4XJ10 00-- ---- 00-- ---- uu-- ----

PIE3 PIC18F2XJ10 PIC18F4XJ10 00-- ---- 00-- ---- uu-- ----

IPR2 PIC18F2XJ10 PIC18F4XJ10 11-- 1--1 11-- 1--1 uu-- u--u

PIR2 PIC18F2XJ10 PIC18F4XJ10 00-- 0--0 00-- 0--0 uu-- u--u

PIE2 PIC18F2XJ10 PIC18F4XJ10 00-- 0--0 00-- 0--0 uu-- u--u

IPR1 PIC18F2XJ10 PIC18F4XJ10 1111 1111 1111 1111 uuuu uuuu

PIR1 PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

PIE1 PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

图注: u = 不变, x = 未知,- = 未用 (读为 0), q = 取值视具体情况而定。

阴影单元表示条件不适用于指定器件。

注 1: 当芯片被中断唤醒且 GIEL 或 GIEH 位被置 1 时,用 PC 的当前值更新 TOSU、 TOSH 和 TOSL。将

STKPTR 修改为指向硬件堆栈的下一个单元。

2: 当芯片被中断唤醒且 GIEL 或 GIEH 位被置 1 时, PC 装入中断矢量地址 (0008h 或 0018h)。

3: INTCONx 或 PIRx 寄存器中的一位或多位会受到影响 (用以唤醒器件)。

4: 关于特定条件下的复位值,请参见表 4-1。

(续)

上电复位,

欠压复位

复位

MCLR

WDT 复位

RESET 指令

堆栈复位

通过 WDT

或中断唤醒器件

(3)

(3)

(3)

2005 Microchip Technology Inc. 高级信息 DS39682A_CN 第 45 页

PIC18F45J10 系列

表 4-2: 所有寄存器的初始化状态

寄存器 适用器件

TRISE PIC18F2XJ10 PIC18F4XJ10 0000 -111 1111 -111 uuuu -uuu

TRISD

TRISC PIC18F2XJ10 PIC18F4XJ10 1111 1111 1111 1111 uuuu uuuu

TRISB PIC18F2XJ10 PIC18F4XJ10 1111 1111 1111 1111 uuuu uuuu

TRISA PIC18F2XJ10 PIC18F4XJ10 --1- 1111 --1- 1111 --u- uuuu

SSP2BUF PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

LATE

LATD

LATC PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

LATB PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

LATA PIC18F2XJ10 PIC18F4XJ10 --x- xxxx --u- uuuu --u- uuuu

SSP2ADD

SSP2STAT

SSP2CON1

SSP2CON2 PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

PORTE

PORTD

PORTC PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

PORTB PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

PORTA PIC18F2XJ10 PIC18F4XJ10 --0- 0000 --0- 0000 --u- uuuu

图注: u = 不变, x = 未知,- = 未用 (读为 0), q = 取值视具体情况而定。

注 1: 当芯片被中断唤醒且 GIEL 或 GIEH 位被置 1 时,用 PC 的当前值更新 TOSU、 TOSH 和 TOSL。将

2: 当芯片被中断唤醒且 GIEL 或 GIEH 位被置 1 时, PC 装入中断矢量地址 (0008h 或 0018h)。

3: INTCONx 或 PIRx 寄存器中的一位或多位会受到影响 (用以唤醒器件)。

4: 关于特定条件下的复位值,请参见表 4-1。

PIC18F2XJ10 PIC18F4XJ10 1111 1111 1111 1111 uuuu uuuu

PIC18F2XJ10 PIC18F4XJ10 ---- -xxx ---- -uuu ---- -uuu

PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

PIC18F2XJ10 PIC18F4XJ10 0000 0000 0000 0000 uuuu uuuu

PIC18F2XJ10 PIC18F4XJ10 ---- -xxx ---- -uuu ---- -uuu

PIC18F2XJ10 PIC18F4XJ10 xxxx xxxx uuuu uuuu uuuu uuuu

阴影单元表示条件不适用于指定器件。