Page 1

PIC16C781/782

Data Sheet

8-Bit CMOS Microcontrollers with A/D,

D/A, OPAMP, Comparators and PSMC

2001 Microchip Technology Inc. Preliminary DS41171A

Page 2

Note the following details of the code protection feature on PICmicro® MCUs.

• The PICmicro family meets the specifications contained in the Microchip Data Sheet.

• Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today,

when used in the intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet.

The person doing so may be engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable”.

• Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of

our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device

applications and the like is intended through suggestion only

and may be superseded by updates. It is your responsibility to

ensure that your application meets with your specifications.

No representation or warranty is given and no liability is

assumed by Microchip Technology Incorporated with respect

to the accuracy or use of such information, or infringement of

patents or other intellectual property rights arising from such

use or otherwise. Use of Microchip’s products as critical components in life support systems is not authorized except with

express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property

rights.

Trademarks

The Microchip name and logo, the Microchip logo, PIC, PICmicro,

PICMASTER, PICSTART, PRO MATE, K

EELOQ, SEEVAL,

MPLAB and The Embedded Control Solutions Company are registered tradem arks of Micr ochip Technology Incorporated in the

U.S.A. and other countries.

Total Endurance, ICSP, In-Circuit Serial Programming, FilterLab, MXDEV, microID, FlexROM, fuzzyLAB, MPASM,

MPLINK, MPLIB, PICC, PICDEM, PICDEM.net, ICEPIC,

Migratable Memory, FanSense, ECONOMONITOR, Select

Mode and microPort are trademarks of Microchip Technology

Incorporated in the U.S.A.

Serialized Quick T erm Programming (SQTP) is a service mark

of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2001, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received QS-9000 quality system

certification for its worldwide headquarters,

design and wafer fabrication facilities in

Chandler and Tempe, Arizona in July 1999. The

Company’s quality system processes and

procedures are QS-9000 compliant for its

PICmicro

devices, Serial EEPROMs and microperipheral

products. In addition, Microchip’s quality

system for the design and manufacture of

development systems is ISO 9001 certified.

®

8-bit MCUs, KEELOQ

®

code hoppin g

DS41171A - page ii Preliminary 2001 Microchip Technology Inc.

Page 3

PIC16C781/782

8-Bit CMOS Microcontrollers with A/D, D/A, OPAMP,

Comparators and PSMC

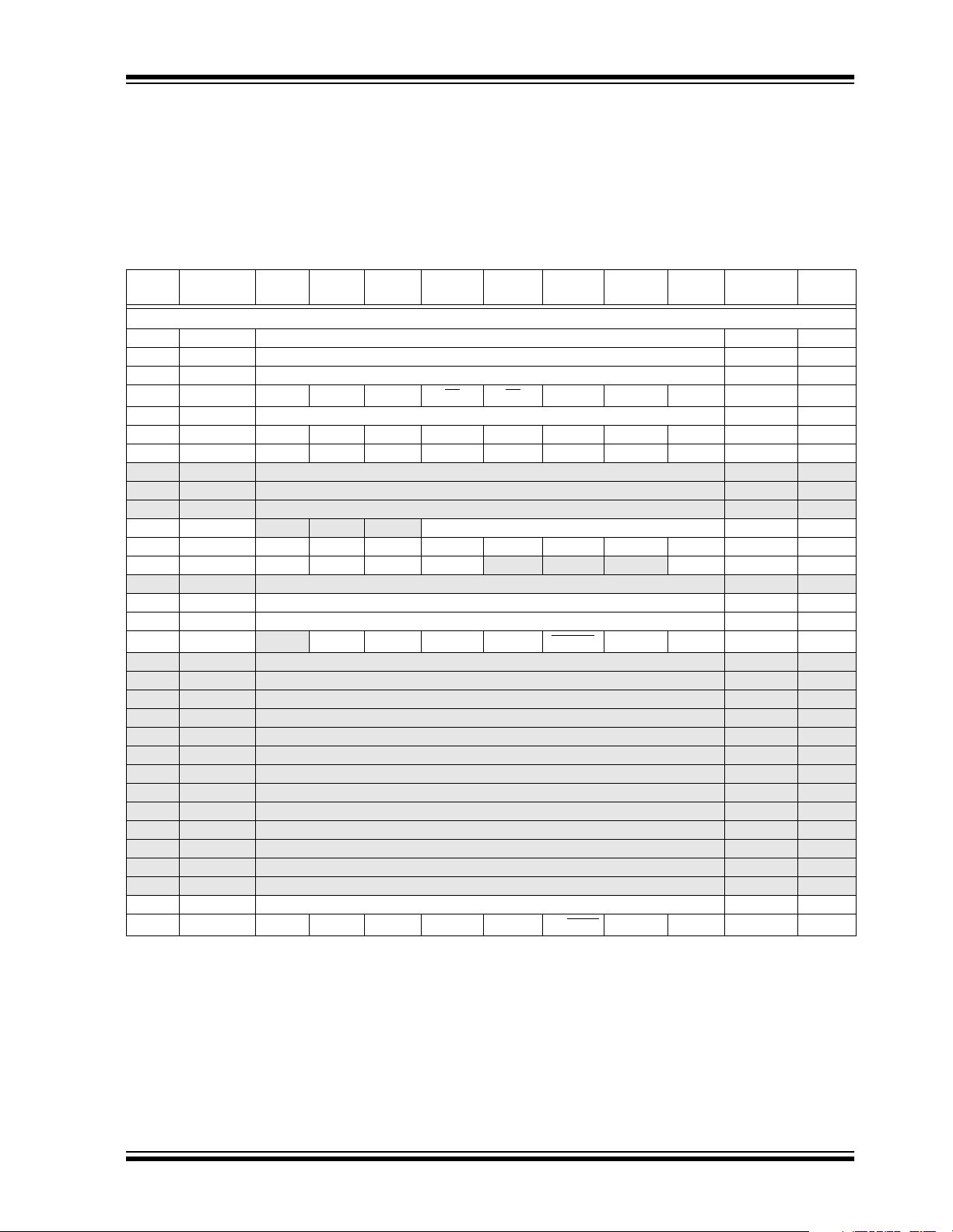

Microcontroller Core Features:

• High performance RISC CPU

• Only 35 single word instructions to learn

• All single cycle instructions except for program

branches which are two cycle

• Direct, indirect and relative addressing modes

- Operating speed: DC - 20 MHz clock input

DC - 200 ns instruction cycle

Program

Device

Memory

X14

PIC16C781 1K 128

PIC16C782 2K 128

• 8-level deep hardware stack

• Interrupt capability (up to 8 internal/external

interrupt sources)

• 16 I/O pins:

- Individual direction control (13 pins)

- Input only (3 pins), low leakage (2 pins)

- Digital/Analog inputs (8 pins)

• Programmable PORTB interrupt-on-change (8 pins)

• Programmable PORTB weak pull-ups (8 pins)

• Power-on Reset (POR)

• Power-up Timer (PWRT) and

Oscillator Start-up Timer (OST)

• Watchdog Timer (WDT) with a software enabled

option and its own on-chip RC oscillator for

reliable operation

• Programmable Brown-out Reset (BOR)

• Programmable Low Voltage Detection (LVD)

• Internal/external MCLR

• Programmable code protection

• Power saving SLEEP mode

• Selectable oscillator options:

HS, XT, LP, EC, RC, INTRC (4 MHz/37 kHz)

• In-Circuit Serial Programming™ (ISCP™)

• Program Memory Read (PMR) capability

• Four user programmable ID locations

• Wide operating voltage range:

- 2.5V to 5.5V for commercial and industrial

temperature ranges

- Extended temperature range available

Data Memory

X8

Microcontroller Core Features (Continued):

• Low power, high speed CMOS EPROM

technology

• Fully static design

• Low power consumption:

- < 2mA @ 5V, 4MHz

-< 1 µA typical standby current.

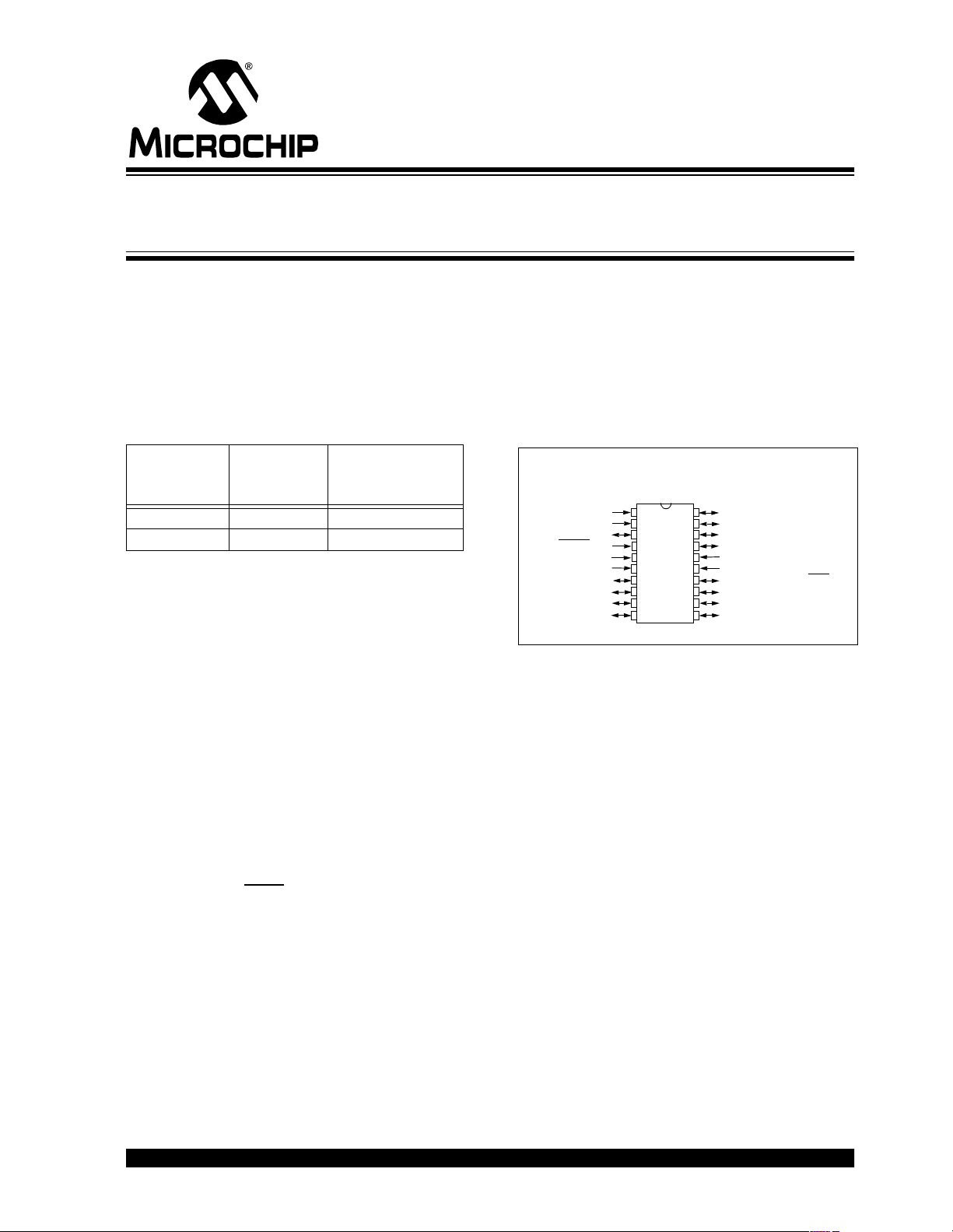

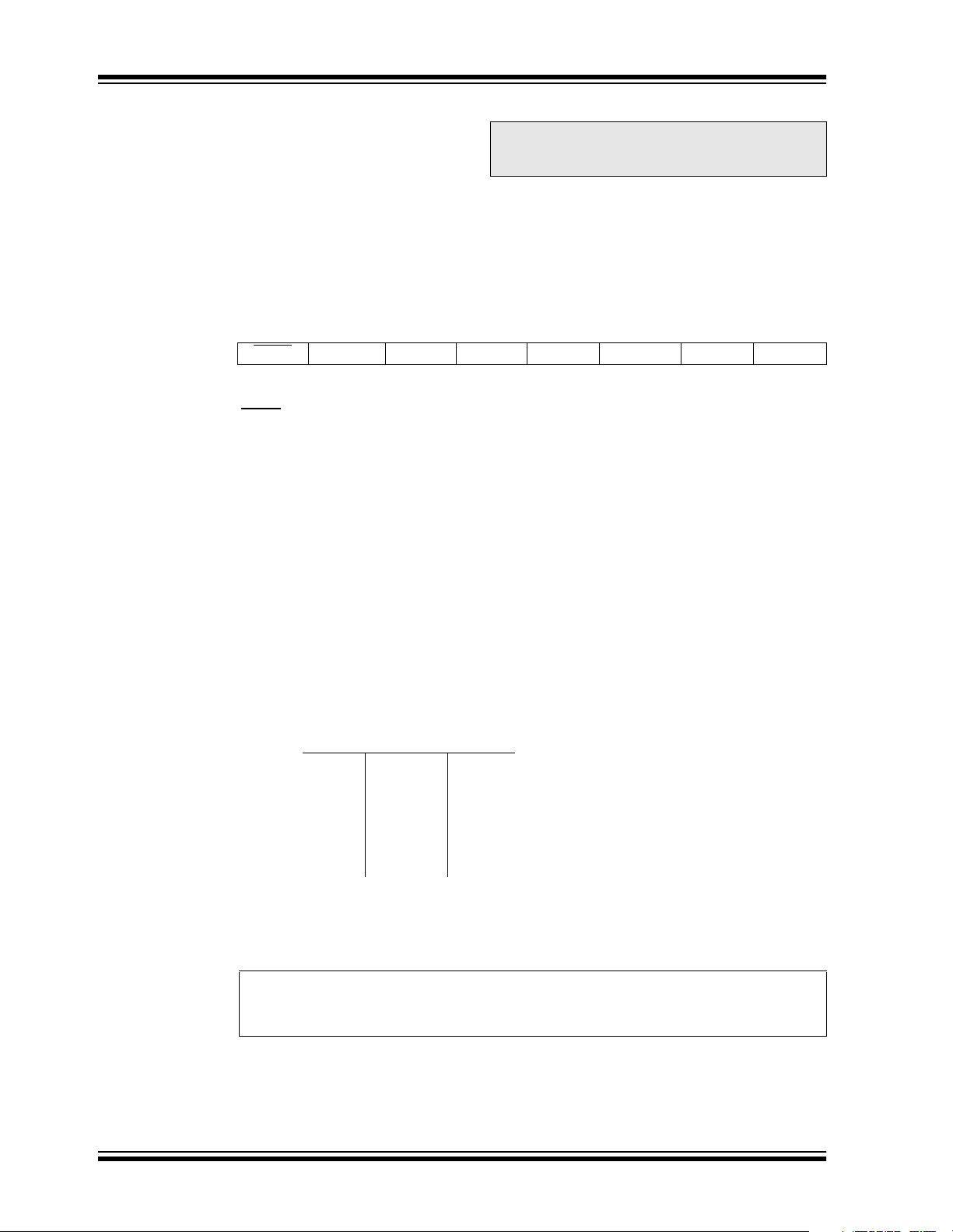

Pin Diagram

PDIP, Windowed CERDIP, SOIC, SSOP

RA0/AN0/OPA+

RA1/AN1/OPA-

RA4/T0CKI

RA5/MCLR

RA2/AN2/VREF2

RA3/AN3/V

RB0/INT/AN4/V

RB1/AN5/VDAC

/VPP

VSS

AVSS

REF1

R

20

•1

1

PIC16C781/782

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

RB3/AN7/OPA

20

RB2/AN6

19

19

RA7/OSC1/CLKIN

18

18

RA6/OSC2/CLKOUT/T1CKI

17

17

16

16

15

15

14

14

13

13

12

12

11

11

DD

V

AVDD

RB7/C2/PSMC1B/T1G

RB6/C1/PSMC1A

RB5

RB4

Peripheral Features:

• Timer0: 8-bit timer/counter with 8-bit prescaler

• Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Gate Input mode

- Option to use OSC1 and OSC2 in LP mode

as Timer1 osci llator, if INTRC oscillator m ode

selected

• Analog-to-Digital Converter (ADC):

- 8-bit resolution

- Programmable 8-channel input

- Internal voltages available for self-

diagnostics

• Digital-to-Analog Converter (DAC):

- 8-bit resolution

- Reference from AV

- Output configurable to V

tors, and ADC reference

• Operational Amplifier module (OPA):

- Firmware initiated input offset voltage Auto

Calibration module

- Low leakage inputs

- Programmable Gain Bandwidth Product

(GBWP)

DD, VREF1, or VR module

DAC pin, Compara-

2001 Microchip Technology Inc. Preliminary DS41171A-page 1

Page 4

PIC16C781/782

Peripheral Features (Continued):

• Dual Analog Comparator module with:

- Individual enable and interrupt bits

- Programmable speed and output polarity

- Fully configurabl e inputs and outputs

- Reference from DAC, or V

- Low input offset voltage.

• V

R voltage reference module :

- 3.072V +/- 0.7% @25°C, AV

- Configurable output to ADC reference, DAC

reference, and V

- 5 mA sink/sourc e

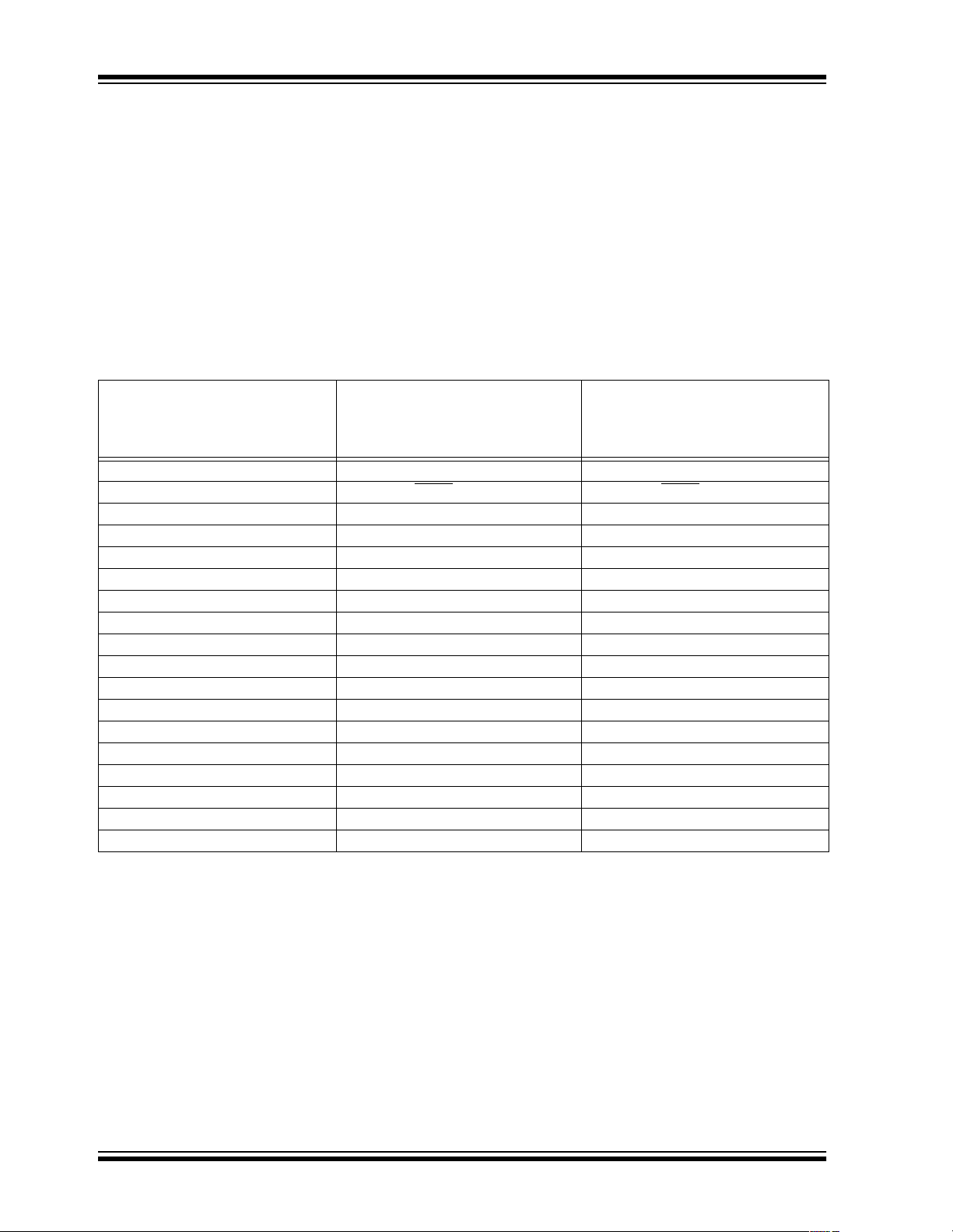

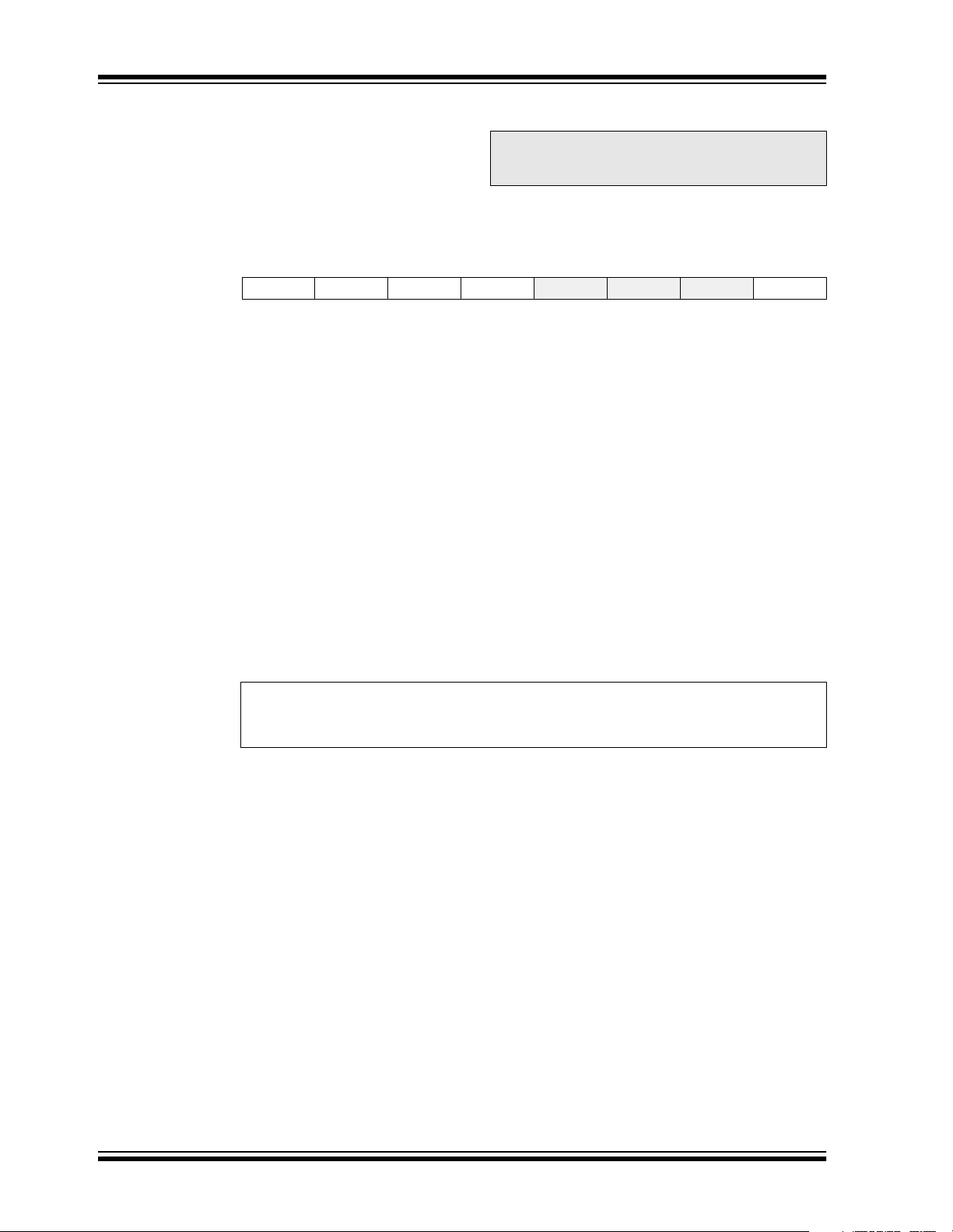

Key Features

PICmicro™ Mid-Range

Reference Manual

Operating Frequency DC - 20 MHz DC - 20 MHZ

RESETS (and Delays) POR, BOR, MCLR

Program Memory (14 bit words) 1K 2K

Data Memory (bytes) 128 128

Interrupts 8 8

I/O Ports 13 + 3 Input only 13 + 3 Input only

Timers 2 2

Programmable Switch Mode Controller 1 1

8-bit Analog-to-Digital Module 1 1

ADC channels 8 External, 2 Internal 8 External, 2 Internal

8-bit Digital-to-Analog Module 1 1

Comparators 2 2

Comparator Channels 4 (AN<7:4>) 4 (AN<7:4>)

Operational Amplifier 1 1

Voltage Reference 1 1

Brown-out Reset Yes Yes

Programmable Low Voltage Detect Yes Yes

Instructi on Set 35 Instr uctions 35 Instruct ions

R pin

(DS33023)

REF1/VREF2

DD = 5V

PIC16C781 PIC16C782

• Programmable Switch Mode Controller module:

- PWM and PSM modes

- Programmable switching frequency

- Configurable for either single or dual

feedback inputs

- Configurable single or dual outputs

- Slope compensation output available in

single output mode

, WDT (PWRT , OST) POR, BOR, MCLR, WDT (PWRT, OST)

DS41171A-page 2 Preliminary 2001 Microchip Technology Inc.

Page 5

PIC16C781/782

Table of Contents

1.0 Device Overview ......................................................................................................................................................................... 5

2.0 Memory Organization ................................................................................................................................................................11

3.0 I/O Ports ................... ................. ................ ................. ................. ................. ............................................................................. 25

4.0 Program Memory Read (PMR) . ................................................................................................................................................. 47

5.0 Timer0 Module .......................................................................................................................................................................... 51

6.0 Timer1 Module with Gate Control .............................................................................................................................................. 55

7.0 Voltage Reference Module (V

8.0 Programmable Low Voltage Detect Module (PLVD) ................................................................................................................. 63

9.0 Analog-to-Digital Converter (ADC) Module ...............................................................................................................................69

10.0 Digital-to-Analog Converter (DAC) Module ...............................................................................................................................79

11.0 Operational Amplifier (OPA) Module ......................................................................................................................................... 83

12.0 Comparator Module ................................................................................................................................................................... 89

13.0 Programmable Switch Mode Contr o lle r (PSMC) ............ .................................. .................................. ....................................... 99

14.0 Special Features of The CPU ....................................... .................................. ......................................................................... 117

15.0 Instruction Set Summary ......................................................................................................................................................... 133

16.0 Development Support .............................................................................................................................................................. 141

17.0 Electrical Characteristics ......................................................................................................................................................... 147

18.0 DC and AC Characteristics Graphs and Tables ...................................................................................................................... 167

19.0 Packaging Information ................... ................. ................ ................. ........................................................................................ 169

Index ..................................................................................................................................................................................................175

On-Line Support.................................................................................................................................................................................181

Reader Response.............................................................................................................................................................................. 182

PIC16C781/782 Product Identification System................................................................... ......... .. .... ................................................183

R) ................................................................................................................................................ 61

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or c omm ents regarding th is publication, p lease c ontact the M a rketing Communications Department via

E-mail at docerrors@mail.microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150.

We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision

of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

• The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

Customer Notification System

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

2001 Microchip Technology Inc. Preliminary DS41171A-page 3

Page 6

PIC16C781/782

NOTES:

DS41171A-page 4 Preliminary 2001 Microchip Technology Inc.

Page 7

PIC16C781/782

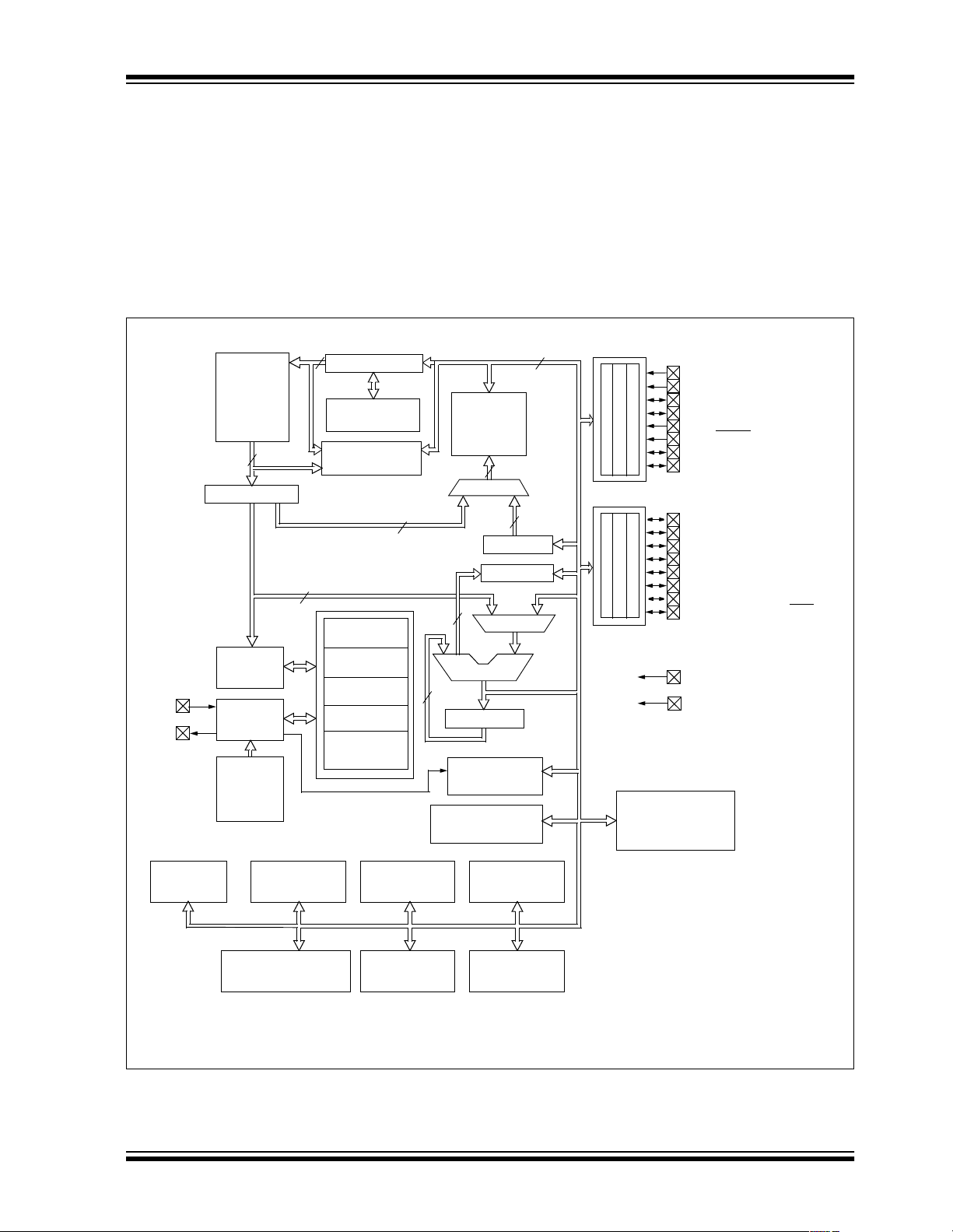

1.0 DEVICE OVERVIEW

This document contains device-specific information.

Additional information m ay be found in the PICm ic ro™

Mid-Range Reference Manual (DS33023), which may

be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The

Reference manual should be considered a complementary document to this data sheet. The Reference

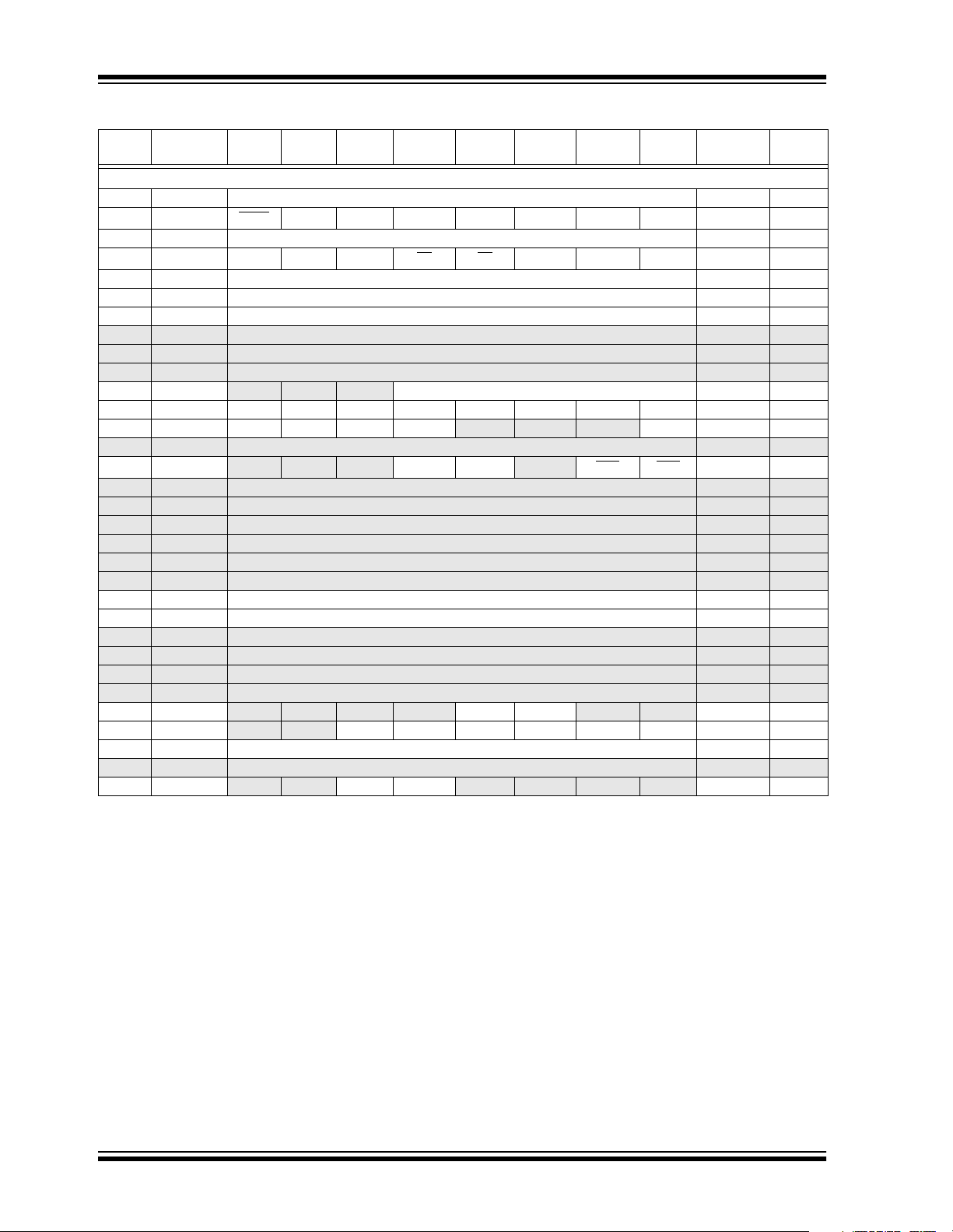

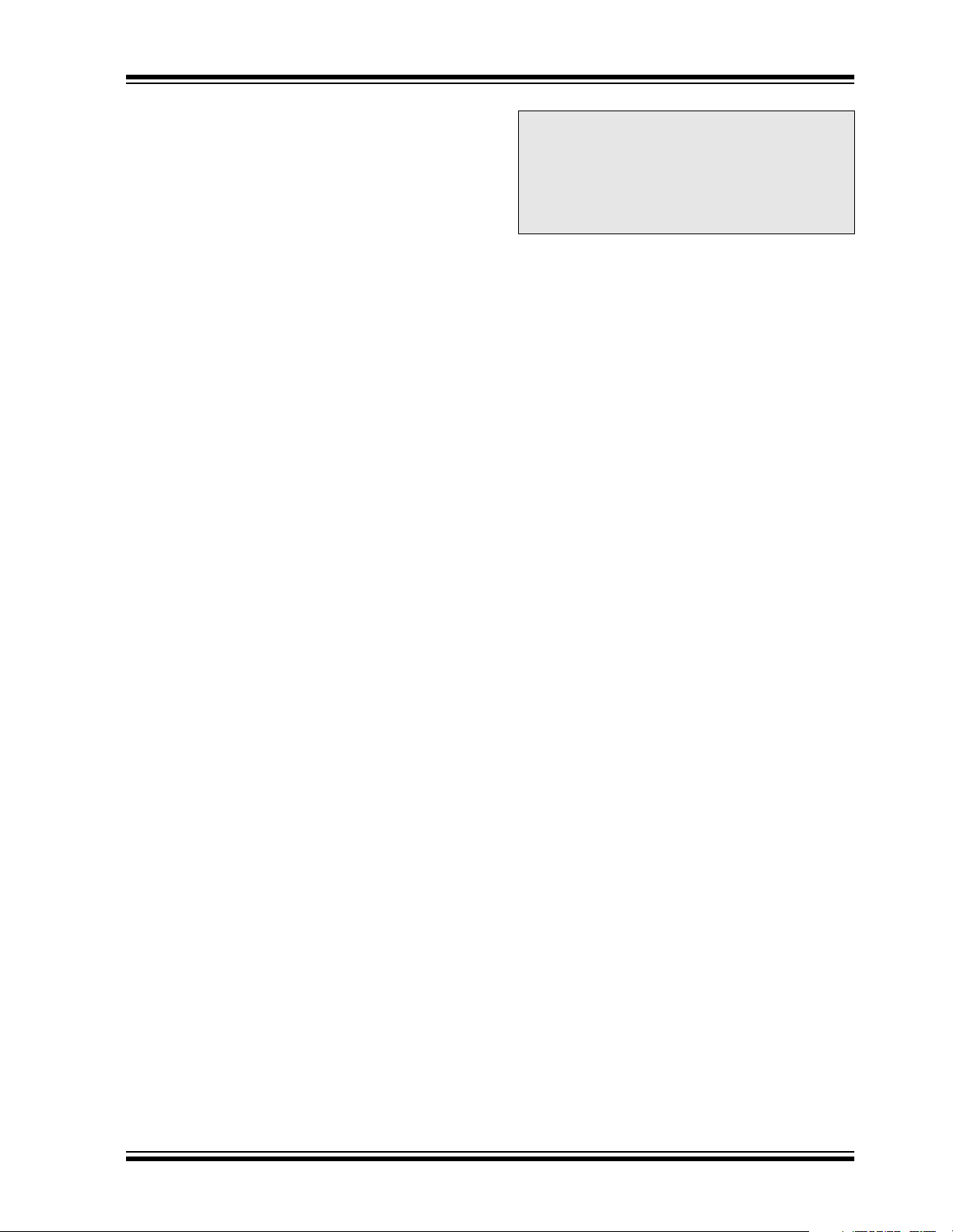

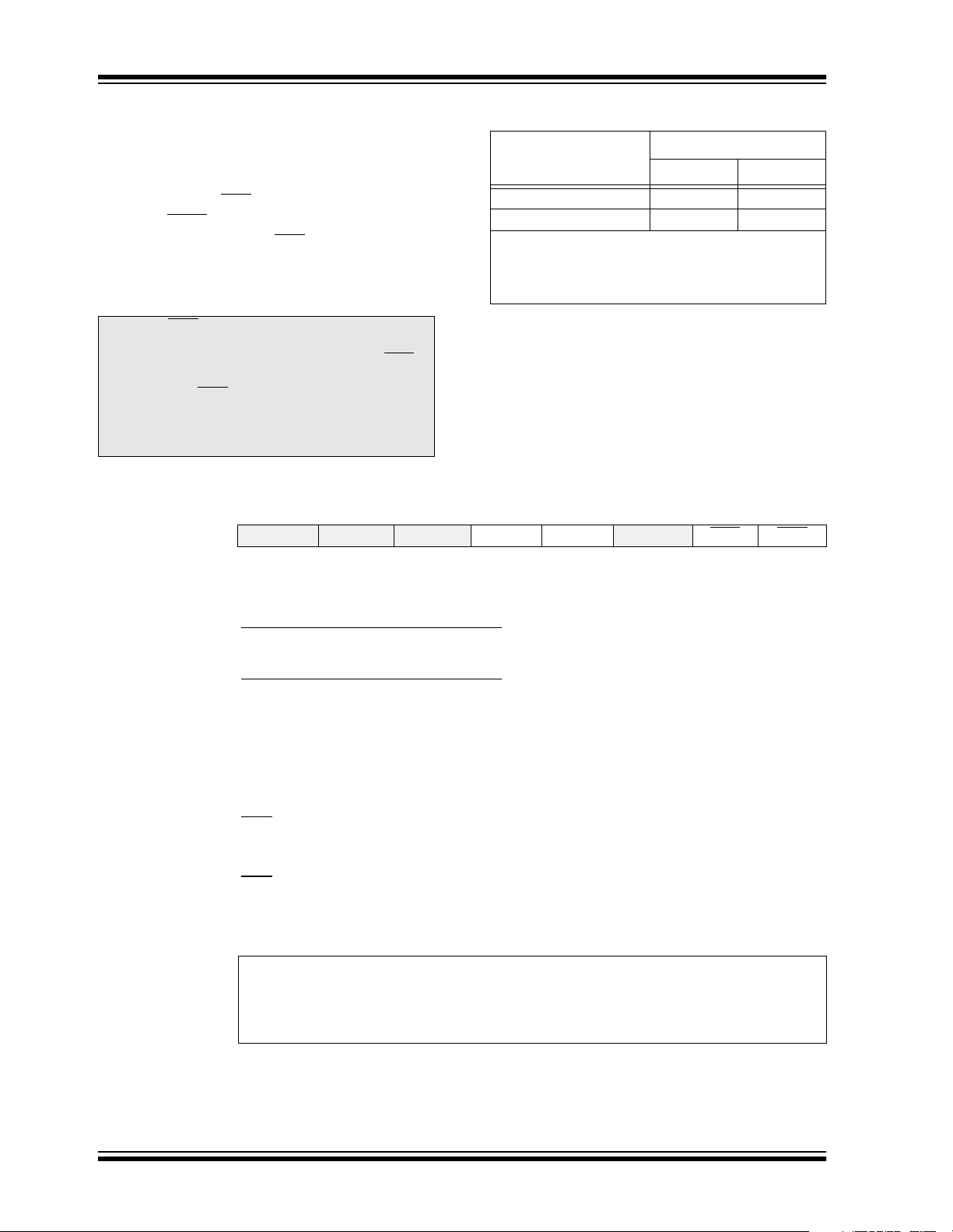

FIGURE 1-1: PIC16C781 BLOCK DIAGRAM

Program

Bus

OSC1/

CLKIN

OSC2/

CLKOUT

EPROM

Program

Memory

1K x 14

14

Instruction reg

Instruction

Decode &

Control

Timing

Generation

Internal

RC

Oscillator

INTRC

13

Program Counter

8 Level Stack

(13-bit)

Program Memory

Read (PMR)

Direct Addr

8

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

Brown-out

Reset

7

Data Bus

RAM

File

Registers

128 x 8

RAM

Addr

Addr MUX

3

ALU

8

W reg

Timer1

(TMR1)

Voltage Reference

(VR) Module

manual is highly recommended reading for a better

understanding o f the d ev ic e arc hi tec ture a nd operation

of the peripheral modules.

This data sheet covers two devices: PIC16C781 and

PIC16C782. Both devices come in a variety of 20-pin

packages.

The following figures are block diagrams of the

PIC16C781 and the PIC16C782.

8

9

Indirect

8

Addr

FSR reg

STATUS r eg

MUX

PORTA

PORTB

Programmable

Low Voltage Detect

(PLVD)

RA0/AN0/OPA+

RA1/AN1/OPARA2/AN2/VREF2

RA3/AN3/VREF1

RA4/T0CKI

RA5/MCLR

RA6/OSC2/CLKOUT/T1CKI

RA7/OSC1/CLKIN

RB0/INT/AN4/VR

RB1/AN5/VDAC

RB2/AN6

RB3/AN7/OPA

RB4

RB5

RB6/C1/PSMC1A

RB7/C2/PSMC1B/T1G

AVDD, AVSS

DD, VSS

V

/VPP

(1)

Timer0

(TMR0)

Note 1: AVDD and AVSS pins are used by the following modules: C1, C2, OPA, DAC, ADC, and VR.

2001 Microchip Technology Inc. Preliminary DS41171A-page 5

Comparator

(C1)

Programmable Switch

Mode Controller

(PSMC)

Comparator

(C2)

OPAMP

(OPA)

8-bit ADC

8-bit

DAC

Page 8

PIC16C781/782

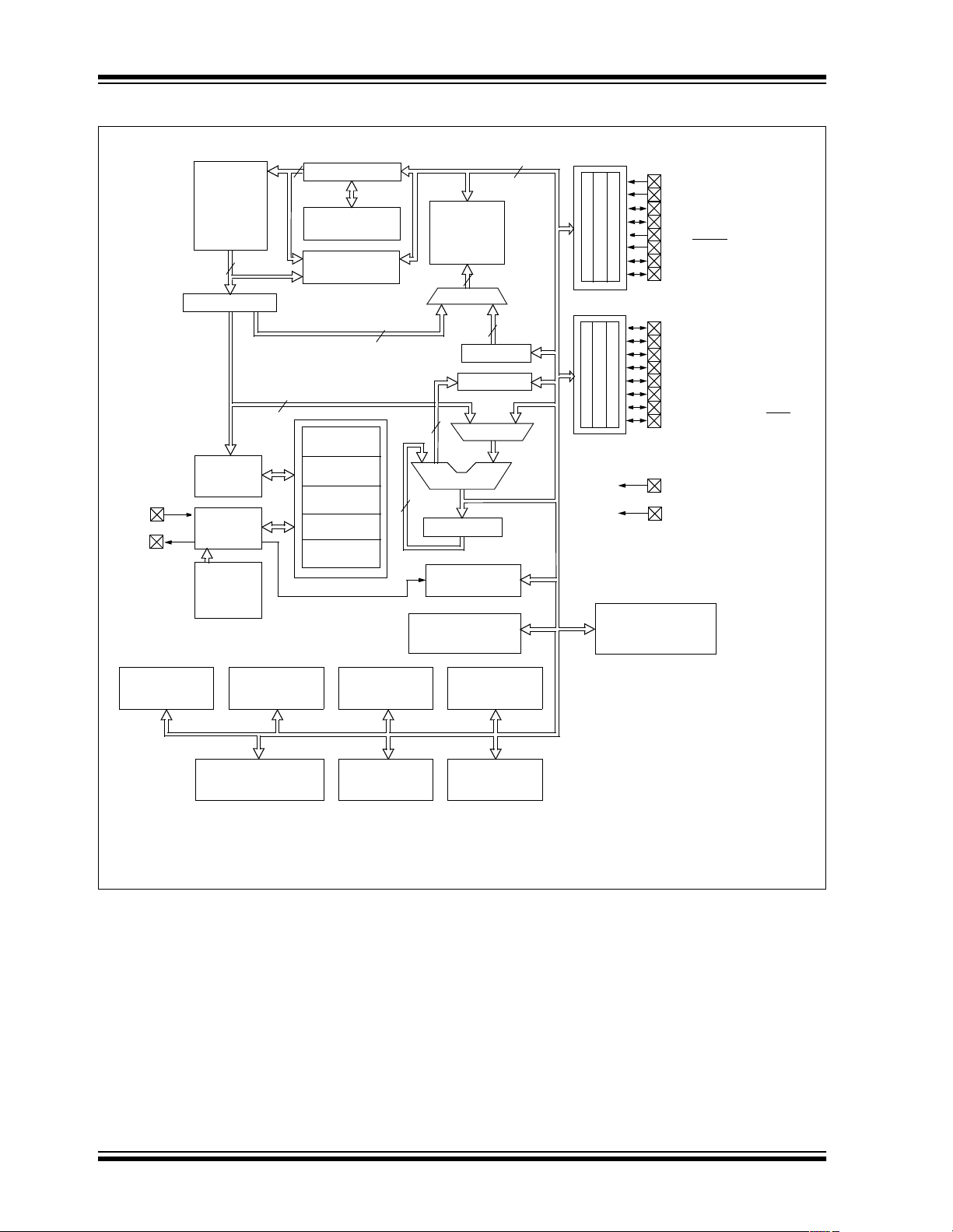

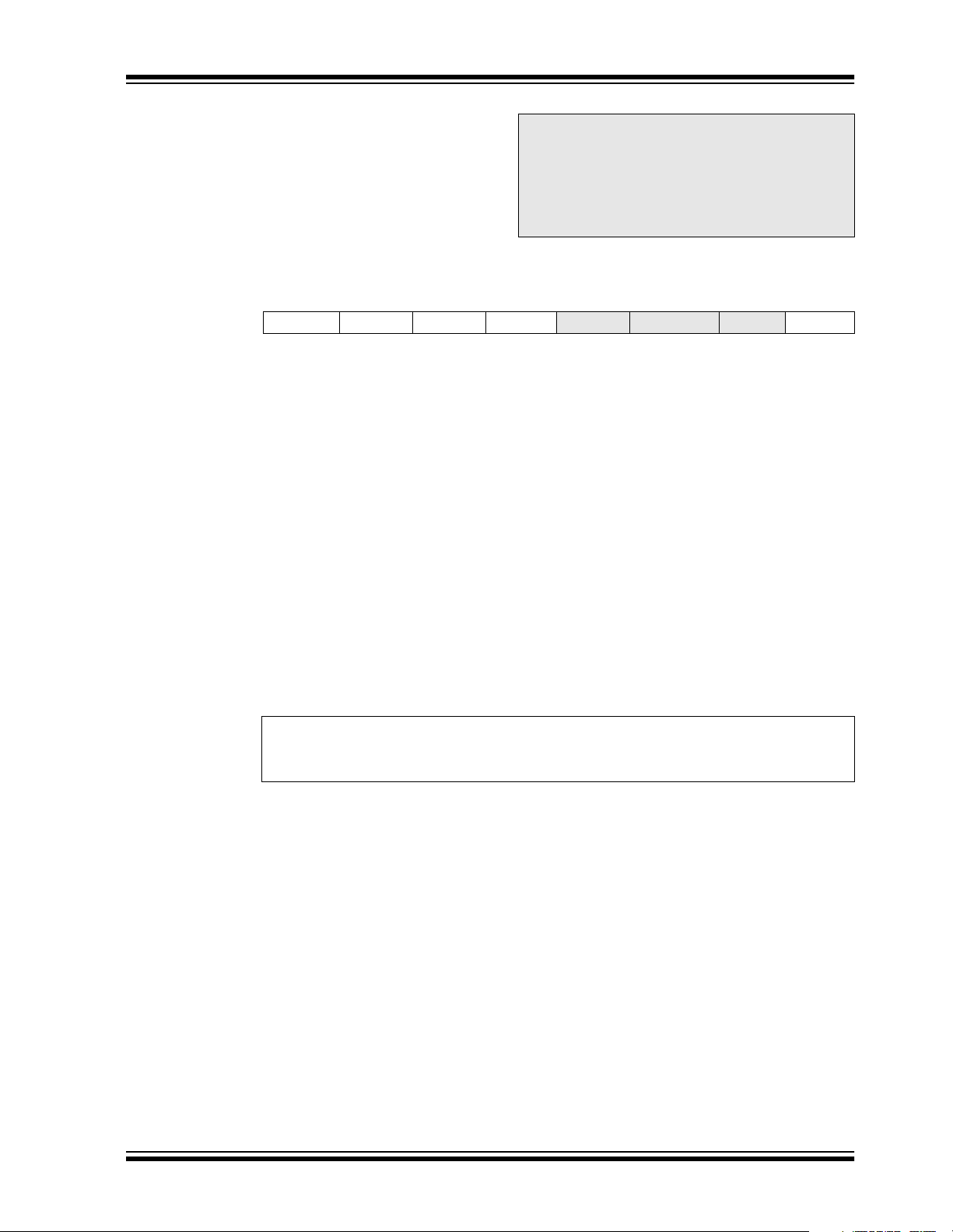

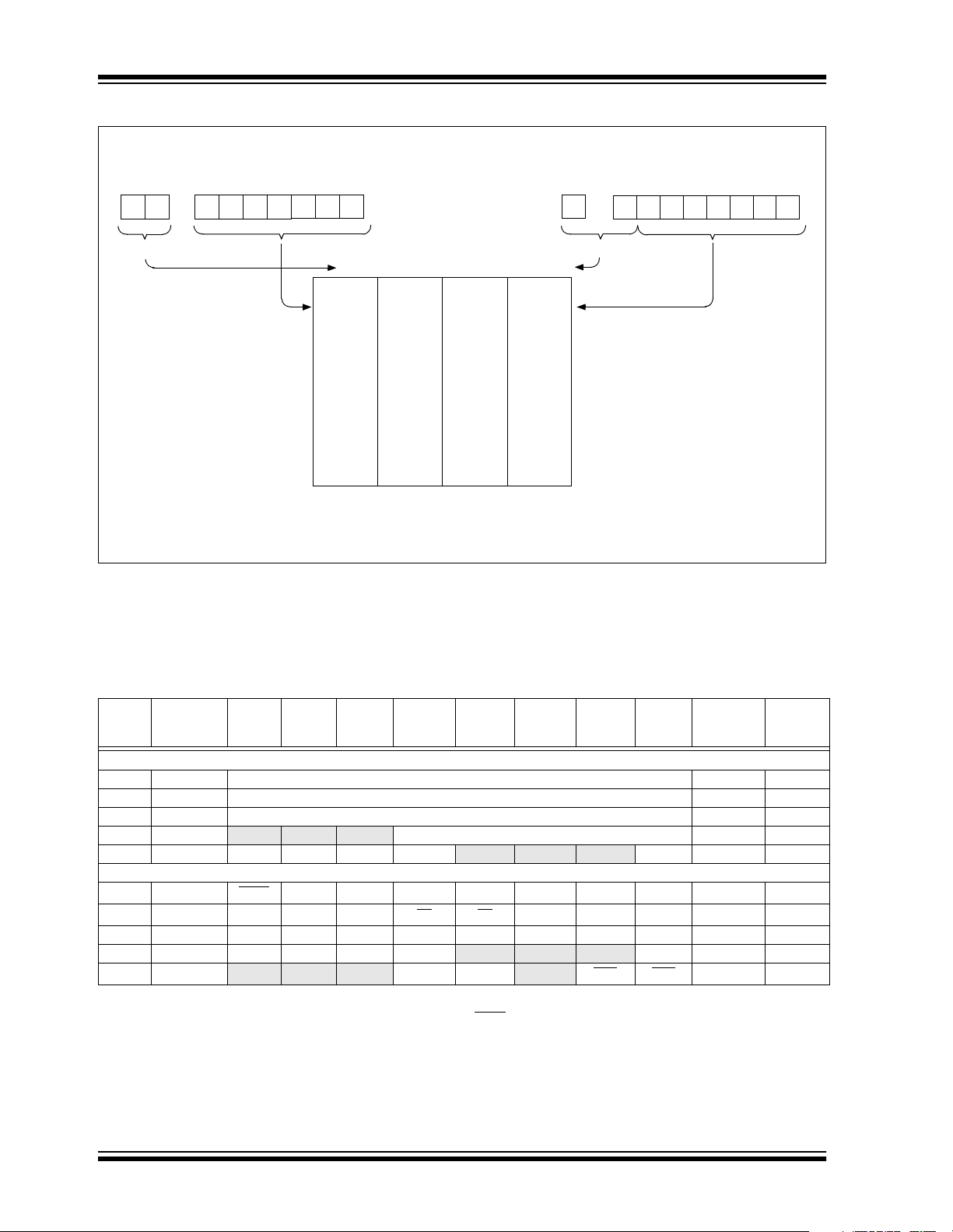

FIGURE 1-2: PIC16C782 BLOCK DIAGRAM

Program

Bus

OSC1/

CLKIN

OSC2/

CLKOUT

EPROM

Program

Memory

2K x 14

14

Instruction reg

Instruction

Decode &

Control

Timing

Generation

Internal

RC

Oscillator

INTRC

13

Program Counter

8 Level Stack

(13-bit)

Program Memory

Read (PMR)

Direct Addr

8

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

Brown-out

Reset

RAM

Addr

7

3

8

Voltage Reference

Data Bus

RAM

File

Registers

128 x 8

Addr MUX

FSR reg

STATUS reg

ALU

W reg

Timer1

(TMR1)

Module

R)

(V

9

8

MUX

8

Indirect

Addr

PORTA

PORTB

Programmable

Low Voltage Detect

PLVD

RA0/AN0/OPA+

RA1/AN1/OPARA2/AN2/VREF2

RA3/AN3/VREF1

RA4/T0CKI

RA5/MCLR

RA6/OSC2/CLKOUT/T1CKI

RA7/OSC1/CLKIN

RB0/INT/AN4/VR

RB1/AN5/VDAC

RB2/AN6

RB3/AN7/OPA

RB4

RB5

RB6/C1/PSMC1A

RB7/C2/PSMC1B/T1G

AVSS, AVSS

DD, VSS

V

/VPP

(1)

Timer0

TMR0

Note 1: AVDD and AVSS pins are used for the following modules: C1, C2, OPA, DAC, ADC, and VR.

Comparator

C1

Programmable Switch

Mode Controller

PSMC

Comparator

C2

OPAMP

OPA

8-bit ADC

8-bit

DAC

DS41171A-page 6 Preliminary 2001 Microchip Technology Inc.

Page 9

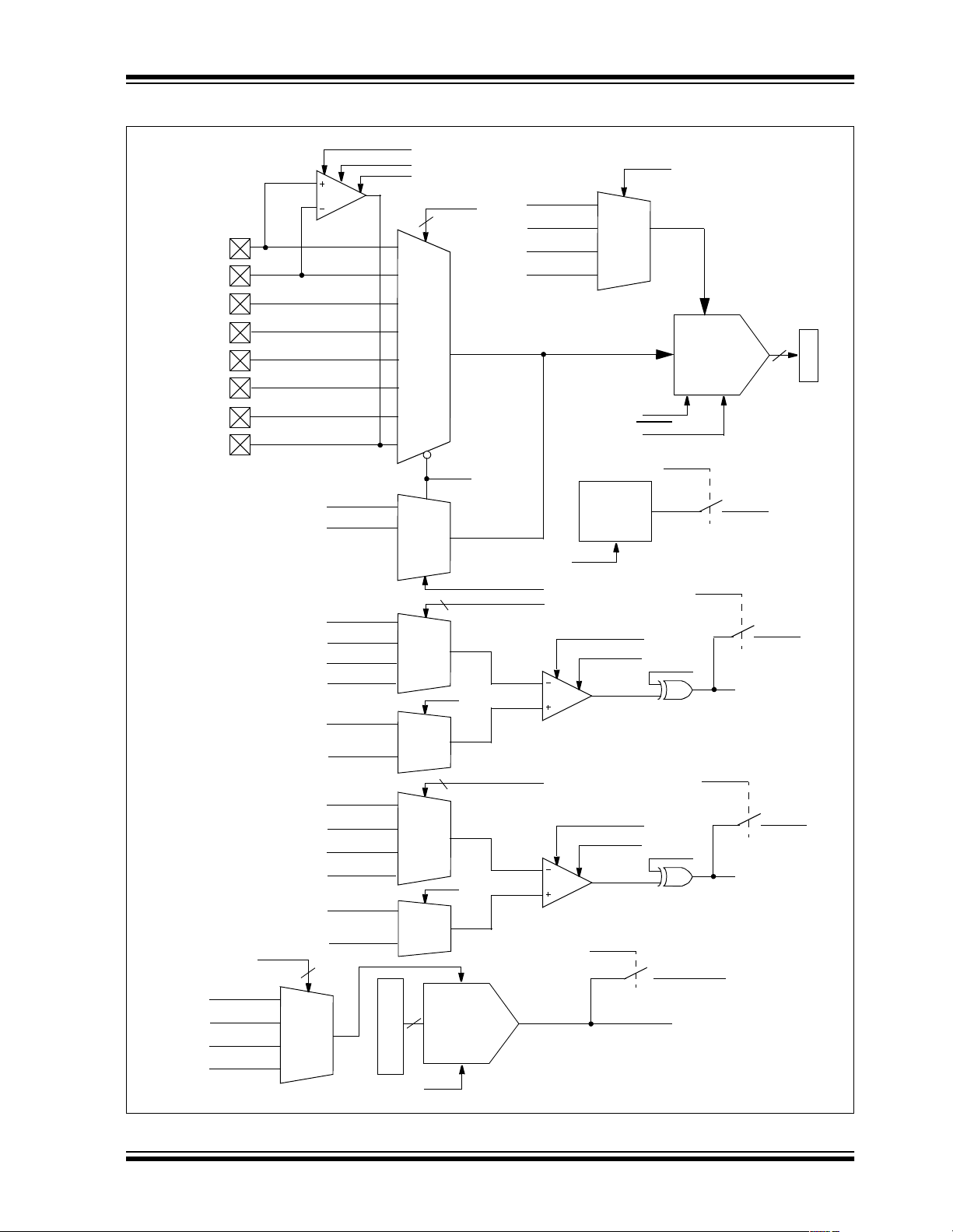

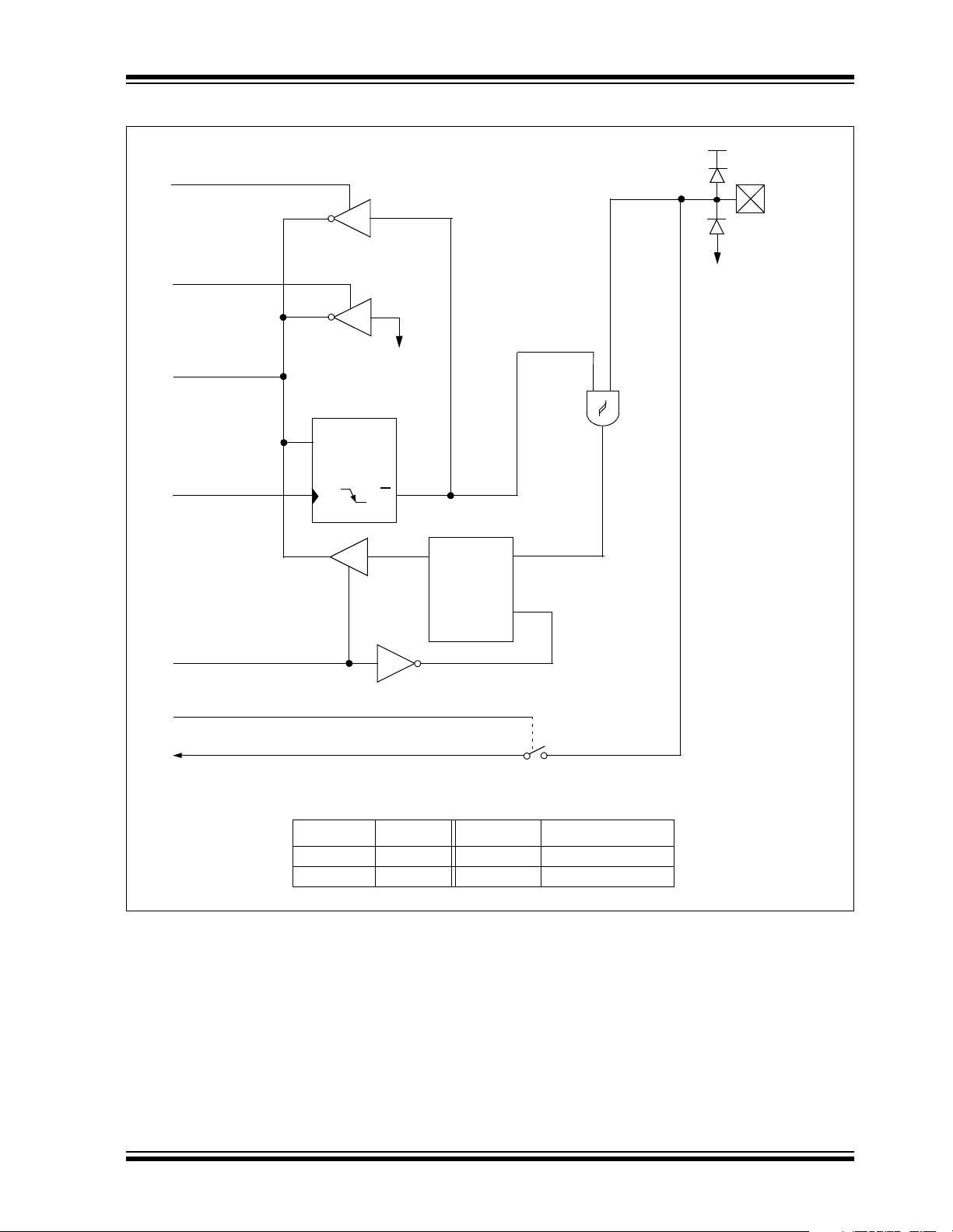

FIGURE 1-3: ANALOG SIGNAL MULTIPLEXING DIAGRAM

PIC16C781/782

RA0/AN0/OPA+

RA1/AN1/OPA-

RA2/AN2/V

RA3/AN3/V

REF2

REF1

RB0/INT/AN4/V

RB1/AN5/VDAC

RB2/AN6

RB3/AN7/OPA

AV

VREF1

V

N/C

R

DARS<1:0>

DD

R

OPAON

CMPEN

VCFG<1:0>

GBWP

OPA

CHS<2:0>

3

0

1

DD

AV

VREF1

R

V

V

DAC

0

1

2

3

2

3

4

ADCREF

ADC

8

ADRES

5

ADON

GO/DONE

VR

REFERENCE

VROE & VREN

AN4

R

V

VDAC

6

EN

7

CHS3

EN

0

1

VREN

2

C1CH<1:0>

AN4

AN5

AN6

AN7

V

REF1

DAC

V

AN4

AN5

AN6

AN7

V

REF2

DAC

V

0

1

2

3

C1R

C1

C1ON

C1SP

0

1

2

C2CH<1:0>

0

1

C2ON

C2SP

2

3

C2R

C2

0

1

DAON & DAOE

2

DAC

CHS0

0

1

8

REF

DAC

C1OE

RB6/C1/

PSMC1A

C1POL

C1OUT

C2OE

RB7/C2

PSMC1B

C2POL

C2OUT

AN4

VDAC

2

3

DAC REGISTER

DAON

2001 Microchip Technology Inc. Preliminary DS41171A-page 7

Page 10

PIC16C781/782

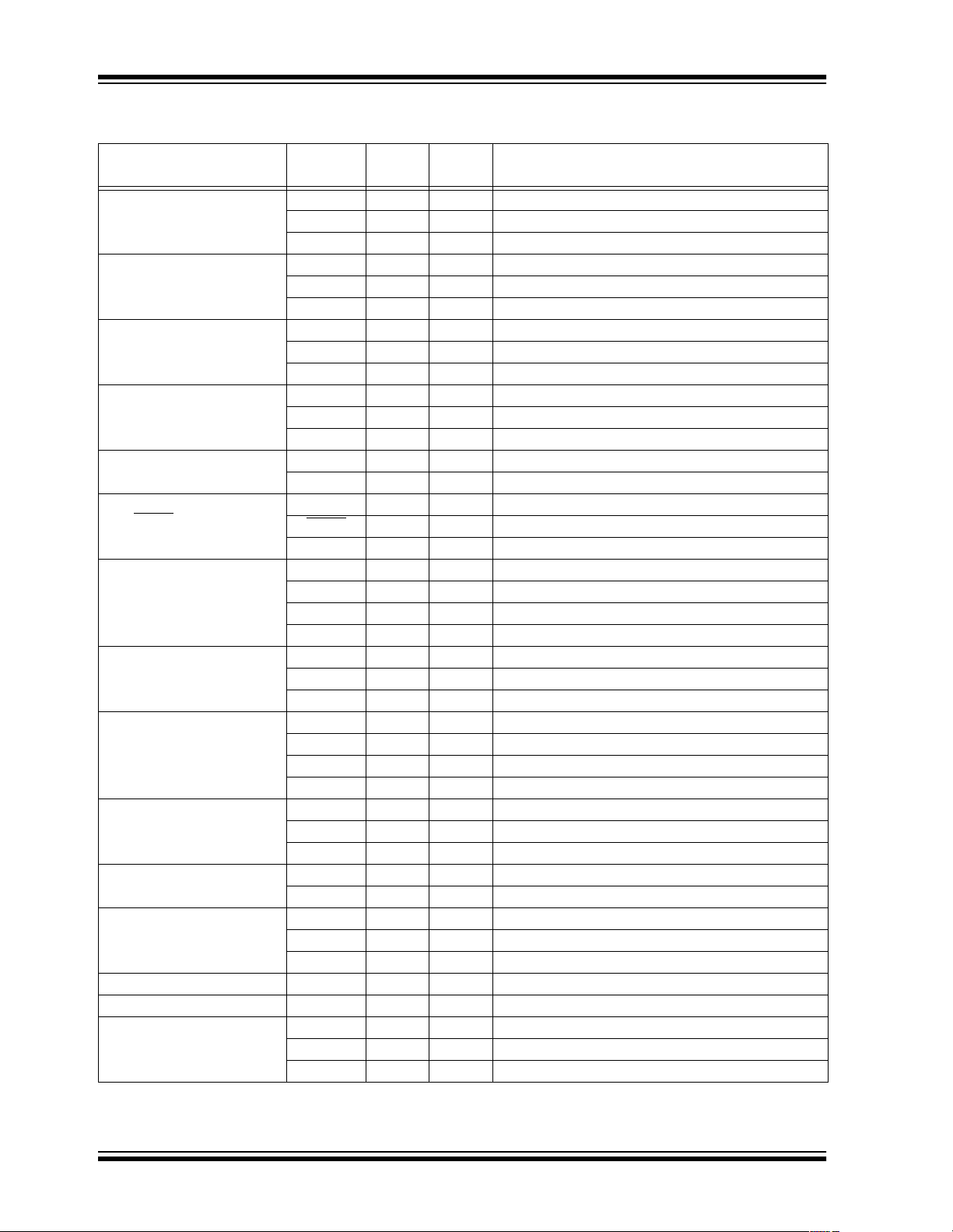

TABLE 1-1: PIC16C781/782 PINOUT DESCRIPTION

Name Function

Input

Type

Output

Type

RA0 ST N/A Port Input

RA0/AN0/OPA+

AN0 AN

OPA+ AN

— ADC Input

— OPAMP Non-inverting I nput

RA1 ST N/A Port Input

RA1/AN1/OPA-

AN1 AN

OPA- AN

— ADC Input

— OPAMP Inverting Input

RA2 ST CMOS Bi-directional I/O

RA2/AN2/V

REF2

AN2 AN

REF2AN — Comparator 2 Voltage Refere nc e Input

V

— ADC Input

RA3 ST CMOS Bi-directional I/O

RA3/AN3/V

REF1

AN3 AN

REF1AN — Comparator 1, ADC, DACREF Input

V

— ADC Input

RA4/T0CKI RA4 ST OD Bi-directional I/O

TOCKI ST — Timer0 Clock Input

RA5 ST N/A Port Input

RA5/MCLR

/VPP

MCLR ST — Master Clear Input

VPP Power — Programming Voltage

RA6 ST CMOS Bi-directional I/O

RA6/OSC2/CLKOUT/T1CKI

OSC2

CLKOUT — CMOS Fosc/4 Output

T1CKI ST

— XTAL Crystal/Resonator

— Timer1 Clock Input

RA7 ST CMOS Bi-directional I/O

RA7/OSC1/CLKIN

OSC1 XTAL — Crystal/Resonator

CLKIN ST

— External Clock Input

RB0 TTL CMOS Bi-directional I/O

RB0/INT/AN4/VR

INT ST — External Interrupt

AN4 AN

— ADC, Compara tor Input

VR — AN Internal Voltage Reference Output

RB1 TTL CMOS Bi-directional I/O

RB1/AN5/V

DAC

AN5 AN

— ADC, Compara tor Input

VDAC — AN DAC Output

RB2/AN6

RB2 TTL CMOS Bi-directional I/O

AN6 AN

— ADC, Compara tor Input

RB3 TTL CMOS Bi-directional I/O

RB3/AN7/OPA

AN7 AN — ADC, Comparator Input

OPA

— AN OPAMP Output

RB4 RB4 TTL CMOS Bi-directional I/O

RB5 RB5 TTL CMOS Bi-directional I/O

RB6 TTL CMOS Bi-directional I/O

RB6/C1/PSMC1A

C1

— CMOS Comparator 1 Output

PSMC1A — CMOS PSMC Output 1A

Description

DS41171A-page 8 Preliminary 2001 Microchip Technology Inc.

Page 11

PIC16C781/782

TABLE 1-1: PIC16C781/782 PINOUT DESCRIPTION (CONTINUED)

Name Function

RB7 TTL CMOS Bi-directional I/O

RB7/C2/PSMC1B/T1G

DD AVDD Power — Positive Supply for Analog

AV

SS AVSS Power — Ground Reference for Analog

AV

VDD VDD Power — Positive Supply for Logic and I/O pins

SS VSS Power — Ground Reference for Logic and I/O pins

V

Legend: ST = Schmitt Trigger AN = Analog OD = open drain TTL = Logic Level

XTAL = Crystal CMOS = CMOS Output Power = Power Supply

C2 — CMOS Comparator 2 Output

PSMC1B

T1G ST — Timer 1 Gate Input

Input

Type

Output

Type

— CMOS PSMC Output 1B

Description

2001 Microchip Technology Inc. Preliminary DS41171A-page 9

Page 12

PIC16C781/782

NOTES:

DS41171A-page 10 Preliminary 2001 Microchip Technology Inc.

Page 13

PIC16C781/782

2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these

PICmicro

data memory) has its own bus, so that concurrent

access can occur.

Additional informa tion on devi ce memory may be found

in the PICmicro™ Mid-Range Reference Manual,

(DS33023).

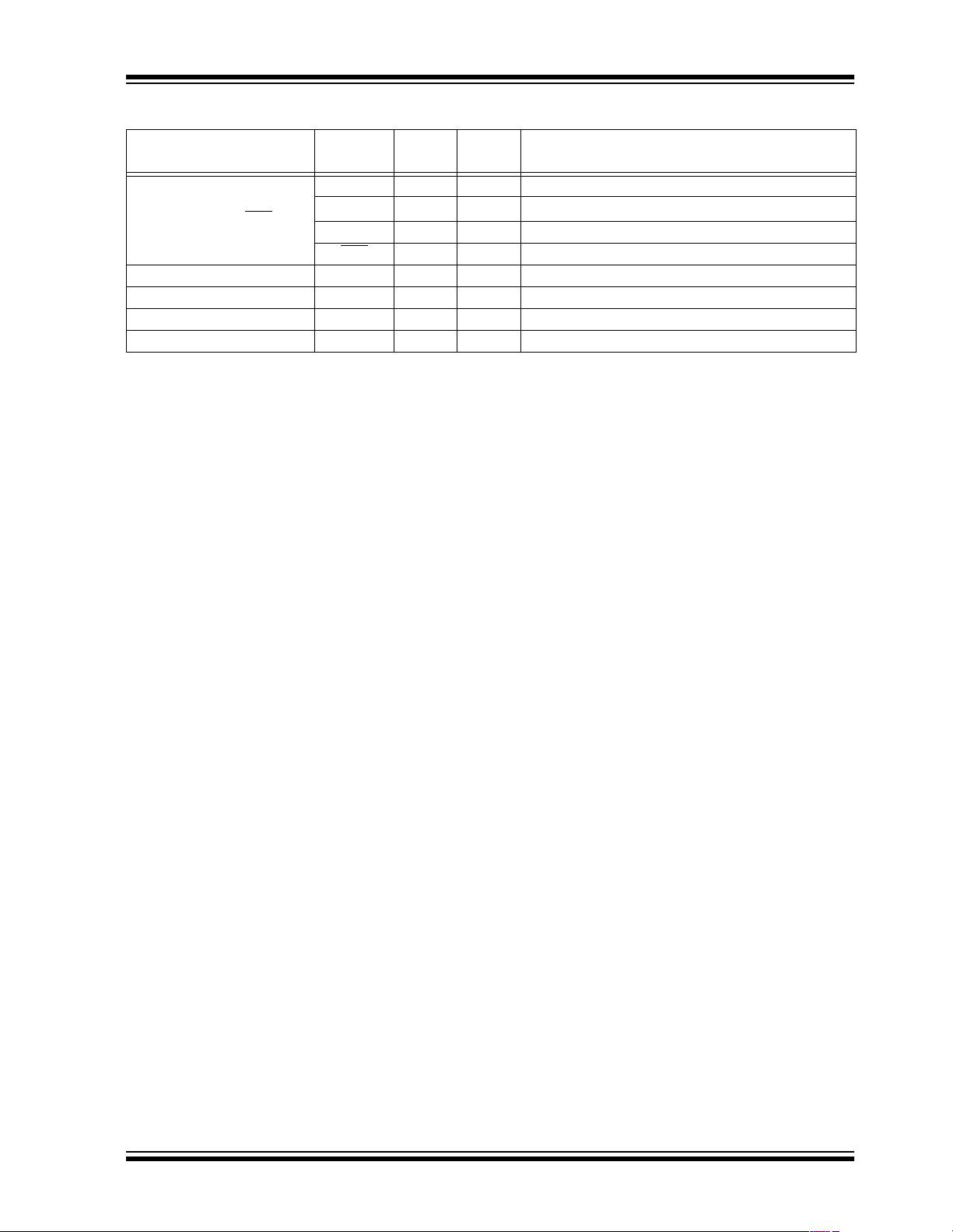

2.1 Program Memory Organization

The PIC16C781/782 devices have a 13-bit program

counter capable of addressing an 8K x 14 program

memory space. The PIC16C781 has 1K x 14 words of

program memo ry. The PIC16C 782 has 2K x 14 w ords

of program memory. Accessing a location above the

physically i mplemented addr ess ca uses a wrap aroun d.

The RESET vector is at 0000h and the interrupt vector

is at 0004h.

FIGURE 2-1: PIC16C781 PROGRAM

®

microcontrollers. Each block (program and

MEMORY MAP AND

STACK

PC<12:0>

FIGURE 2-2: PIC16C782 PROGRAM

MEMORY MAP AND

STACK

PC<12:0>

CALL, RETURN

RETFIE, RETLW

On-Chip

Program

Memory

Stac k Lev el 1

Stack Level 2

Stack Level 8

RESET Vector

Interrupt Vector

Page 0

13

0000h

0004h

0005h

07FFh

0800h

CALL, RETURN

RETFIE, RETLW

On-Chip

Program

Memory

13

Stack Level 1

Stack Le vel 2

Stac k Lev el 8

RESET Vector

Interrupt Vector

Page 0

0000h

0004h

0005h

03FFh

0400h

1FFFh

1FFFh

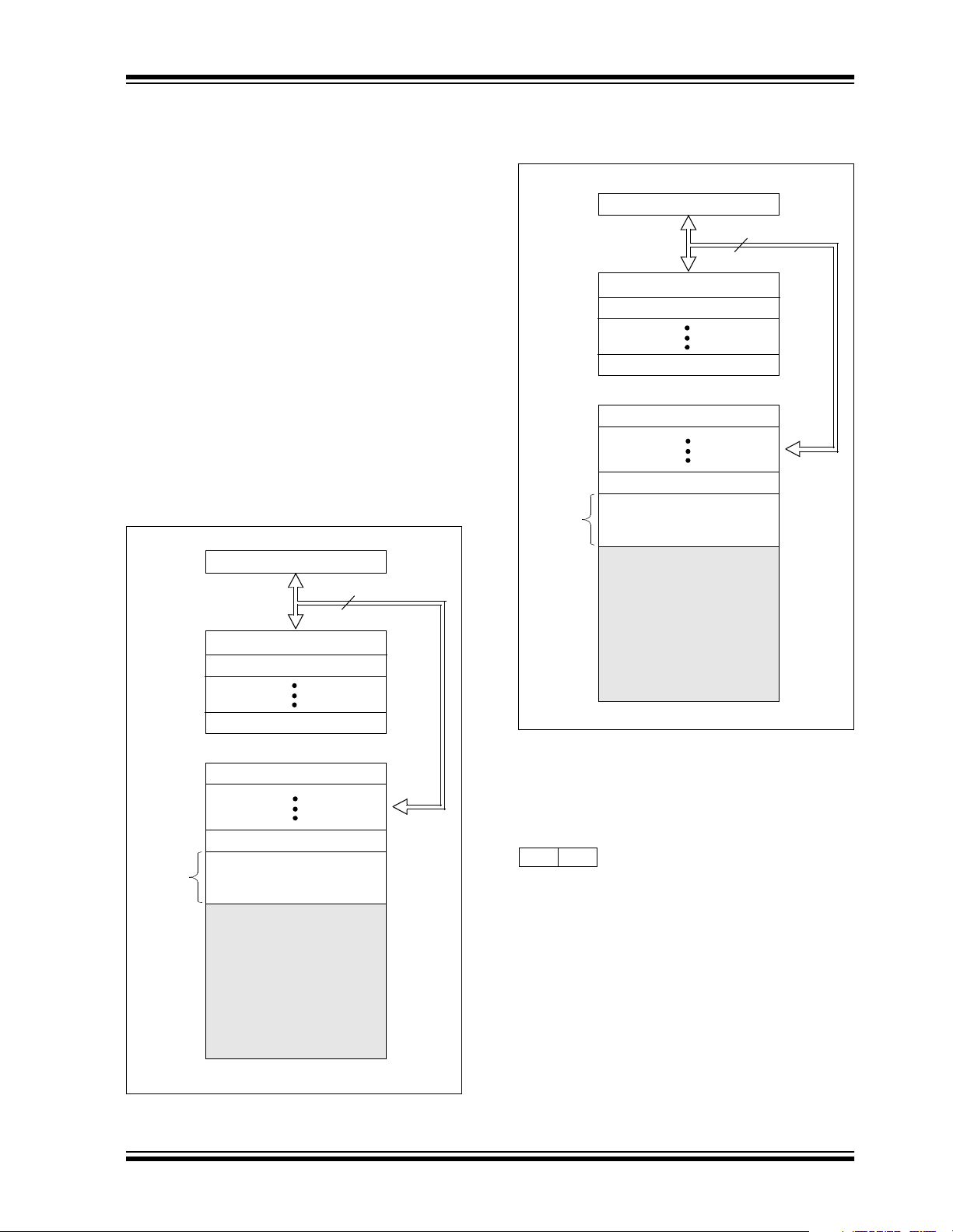

2.2 Data Memory Organization

The data memory is partitioned into multiple banks,

which contain the General Purpose Registers and the

Special Function Registers. Bits RP0 and RP1 are

bank select bits.

RP1 RP0 (STATUS<6:5>)

= 00 → Bank0

= 01 → Bank1

= 10 → Bank2

= 11 → Bank3

Each bank extends up to 7Fh (128 bytes). The lower

locations of each bank are reserved for the Special

Function Registers. Above the Special Function Registers are th e Genera l Purpos e Regist ers, im plement ed

as static RAM. All implemented banks contain Special

Function Registers. Some frequently used Special

Function Registers from one bank are mirrored in

another bank for code reduction and quicker access.

2001 Microchip Technology Inc. Preliminary DS41171A-page 11

Page 14

PIC16C781/782

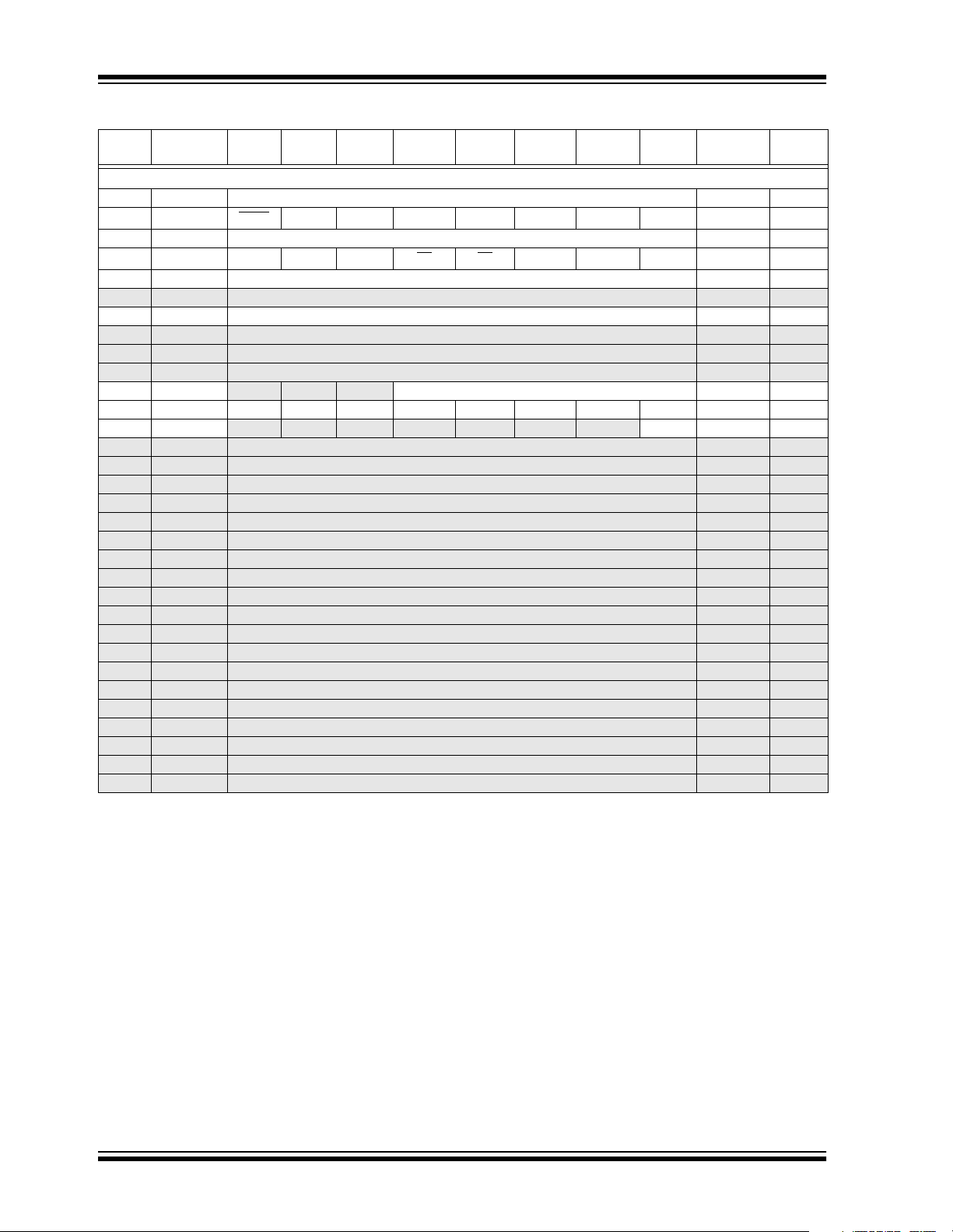

FIGURE 2-3: REGISTER FILE MAP

File

Address

Indirect addr.

TMR0

PCL

STATUS

FSR

PORTA

PORTB

PCLATH

INTCON

PIR1

TMR1L

TMR1H

T1CON

ADRES

ADCON0

General

Purpose

Register

96 Bytes

Bank 0 Bank 1

(*)

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

0Dh

0Eh

0Fh

10h

11h

12h

13h

14h

15h

16h

17h

18h

19h

1Ah

1Bh

1Ch

1Dh

1Eh

1Fh

20h

7Fh

Indirect addr.

OPTION_REG

REFCON

LVDCON

ADCON1

General

Purpose

Register

32 Bytes

accesses

70h-7Fh

PCL

STATUS

FSR

TRISA

TRISB

PCLATH

INTCON

PIE1

PCON

WPUB

IOCB

ANSEL

File

Address

(*)

80h

81h

82h

83h

84h

85h

86h

87h

88h

89h

8Ah

8Bh

8Ch

8Dh

8Eh

8Fh

90h

91h

92h

93h

94h

95h

96h

97h

98h

99h

9Ah

9Bh

9Ch

9Dh

9Eh

9Fh

A0h

BFh

EFh

F0h

FFh

Indirect addr.

TMR0

PCL

STATUS

FSR

PORTB

PCLATH

INTCON

PMDATL

PMADRL

PMDATH

PMADRH

CALCON

PSMCCON0

PSMCCON1

CM1CON0

CM2CON0

CM2CON1

OPACON

DAC

DACON0

accesses

70h-7Fh

Bank 2

File

Address

(*)

100h

101h

102h

103h

104h

105h

106h

107h

108h

109h

10Ah

10Bh

10Ch

10Dh

10Eh

10Fh

110h

111h

112h

113h

114h

115h

116h

117h

118h

119h

11Ah

11Bh

11Ch

11Dh

11Eh

11Fh

120h

170h

17Fh

Indirect addr.

OPTION_REG

PCL

STATUS

FSR

TRISB

PCLATH

INTCON

PMCON1

accesses

70h-7Fh

Bank 3

File

Address

(*)

180h

181h

182h

183h

184h

185h

186h

187h

188h

189h

18Ah

18Bh

18Ch

18Dh

18Eh

18Fh

190h

191h

192h

193h

194h

195h

196h

197h

198h

199h

19Ah

19Bh

19Ch

19Dh

19Eh

19Fh

1A0h

1F0h

1FFh

Unimplemented data memory locations, read as ’0’.

* Not a physical register.

DS41171A-page 12 Preliminary 2001 Microchip Technology Inc.

Page 15

PIC16C781/782

2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be acces sed either directly, or indirectly, through the File Select Register (FSR).

2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by

the CPU and Peripheral Modules for controlling the

desired operation of the device. These registers are

implemented as static RAM. A list of these registers is

given in Table 2-1.

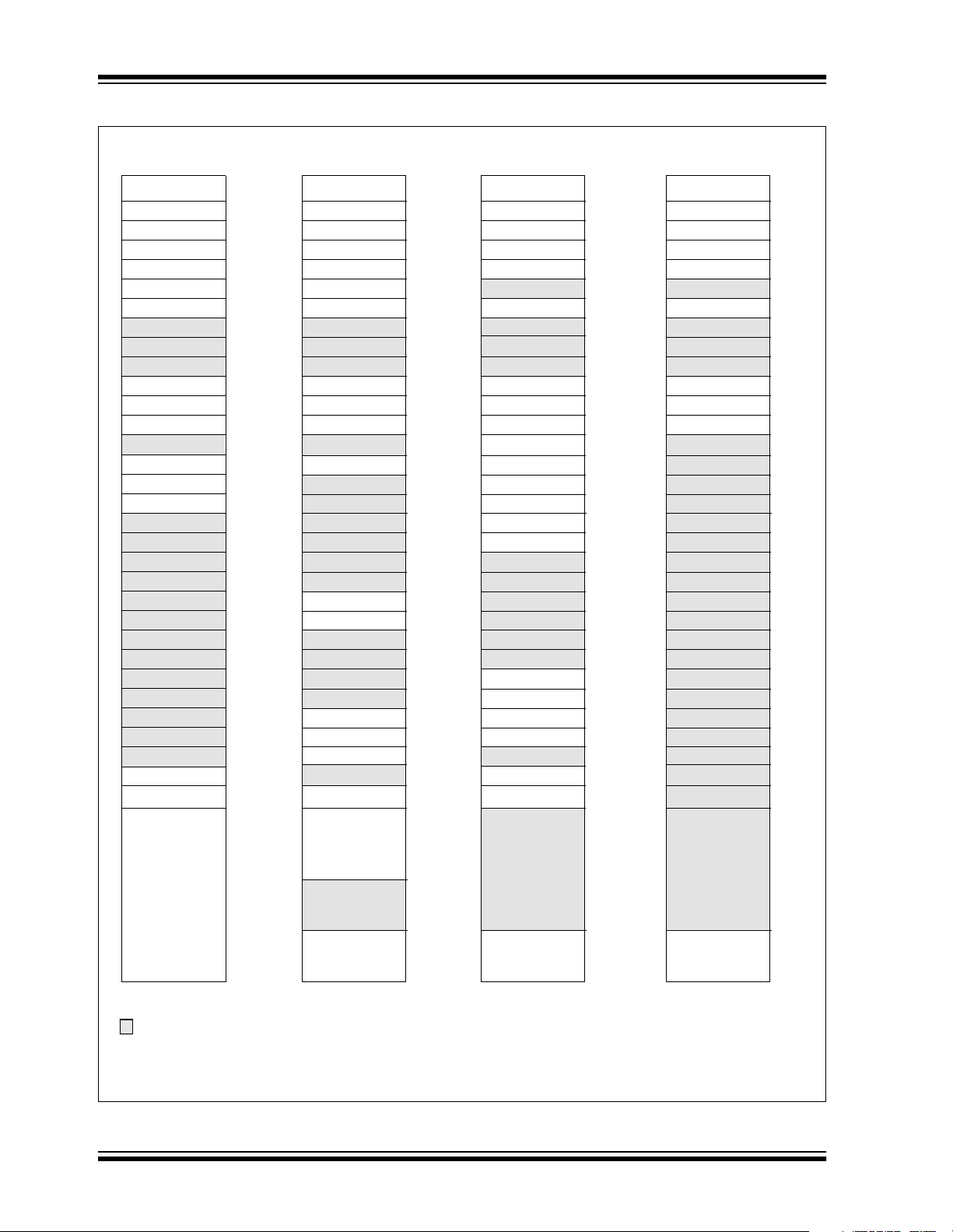

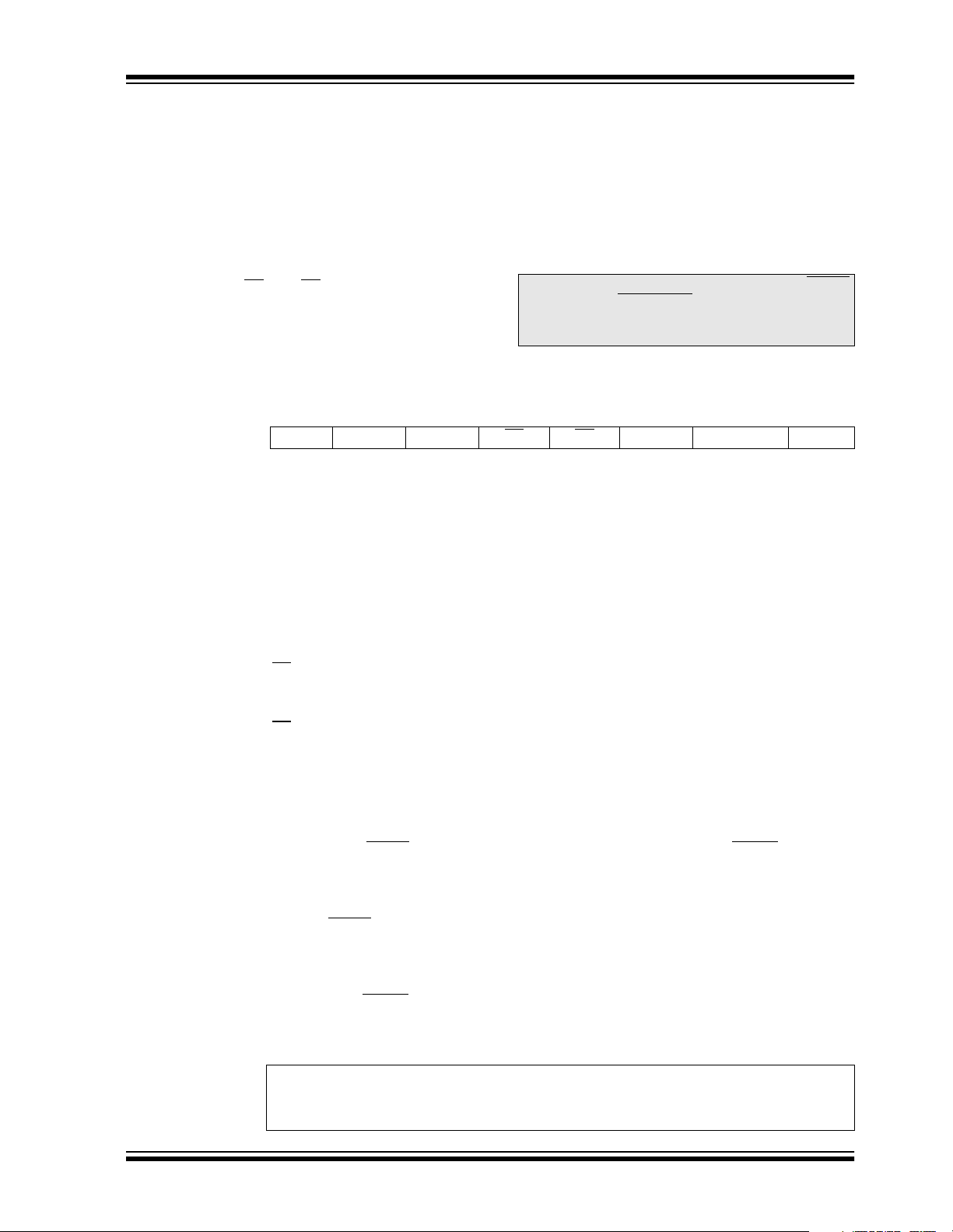

TABLE 2-1: PIC16C781/782 SPECIAL FUNCTION REGISTER SUMMARY

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bank 0

(2)

00h

01h TMR0 Timer0 Module’s Register

02h

03h

04h

05h PORTA RA7 RA6 RA5 RA4 RA3 RA2 RA1 RA0

06h PORTB RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0

07h — Unimplemented — —

08h — Unimplemented — —

09h — Unimplemented — —

0Ah

0Bh

0Ch PIR1 LVDIF ADIF C2IF C1IF

0Dh — Un implemented — —

0Eh TMR1L Holding register for the Least Significant Byte of the 16-bit TMR1 Register

0Fh TMR1H Holding register for the Most Significant Byte of the 16-bit TMR1 Register

10h T1CON

11h — Un implemented — —

12h — Unimplemented — —

13h — Unimplemented — —

14h — Unimplemented — —

15h — Unimplemented — —

16h — Unimplemented — —

17h — Unimplemented — —

18h — Unimplemented — —

19h — Unimplemented — —

1Ah — Unimplemented — —

1Bh — Unimplemented — —

1Ch — Un implemented — —

1Dh — Un implemented — —

1Eh ADRES ADC Result Register

1Fh ADCON0 AD CS1 ADCS0 CHS2 CHS1 CHS0 GO/DONE

Legend:

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are trans-

INDF Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 23

(2)

PCL Program Counter's (PC) Least Significant Byte 0000 0000 23

(2)

STATUS IRP RP1 RP0

(2)

FSR Indirect Data Memory Address Pointer xxxx xxxx 23

(1, 2)

PCLATH — — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 23

(2)

INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 19

— TMR1GE T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON -000 0000 57

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0'.

Shaded locations are unimplemented, read as ‘0’.

ferred to the upper byte of the program counter. See Section 2.9 for more detail.

2: These registers can be addressed from any bank.

TO

PD

— — — TMR1IF 0000 ---0 21

ZDCC0001 1xxx 17

CHS3 ADON 0000 0000 70

Value on:

POR, BOR

xxxx xxxx 51

xxxx 0000 26

xxxx 0000 35

xxxx xxxx 55

xxxx xxxx 55

xxxx xxxx 71

Details on

Page:

2001 Microchip Technology Inc. Preliminary DS41171A-page 13

Page 16

PIC16C781/782

TABLE 2-1: PIC16C781/782 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bank 1

(2)

80h

81h OPTION_REG RBPU

82h

83h

84h

85h TRISA PORTA Data Direction Register

86h TRISB PORTB Data Direction Register

87h — Unimplemented — —

88h — Unimplemented — —

89h — Unimplemented — —

8Ah

8Bh

8Ch PIE1 LVDIE ADIE C2IE C1IE

8Dh — Un implemented

8Eh PCON

8Fh Unimplemented — —

90h — Unimplemented — —

91h — Unimplemented — —

92h — Unimplemented — —

93h — Unimplemented — —

94h — Unimplemented — —

95h WPUB PORTB Weak Pull-up Control

96h IOCB PORTB Interrupt-on-Change Control

97h — Unimplemented — —

98h — Unimplemented — —

99h — Unimplemented — —

9Ah — Unimplemented — —

9Bh REFCON

9Ch LVDCON

9Dh ANSEL Analog Channel Select

9Eh — Unimplemented — —

9Fh ADCON1

Legend:

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are trans-

INDF Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 23

(2)

PCL Program Counter’s (PC) Least Significant Byte 0000 0000 23

(2)

STATUS IRP RP1 RP0 TO PD ZDCC0001 1xxx 17

(2)

FSR Indirect Data Memory Address Pointer xxxx xxxx 23

(1,2)

PCLATH — — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 23

(2)

INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 19

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0'.

Shaded locations are unimplemented, read as ‘0’.

ferred to the upper byte of the program counter. See Section 2.9 for more detail.

2: These registers can be addressed from any bank.

INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 18

— — — TMR1IE 0000 ---0 20

— — — WDTON OSCF — POR BOR ---q 1-qq 22, 120

— — — — VREN VROE — ---- 00-- 61

— — BGST LVDEN LV3 LV2 LV1 LV0 --00 0101 66

— — VCFG1 VCFG0 — — — — --00 ---- 71

Value on:

POR, BOR

1111 1111 26

1111 1111 35

1111 1111 36

1111 0000 36

1111 1111 25

Details on

Page:

DS41171A-page 14 Preliminary 2001 Microchip Technology Inc.

Page 17

Bank 2

(2)

100h

101h TMR0 Time r0 Mod ul e ’s Register

102h

103h

INDF Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 23

(2)

PCL Program Counter's (PC) Least Significant Byte 0000 0000 23

(2)

STATUS IRP RP1 RP0 6.18Tc0.001 .52 981/F9st88Q(P1)-3216.1(99( C)-5.2)-14.9(am)-14.9( C)-5.2(o)1.2(u)-16.1(n1(e. )1069 )iuinaOED 01nt Byte

PIC16C781/782

xxxx xxxx 51

2001 Microchip Technology Inc. Preliminary DS41171A-page 15

Page 18

PIC16C781/782

TABLE 2-1: PIC16C781/782 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bank 3

(2)

180h

181h OPTION_REG RBPU

182h

183h

184h

185h — Un implemented — —

186h TRISB PORTB Data Direction Register

187h — Un implemented — —

188h — Un implemented — —

189h — Un implemented — —

18Ah

18Bh

18Ch PMCON1

18Dh — Unimplemented — —

18Eh — Unimplemented — —

18Fh — Unimplemented — —

190h — Un implemented — —

191h — Un implemented — —

192h — Un implemented — —

193h — Un implemented — —

194h — Un implemented — —

195h — Un implemented — —

196h — Un implemented — —

197h — Un implemented — —

198h — Un implemented — —

199h — Un implemented — —

19Ah — Unimplemented — —

19Bh — Unimplemented — —

19Ch — Unimplemented — —

19Dh — Unimplemented — —

19Eh — Unimplemented — —

19Fh — Unimplemented — —

Legend:

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are trans-

INDF Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 23

(2)

PCL Program Counter’s (PC) Least Significant Byte 0000 0000 23

(2)

STATUS IRP RP1 RP0 TO PD ZDCC0001 1xxx 17

(2)

FSR Indirect Data Memory Address Pointer xxxx xxxx 23

(1,2)

PCLATH — — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 23

(2)

INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 19

Reserved — — — — — — RD 1--- ---0 47

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0'.

Shaded locations are unimplemented, read as ‘0’.

ferred to the upper byte of the program counter. See Section 2.9 for more detail.

2: These registers can be addressed from any bank.

INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 18

Value on:

POR, BOR

1111 1111 35

Details on

Page:

DS41171A-page 16 Preliminary 2001 Microchip Technology Inc.

Page 19

PIC16C781/782

2.3 STATUS Register

The STATUS register, shown in Register 2-1, contains

the arithmetic st atus of th e ALU, the RE SET statu s and

the bank select bits for data memory.

The STATUS register can be the destination for any

instruction, as with any other register. If the STATUS

register is the destination for an instruction that affects

the Z, DC, or C bits, the write to these three bits is disabled. These bits are set or cleared according to the

device logic. The TO

Therefore, the result of an instruction with the STATUS

register as the destination may be different than

intended.

and PD bits are not writable.

For example, CLRF STATUS cle ars the upper thr ee bit s

and sets the Z bit. This leaves the STA T US register a s

000u u1uu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF,

SWAPF and MOVWF instructions are used to alter the

STATUS register, since these instructions do not affect

the Z, C, or DC bits fro m the ST A TUS registe r. Fo r other

instructions not affecting any status bits, see the

"Instruction Set Summary."

Note: The C and DC bits operate as a borrow

and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF

instructions for examples.

REGISTER 2-1: STATUS REGISTER (STATUS: 03h, 83h, 103h, 183h)

R/W-0 R/W-0 R/W-0 R-1 R-1 R/W-x R/W-x R/W-x

IRP RP1 RP0 TO

bit7 bit0

bit 7 IRP: Register Bank Select bit (used for indirect addressing)

1 = Bank 2, 3 (100h - 1FFh)

0 = Bank 0, 1 (00h - FFh)

bit 6-5 RP<1:0>: Register Bank Select bits (used for direct addressing)

11 = Bank 3 (180h - 1FFh)

10 = Bank 2 (100h - 17Fh)

01 = Bank 1 (80h - FFh)

00 = Bank 0 (00h - 7Fh)

Each bank is 128 bytes

bit 4 TO

bit 3 PD

bit 2 Z: Zero bit

bit 1 DC: Digit carry/borrow

bit 0 C: Carry/borrow

: Time-out bit

1 = After power-up, CLRWDT instruction, or SLEEP instruction

0 = A WDT time-out occurred

: Power-down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

bit (ADDWF, ADDLW,SUBLW,SUBWF instructio ns) (for borrow, the polarity

is reversed)

1 = A carry-out from the 4th low order bit of the result occurred

0 = No carry-out from the 4th low order bit of the result

bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

PD ZDCC

Note: For bo rrow, the polarity is reversed. A subtraction is executed by adding the two’s

compleme nt of th e sec ond ope rand . For rotate (RRF, RLF) instructions, this bit is

loaded with either the high or low order bit of the source register.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

2001 Microchip Technology Inc. Preliminary DS41171A-page 17

Page 20

PIC16C781/782

2.4 OPTION_REG Register

The OPTION_REG register is a readable and writable

register which contains various control bits to configure:

• TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler)

• External INT interrupt

• TMR0

• Weak pull-ups on PORTB

REGISTER 2-2: OPTION REGISTER (OPTION_REG: 81h, 181h)

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1

RBPU

bit7 bit0

bit 7 RBPU

1 = PORTB weak pull-ups are disabled

0 = PORTB weak pull-ups are enabled by the WPUB register

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin

0 = Interrupt on falling edge of RB0/INT pin

bit 5 T0CS: TMR0 Clock Source Select bit

1 = Transition on RA4/T0CKI pin

0 = Internal instruction cycle clock ( F

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI pin

0 = Increment on low-to-high transition on RA4/T0CKI pin

bit 3 PSA: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 PS<2:0>: Prescaler Rate Select bits

INTEDG T0CS T0SE PSA PS2 PS1 PS0

: PORTB Pull-up Enable bit

Bit Value TMR0 Rate WDT Rate

000

001

010

011

100

101

110

111

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

1 : 256

(1)

Note: To achieve a 1:1 prescaler assignment for

the TMR0 register, assign the prescaler to

the Watchdog Timer.

OSC/4)

1 : 1

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

Note 1: Individual weak pull-up s on RB pi ns can be e nabled/disa bled from the weak pul l-up

PORTB register (WPUB).

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

DS41171A-page 18 Preliminary 2001 Microchip Technology Inc.

Page 21

PIC16C781/782

2.5 INTCON Register

The INTCON register is a readable and writable register which contains:

• Enable and interrupt flag bits for TMR0 register

overflow

• Enable and interrupt flag bits for the external

interrupt (INT)

• Enable and interrupt flag bits for PORTB

Interrupt-on-Change (IOCB)

• Peripheral interrupt enable bit

• Global interrupt enable bit

Note: Interrupt flag bits are se t w he n an interrupt

condition occurs, re gardless of the state of

its corresponding enable bit, or the global

enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an

interrupt.

REGISTER 2-3: INTERRUPT CONTROL REGISTER (INTCON: 0Bh, 8Bh, 10Bh, 18Bh)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-x

GIE PEIE T01E INTE RBIE T0IF INTF RBIF

bit 7 bit 0

bit 7 GIE: Global Interrupt Enable bit

1 = Enables all unmasked interrupts

0 = Disables all interrupts

bit 6 PEIE: Peripheral Interrupt Enable bit

1 = Enables all unmasked peripheral interrupts

0 = Disables all peripheral interrupts

bit 5 T0IE: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 interrupt

0 = Disables the TMR0 interrupt

bit 4 INTE: RB0/INT External Interrupt Enable bit

1 = Enables the RB0/INT external interrupt

0 = Disables the RB0/INT external interrupt

bit 3 RBIE: RB Port Change Interrupt Enable bit

1 = Enables the RB port change interrupt

0

(1)

2001 Microchip Technology Inc. Preliminary DS41171A-page 19

Page 22

PIC16C781/782

2.6 PIE1 Register

The PIE1 register cont ains the ind ividual enab le bits for

the periph eral interrupts.

REGISTER 2-4: PERIPHERAL INTERRUPT ENABLE REGISTER (PIE1: 8Ch)

R/W-0 R/W-0 R/W-0 R/W-0 U-0 U-0 U-0 R/W-0

LVDIE ADIE C2IE C1IE

bit7 bit0

bit 7 LVDIE: Low Voltage Detect Interrupt Enable bit

1 = LVD interrupt is enabled

0 = LVD interrupt is disabled

bit 6 ADIE: Analog-to-Digital Converter Interrupt Enable bit

1 = Enables the Analog-to-Digital Converter interrupt

0 = Disables the Analog-to-Digital Converter interrupt

bit 5 C2IE: Comparator C2 Interrupt Enable bit

1 = Enables the Comparator C2 interrupt

0 = Disables the Comparator C2 interrupt

bit 4 C1IE: Comparator C1 Interrupt Enable bit

1 = Enables the Comparator C1 interrupt

0 = Disables the Comparator C1 interrupt

bit 3-1 Unimplemented: Read as '0'

bit 0 TMR1IE: TMR1 Overflow Interrupt Enable bit

1 = Enables the TMR1 overflow interrupt

0 = Disables the TMR1 overflow interrupt

Note: Bit PEIE (INTCON<6>) must be set to

enable any peripheral interrupt (see

Register 2-3).

— — — TMR1IE

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

DS41171A-page 20 Preliminary 2001 Microchip Technology Inc.

Page 23

PIC16C781/782

2.7 PIR1 Register

This register contains the individual flag bits for the

peripheral interrupts.

Note: Interrupt flag bits are se t w he n an interrupt

condition occurs, re gardless of the state of

its corresponding enable bit, or the global

enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an

interrupt.

REGISTER 2-5: PERIPHERAL INTERRUPT REGISTER (PIR1 0Ch)

R/W-0 R/W-0 R/W-0 R/W-0 U-0 U-0 U-0 R/W-0

LVDIF ADIF C2IF C1IF

bit7 bit 0

bit 7 LVDIF: Low Voltage Detect Interrupt Flag bit

1 = The supply volt age has fall en below t he spe cified LVD volt age (m ust be cle ared in s oftwa re)

0 = The supply voltage is greater than the specified LVD voltage

bit 6 ADIF: Analog-to-Digital Converter Interrupt Flag bit

1 = An ADC conversion completed (must be cleared in software)

0 = The ADC conversion is not complete

bit 5 C2IF: Comparator C2 Interrupt Flag bit

1 = Comparator C2 input has crossed the threshold (must be cleared in software)

0 = Comparator C2 input has not crossed the threshold

bit 4 C1IF: Comparator C1 Interrupt Flag bit

1 = Comparator C1 input has crossed the threshold (must be cleared in software)

0 = Comparator C1 input has not crossed the threshold

bit 3-1 Unimplemented: Read as ‘0’

bit 0 TMR1IF: TMR1 Overflow Interrupt Flag bit

1 = TMR1 register overflowed (must be cleared in software)

0 = TMR1 register did not overflow

— — — TMR1IF

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

2001 Microchip Technology Inc. Preliminary DS41171A-page 21

Page 24

PIC16C781/782

2.8 PCON Register

The Power Control (PCON) register contains two flag

bits to allow determination of the source of the most

recent RESET:

• Power-on Reset (POR

• External MCLR Reset

• Power Supply Brown-out (BOR

The Power Control register also contains frequency

select bits for the INTRC oscillator and the WDT software enable bit.

Note: BOR is unknown on Power-on Reset. It

must then be set by the user and checked

on subsequent RESETS to see if BOR

clear , indic ating a brow n-out has occurred.

The BOR status bit is a don't care and is

not necessarily predic table if the brown-o ut

circuit is disabled (by clearing the BODEN

bit in the Configuration word).

)

) Reset

is

Direction of Change

4 MHz → 37 kHz 100 µs 300 µs

37 kHz→4 MHz 1.25 µs 3.25 µs

Note: When changing the internal oscillator

speed (i.e., the OSCF bit, INTRC mode),

the processor will be inactive during the

oscillator frequency change.

REGISTER 2-6: POWER CONTROL REGISTER (PCON: 8Eh)

U-0 U-0 U-0 R/W-q R/W-1 U-0 R/W-q R/W-q

— — — WDTON OSCF — POR BOR

bit 7 bit 0

bit 7-5 Unimplemented: Read as '0'

bit 4 WDTON: WDT Software Enable bit

If WDTE bit (Configuration Word <3>) = 1:

This bit is not writable, always reads ‘1’

Typical Time Inactive

Minimum Maximum

If WDTE bit (Configuration Word <3>) = 0:

1 = WDT is enabled

0 = WDT is disabled

bit 3 OSCF: Oscillator Speed INTRC Mode bit

1 = 4 MHz typical

0 = 37 kHz typical

All other oscillator modes (X = Ignored)

bit 2 Unimplemented: Read as '0'

bit 1 POR

bit 0 BOR

: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

: Brown-out Reset Status bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred

Legend:

q = Value depends on conditions

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

DS41171A-page 22 Preliminary 2001 Microchip Technology Inc.

Page 25

2.9 PCL and PCLATH

The program counter (PC) s pec ifi es the add res s o f the

instruction to fetch for execution. The PC is 13-bits

wide. The low byte is call ed th e PCL reg is ter. This register is readable and writable. The high byte is called

PIC16C781/782

2001 Microchip Technology Inc. Preliminary DS41171A-page 23

Page 26

PIC16C781/782

FIGURE 2-5: DIRECT/INDI RECT ADDRESSING

RP1:RP 0 6

From Opcode

0

Indirect AddressingDirect Addressing

IRP FSR Register

7

0

Bank Select Location Select

Bank Select

Location Select

00 01 10 11

80h

FFh

100h

17Fh

180h

1FFh

Data

Memory

00h

(1)

7Fh

Bank 0 Bank 1 Bank 2 Bank 3

Note 1: For register file map detail, see Figure 2-3.

2.12 Effect of RESET on Core Registers

Refer to Table 2-2 for the effect of a RESET operation

on core registers.

TABLE 2-2: EFFECT OF RESET ON CORE REGISTERS

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bank 0

00h INDF Addressing this location uses contents of FSR to address data memory (not a physical register)

02h PCL Program Counter’s (PC) Least Significant Byte 0000 0000 0000 0000

04h FSR Indirect Data Memory Address Pointer xxxx xxxx uuuu uuuu

0Ah PCLATH — — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 ---0 0000

0Ch PIR1 LVDIF ADIF C2IF C1IF — — — TMR1IF 0000 ---0 0000 ---0

Bank 1

81h OPTION_REG RBPU

83h STATUS IRP RP1 RP0 TO PD ZDCC0001 1xxx 000q quuu

8Bh INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u

8Ch PIE1 LVDIE ADIE C2IE C1IE — — — TMR1IE 0000 ---0 0000 ---0

8Eh PCON — — — WDTON OSCF — POR BOR ---q 1-qq ---q 1-qq

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0'.

Note 1: Other (non power-up) RESETS include external RESET through MCLR

Shaded locations are unimplemented, read as ‘0’.

INTEDG T0CS T0SE PSA PS2 PS1 PS0 xxxx xxxx 1111 1111

and Watchdog Timer Reset.

Value on:

POR, BOR

0000 0000 0000 0000

Value on

all other

RESETS

(1)

DS41171A-page 24 Preliminary 2001 Microchip Technology Inc.

Page 27

PIC16C781/782

3.0 I/O PORTS

Most pins for the I/O p orts are mu ltiplexed w ith an alternate function for the peripheral features on the device.

In general, when a peripheral is enabled, that pin may

not be used as a general purpose I/O pin.

Additional inform atio n o n I/O ports may be f oun d i n th e

PICmicro™ Mid-Range Reference Man ual (DS33023 )

3.1 I/O Port Analog/Digital Mode

The PIC16C781/782 has two I/O ports: PORTA and

PORTB. Some of these po rt pins are mixed si gnal (can

be digital or anal og). When an analog signal is present

on a pin, the pin mus t be c onfigu red as an an alo g inp ut

to prevent unnecessary current drawn from the power

supply. The Analog Select regist er (ANSEL) a llo w s th e

user to individually select the Digital/Analog mode on

these pins. When the Analog mode is active, the port

pin always reads as a logic 0.

Note 1: On a Power-on Reset, the ANSEL regis-

ter configures these mixed signal pins as

Analog mode: RA<3:0>, RB<3:0>.

2: If a pin is configured as Anal og mode, the

pin always reads '0', even if th e digital ou tput is active.

REGISTER 3-1: ANALOG SELECT REGISTER (ANSEL: 9Dh)

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1

ANS7 ANS6 ANS5 ANS4 ANS3 ANS2 ANS1 ANS0

bit 7 bit 0

bit 7-0 ANS<7:0>: Select Analog Input Function on AN<7:0> bits

1 = Analog input

0 = Digital I/O

Note: Setting a pin to an analog input disables the digital input buffer. The corresponding

TRIS bit should be set to input mode when using pins as analog inputs.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

2001 Microchip Technology Inc. Preliminary DS41171A-page 25

Page 28

PIC16C781/782

3.2 PORTA and the TRISA Register

PORTA is an 8-bit wide, bi-directional port with the

exception of RA0, RA1 and RA5, w hich are inputs only.

The corresponding data direction register is TRISA.

Setting a TRISA bit (= 1) makes the corresponding

PORTA pin an input (i.e., disables the digital output).

Clearing a TRISA bit (= 0) makes the corresponding

PORTA pin an output (i.e., disables the digital output).

Reading the PORTA register reads the status of the

pins, whereas writing to it, writes to the port latch. All

write operations are read-modify-write operations.

Therefore, a write to a port implies that the port pins are

read, this value is then modified and written to the port

data latch.

Pins RA<3:0> are multiplexed with analog functions:

• Analog inputs AN<3:0> to the A/D Converter.

REF1 and VREF2 inputs to the comparators .

• V

• OPAMP inverting/non-inverting inputs.

Note:

Pins RA<7:4> are multiplexed with digital functions:

• Pin RA4 is multiplexed with the TMR0 module

clock input.

• Pin RA5 is multiplexed with the device RESET

(MCLR

) and programming input (VPP) function.

• Pins RA6 and RA7 are multiplexed with the

oscillator/clock I/O functions. RA6 can also be

configured as the TMR1 clock input.

PORTA has the following I/O characteristics:

• RA0, RA1, and RA5 are input only.

• RA4 is an open drain output. All other PORTA

pins have full CMOS buffer outputs.

• All PORTA pins have Schmitt trigger inputs.

EXAMPLE 3-1: INITIALIZING PORTA

;* This code block will configure PORTA

;* as follows

;* RA<7:4> digital outputs

;* RA<3:2> digital inputs

;* RA<1:0> analog inputs

;* RB<3:0> digital I/O

;* Note 1: RB<3:0> configured as digital I/O

;* Note 2: RA<7:6> availability depends on

;* the oscillator selection

BANKSEL PORTA ; Select Bank 0

CLRF PORTA ; Preset PORTA data

; reg

BANKSEL TRISA ; Select Bank 1

MOVLW B’00001111’; Digital I/O

; config data

MOVWF TRISA ; Configure PORTA

; digital

MOVLW B’00000011’; Analog I/O config

; data

MOVWF ANSEL ; Configure PORTA

; analog

3.2.1 TRISA, ANSEL, AND CONTROL PRECEDENCE

The ANSEL and TRISA registers are the primary software controls for the configuration of PORTA pins.

TRISA bits tri-state the output drivers of PORTA, and

ANSEL register bits control the digital input buffers. It is

important to program bo th registers when configu ring a

mixed signal port pin, as most peripherals cann ot override the TRISA and ANSEL registers control. Even if a

peripheral has the ability to override control of the

TRISA and ANSEL registers, it is good programming

practice to program both registers appropriately.

There are specific cases in which the TRISA and

ANSEL registers can be overridden by a peripheral or

a configuration bit, see Figures 3-1 through 3-8 for

details.

DS41171A-page 26 Preliminary 2001 Microchip Technology Inc.

Page 29

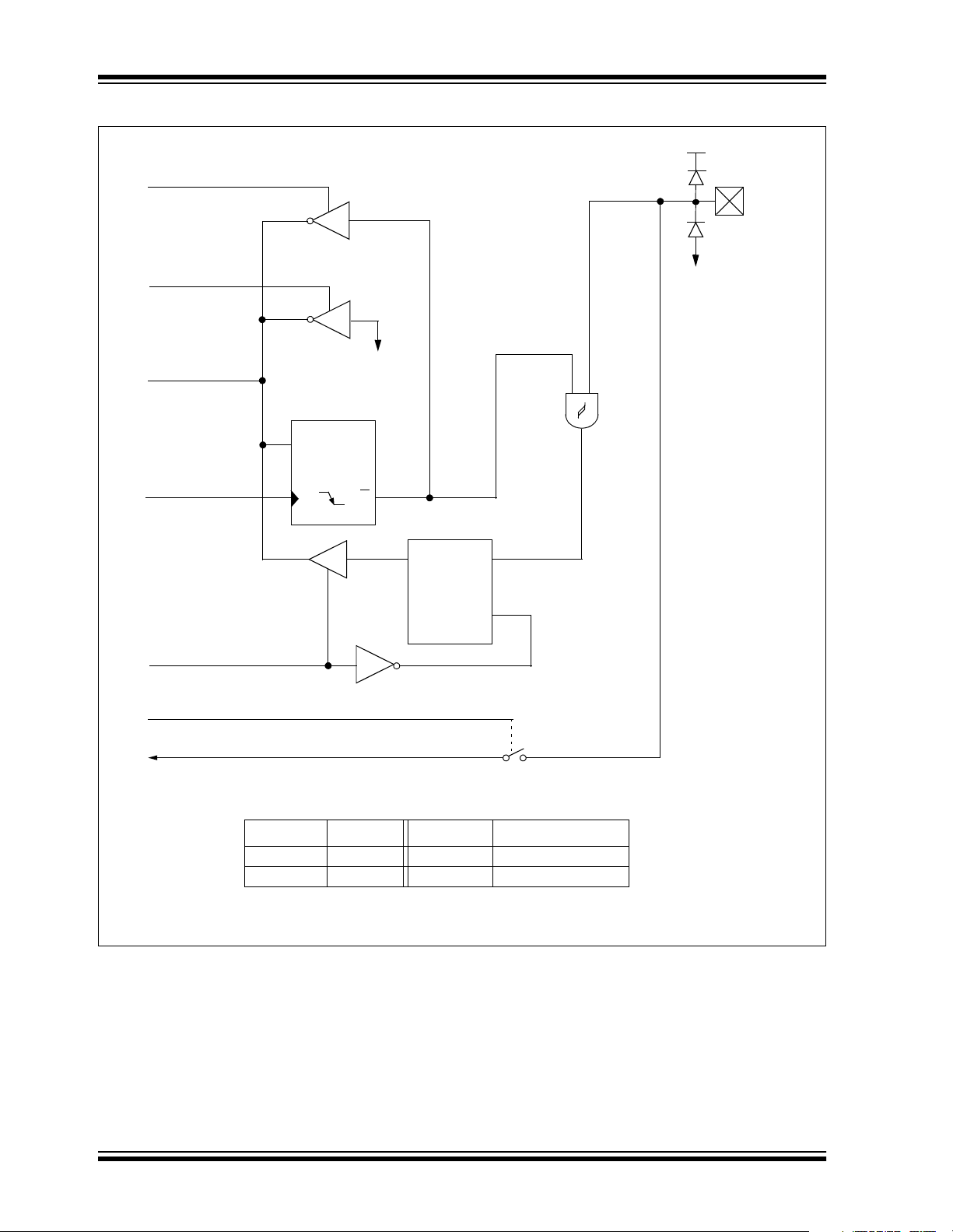

FIGURE 3-1: BLOCK DIAGRAM OF RA0/AN0/OPA+ PIN

PIC16C781/782

VDD

RD

ANSEL

RD TRISA

Data Bus

WR ANSEL

ANSEL Reg.

D

CK

RA0/AN0/OPA+

VSS

V

SS

Q

Q

Data Reg.

QD

EN

RD PORTA

Analog Function Enable

AN0/OPA+ (see Figure 1-3)

ANSEL<0> TRISA<0> FUNCTION PORTA<0> READ

0 x Digital In Pin

1 x Analog In 0

2001 Microchip Technology Inc. Preliminary DS41171A-page 27

Page 30

PIC16C781/782

FIGURE 3-2: BLOCK DIAGRAM OF RA1/AN1/OPA- PIN

VDD

RD ANSEL

RD TRISA

Data Bus

WR ANSEL

ANSEL Reg.

CK

RA1/AN1/OPA-

VSS

V

SS

QD

Q

Data Reg.

Q

D

EN

RD PORTA

Analog Function Enable

AN1/OPA- (see Figure 1-3)

ANSEL<1> TRISA<1> FUNCTION PORTA<1> READ

0 x Digital In Pin

1 x Analog In 0

DS41171A-page 28 Preliminary 2001 Microchip Technology Inc.

Page 31

FIGURE 3-3: BLOCK DIAGRAM OF RA2/AN2/VREF2 PIN

RD ANSEL

Data Bus

Data Reg.

WR PORTA

D

CK

TRIS Reg.

D

Q

VDD

Q

Q

P

N

PIC16C781/782

VDD

V

RA2/AN2/

REF2

WR TRISA

RD TRISA

WR ANSEL

RD PORT A

Analog Function Enable

AN2/VREF2 (see Figure 1-3)

SS

CK

ANSEL Reg.

CK

ANSEL<2> TRISA<2> FUNCTION PORTA<2> READ

0 1 Digital In Pin

0 0 Digital Out Pin

1 x Analog In 0

Q

QD

Q

Data Reg.

Q

D

EN

V

VSS

2001 Microchip Technology Inc. Preliminary DS41171A-page 29

Page 32

PIC16C781/782

FIGURE 3-4: BLOCK DIAGRAM OF RA3/AN3/VREF1 PIN

Data Bus

WR PORTA

WR TRISA

RD TRISA

WR ANSEL

Data Reg.

D

CK

TRIS Reg.

D

CK

ANSEL Reg.

D

CK

Q

VDD

Q

Q

Q

Q

Q

P

N

SS

V

RD PORTA

AN3/VREF1 (see Figure 1-3)

DS41171A-page 30 Preliminary 2001 Microchip Technology Inc.

Page 33

FIGURE 3-5: BLOCK DIAGRAM OF RA4/T0CKI PIN

Data Reg.

Data Bus

D

Q

PIC16C781/782

WR PORTA

WR TRISA

RD TRISA

RD PORTA

TMR0 Clock Input

CK

TRIS Reg.

D

CK

Q

Q

Q

Data Reg.

Q

N

Vss

D

EN

RA4/T0CKI

Vss

TRISA<4> PORTA<4> FUNCTION PORTA<4> READ

1 x Digital In Pin

0 0 0 Output Pin

0 1 Hi-Z Output Pin

2001 Microchip Technology Inc. Preliminary DS41171A-page 31

Page 34

PIC16C781/782

FIGURE 3-6: BLOCK DIAGRAM OF RA5/MCLR/VPP PIN

MCLRE

To MCLR Circuit

MCLR Filter

RA5/MCLR/VPP

Program Mode

Data Bus

RD TRISA

RD PORTA

HV Detect

VSS

Data Reg.

Q

VSS

D

EN

(1)

MCLRE

Internal x Digital In Pin

External x MCLR

Note 1: See Configuration Word <5>, Register 14-1.

DS41171A-page 32 Preliminary 2001 Microchip Technology Inc.

TRISA<5> FUNCTION PORTA<5> READ

0

Page 35

PIC16C781/782

FIGURE 3-7: BLOCK DIAGRAM OF RA6/OSC2/CLKOUT/T1CKI PIN

(INTRC w/ CLKOUT) or (RC w/ CLKOUT)

Data Bus

WR PORTA

WR TRISA

RD TRISA

Data Reg.

CK

TRIS Reg.

D

CK

OSC1

1

0

QD

Q

Q

Q

Oscillator

Circuit

VDD

P

N

V

SS

RD PORTA

2001 Microchip Technology Inc. Preliminary DS41171A-page 33

Page 36

PIC16C781/782

FIGURE 3-8: BLOCK DIAGRAM OF RA7/OSC1/CLKIN PIN

Data Bus

WR PORTA

WR TRISA

RD TRISA

Data Reg.

CK

TRIS Reg.

D

CK

OSC2

To Chip Clock Drivers

QD

Q

Q

Q

VDD

P

N

VSS

(INTRC w/o CLKOUT)

Oscillator

Circuit

EC Mode

DQ

RD PORTA

TABLE 3-1: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

DS41171A-page 34 Preliminary 2001 Microchip Technology Inc.

Page 37

PIC16C781/782

3.3 PORTB and the TRISB Register

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a

TRISB bit (= 1) makes the corr esponding PORTB pin

an input (i.e., puts the corresponding output driver into

a Hi-Impedance mode). Clearing a TRISB bit (= 0)

makes the corresponding PORTB pin an output (i.e.,

puts the contents of the output latch on the selected

pin.

EXAMPLE 3-2: INITIALIZING PORTB

;* This code block will configure PORT B

;* as follows

;* RB<7:6> analog inputs

;* RB<5:4> digital inputs

;* RB<3:2> digital inputs

;* RB<1:0> digital inputs

;* RA<3:0> digital I/O

BANKSEL PORTB ; Select Bank 0

CLRF PORTB ; Preset PORTB data

; reg.

BANKSEL TRISB ; Select Bank 1

MOVLW B’11001111’ ; Digital I/O

; config data

MOVWF TRISB ; Configure PORTB

; digital

MOVLW B’00000011’ ; Analog I/O config

; data

MOVWF ANSEL ; Configure PORTB

; analog

Pin RB2 is multiplexed with the analog function ADC/

Comparator Input AN6. When the pin is used as an

analog input, the ANSEL register must have bit 6 to

select the Analog mode for the pin.

The RB3 pin is multiplexed with two analog functions:

ADC/Comparator Analog Input AN7, and the output of

the OPA module. When the pin is used as analog I/O,

the ANSEL register must have bit 7 set to select the

Analog mode of the pin.

Pins RB<7:6> are multiplexed with the outputs of the

two on-board comparators, the outputs of the PSMC

module, and the clock gate input for Timer1. Note,

when enabled, these peripherals override the PORTB

data register; however, TRISB retains control of output

drivers. Therefore, TRISB<7:6> must be programmed

appropriately for Comparator and PSMC outputs to

operate.

3.3.1 PORTB WEAK PULL-UP

Each of the PORTB pins has an internal weak pull-up

resistance, which can be individually enabled from the

WPUB register. A single global enable bit, RBPU

(OPTION_REG<7>), can turn on/off all of the selected

pull-ups. Clearing the RBPU

bit (OPTION_REG<7>)

enables the weak pull-up resistors (see Register 3-2).

The weak pull-up is automatically turned off when the

port pin is configu red as an outpu t. The pull-up s are disabled on a Power-on Reset.

3.3.2 PORTB INTERRUPT-ON-CHANGE

The RB0 pin can be configured as:

• Digital I/O

• ADC/Comparator Analog Input (AN4)

• External Interrupt (INT)

• Volt a ge R efere nc e Output (VR)

When the pin is u sed as an analo g I/O, th e ANSEL re gister must have bit 4 set to config ure the RB0 pi n as an

analog input.

Pin RB1 is multiplexed with two analog function s: ADC/

Comparator Analog Input AN5, and the output of the

DAC. When the pin is used as an analog I/O, the

ANSEL register must have bit 5 set to configure the

RB1 pin as an analog I/O.

Each of the POR TB pin s, if con figured a s input, has th e

ability to generate an interrupt-on-change. To enable

the interrupt-on-change feature, the corresponding bit

must be set in the IOCB register (see Register 3-3).

The RBIE bit in the INTCON re gister functio ns as a global enable bit to turn on/off the interrupt-on-change feature. The select ed input s are comp ared to the old value

latched on the last read of PORTB. The ”mismatch”

outputs are OR -ed together to gen erate the RB Port

Change Interrupt with flag bit RBIF (INTCON<0>).

The IOCB interrupt can also awaken the device from

SLEEP. The user, in the Interrupt Service Routine,

must clear the interrupt in the following manner:

a) A read or write to PORTB. This copies the cur-

rent state into the latch and ends the mismatch

condition.

b) Clear flag bit RBIF.

2001 Microchip Technology Inc. Preliminary DS41171A-page 35

Page 38

PIC16C781/782

REGISTER 3-2: WEAK PULL-UP PORTB REGISTER (WPUB: 95h)

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R /W-1 R/W-1 R/W-1

WPUB7 WPUB6 WPUB5 WPUB4 WPUB3 WPUB2 WPUB1 WPUB0

bit7 bit0

bit 7-0 WPUB<7:0>: PORTB Weak Pull-Up Control bits

1 = Weak pull-up enabled for corresponding pin

0 = Weak pull-up disabled for corresponding pin

REGISTER 3-3:

bit 7-0 IOCB<7:0>: Interrupt-on-Change PORTB Control bits

Note 1: For the WPUB register setting to take effect, the RBPU

register must be cleared.

2: The weak pull-up device is automatically disabled if the pin is in output mode, i.e.,

(TRISB = 0) for corresponding pin.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

bit in the OPTION_REG

INTERRUPT-ON-CHANGE PORTB REGISTER (IOCB: 96h)

R/W-1 R/W-1 R/W-1 R/W-1 R/W-0 R/W-0 R/W-0 R/W-0

IOCB7 IOCB6 IOCB5 IOCB4 IOCB3 IOCB2 IOCB1 IOCB0

bit7 bit0

1 = Interrupt-on-change enabled for corresponding pin

0 = Interrupt-on-change disabled for corresponding pin

Note 1: The interrupt enable bits, GIE and RBIE in the INTCON regi ste r, must be set for indi-

vidual interrupts to be recognized.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

- n = Value at POR ’1’ = Bit is set ’0’ = Bit is cleared x = Bit is unknown

3.3.3 TRISB, ANSEL, AND CONTROL PRECEDENCE

The ANSEL and TRISB registers are the primary controls for the configuration of PORTB pins. TRISB tristates the output drivers of PORTB, and the ANSEL

register disable s the in put buf fers. It is im portan t to program both registers when configuring a port pin, since

most peripherals do not have precedence over the

TRISB and ANSEL registers’ control of the pin. Even if

a peripheral has the ability to override the control of the

TRISB and ANSEL registers, it is good practice to program both registers appropriately.

DS41171A-page 36 Preliminary 2001 Microchip Technology Inc.

Note 1: Upon RESET , the ANSEL r egiste r config-

ures the RB<3:0> pins as analog inputs.

2: When programmed as analog inputs,

RB<3:0> pins will read as ‘0’.

3: There are specific cases in which the

functions of the TRISB and ANSEL registers can be overridden by a peripheral or

configuration word (see Figure 3-9

through Figure 3-16 for details).

Page 39

FIGURE 3-9: BLOCK DIAGRAM OF RB0/INT/AN4/VR PIN

VREN

VROE

VR Output

PIC16C781/782

Data Bus

WR WPUB

RD WPUB

WR PORTB

WR TRISB

RD TRISB

WR ANSEL

WPUB Reg.

D

Q

CK

Q

PORTB Reg.

D

Q

CK

Q

TRIS Reg.

D

Q

CK

Q

ANSEL Reg.

QD

CK

Q

RBPU

VDD

P

N

VSS

VDD

P

Weak

Pull-up

VDD

RB0/INT/AN4/VR

VSS

RD ANSEL

IOCB Reg .

WR IOCB

RD IOCB

RD PORTB

INT Input

Analog Function Enable

AN4/VR

VREN & VROE ANSEL<4> TRISB<0> FUNCTION PORTB<0> READ

TTL

D

Q

Set

CK

RBIF

Q

...

From other

RB<7:0> pins

QD

EN

EN

Q

D

EN

Q

D

EN

0 0 1 Digital In Pin

0 0 0 Digital Out Pin

0 1 x Analog In 0

1 x x Analog Out 0

Q1

Q3

2001 Microchip Technology Inc. Preliminary DS41171A-page 37

Page 40

PIC16C781/782

FIGURE 3-10: BLOCK DIAGRAM OF RB1/AN5/VDAC PIN

Data Bus

PORTB Reg.

D

Q

WR PORTB

WR TRISB

RD TRISB

RD PORT B

CK

TRIS Reg.

D

Q

CK

Q

D

EN

EN

DS41171A-page 38 Preliminary 2001 Microchip Technology Inc.

Page 41

FIGURE 3-11: BLOCK DIAGRAM OF RB2/AN6 PIN

PIC16C781/782

Data Bus

WR WPUB

RD WPUB

WR PORTB

WR TRISB

RD TRISB

WR ANSEL

RD ANSEL

WR IOCB

RD IOCB

RD PORTB

WPUB Reg.

D

Q

CK

Q

PORTB Reg.

D

Q

CK

Q

TRIS Reg.

D

Q

CK

Q

ANSEL Reg.

D

Q

CK

Q

IOCB Reg.

D

Q

CK

Q

Set

RBIF

RBPU

...

From other

RB<7:0> pins

QD

EN

EN

VDD

P

N

VSS

VDD

Weak

P

Pull-up

VDD

RB2/AN6

VSS

TTL

Q

D

EN

Q

D

EN

Q1

Q3

Analog Function Enable

AN6

ANSEL<6> TRISB<2> FUNCTION PORTB<2> READ

0 1 Digital In Pin

0 0 Digital Out Pin

1 x Analog In 0

2001 Microchip Technology Inc. Preliminary DS41171A-page 39

Page 42

PIC16C781/782

FIGURE 3-12: BLOCK DIAGRAM OF RB3/AN7/OPA PIN

Data Bus

WR WPUB

WR PORTB

WR TRISB

RD TRISB

WPUB Reg.

D

Q

CK

PORTB Reg.

D

Q

CK

TRIS Reg.

D

Q

CK

Q

RBPU

VDD

P

N

VSS

Weak

Pull-up

RD PORTB

AN7/OPA

IOCB Reg.

D

Q

Q

CK

QD

EN

EN

D

EN

Q

D

EN

OPA MODULE

ANSEL<7> ADC/C1/C2 INPUT FUNCTION PORTB<3> READ

OPAON CAL_ACTIVE

0 x 0 Digital Digital I/O Pin

0 x 1 Analog Analog In 0

1 0 1 Analog OPA Output 0

1 1 1 Analog HI-Z Calibration 0

Analog HI-Z = No internal drive on pin (analog input) during calibration.

DS41171A-page 40 Preliminary 2001 Microchip Technology Inc.

Page 43

FIGURE 3-13: BLOCK DIAGRAM OF RB4 PIN

PIC16C781/782

Data Bus

WR WPUB

RD WPUB

WR PORTB

WR TRISB

RD TRISB

RD IOCB

WR IOCB

WPUB Reg.

D

Q

CK

Q

PORTB Reg.

D

Q

CK

Q

TRIS Reg.

D

Q

CK

Q

IOCB Reg.

D

Q

CK

Q

Set

RBIF

RBPU

...

From other

RB<7:0> pins

VDD

Weak

P

VDD

P

Pull-up

VDD

RB4

N

VSS

VSS

TTL

Q

D

EN

Q1

RD PORTB

QD

EN

EN

TRISB<4> FUNCTION P ORTB<4> READ

0 Digital Out Pin

1 Digital In Pin

Q

D

EN

Q3

2001 Microchip Technology Inc. Preliminary DS41171A-page 41

Page 44

PIC16C781/782

FIGURE 3-14: BLOCK DIAGRAM OF RB5 PIN

Data Bus

WR WPUB

RD WPUB

WR PORTB

WR TRISB

RD TRISB

RD IOCB

WR IOCB

WPUB Reg.

D

Q

CK

Q

PORTB Reg.

D

Q

CK

Q

TRIS Reg.

D

Q

CK

Q

IOCB Reg.

D

Q

CK

Q

Set

RBIF

RBPU

...

From other

RB<7:0> pins

VDD

Weak

P

VDD

P

Pull-up

VDD

RB5

N

VSS

VSS

TTL

Q

D

EN

Q1

Q

D

EN

EN

RD PORTB

Q

D

EN

Q3

TRISB<5> FUNCTION P ORTB<5> READ

0 Digital Out Pin

1 Digital In Pin

DS41171A-page 42 Preliminary 2001 Microchip Technology Inc.

Page 45

FIGURE 3-15: BLOCK DIAGRAM OF RB6/C1/PSMC1A PIN

C1OE

SMCON

PSMC1A

C1OUT

WPUB Reg.

Data Bus

WR WPUB

RD WPUB

WR PORTB

D

Q

CK

Q

Data Reg.

D

Q

CK

Q

RBPU

PIC16C781/782

VDD

Weak Pull-up

P

VDD

P

VDD

RB6/C1/PSMC1A

WR TRISB

RD TRISB

RD PORTB

RD IOCB

WR IOCB

Serial Programming Clock

TRIS Reg.

D

CK

IOCB Reg.

D

Q

CK

Q

EN

N

SS

V

TTL

V

Q1

SS

Q

Q

QD

Set RBIF

From other

RB<7:0> pins

PSMC SMCON COMPARATOR C1OE PORTB TRISB<6> FUNCTION

x x 1 Digital In

0 0 0 Digital Out

01 0 C1OUT

1x 0 PSMC1A

2001 Microchip Technology Inc. Preliminary DS41171A-page 43

Q

EN

D

RD Port

Q3

Page 46

PIC16C781/782

FIGURE 3-16: BLOCK DIAGRAM OF RB7/C2/PSMC1B/T1G PIN

C2OE

SCEN

SMCOM

SMCON

RD WPUB

Data Bus

WPUB Reg.

D

Q

RBPU

VDD

Weak Pull-up

P

VDD

RB7/C2/PSMC1B/T1G

WR WPUB

WR PORTB

WR TRISB

RD TRISB

RD IOCB

RD PORTB

WR IOCB

CK

Data Reg.

D

CK

TRIS Reg.

D

CK

IOCB Reg.

D

Q

CK

Q

Q

VSS

Q

Q

Q

Q

C2OUT

PSMC1B

SC Switch

VDD

P

N

VSS

TTL

Serial Programming Data

and Timer1 Gate

Set RBIF

From other

RB<7:0> pins

PSMC MODULE

SMCON SMCOM SCEN

Q

Q

COMPARATOR

C2OE

D

EN

D

EN

Q1

RD Port

Q3

PORTB TRISB<7> FUNCTION

x x x x 1 Digital In

0 x x 0 0 Digital Out

1 0 0 0 0 Digital Out

0xx1 0 C2OUT

1001 0 C2OUT

1 0 1 x 0 Slope Compensation

11xx 0 PSMC1B

DS41171A-page 44 Preliminary 2001 Microchip Technology Inc.

Page 47

PIC16C781/782

TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

06h PORTB RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0 xxxx 0000 uuuu 0000

86h

81h OPTION_REG RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111

95h

96h

9Dh

Legend: x = unknown, u = unchanged, - = unimplemented, read as ’0’. Shaded cells are not used by PORTB.

TRISB PORTB Data Direction Register 1111 1111 1111 1111

WPUB PORTB Weak Pull-up Control 1111 1111 1111 1111

IOCB PORTB Interrupt-on-Change Control 1111 0000 1111 0000

ANSEL AN7 AN6 AN5 AN4

AN3 AN2 AN1 AN0 1111 1111 1111 1111

Value on:

POR, BOR

Value on

all other

RESETS

2001 Microchip Technology Inc. Preliminary DS41171A-page 45

Page 48

PIC16C781/782