Page 1

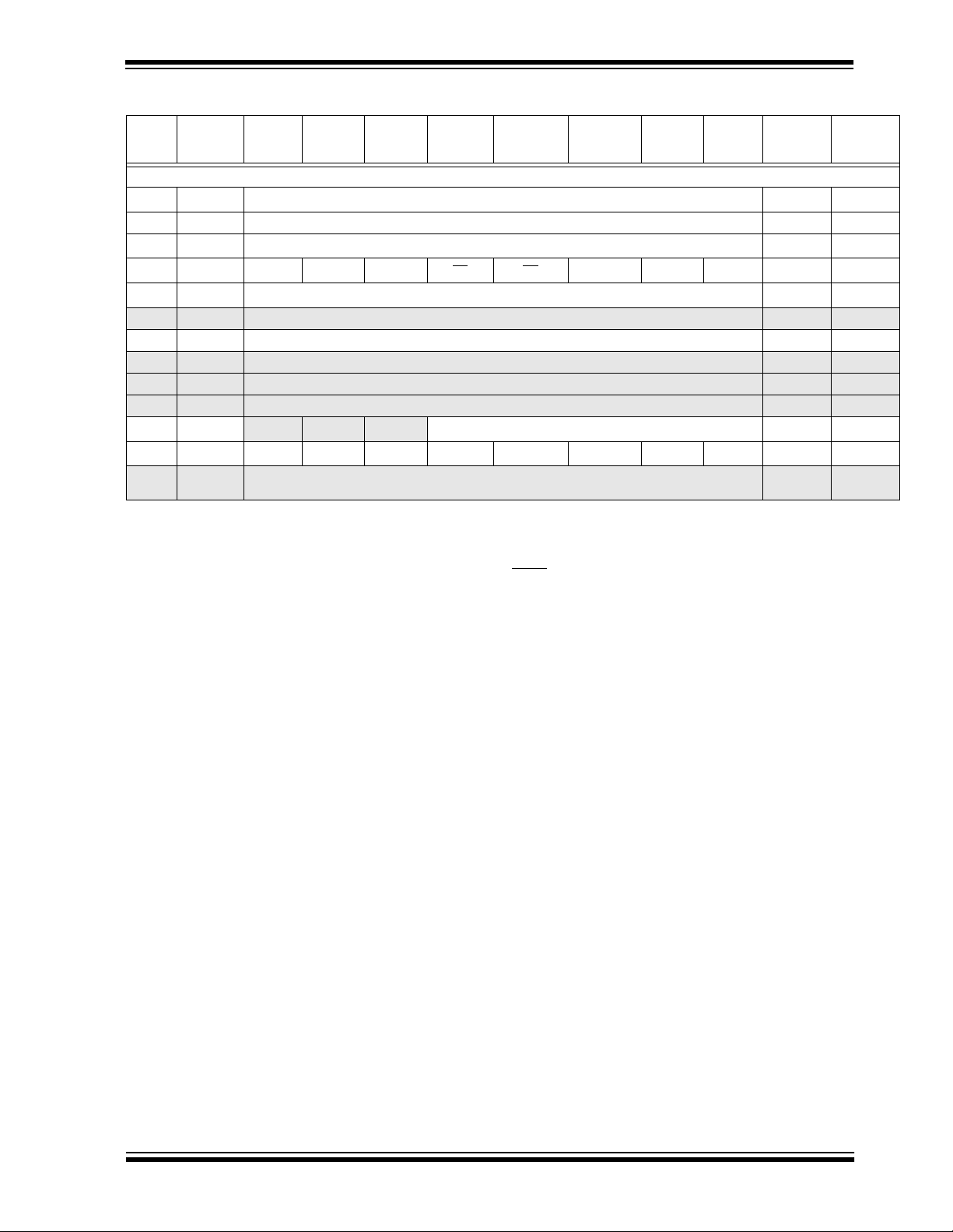

PIC16C745/765

8-Bit CMOS Microcontrollers with USB

Devices included in this data sheet:

• PIC16C745 • PIC16C765

Microcontroller Core Features:

• High-performance RISC CPU

• Only 35 sing le word instructions

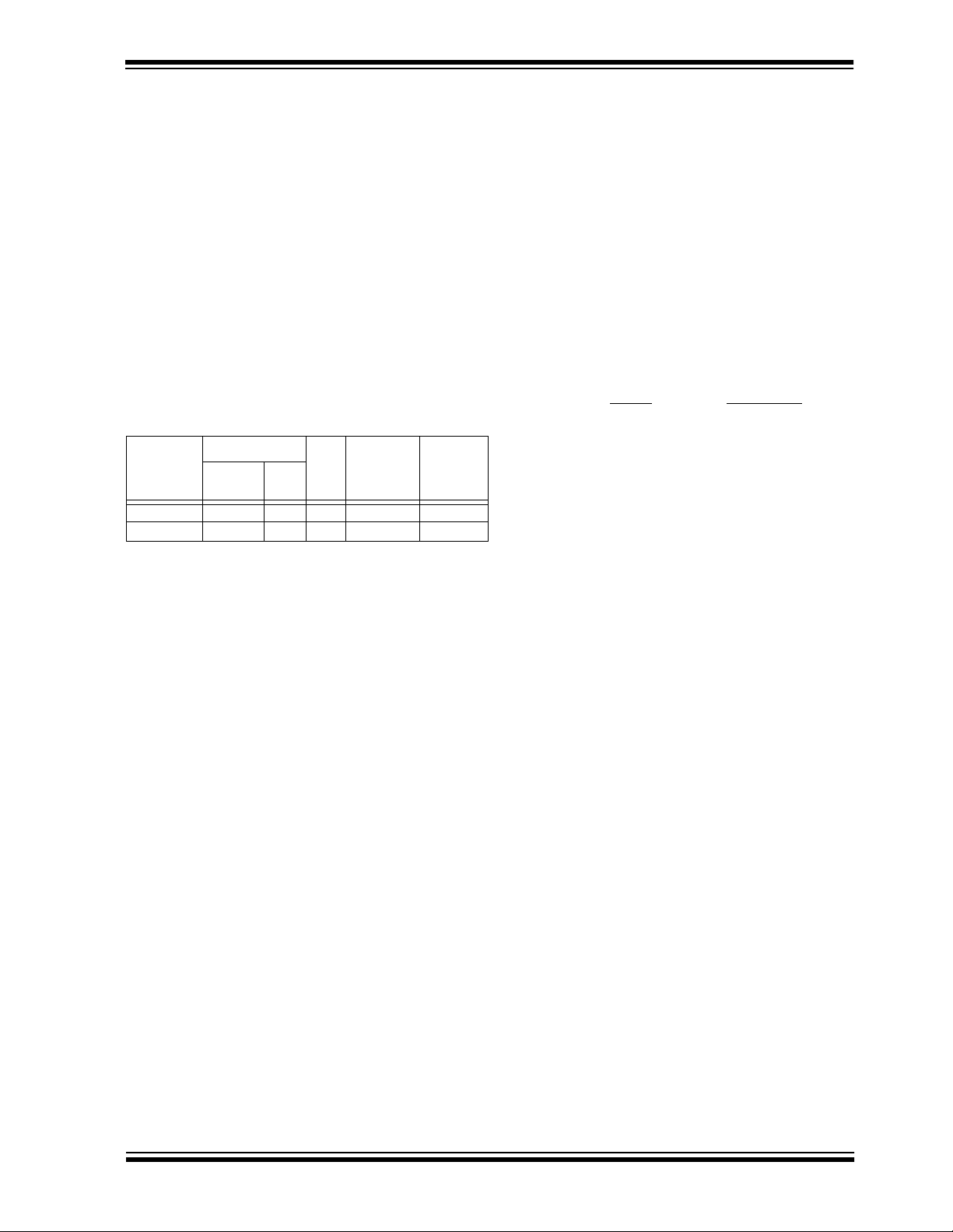

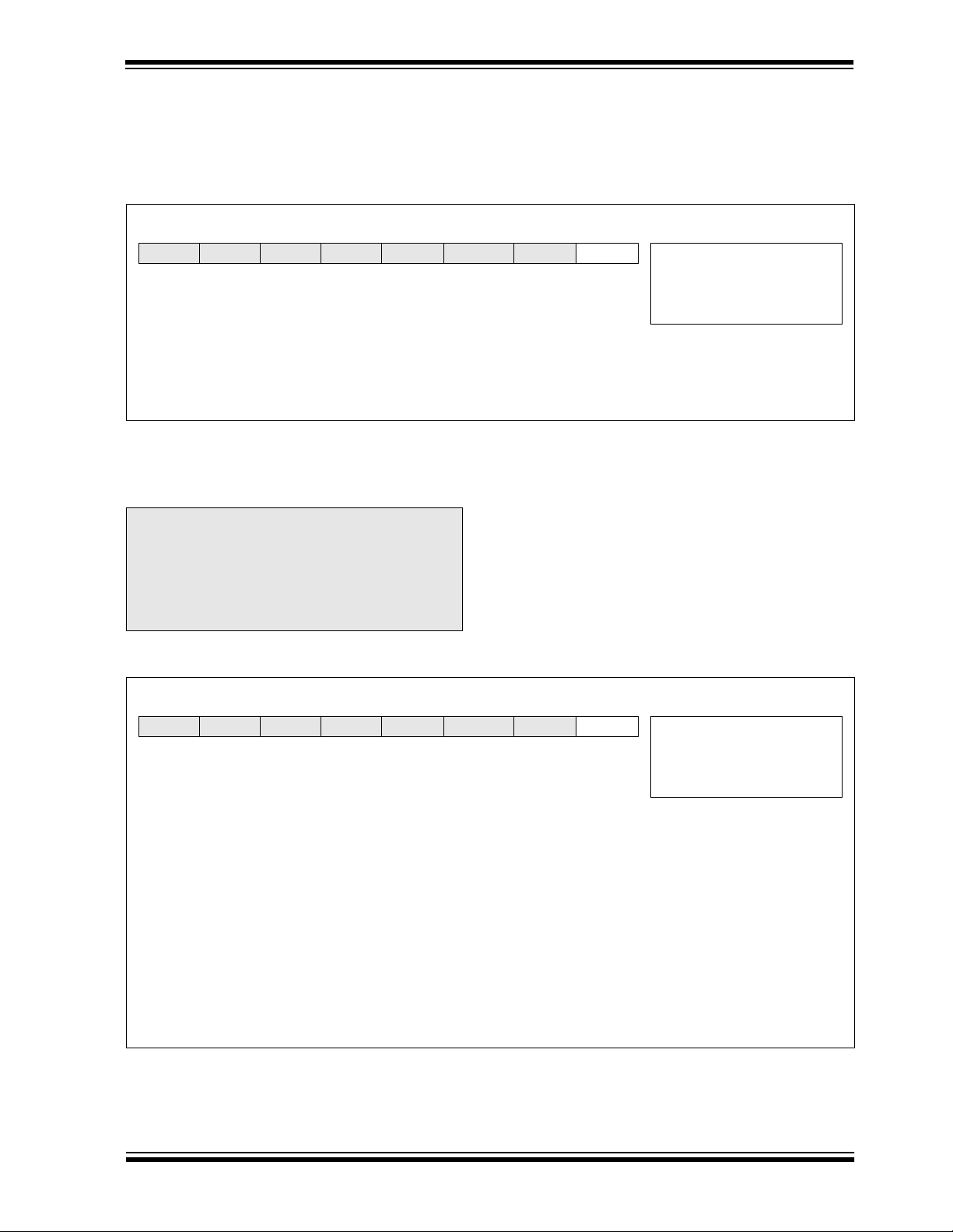

Memory

Device

PIC16C745 8K 256 28 8 5

PIC16C765 8K 256 40 8 8

Program

x14

Data

x8

Pins

• All single cycle instructions except for program

branches which are two cycle

• Interrupt capability (up to 12 internal/external

interrupt sources)

• Eight level deep hardware stack

• Direct, indirect and relative addressing modes

• Power-on Reset (POR)

• Power-up Timer (PWRT) and Oscillator Start-up

Timer (OST)

• Watchdog Timer (WDT) with its own on-chip RC

oscillator for reliable operation

• Brown-out detection circuitry for

Brown-out Reset (BOR)

• Programmable code-protect ion

• Power saving SLEEP mode

• Selectable oscillator options

- EC - External clock (24 MHz)

- E4 - External clock with PLL (6 MHz)

- HS - Crystal/Resonator (24 MHz)

- H4 - Crystal/Resonator with PLL (6 MHz)

• Processor clock of 24MHz derived from 6 MHz

crystal or resonator

• Fully static low-power, high-speed CMOS

• In-Circuit Serial Programming (ICSP)

• Operating voltage range

- 4.35 to 5.25V

• High Sink/Source Current 25/25 mA

• Wide temperature range

- Industrial (-40°C - 85°C)

• Low-power consumption:

- < TBD @ 5V, 6 MHz

- < TBD typical standby current

A/D

Resolution

Channels

A/D

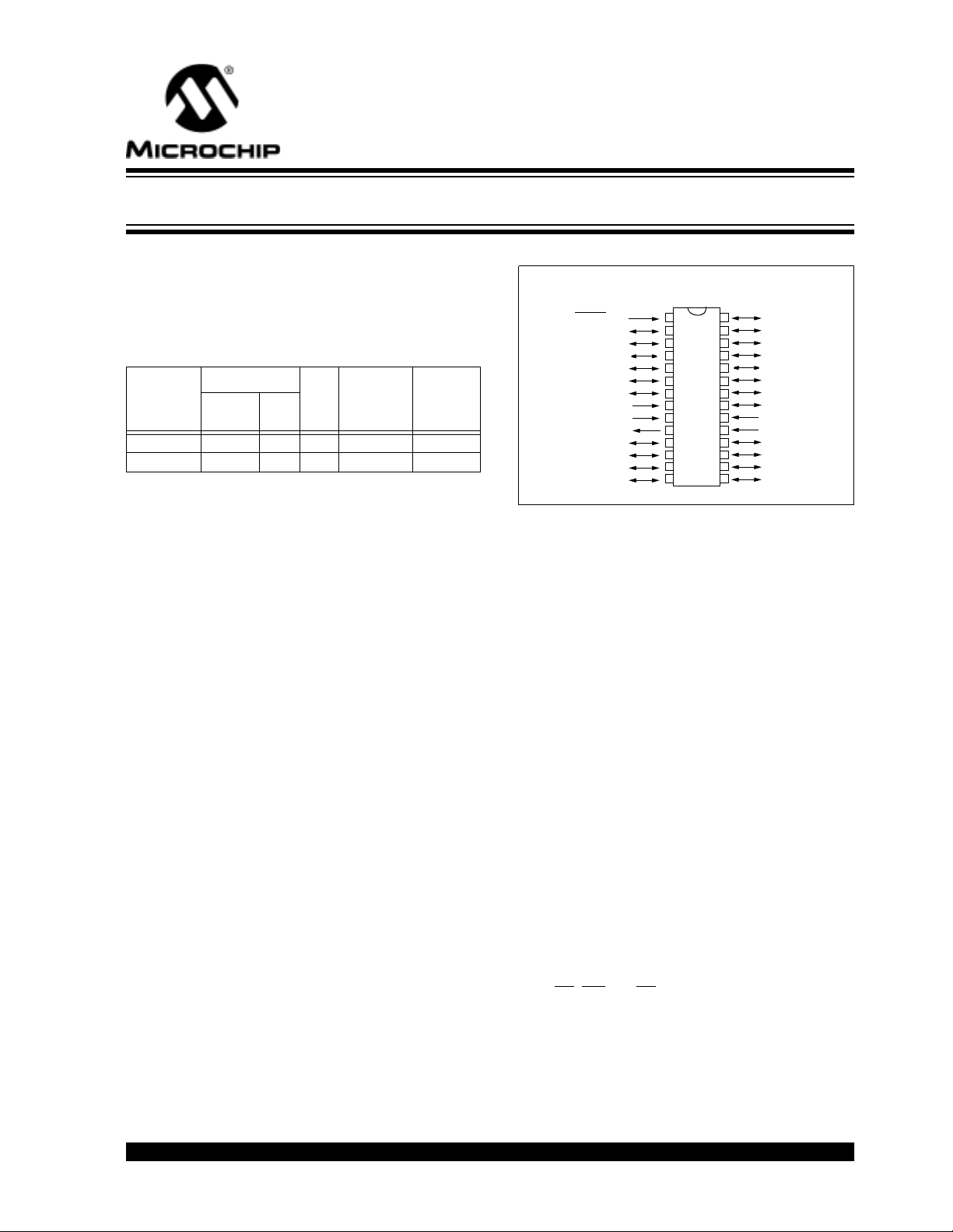

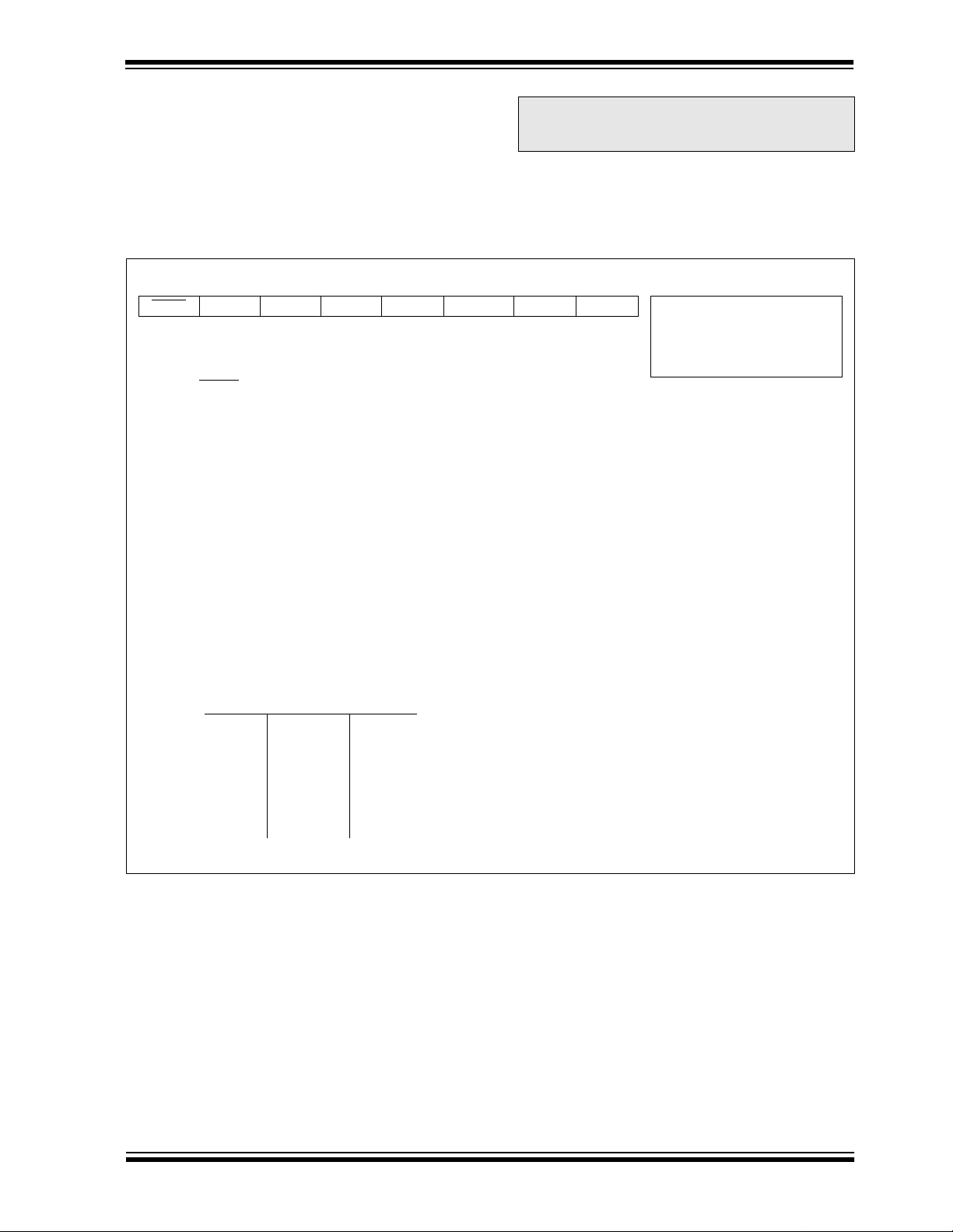

Pin Diagrams

28-Pin DIP, SOIC

MCLR/VPP

RA0/AN0

RA1/AN1

RA2/AN2

RA3/AN3/V

OSC1/CLKIN

OSC2/CLKOUT

RC0/T1OSO/T1CKI

RC1/T1OSI/CCP2

REF

RA4/T0CKI

RA5/AN4

Vss

RC2/CCP1

USB

V

• 1

28

2

27

3

26

4

25

5

24

6

23

7

22

8

21

9

20

PIC16C745

10

19

11

18

12

17

13

16

14

15

RB7

RB6

RB5

RB4

RB3

RB2

RB1

RB0/INT

DD

V

Vss

RC7/RX/DT

RC6/TX/CK

D+

D-

Peripheral Features:

• Universal Serial Bus (USB 1.1)

• 64 bytes of USB dual port RAM

• 22 (PIC16C745) or 33 (PIC16C765) I/O pins

- Individual direction control

- 1 high voltage open drain (RA4)

- 8 PORTB pins with:

- Interrupt on change control (RB<7 :4> only)

- Weak pull up control

- 3 pins dedicated to USB

• Timer0: 8-bit timer/counter with 8-bit prescaler

• Timer1: 16-bit timer/counter with prescaler

can be incremented during sleep via external

crystal/clock

• Timer2: 8-bit timer/counter with 8-bit period

register, prescaler and postscaler

• 2 Capture, Compare and PWM modules

- Capture is 16 bit, max. resolution is 10.4 ns

- Compare is 16 bit, max. resolution is 167 ns

- PWM maximum resolution is 10 bit

• 8-bit multi-channel Analog-to-Digital con verter

• Universal Synchronous Asynchronous Receiver

Transmitter (USART/SCI)

• Parallel Slave Port (PSP) 8-bits wide, with external RD

, WR and CS controls (PIC16C765 only)

1999 Microchip Technology Inc.

Advanced Information DS41124A-page 1

Page 2

PIC16C745/765

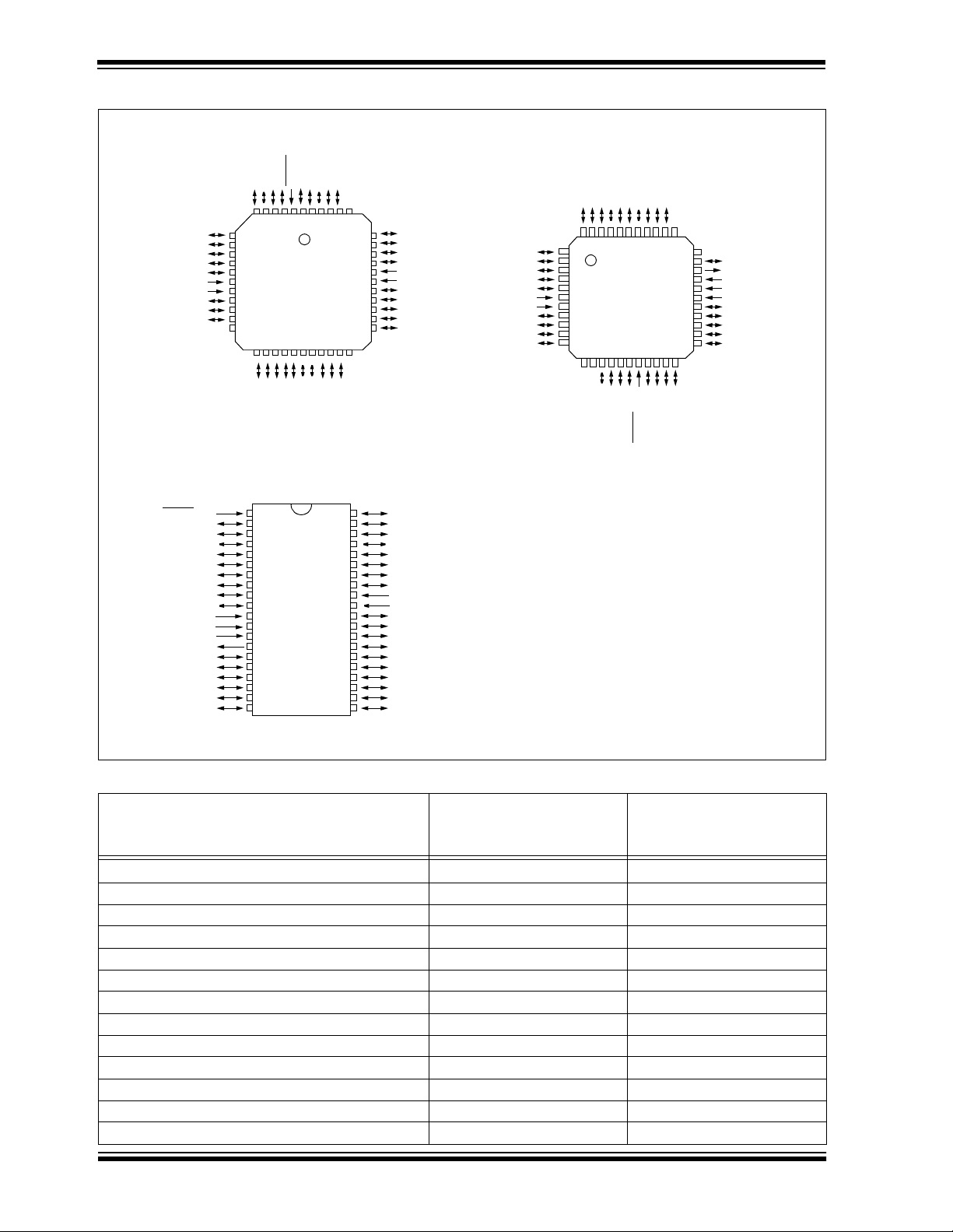

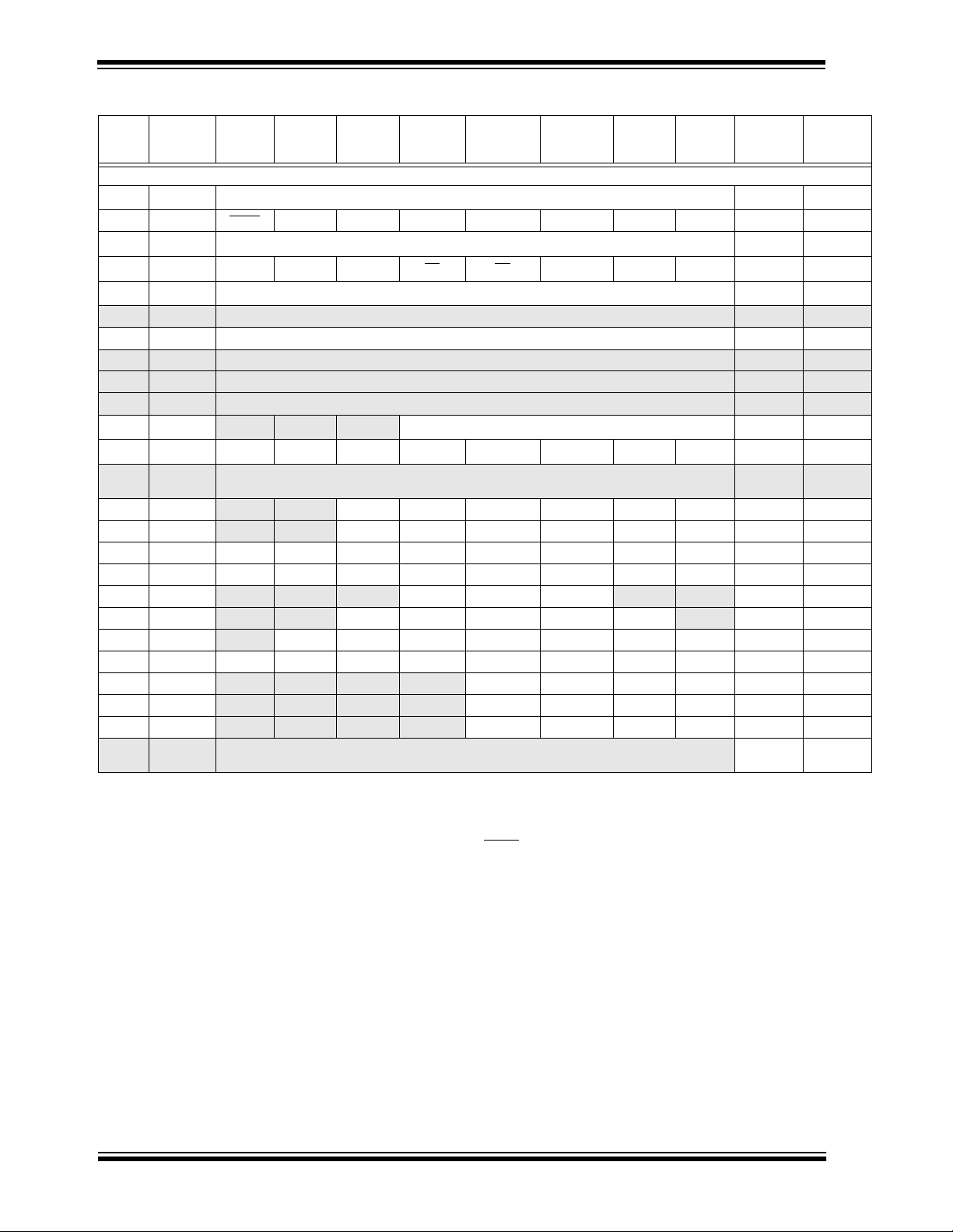

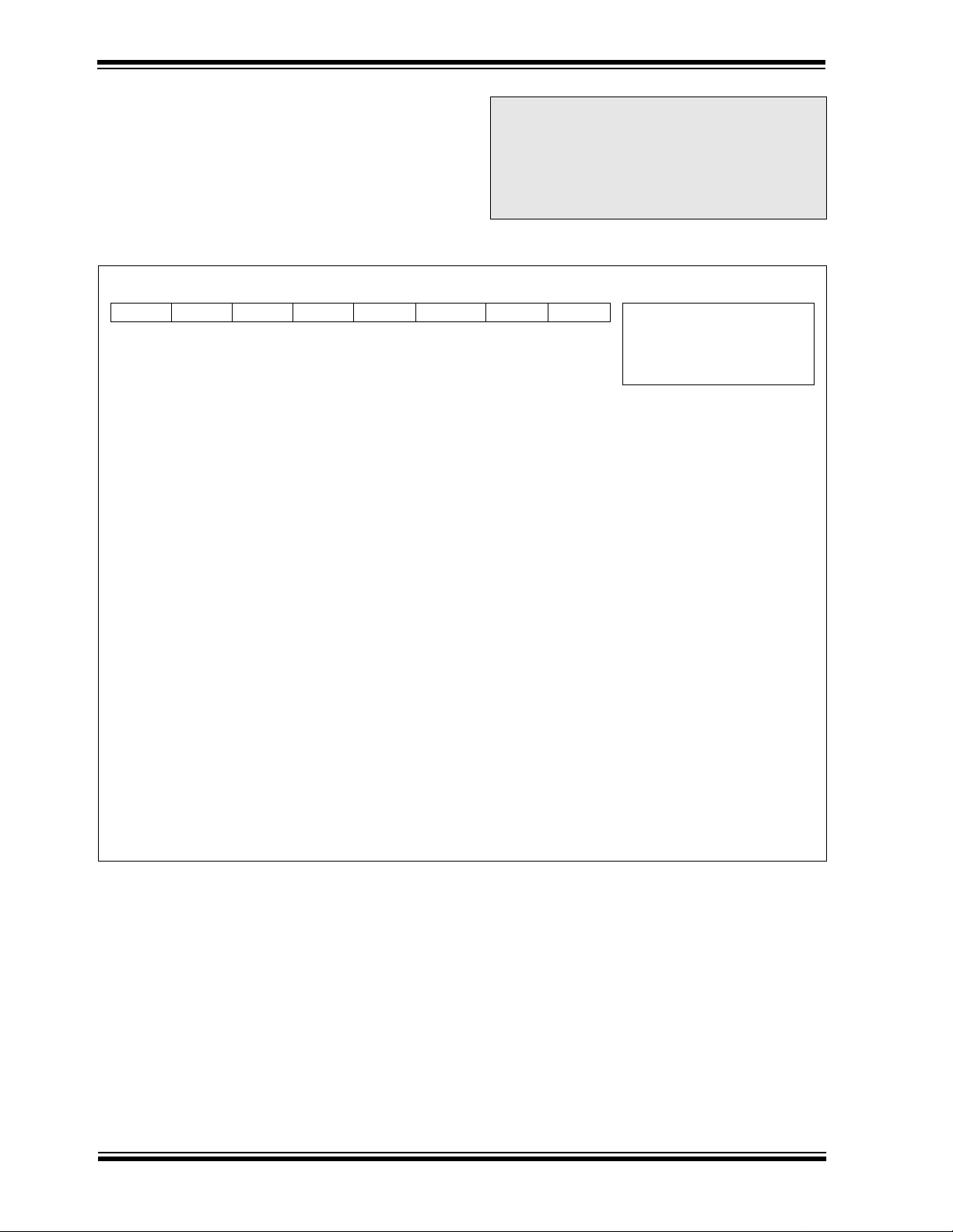

44-Pin PLCC

RA4/T0CKI

RA5/AN4

RE0/RD/AN5

RE1/WR/AN6

RE2/CS/AN7

V

DD

VSS

OSC1/CLKIN

OSC2/CLKOUT

RC0/T1OSO/T1CKI

NC

40-Pin PDIP

MCLR/VPP

RA0/AN0

RA1/AN1

RA2/AN2

RA3/AN3/V

RA4/T0CKI

RA5/AN4

RE0/RD/AN5

RE1/WR/AN6

RE2/CS/AN7

OSC1/CLKIN

OSC2/CLKOUT

RC0/T1OSO/T1CKI

RC1/T1OSI/CCP2

RC2/CCP1

RD0/PSP0

RD1/PSP1

V

REF

V

VSS

USB

DD

RA3/AN3/VREF

RA2/AN2

65432

7

8

9

10

11

12

PIC16C765

13

14

15

16

17

18

RC2/CCP1

RC1/T1OSI/CCP2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

RA1/AN1

19

USB

V

RA0/AN0

RD0/PSP0

/VPP

NC

MCLR

1

RD2/PSP2

RD1/PSP1

PIC16C765

RB7

RB6

RB5

RB4

4443424140

D-

D+

RD3/PSP3

RC6/TX/CK

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

NC

282726252423222120

NC

39

38

37

36

35

34

33

32

31

30

29

RB3

RB2

RB1

RB0/INT

DD

V

VSS

RD7/PSP7

RD6/PSP6

RD5/PSP5

RD4/PSP4

RC7/RX/DT

RB7

RB6

RB5

RB4

RB3

RB2

RB1

RB0/INT

DD

V

VSS

RD7/PSP7

RD6/PSP6

RD5/PSP5

RD4/PSP4

RC7/RX/DT

RC6/TX/CK

D+

DRD3/PSP3

RD2/PSP2

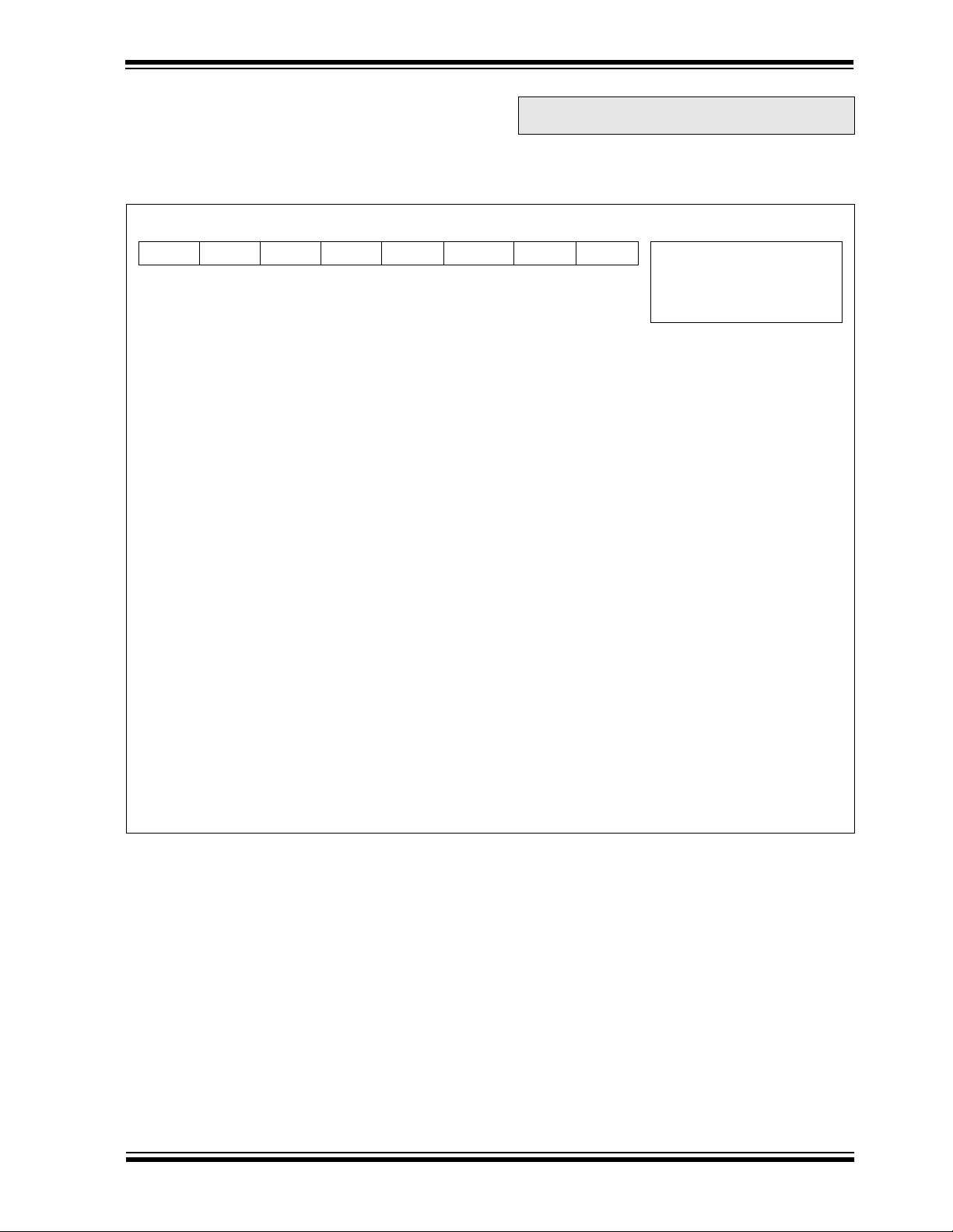

44-Pin TQFP

RC7/RX/DT

RD4/PSP4

RD5/PSP5

RD6/PSP6

RD7/PSP7

V

SS

VDD

RB0/INT

RB1

RB2

RB3

RC6/TX/CK

D+D-RD3/PSP3

RD2/PSP2

RD1/PSP1

RD0/PSP0

4443424140393837363534

1

2

3

4

5

6

PIC16C765

7

8

9

10

11

NC

NC

RB7

RB6

RB5

RB4

/VPP

MCLR

USB

V

RC2/CCP1

RA0/AN0

RC1/T1OSI/CCP2

RA1/AN1

NC

RA2/AN2

33

NC

32

RC0/T1OSO/T1CKI

31

OSC2/CLKOUT

30

OSC1/CLKIN

29

28

27

26

25

24

23

2221201918171615141312

RA3/AN3/VREF

SS

V

VDD

RE2/CS/AN7

RE1/WR/AN6

RE0/RD/AN5

RA5/AN4

RA4/T0CKI

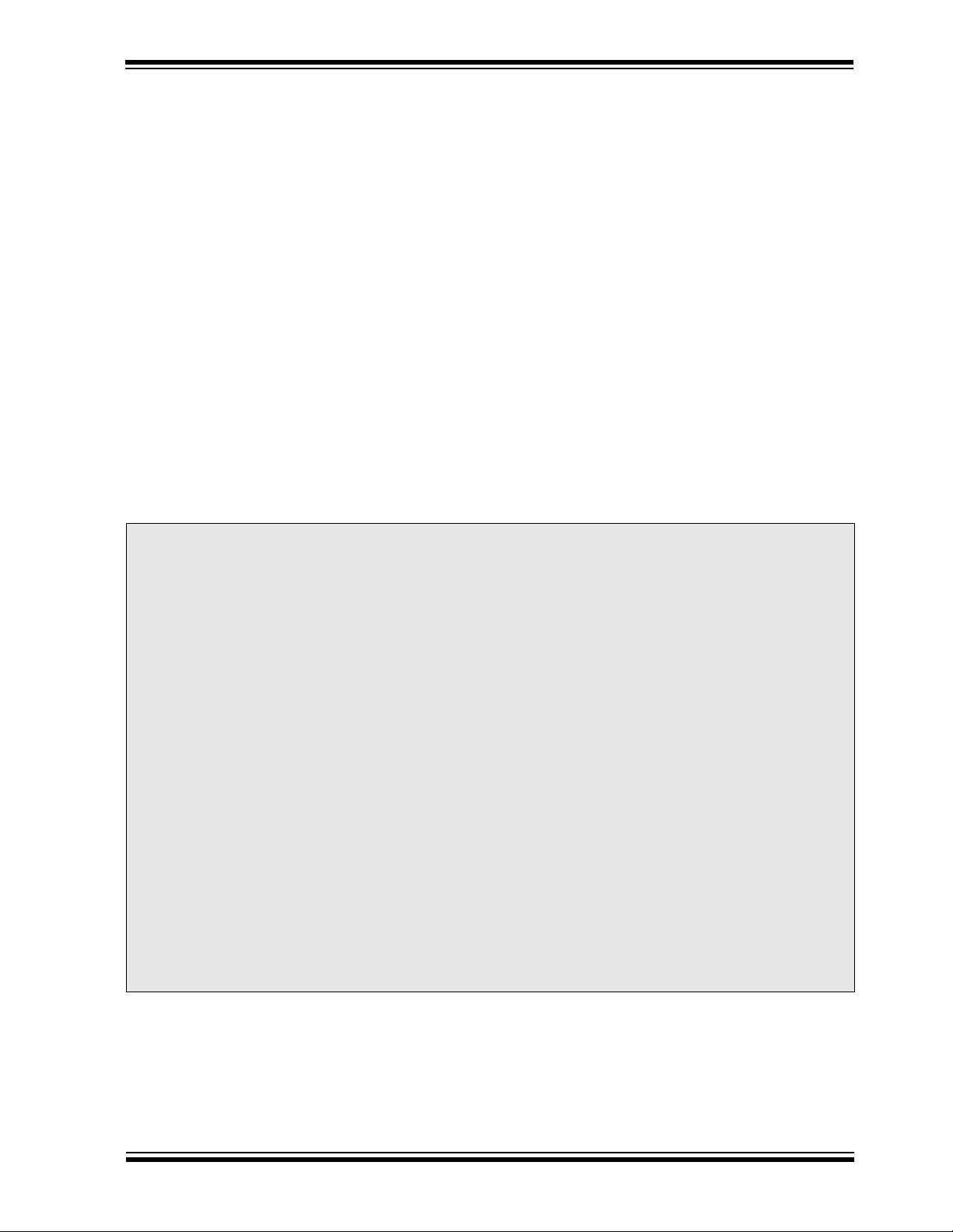

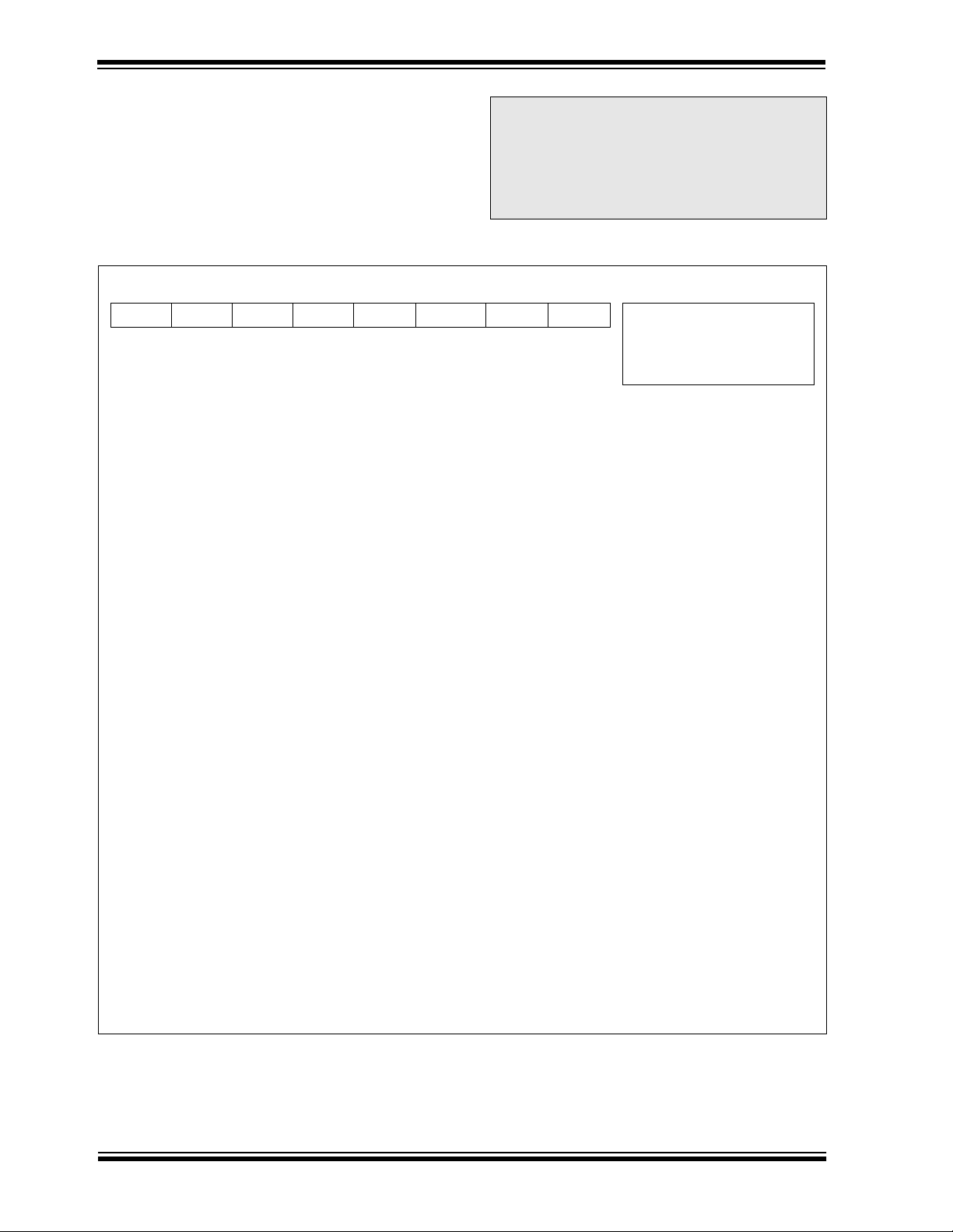

Key Features

PICmicro

TM

Mid-Range Reference Manual

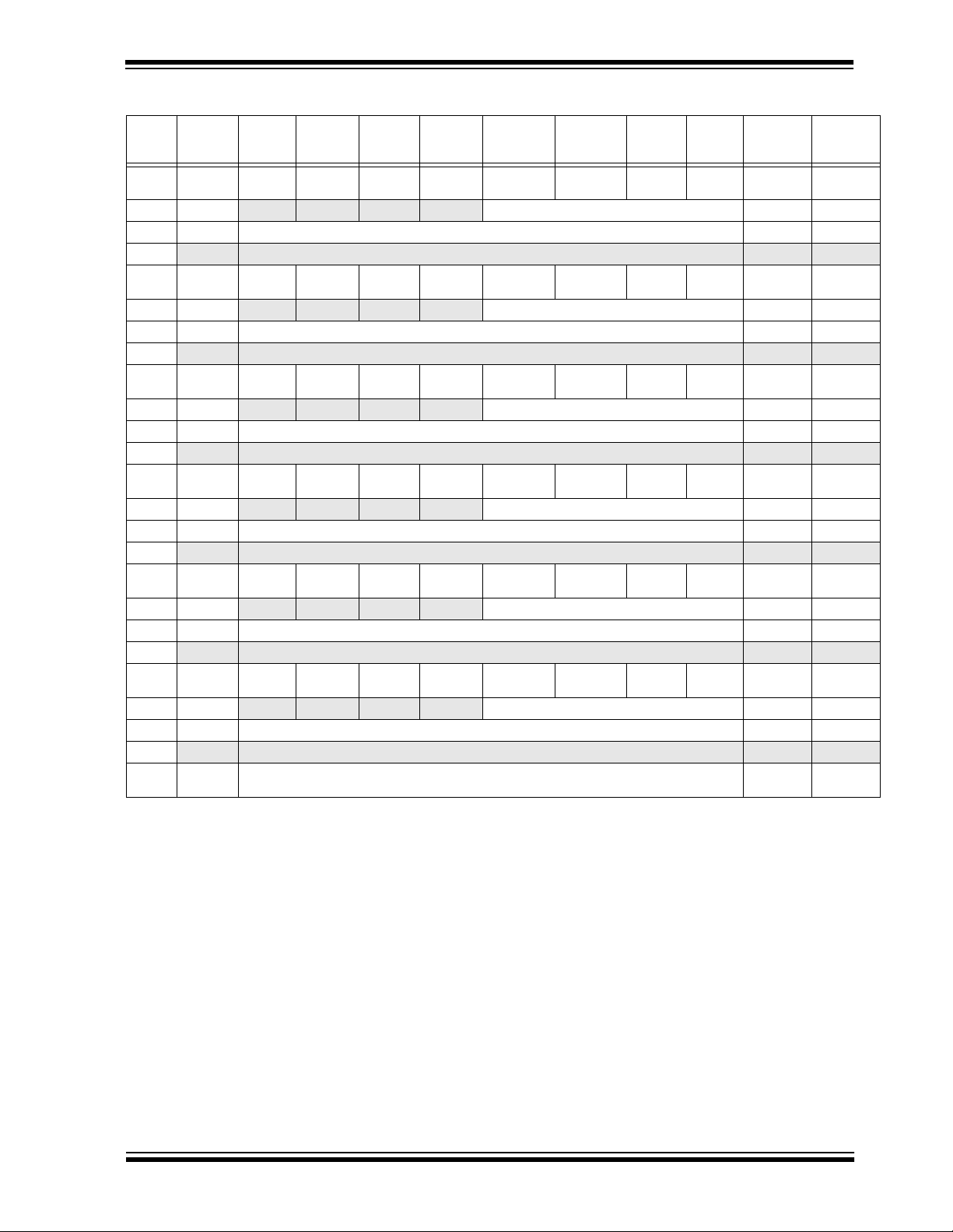

PIC16C745 PIC16C765

(DS33023)

Operating Frequency 6 MHz or 24 MHz 6 MHz or 24 MHz

Resets (and Delays) POR, BOR (PWRT, OST) POR, BOR (PWRT, OST)

Program Memory (14-bit words) 8K 8K

Data Memory (bytes) 256 256

Dual Port Ram 64 64

Interrupt Sources 11 12

I/O Ports 22 (Ports A, B, C) 33 (Ports A, B, C, D, E)

Timers 3 3

Capture/Compare/PWM modules 2 2

Analog-to-Digital Converter Module 5 channel x 8 bit 8 channel x 8 bit

Parallel Slave Port —Yes

Serial Communication USB, USART/SCI USB, USART/SCI

Brown Out Detect Reset Yes Yes

DS41124A-page 2 Advanced Information

1999 Microchip Technology Inc.

Page 3

PIC16C745/765

Table of Contents

1.0 General Description..............................................................................................................................................5

2.0 PIC16C745/765 Device Varieties .........................................................................................................................7

3.0 Architectural Overview..........................................................................................................................................9

4.0 Memory Organization..........................................................................................................................................15

5.0 I/O Ports..............................................................................................................................................................31

6.0 Timer0 Module....................................................................................................................................................43

7.0 Timer1 Module....................................................................................................................................................45

8.0 Timer2 Module....................................................................................................................................................49

9.0 Capture/Compare/PWM Modules.......................................................................................................................51

10.0 Universal Serial Bus............................................................................................................................................57

11.0 Universal Synchronous Asynchronous Receiver Transmitter (USART).............................................................75

12.0 Analog-to-Digital Converter (A/D) Module ..........................................................................................................89

13.0 Special Features of the CPU..............................................................................................................................95

14.0 Instruction Set Summary...................................................................................................................................109

15.0 Development Support.......................................................................................................................................117

16.0 Electrical Characteristics.......................... ...... ...... ..... .................................................................... ..... ...... ..... ....123

17.0 DC and AC Characteristics Graphs and Tables ...............................................................................................141

18.0 Packaging Information......................................................................................................................................143

Index ..........................................................................................................................................................................151

On-Line Support..........................................................................................................................................................155

Reader Response.......................................................................................................................................................156

Product Identification System .....................................................................................................................................157

To Our V alued Customers

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the ver sion number. e.g., DS30000A is version A of document DS30000.

New Customer Notification System

Register on our web site (www.microchip.com/ cn) to rece ive the most current information on our products.

Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended

workarounds. As device/documentation issues become known to us, w e will pub lish an errata sheet. The errata will specify the re vision of silicon and revision of document to which it applies.

To deter mine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

• The Microchip Corporate Literature Center; U.S. FAX: (480) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include liter-

ature number) you are using.

Corrections to this Data Sheet

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure

that this document is correct. However , w e realize that we ma y have missed a few things. If y ou find any inf ormation that is missing

or appears in error, please:

• Fill out and mail in the reader response form in the back of this data sheet.

• E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

1999 Microchip Technology Inc.

Advanced Information DS41124A-page 3

Page 4

PIC16C745/765

NOTES:

DS41124A-page 4 Advanced Information

1999 Microchip Technology Inc.

Page 5

PIC16C745/765

1.0 GENERAL DESCRIPTION

The PIC16C745/765 devices are lo w-cost, high-perf or-

mance, CMOS, fully-static, 8-bit microcontrollers in the

PIC16CXX mid-range family.

®

All PICmicro

RISC architecture. The PIC16CXX micro controller family has enhanced core features, eight-level deep stack

and multiple internal and external interrupt sources.

The separate instruction and data buses of the Harvard

architecture allow a 14-bit wide instruction word with

the separate 8-bit wide data. The two stage instruction

pipeline allows all instructions to execute in a single

cycle, except for program branches, which require two

cycles. A total of 35 instructions (reduced instruction

set) are avai lable. Ad ditionally, a large register set giv es

some of the architectu ral inno v ations us ed to achie v e a

very high performance.

The PIC16C745 device has 22 I/O pins. The

PIC16C765 device has 33 I/O pins. Each device has

256 bytes of RAM. In addition, several peripheral features are available including: three timer/counters, two

Capture/Compare/PWM modules and two serial ports.

The Universal Serial Bus (USB 1.1) peripheral provides bus communications. The Universal Synchronous Asynchronous Receiver Transmitter (USART) is

also known as the Serial Communications Interface or

SCI. Also, a 5-channel high-speed 8-bit A/D is provided on the PIC16C745, while the PIC16C765 offers

8 channels. The 8-bit resolution is ideally suited for

applications requiring a low-cost analog interface,

(e.g., thermostat control, pressure sensing, etc).

The PIC16C745/765 devices have special features to

reduce external components, thus reducing cost,

enhancing system reliability and reducing power consumption. There are 4 o scillato r options , of whic h EC is

for the external regulated clock source, E4 is for the

external regulated clock source with PLL, HS is for the

high speed crystals/resonators and H4 is for high

speed crystals/resontators with PLL. The SLEEP

(power-down) feature provides a power-saving mode.

The user can wake up the chip from SLEEP through

several external and internal interrupts and resets.

microcontrollers employ an advanced

A highly reliable Watchdog Timer (WDT), with a dedicated on-chip RC oscill ator, pr ovides protec tion against

software lock-up, and also provides one way of waking

the device from SLEEP.

A UV erasable CERDIP packaged version is ideal for

code development, while the cost-effective One-TimeProgrammable (OTP) version is suitable for production

in any volume.

The PIC16C745/765 devices fit nicely in many applications ranging from security and remote sensors to appliance controls and automotives. The EPROM

technology makes customization of application programs (data loggers, industrial controls, UPS) extremely

fast and convenient. The small footprint packages make

this microcontroller series perfect for all applications

with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the

PIC16C745/765 devices very versatile, even in areas

where no microcontroller use has been considered

before (e.g., timer functions, serial communication, capture and compare, PWM functions and coprocessor

applications).

1.1 Family and Upward Compatibility

Users familiar with the PIC16C5X microcontroller family will realize that this is an enhanced version of the

PIC16C5X architecture. Code written for the

PIC16C5X can be easil y p orted to the PIC16 CXX family of devices.

1.2 Development Support

PICmicro® devices are supported by the complete line

of Microchip Development tools.

Please refer to Section 15.0 for more details about

Microchip’s development tools.

1999 Microchip Technology Inc.

Advanced Information DS41124A-page 5

Page 6

PIC16C745/765

NOTES:

DS41124A-page 6 Advanced Information

1999 Microchip Technology Inc.

Page 7

PIC16C745/765

2.0 PIC16C745/765 DEVICE VARIETIES

A variety of frequency ranges and packaging options

are avai lable . Dependin g on applicati on and production

requirements, th e proper de vice option ca n be selected

using the information in the PIC16C745/765 Product

Identification System section at the end of this data

sheet. When placing orders, please use that page of

the data sheet to specify the correct part number.

2.1 UV Erasable Devices

The UV erasable version, offered in windowed CERDIP

packages (600 mil), is optimal for prototype development and pilot programs. This version can be erased

and reprogrammed to any of the supported oscillator

modes.

Microchip’s PICSTART

programmers both support programming of the

PIC16C745/765.

2.2 One-Time-Programmable (OTP) Devices

The availability of OTP devices is especially useful for

customers who need the flexibility for frequent code

updates and small volume applications.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the

program memory, the configuration bits must also be

programmed.

Plus and PROMATEII

2.3 Quick-Turnaround-Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available

for users who choose not to program a medium to high

quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but

with all EPROM locations and configuration options

already programmed by the factory. Certain code and

prototype verification procedures apply before production shipments are available. Please contact your local

Microchip Technology sales office for more details.

2.4 Serialized Quick-Turnaround Production (SQTPSM) Devices

Microchip offers a unique programming service where

a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be rando m, ps eudo-random or sequential.

Serial programming allows each device to have a

unique number, which can serve as an entry-code,

password or ID number.

1999 Microchip Technology Inc.

Advanced Information DS41124A-page 7

Page 8

PIC16C745/765

NOTES:

DS41124A-page 8 Advanced Information

1999 Microchip Technology Inc.

Page 9

PIC16C745/765

3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXX family can be

attributed to a number of architectural features commonly found in RISC microprocessor s. To begi n with,

the PIC16CXX uses a Har vard architecture, in which

program and data are accessed from separate memories using separate buses. This improves bandwidth

over tr aditional von Neu mann archi tecture in wh ich program and data are fetched from the same memory

using the same bus. Separating program and data

buses further allows instructions to be sized differently

than the 8-bit wide data word. Instruction opcodes are

14-bits wid e maki ng it po ssible to have all singl e word

instructions. A 14-bit wide program memory access

bus fet ches a 14 -bit ins tructio n in a sing le cycle . A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, most instructions

execute in a single cycle (166.6667 ns @ 24 MHz)

except for program branches.

Memory

Device

PIC16C745 8K 256 28 8 5

PIC16C765 8K 256 40 8 8

Program

x14

Data

x8

Pins

The PIC16CXX can directly or indirectly address its

register files or data memory. Al l s pec ia l function registers, including the program counter, are mapped in the

data memory . The PIC16CXX has an orthogonal (symmetrical) ins tr ucti on s et th at m akes it po ssible to c arr y

out any operatio n on any reg ister usin g any add ressin g

mode. This symmetrical nature and lack of ‘special

optimal situations’ make programming with the

PIC16CXX simple yet e fficient. In addition, the learning

curve is reduced signifi c antly.

A/D

Resolution

A/D

Channels

PIC16CXX devices contain an 8-bit ALU and working

register. The ALU is a general purpose arithmetic unit.

It performs arithmetic and Boolean functions between

the data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise

mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically

one operand is the working register (W register). The

other operand is a file register or an immediate constant. In single operand instructions, the operand is

either the W register or a file register.

The W register is an 8-bit working register use d for ALU

operations. It is not an addressable register.

Depending on the instruction executed, the ALU may

affect the v alu es of th e Ca rry (C), Digit Carry (DC), an d

Zero (Z) bits in th e STATUS register. The C and DC bits

operate as a borrow

bit and a digit borrow out bit,

respectively, in subtraction. See the SUBLW and SUBWF

instructions for examples.

1999 Microchip Technology Inc.

Advanced Information DS41124A-page 9

Page 10

PIC16C745/765

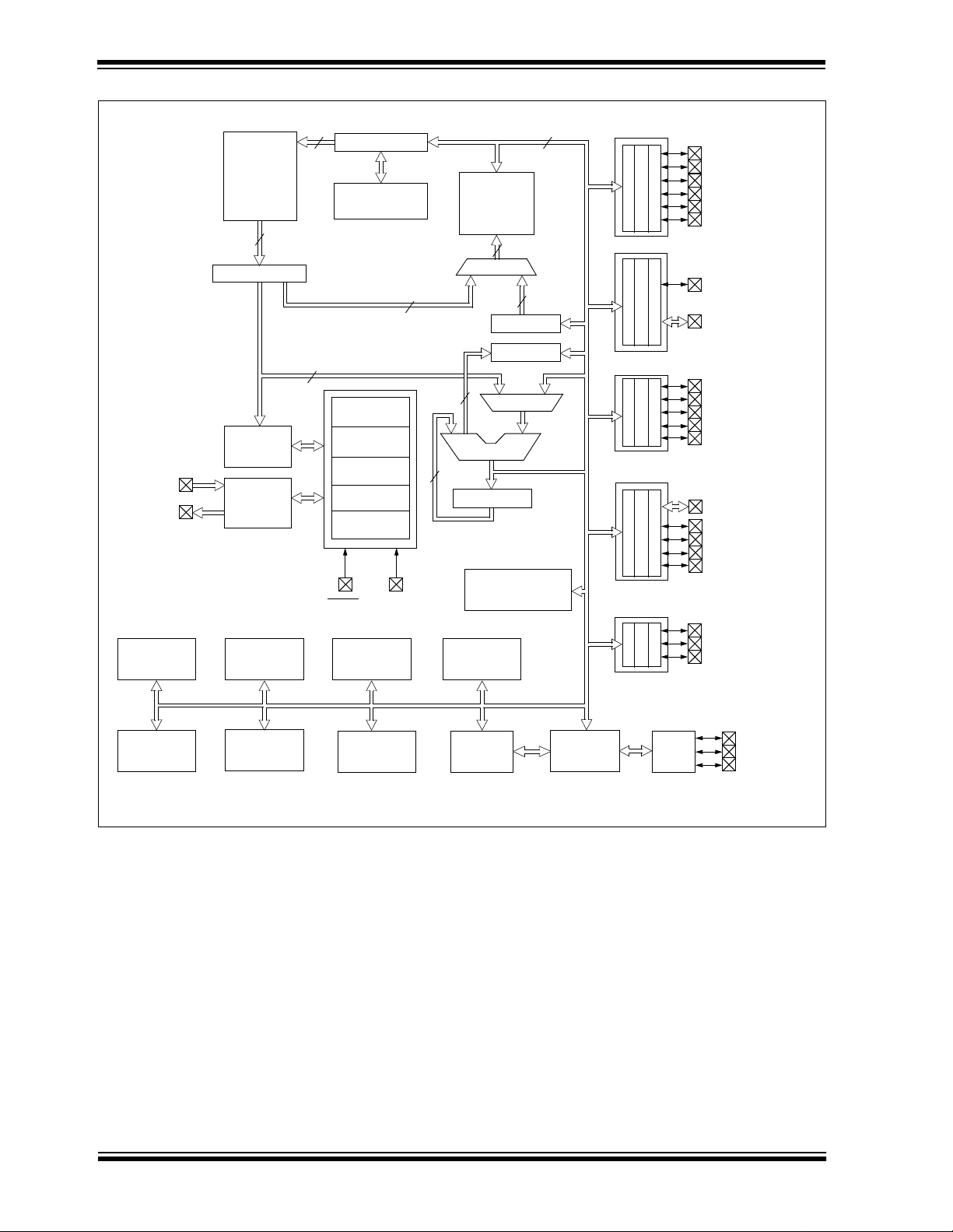

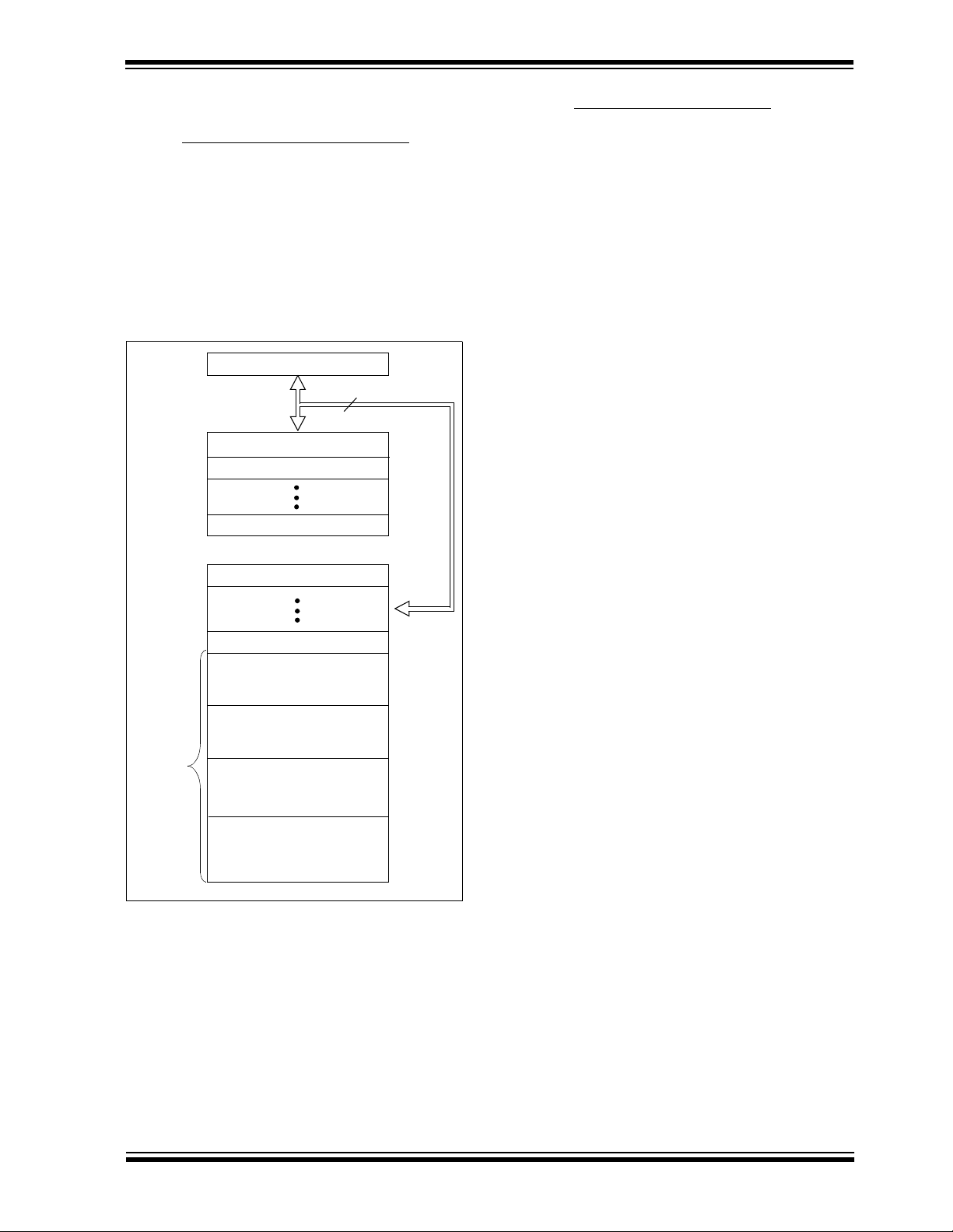

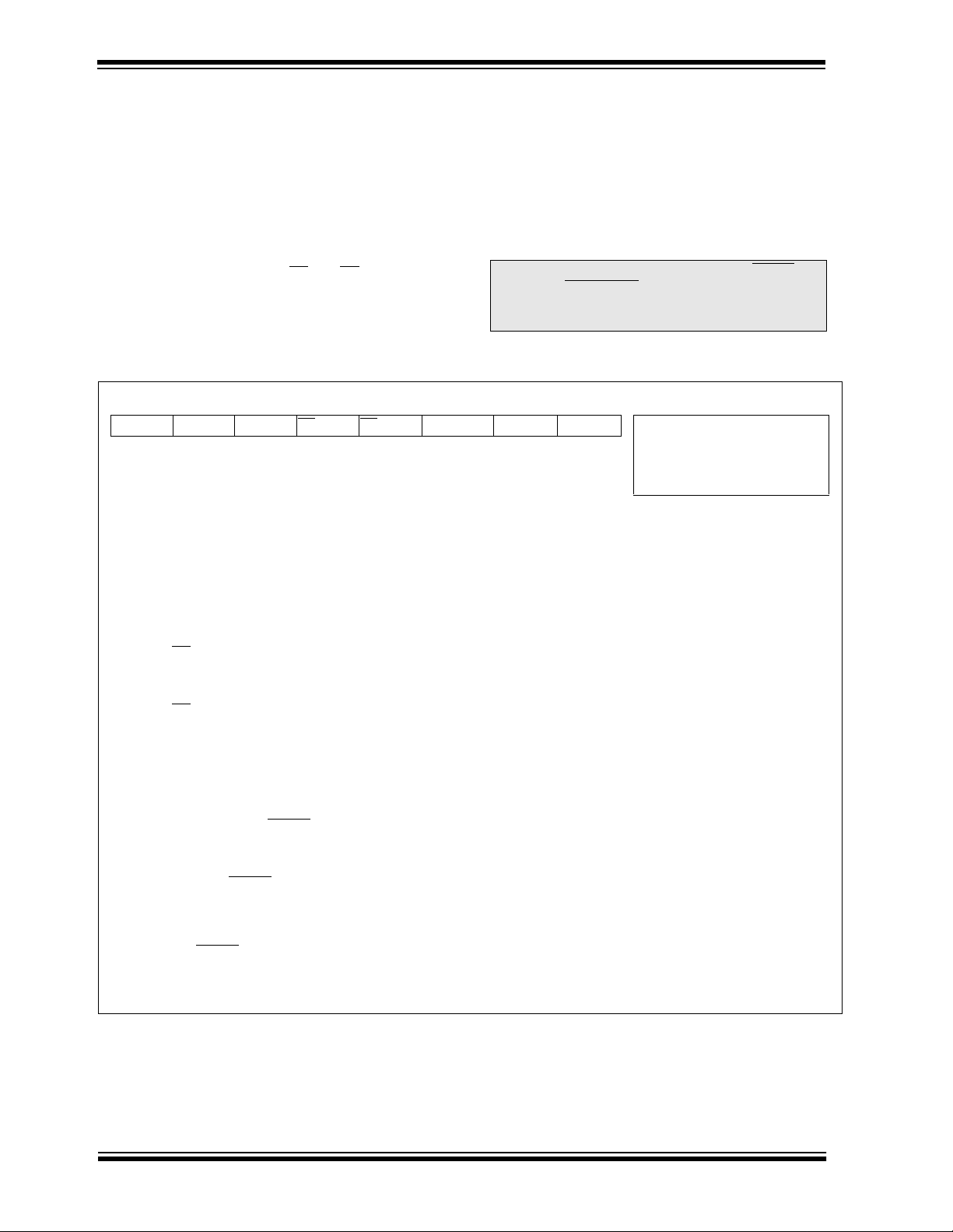

FIGURE 3-1: PIC16C745/765 BLOCK DIAGRAM

OSC1/

CLKIN

OSC2/

CLKOUT

Program

Bus

EPROM

Program

Memory

8K x 14

14

Instruction reg

Instruction

Decode &

Control

Timing

Generation

x4 PLL

13

Program Counter

8 Level Stack

Direct Addr

8

Power-up

Oscillator

Start-up Timer

Power-on

Watchdog

Brown-out

MCLR

(13 bit)

Timer

Reset

Timer

Reset

VDD, VSS

RAM Addr(1)

7

8

Data Bus

RAM

File

Registers

256 x 8

9

Addr MUX

8

FSR reg

STATUS reg

3

8-bit A/DTimer0 Timer1 Timer2

MUX

ALU

W reg

Parallel Slave Port

8

Indirect

Addr

PORTA

RA0/AN0

RA1/AN1

RA2/AN2

RA3/AN3/VREF

RA4/T0CKI

RA5/AN4

PORTB

RB0/INT

RB<7:1>

PORTC

RC0/T1OSO/T1CKI

RC1/T1OSI/CCP2

RC2/CCP1

RC6/TX/CK

RC7/RX/DT

PORTD

RD3:0/PSP3:0

RD4/PSP4

RD5/PSP5

RD6/PSP6

RD7/PSP7

(2)

PORTE

RE0/AN5/RD

RE1/AN6/WR

RE2/AN7/CS

(2)

(2)

(2)

(2)

(2)

(2)

(2)

(2)

CCP2

CCP1

USART

RAM

64 x 8

USB

Dual Port

Note 1: Higher order bits are from the STATUS register .

2: Not available on PIC16C745.

DS41124A-page 10 Advanced Information

USB

V

XCVR

DD+

1999 Microchip Technology Inc.

Page 11

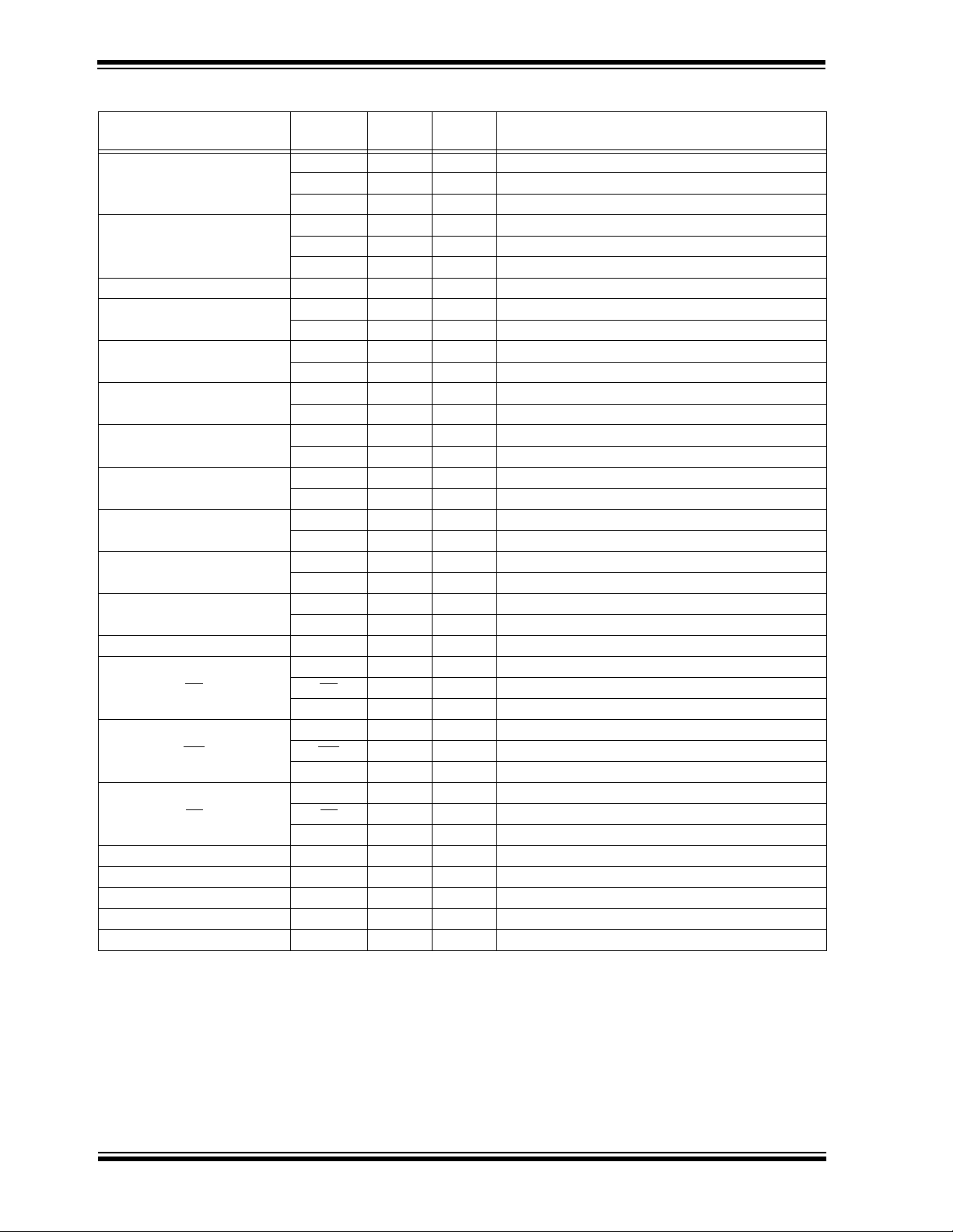

TABLE 3-1: PIC16C745/765 PINOUT DESCRIPTION

Name Function

/VPP

MCLR

OSC1/CLKIN

OSC2/CLKOUT

Input

Type

MCLR ST — Master Clear

PP Power — Programming Voltage

V

OSC1 Xtal — Crystal/Resonator

CLKIN ST — External Clock Input/ER resistor connection.

OSC2 — Xtal Crystal/Resonator

CLKOUT — CMOS Internal Clock (F

Output

Type

PIC16C745/765

Description

INT/4) Output

RA0/AN0

RA1/AN1

RA2/AN2

RA3/AN3/V

RA4/T0CKI

RA5/AN4

RB6/ICSPC

RB7/ICSPD

REF

RB0/INT

RB1 RB1 TTL CMOS Bi-directional I/O

RB2 RB2 TTL CMOS Bi-directional I/O

RB3 RB3 TTL CMOS Bi-directional I/O

RB4 RB4 TTL CMOS Bi-directional I/O with Interrupt on Change

RB5 RB5 TTL CMOS Bi-directional I/O with Interrupt on Change

RA0 ST CMOS Bi-directional I/O

AN0 AN — A/D Input

RA1 ST CMOS Bi-directional I/O

AN1 AN — A/D Input

RA2 ST CMOS Bi-directional I/O

AN2 AN — A/D Input

RA3 ST CMOS Bi-directional I/O

AN3 AN — A/D Input

REF AN — A/D Positive Reference

V

RA4 ST OD Bi-directional I/O

T0CKI ST — Timer 0 Clock Input

RA5 ST Bi-directional I/O

AN4 AN — A/D Input

RB0 TTL CMOS Bi-directional I/O

INT ST — Interrupt

RB6 TTL CMOS Bi-directional I/O with Interrupt on Change

ICSPC ST In-Circuit Serial Programming Clock input

RB7 TTL CMOS Bi-directional I/O with Interrupt on Change

ICSPD ST CMOS In-Circuit Serial Programming Data I/O

RC0 ST CMOS Bi-directional I/O

RC0/T1OSO/T1CKI

RC!/T1OSI/CCP2

RC2/CCP1/V

Legend: OD = open drain, ST = Schmitt Trigger

Note 1: Weak pull-ups. PORT B pull-ups are byte wide programmable.

2: PIC16C765 only.

1999 Microchip Technology Inc.

USB

USB VUSB Power 3.3V for pull up resistor

V

D- D- USB USB USB Differential Bus

D+ D+ USB USB USB Differential Bus

T1OSO — Xtal T1 Oscillator Output

T1CKI ST — T1 Clock Input

RC1 ST CMOS Bi-directional I/O

T1OSI Xtal — T1 Oscillator Input

CCP2 Capture In/Compare Out/PWM Out 2

RC2 ST CMOS Bi-directional I/O

CCP1 Capture In/Compare Out/PWM Out 1

Advanced Information DS41124A-page 11

Page 12

PIC16C745/765

TABLE 3-1: PIC16C745/765 PINOUT DESCRIPTION (CONTINUED)

Name Function

RC6/TX/CK

RC7/RX/DT

Input

Type

RC6 ST CMOS Bi-directional I/O

TX — CMOS USART Async Transmit

CK ST CMOS USART Master Out/ Slave In Clock

RC7 ST CMOS Bi-directional I/O

RX ST — USART Async Receive

DT ST CMOS USART Data I/O

Output

Type

Description

RD0/PSP0

RD1/PSP1

RD2/PSP2

RD3/PSP3

RD4/PSP4

RD5/PSP5

RD6/PSP6

RD7/PSP7

RE0/RD/AN5

RE1/WR/AN6

RE2/CS/AN7

RD0 TTL CMOS Bi-directional I/O

(2)

PSP0 TTL — Parallel Slave Port data input

RD1 TTL CMOS Bi-directional I/O

(2)

PSP1 TTL — Parallel Slave Port data input

RD2 TTL CMOS Bi-directional I/O

(2)

PSP2 TTL — Parallel Slave Port data input

RD3 TTL CMOS Bi-directional I/O

(2)

PSP3 TTL — Parallel Slave Port data input

RD4 TTL CMOS Bi-directional I/O

(2)

PSP4 TTL — Parallel Slave Port data input

RD5 TTL CMOS Bi-directional I/O

(2)

PSP5 TTL — Parallel Slave Port data input

RD6 TTL CMOS Bi-directional I/O

(2)

PSP6 TTL — Parallel Slave Port data input

RD7 TTL CMOS Bi-directional I/O

(2)

PSP7 TTL — Parallel Slave Port data input

RE0 ST CMOS Bi-directional I/O

(2)

RD TTL — Parallel Sl ave Port control input

AN5 AN — A/D Input

RE1 ST CMOS Bi-directional I/O

(2)

(2)

WR TTL — Parallel Slave Port control input

AN6 AN — A/D Input

RE2 ST CMOS Bi-directional I/O

(2)

(2)

CS TTL — Parallel Slave Port data input

AN7 AN — A/D Input

(2)

(2)

(2)

(2)

(2)

(2)

(2)

(2)

(2)

(2)

(2)

(2)

VDD VDD Power — Power

SS VSS Power — Ground

V

DD AVDD Power — Analog Power

AV

SS AVSS Power — Analog Ground

AV

Legend: OD = open drain, ST = Schmitt Trigger

Note 1: Weak pull-ups. PORT B pull-ups are byte wide programmable.

2: PIC16C765 only.

DS41124A-page 12 Advanced Information

1999 Microchip Technology Inc.

Page 13

PIC16C745/765

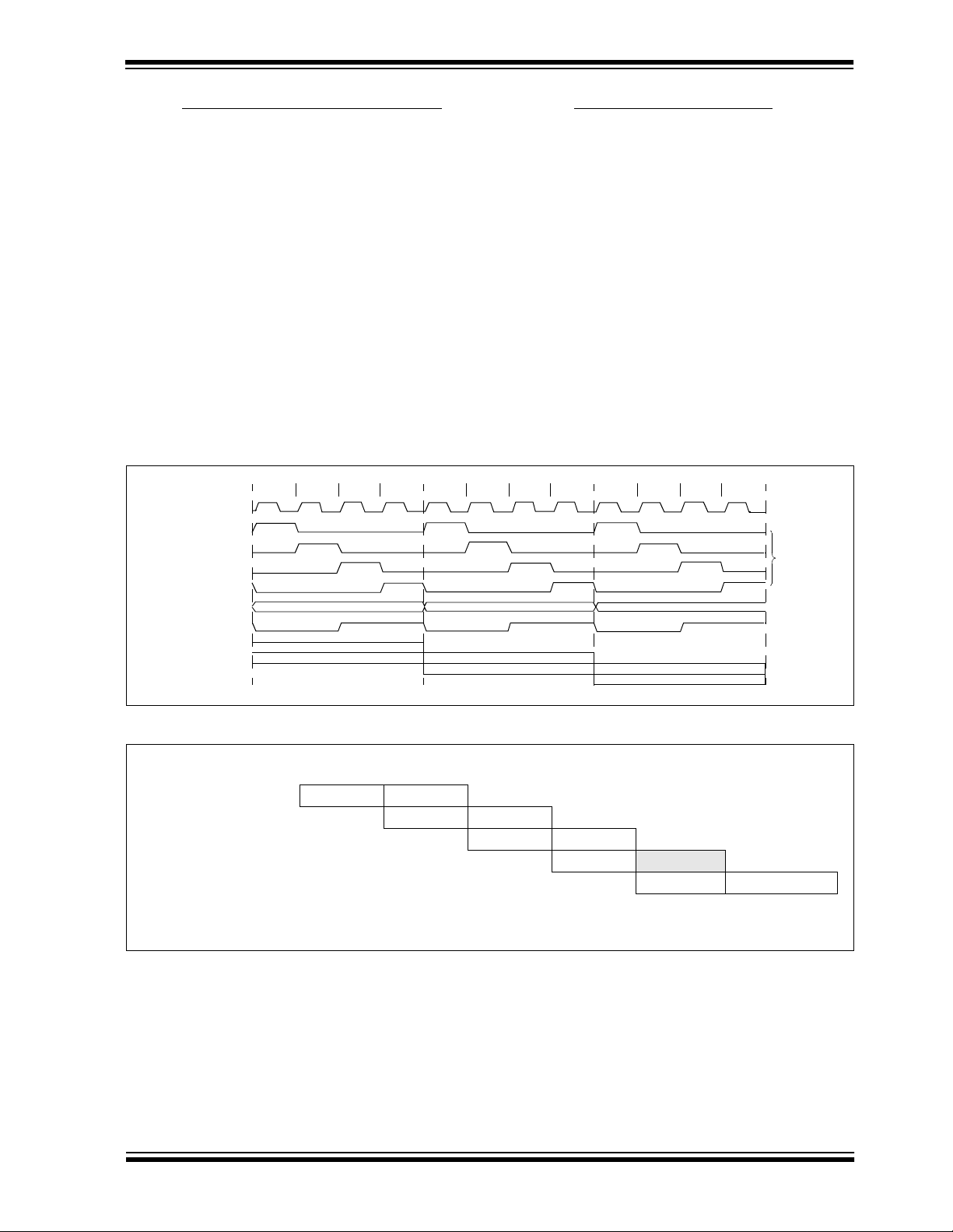

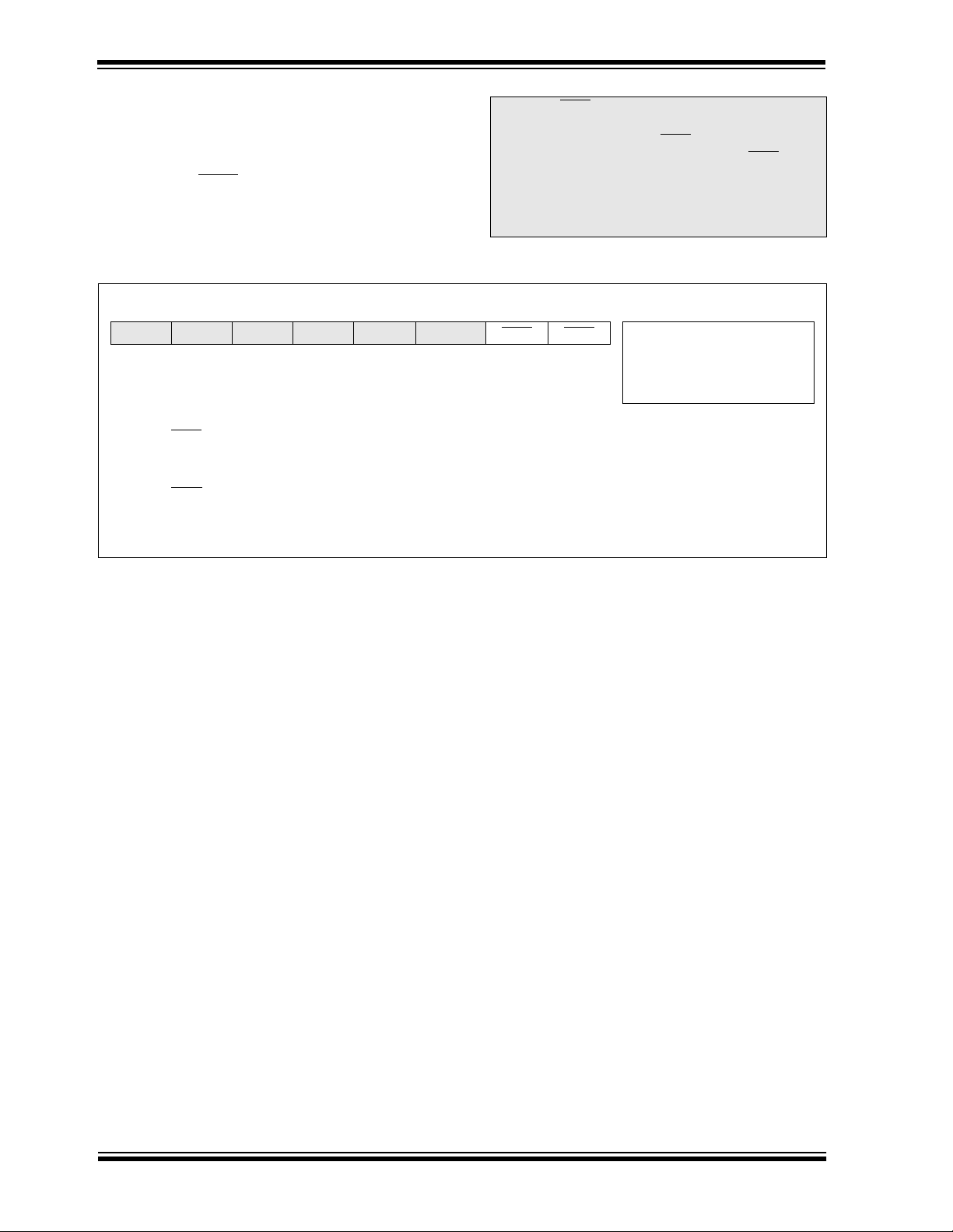

3.1 Clocking Scheme/Instruction Cycle

The clock input feeds an on-chip PLL. The clock output

from the PLL (F

INT) is internally divided by four to gen-

erate four non-overlapping quadrature clocks namely,

Q1, Q2, Q3 and Q4. Internally, the program counter

(PC) is incremented e very Q1, the instruction is f etched

from the program memory and latched into the instruction register in Q4. The ins truction is decod ed and executed during the following Q1 through Q4. The clocks

and instruction execution flow is shown in Figure 3-2.

FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

Q2 Q3 Q4

OSC2/CLKOUT

(EC mode)

FINT

Q1

Q2

Q3

Q4

PC

Q1

PC PC+1 PC+2

Fetch INST (PC)

Execute INST (PC-1) Fetch INST (PC+1)

Q1

3.2 Instruction Flow/Pipelining

An “Instruction Cycle” consists of four Q cycles (Q1,

Q2, Q3 and Q4). The instruction fetch and execute are

pipelined such that fetch takes one instruction cycle,

while decode and execute takes another instruction

cycle. However, due to the pipelining, each instruction

effectively executes in one cycle. If an instruction

causes the program counter to change (e.g., GOTO),

then two cycles are required t o complete t he instruction

(Example 3-1).

A fetch cycle begins with the program counter (PC)

incrementing in Q1.

In the ex ecu tion cycle , t he f etched i nstruction i s latche d

into the “Instruction Register" (IR) in cycle Q1. This

instruction is then decoded and executed during the

Q2, Q3 and Q4 cycles . Data mem ory is read during Q2

(operand read) and written during Q4 (destination

write).

Q2 Q3 Q4

Execute INST (PC) Fetch INST (PC+2)

Q2 Q3 Q4

Q1

Execute INST (PC+1)

Internal

phase

clock

EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

TCY0TCY1TCY2TCY3TCY4TCY5

1. MOVLW 55h

2. MOVWF PORTB

3. CALL SUB_1

4. BSF PORTA, BIT3 (Forced NOP)

5. Instruction @ address SUB_1

Note: All instructions are single cycle, except for any program branches. These take two cycles, since the fetch

instruction is “flushed” from the pipeline, while the new instruction is being fetched and then executed.

1999 Microchip Technology Inc.

Fetch 1 Execute 1

Fetch 2 Execute 2

Fetch 3 Execute 3

Fetch 4 Flush

Fetch SUB_1 Execute SUB_1

Advanced Information DS41124A-page 13

Page 14

PIC16C745/765

NOTES:

DS41124A-page 14 Advanced Information

1999 Microchip Technology Inc.

Page 15

PIC16C745/765

4.0 MEMORY ORGANIZATION

4.1 Program Memory Organization

The PIC16C745/765 has a 13-bit program counter

capable of addressing an 8K x 14 program memory

space. All devices covered by this datasheet have 8K x

14 bits of program memory. The address range is

0000h - 1FFFh for all devices.

The reset vector is at 0000h and the interrupt vector is

at 0004h.

FIGURE 4-1: PIC16C745/765 PROGRAM

MEMORY MAP AND STACK

PC<12:0>

CALL, RETURN

RETFIE, RETLW

Stack Level 1

Stack Level 2

Stack Level 8

13

4.2 Data Memory Organization

The data memory is partitioned into multiple banks

which contain the General Purpose Registers (GPR)

and the Special Function Registers (SFR). Bits RP1

and RP0 are the bank select bits.

RP<1:0> (STATUS<6:5>)

= 00 → Bank0

= 01 → Bank1

= 10 → Bank2

= 11 → Bank3

Each bank extends up to 7Fh (128 bytes). The lower

locations of each bank are reserved for the SFRs.

Above the SFRs are GPRs, implemented as static

RAM.

All implemented ban ks co ntain SF Rs. Some “h igh us e”

SFRs from one bank may be mirrored in another bank

for code reduction and quicker access.

4.2.1 GENERAL PURPOSE REGISTER FILE The register file can b e access ed eithe r dire ctly o r indi-

rectly through the File Select Register (FSR)

(Section 4.5).

On-chip

Program

Memory

Reset Vector

Interrupt Vector

Page 0

Page 1

Page 2

Page 3

0000h

0004h

0005h

07FFh

0800h

0FFFh

1000h

17FFh

1800h

1FFFh

1999 Microchip Technology Inc.

Advanced Information DS41124A-page 15

Page 16

PIC16C745/765

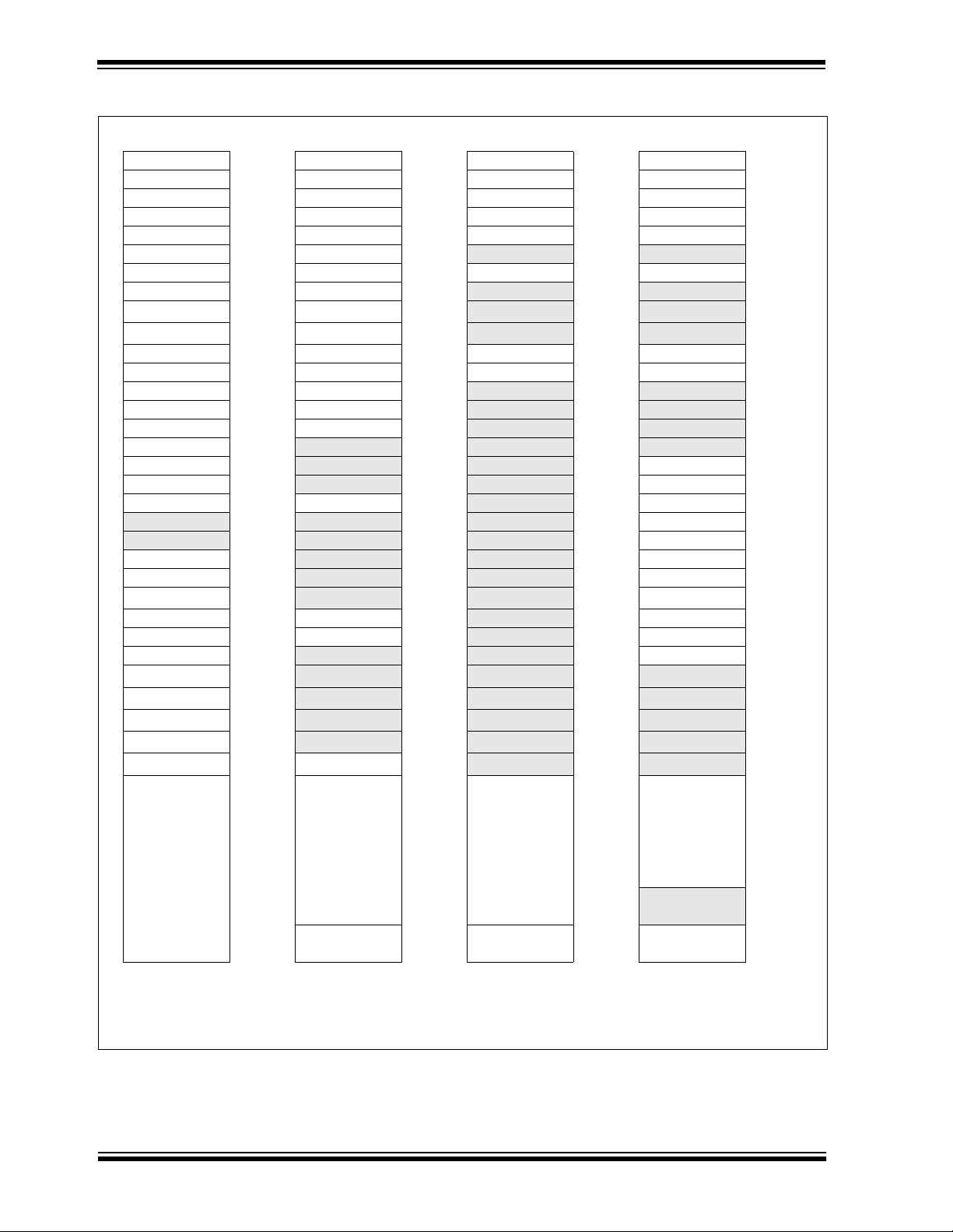

FIGURE 4-2: DATA MEMORY MAP FOR PIC16C745/765

Bank 0 File

Indirect addr.(*) 00h Indirect addr.(*) 80h Indirect addr.(*) 100h Indirect addr.(*) 180h

TMR0 01h OPTION_REG 81h TMR0 101h OPTION_REG 181h

PCL 02h PCL 82h PCL 102h PCL 182h

STATUS 03h STATUS 83h STATUS 103h STATUS 183h

FSR 04h FSR 84h FSR 104h FSR 184h

PORTA 05h TRISA 85h

PORTB 06h TRISB 86h PORTB 106h TRISB 186h

PORTC 07h TRISC 87h

(2)

PORTD

(2)

PORTE

PCLATH 0Ah PCLATH 8Ah PCLATH 10Ah PCLATH 18Ah

INTCON 0Bh INTCON 8Bh INTCON 10Bh INTCON 18B h

PIR1 0Ch PIE1 8Ch

PIR2 0Dh PIE2 8Dh

TMR1L 0Eh PCON 8Eh

TMR1H 0Fh

T1CON 10h

TMR2 11h

T2CON 12h PR2 92h

CCPR1L 15h

CCPR1H 16h

CCP1CON 17h

RCSTA 18h TXSTA 98h

TXREG 19h SPBRG 99h

RCREG 1Ah

CCPR2L 1B h

CCPR2H 1Ch 9Ch 11Ch

CCP2CON 1Dh 9Dh 11Dh

ADRESH 1Eh 9Eh 11Eh

ADCON0 1Fh ADCON1 9Fh 11Fh

General

Purpose

Register

96 Bytes

Address

08h

09h

13h 93h 113h UEIE 193h

14h 94h 114h USTAT 194h

20h General

Bank 1 File

(2)

TRISD

(2)

TRISE

Purpose

Register

80 Bytes

Address

88h 108h 188h

89h 109h 189h

8Fh 10Fh 18Fh

90h 110h UIR 190h

91h 111h UIE 191h

95h 115h UCTRL 195h

96h 116h UADDR 196h

97h 117h

9Ah 11Ah U EP 2 19Ah

9Bh 11Bh

A0h General

Bank 2 File

Address

105h 185h

107h 187h

10Ch 18Ch

10Dh 18Dh

10Eh 18Eh

112h UEIR 192h

118h UEP0 198h

119h UEP1 199h

120h USB Dual Port

Purpose

Register

80 Bytes

Bank 3 File

USWSTAT

Memory

64 Bytes

(1)

Address

197h

(1)

19Bh

(1)

19Ch

(1)

19Dh

(1)

19Eh

(1)

19Fh

1A0h

EFh 16Fh 1EFh

accesses

7Fh FFh 17Fh 1FFh

Unimplemented data memory locations, read as ‘0’.

*Not a physical register.

Note 1: Reserved registers may contain USB state information.

2: Parallel slave ports (PORTD and PORTE) not implemented on PIC16C745; always maintain these bits clear.

DS41124A-page 16 Advanced Information

70h-7Fh

F0h accesses

70h-7Fh

170h accesses

1DFh

1E0h

1F0h

70h-7Fh

1999 Microchip Technology Inc.

Page 17

PIC16C745/765

4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers can be classified into

two sets (core and periphe ral). Those registers associ-

The Special Function Registers are registers used by

the CPU and Peripheral Modules for controlling the

desired operation of the device. These registers are

implemented as static RAM.

ated with the “core” func tions are described i n this section, and those related to the operation of the peripheral

features are described in the section of that peripheral

feature.

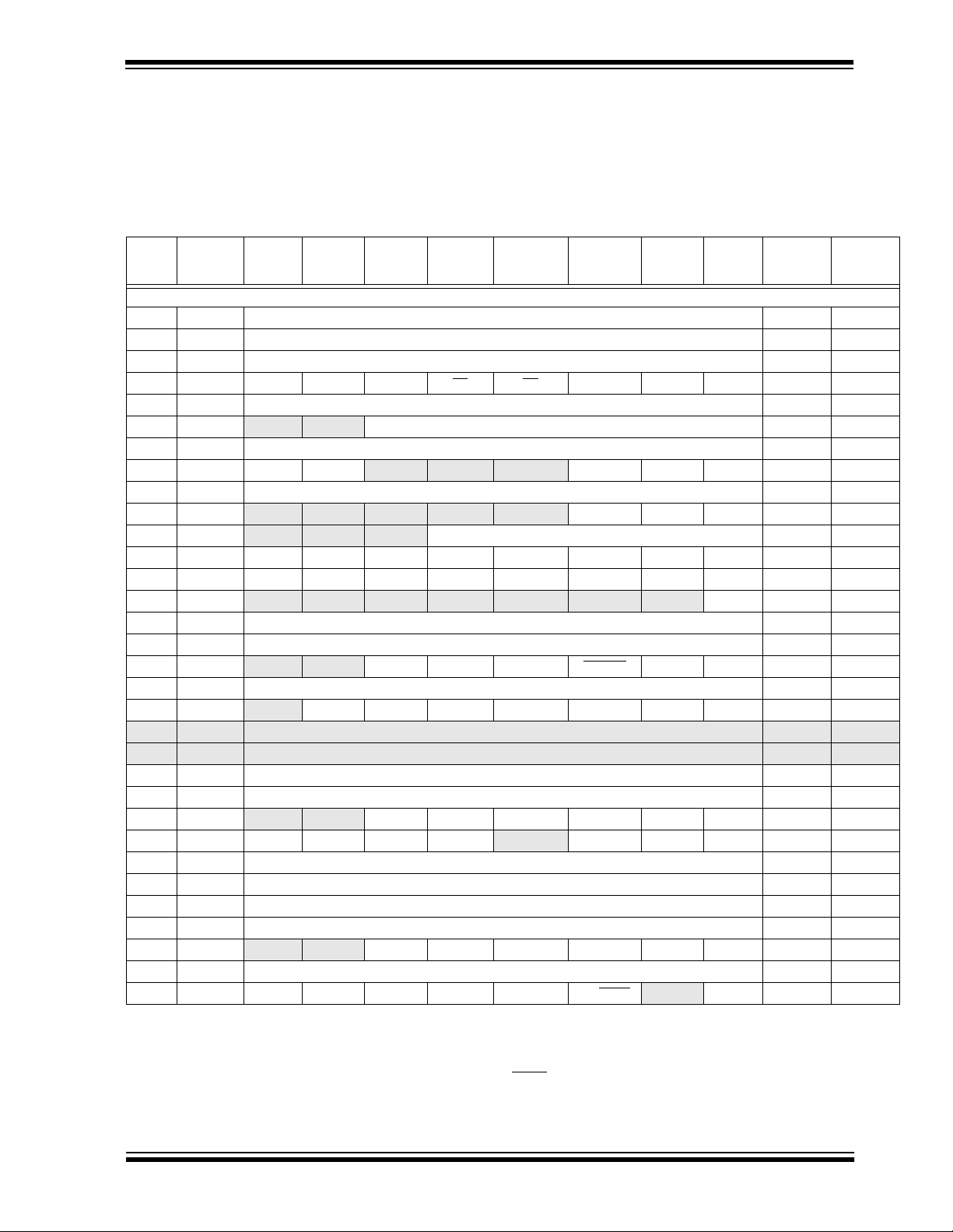

TABLE 4-1: SPECIAL FUNCTION REGISTER SUMMARY

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Value on:

POR,

BOR

Bank 0

00h INDF

01h TMR0 Timer0 module’s register xxxx xxxx uuuu uuuu

02h PCL

03h STATUS

04h FSR

05h PORTA

06h PORTB PORTB Data Latch when written: PORTB pins when read xxxx xxxx uuuu uuuu

07h PORTC

08h PORTD

09h PORTE

0Ah PCLATH

0Bh INTCON

0Ch PIR1 PSPIF

0Dh PIR2

0Eh TMR1L Holding register for the Least Significant Byte of the 16-bit TMR1 register xxxx xxxx uuuu uuuu

0Fh TMR1H Holding register for the Most Significant Byte of the 16-bit TMR1 register xxxx xxxx uuuu uuuu

10h T1CON

11h TMR2 Timer2 module’s register 0000 0000 0000 0000

12h T2CON

13h — Unimplemented — —

14h — Unimplemented — —

15h CCPR1L Capture/Compare/PWM Register1 (LSB) xxxx xxxx uuuu uuuu

16h CCPR1H Capture/Compare/PWM Register1 (MSB) xxxx xxxx uuuu uuuu

17h CCP1CON

18h RCSTA SPEN RX9 SREN CREN

19h TXREG USART Transmit Data Register 0000 0000 0000 0000

1Ah RCREG USART Receive Data Register 0000 0000 0000 0000

1Bh CCPR2L Capture/Compare/PWM Register2 (LSB) xxxx xxxx uuuu uuuu

1Ch CCPR2H Capture/Compare/PWM Register2 (MSB) xxxx xxxx uuuu uuuu

1Dh CCP2CON

1Eh ADRES A/D Result Register xxxx xxxx uuuu uuuu

1Fh ADCON0 ADCS1 ADCS0 CHS2 CHS1 CHS0 GO/DONE

(3)

Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 0000 0000

(3)

Program Counter's (PC) Least Significant Byte 0000 0000 0000 0000

(3)

(3)

(4)

(4)

(1,3)

(3)

(2)

IRP

Indirect data memory address pointer xxxx xxxx uuuu uuuu

— — PORTA Data Latch when written: PORTA pins when read --0x 0000 --0u 0000

RC7 RC6

PORTD Data Latch when written: PORTD pins when read xxxx xxxx uuuu uuuu

— — — — — RE2 RE1 RE0 ---- -xxx ---- -uuu

— — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 ---0 0000

GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u

(4)

— — — – — — — CCP2I F ---- ---0 ---- ---0

— — T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON --00 0000 --uu uuuu

— TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 -000 0000 -000 0000

— — DC1B1 DC1B0 CCP1M3 CCP1M2 CCP1M1 C CP1M0 --00 0000 --00 0000

— — DC2B1 DC2B1 CCP2M3 CCP2M2 CCP2M1 C CP2M0 --00 0000 --00 0000

(2)

RP1

ADIF RCIF TXIF USBIF CCP1IF TMR2IF TMR1IF 0000 0000 0000 0000

RP0 TO PD ZDCC0001 1xxx 000q quuu

— — —

— FERR OERR RX9D 0000 -00x 0000 -00x

RC2 RC1 RC0

—ADON0000 00-0 0000 00-0

xx-- -xxx uu-- -uuu

Legend:x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as ’0’.

Shaded locations are unimplemented, read as ‘0’.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents

are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR

and Watchdog Timer Reset.

3: These registers can be addressed from either bank.

4: The Parallel Slav e Port (PORTD and PORTE) is not implemented on the PIC16C745, always maintain these bits clear.

Value on all

other resets

(2)

1999 Microchip Technology Inc.

Advanced Information DS41124A-page 17

Page 18

PIC16C745/765

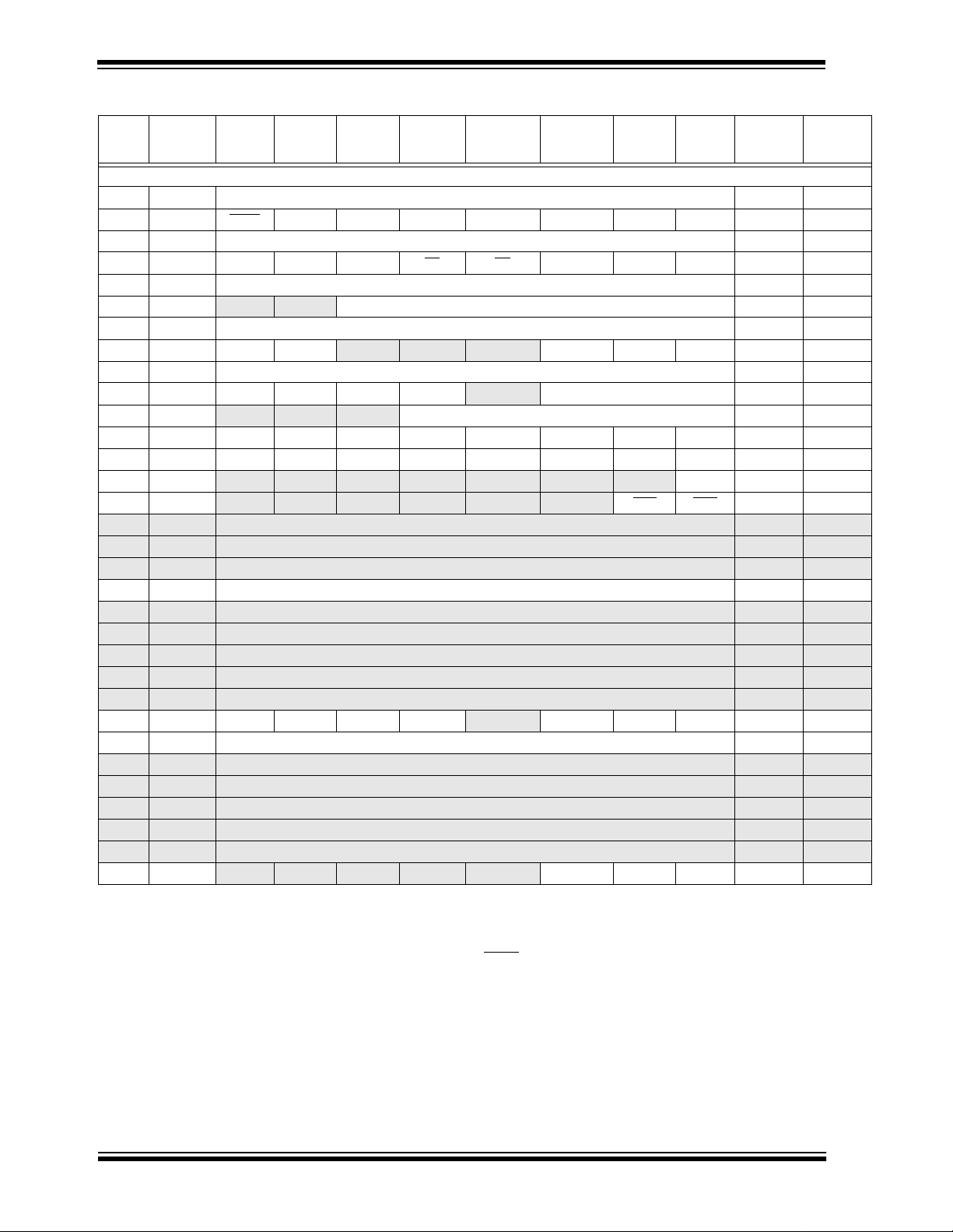

TABLE 4-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bank 1

(3)

80h INDF

81h OPTION RBPU

82h PCL

83h STATUS

84h FSR

85h TRISA

86h TRISB PORTB Data Direction Register 1111 1111 1111 1111

87h TRISC

88h TRISD

89h TRISE

8Ah PCLATH

8Bh INTCON

8Ch PIE1 PSPIE

8Dh PIE2

8Eh PCON

8Fh — Unimplemented — —

90h — Unimplemented — —

91h — Unimplemented — —

92h PR2 Timer2 Period Register 1111 1111 1111 1111

93h — Unimplemented — —

94h — Unimplemented — —

95h — Unimplemented — —

96h — Unimplemented — —

97h — Unimplemented — —

98h TXSTA CSRC TX9 TXEN SYNC

99h SPBRG Baud Rate Generator Register 0000 0000 0000 0000

9Ah — Unimplemented — —

9Bh — Unimplemented — —

9Ch — Unimplemented — —

9Dh — Unimplemented — —

9Eh — Unimplemented — —

9Fh ADCON1

Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 0000 0000

INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111

(3)

Program Counter’s (PC) Least Significant Byte 0000 0000 0000 0000

(3)

IRP RP1 RP0 TO PD ZDCC0001 1xxx 000q quuu

(3)

Indirect data memory address pointer xxxx xxxx uuuu uuuu

— — PORTA Data Direction Register --11 1111 --11 1111

TRISC7 TRISC8

(4)

PORTD Data Direction Register 1111 1111 1111 1111

(4)

IBF OBF IBOV PSPMODE — PORTE Data Direction Bits 0000 -111 0000 -111

(1,3)

— — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 ---0 0000

(3)

GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u

(4)

ADIE RCIE TXIE USBIE CCP1IE TMR2IE TMR1IE 0000 0000 0000 0000

— — — — — — —CCP2IE---- ---0 ---- ---0

— — — — — —PORBOR ---- --qq ---- --uu

— — — — — PCFG2 PCFG1 PCFG0 ---- -000 ---- -000

— — —

— BRGH TRMT TX9D 0000 -010 0000 -010

TRISC2 TRISC1 TRISC0

Value on:

POR,

BOR

11-- -111 11-- -111

Legend:x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as ’0’.

Shaded locations are unimplemented, read as ‘0’.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents

are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR

and Watchdog Timer Reset.

3: These registers can be addressed from either bank.

4: The Parallel Slav e Port (PORTD and PORTE) is not implemented on the PIC16C745, always maintain these bits clear.

Value on all

other resets

(2)

DS41124A-page 18 Advanced Information

1999 Microchip Technology Inc.

Page 19

PIC16C745/765

TABLE 4-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bank 2

(3)

100h

101h TMR0 Timer0 module’s register xxxx xxxx uuuu uuuu

102h

103h

104h

105h — Unimplemented — —

106h PORTB PORTB Data Latch when written: PORTB pins when read xxxx xxxx uuuu uuuu

107h — Unimplemented — —

108h — Unimplemented — —

109h — Unimplemented — —

10Ah

10Bh

10Ch-

11Fh

INDF

(3)

PCL

ST ATUS

(3)

FSR

PCLATH

INTCON

Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 0000 0000

Program Counter's (PC) Least Significant Byte 0000 0000 0000 0000

(3)

IRP RP1 RP0 TO PD ZDCC0001 1xxx 000q quuu

Indirect data memory address pointer xxxx xxxx uuuu uuuu

(1,3)

— — — Write Buffer for the upper 5 bits of the Program Counter ---0 0000 ---0 0000

(3)

GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u

— Unimplemented — —

Value on:

POR,

BOR

Legend:x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as ’0’.

Shaded locations are unimplemented, read as ‘0’.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents

are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR

and Watchdog Timer Reset.

3: These registers can be addressed from either bank.

4: The Parallel Slav e Port (PORTD and PORTE) is not implemented on the PIC16C745, always maintain these bits clear.

Value on all

other resets

(2)

1999 Microchip Technology Inc.

Advanced Information DS41124A-page 19

Page 20

PIC16C745/765

TABLE 4-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bank 3

(3)

180h

181h OPTION_REG RBPU

182h

183h

184h

185h — Unimplemented — —

186h TRISB PORTB Data Direction Register 1111 1111 1111 1111

187h — Unimplemented — —

188h — Unimplemented — —

189h — Unimplemented — —

18Ah

18Bh

18Ch-

18Fh

190h UIR

191h UIE

192h UEIR BTS_ERR OWN_ERR WRT_ERR BTO_ERR DFN8 CRC16 CRC5 PID_ERR 0000 0000 0000 0000

193h UEIE BTS_ERR OWN_ERR WRT_ERR BTO_ERR DFN8 CRC16 CRC5 PID_ERR 0000 0000 0000 0000

194h USTAT

195h UCTRL

196h UADDR

197h USWSTAT SWSTAT7 SWSTAT6 SWSTAT5 SWSTAT4 SWSTAT3 SWSTAT2 SWSTAT1 SWSTAT0 0000 0000 0000 0000

198h UEP0

199h UEP1

19Ah UEP2

19Bh-

19Fh

INDF

(3)

PCL

ST ATUS

FSR

PCLATH

INTCON

Reserved Reserved, do not use. 0000 0000 0000 0000

Addressing this location uses contents of FSR to address data memory (not a physical register) 0000 0000 0000 0000

INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111

Program Counter’s (PC) Least Significant Byte 0000 0000 0000 0000

(3)

IRP RP1 RP0 TO PD ZDCC0001 1xxx 000q quuu

(3)

Indirect data memory address pointer xxxx xxxx uuuu uuuu

(1,3)

(3)

— Unimplemented — —

— — —

GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u

— — STALL UIDLE TOK_DNE ACTIVITY UERR USB_RST --00 0000 --00 0000

— — STALL UIDLE TOK_DNE ACTIVITY UERR USB_RST --00 0000 --00 0000

— — — ENDP1 ENDP0 IN — — ---x xx-- ---u uu--

— — SEO PKT_DIS DEV_ATT RESUME SUSPND — --x0 000- --xq qqq-

— ADDR6 ADDR5 ADDR4 ADDR3 ADDR2 ADDR1 ADDR0 -000 0000 -000 0000

— — — — EP_CTL_DIS EP_OUT_EN EP_IN_EN EP_STALL ---- 0000 ---- 0000

— — — — EP_CTL_DIS EP_OUT_EN EP_IN_EN EP_STALL ---- 0000 ---- 0000

— — — — EP_CTL_DIS EP_OUT_EN EP_IN_EN EP_STALL ---- 0000 ---- 0000

Write Buffer for the upper 5 bits of the Program Counter

Value on:

POR,

BOR

---0 0000 ---0 0000

Legend:x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as ’0’.

Shaded locations are unimplemented, read as ‘0’.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents

are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR

and Watchdog Timer Reset.

3: These registers can be addressed from either bank.

4: The Parallel Slav e Port (PORTD and PORTE) is not implemented on the PIC16C745, always maintain these bits clear.

Value on all

other resets

(2)

DS41124A-page 20 Advanced Information

1999 Microchip Technology Inc.

Page 21

PIC16C745/765

TABLE 4-2: USB DUAL PORT RAM

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

1A0h BD0OST

1A1h BD0OBC

1A2h BD0OAL Buffer Address Low xxxx xxxx uuuu uuuu

1A3h

1A4h BD0IST

1A5h BD0IBC

1A6h BD0IAL Buffer Address Low xxxx xxxx uuuu uuuu

1A7h

1A8h BD1OST

1A9h BD1OBC

1AAh BD1OAL Buffer Address Low xxxx xxxx uuuu uuuu

1ABh

1ACh BD1IST

1ADh BD1IBC

1AEh BD1IAL Buffer Address Lo w xxxx xxxx uuuu uuuu

1AFh

1B0h BD2OST

1B1h BD2OBC

1B2h BD2OAL Buffer Address Low xxxx xxxx uuuu uuuu

1B3h

1B4h BD2IST

1B5h BD2IBC

1B6h BD2IAL Buffer Address Low xxxx xxxx uuuu uuuu

1B7h

1B8h-

1DFh

— Reserved — —

— Reserved — —

— Reserved — —

— Reserved — —

— Reserved — —

— Reserved — —

UOWN

UOWN

UOWN

UOWN

UOWN

UOWN

UOWN

UOWN

UOWN

UOWN

UOWN

UOWN

40 byte USB Buffer xxxx xxxx uuuu uuuu

DATA0/1

DATA0/1

— — — —

DATA0/1

DATA0/1

— — — —

DATA0/1

DATA0/1

— — — —

DATA0/1

DATA0/1

— — — —

DATA0/1

DATA0/1

— — — —

DATA0/1

DATA0/1

— — — —

PID3

—

PID3

—

PID3

—

PID3

—

PID3

—

PID3

—

PID2

PID2

PID2

PID2

PID2

PID2

—

—

—

—

—

—

PID1

DTS

Byte Count

PID1

DTS

Byte Count

PID1

DTS

Byte Count

PID1

DTS

Byte Count

PID1

DTS

Byte Count

PID1

DTS

Byte Count

PID0

BSTALL

PID0

BSTALL

PID0

BSTALL

PID0

BSTALL

PID0

BSTALL

PID0

BSTALL

—

—

—

—

—

—

—

—

—

—

—

—

Value on:

POR,

BOR

—

xxxx xxxx uuuu uuuu

—

xxxx xxxx uuuu uuuu

—

xxxx xxxx uuuu uuuu

—

xxxx xxxx uuuu uuuu

—

xxxx xxxx uuuu uuuu

—

xxxx xxxx uuuu uuuu

—

xxxx xxxx uuuu uuuu

—

xxxx xxxx uuuu uuuu

—

xxxx xxxx uuuu uuuu

—

xxxx xxxx uuuu uuuu

—

xxxx xxxx uuuu uuuu

—

xxxx xxxx uuuu uuuu

Legend:x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as ’0’.

Shaded locations are unimplemented, read as ‘0’.

Value on all

other resets

(2)

1999 Microchip Technology Inc.

Advanced Information DS41124A-page 21

Page 22

PIC16C745/765

4.2.2.1 STATUS REGISTER

The STATUS register, shown in Register 4-1, contains

the arithmetic status of th e ALU , the RE SET status an d

the bank select bits for data memory.

The STATUS register can be the destination for any

instruction, as with any other register. If the STATUS

register is the destination for an instruction that affects

the Z, DC or C bits, then the write to these three bits is

disabled. The se bi ts ar e set or c leared accordi ng to the

device logic. Fur th er more, the TO

and PD bits are not

writable. Therefore, the result of an instruction with the

STATUS register as desti nation may be different th an

intended.

For example, CLRF STATUS will clear the up p er- t h ree

bits and set th e Z bi t. T his l ea v es the STATUS register

as 000u u1uu (where u = unchanged).

It is recommended that only BCF, BSF, SWAPF and

MOVWF instruct io ns be used to alter t he S TATUS register. Thes e in stru cti on s do not affect the Z, C or DC bits

in the STATUS register. For other instructions which do

not affect status bits, see the "Instruction Set Summary."

Note 1: The C and DC bits operate as borrow and

digit borrow

tion. See the SUBLW and SUBWF instruc-

tions for examples.

REGISTER 4-1: STATUS REGISTER (STATUS: 03h, 83h, 103h, 183h)

R/W-0 R/W-0 R/W-0 R-1 R-1 R/W-x R/W-x R/W-x

IRP RP1 RP0 TO

bit7 bit0

PD ZDC

bit 7: IRP: Register Bank Select bit (used for indirect addressing)

1 = Bank 2, 3 (100h - 1FFh)

0 = Bank 0, 1 (00h - FFh)

bit 6-5: RP<1:0>: Register Bank Select bits (used for direct addressing)

00 = Bank 0 (00h - 7Fh)

01 = Bank 1 (80h - FFh)

10 = Bank 2 (100h - 17Fh)

11 = Bank 3 (180h - 1FFh)

bit 4: TO

: Time-out bit

1 = After power-up, CLRWDT instruction, or SLEEP instruction

0 = A WDT time-out occurred

bit 3: PD

: Power-down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

bit 2: Z: Zero bit

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

bit 1: DC: Digit carry/borrow

bit (ADDWF, ADDLW,SUBLW,SUBWF instructions)

1 = A carry-out from the 4th low order bit of the result occurred

0 = No carry-out from the 4th low order bit of the result

bit 0: C: Carry/borrow

bit (ADDWF, ADDLW,SUBLW,SUBWF instructions)

1 = A carry-out from the most significant bit of the result occurred

0 = No carry-out from the most significant bit of the result occurred

(1)

C

(1)

bits, respectively, in subtrac-

R = Readable bit

W = Writable bit

U = Unimplemented bit,

read as ‘0’

- n = Value at POR reset

(1)

Note1: For borrow

the polarity is reversed. A subtraction is executed by adding the two’s complement of the second operand. F or rotate (RRF, RLF) instructions, this bit is loade d with eithe r the high or lo w ord er bit of the

source register.

DS41124A-page 22 Advanced Information

1999 Microchip Technology Inc.

Page 23

PIC16C745/765

4.2.2.2 OPTION REGISTER

Note: To achieve a 1:1 prescaler as signmen t for

The OPTION_REG register is a readable and writable

register , which contai ns various c ontrol bits to c onfigure

the TMR0/WDT prescaler, the external INT Interrupt,

TMR0 and the weak pull-ups on PORTB.

REGISTER 4-2: OPTION REGISTER (OPTION_REG: 81h, 181h)

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1

RBPU

bit7 bit0

bit 7: RBPU : PORTB Pull-up Enable bit

bit 6: INTEDG: Interrupt Edge Select bit

bit 5: T0CS: TMR0 Clock Source Select bit

bit 4: T0SE: TMR0 Source Edge Select bit

bit 3: PSA: Prescaler Assignment bit

bit 2-0: PS<2:0>: Prescaler Rate Select bits

INTEDG T0CS T0SE PSA PS2 PS1 PS0 R = Readable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

1 = Interrupt on rising edge of RB0/INT pin

0 = Interrupt on falling edge of RB0/INT pin

1 = Transition on RA4/T0CKI pin

0 = Internal instruction cycle clock (CLKOUT)

1 = Increment on high-to-low transition on RA4/T0C KI pin

0 = Increment on low-to-high transition on RA4/T0C KI pin

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

Bit Value TMR0 Rate WDT Rate

000

001

010

011

100

101

110

111

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

1 : 256

1 : 1

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

the TMR0 register, assign the prescaler to

the watchdog timer.

W = Writable bit

U = Unimplemented bit,

read as ‘0’

-n = Value at POR reset

1999 Microchip Technology Inc.

Advanced Information DS41124A-page 23

Page 24

PIC16C745/765

4.2.2.3 INTCON REGISTER

The INTCON register is a readable and writable regis-

ter, which contains various enable and flag bits for the

TMR0 register overflow, RB Port change and external

RB0/INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt

condition occurs , regardless of the state of

its corresponding enable bit or the global

enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an

interrup t

.

REGISTER 4-3: INTERRUPT CONTROL REGISTER (INTCON: 10Bh, 18Bh)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-x

GIE PEIE T0IE INTE RBIE T0IF INTF RBIF

bit7 bit0

bit 7: GIE: Global Interrupt Enable bit

1 = Enables all un-masked interrupts

0 = Disables all interrupts

bit 6: PEIE: Peripheral Interrupt Enable bit

1 = Enables all un-masked peripheral interrupts

0 = Disables all peripheral interrupts

bit 5: T0IE: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 interrupt

0 = Disables the TMR0 interrupt

bit 4: INTE: RB0/INT External Interrupt Enable bit

1 = Enables the RB0/INT external interrupt

0 = Disables the RB0/INT external interrupt

bit 3: RBIE: RB Port Change Interrupt Enable bit

1 = Enables the RB port change interrupt

0 = Disables the RB port change interrupt

bit 2: T0IF: TMR0 Overflow Interrupt Flag bit

1 = TMR0 register has overflowed (must be cleared in software)

0 = TMR0 register did not overflow

bit 1: INTF: RB0/INT External Interrupt Flag bit

1 = The RB0/INT external interrupt occurred (must be cleared in software)

0 = The RB0/INT external interrupt did not occur

bit 0: RBIF: RB Port Change Interrupt Flag bit

1 = At least one of the RB<7:4> pins changed state (must be cleared in software)

0 = None of the RB<7:4> pins have changed state

R = Readable bit

W = Writable bit

U = Unimplemented bit,

-n = Value at POR reset

read as ‘0’

DS41124A-page 24 Advanced Information

1999 Microchip Technology Inc.

Page 25

PIC16C745/765

4.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the

peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to

enable any peripheral interrupt.

REGISTER 4-4: PERIPHERAL INTERRUPT ENABLE1 REGISTER (PIE1: 8Ch)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

(1)

PSPIE

bit7 bit0

bit 7: PSPIE

bit 6: ADIE: A/D Converter Interrupt Enable bit

bit 5: RCIE: USART Receive Interrupt Enable bit

bit 4: TXIE: USART Transmit Interrupt Enable bit

bit 3: USBIE: Universal Serial Bus Interrupt Enable bit

bit 2: CCP1IE: CCP1 Interrupt Enable bit

bit 1: TMR2IE: TMR2 to PR2 Match Interrupt Enable bit

bit 0: TMR1IE: TMR1 Overflow Interrupt Enable bit

ADIE RCIE TXIE USBIE CCP1IE TMR2IE TMR1IE

(1)

: Parallel Slave Port Read/Write Interrupt Enable bit

1 = Enables the PSP read/write interrupt

0 = Disables the PSP read/write interrupt

1 = Enables the A/D interrupt

0 = Disables the A/D interrupt

1 = Enables the USART receive interrupt

0 = Disables the USART receive interrupt

1 = Enables the USART transmit interrupt

0 = Disables the USART transmit interrupt

1 = Enables the USB interrupt

0 = Disables the USB interrupt

1 = Enables the CCP1 interrupt

0 = Disables the CCP1 interrupt

1 = Enables the TMR2 to PR2 match interrupt

0 = Disables the TMR2 to PR2 match interrupt

1 = Enables the TMR1 overflow interrupt

0 = Disables the TMR1 overflow interrupt

R = Readable bit

W = Writable bit

U = Unimplemented bit,

-n = Value at POR reset

read as ‘0’

Note 1: PIC16C745 device does not have a parallel slave port implemented; always maintain this bit clear.

1999 Microchip Technology Inc.

Advanced Information DS41124A-page 25

Page 26

PIC16C745/765

4.2.2.5 PIR1 REGISTER

This register contains the individual flag bits for the

peripheral interrupts.

Note: Interrupt flag bits are set when an interrupt

condition occurs , regardless of the state of

its corresponding enable bit or the global

enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an

interrupt.

REGISTER 4-5: PERIPHERAL INTERRUPT REGISTER1 (PIR1: 0Ch)

R/W-0 R/W-0 R-0 R-0 R/W-0 R/W-0 R/W-0 R/W-0

(1)

PSPIF

bit7 bit0

ADIF

bit 7: PSPIF

1 = A read or a write operation has taken pl ace (must be cleared in software)

0 = No read or write has occurred

bit 6: ADIF: A/D Converter Interrupt Flag bit

1 = An A/D conversion completed (must be cleared in software)

0 = The A/D conversion is not complet e

bit 5: RCIF: USART Receive Interrupt Flag bit

1 = The USART receive buffer is full (clear by reading RCREG)

0 = The USART receive buffer is empty

bit 4: TXIF: USART Transmit Interrupt Flag bit

1 = The USART transmit buffer is empty (clear by writing to TXREG)

0 = The USART transmit buffer is full

bit 3: USBIF: Universal Serial Bus (USB) Interrupt Flag

1 = A USB interrupt condition has oc cu rred. The specific cause can be found by examining the contents

of the UIR and UIE registers.

0 = No USB interrupt conditions that are enabled have occurred.

bit 2: CCP1IF: CCP1 Interrupt Flag bit

Capture Mode

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

Compare Mode

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

PWM Mode

Unused in this mode

bit 1: TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

1 = TMR2 to PR2 match occurred (must be cleared in software)

0 = No TMR2 to PR2 match occurred

bit 0: TMR1IF: TMR1 Overflow Interrupt Flag bit

1 = TMR1 register overflowed (must be cleared in software)

0 = TMR1 register did not overflow

RCIF TXIF USBIF CCP1IF TMR 2IF TMR1IF

(1)

: Parallel Slave Port Read/Write Interrupt Flag bit

R = Readable bit

W = Writable bit

U = Unimplemented bit,

read as ‘0’

-n = Value at POR reset

Note 1: PIC16C745 device does not hav e a par al lel sla v e port implement ed. This bit locati on is res erved on thi s

device. Always maintain this bit clear.

DS41124A-page 26 Advanced Information

1999 Microchip Technology Inc.

Page 27

PIC16C745/765

4.2.2.6 PIE2 REGISTER

This register contains the individual enable bit for the

CCP2 peripheral interrupt.

REGISTER 4-6: PERIPHERAL INTERRUPT ENABLE 2 REGISTER (PIE2: 8Dh)

U-0 U-0 U-0 U-0 U-0 U-0 U-0 R/W-0

— — — — — — — CCP2IE

bit7 bit0

bit 7-1: Unimplemented: Read as ’0’

bit 0: CCP2IE: CCP2 Interrupt Enable bit

1 = Enables the CCP2 interrupt

0 = Disables the CCP2 interrupt

4.2.2.7 PIR2 REGISTER

This register contains the CCP2 interrupt flag bit. .

R = Readable bit

W = Writable bit

U = Unimplemented bit,

-n = Value at POR reset

read as ‘0’

Note: Interrupt flag bits are set when an in terrupt

condition occur s , rega rdle ss of the state of

its corresponding enable bit or the global

enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an

interrupt.

REGISTER 4-7: PERIPHERAL INTERRUPT REGISTER 2 (PIR2: 0Dh)

U-0 U-0 U-0 U-0 U-0 U-0 U-0 R/W-0

— — — — — — — CCP2IF

bit7 bit0

bit 7-1: Unimplemented: Read as ’0’

bit 0: CCP2IF: CCP2 Interrupt Flag bit

Capture Mode

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

Compare Mode

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

R = Readable bit

W = Writable bit

U = Unimplemented bit,

read as ‘0’

-n = Value at POR reset

PWM Mode

Unused

1999 Microchip Technology Inc.

Advanced Information DS41124A-page 27

Page 28

PIC16C745/765

4.2.2.8 PCON REGISTER

The Po wer Control (PCO N) register contains flag bits to

allow diff erentia tion be tween a Power-on Reset (POR),

a Brown-out Reset (BOR), a Watch-dog Reset (WDT)

and an external MCLR

Reset.

Note: BOR is unknown on POR. It must be set by

the user and checked on subsequent

resets to se e if BOR

brown-out ha s occurred. The BO R

bit is a “don't care” and is not predictable if

the brown-out ci rcuit i s disabled (by clea ring the BODEN bit in the configuration

word).

REGISTER 4-8: POWER CONTROL REGISTER REGSTER (PCON: 8Eh)

U-0 U-0 U-0 U-0 U-0 U-0 R/W-0 R/W-q

— — — — — —

bit7 bit0

bit 7-2: Unimplemented: Read as ’0’

bit 1: POR

bit 0: BO

: Power-on Reset Status bit

1 = No power-on reset occurred

0 = A power-on reset occurred (must be set in software after a power-on reset occurs)

R: Brown-out Reset Status bit

1 = No brown-out reset occurred

0 = A brown-out reset occurred (must be set in software after a brown-out reset occurs)

POR

BOR

is clear, indicating a

status

R = Readable bit

W = Writable bit

U = Unimplemented bit,

read as ‘0’

-n = Value at POR reset

DS41124A-page 28 Advanced Information

1999 Microchip Technology Inc.

Page 29

PIC16C745/765

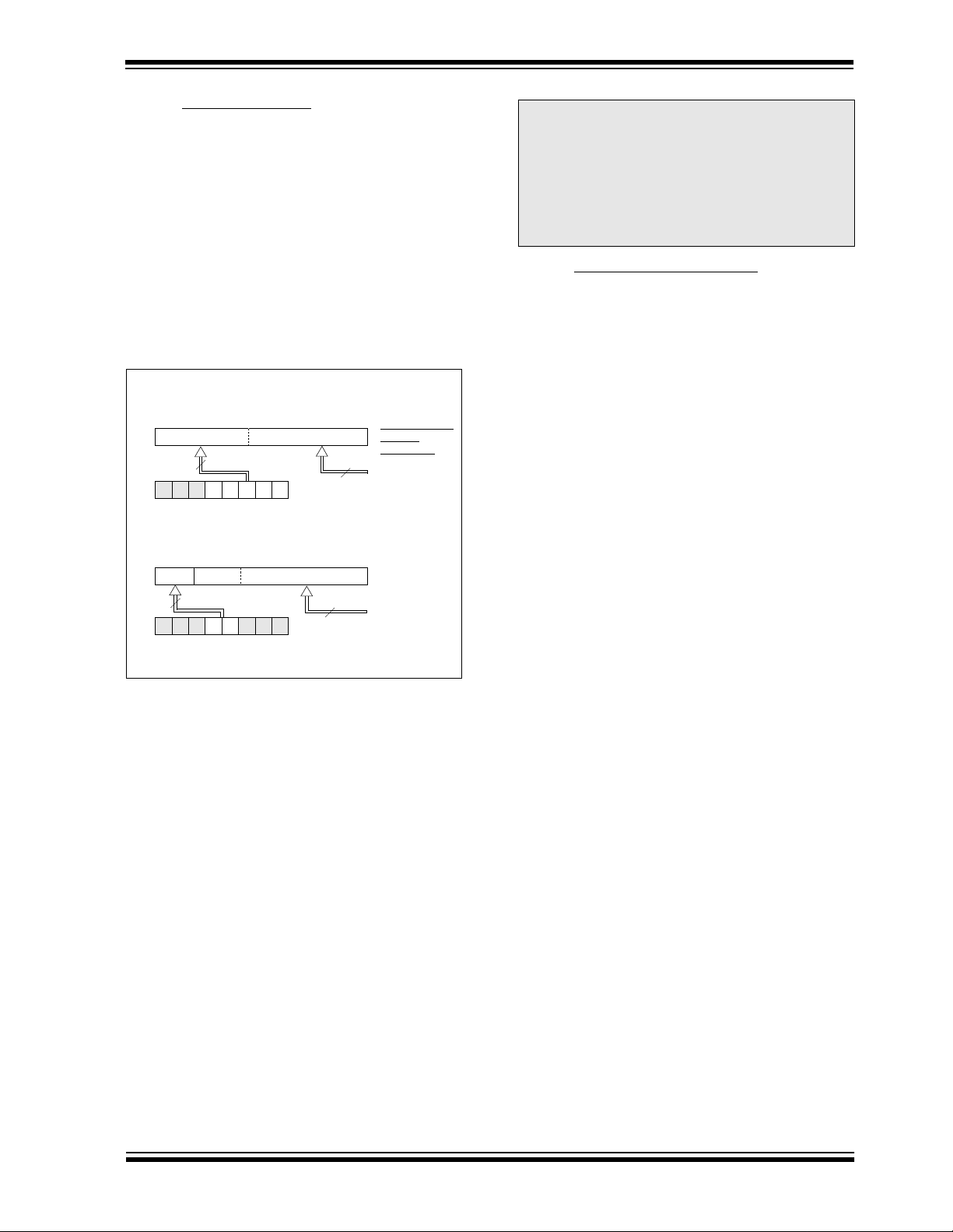

4.3 PCL and PCLATH

The program coun ter (PC) is 13-bits wide . The low b yte

comes from the PCL register, which is a readable and

writable register. The upper bits (PC<12:8>) are not

readable, but are indirectly writable through the

PCLATH register. On any reset, the upper bits o f the PC

will be cleared. Figure4-3 shows the two situations for

the loading of the PC. The upper example in the figure

shows how the PC is loaded on a write to PCL

(PCLATH<4:0> → PCH). The lower example in the fig-

ure shows ho w the PC is loaded during a CALL or GOTO

instruction (PCLATH<4:3> → PCH).

FIGURE 4-3: LOADING OF PC IN

DIFFERENT SITUATIONS

PCH PCL

12 8 7 0

PC

PCLATH<4:0>

5

PCLATH

PCH PCL

12 11 10 0

PC

2

87

PCLATH<4:3>

PCLATH

11

4.3.1 COMPUTED GOTO A computed GOTO is accomplished by adding an offset

to the progra m counter (ADDWF PCL). When doing a

table read using a computed GOTO method, care

should be exercised if the tabl e loc ati on crosses a PCL

memory boundary (each 256 by te block). Refer to the

application note

“Implementing a Table Read"

4.3.2 STACK

8

Instruction with

PCL as

Destination

ALU

GOTO,CALL

Opcode <10:0>

(AN556).

Note 1: There are no status bits to indicate stack

overflow or stack underflow conditions.

2: There are no instructions/mnemonics

called PUSH or POP. These are acti ons that

occur from the execution of the CALL,

RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt

address.

4.4 Program Memory Paging

PIC16CXX devices are capab le of addressing a co ntinuous 8K word bl ock of p rogram me mory . The CALL and

GOTO instructions provide only 11 bits of address to

allow branching within any 2K program memory page.

When doing a CALL or GOTO instruction, the upper 2

bits of the address are provided by PCLATH<4:3>.

When doing a CALL or GOTO instructio n, th e u ser m ust

ensure that the page select bits are programmed so

that the desired pro gram memory page is addressed. If

a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack.

Therefore , manipulation of the PC LA TH <4:3> bits is not

required for the return instructions (which POPs the

address from the stack).

Example 4-1 shows the calling of a subroutine in

page 1 of the program m emory . Th is ex ample assu mes

that PCLATH is saved and restored b y the interrupt service routine

(if interrupts are used).

EXAMPLE 4-1: CALL OF A SUBROUTINE IN

PAGE 1 FROM PAGE 0

ORG 0x500

BSF PCLATH,3 ;Select page 1 (800h-FFFh)

CALL SUB1_P1 ;Call subroutine in

: ;page 1 (800h-FFFh)

:

ORG 0x900 ;page 1 (800h-FFFh)

SUB1_P1

: ;called subroutine

: ;page 1 (800h-FFFh)

:

RETURN ;return to Call subroutine

;in page 0 (000h-7FFh)

The PIC16CXX f amily ha s an 8-le ve l deep x 13 -bit wide

hardware stack. T he stack space is not part of either

program or data space and the stack pointer is not

readable or writab le. The PC is PUSHed onto the stac k

when a CALL instruction is executed or an interrupt

causes a branch. The stack is POPed in the event of a

RETURN,RETLW or a RETFIE instruction execution.

PCLATH is not affected by a PUSH or POP operation.

The stack oper ates as a circular b uffer . This means that

after the stack has been PUSHed e ight ti mes , th e nin th

push overw rites th e value that was stored from the firs t

push. The tenth push overwrites the second push (and

so on).

1999 Microchip Technology Inc.

Advanced Information DS41124A-page 29

Page 30

PIC16C745/765

4.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a ph ysi cal register . Add ressing

the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually

accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly

(FSR = ’0’) will read 00h. Writing to the INDF register

indirectly results in a no-o per atio n (althou gh statu s bits

may be affected). An effectiv e 9-b it ad dress is o btaine d

by concatena tin g the 8 - bit FS R re gis ter an d the IRP bit

(STATUS<7>), as shown in Figure 4-4.

A simple program to clear RAM locations 20h-2Fh

using indirect addressing is shown in Example 4-2.

FIGURE 4-4: DIRECT/INDIRECT ADDRESSING

RP<1:0> 6

bank select location select

from opcode

0

00 01 10 11

00h

80h

EXAMPLE 4-2: INDIRECT ADDRESSING

movlw 0x20 ;initialize pointer

NEXT clrf INDF ;clear INDF register

CONTINUE

100h

180h

movwf FSR ;to RAM

incf FSR,F ;inc pointer

btfss FSR,4 ;all done?

goto NEXT ;no clear next

: ;yes continue

Indirect AddressingDirect Addressing

IRP FSR register

bank select

7

0

location select

Data

Memory

7Fh

FFh

17Fh

Bank 0 Bank 1 Bank 2 Bank 3

Note: For register file map detail see Figure 4-2.

1FFh

DS41124A-page 30 Advanced Information

1999 Microchip Technology Inc.

Page 31

PIC16C745/765

5.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an

alternate function for the peripheral features on the

device. In general, when a peripheral is enabled, that

pin may not be used as a general purpose I/O pin.

5.1 PORTA and TRISA Registers

PORTA is a 6-bit latch.

The RA4/T0CKI pin is a Schmitt Trigger input and an

open drain outp ut. All other RA port pins have T TL input

levels and full CMOS output drivers. All pins have data

direction bits (TRIS registers), which can configure

these pins as output or input.

Setting a TRISA registe r bit puts the cor responding output driver in a hi- imped ance m ode . Cle aring a bit in the

TRISA register puts the contents of the output latch on

the selected pin(s).

Reading the PORTA register reads the status of the

pins, whereas writing to it will write to the port latch. All

write operations are read-modify-write operations.

Therefore , a write to a port implies that the port pins are

read, the value is modified, and then written to the port

data latch.

Pin RA4 is multiplexed with the Timer0 module clock

input to become the RA4/T0CKI pin.

On the PIC16C745/765, PORTA pins are multiplexed

with analog inputs and analog V

tion of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control

Register1).

Note: On all resets, pins with analog and digital

functions are configured as analog inputs.

The TRISA register controls the direction of the RA

pins, even when they are being used as analog inputs.

The user must ensure the bits in the TRISA registe r are

maintained set when using them as analo g inputs.

EXAMPLE 5-1: INITIALIZING PORTA

(PIC16C745/765)

BCF STATUS, RP1 ;

BCF STATUS, RP0 ;

CLRF PORTA ; Initialize PORTA by

BSF STATUS, RP0 ; Select Bank 1

MOVLW 0x06 ; Configure all pins

MOVWF ADCON1 ; as digital inputs

MOVLW 0xCF ; Value used to

MOVWF TRISA ; Set RA<3:0> as inputs

REF input. The opera-

; clearing output

; data latches

; initialize data

; direction

; RA<5:4> as outputs

; TRISA<7:6> are always

; read as ’0’.

FIGURE 5-1: BLOCK DIAGRAM OF RA<3:0>

AND RA5 PINS

Data

Bus

WR

Port

WR

TRIS

RD PORT

To A/D Converter

CK

Data Latch

CK

TRIS Latch

QD

Q

QD

Q

RD TRIS

QD

EN

VDD

P

N

V

Analog

Input

Mode

VDD

I/O Pin

SS

Schmitt

Trigger

Input

Buffer

FIGURE 5-2: BLOCK DIAGRAM OF

RA4/T0CKI PIN

Data

Bus

WR

PORT

Data Latch

WR

TRIS

TRIS Latch

RD PORT

TMR0 Clock Input

CK

CK

RD TRIS

QD

Q

QD

Q

N

V

Schmitt

Trigger

Input

Buffer

QD

EN

EN

VDD

I/O pin

SS

1999 Microchip Technology Inc.

Advanced Information DS41124A-page 31

Page 32

PIC16C745/765

TABLE 5-1: PORTA FUNCTIONS

Name Function

RA0/AN0

RA1/AN1

RA2/AN2

RA3/AN3/V

RA4/T0CKI

RA5/AN4

Legend: OD = open drain, ST = Schmitt Trigger

REF

RA0 ST CMOS Bi-directional I/O

AN0 AN — A/D Input

RA1 ST CMOS Bi-directional I/O

AN1 AN — A/D Input

RA2 ST CMOS Bi-directional I/O

AN2 AN — A/D Input

RA3 ST CMOS Bi-directional I/O

AN3 AN — A/D Input

REF AN — A/D Positive Reference

V

RA4 ST OD Bi-directional I/O

T0CKI ST — Timer 0 Clock Input

RA5 ST Bi-directional I/O

AN4 AN — A/D Input

Input

Type

Output

Type

Description

TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

05h PORTA

— — RA5 RA4 RA3 RA2 RA1 RA0 --0x 0000 --0u 0000

Value on:

POR,

BOR

Value on all

other resets

85h TRISA

9Fh

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

ADCON1

— — PORTA Data Direction Register --11 1111 --11 1111

— — — — — PCFG2 PCFG1 PCFG0 ---- -000 ---- -000

DS41124A-page 32 Advanced Information

1999 Microchip Technology Inc.

Page 33

PIC16C745/765

5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a bit

in the TRISB register puts the corresponding output

driver in a hi-impedance input mode. Clearing a bit in

the TRISB register puts the cont ents of the out put latch

on the selected pin(s).

Each of the PORTB pins has a weak internal p ull -up. A

single control bit ca n turn on all the pull-u ps. This is performed by clea ring bi t RBPU

(OPTION_REG<7>). The

weak pull-up i s autom atically tur ned off when the po rt

pin is configured as an output. The pull-ups are disabled on a power-on reset.

FIGURE 5-3: BLOCK DIAGRAM OF RB<3:0>

PINS

V

TTL

Input

Buffer

EN

DD

weak

P

pull-up

RD Port

(1)

RBPU

Data Bus

WR Port

WR TRIS

RB0/INT

Note 1: To enable weak pull-ups, set the appropriate TRIS bit(s)

Data Latch

QD

CK

TRIS Latch

QD

CK

RD TRIS

RD Port

Schmitt Trigger

Buffer

and clear the RBPU

QD

bit (OPTION_REG<7>).

Four of PORTB’s pins, RB<7:4>, have an interrupt on

change feature. Only pins configured as inputs can

cause this interrupt to occ ur (i.e. any RB<7:4> pin configured as an output is excluded from the interrupt-onchange comparison). The input pins (of RB<7:4>) are

compared with the value latched on the last read of

PORTB. The “mismatch” outputs of RB<7:4> are