PIC12F510/16F506

数据手册

8/14 引脚 8 位闪存单片机

*8 位 8 引脚器件受 Microchip 低引脚数专利保护:美国专利号为 5,847,450。其他美国或他国专利可能已经颁发,或正在

接受审查。

2006 Microchip Technology Inc. 初稿 DS41268A_CN

请注意以下有关 Microchip 器件代码保护功能的要点:

•Microchip的产品均达到 Microchip 数据手册中所述的技术指标。

•Microchip确信:在正常使用的情况下, Microchip 系列产品是当今市场上同类产品中最安全的产品之一。

• 目前,仍存在着恶意、甚至是非法破坏代码保护功能的行为。就我们所知,所有这些行为都不是以 Microchip 数据手册中规定的

操作规范来使用 Microchip 产品的。这样做的人极可能侵犯了知识产权。

•Microchip愿与那些注重代码完整性的客户合作。

•Microchip或任何其他半导体厂商均无法保证其代码的安全性。代码保护并不意味着我们保证产品是 “牢不可破”的。

代码保护功能处于持续发展中。 Microchip 承诺将不断改进产品的代码保护功能。任何试图破坏 Microchip 代码保护功能的行为均可视

为违反了 《数字器件千年版权法案 (Digital Millennium Copyright Act)》。如果这种行为导致他人在未经授权的情况下,能访问您的

软件或其他受版权保护的成果,您有权依据该法案提起诉讼,从而制止这种行为。

提供本文档的中文版本仅为了便于理解。请勿忽视文档中包含

的英文部分,因为其中提供了有关 Microchip 产品性能和使用

情况的有用信息。Microchip Technology Inc. 及其分公司和相

关公司、各级主管与员工及事务代理机构对译文中可能存在的

任何差错不承担任何责任。建议参考 Microchip Technology

Inc. 的英文原版文档。

本出版物中所述的器件应用信息及其他类似内容仅为您提供便

利,它们可能由更新之信息所替代。确保应用符合技术规范,

是您自身应负的责任。Microchip 对这些信息不作任何明示或

暗示、书面或口头、法定或其他形式的声明或担保,包括但不

限于针对其使用情况、质量、性能、适销性或特定用途的适用

性的声明或担保。 Microchip 对因这些信息及使用这些信息而

引起的后果不承担任何责任。如果将 Microchip 器件用于生命

维持和 / 或生命安全应用,一切风险由买方自负。买方同意在

由此引发任何一切伤害、索赔、诉讼或费用时,会维护和保障

Microchip 免于承担法律责任,并加以赔偿。在 Microchip 知识

产权保护下,不得暗中或以其他方式转让任何许可证。

商标

Microchip 的名称和徽标组合、 Microchip 徽标、 Accuron、

dsPIC、 K

EELOQ、 microID、 MPLAB、 PIC、 PICmicro、

PICSTART、 PRO MATE、 PowerSmart、 rfPIC 和

SmartShunt 均为 Microchip Technology Inc. 在美国和其他国

家或地区的注册商标。

AmpLab、 FilterLab、 Migratable Memory、 MXDEV、

MXLAB、SEEVAL、SmartSensor 和 The Embedded Control

Solutions Company 均为 Microchip Technology Inc. 在美国的

注册商标。

Analog-for-the-Digital Age、 Application Maestro、

dsPICDEM、 dsPICDEM.net、 dsPICworks、 ECAN、

ECONOMONITOR、 FanSense、 FlexROM、 fuzzyLAB、

In-Circuit Serial Programming、 ICSP、 ICEPIC、 Linear

Active Thermistor、 MPASM、 MPLIB、 MPLINK、 MPSIM、

PICkit、 PICDEM、 PICDEM.net、 PICLAB、 PICtail、

PowerCal、 PowerInfo、 PowerMate、 PowerTool、 REAL

ICE、 rfLAB、 rfPICDEM、 Select Mode、 Smart Serial、

SmartTel、 Total Endurance、 UNI/O、 WiperLock 和 Zena

均为 Microchip Technology Inc. 在美国和其他国家或地区的

商标。

SQTP 是 Microchip Technology Inc. 在美国的服务标记。

在此提及的所有其他商标均为各持有公司所有。

© 2006, Microchip Technology Inc. 版权所有。

Microchip

州

10

位单片机、

性存储器和模拟产品方面的质量体系流程均符合

16949:2002

系也已通过了

位于美国亚利桑那州

Mountain View

月通过了

ISO/TS-16949:2002

KEELOQ

。此外,

ISO 9001:2000

的全球总部、设计中心和晶圆生产厂均于

®

跳码器件、串行

Microchip

Chandler和Tem pe

质量体系认证。公司在

EEPROM

在开发系统的设计和生产方面的质量体

认证。

及位于加利福尼亚

PICmicro

、单片机外设、非易失

ISO/TS-

2003

年

®

DS41268A_CN 第 ii 页 初稿 2006 Microchip Technology Inc.

8

PIC12F510/16F506

8/14 引脚 8 位闪存单片机

本数据手册所包含的器件:

• PIC16F506

• PIC12F510

高性能 RISC CPU:

• 仅需学习 33 条单字指令

• 除程序跳转指令为双周期指令外,其他指令都是单

周期指令。

• 指令宽度为 12 位

• 两级深硬件堆栈

• 数据和指令的直接、间接和相对寻址模式

• 数据总线宽度为 8 位

• 10 个特殊功能硬件寄存器 (PIC12F510)

• 13 个特殊功能硬件寄存器 (PIC16F506)

• 工作速度:

- 晶振频率为 DC - 8MHz(PIC12F510)

- 指令周期为 DC - 500 ns (PIC12F510)

- 晶振频率为 DC - 20 MHz (PIC16F506)

- 指令周期为 DC - 200 ns (PIC16F506)

单片机的特殊性能:

• 可选的 4 或 8MHz高精度内部振荡器:

- 出厂时精度校准为 ±1%

• 在线串行编程 (In-Circuit Serial

Programming™, ICSP™)

• 支持在线调试 (In-Circuit Debugging, ICD)

• 上电复位 (Power-on Reset, POR)

• 器件复位定时器 (Device Reset Timer, DRT)

- 在 INTOSC、 EXTRC 和 EC 模式下可提供短

暂的 DRT 延时 (1.125 ms,典型值)

- 在 HS、 XT 和 LP 模式下可提供 DRT 延时

(18 ms,典型值)

• 具有专用片上 RC 振荡器的看门狗定时器

(Watchdog Timer, WDT),能够可靠地工作

• 可编程代码保护

• 复用的 MCLR

• I/O 引脚具有可选的内部弱上拉

• 低功耗休眠模式

• 在引脚电平发生变化时从休眠模式唤醒

• 在比较器电平发生变化时从休眠模式唤醒

输入引脚

• 振荡器选项:

-INTOSC:4/8 MHz 高精度内部振荡器

- EXTRC:外部低成本 RC 振荡器

-XT:标准的晶振 / 谐振器

-HS:高速晶振 / 谐振器 (仅 PIC16F506)

-LP:低功耗低频晶振

-EC:高速外部时钟输入 (仅 PIC16F506)

• 模数 (A/D)转换器

-8位分辩率

- 四路输入通道 (一路通道专用于转换内部

0.6V 绝对参考电压)

• 用于直接驱动 LED 的高灌 / 拉电流

• 带有 8 位可编程预分频器的 8 位实时时钟 / 计数器

(TMR0)

低功耗特性 /CMOS 技术:

• 工作电流:

-4MHz、 2V时 < 350 µA

• 待机电流:

-2V时典型值为 100 nA

• 低功耗、高速闪存技术:

- 可经受 10 万次擦写

- 数据保存时间 > 40年

• 全静态设计

• 宽工作电压范围:2.0V 至 5.5V

• 宽温度范围:

- 工业级:-40°C 至 +85°C

- 扩展级:-40°C 至 +125°C

外设特性 (PIC12F510):

• 6 个 I/O 引脚:

-5个具有独立方向控制的 I/O 引脚

-1个只可输入的引脚

• 一个带有绝对参考电压的模拟比较器

外设特性 (PIC16F506):

• 12 个 I/O 引脚:

-11个具有独立方向控制的 I/O 引脚

-1个只可输入的引脚

• 2 个带有绝对参考电压和可编程参考电压的模拟比

较器

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 1 页

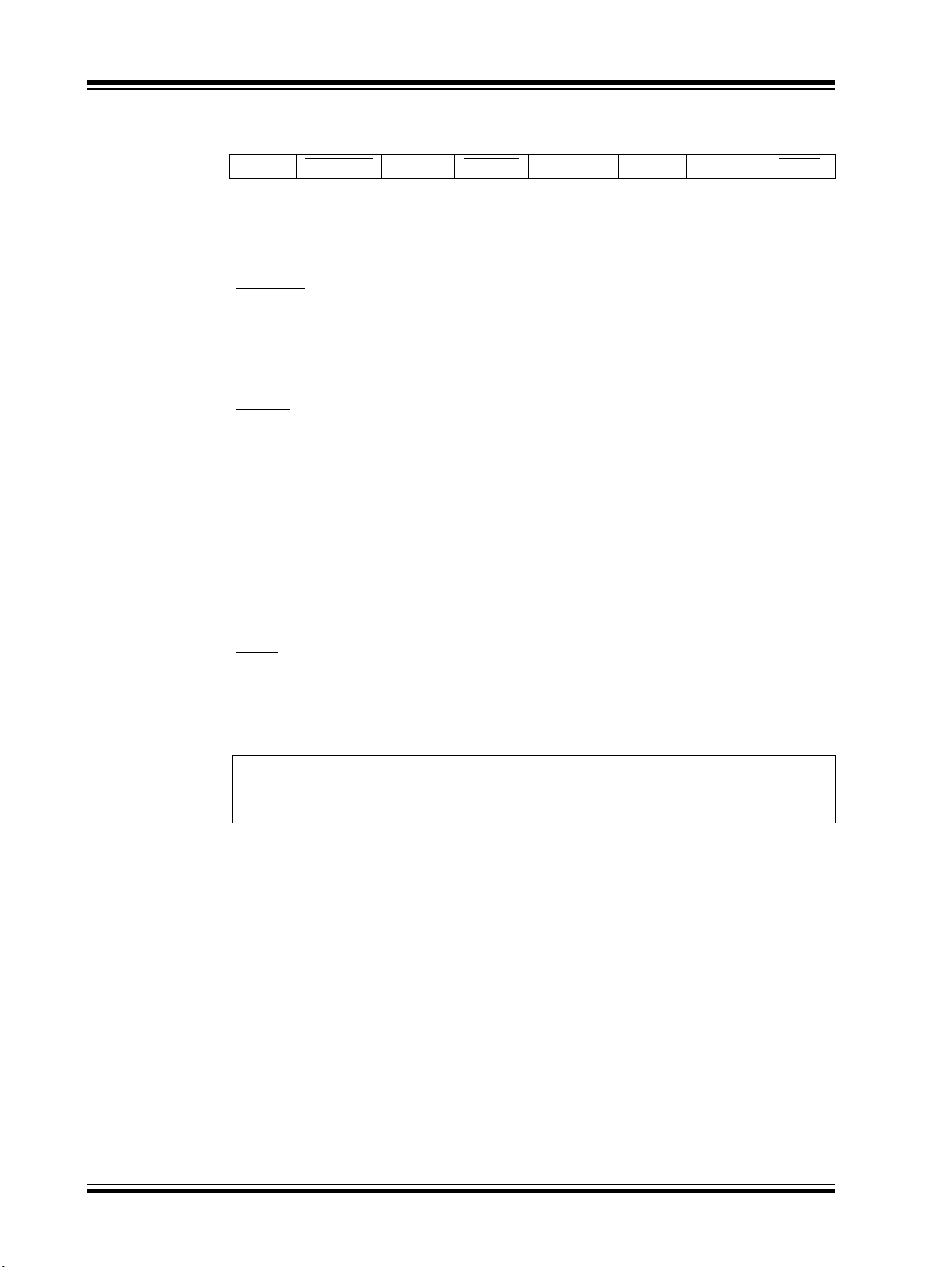

PIC12F510/16F506

器件

程序存储器 数据存储器

闪存 (字) SRAM (字节)

I/O

定时器

PIC16F506 1024 67 12 1

PIC12F510 1024 38 6 1

引脚图

PDIP、SOIC 和 TSSOP

VSS

RB0/AN0/C1IN+/ICSPDAT

RB1/AN1/C1IN-/ICSPCLK

RB2/AN2/C1OUT

RC0/C2IN+

RC1/C2IN-

REF

RC2/CV

VSS

GP0/AN0/C1IN+/ICSPDAT

GP1/AN1/C1IN-//ICSPCLK

GP2/AN2/T0CKI/C1OUT

PDIP、SOIC 和 MSOP

VDD

RB5/OSC1/CLKIN

RB4/OSC2/CLKOUT

RB3/MCLR

GP5/OSC1/CLKIN

GP3/MCLR

/VPP

RC5/T0CKI

RC4/C2OUT

RC3

VDD

GP4/OSC2

/VPP

1

2

3

4

5

6

7

1

2

3

4

PIC16F506

PIC12F510

14

13

12

11

10

9

8

8

7

6

5

8 位

DS41268A_CN 第 2 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

目录

1.0 一般说明 ....................................................................................................................................................................................... 5

2.0 PIC12F510/16F506 系列器件....................................................................................................................................................... 7

3.0 架构概述 ....................................................................................................................................................................................... 9

4.0 存储器构成 ................................................................................................................................................................................. 15

5.0 I/O 端口 ...................................................................................................................................................................................... 27

6.0 TMR0 模块和 TMR0 寄存器 ....................................................................................................................................................... 39

7.0 比较器模块 ................................................................................................................................................................................. 43

8.0 比较器参考电压模块 ................................................................................................................................................................... 49

9.0 模数 (A/D)转换器 ................................................................................................................................................................... 51

10.0 CPU 的特殊性能......................................................................................................................................................................... 55

11.0 指令集综述 ................................................................................................................................................................................. 71

12.0 开发支持 ..................................................................................................................................................................................... 79

13.0 电气规范 ..................................................................................................................................................................................... 83

14.0 直流和交流特性图表 ................................................................................................................................................................... 95

15.0 封装 ............................................................................................................................................................................................ 97

索引.................................................................................................................................................................................................... 107

Microchip 网站.................................................................................................................................................................................... 109

变更通知客户服务 .............................................................................................................................................................................. 109

客户支持............................................................................................................................................................................................. 109

读者反馈表 ......................................................................................................................................................................................... 110

产品标识体系 ..................................................................................................................................................................................... 111

致 客 户

我们旨在提供最佳文档供客户正确使用 Microchip 产品。为此,我们将不断改进出版物的内容和质量,使之更好地满足您的要求。

出版物的质量将随新文档及更新版本的推出而得到提升。

如果您对本出版物有任何问题和建议,请通过电子邮件联系我公司 TRC 经理,电子邮件地址为 CTRC@microchip.com,或将本

数据手册后附的 《读者反馈表》传真到 86-21-5407 5066。我们期待您的反馈。

最新数据手册

欲获得本数据手册的最新版本,请查询我公司的网站:

http://www.microchip.com

查看数据手册中任意一页下边角处的文献编号即可确定其版本。文献编号中数字串后的字母是版本号

的 A 版本。

勘误表

现有器件可能带有一份勘误表,描述了实际运行与数据手册中记载内容之间存在的细微差异以及建议的变通方法。一旦我们了解到

器件 / 文档存在某些差异时,就会发布勘误表。勘误表上将注明其所适用的硅片版本和文件版本。

欲了解某一器件是否存在勘误表,请通过以下方式之一查询:

• Microchip 网站 http://www.microchip.com

• 当地 Microchip 销售办事处 (见最后一页)

在联络销售办事处时,请说明您所使用的器件型号、硅片版本和数据手册版本 (包括文献编号)。

客户通知系统

欲及时获知 Microchip 产品的最新信息,请到我公司网站 www.microchip.com 上注册。

,例如:DS30000A是DS30000

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 3 页

PIC12F510/16F506

注:

DS41268A_CN 第 4 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

1.0 一般说明

PIC12F510/16F506 器件是 Microchip Technology 生产

的低成本、高性能、8 位全静态的基于闪存的 CMOS 单

片机。它们采用 RISC 架构,仅有 33 条单字 / 单周期指

令。除需要两个周期的程序跳转指令之外,所有指令都

是单周期指令。PIC12F510/16F506 器件的性能比同价

位的其他产品要高出很多。12 位宽的指令具有高度的对

称性,与同类的 8 位单片机相比其代码压缩了两倍。易

于使用和记忆的指令集,大大缩短了开发时间。

PIC12F510/16F506 产品具备可以降低系统成本和功耗

的特殊功能。上电复位(POR)和器件复位定时器

(DRT)使器件不再需要外部复位电路。有四种振荡器

配置可供选择 (PIC16F506 器件有六种) ,包括

INTOSC 内部振荡模式和节省功耗的 LP (低功耗)振

荡模式。节省功耗的休眠模式、看门狗定时器和代码保

护功能降低了系统的成本和功耗,提高了系统的可靠

性。

PIC12F510/16F506 使得用户可以充分利用 Microchip

在可编程闪存单片机市场上的价格优势,同时获得可灵

活编程的闪存产品。

支持 PIC12F510/16F506 产品的开发工具有:全功能的

宏汇编器、软件模拟器、在线仿真器、 C 编译器、低成

本的开发编程器和全功能编程器。IBM

能支持这些工具。

PC 和兼容机都

1.1 应用

PIC12F510/16F506 器件适合从个人护理设备和安防系

统到低功耗远程发送器 / 接收器等各种应用。闪存技术

使定制应用程序(发送器代码、设备设置和接收器频率

等)变得非常迅速和方便。小型封装适用于通孔或表面

贴装,使本单片机系列能适应各种空间有限的应用。低

成本、低功耗、高性能、易于使用和 I/O 灵活性使

PIC12F510/16F506 器件能够在您认为根本不能使用单

片机的场合也可以大显神通(如定时器功能、逻辑电路

和较大系统中的 PLD 以及协处理器应用)。

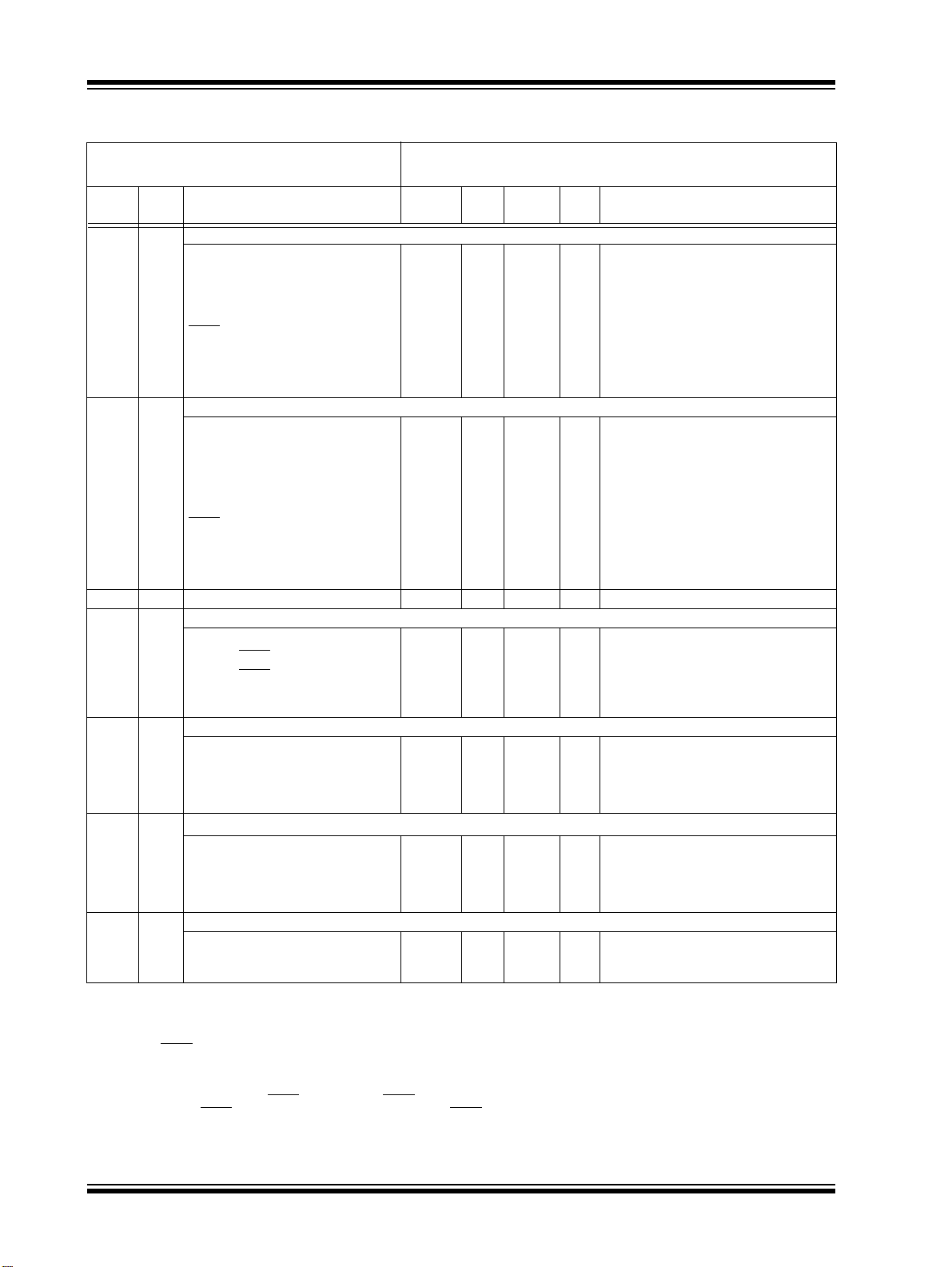

表 1-1: PIC12F510/16F506 器件

PIC16F506 PIC12F510

时钟 最大工作频率 (MHz)

存储器 闪存程序存储器

数据存储器 (字节)

外设 定时器模块

在引脚电平发生变化时从休眠模式唤醒 有 有

特性 I/O 引脚

只能输入的引脚

内部上拉 有 有

在线串行编程 有 有

指令数量

封装 14 引脚 PDIP、 SOIC 和

PIC12F510/16F506 器件具有上电复位、可选的看门狗定时器、可选的代码保护、高 I/O 电流能力和高精度内部振荡器。

PIC12F510/16F506 器件通过数据引脚 RB0/GP0 和时钟引脚 RB1/GP1 进行串行编程。

20 8

1024 1024

67 38

TMR0 TMR0

11 5

11

33 33

TSSOP

8 引脚 PDIP、 SOIC 和

MSOP

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 5 页

PIC12F510/16F506

注:

DS41268A_CN 第 6 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

2.0 PIC12F510/16F506 系列器件

器件提供不同的封装类型。根据应用和产品要求,可以

使用本章中的信息选择正确的器件。在下订单时,请使

用本数据手册后面的 PIC12F510/16F506 产品标识体系

来指定正确的器件编号。

2.1 快速批量编程 (QTP)器件

Microchip 为工厂生产订单提供快速批量变成 (Quick

Turn Programming , QTP)编程服务。此服务适用于

那些不想为中到大批量器件进行编程并且自有代码已稳

定的用户。此器件与闪存器件相同,只是所有闪存单元

和熔丝选项已在出产前预先编程了。批量产品交付前经

过了某些代码和原型校验。欲知更多详情,请与当地

的 Microchip 销售办事处联系。

2.2 带序列号的快速批量编程

(SQTP

Microchip 提供这种独特的编程服务,可通过编程为每

个器件中一些用户定义的单元指定不同的序列号。这些

序列号可以是随机的、伪随机或连续的。

串行编程使每个器件都具有一个惟一的编号,可作为登

录码、密码或 ID 编号。

SM

)器件

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 7 页

PIC12F510/16F506

注:

DS41268A_CN 第 8 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

3.0 架构概述

PIC12F510/16F506 系列的高性能可以归功于 RISC 单

片机中普遍采用的许多架构特点。 PIC12F510/16F506

采用了哈佛架构,在这种架构中,分别使用独立的总线

访问程序和数据存储器。与传统的程序和数据存储共用

同一条总线的冯·诺依曼架构相比,哈佛架构具有更加

优良的总线带宽。独立的程序和数据存储器使得指令宽

度不再是 8 位。由于指令操作码为 12 位宽,所以所有

指令都可以是单字指令。通过 12 位宽的程序存储器总

线可以在单周期内取一条 12 位的指令。两级流水线可

以使取指和执指同时进行。因此,除了程序跳转指令以

外,所有指令 (33 条)都可以在单周期 (20 MHz 时

为 200 ns, 4MHz时为 1 µs)内执行。

下面的表 3-1 列出了 PIC12F510/16F506 器件的程序存

储器 (闪存)和数据存储器 (RAM)。

表 3-1: PIC12F510/16F506 存储器

器件

PIC12F510

PIC16F506

PIC12F510/16F506 器件可以直接或间接地寻址它的文

件寄存器和数据存储器。所有特殊功能寄存器(Special

Function Register,SFR), 包 括 PC,都在数据存储器

中映射。 PIC12F510/16F506 器件具有高度正交 (对

称)的指令集,让它可以在任何寄存器上使用任何寻址

模式进行任何操作。此对称特性以及没有 “最佳状态”

让使用 PIC12F510/16F506 器件编程变得非常简单而高

效。此外,学习时间也大大的缩短了。

PIC12F510/16F506 器件包含一个 8 位 ALU 和工作寄存

器。ALU 是通用算术单元。它在工作寄存器中的数据和

其他任何寄存器文件之间进行算术和布尔运算。

程序 数据

1024 × 12 38 × 8

1024 × 12 67 × 8

存储器

ALU 为 8 位宽,并且能够执行加法、减法、移位和逻辑

运算。除非另外声明,算术运算一般都是以 2 的补码

(Two’s Complement)方式进行的。在具有两个操作数

的指令中,一个操作数通常是 W(工作)寄存器。其他

操作数可以是文件寄存器或者立即数常数。在只有一个

操作数的指令中,操作数可以是 W 寄存器,也可以是文

件寄存器。

W 寄存器是用于 ALU 操作的 8 位工作寄存器。它是不

可寻址的寄存器。

根据所执行的指令,ALU 可能影响状态(STATUS)寄

存器中进位 (C)、半进位 (DC)和零位 (Z)的值。

C 位和 DC 位在减法运算中可以分别作为借位

位。请参见 SUBWF 和 ADDWF 指令示例。

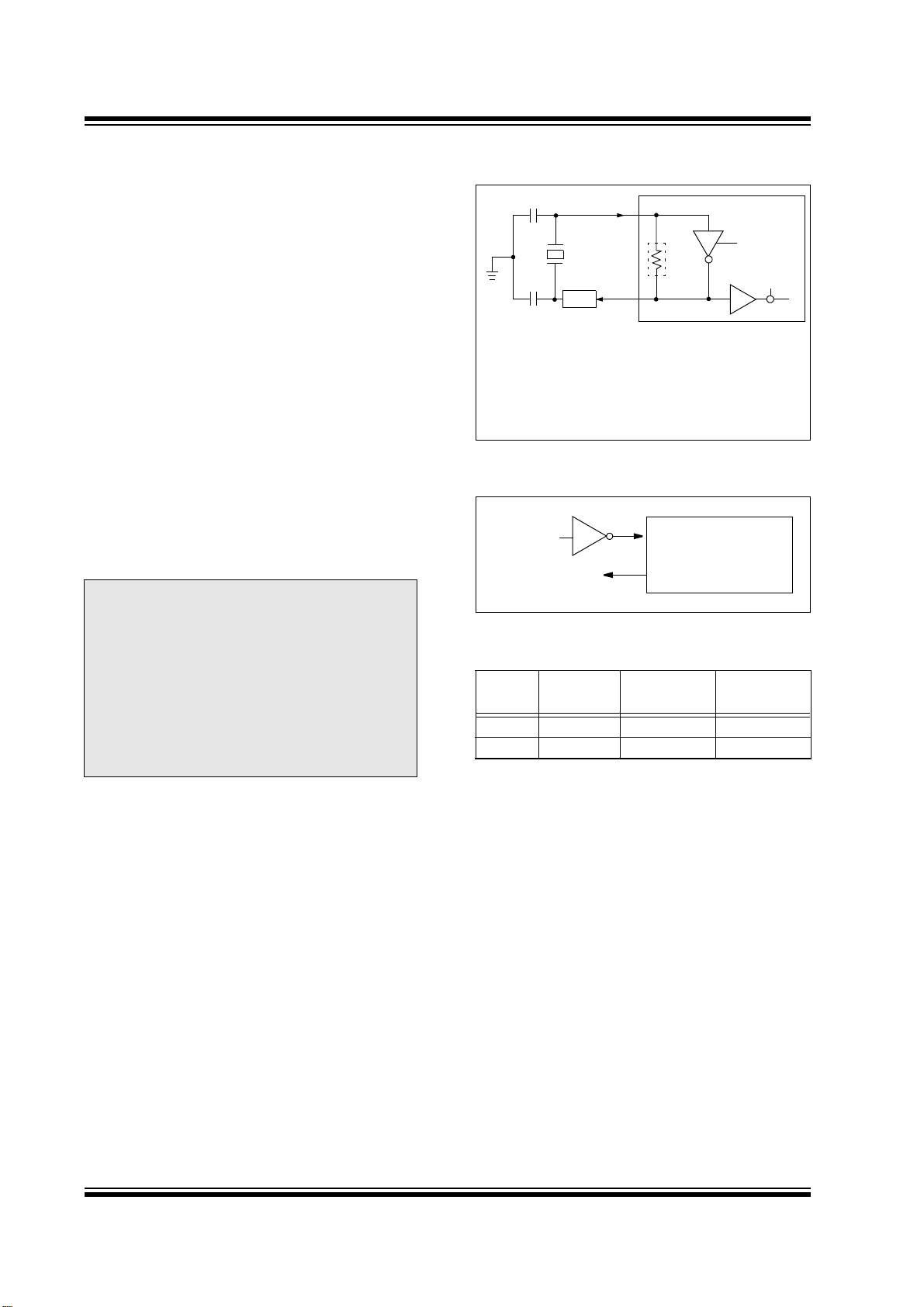

图 3-1 所示为 PIC12F510 的简化框图,表 3-2 给出了该

器件的引脚配置。图 3-2 所示为PIC16F506 的简化框图,

表 3-3 给出了该器件的引脚配置。

和半借位

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 9 页

PIC12F510/16F506

图 3-1: PIC12F510 系列框图

OSC2/OSC1/CLKIN

程序

总线

闪存

1K x 12

程序

存储器

12

指令寄存器

指令

译码和

控制

时序

发生

10-11

8

MCLR

程序计数器

堆栈 1

堆栈 2

直接寻址

器件复位

定时器

上电

复位

看门狗

定时器

内部RC

时钟

5

VDD,VSS

RAM 地址

3

8

数据总线

RAM

38 字节

文件

寄存器

地址 MUX

FSR 寄存器

ALU

W 寄存器

Timer0

9

间接寻址

5-7

状态寄存器

MUX

8

GPIO

比较器

VREF

8 位 ADC

GP0/ICSPDAT

GP1/ICSPCLK

GP2/T0CKI

GP3/MCLR/VPP

GP4/OSC2

GP5/OSC1/CLKIN

C1IN+

C1INC1OUT

AN0

AN1

AN2

DS41268A_CN 第 10 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

表 3-2: 引脚配置说明——PIC12F510

名称 I/O/P 类型 输入类型 输出类型 说明

GP0/AN0/C1IN+/ICSP-DAT GP0 TTL CMOS

AN0 AN

C1IN+ AN

ICSPDAT ST CMOS

GP1/AN1/C1IN-/ICSPCLK GP1 TTL CMOS

AN1 AN

C1IN- AN

ICSPCLK ST CMOS

GP2/AN2/T0CKI/C1OUT GP2 TTL CMOS

AN2 AN

T0CKI ST

C1OUT CMOS

GP3/MCLR/

GP4/OSC2 GP4 TTL CMOS

GP5/OSC1/CLKIN GP5 TTL CMOS

V

DD VDD P

V

SS VSS P

图注: I = 输入, O = 输出, I/O = 输入 / 输出, P = 电源,- = 未用, TTL = TTL 输入, ST = 施密特触发器输入,

VPP GP3 TTL

AN = 模拟电压

MCLR

V

PP

OSC2

OSC1 XTAL

CLKIN ST

ST

高压 - 编程电压输入。

-

- ADC 通道输入。

- 比较器输入。

- ADC 通道输入。

- 比较器输入。

- ADC 通道输入。

- Timer0 时钟输入。

- 比较器输出。

-标准TTL 输入。可由软件编程为内部弱上拉并在该引

- MCLR

XTAL

- XTAL 振荡器输入引脚。

- EXTRC 施密特触发器输入。

- 逻辑电路和 I/O 引脚的正电源。

- 逻辑电路和 I/O 引脚的参考地。

双向 I/O 引脚。可由软件编程为内部弱上拉并在该引

脚电平改变时从休眠模式唤醒。

在线串行编程数据引脚。

双向 I/O 引脚。可由软件编程为内部弱上拉并在该引

脚电平改变时从休眠模式唤醒。

在线串行编程时钟引脚。

双向 I/O 端口。

脚电平改变时从休眠模式唤醒。

输入——在该模式下始终使能弱上拉。

双向 I/O 端口。

XTAL 振荡器输出引脚。

双向 I/O 端口。

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 11 页

PIC12F510/16F506

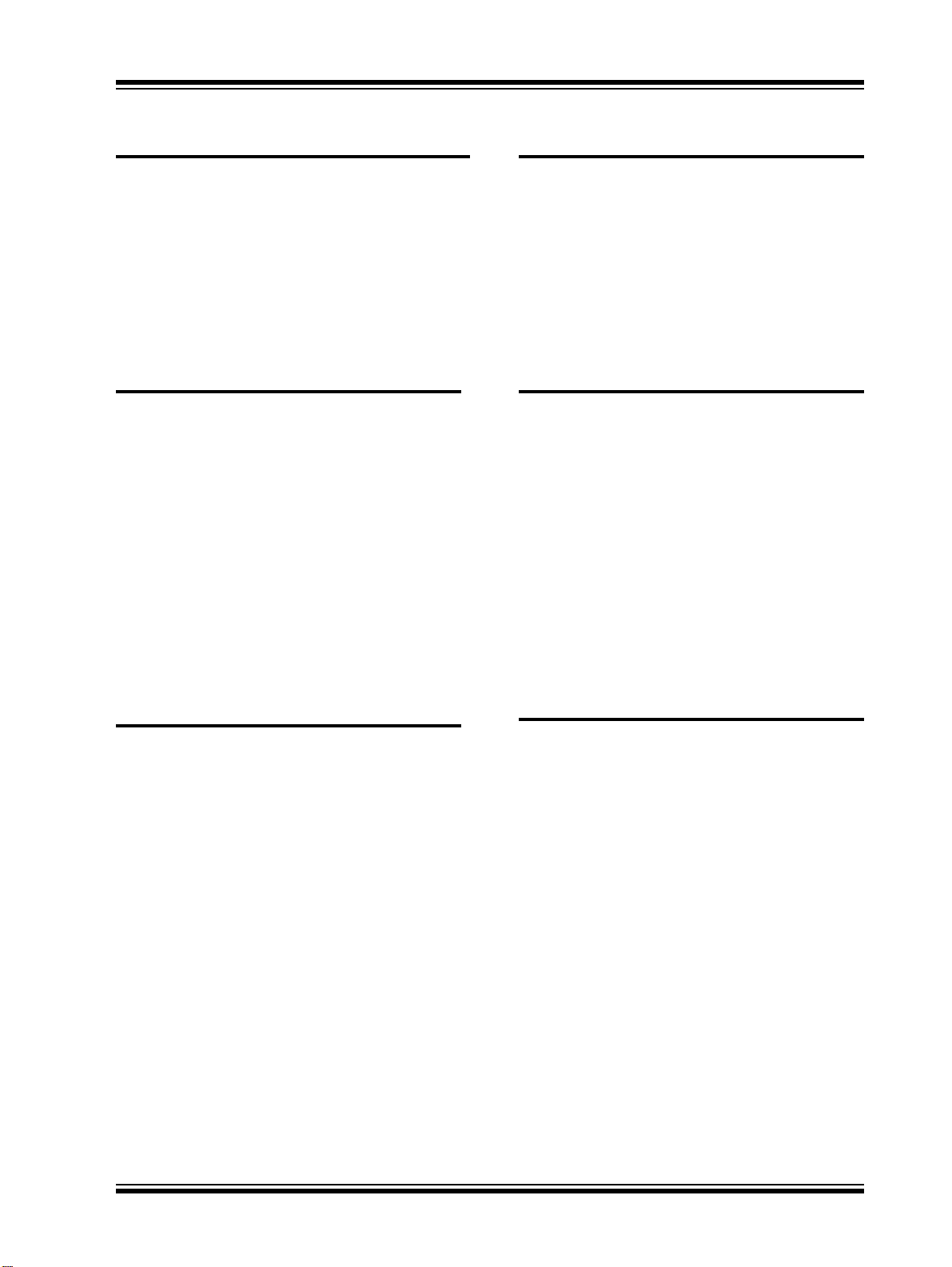

图 3-2: PIC16F506 系列框图

OSC1/CLKIN

OSC2/CLKOUT

程序

总线

闪存

1K x 12

程序

存储器

10

指令寄存器

指令

译码和

控制

时序

发生

10

8

MCLR

程序计数器

堆栈 1

堆栈 2

直接寻址

器件复位

定时器

上电

复位

看门狗

定时器

内部 RC

时钟

5

VDD,VSS

RAM 地址

3

8

数据总线

RAM

67 字节

文件

寄存器

地址 MUX

FSR 寄存器

状态寄存器

ALU

W 寄存器

Timer0

5-7

9

MUX

间接

寻址

8

PORTB

PORTC

比较器 1

比较器 2

VREF

CVREF

CVREF

8 位 ADC

RB0/ICSPDAT

RB1/ICSPCLK

RB2

RB3/MCLR/VPP

RB4/OSC2/CLKOUT

RB5/OSC1/CLKIN

RC0

RC1

RC2

RC3

RC4

RC5/T0CKI

C1IN+

C1INC1OUT

C2IN+

C2IN-

C2OUT

CVREF

AN0

AN1

AN2

VREF

DS41268A_CN 第 12 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

表 3-3: 引脚配置说明——PIC16F506

名称 功能 输入类型 输出类型 说明

RB0/AN0/C1IN+/ICSPDAT RB0 TTL CMOS

AN0 AN

C1IN+ AN

ICSPDAT ST CMOS

RB1/AN1/C1IN-/ICSPCLK RB1 TTL CMOS

AN1 AN

C1IN- AN

ICSPCLK ST

RB2/AN2/C1OUT RB2 TTL CMOS

AN2 AN

C1OUT

RB3/MCLR

RB4/OSC2/CLKOUT RB4 TTL CMOS

RB5/OSC1/CLKIN RB5 TTL CMOS

RC0/C2IN+ RC0 TTL CMOS

RC1/C2IN- RC1 TTL CMOS

RC2/CV

RC3 RC3 TTL CMOS

RC4/C2OUT RC4 TTL CMOS

RC5/T0CKI RC5 TTL CMOS

V

DD VDD P

V

SS VSS P

图注: I = 输入, O = 输出, I/O = 输入 / 输出, P = 电源,- = 未用, TTL = TTL 输入, ST = 施密特触发器输入,

/VPP RB3 TTL

MCLR

V

PP

OSC2

CLKOUT

OSC1 XTAL

CLKIN ST

C2IN+ AN

C2IN- AN

REF RC2 TTL CMOS

CV

REF

C2OUT

T0CKI ST

AN = 模拟电压

-

ST

高压 - 测试模式高压引脚。

-

-

-

-

- ADC 通道输入。

-比较器1 输入。

- ADC 通道输入。

-比较器1 输入。

- 在线串行编程数据引脚。

- ADC 通道输入。

CMOS

-标准TTL 输入。可由软件编程为内部弱上拉并在该引脚

- MCLR 输入——在该模式下始终使能弱上拉。

XTAL

CMOS

- XTAL 振荡器输入引脚。

- EXTRC/EC 施密特触发器输入。

-比较器2 输入。

-比较器2 输入。

AN

CMOS

- Timer0 施密特触发器输入引脚。

- 逻辑电路和 I/O 引脚的正电源。

- 逻辑电路和 I/O 引脚的参考地。

双向 I/O 端口。可由软件编程为内部弱上拉并在该引脚电

平改变时从休眠模式唤醒。

在线串行编程数据引脚。

双向 I/O 端口。可由软件编程为内部弱上拉并在该引脚电

平改变时从休眠模式唤醒。

双向 I/O 端口。

比较器 1 输出。

电平改变时从休眠模式唤醒。

双向 I/O 端口。可由软件编程为内部弱上拉并在该引脚电

平改变时从休眠模式唤醒。

XTAL 振荡器输出引脚。

EXTRC/INTOSC CLKOUT 引脚 (F

双向 I/O 端口。

双向 I/O 端口。

双向 I/O 端口。

双向 I/O 端口。

可编程参考电压输出。

双向 I/O 端口。

双向 I/O 端口。

比较器 2 输出。

双向 I/O 端口。

OSC/4)。

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 13 页

PIC12F510/16F506

3.1 时钟机制 / 指令周期

由OSC1/CLKIN引脚输入的时钟信号在器件内部被四分

频后,产生四个不重叠的正交时钟节拍,称为 Q1、Q2、

Q3 和 Q4。在每个 Q1 节拍,PC 递增;在 Q4 节拍从程

序存储器取指并将指令锁存到指令寄存器。指令的译码

和执行是在下一个 Q1 到 Q4 节拍中完成的。图 3-3 和

例 3-1 所示为时钟和指令执行流程。

图 3-3:时钟/ 指令周期

Q2 Q3 Q4

OSC1

Q1

Q2

Q3

Q4

PC

Q1

PC

Q1

3.2 指令流 / 流水线

一个指令周期由四个 Q 节拍组成 (Q1、 Q2、 Q3 和

Q4)。取指和执行指令是流水线操作的,因此取指需要

一个指令周期,而译码和执行指令则需要另一个指令周

期。但由于是流水线操作,所以每条指令的有效执行时

间都是一个指令周期。如果一条指令导致 PC 改变 (如

GOTO),则执行该指令需要两个周期 (例 3-1)。

取指周期由 Q1 节拍中 PC 加 1 开始。

在执行周期中,在 Q1 节拍将所取指令锁存到指令寄存

器(Instruction Register, IR)中。然后在 Q2、Q3 和

Q4 节拍中对该指令译码并执行指令。其中读数据存储

器 (读操作数)发生在 Q2 节拍,写操作发生在 Q4 节

拍 (写目标单元)。

Q2 Q3 Q4

PC + 1 PC + 2

Q1

Q2 Q3 Q4

内部

相位

时钟

取指(PC)

执行指令(PC – 2)

取指(PC + 1)

执行指令(PC)

取指(PC + 2)

执行指令(PC + 1)

例 3-1: 指令流水线

1. MOVLW 03H

2. MOVWF PORTB

3. CALL SUB_1

4. BSF PORTB, BIT1

除程序转移指令之外,所有指令都是单周期指令。由于程序转移指令将导致一条已取指令从流水线清除,需要重新

取指,然后执行指令,所以程序转移指令需要两个周期。

取指 1 执行 1

取指 2 执行 2

取指 3 执行 3

取指 4

清除

取指 SUB_1 执行 SUB_1

DS41268A_CN 第 14 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

4.0 存储器构成

PIC12F510/16F506 系列器件的存储器被分为程序存储

器和数据存储器。对于程序存储器大于 512 字节的器

件,使用分页机制。使用状态寄存器中的一位来访问程

序存储器页。对于数据存储器的文件寄存器多于 32 的

PIC12F510 和 PIC16F506 器件,使用分区机制。使用

文件选择寄存器 (File Select Register, FSR)访问数

据存储区。

4.1 PIC12F510/16F506 器件的程序存储 器构成

PIC12F510/16F506 器件具有一个 10 位程序计数器

(Program Counter,PC),此计数器可以寻址 2K x 12

位的程序存储空间。

只有前 1K x 12 (0000h-03FFh)单元是物理实现的

(见图 4-1)。访问这些边界以外的单元将导致返回到

1K x 12 空间。有效的复位向量为 0000h(见图 4-1)。

03FFh 单元包含内部时钟校准值。绝不能改写该值。

图 4-1: PIC12F510/16F506 器件的程序

存储器映射和堆栈

CALL,RETLW

空间

用户存储

PC<11:0>

1 级堆栈

2 级堆栈

复位向量

片上程序

存储器

512 字

片上程序

存储器

1024 字

10

(1)

0000H

01FFH

0200H

03FFh

0400h

7FFH

注 1: 地址 0000h 变为有效的复位向量。

03FFh 单元包含 MOVLW XX 内部时钟

校准值。

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 15 页

PIC12F510/16F506

4.2 数据存储器构成

数据存储器由寄存器或 RAM 字节组成。因此,器件的

数据存储器是由其文件寄存器指定的。文件寄存器被分

为两个功能组:特殊功能寄存器 (SFR)和通用寄存器

(General Purpose Registers, GPR)。

特殊功能寄存器包括 TMR0 寄存器、程序计数器

(PCL)、状态寄存器、I/O 寄存器(端口)和文件选择

寄存器 (FSR)。此外,特殊功能寄存器还被用于控制

I/O 端口配置和预分频比选择。

通用寄存器被用于存储数据和对指令命令的控制信息。

对于 PIC12F510 器件,文件寄存器由 10 个特殊功能寄

存器、6 个通用寄存器和 32 个可通过分区寻址的通用寄

存器组成 (见图 4-5)。

对于 PIC16F506 器件,文件寄存器由 13 个特殊功能寄

存器、3 个通用寄存器和 64 个可通过分区寻址的通用寄

存器组成 (见图 4-6)。

4.2.1 通用文件寄存器

通用文件寄存器可以被直接寻址,也可以通过文件选择

寄存器 (FSR)间接寻址。请参见第 4.8 节“间接数据

寻址:INDF 和 FSR 寄存器”。

图 4-2: PIC12F510 文件寄存器映射

FSR<5> 0 1

寄存器地址

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Fh

10h

1Fh

注 1: 不是物理寄存器。

(1)

INDF

20h

TMR0

PCL

STATUS

FSR

地址映射返回

到Bank 0 中的

地址。

OSCCAL

GPIO

CM1CON0

ADCON0

ADRES

通用

寄存器

2Fh

30h

通用

寄存器

通用

寄存器

3Fh

Bank 0 Bank 1

图 4-3: PIC16F506 文件寄存器映射

FSR<6:5> 00 01 10 11

寄存器地址

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

0Dh

0Fh

10h

1Fh

注 1: 不是物理寄存器。

(1)

INDF

TMR0

PCL

STATUS

FSR

OSCCAL

PORTB

PORTC

CM1CON0

ADCON0

ADRES

CM2CON0

VRCON

20h

通用

寄存器

2Fh 4Fh 6Fh

通用

寄存器

Bank 0 Bank 1 Bank 2 Bank 3

30h

3Fh

通用

寄存器

40h

地址映射返回到 Bank 0 中

的地址。

50h

通用

寄存器

5Fh

60h

70h

7Fh

通用

寄存器

DS41268A_CN 第 16 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

4.2.2 特殊功能寄存器

特殊功能寄存器 (SFR)由 CPU 和外设使用,用于控

制器件的操作 (见表 4-1)。

特殊功能寄存器可分为两类。与内核功能有关的特殊功

能寄存器将在本节讲述。而另一类与外设功能操作有关

的特殊功能寄存器将在相应的外设功能模块章节中讲

述。

表 4-1: 特殊功能寄存器汇总——PIC12F510

地址 名称

N/A TRIS

N/A OPTION

00h INDF

01h TMR0

(1)

02h

03h STATUS GPWUF CWUF PA0 TO PD ZDCC0001 1xxx

04h FSR

05h OSCCAL CAL6 CAL5 CAL4 CAL3 CAL2 CAL1 CAL0

06h GPIO

07h CM1CON0 C1OUT C1OUTEN C1POL C1T0CS C1ON C1NREF C1PREF C1WU 1111 1111

08h ADCON0 ANS1 ANS0 ADCS1 ADCS0 CHS1 CHS0 GO/DONE ADON 1111 1100

09h ADRES

图注: x = 未知, u = 不变,- = 未用 (读为 0)(如果适用)。阴影单元 = 未实现或未用。

注 1: 程序计数器的最高字节是不可直接访问的。欲知关于如何访问这些位的说明,请参见第 4.4 节 “选项寄存器”。

PCL

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

I/O 控制寄存器 (TRISGPIO)

包含配置 Timer 0 和 Tim er0/WDT 预分频器的控制位

使用 FSR 的内容寻址数据存储器 (非物理寄存器)

Timer0 模块寄存器

PC 的低 8 位

间接数据存储器地址指针

- -

ADC 转换结果

GP5 GP4 GP3 GP2 GP1 GP0 --xx xxxx

-

上电复位

时的值

--11 1111

1111 1111

xxxx xxxx

xxxx xxxx

1111 1111

110x xxxx

1111 111-

xxxx xxxx

表 4-2: 特殊功能寄存器汇总——PIC16F506

地址 名称

N/A TRIS

N/A OPTION

00h INDF

01h TMR0

(1)

02h

03h STATUS RBWUF CWUF PA0 TO

04h FSR

05h OSCCAL CAL6 CAL5 CAL4 CAL3 CAL2 CAL1 CAL0

06h PORTB

07h PORTC

08h CM1CON0 C1OUT C1OUTEN C1POL C1T0CS C1ON C1NREF C1PREF C1WU 1111 1111

09h ADCON0 ANS1 ANS0 ADCS1 ADCS0 CHS1 CHS0 GO/DONE ADON 1111 1100

0Ah ADRES

0Bh CM2CON0 C2OUT C2OUTEN C2POL C2PREF2 C2ON C2NREF C2PREF1 C2WU 1111 1111

0Ch VRCON VREN VROE VRR

图注: x = 未知, u = 不变,- = 未用 (读为 0)(如果适用)。阴影单元 = 未实现或未用。

注 1: 程序计数器的最高字节是不可直接访问的。 欲知关于如何访问这些位的说明,请参见第 4.4 节 “选项寄存器”。

PCL

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

I/O 控制寄存器 (TRISB 和 TRISC)

包含配置 Timer0 和 Timer0/WD T 预分频器的控制位

使用 FSR 的内容寻址数据存储器 (非物理寄存器)

Time r0 模块寄存器

PC 的低 8 位

PD ZDCC0001 1xxx

间接数据存储器地址指针

- -

- -

ADC 转换结果

RB5 RB4 RB3 RB2 RB1 RB0 --xx xxxx

RC5 RC4 RC3 RC2 RC1 RC0 --xx xxxx

-

VR3 VR2 VR1 VR0 001- 1111

-

上电复位

时的值

--11 1111

1111 1111

xxxx xxxx

xxxx xxxx

1111 1111

100x xxxx

1111 111-

xxxx xxxx

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 17 页

PIC12F510/16F506

4.3 状态寄存器

例如,CLRF STATUS 会将状态寄存器的高 3 位清零且

将 Z 位置 1。这会使状态寄存器的值为 000u u1uu(其

该寄存器包含 ALU 的数学运算状态、复位状态和页预选

择位。

和其他寄存器一样,状态寄存器可以作为任何指令的目

标寄存器。如果将该寄存器作为一条影响 Z、 DC 或 C

位的指令的目标寄存器,那么将禁止对这 3 位执行写操

中 u = 不变)。

因此,建议只使用 BCF、 BSF 和 MOVWF 指令来改变

STATUS 寄存器的值。这些指令不会影响状态寄存器的

Z、 DC 或 C 位。对于其他影响状态位的指令,请参见

第 11.0 节 “指令集综述”。

作。根据器件逻辑,这些位会被置 1 或清零。此外,TO

和 PD 位是不可写的。所以当执行一条把状态寄存器作

为目标寄存器的指令后,结果可能和预想的不同。

寄存器 4-1: 状态寄存器 (地址:03h)( PIC12F510)

R/W-0 R/W-0 R/W-0 R-1 R-1 R/W-X R/W-X R/W-X

GPWUF CWUF PA0 TO

bit 7 bit 0

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

GPWUF:GPIO 复位位

1 = 由于引脚电平变化从休眠唤醒的复位

0 = 上电或其他复位之后

CWUF:比较器复位位

1 = 由于比较器电平变化从休眠唤醒的复位

0 = 上电或其他复位之后

PA0 :程序页选择位

1 = 第 1 页(200h-3FFh)

0 = 第 0 页(000h-1FFh)

每页 512 个字节。

建议在不使用 PA0 位作为程序页预选择位的器件中也不要使用该位作为通用读 / 写位,因为这样可能会影

响与未来产品的向上兼容性。

TO

:超时位

1 = 在上电或执行 CLRWDT 或 SLEEP 指令后

0 = 发生了 WDT 超时

PD

:掉电位

1 = 在上电或执行 CLRWDT 指令后

0 = 执行 SLEEP 指令

Z:结果为 0 位

1 = 算术运算或逻辑运算结果为零

0 = 算术运算或逻辑运算结果不为零

DC:半进位 / 借

ADDWF:

1 = 发生了结果的第 4 个低位向高位的进位

0 = 未发生结果的第 4 个低位向高位的进位

SUBWF:

1 = 未发生结果的第 4 个低位向高位的借位

0 = 发生了结果的第 4 个低位向高位的借位

C:进位 / 借

ADDWF: SUBWF: RRF 或 RLF:

1 = 发生了进位 1 = 未发生借位 分别装载最低位和最高位

0 = 未发生进位 0 = 发生了借位

位位(对于ADDWF 和 SUBWF 指令)

位位(对于ADDWF、 SUBWF、 RRF 和 RLF 指令)

PD ZDC C

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 10 = 清零 x = 未知

DS41268A_CN 第 18 页 初稿 2006 Microchip Technology Inc.

寄存器 4-2: 状态寄存器 (地址:03h)( PIC16F506)

R/W-0 R/W-0 R/W-0 R-1 R-1 R/W-X R/W-X R/W-X

RBWUF CWUF PA0 TO

bit 7 bit 0

PIC12F510/16F506

PD ZDC C

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

RBWUF:PORTB 复位位

1 = 由于引脚电平变化从休眠唤醒的复位

0 = 上电或其他复位之后

CWUF:比较器复位位

1 = 由于比较器电平变化从休眠唤醒的复位

0 = 上电或其他复位之后

PA0 :程序页选择位

1 = 第 1 页(200h-3FFh)

0 = 第 0 页(000h-1FFh)

每页 512 个字节。

建议在不使用 PA0 位作为程序页预选择位的器件中也不要使用该位作为通用读 / 写位,因为这样可能会影

响与未来产品的向上兼容性。

TO

:超时位

1 = 在上电和执行 CLRWDT 或 SLEEP 指令后

0 = 发生了 WDT 超时

PD

:掉电位

1 = 在上电或指行 CLRWDT 指令后

0 = 执行 SLEEP 指令

Z:结果为 0 位

1 = 算术运算或逻辑运算结果为零

0 = 算术运算或逻辑运算结果不为零

DC:半进位 / 借位

ADDWF:

1 = 发生了结果的第 4 个低位向高位的进位

0 = 未发生结果的第 4 个低位向高位的进位

SUBWF:

1 = 未发生结果的第 4 个低位向高位的借位

0 = 发生了结果的第 4 个低位向高位的借位

C:进位 / 借位

ADDWF: SUBWF: RRF 或 RLF:

1 = 发生了进位 1 = 未发生借位 分别装载最低位和最高位

0 = 未发生进位 0 = 发生了借位

位(对于ADDWF 和 SUBWF 指令)

位(对于ADDWF、 SUBWF、 RRF 和 RLF 指令)

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 10 = 清零 x = 未知

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 19 页

PIC12F510/16F506

4.4 选项寄存器

选项 (OPTION)寄存器是一个 8 位宽的只读寄存器,

它包含各种配置 Timer0/WDT 预分频器和 Timer0 的控

制位。

通过执行 OPTION 指令,可将 W 寄存器的内容传送到

选项寄存器。复位会将 OPTION<7:0> 位置 1。

注 1: 当 TRIS 位清零 (=0)时,相应引脚的电

平变化唤醒和上拉功能都被禁止 (即,注

意 TRIS 将改写 GPPU/RBPU 和 GPWU/

选择控制位)。

RBWU

2: 当 T0CS 位置 1 时,它将改写 T0CKI 引脚

的 TRIS 功能。

寄存器 4-3: 选项寄存器 (PIC12F510)

W-1 W-1 W-1 W-1 W-1 W-1 W-1 W-1

GPWU GPPU T0CS T0SE PSA PS2 PS1 PS0

bit 7 bit 0

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2-0

GPWU:引脚电平变化唤醒使能位 (GP0、 GP1 和 GP3)

1 = 禁止

0 = 使能

GPPU:弱上拉使能位 (GP0、 GP1 和 GP3)

1 = 禁止

0 = 使能

T0CS:Timer0 时钟源选择位

1 = T0CKI 引脚电平的跳变沿

0 = 内部指令周期时钟 (CLKOUT)

T0SE:Timer0 时钟源边沿选择位

1 = 在 T0CKI 引脚电平从高电平变化到低电平时递增

0 = 在 T0CKI 引脚电平从低电平变化到高电平时递增

PSA:预分频器分配位

1 = 将预分频器分配给 WDT

0 = 将预分频器分配给 Timer 0

PS<2:0>:预分频比选择位

位值 Timer0 预分频比 WDT 预分频比

000

001

010

011

100

101

110

111

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

1 : 256

1 : 1

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 10 = 清零 x = 未知

DS41268A_CN 第 20 页 初稿 2006 Microchip Technology Inc.

寄存器 4-4: 选项寄存器 (PIC16F506)

W-1 W-1 W-1 W-1 W-1 W-1 W-1 W-1

RBWU RBPU T0CS T0SE PSA PS2 PS1 PS0

bit 7 bit 0

PIC12F510/16F506

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2-0

RBWU:引脚电平变化唤醒使能位 (RB0、 RB1、 RB3 和 RB4)

1 = 禁止

0 = 使能

RBPU:弱上拉使能位 (RB0、 RB1、 RB3 和 RB4)

1 = 禁止

0 = 允许

T0CS:Timer0 时钟源选择位

1 = T0CKI 引脚电平的跳变沿

0 = 内部指令周期时钟 (CLKOUT)

T0SE:Timer0 时钟源边沿选择位

1 = 在 T0CKI 引脚电平从高电平变化到低电平时递增

0 = 在 T0CKI 引脚电平从低电平变化到高电平时递增

PSA:预分频器分配位

1 = 将预分频器分配给 WDT

0 = 将预分频器分配给 Timer 0

PS<2:0>:预分频比选择位

Timer0 预分频比 WDT 预分频比

位值

000

001

010

011

100

101

110

111

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

1 : 256

1 : 1

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 10 = 清零 x = 未知

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 21 页

PIC12F510/16F506

4.5 OSCCAL 寄存器

振荡器校准(OSCCAL)寄存器被用来校准内部高精度

4/8 MHz 振荡器。它包含用于校准的 7 位。

注: 擦除器件同时也会擦除预编程的内部振荡

器内部校准值。必须在擦除该部分之前读

取校准值,这样以后才可以正确地重新编

程。

在移入了校准常数以后,请不要更改它。请参见第10.2.5

节“内部4/8 MHz RC 振荡器”。

寄存器 4-5: OSCCAL 寄存器 (地址:05h)

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 U-0

CAL6 CAL5 CAL4 CAL3 CAL2 CAL1 CAL0

bit 7 bit 0

-

bit 7-1

bit 0

CAL<6:0>:振荡器校准位

0111111 = 最大频率

•

•

•

0000001

0000000 = 中心频率

1111111

•

•

•

1000000 = 最小频率

未用:读为 0

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 10 = 清零 x = 未知

DS41268A_CN 第 22 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

4.6 程序计数器

当执行程序指令时,程序计数器 (PC)中将包含下一

条要被执行的程序指令的地址。除更改 PC 的指令外,

每执行一条指令, PC 值都会增 1。

对于 GOTO 指令,PC 的 bit 0 到 bit 8 由 GOTO 指令字提

供。程序计数器(PCL)被映射到 PC<7:0>。状态寄存

器的 bit 5 将页信息提供给 PC 的 bit 9 (见图 4-4)。

对于 CALL 指令或其他以 PCL 作为目标寄存器的指令,

PC 的 bit 0 到 bit 7 也是由指令字提供的。然而,PC<8>

不是由指令字提供,它始终保持清零 (见图 4-4)。

以 PCL 作为目标寄存器或修改 PCL 的指令包括 MOVWF

PC, ADDWF PC 和 BSF PC,5。

注: 由于 CALL 指令或任何修改 PCL 的指令会

将 PC<8> 清零,因此所有子程序调用或相

对跳转指令都被限制在任何程序存储器页

(512 字长)的前 256 个单元中。

图 4-4: 执行跳转指令时装载 PC 的过程

GOTO 指令

9

87 0

PC

70

状态寄存器

PCL

指令字

PA0

4.6.1 复位的影响

复位时 PC 被置为全 1,这意味着 PC 指向最后一页中

的最后一个单元 (即振荡器校准指令) 。执行 MOVLW

XX 指令后,PC 将计满返回到 00h 单元并开始执行用户

代码。

复位后状态寄存器页预选择位清零,这意味着预选择

第 0 页。

因此,复位时 GOTO 指令会自动使程序跳转到第 0 页直

到页预选择位的值被更改为止。

4.7 堆栈

PIC12F510/16F506 器件具有 2 级深、 12 位宽的硬件

PUSH/POP 堆栈。

执行 CALL 指令会将堆栈第一级单元中的内容压入

(PUSH)第二级单元中,然后将 PC 的当前值加 1 压入

堆栈的第一级。如果连续执行了两条以上 CALL 指令,

只会存储最近的两个返回地址。

执行 RETLW 指令会将堆栈第一级单元中的内容弹出

(POP)到 PC,然后将堆栈第二级单元中的内容复制到

第一级单元中。如果连续执行了两条以上 RETLW 指令,

将使用先前存储在堆栈第二级单元中的地址填充堆栈。

注 1: 可以使用在指令中指定的立即数装载 W 寄

存器。这对于在程序存储器中实现数据查

找表尤其有用。

2: 不存在指示堆栈上溢或下溢的状态位。

3: 不存在称为 PUSH 或 POP 的指令助记符。

这些是执行 CALL 和 RETLW 指令后出现的

情形。

CALL 或修改 PCL 的指令

87 0

9

PC

复位为 0

PA0

70

状态寄存器

PCL

指令字

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 23 页

PIC12F510/16F506

4.8 间接数据寻址:INDF 和 FSR 寄存器

INDF 寄存器不是物理寄存器。寻址 INDF 实际寻址的是

地址包含在 FSR 寄存器中的寄存器 (FSR 是一个

针

)。这就是间接寻址。

4.8.1 间接寻址示例

• 地址为 07 的文件寄存器包含值 10h

• 地址为 08 的文件寄存器包含值 0Ah

• 将值 07 载入 FSR 寄存器

• 读 INDF 寄存器将返回值 10h

• 将 FSR 寄存器的值增 1 (FSR = 08)

• 读 INDR 寄存器将返回值 0Ah

间接读 INDF (FSR = 0)将返回 00h,而间接写 INDF

寄存器将导致执行空操作 (虽然会影响状态位)。

例 4-1 给出了使用间接寻址将 RAM 单元 10h-1Fh 清零

的简单程序。

图 4-5:直接/ 间接寻址 (PIC12F510)

直接寻址

(FSR)

5

6

(操作码)

321

04

指

例 4-1: 使用间接寻址清零 RAM 的方法

MOVLW 0x10 ;initiali ze po i n t er

NEXT CLRF INDF ;cl e ar I N D F r e g i s te r

CONTINUE

FSR 是一个 5 位宽的寄存器。它由 INDF 寄存器配合使

用来间接寻址数据存储区。

FSR<4:0> 位用于选择数据存储器地址 00h 到 1Fh。

PIC16F506——使用 FSR<6:5>。在 Bank 0 至 Bank 3 之

间进行选择。 FSR<7> 未用,其读取值为 1。

PIC12F510——使用 FSR<5>。在 Bank 0 至 Bank 1

之间进行选择。 FSR<7:6> 未用,其读取值为 11。

MOVWF FSR ;to RAM

INCF FSR,F ;inc pointer

BTFSC FSR,4 ;all done?

GOTO NEXT ;NO, clear next

: ;YES, continue

:

间接寻址

(FSR)

5

3

6

4

1

2

0

存储区选择

注 1: 对于寄存器映射的细节,请参见图 4-2。

单元选择

数据

(1)

存储器

00 01

00h

0Fh

10h

1Fh 3Fh

Bank 0 Bank 1

地址映射返回到 Bank 0

中的地址。

存储区

选择

单元选择

DS41268A_CN 第 24 页 初稿 2006 Microchip Technology Inc.

图 4-6:直接/ 间接寻址 (PIC16F506)

PIC12F510/16F506

直接寻址

数据

存储器

(操作码)

(1)

00 01 10 11

00h

0Fh

10h

1Fh 3Fh 5Fh 7Fh

Bank 0 Bank 1 Bank 2 Bank 3

(FSR)

65 43210

存储区选择 单元选择

注 1: 对于寄存器映射的细节,请参见图 4-3。

地址映射返

回到 Bank 0

中的地址。

间接寻址

(FSR)

6 543210

存储区

单元选择

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 25 页

PIC12F510/16F506

注:

DS41268A_CN 第 26 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

5.0 I/O 端口

和任何其他寄存器一样, I/O 寄存器也可在程序控制下

进行读写。但是,读指令 (如 MOVF PORTB,W)将始

终读取 I/O 引脚,而与引脚是处于输入还是输出模式无

关。复位时,由于 I/O 控制器被置为全 1,因此所有 I/O

端口都被定义为输入 (输入为高阻态)。

注: 在 PIC12F510 器件中,I/O 端口 PORTB 被

称为 GPIO。在 PIC16F506 器件中,I/O 端

口 PORTB 被称为 PORTB。

5.1 PORTB/GPIO

PORTB/GPIO 是一个 8 位 I/O 寄存器。仅使用其低 6 位

(RB/GP<5:0>)。 bit 7 和 bit 6 未用,它们的读取值为

0。请注意 RB3/GP3 为只能输入的引脚。配置字寄存器

可以将某些 I/O 设置为备用功能。当用作备用功能时,

在读取端口期间,引脚将读为 0。 RB0/GP0、 RB1/

GP1、 RB3/GP3 和 RB4 引脚 (仅 PIC16F506 器件)

可以被配置为带有内部弱上拉,并且可在这些引脚的电

平发生变化时唤醒器件。电平变化时唤醒和弱上拉功能

并不可通过引脚选择。如果 RB3/GP3/MCLR

MCLR,其弱上拉是始终使能的,但该引脚的电平变化

时唤醒则是被禁止的。

5.2 PORTC (仅 PIC16F506 器件)

PORTC 是一个 8 位 I/O 寄存器。仅使用其低 6 位

(RC<5:0>)。 bit 7 和 bit 6 未用,它们的读取值为 0。

被配置为

5.4 I/O 接口

I/O 端口引脚的等效电路如图 5-1 所示。除只能输入的

RB3/GP3引脚外,所有端口引脚都可用于输入和输出操

作。对于输入操作,这些端口是不锁存的。所有输入数

据都必须位于引脚上,直到被输入指令 (如 MOVF

PORTB,W)读取为止。输出是锁存的并将保持不变,直

到输出锁存器被再次写入为止。要将端口引脚用作输

出,必须将 TRIS 寄存器中相应的方向控制位清零

(= 0)。要将端口引脚用作输入,必须将相应的 TRIS

位置 1。任何 I/O 引脚(除 RB3/GP3)都可被分别编程

为输入或输出。

图 5-1: PIC12F510/16F506 引脚驱动等效

数据

总线

数据

总线

接口

D

CK

电路

Q

Q

(2)

VDD

P

N

V

SS

VDD

(1)

I/O

引脚

VSS

5.3 TRIS 寄存器

通过执行 TRIS f 指令,可使用 W 寄存器的内容装载

输出驱动器控制寄存器。将 TRIS 寄存器的某位置 1,可

使相应的输出驱动器置于高阻模式。而将 TRIS 寄存器

的某位清零,会将输出数据锁存器的内容送入选定的引

脚并使能输出缓冲器。特殊的引脚为 RB3/GP3 引脚和

T0CKI 引脚,前者为只输入引脚,后者是由选项寄存器

控制的引脚。请参见寄存器 4-3。

注: 读端口读的是引脚而非输出数据锁存器。

也就是说,如果使能了某个引脚的输出驱

动器,并驱动为高电平,但外部系统将该

引脚保持为低电平,那么读相应端口将表

明该引脚为低电平。

注: TRIS 寄存器是 “只写”的,并且在复位时

被置为全 1 (禁止输出驱动器)。

复位

注 1: GP3/RB3 只有连接到 V

2: 关于引脚具体信息,请参见图 5-2 至图 5-13。

SS 的保护二极管。

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 27 页

PIC12F510/16F506

图 5-2: GP0/RB0 和 GP1/RB1 框图 图 5-3: GP3/RB3 框图 (带有弱上拉和

GPPU

RBPU

GPPU

RBPU

引脚电平变化时唤醒)

数据

总线

写

端口

W

寄存器

TRIS 'f'

QD

数据

锁存器

CK

CK

ADC 引脚使能

COMP 引脚使能

Q

QD

TRIS

锁存器

Q

复位

RD 端口

MCLRE

(1)

I/O 引脚

复位

I/O 引脚

数据总线

读端口

Q

不匹配

Q

D

D

CK

(1)

CK

不匹配

ADC

COMP

注 1: I/O 引脚上有连接到 VDD 和VSS 的保护二极管。

注 1: GP3/MCLR 引脚只有连接到 VSS 的保护二极

管。

DS41268A_CN 第 28 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

图 5-4: GP2 框图 图 5-5: RB2 框图

数据

总线

写

端口

W

寄存器

TRIS 'f'

数据

锁存器

CK

TRIS

锁存器

CK

复位

T0CS

C1T0CS

ADC 引脚使能

C1OUT

QD

Q

C1OUTEN

QD

Q

读端口

T0CKI

0

1

I/O 引脚

(1)

数据

总线

写

端口

W

寄存器

TRIS 'f'

C1OUT

数据

锁存器

CK

C1OUTEN

TRIS

锁存器

CK

复位

ADC 引脚使能

读端口

0

1

QD

Q

QD

Q

I/O 引脚

(1)

ADC

注 1: I/O 引脚上有连接到 VDD 和VSS 的保护二极管。

ADC

注 1: I/O 引脚上有连接到VDD 和VSS 的保护二极管。

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 29 页

PIC12F510/16F506

图 5-6: RB4 框图 图 5-7: GP4 框图

数据

总线

写

端口

W

寄存器

TRIS 'f'

RBPU

QD

数据

锁存器

TRIS

锁存器

复位

Q

OSC/4

F

QD

Q

CK

CK

INTOSC/RC/EC

数据

总线

写

0

1

(注 2)

I/O

引脚

(1)

端口

W

寄存器

TRIS 'f'

CK

CK

QD

数据

锁存器

Q

QD

TRIS

锁存器

Q

复位

INTOSC/RC

读端口

OSC1

振荡器

电路

I/O

引脚

(1)

读端口

OSC1

注 1: I/O 引脚上有连接到 VDD 和 VSS 的保护二极管。

2:当引脚由振荡器使用时,禁止输入模式。

振荡器

电路

注 1: I/O 引脚上有连接到 VDD 和VSS 的保护二极管。

DS41268A_CN 第 30 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

图 5-8: RB5/GP5 框图 图 5-9: RC0/RC1 框图

数据

总线

写

端口

W

寄存器

TRIS 'f'

数据

锁存器

CK

TRIS

锁存器

CK

复位

QD

Q

QD

Q

读端口

(注 2)

I/O

引脚

(1)

数据

总线

写

端口

W

寄存器

TRIS 'f'

QD

数据

锁存器

CK

CK

Q

QD

TRIS

锁存器

Q

复位

比较器引脚使能

I/O

引脚

(1)

OSC2

注 1: I/O引脚上有连接到 VDD 和 VSS 的保护二极管。

2: 当引脚由振荡器使用时,禁止输入模式。

振荡器

电路

读端口

COMP2

注 1: I/O 引脚上有连接到VDD 和VSS 的保护二极管。

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 31 页

PIC12F510/16F506

图 5-10: RC2 框图 图 5-11: RC3 框图

VROE

数据

数据

总线

写

端口

W

寄存器

TRIS 'f'

数据

锁存器

CK

TRIS

锁存器

CK

总线

CVREF

QD

Q

QD

Q

1

I/O

0

引脚

(1)

写

端口

W

寄存器

TRIS 'f'

CK

CK

QD

数据

锁存器

Q

QD

TRIS

锁存器

Q

复位

I/O 引脚

(1)

复位

读端口

COMP2

注 1: I/O 引脚上有连接到VDD 和VSS 的保护二极管。

读端口

注 1: I/O 引脚上有连接到 VDD 和VSS 的保护二极管。

DS41268A_CN 第 32 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

图 5-12: RC4 框图 图 5-13: RC5 框图

数据

总线

写

端口

W

寄存器

TRIS 'f'

数据

锁存器

CK

TRIS

锁存器

CK

C2OUT

C2OUTEN

复位

读端口

0

QD

Q

QD

Q

1

I/O 引脚

(1)

数据

总线

写

端口

W

寄存器

TRIS 'f'

数据

锁存器

CK

TRIS

锁存器

CK

I/O 引脚

QD

Q

QD

Q

T0CS

复位

读端口

T0CKI

(1)

注 1: I/O 引脚上有连接到VDD 和VSS 的保护二极管。

注 1: I/O 引脚上有连接到VDD 和VSS 的保护二极管。

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 33 页

PIC12F510/16F506

表 5-1: 端口寄存器汇总

地址 名称

N/A TRISGPIO

N/A TRISB

N/A TRISC

N/A OPTION

N/A OPTION

03h STATUS

03h STATUS

06h GPIO

06h PORTB

07h PORTC

图注: - = 未用 (读为 0), x = 未知, u = 不变, q = 取值视情况而定。

注 1: 仅 PIC12F510 器件才具有该寄存器。

2: 仅 PIC16F506 器件才具有该寄存器。

3: 如果由于引脚电平变化唤醒而产生复位,则 bit 7 = 1。所有其他复位都将导致 bit 7 = 0。

(2)

(2)

(1)

(2)

(1)

(2)

(1)

(2)

(2)

表 5-2: I/O 引脚功能的优先级 (PIC16F506)

优先级

1 AN0/C1IN+ AN1/C1IN- C1OUT

2 TRISB TRISB AN2

3

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

(1)

- - I/O 控制寄存器

- - I/O 控制寄存器

- - I/O 控制寄存器

GPWU GPPU T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111

RBWU RBPU T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111

GPWUF CWUF PA0 TO PD ZDCC0001 1xxx qq0q quuu

RBWUF CWUF PA0 TO PD ZDCC0001 1xxx qq0q quuu

- -

- -

- -

GP5 GP4 GP3 GP2 GP1 GP0 --xx xxxx --uu uuuu

RB5 RB4 RB3 RB2 RB1 RB0 --xx xxxx --uu uuuu

RC5 RC4 RC3 RC2 RC1 RC0 --xx xxxx --uu uuuu

RB0 RB1 RB2 RB3 RB4 RB5

输入 /MCLR

-

- -

TRISB

- - -

上电复位

时的值

--11 1111 --11 1111

--11 1111 --11 1111

--11 1111 --11 1111

所有其他

复位时的值

OSC2/CLKOUT OSC1/CLKIN

TRISIO TRISIO

(3)

(3)

表 5-3: I/O 引脚功能的优先级 (PIC16F506)

优先级

1C2IN+ C2IN-CVREF TRISC C2OUT T0CKI

2 TRISC TRISC TRISC

RC0 RC1 RC2 RC3 RC4 RC5

-

TRISC TRISC

表 5-4: I/O 引脚功能的优先级 (PIC12F510)

优先级

1 AN0/C1IN+ AN1/C1IN- C1OUT

2 TRISIO TRISIO AN2

3

4

GP0 GP1 GP2 GP3 GP4 GP5

OSC2 OSC1/CLKIN

TRISIO TRISIO

- -

- -

T0CKI

TRISIO

输入 /MCLR

-

- - -

- - -

DS41268A_CN 第 34 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

表 5-5: 数字引脚操作要求 (PIC12F510)

GP0 GP0 GP1 GP1 GP2 GP2 GP3 GP4 GP5

CM1CON0

C1ON 010 1 01

C1PREF - 0 - 1 - -

C1NREF

C1T0CS

C1OUTEN

CM2CON0

C2ON

C2PREF1

C2PREF2

C2NREF

C2OUTEN

VRCON0

VROE

VREN

OPTION

T0CS

ADCON0

ANS<1:0> 00, 01 00, 01 00, 01, 10 00, 01, 10 00 00

CONFIG

MCLRE

INTOSC

LP

EXTRC

XT

注 1: 某一引脚列中的多项代表此引脚数字功能的不同排列顺序。

2: 阴影单元表明此位的状态不会影响引脚的数字功能。

- - - 0 - -

- - - - - 1

- - - - - 1

- - - - - - - - -

- - - - - - - - -

- - - - - - - - -

- - - - - - - - -

- - - - - - - - -

- - - - - - - - -

- - - - - - - - -

- - - - -

- - - - - - - - -

- - - - - - - - -

- - - - - - -禁止禁止

- - - - - - - -禁止

- - - - - - -禁止禁止

0

- - -

- - -

- - -

- - -

- - -

- - -

- - -

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 35 页

PIC12F510/16F506

表 5-6: 数字引脚操作要求 (PIC16F506 PORTB)

RB0 RB0 RB0 RB1 RB1 RB2 RB2 RB3 RB4 RB5

CM1CON0

C1ON

C1PREF

C1NREF

C1T0CS

C1OUTEN

CM2CON0

C2ON 1

C2PREF1 0

C2PREF2 1

C2NREF

C2OUTEN

OPTION

T0CS

ADCON0

ANS<1:0> 00, 0100, 01 00, 01 00, 01, 10 00, 01, 10 00 00

CONFIG

MCLRE

INTOSC

LP

EXTRC

XT

EC

HS

INTOSC CLKOUT

EXTRC CLOCKOUT

注 1: 某一引脚列中的多项代表此引脚数字功能的不同排列顺序。

2: 阴影单元表明此位的状态不会影响引脚的数字功能。

-

- -

- - - -

- - - - - - - - - -

- - - - - -

- - - - - - - - - -

- - - - - - - - - -

- - - - - - - - - -

- - - - - - -

- - - - - - - - - -

- - - - - - - -禁止禁止

- - - - - - - - -禁止

- - - - - - - -禁止禁止

- - - - - - - - -禁止

- - - - - - - -禁止禁止

- - - - - - - -禁止禁止

- - - - - - - -禁止禁止

01 0 1 01

0

- - - - - - - - -

- - - - - - - - -

- - - - - - - - -

- - - - - - -

(1),(2)

0

- - - - -

- - -

1

- - -

- - -

0

- -

(1),(2)

表 5-7: 数字引脚操作要求 (PIC16F506 PORTC)

RC0 RC0 RC1 RC1 RC2 RC3 RC4 RC4 RC5 RC5

CM2CON0

C2ON 0101

C2PREF1

C2PREF2

C2NREF

C2OUTEN

VRCON0

VROE

OPTION

T0CS

注 1: 某一引脚列中的多项代表此引脚数字功能的不同排列顺序。

2: 阴影单元表明此位的状态不会影响引脚的数字功能。

DS41268A_CN 第 36 页 初稿 2006 Microchip Technology Inc.

-

-

- - -

- - - - - - -

- - - -

- - - - - - - -

0

0

- - - - - - - -

- - - - - - - -

0

- -

- - - - - -

01

1

0

- - ---

- -

- -

0

-

PIC12F510/16F506

5.5 I/O 编程注意事项

5.5.1 双向 I/O 端口

某些指令在内部是先执行一个读操作,再执行一个写操

作。例如 BCF 和 BSF 指令,这两个指令将整个端口的

数据读入 CPU,执行位操作,然后重写结果。当一个端

口有一个或一个以上的引脚用作输入 / 输出时,对其执

行这些指令必须加倍小心。例如,对 PORTB/GPIO 的

bit 5 执行 BSF 操作时,先将 PORTB/GPIO 的全部 8 位

数据读入 CPU,然后将 bit 5 置 1,最后将 PORTB/GPIO

的值写入输出锁存器。如果 PORTB/GPIO 的另一个位

被用作双向 I/O 引脚 (假设为 bit 0),并且该引脚此时

被定义为输入,则该引脚当前的输入信号被读入 CPU,

然后将值重新写入该特定引脚的数据锁存器,覆盖先前

的内容。只要该引脚保持输入模式,就毫无问题。然而,

如果 bit 0 随后变成了输出模式,则输出锁存器的内容将

无法得知。

例 5-1 给出了对一个 I/O 端口执行两条连续的读—修改

—写指令 (如 BCF 和 BSF 等)的效果。

当某引脚设置为输出 (高电平或低电平)时,不应通过

外部器件来驱动该引脚,以达到改变该引脚电平的目的

(“线或”或“线与”)。否则,引起的高输出电流可能

会损坏器件。

例 5-1:对I/O 端口执行读—修改—

写指令 (如 PIC16F506)

;Initial PORTB Settings

;PORTB<5:3> Inputs

;PORTB<2:0> Outputs

;

; PORTB latch PORTB pins

; ---------- ----------

BCF PORTB, 5 ;--01 -ppp --11 pppp

BCF PORTB, 4 ;--10 -ppp --11 pppp

MOVLW 007h;

TRIS PORTB ;--10 -ppp --11 pppp

;

注: 用户原本希望引脚值为 --00 pppp。第二条

BCF 指令将使 RB5 被锁存为该引脚的值(高电

平)。

5.5.2 I/O 端口的连续操作

对 I/O 端口的写操作实际发生在指令周期的末尾时刻。

但对于读操作,在指令周期的开始处所读的数据就必须

有效 (见图 5-14)。因此,如果对同一个 I/O 端口执行

写操作之后,接着执行读操作,就必须特别小心。指令

序列应使引脚电压先稳定下来 (与负载有关),才执行

下一条指令将端口值读入 CPU。否则,读入的可能是引

脚的前一个状态而不是新状态。当状态不确定时,最好

用一条 NOP 指令或者其他不访问 I/O 端口的指令隔开这

些指令。

图 5-14:连续I/O 操作 (以 PIC16F506 器件为例)

Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4

取指令

RB<5:0>

执行指令

PC PC + 1 PC + 2

MOVWF PORTB

MOVF PORTB, W

此时写

端口引脚

MOVWF PORTB

(写入 PORTB)

NOP

此时对端口引脚

进行采样

(读 PORTB)

PC + 3

NOP

NOPMOVF PORTB,W

此例为对 PORTB 执行写操作,接着读 PORTB。

数据建立时间 = (0.25 T

CY = 指令周期

其中: T

PD = 传播延时

T

因此,当时钟频率很高时,写端口后马上再读端口可

能会有问题。

CY – TPD)

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 37 页

PIC12F510/16F506

注:

DS41268A_CN 第 38 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

6.0 TMR0 模块和 TMR0 寄存器

Timer0 模块有以下特性:

• 8 位定时器 / 计数器 TMR0

• 可读写

• 软件可编程的 8 位预分频器

• 内部或外部时钟选择:

- 外部时钟边沿选择

- 来自 T0CKI 引脚或比较器输出的外部时钟

图 6-1 是 Timer0 模块的简化框图。

将 T0CS 位(OPTION<5>)清零可选择定时器模式。

在定时器模式下,Timer0 模块在每个指令周期递增(不

使用预分频器)。 TMR0 寄存器被写入时,在接下来的

两个指令周期禁止递增 (见图 6-2 和图 6-3)。用户可

通过将校正值写入 TMR0 寄存器避开这一问题。

有两种计数器模式。在第一种计数器模式下,Timer0 依

靠 T0CKI 引脚电平递增。通过将 T0CKI 位

(OPTION<5>)、 CMPT0CS

COUTEN 位(CM1CON0<6>)置 1 来选择这种模式。

在这种模式下, Timer0 可在 T0CKI 引脚信号的每个上

升沿或下降沿递增。具体是上升沿还是下降沿由 T0SE

位(OPTION<4>)决定。将 T0SE 位清零选择上升沿。

外部时钟输入的限制在第 6.1 节“Timer0 外部时钟的使

用(特性2)”中详细讨论。

位(CM1CON0<4>)和

在第二种计数器模式下,Timer0 依靠比较器输出递增。

有两种不同的方式选择这种模式。第一种方式是通过将

T0CS 位(OPTION<5>)置 1 并将 CMPT0CS

位

(CMCON<4>)清零 ( COUTEN [CMCON<6>] 不会对

这种模式产生影响)来选择的。这样允许比较器和

Timer0 之间建立内部连接。

第二种方式是通过将 T0CS 位(OPTION<5>)和

CMPT0CS

位(CM1CON0)置 1,并将 COUTEN 位

(CM1CON0<6>)清零来选择的。这样将允许在 T0CKI

输入保持有效的同时将比较器输出送入 T0CKI 引脚。因

此,比较器 COUT 引脚上电平的任何变化都将反馈给

T0CKI 输入引脚。导致计数器递增的边沿由 T0SE 位

(OPTION<4>)决定。将 T0SE 位清零选择上升沿。外

部时钟输入的限制在第 6.1 节“Timer0 外部时钟的使用

(特性 2)”中详细讨论。

该预分频器可由 Timer0 模块或看门狗定时器使用,但

它们不可同时使用。预分频器的分配在软件中由 PSA

(OPTION<3>)控制位控制。将 PSA 位清零将预分频

器分配给 Timer0。预分频器是不可读写的。当预分频器

分配给 Timer0 模块时,可选择的预分频比有 1:2,1:4,

...,1:256。预分频器的具体操作请参见第 6.2 节“预分

频器”。

与 Timer0 模块相关的寄存器汇总请参见表 6-1。

图 6-1: TIMER0 框图

T0CKI

引脚

FOSC/4

内部

比较器

输出

注 1: T0CS、 T0SE、 PSA、 PS2、 PS1 和 PS0 均位于选项寄存器中。

2: 该预分频器是与看门狗定时器共用的 (见图 6-5)。

3: CMPT0CS

1

0

CMPT0CS

(1)

T0SE

(3)

位位于 CM1CON0 寄存器中,为 CM1CON0<4>。

0

1

T0CS

PS2, PS1, PS0

(1)

可编程

预分频器

3

(2)

(1)

1

PSA

OUT

PS

0

(1)

与内部

时钟

同步

(延时两个 TCY)

数据总线

8

TMR0 寄存器

PSOUT

同步

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 39 页

PIC12F510/16F506

图 6-2: TIMER0 时序图:内部时钟 / 无预分频器

PC

(程序

计数器)

取指令

Timer0

执行指令

Q1 Q2 Q3 Q4

PC - 1

T0

Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4

PC PC + 1 PC + 2 PC + 3 PC + 4 PC + 6

MOVWF TMR0 MOVF TMR0,W MOVF TMR0,W MOVF TMR0,W MOVF TMR0,W MOVF TMR0,W

T0 + 1 T0 +2 NT0

执行写

TMR0

读 TMR0

为 NT0

图 6-3: TIMER0 时序图:内部时钟 / 预分频比 1:2

PC

(程序

计数器)

取指令

Timer0

执行指令

Q1 Q2 Q3 Q4

PC - 1

T0

Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4

PC PC + 1 PC + 2 PC + 3 PC + 4 PC + 6

MOVWF TMR0 MOVF TMR0,W MOVF TMR0,W MOVF TMR0,W MOVF TMR0,W MOVF TMR0,W

T0 + 1 NT0

执行写

TMR0

读 TMR0

为 NT0

读 TMR0

为 NT0

读 TMR0

为 NT0

读 TMR0

为 NT0

读 TMR0

为 NT0

PC + 5

NT0 + 1

读 TMR0

为 NT0 + 1

PC + 5

读 TMR0

为 NT0 + 1

NT0 +2

读 TMR0

为 NT0 + 2

NT0 + 1

读 TMR0

为 NT0 + 2

表 6-1:与TIMER0 相关的寄存器

地址 名称

01h TMR0

07h

CM1CON0

08h CM1CON0

N/A OPTION

N/A TRISGPIO

图注: Time r0 不使用阴影单元,- = 未用, x = 未知, u = 不变。

注 1: 当 T0CS = 1 时, T0CKI 引脚的 TRIS 被忽略。

2: 仅 PIC12F510 器件才具有该寄存器。

3: 仅 PIC16F506 器件才具有该寄存器。

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Timer0——8 位实时时钟 / 计数器

(2)

C1OUT C1OUTEN C1POL C1T0CS C1ON C1NREF C1PREF C1WU

(3)

C1OUT C1OUTEN C1POL C1T0CS C1ON C1NREF C1PREF C1WU 1111 1111

GPWU GPPU T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111

(1)

- - I/O 控制寄存器

上电复位

时的值

所有其他

复位时的值

xxxx xxxx uuuu uuuu

1111 1111

uuuu uuuu

uuuu uuuu

---- 1111 --11 1111

DS41268A_CN 第 40 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

6.1 Timer0 外部时钟的使用 (特性 2)

当 Timer0 使用外部时钟输入时,必须满足一定要求。这

种外部时钟要求是为了确保外部时钟和内部相位时钟

(TOSC)保持同步。同步后,Timer0 的实际递增还将有

一定延时。

6.1.1 外部时钟同步

当不使用预分频器时,外部时钟输入与预分频器输出

相同。在内部相位时钟的 Q2 和 Q4 周期对预分频器输

出进行采样可实现 T0CKI 与内部相位时钟的同步(见

图 6-4)。因此, T0CKI 或比较器输出的高电平必须至

少保持 2 个 T

并且其低电平也必须至少保持 2 个 T

的一小段 RC 延时)。请参见所用器件的电气规范。

图 6-4: TIMER0 与外部时钟时序图

OSC (加上 2 Tt0H 的一小段 RC 延时),

OSC (加上 2 Tt0H

Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4

外部时钟输入或

预分频器输出

采样后外部时钟 /

预分频器的输出

Timer0 递增(Q4)

(2)

(1)

(3)

当使用预分频器时,外部时钟输入被异步波纹计数器类

型的预分频器分频,故预分频器的输出是对称的。为了

使外部时钟满足采样要求,必须考虑波纹计数器。因

此,T0CKI 或比较器输出的周期必须至少保持4 个 T

OSC

(加上4 Tt0H 的一小段RC 延时)除以分频值。对 T0CKI

或比较器输出的高、低电平时间的惟一要求是脉宽不得

小于 Tt0H。请参见所用器件的电气规范中的参数 40、

41 和 42。

6.1.2 TIMER0 的递增延时

由于预分频器的输出与内部时钟同步,因此从出现外部

时钟沿到 Timer0 模块实际递增有一小段延时。图 6-4 显

示了从外部时钟沿到定时器递增的延时。

窄脉冲

丢失采样

Timer0

注 1: 从时钟输入变化到 Time r0 递增有 3 到 7 个 T

边沿之间的间隔的最大误差为± 4 个 T

2: 如果未选择预分频器,则为外部时钟,否则为预分频器输出。

3: 箭头所指为采样时刻。

OSC。

6.2 预分频器

一个 8 位的计数器可分别作为 Timer0 模块的预分频器

或看门狗定时器 (WDT)的后分频器 (见图 10-12)。

为简化起见,在本数据手册中称该计数器为 “预分频

器”。

注: 该预分频器由 Timer0 模块或看门狗定时器

使用,但它们不可同时使用。因此,如果

把预分频器分配给 Timer0 模块就意味着

WDT 无分频器可用,反之亦然。

T0 T0 + 1 T0 +2

OSC 的延时 (持续时间 Q = TOSC)。因此,测量 Timer0 输入脉冲相邻

PSA 和 PS<2:0> 位(OPTION<3:0>)决定预分频器的

分配和分频比。

当预分频器分配给 Timer0 模块时,所有写入 TMR0 寄

存器的指令 (如 CLRF 1, MOVWF 1, BSF 1, x,

等)都会将预分频器清零。当预分频器分配给 WDT 时,

执行 CLRWDT 指令会同时将预分频器和 WDT 清零。预

分频器是不可读写的。复位时,预分频器包含为全 0 的

值。

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 41 页

PIC12F510/16F506

6.2.1 切换预分频器的分配

预分频器的分配完全由软件控制(即,它可在程序执行

期间被 “随时”改变)。为避免器件意外复位,当把预

分频器从 Timer0 分配给 WDT 时,必须执行下列指令序

列 (见例 6-1)。

例 6-1 : 改变预分频器 (TIMER0 → WDT)

CLRWDT ;Clear WDT

CLRF TMR0 ;Clear TMR0 & Prescaler

MOVLW ‘00xx1111’b ;These 3 lines (5, 6, 7)

OPTION ;are required only if

;desired

CLRWDT ;PS<2:0> are 000 or 001

MOVLW ‘00xx1xxx’b ;Set Postscaler to

OPTION ;desired WDT rate

图 6-5: TIMER0/WDT 预分频器框图

(2)

T0CKI

比较器

输出

引脚

TCY (= FOSC/4)

1

0

(1)

T0SE

0

1

T0CS

要将预分频器从 WDT 分配给 Timer0 模块,使用例 6-2

所示的指令序列。即使在 WDT 被禁止时,也必须使用

该序列。应该在切换预分频器之前执行 CLRWDT 指令。

例 6-2: 改变预分频器 (WDT →TIMER0)

CLRWDT ;Clear WDT and

;prescaler

MOVLW ‘xxxx0xxx’ ;Select TMR0, new

OPTION

M

U

X

(1)

1

0

PSA

M

U

X

(1)

;prescale value and

;clock source

数据总线

2 周期

同步电路

TMR0 寄存器

8

CMPT0CS

WDT 使能位

注 1: T0CS 、 T0SE、 PSA 和 PS<2:0> 均为选项寄存器中的位。

2: 在 PIC12F510 器件中 T0CKI 与 GP2 引脚复用,而在 PIC16F506 器件中 T0CKI 与 RC5 复用。

3: CMPT0CS

(3)

0

看门狗

定时器

位位于 CM1CON0 寄存器中。

1

PSA

M

U

X

(1)

8 位预分频器

8

8 选 1 MUX

0

MUX

WDT

超时溢出

PS<2:0>

1

(1)

PSA

(1)

DS41268A_CN 第 42 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

7.0 比较器模块

PIC12F510 器件包含一个模拟比较器模块。 PIC16F506 包

含两个比较器模块和一个比较器参考电压模块。第二个比

较器旨在为器件提供一些额外的比较器功能。

寄存器 7-1: CM1CON0 寄存器 (地址:07h)( PIC12F510)

R-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1

C1OUT C1OUTEN

bit 7 bit 0

C1POL C1T0CS C1ON C1NREF C1PREF C1WU

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

C1OUT:比较器输出位

1 = V

IN+ > VIN-

0 = VIN+ < VIN-

C1OUTEN

1 = 比较器不通过 C1OUT 引脚输出电平

0 = 比较器通过 C1OUT 引脚输出电平

C1POL:比较器输出极性位

1 = 比较器输出不反相

0 = 比较器输出反相

C1T0CS:比较器 TMR0 时钟源位

1 = T0CS 控制位决定 TMR0 时钟源的选择

0 = 比较器输出作为 TMR0 的时钟源

C1ON:比较器使能位

1 = 比较器开启

0 = 比较器关闭

C1NREF:比较器负参考电压选择位

1 = CIN- 引脚

0 = V

C1PREF:比较器正参考电压选择位

1 = CIN+ 引脚

0 = CIN- 引脚

C1WU

1 = 禁止比较器电平变化唤醒

0 = 使能比较器电平变化唤醒

注 1: 该位改写 T0CS 位以进行 GP2 的 TRIS 控制。

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 10 = 清零 x = 未知

:比较器输出使能位

REF

:比较器电平变化唤醒使能位

2: 当比较器开启时,这些控制位都将有效,否则其他寄存器具有优先权。

(1),(2)

(2)

(2)

(2)

(2)

(2)

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 43 页

PIC12F510/16F506

寄存器 7-2: CM1CON0 寄存器 (地址:08h)( PIC16F506)

R-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1

C1OUT C1OUTEN

bit 7 bit 0

C1POL C1T0CS C1ON C1NREF C1PREF C1WU

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

C1OUT:比较器输出位

1 = V

IN+ > VIN-

0 = VIN+ < VIN-

C1OUTEN

:比较器输出使能位

(1),(2)

1 = 比较器不通过 C1OUT 引脚输出电平

0 = 比较器通过 C1OUT 引脚输出电平

C1POL:比较器输出极性位

(2)

1 = 比较器输出不反相

0 = 比较器输出反相

C1T0CS

:比较器 TMR0 时钟源位

(2)

1 = T0CS 控制位决定 TMR0 时钟源的选择

0 = 比较器输出作为 TMR0 的时钟源

C1ON:比较器使能位

1 = 比较器开启

0 = 比较器关闭

C1NREF:比较器负参考电压选择位

(2)

1 = CIN- 引脚

0 = V

REF

C1PREF:比较器正参考电压选择位

(2)

1 = CIN+ 引脚

0 = CIN- 引脚

C1WU

:比较器电平变化唤醒使能位

(2)

1 = 禁止比较器电平变化唤醒

0 = 使能比较器电平变化唤醒

注 1: 该位改写 T0CS 位以进行 RC5 的 TRIS 控制。

2: 当比较器开启时,这些控制位都将有效,否则其他寄存器具有优先权。

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 10 = 清零 x = 未知

DS41268A_CN 第 44 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

寄存器 7-3: CM2CON0 寄存器 (地址:0Bh)( PIC16F506)

R-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1

C2OUT C2OUTEN

bit 7 bit 0

C2POL C2PREF2 C2ON C2NREF C2PREF1 C2WU

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

C2OUT:比较器输出位

1 = V

IN+ > VIN-

0 = VIN+ < VIN-

C2OUTEN

:比较器输出使能位

(1),(2)

1 = 比较器不通过 C2OUT 引脚输出电平

0 = 比较器通过 C2OUT 引脚输出电平

C2POL:比较器输出极性位

(2)

1 = 比较器输出不反相

0 = 比较器输出反相

C2PREF2:比较器正参考电压选择位

(2)

1 = C1IN+ 引脚

0 = C2IN- 引脚

C2ON:比较器使能位

1 = 比较器开启

0 = 比较器关闭

C2NREF:比较器负参考电压选择位

(2)

1 = C1IN- 引脚

0 = V

REF

C2PREF1:比较器正参考电压选择位

(2)

1 = C2IN+ 引脚

0 = C2PREF2 控制模拟输入选择

C2WU

:比较器电平变化唤醒使能位

(2)

1 = 禁止比较器电平变化唤醒

0 = 使能比较器电平变化唤醒

注 1: 该位改写 T0CS 位以进行 RC4 的 TRIS 控制。

2: 当比较器开启时,这些控制位都将有效,否则其他寄存器具有优先权。

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 10 = 清零 x = 未知

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 45 页

PIC12F510/16F506

图 7-1: PIC12F510 的比较器框图

C1PREF

C1IN-

C1IN+

C2NREF

0

MUX

1

C1ON

至

数据总线

读 CM2CON0

DQ

Q3* 读 CM1CON0

(1)

NRESET

EN

CL

C1WU

C1WUF

使能 C1 输出

C1IN-

0.6 VREF

1

MUX

0

+

C1

-

C1POL

注 1: 当 C1ON = 0 时, C1 比较器将产生一个 0 输出到异或门。

图 7-2: PIC16F506 的比较器框图

C2PREF1

C1IN+

C2IN-

C2PREF2

C2NREF

1

C2VN

MUX

C2VP

0

1

C2IN+

1

MUX

0

C2IN-

+

C2

-

C2ON

(1)

C2POL

C1OUT

Q3* 读 CM2CON0

NRESET

C2OUT

DQ

EN

CL

C1OUT

至

数据总线

读 CM2CON0

C2WUF

C2WU

使能 C2 输出

C2OUT

CV

REF

注 1: 当 C2ON = 0 时, C2 比较器将产生一个 0 输出到异或门。

MUX

0

DS41268A_CN 第 46 页 初稿 2006 Microchip Technology Inc.

7.1 比较器工作原理

图 7-3 所示为单比较器以及模拟输入电平和数字输出之

间的关系。当 VIN+ 上的模拟输入小于 VIN- 上的模拟输

入时,比较器将输出数字低电平。图 7-3 中比较器输出

的阴影部分代表由于输入失调电压和响应时间所引起的

不确定区。关于共模电压,请参见表 13-1。

PIC12F510/16F506

注: 对被定义为数字输入的任何引脚施加模拟

电平均可能使输入缓冲器的电流消耗超过

规定值。

7.5 比较器唤醒标志

图 7-3: 单比较器

V

IN-

VIN+

结果

VIN+

V

IN-

+

–

结果

7.2 比较器参考电压

根据工作模式,比较器可以使用内部参考电压。加在

Vin- 上的模拟信号会与 Vin+ 上的信号相比较,比较器

的数字输出会相应调整 (见图 7-3)。关于内部参考电

压规范请参见第 8.0 节 “比较器参考电压模块”。

7.3 比较器响应时间

响应时间是指比较器从选定一个新的参考电压或输入电

压源到输出达到一个有效电平时的最短时间。如果比较

器输入发生了改变,则必须要有一段延时允许比较器达

到稳定的新状态。关于比较器响应时间规范的信息请参

见表 13-1。

当符合下面所有条件时,比较器唤醒标志将置 1:

• C1WU

• 读取 CM1CON0 或 CM2CON0 以锁存 CMPOUT

• 器件处于休眠模式

• 比较器的输出状态发生了改变

此唤醒标志可由软件或器件复位清零。

= 0 (CM1CON0<0>)或

C2WU = 0 (CM2CON0<0>)

位的上一个已知状态 (MOVF CM1CON0, W)

7.6 比较器在休眠模式下的工作方式

当比较器处于活动状态而器件处于休眠模式时,比较器

仍可保持正常工作。在比较器上电复位时,会产生较高

的休眠电流 (在掉电电流规范中有说明)。若要把休眠

模式下的功耗减少到最小,应该在进入休眠之前关闭比

较器。

7.7 复位的影响

上电复位会强制 CM2CON0 寄存器进入复位状态。这将

使比较器模块处于比较器复位模式。确保所有可能的输

入都为模拟输入。复位时引脚为模拟输入将使器件电流

达到最小。在复位期间,比较器将掉电。

7.8 模拟输入连接注意事项

图 7-4 是一个简化的模拟输入电路。由于模拟引脚和数

字输出端相连,因此在模拟引脚与 VDD 和 VSS 之间连

有反向偏置的二极管,将其电压限制在 V

间。一旦输入电压超出该范围 0.6V 以上,其中一个二

极管就会发生正向偏置从而可能使输入电压闭锁。模拟

信号源的最大阻抗推荐值为 10 kΩ。任何连接到模拟输

入引脚上的外部元件 (如电容器或齐纳二极管),均应

保证其只有极小的漏电流。

SS 和 VDD 之

7.4 比较器输出

通过读取 CM1CON0 或 CM2CON0 寄存器中的相应位

可得到比较器的输出。该位是只读的。比较器输出也可

供内部使用,请参见图 7-3。

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 47 页

PIC12F510/16F506

图 7-4: 模拟输入模型

V

DD

RS < 10 K

VA

A

IN

CPIN

5pF

VT = 0.6V

T = 0.6V

V

图注: CPIN = 输入电容

T = 门限电压

V

ILEAKAGE = 引脚上的泄漏电流

RIC = 内部走线等效阻抗

RS = 信号源内阻

VA = 模拟电压

表 7-1: 与比较器模块相关的寄存器

地址 名称

03h STATUS GPWUF CWUF

07h CM1CON0

08h CM1CON0

0Bh CM2CON0

N/A TRISB

N/A TRISC

N/A TRISGPIO

图注: x = 未知, u = 不变,- = 未用 (读为 0), q = 取值视情况而定。

注 1: 仅 PIC12F510 器件才具有该寄存器。

2: 仅 PIC16F506 器件才具有该寄存器。

(2)

(2)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

-

(1)

C1OUT C1OUTEN C1POL C1T0CS C1ON C1NREF C1PREF C1WU 1111 1111 uuuu uuuu

(2)

C1OUT C1OUTEN C1POL C1T0CS C1ON C1NREF C1PREF C1WU 1111 1111 uuuu uuuu

(2)

C2OUT C2OUTEN C2POL C2PREF2 C2ON C2NREF C2PREF1 C2WU 1111 1111 uuuu uuuu

- - I/O 控制寄存器

- - I/O 控制寄存器

(1)

- - I/O 控制寄存器

TO

R

IC

ILEAKAGE

±500 nA

V

SS

上电复位

时的值

PD ZDCC0001 1xxx qq0q quuu

--11 1111 --11 1111

--11 1111 --11 1111

--11 1111 --11 1111

所有其他复

位时的值

DS41268A_CN 第 48 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

8.0 比较器参考电压模块

比较器参考电压模块允许选择内部产生的参考电压作为

比较器的一个输入。 VRCON 寄存器 (寄存器 8-1)控

制参考电压模块,如图 8-1 所示。

8.1 配置参考电压

参考电压模块可以输出 32 种不同的电压; 16 个属于高

电压范围, 16 个属于低电压范围。

公式 8-1 决定输出电压:

公式 8-1:

VRR = 1

VRR = 0

(低电平范围):

(高电平范围)

CVREF = (VDD/4) + (VR3:VR0 x VDD/32)

CVREF = (VR3:VR0/24) x VDD

:

8.2 参考电压精度 / 误差

由于模块的结构所限,不能达到从 VSS 到 VDD 的整个

电压范围。梯形电阻网络 (图 8-1)顶部和底部的晶体

管使 CVREF 无法达到 VSS 或 VDD。但例外情况是当将

VREN 位(VRCON<7>)清零以禁止该模块时。如果

禁止该模块,当 VR<3:0> 是 0000 且 VRR

(VRCON<5>)置 1 时,参考电压为 V

进行过零检测且不消耗 CV

由于参考电压是由 V

DD 的波动而变化。经测试的比较器参考电压绝对

随着 V

精度请参见第 13.2 节“直流特性:PIC12F510/16F506

(扩展级)”。

寄存器 8-1: VRCON——仅 PIC16F506 (地址:0Ch)

R/W-0 R/W-0 R/W-1 U-0 R/W-1 R/W-1 R/W-1 R/W-1

bit 7

bit 6

bit 5

bit 4

bit 3-0

VREN VROE VRR

bit 7 bit 0

VREN:CV

1 = CV

0 = CVREF 掉电,不输出电流

VROE:CV

1 = 使能 VREF 输出

0 = 禁止 VREF 输出

VRR:CV

1 = 低电平范围

0 = 高电平范围

未用:读为 0

VR<3:0>:CV

当 VRR = 1 时:CVREF= (VR<3:0>/24)*VDD

当 VRR = 0 时:CVREF= VDD/4+(VR<3:0>/32)*VDD

注 1: 当此位置 1 时, VREF 引脚的 TRIS 被改写并且模拟电压置于 VREF 引脚。

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 10 = 清零 x = 未知

REF 使能位

REF 上电

REF 输出使能位

REF 范围选择位

REF 值选择位

2: 取 V

REF 的某个比例作为参考电压的控制仅适用于 PIC12F506 器件上的比较器 2。

(1)

(2)

-

SS。允许比较器

REF 模块电流。

DD 产生的,因此 CVREF 的输出会

VR3 VR2 VR1 VR0

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 49 页

PIC12F510/16F506

图 8-1: 比较器参考电压框图

16 阶

VDD

8R R R

16-1 模拟

VREN

MUX

CVREF 至

比较器

输入

RC3/VREF

VR3:VR0

VREN

VR3:VR0 = 0000

VRR

表 8-1: 与比较器参考电压相关的寄存器

地址 名称

0Ch VRCON VREN VROE VRR

07h CM1CON0

08h CM1CON0

0Bh CM2CON0

图注: x = 未知, u = 不变,- = 未用 (读为 0)。

注 1: 仅 PIC12F510 器件才具有该寄存器。

2: 仅 PIC16F506 器件才具有该寄存器。

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

(1)

C1OUT C1OUTEN C1POL C1T0CS C1ON C1NREF C1PREF C1WU 1111 1111 uuuu uuuu

(2)

C1OUT C1OUTEN C1POL C1T0CS C1ON C1NREF C1PREF C1WU 1111 1111 uuuu uuuu

(2)

C2OUT C2OUTEN C2POL C2PREF2 C2ON C2NREF C2PREF1 C2WU 1111 1111 uuuu uuuu

-

RR

8R

上电复位

时的值

VR3 VR2 VR1 VR0 001- 1111 001- 1111

VRR

其他复位

时的值

DS41268A_CN 第 50 页 初稿 2006 Microchip Technology Inc.

9.0 模数 (A/D)转换器

PIC12F510/16F506

A/D 转换器可以将模拟信号转换为表示该信号的 8 位数

字信号。

9.1 时钟分频器

AD转换器(ADC)有 4个时钟源可分别通过ADCS<1:0>

进行设置。前 3 种设置分别将信号进行 32、 16 和 8 分

频。第 4 种设置为带有分频比为 4 的分频器的 INTOSC。

当使用工作频率为 350 KHz 到 20 MHz 之间的外部振荡

器时,这些设置使转换能顺利进行。使用工作频率低于

350 kHz 的外部振荡器时需要将 ADC 振荡器设置为

INTOSC/8,以得到有效的 ADC 转换结果。

ADC 转换需要 13 个 T

换需要的 TAD 周期数,它只决定 TAD 周期的长度。

当在 ADC 转换的过程中改变 ADCS<1:0> 位时,在下一

次转换开始前,不会选择新的 ADC 时钟源。当器件进

入休眠模式时,将丢失选择的时钟源。

注: ADC 时钟由指令时钟产生。ADCS 分频器

可用于产生 ADC 时钟。

9.1.1 参考电压

ADC 没有外部参考电压。 ADC 参考电压总是 VDD。

9.1.2 模拟模式选择

ANS<1:0> 位用于将引脚配置为模拟输入。发生任何复

位时, ANS<1:0> 都默认为 11,从而将 AN0、 AN1 和

AN2 引脚配置为模拟输入。如果使能比较器输出,则比

较器输出 C1OUT 将使 AN2 变为输出。配置为模拟输入

的引脚不可用于数字输出。当在进行转换时,用户不应

改变 ANS 位。不论 ADON 的状态如何,ANS 位始终有

效。

AD 周期。分频值不会影响执行转

注: 用户负责确保在 ADC 和比较器同时使用同

一引脚时,不会影响对引脚信号的监控并

且不会对器件工作造成负面影响。

如果在 ADC 转换过程中改变了 CHS<1:0> 位,在当前

转换完成前,不会选择新通道。这样能确保当前转换完

成后的结果有效。当器件进入休眠模式时,将丢失所有

有关通道选择的信息。

表 9-1: 事件发生后的通道选择 (ADCS)位

事件

MCLR

转换完成

转换终止

上电复位

从休眠模式唤醒

9.1.4 GO/DONE

GO/DONE 位用于确定转换状态、启动一个转换并手动

停止正在进行的转换。将 GO/DONE 位置 1 将启动转

换。当转换完成后,ADC 模块将 GO/DONE 位清零。手

动将 GO/DONE 位清零可终止正在进行的转换。手动终

止转换可能导致 ADRES 中只有部分转换结果。

当器件进入休眠模式时,GO/DONE

前转换。 ADC 没有专用的振荡器,它依靠指令时钟工

作。因此,在休眠模式不会进行转换。

当 ADON 清零时,不能将 GO/DONE

位

ADCS<1:0>

11

CS<1:0>

CS<1:0>

11

11

位被清零,停止当

位置 1。

9.1.3 ADC 通道选择

CHS 位用于选择 ADC 采样的模拟通道。可在任何时刻

更改 CHS<1:0> 位而不会对转换造成负面影响。要获得

模拟信号,CHS<1:0> 的选择必须与 ANS<1:0> 位所选

的引脚 (或其中之一)匹配。当 ADC 启动 (ADON = 1)

并选择了比较器也正在使用的通道时,比较器和 ADC 都

将在该引脚上获得模拟电压。

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 51 页

PIC12F510/16F506

9.1.5 休眠模式

ADC 没有专用的 ADC 时钟,因此在休眠模式不可能工

作。如果在转换进行过程中执行一条 SLEEP 指令,则

GO/DONE 和 ADON 位将被清零。这样会停止任何正在

进行的转换,并且关闭 ADC 模块以节约功耗。由于转

换过程的特性, ADRES 可能保存部分转换的结果,在

进入休眠模式前至少要转换 1 位数据,才会使 ADRES

中有部分完成的转换数据。 ADCS 和 CHS 位复位到默

认状态; ANS<1:0> = 11 且 CHS<1:0> = 11。

表 9-2: 使用各种振荡器在 ADCS 不同设置下的 TAD

时钟源

INTOSC 11 8.5µs1 µs

FOSC 10 8

FOSC 01 16

FOSC 00 32 .8 µs1µs2µs4µs16µs32µs46µs

要得到正确的转换结果, TAD 必须符合以下条件:

• 500 ns < T

• T

AD = 1/(FOSC/ 分频值 )

阴影部分表示 T

的模拟处于这些频率范围内,则请使用 INTOSC/8 作为

ADC 的时钟源。

ADCS

<1:0>

AD < 50 µs

分频器

AD 超出了精确转换范围。如果需要转换

20

MHz

.2 µs .25 µs.5µs1µs4µs8µs11µs20µs40µs 125 µs

.4 µs.5µs1µs2µs8µs16µs23µs40µs 80 µs 250 µs

16

MHz

8MHz 4MHz 1MHz

500

kHz

350

kHz

200

kHz

80 µs 160 µs 500 µs

100

kHz

32 kHz

9.1.6 模拟转换结果寄存器

ADRES 寄存器保存上次转换的结果。这些结果一直保

持到下一次模拟转换的采样阶段。当采样周期结束后,

ADRES 清零 (= 0)。“前导位”向右移入 ADRES 作

为内部转换完成位。从高字节开始按位依次进行转换,

“前导位”不断右移以使后来转换的位填入 ADRES 中。

当 “前导位”右移 9 次后转换完成; “前导位”移出

且 GO/DONE

如果在转换过程中 GO/DONE

止。 ADRES 中的数据为部分转换结果。此数据对于已

转换的位是有效的。“前导位”的位置决定已转换位的

个数。在 GO/DONE

恢复的。

位清零。

位由软件清零,转换即停

位清零以前没有被转换的位是不可

DS41268A_CN 第 52 页 初稿 2006 Microchip Technology Inc.

寄存器 9-1: ADCON0 寄存器

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-0 R/W-0

ANS1 ANS0 ADCS1 ADCS0 CHS1 CHS0 GO/DONE ADON

bit 7 bit 0

PIC12F510/16F506

bit 7-6

bit 5-4

bit 3-2

bit 1

bit 0

ANS<1:0>:PIC16F506 的 ADC 模拟输入引脚选择位

00 = 没有引脚被配置为模拟输入

01 = GP2/AN2 被配置为模拟输入

10 = GP2/AN2 和 GP0/AN0 被配置为模拟输入

11 = GP2/AN2、 GP1/AN1 和 GP0/AN0 被配置为模拟输入

ADCS<1:0>:ADC 转换时钟选择位

00 = F

OSC/32

01 = FOSC/16

OSC/8

10 = F

11 = INTOSC/8

CHS<1:0>:PIC16F506 的 ADC 通道选择位

00 = 通道 00 (GP0/AN0)

01 = 通道 01 (GP1/AN1)

10 = 通道 02 (GP2/AN2)

11 = 0.6V 绝对参考电压

GO/DONE

1 = 正在进行 ADC 转换。将此位置 1 启动 ADC 转换。当执行 ADC 转换时,此位会被硬件自动清

0 =ADC转换完成 / 不在进行中。在转换过程中手动清零该位将终止当前转换。

ADON:ADC 使能位

1 =ADC模块在运行

0 =ADC模块被关闭且不消耗功耗

注 1: 在 PIC16F506 上,此项为 RBx ;在 PIC12F510 上,此项为 GPx。

:ADC 转换状态位

零。

2: 当 ANS 位置 1 时,不管先前将引脚定义为何功能,都会自动强制选定通道为模拟模

式。惟一的例外情况是比较器,在这种情况下,输入到比较器和 ADC 的模拟输入将

同时有效。用户负责确保比较器输入端上的 ADC 负载不会影响其应用。

3: 不论 ADON 是什么状态, ANS<1:0> 位始终有效。

4: 任何复位后, CHS<1:0> 位都默认为 11。

5: 如果 ADON 位清零,则 GO/DONE

6: 当使能 C1OUT 时,它将改写 AN2 引脚的功能。

(5)

(4),(6)

(1),(2),(3),(6)

位不能被置 1。

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 10 = 清零 x = 未知

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 53 页

PIC12F510/16F506

寄存器 9-2: ADRES 寄存器

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-0 R/W-0

ADRES7 ADRES6 ADRES5 ADRES4 ADRES3 ADRES2 ADRES1 ADRES0

bit 7 bit 0

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 10 = 清零 x = 未知

表 9-3:休眠对ADRES0 的影响

ANS1 ANS0 ADCS1 ADCS0 CHS1 CHS0 GO/DONE ADON

进入

不变 不变

休眠模式

唤醒或复位

11111100

例 9-1: 执行模数转换 例 9-2: 转换过程中改变通道选择

;来自于存储区 0 的采样代码

MOVLW 0xF1 ;configure A/D

MOVWF ADCON0

BSF ADCON0, 1 ;start conversion

loop0 BTFSC ADCON0, 1;wait for ‘DONE’

GOTO loop0

MOVF ADRES, W ;read result

MOVWF result0 ;save result

BSF ADCON0, 2 ;setup for read of

;channel 1

loop1 BTFSC ADCON0, 1;wait for ‘DONE’

loop2 BTFSC ADCON0, 1;wait for ‘DONE’

BSF ADCON0, 1 ;start conversion

GOTO loop1

MOVF ADRES, W ;read result

MOVWF result1 ;save result

BSF ADCON0, 3 ;setup for read of

BCF ADCON0, 2 ;channel 2

BSF ADCON0, 1 ;start conversion

GOTO loop2

MOVF ADRES, W ;read result

MOVWF result2 ;save result

111100

MOVLW 0xF1 ;configure A/D

MOVWF ADCON0

BSF ADCON0, 1 ;start conversion

BSF ADCON0, 2 ;setup for read of

;channel 1

loop0 BTFSC ADCON0, 1;wait for ‘DONE’

GOTO loop0

MOVF ADRES, W ;read result

MOVWF result0 ;save result

BSF ADCON0, 1 ;start conversion

BSF ADCON0, 3 ;setup for read of

BCF ADCON0, 2 ;channel 2

loop1 BTFSC ADCON0, 1;wait for ‘DONE’

GOTO loop1

MOVF ADRES, W ;read result

MOVWF result1 ;save result

BSF ADCON0, 1 ;start conversion

loop2 BTFSC ADCON0, 1;wait for ‘DONE’

GOTO loop2

MOVF ADRES, W ;read result

MOVWF result2 ;save result

CLRF ADCON0 ;optional: returns

;pins to Digital mode and turns off

;the ADC module

DS41268A_CN 第 54 页 初稿 2006 Microchip Technology Inc.

PIC12F510/16F506

10.0 CPU 的特殊性能

单片机与其他处理器的区别在于其具有处理实时应用需

要的特殊电路。PIC12F510/16F506 单片机具有许多特

性,旨在最大限度地提高系统的可靠性,通过减少外部

元件将成本降至最低,并且还提供了低功耗工作模式和

代码保护功能。这些特性如下:

• 振荡器选择

• 复位:

- 上电复位 (POR)

- 器件复位定时器 (DRT)

- 引脚电平变化时从休眠模式唤醒

• 看门狗定时器 (WDT)

• 休眠

• 代码保护

• ID 单元

• 在线串行编程 (ICSP™)

• 时钟输出

PIC12F510/16F506 器件具有一个看门狗定时器,只有

通过配置位 WDTE 才可将其关闭。为了增强可靠性,它

依靠自己的 RC 振荡器运行。如果使用 HS

(PIC16F506)、 XT 或 LP 可选振荡器,就总是会由器

件复位定时器(DRT)提供一定的延时,用于在晶振稳

定之前使芯片保持为复位状态。如果使用 INTRC、

EXTRC 或 EC,那么将只在V

(标称值)的延时。有了此片上定时器,大部分应用都

不再需要外部复位电路。

休眠模式是为提供电流非常低的掉电模式而设计的。用

户可以通过输入引脚上的电平变化或通过看门狗定时器

超时溢出使器件从休眠模式唤醒。有几种振荡器供器件

选择以适应不同的应用,其中包括内部 4/8 MHz 振荡

器。EXTRC 振荡器可以节省系统成本,而 LP 晶振可以

节省功耗。可以使用一组配置位来选择不同的振荡器。

DD 上电时才具有 1.125 ms

10.1 配置位

PIC12F510/16F506 配置字由 12 位组成。可以编程配置

位来选择不同的器件配置。有三个位可用于选择振荡器

类型; (PIC12F510 器件为两个位),一个位是看门狗

定时器使能位,一个位是 MCLR

于代码保护 (寄存器 10-1 和寄存器 10-2)。

使能位,还有一个位用

2006 Microchip Technology Inc. 初稿 DS41268A_CN 第 55 页

PIC12F510/16F506

寄存器 10-1: 配置字——PIC12F510

- - - - - -

bit 11 bit 0

bit 11-6

bit 5

bit 4: MCLRE:主复位使能位

bit 3: CP:代码保护位

bit 2: WDTE:看门狗定时器使能位

bit 1-0: FOSC1:FOSC0:振荡器选择位

未用:读为 1

IOSCFS:内部振荡器频率选择位

1 = 8 MHz INTOSC 速率

0 = 4 MHz INTOSC 速率

1 = GP3/MCLR

0 = GP3/MCLR 用作 GP3, MCLR 内部连接到 VDD

1 = 代码保护关闭

0 = 代码保护打开

1 = 使能 WDT

0 = 禁止 WDT

00 = 带 18 ms DRT 的 LP 振荡器

01 = 带 18 ms DRT 的 XT 振荡器

10 = 带 1.125 ms DRT 的 INTOSC

11 = 带 1.125 ms DRT 的 EXTRC

注 1: 请参见 “PIC12F510 Memory Programming Specification”( DS41257)和 “PIC16F506

2: 应用设计人员负责确保使用 1.125 ms(标称值) DRT 时可实现正确的操作。请参见电气规范了

引脚功能为 MCLR

(1),(2)

(1),(2)

Memory Programming Specification”(DS41258)确定访问配置字的方法。

解该工作模式下对 V

DD 上升时间和稳定性的要求。

IOSCFS MCLRE CP

WDTE FOSC1 FOSC0

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 10 = 清零 x = 未知

DS41268A_CN 第 56 页 初稿 2006 Microchip Technology Inc.

寄存器 10-2: 配置字——PIC16F506

PIC12F510/16F506

- - - - -

bit 11 bit 0

bit 11-7

bit 6

bit 5

bit 4

bit 3

bit 2-0

未用:读为 1

IOSCFS:内部振荡器频率选择位

1 = 8 MHz INTOSC 速率

0 = 4 MHz INTOSC 速率

MCLRE:主复位使能位

1 = RB3/MCLR

0 = RB3/MCLR 用作 RB3, MCLR 内部连接到 VDD

CP

:代码保护位

1 = 代码保护关闭

0 = 代码保护打开

WDTE:看门狗定时器使能位

1 = 使能 WDT

0 = 禁止 WDT

FOSC2:FOSC0:振荡器选择位

000 = 带 18 ms DRT 的 LP 振荡器

001 = 带 18 ms DRT 的 XT 振荡器

010 = 带 18 ms DRT 的 HS 振荡器

011 = RB4/OSC2/CLKOUT 用作 RB4 并带 1.125 ms DRT 的 EC 振荡器

100 = RB4/OSC2/CLKOUT 用作 RB4 并带 1.125 ms DRT 的 INTOSC 振荡器

101 = RB4/OSC2/CLKOUT 用作 RCLKOUT 并带 1.125 ms DRT 的 INTOSC 振荡器

110 = RB4/OSC2/CLKOUT 用作 RB4 并带 1.125 ms DRT 的 EXTRC 振荡器

111 = RB4/OSC2/CLKOUT 用作 RCLKOUT 并带 1.125 ms DRT 的 EXTRC 振荡器

引脚用作 MCLR

IOSCFS MCLRE CP

WDTE FOSC2 FOSC1 FOSC0

(1),(2)

(1),(2)

(1),(2)

(1),(2)

(1),(2)

注 1: 请参见 “PIC12F510 Memory Programming Specification”( DS41257)和 “PIC16F506

Memory Programming Specification”(DS41258)确定访问配置字的方法。

2: 应用设计人员负责确保使用 1.125 ms(标称值) DRT 时可实现正确的操作。请参见电气规范了

解该工作模式下对 V