Page 1

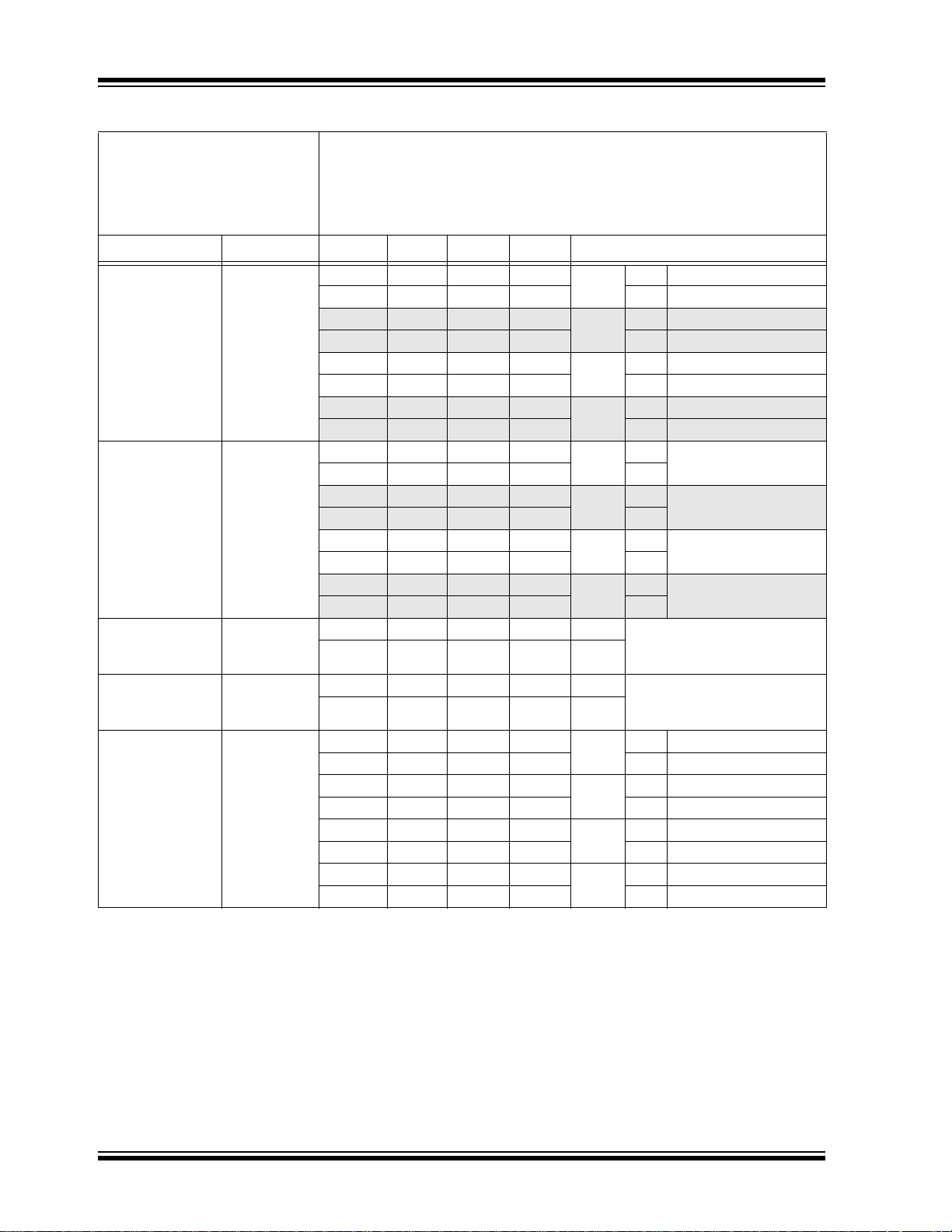

MCP414X/416X/424X/426X

1

2

3

4

5

6

7

8

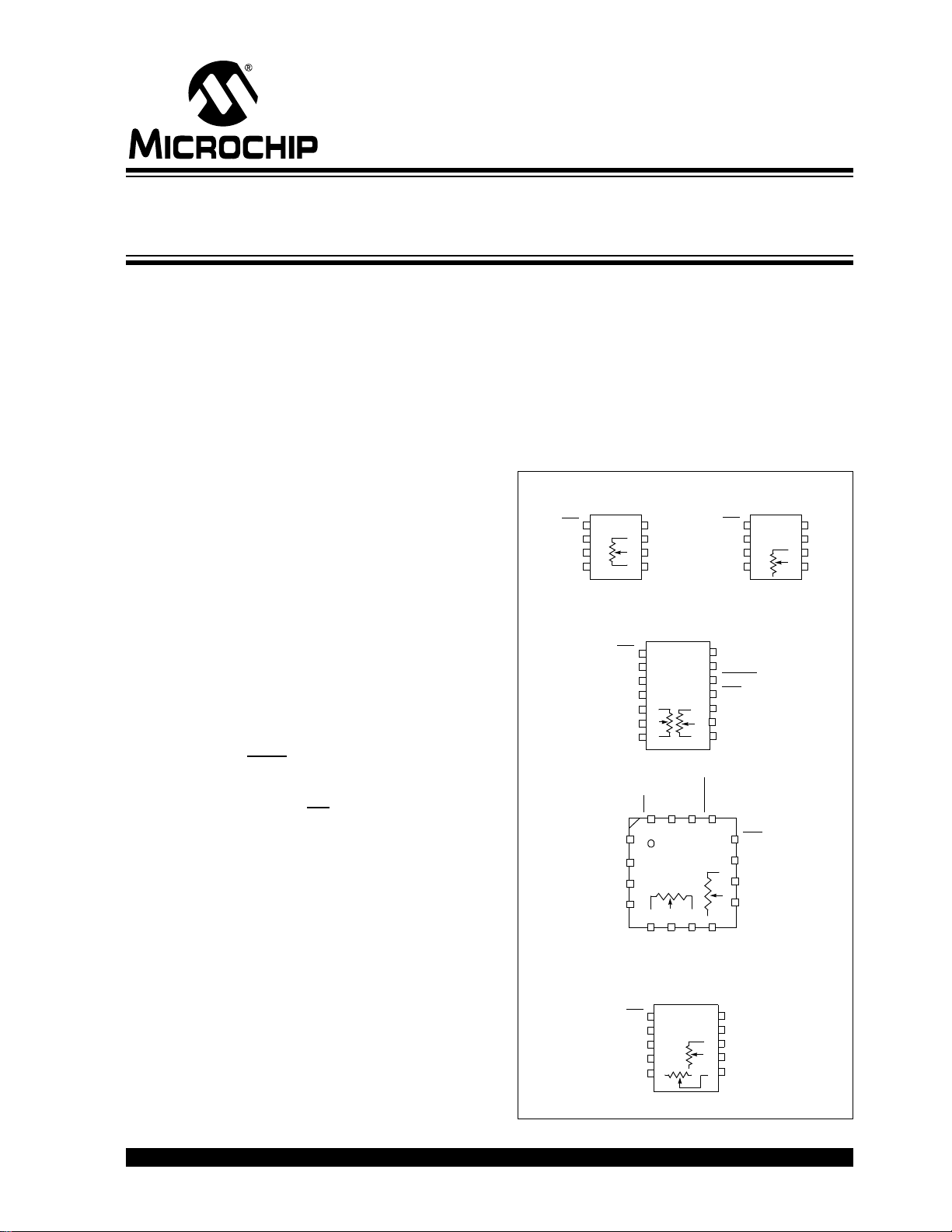

P0W

P0B

P0A

V

SS

V

DD

MCP41X1

Single Potentiometer

PDIP, SOIC, MSOP,

CS

SDI/SDO

SCK

1

2

3

4

5

6

7

8

P0B

SDO

P0W

V

DD

MCP41X2

Single Rheostat

PDIP, SOIC, MSOP,

1

2

3

4

11

12

13

14

SHDN

SDO

WP

V

DD

MCP42X1 Dual Potentiometers

PDIP, SOIC, TSSOP

5

6

7

8

9

10

P0W

P0B

P0A

P1A

P1W

P1B

V

SS

CS

SDI

SCK

V

SS

CS

SDI

SCK

1

2

3

4

11

12

13

14

SDO

SHDN

4x4 QFN

5

6

78

9

10

P0B

NC

P0W

P0A

P1A

P1W

V

SS

SCK

V

SS

SDI

15

16

P1B

V

DD

CS

WP

1

2

3

4

7

8

9

10

SDO

V

DD

MCP42X2 Dual Rheostat

MSOP, DFN

5

6

P0B

P0W

P1W

P1B

V

SS

CS

SDI

SCK

3x3 DFN

3x3 DFN

7/8-Bit Single/Dual SPI Digital POT with

Non-Volatile Memory

Features

• Single or Dual Resistor Network options

• Potentiometer or Rheostat configuration options

• Resistor Network Resolution

- 7-bit: 128 Resistors (129 Steps)

- 8-bit: 256 Resistors (257 Steps)

Resistances options of:

•R

AB

-5kΩ

-10kΩ

-50kΩ

- 100 kΩ

Description

The MCP41XX and MCP42XX devices offer a wide

range of product offerings using an SPI interface. This

family of devices support 7-bit and 8-bit resistor

networks, Non-Volatile memory configurations, and

Potentiometer and Rheostat pinouts.

WiperLock Technology allows application-specific

calibration settings to be secured in the EEPROM.

Package Types

• Zero-Scale to Full-Scale Wiper operation

• Low Wiper Resistance: 75Ω (typ.)

• Low Tempco:

- Absolute (Rheostat): 50 ppm typical

(0°C to 70°C)

- Ratiometric (Potentiometer): 15 ppm typical

• Non-volatile Memory

- Automatic Recall of Saved Wiper Setting

- WiperLock™ Technology

• SPI serial interface (10 Mhz, modes 0,0 & 1,1)

- High-Speed Read/Writes to wiper registers

- Read/Write to Data EEPROM registers

- Serially enabled EEPROM write protect

- SDI/SDO multiplexing (MCP41X1 only)

• Resistor Network Terminal Disconnect Feature

via:

- Shutdown pin (SHDN

- Terminal Control (TCON) Register

• Write Protect Feature:

- Hardware Write Protect (WP

- Software Write Protect (WP) Configuration bit

• Brown-out reset protection (1.5V typical)

)

) Control pin

• Serial Interface Inactive current (2.5 uA typ.)

• High-Voltage Tolerant Digital Inputs: Up to 12.5V

• Supports Split Rail Applications

• Internal weak pull-up on all digital inputs

Specified

• Wide Operating Voltage:

- 2.7V to 5.5V - Device Characteristics

- 1.8V to 5.5V - Device Operation

• Wide Bandwidth (-3dB) Operation:

- 2 MHz (typ.) for 5.0 kΩ device

• Extended temperature range (-40°C to +125°C)

© 2007 Microchip Technology Inc. DS22059A-page 1

Page 2

MCP414X/416X/424X/426X

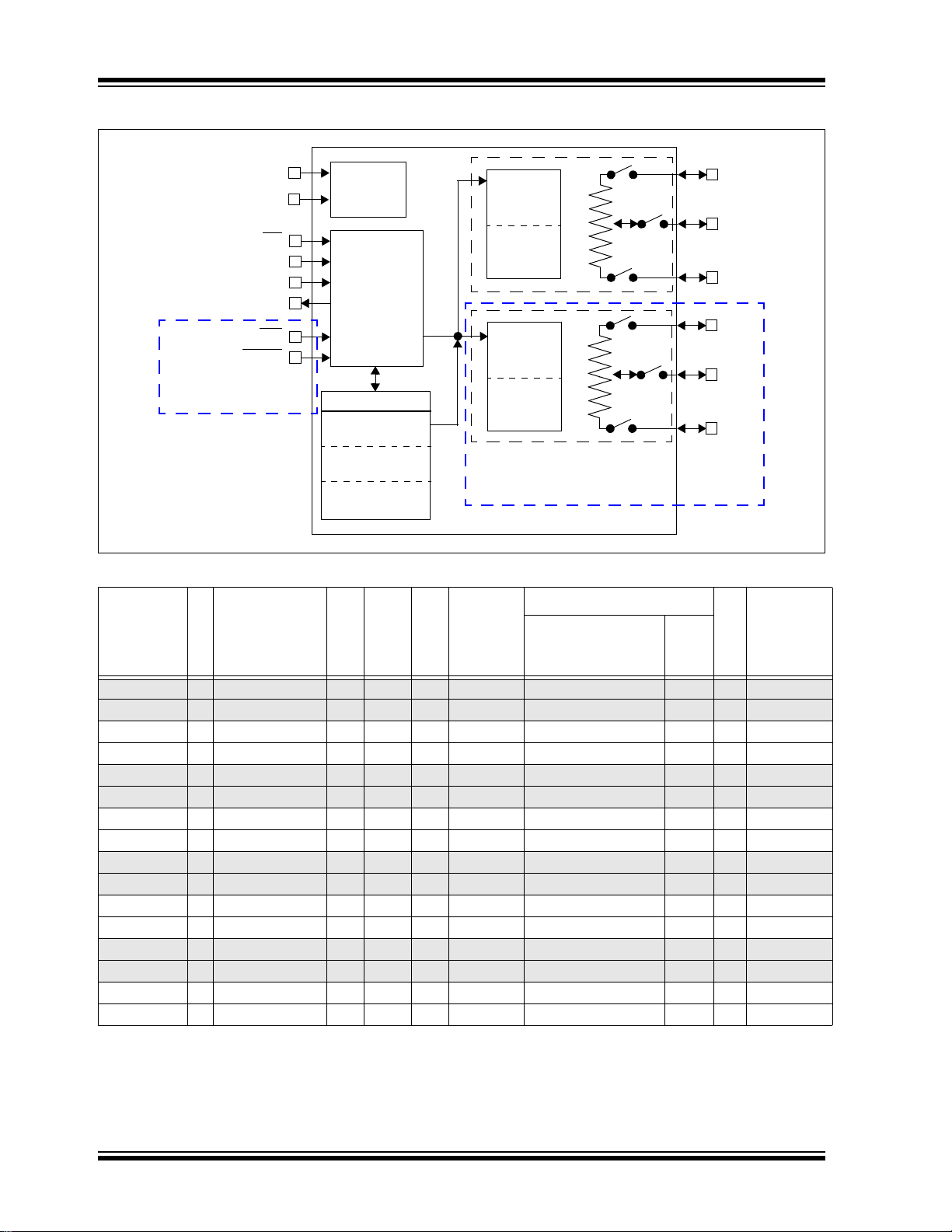

Power-up/

Brown-out

Control

VDD

V

SS

SPI Serial

Interface

Module &

Control

Logic

(WiperLock™

Technology)

Resistor

Network 0

(Pot 0)

Wiper 0

& TCON

Register

Resistor

Network 1

(Pot 1)

Wiper 1

& TCON

Register

CS

SCK

SDI

SDO

WP

SHDN

Memory (16x9)

Wiper0 (V & NV)

Wiper1 (V & NV)

TCON

STATUS

Data EEPROM

(10 x 9-bits)

P0A

P0W

P0B

P1A

P1W

P1B

For Dual Resistor Network

Devices Only

For Dual Potentiometer

Devices Only

Device Block Diagram

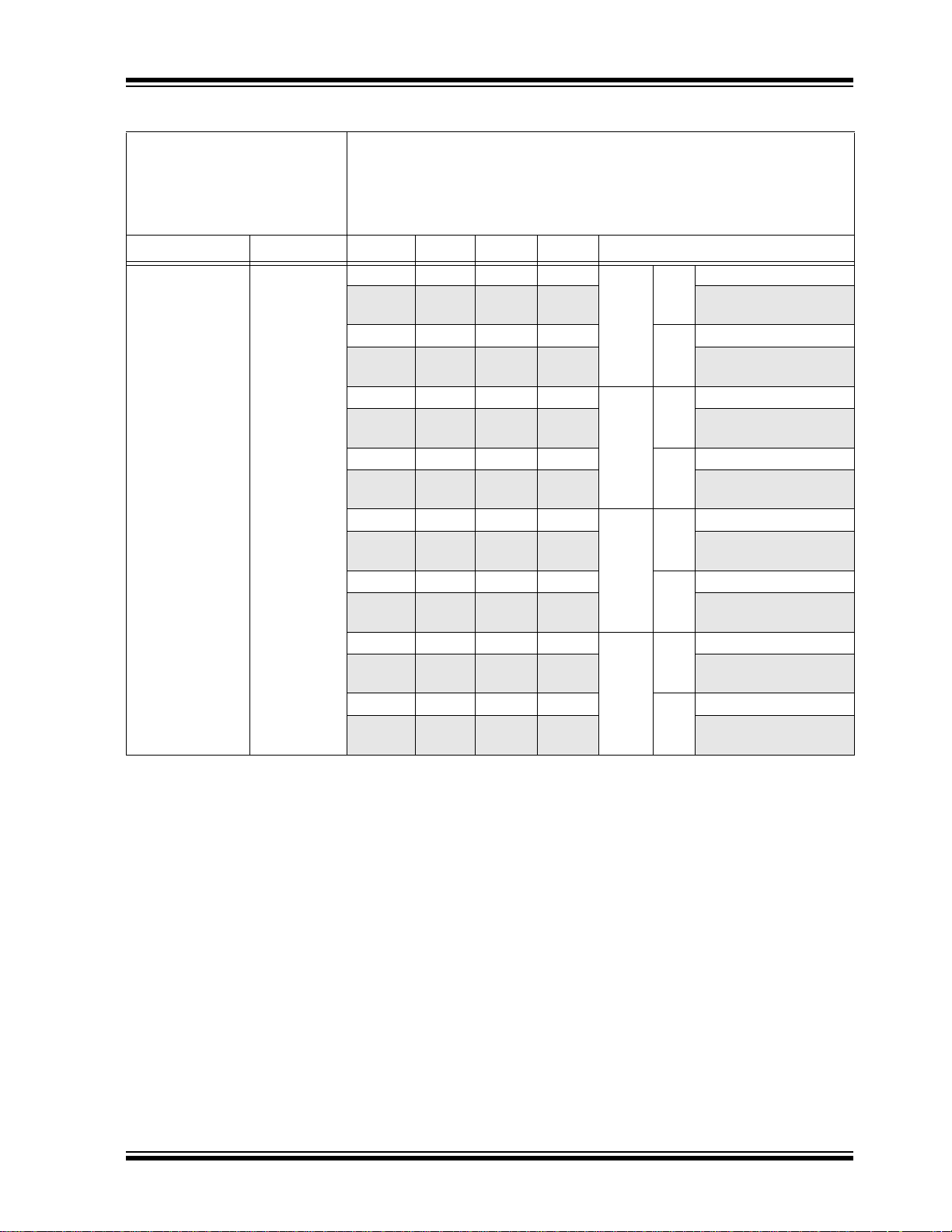

Device Features

Resistance (typical)

Device

MCP4131

MCP4132

(3)

1 Potentiometer

(3)

1 Rheostat SPI RAM No Mid-Scale 5.0, 10.0, 50.0, 100.0 75 129 1.8V to 5.5V

MCP4141 1 Potentiometer

Wiper

Configuration

# of POTs

Type

Memory

Control

Interface

(1)

SPI RAM No Mid-Scale 5.0, 10.0, 50.0, 100.0 75 129 1.8V to 5.5V

(1)

SPI EE Yes NV Wiper 5.0, 10.0, 50.0, 100.0 75 129 2.7V to 5.5V

WiperLock

Technology

POR Wiper

R

Setting

Options (kΩ)

AB

MCP4142 1 Rheostat SPI EE Yes NV Wiper 5.0, 10.0, 50.0, 100.0 75 129 2.7V to 5.5V

MCP4151

MCP4152

(3)

1 Potentiometer

(3)

1 Rheostat SPI RAM No Mid-Scale 5.0, 10.0, 50.0, 100.0 75 257 1.8V to 5.5V

MCP4161 1 Potentiometer

MCP4162 1 Rheostat SPI EE Yes NV Wiper 5.0, 10.0, 50.0, 100.0 75 257 2.7V to 5.5V

MCP4231

MCP4232

(3)

2 Potentiometer

(3)

2 Rheostat SPI RAM No Mid-Scale 5.0, 10.0, 50.0, 100.0 75 129 1.8V to 5.5V

MCP4241 2 Potentiometer

MCP4242 2 Rheostat SPI EE Yes NV Wiper 5.0, 10.0, 50.0, 100.0 75 129 2.7V to 5.5V

MCP4251

MCP4252

MCP4261 2 Potentiometer

MCP4262 2 Rheostat SPI EE Yes NV Wiper 5.0, 10.0, 50.0, 100.0 75 257 2.7V to 5.5V

Note 1: Floating either terminal (A or B) allows the device to be used as a Rheostat (variable resistor).

(3)

2 Potentiometer

(3)

2 Rheostat SPI RAM No Mid-Scale 5.0, 10.0, 50.0, 100.0 75 257 1.8V to 5.5V

2: Analog characteristics only tested from 2.7V to 5.5V unless otherwise noted.

3: Please check Microchip web site for device release and availability

(1)

SPI RAM No Mid-Scale 5.0, 10.0, 50.0, 100.0 75 257 1.8V to 5.5V

(1)

SPI EE Yes NV Wiper 5.0, 10.0, 50.0, 100.0 75 257 2.7V to 5.5V

(1)

SPI RAM No Mid-Scale 5.0, 10.0, 50.0, 100.0 75 129 1.8V to 5.5V

(1)

SPI EE Yes NV Wiper 5.0, 10.0, 50.0, 100.0 75 129 2.7V to 5.5V

(1)

SPI RAM No Mid-Scale 5.0, 10.0, 50.0, 100.0 75 257 1.8V to 5.5V

(1)

SPI EE Yes NV Wiper 5.0, 10.0, 50.0, 100.0 75 257 2.7V to 5.5V

DS22059A-page 2 © 2007 Microchip Technology Inc.

Wiper

- RW

(Ω)

# of Steps

VDD

Operating

Range

(2)

Page 3

MCP414X/416X/424X/426X

1.0 ELECTRICAL CHARACTERISTICS

Absolute Maximum Ratings †

Voltage on VDD with respect to VSS............... -0.6V to +7.0V

Voltage on CS

SHDN

Voltage on all other pins (PxA, PxW, PxB, and

SDO) with respect to V

Input clamp current, I

(V

< 0, VI > VDD, VI > VPP ON HV pins)......................±20 mA

I

Output clamp current, I

(V

< 0 or VO > VDD) ..................................................±20 mA

O

Maximum output current sunk by any Output pin

......................................................................................25mA

Maximum output current sourced by any Output pin

......................................................................................25mA

Maximum current out of V

Maximum current into V

Maximum current into P

Storage temperature ....................................-65°C to +150°C

Ambient temperature with power applied

-40°C to +125°C

Total power dissipation (Note 1)................................400 mW

Soldering temperature of leads (10 seconds).............+300°C

ESD protection on all pins ..................................≥ 4 kV (HBM),

.......................................................................... ≥ 300V (MM)

Maximum Junction Temperature (T

Note 1: Power dissipation is calculated as follows:

, SCK, SDI, SDI/SDO, WP, and

with respect to VSS

......................................

SS ............................

IK

OK

SS

pin....................................100 mA

DD

XA, PXW & PXB pins ............±2.5 mA

Pdis = VDD x {IDD - ∑ IOH} + ∑ {(VDD-VOH) x IOH} + ∑(VOl x IOL)

-0.6V to 12.5V

-0.3V to VDD + 0.3V

pin.................................100 mA

) ......................... +150°C

J

† Notice: Stresses above those listed under “Maximum

Ratings” may cause permanent damage to the device. This is

a stress rating only and functional operation of the device at

those or any other conditions above those indicated in the

operational listings of this specification is not implied.

Exposure to maximum rating conditions for extended periods

may affect device reliability.

© 2007 Microchip Technology Inc. DS22059A-page 3

Page 4

MCP414X/416X/424X/426X

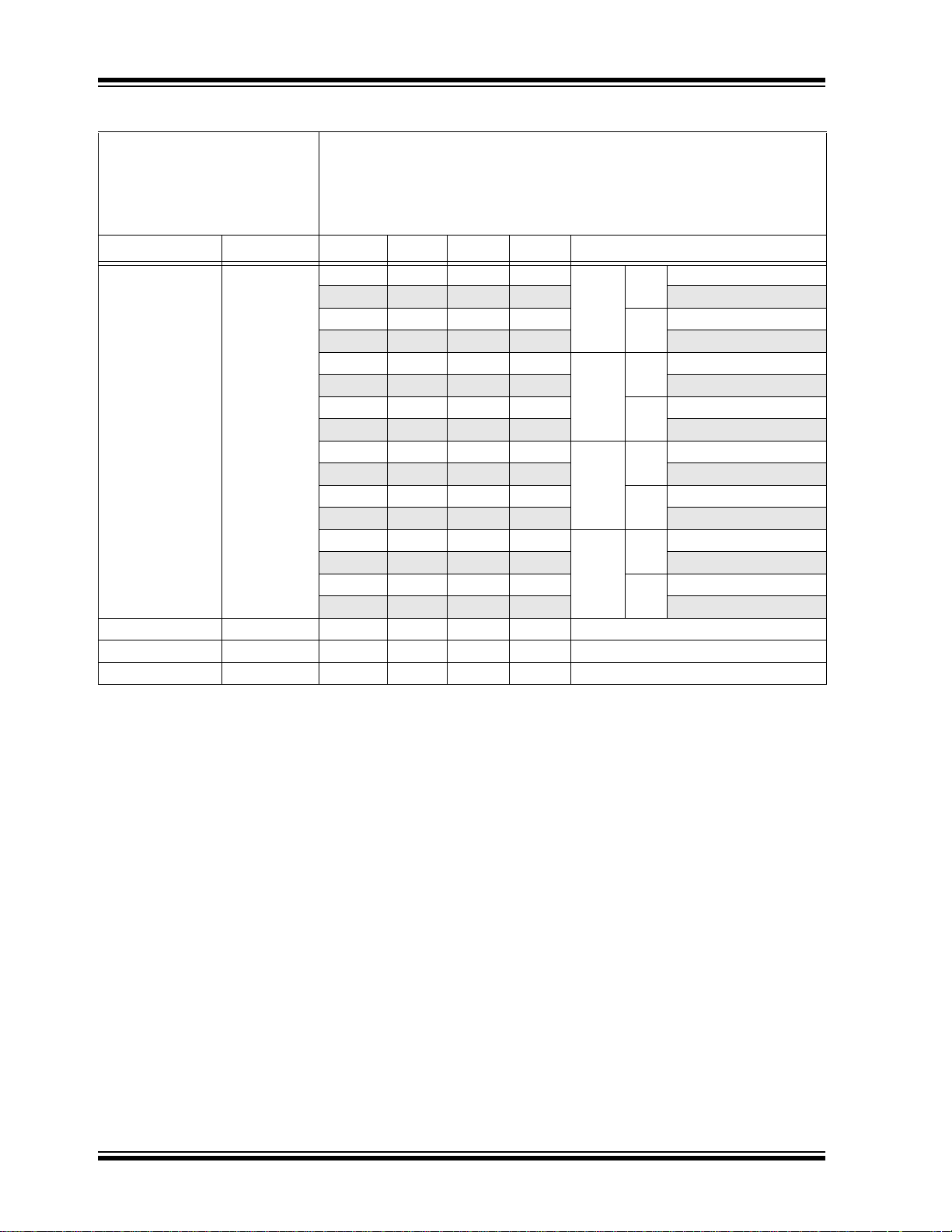

AC/DC CHARACTERISTICS

Standard Operating Conditions (unless otherwise specified)

Operating Temperature –40°C ≤ TA ≤ +125°C (extended)

DC Characteristics

Parameters Sym Min Typ Max Unit s Conditions

Supply Voltage V

, SDI, SDO,

CS

DD

VHV V

SCK, WP, SHDN

pin Voltage Range

DD Start Voltage

V

V

BOR

to ensure Wiper

Reset

DD Rise Rate to

V

V

DDRR

ensure Power-on

Reset

Delay after device

T

BORD

exits the reset

state

(VDD > V

Supply Current

BOR

)

I

DD

(Note 10)

Note 1: Resistance is defined as the resistance between te rminal A to terminal B.

2: INL and DNL are measured at V

3: MCP4XX1 only.

4: MCP4XX2 only, inclu des V

5: Resistor terminals A, W and B’s polarity with respect to each other is not restricted.

6: This specification by design.

7: Non-linearity is affected by wiper resistance (R

temperature.

8: The MCP4XX1 is externally connected to match the configurations of the MCP41X2 and MCP42X2, and

then tested.

9: POR/BOR is not rate dependent.

10: Supply current is independent of current through the resistor network

All parameters apply across the specified operating ranges unless noted.

= +2.7V to 5.5V, 5 kΩ, 10 kΩ, 50 kΩ, 100 kΩ devices.

V

DD

Typical specifications represent values for VDD = 5.5V, TA = +25°C.

2.7 — 5.5 V

1.8 — 2.7 V Serial Interface only.

— 12.5V V VDD ≥

SS

VSS —VDD +

VVDD <

8.0V

4.5V

4.5V

The CS pin will be at one

of three input levels

(VIL, VIH or V

IHH

— — 1.65 V RAM retention voltage (V

(Note 9)V/ms

—1020µS

— — 450 µA Serial Interface Active,

VDD = 5.5V, CS = VIL, SCK @ 5 MHz,

write all

0’s to volatile Wiper 0 (address

0h)

— — 1 mA EE Write Current,

= 5.5V, CS = VIL, SCK @ 5 MHz,

V

DD

write all 0’s to non-volatile Wiper 0

(address 2h)

— 2.5 5 µA Serial Interface Inactive,

= VIH, VDD = 5.5V

CS

— 0.55 1 mA Serial Interface Active,

= 5.5V, CS = V

V

DD

IHH

,

SCK @ 5 MHz,

decrement non-volatile Wiper 0

(address 2h)

with VA = VDD and VB = VSS.

WZSE

W

and V

WFSE

.

), which changes significantly over voltage and

W

). (Note 6)

) < V

RAM

BOR

DS22059A-page 4 © 2007 Microchip Technology Inc.

Page 5

MCP414X/416X/424X/426X

AC/DC CHARACTERISTICS (CONTINUED)

Standard Operating Conditions (unless otherwise specified)

Operating Temperature –40°C ≤ T

DC Characteristics

All parameters apply across the specified operating ranges unless noted.

= +2.7V to 5.5V, 5 kΩ, 10 kΩ, 50 kΩ, 100 kΩ devices.

V

DD

Typical specifications represent values for V

Parameters Sym Min Typ Max Unit s Conditions

Resistance

(± 20%)

R

AB

4.0 5 6.0 kΩ -502 devices (Note 1)

8.0 10 12.0 kΩ -103 devices (Note 1)

40.0 50 60.0 kΩ -503 devices (Note 1)

80.0 100 120.0 kΩ -104 devices (Note 1)

Resolution N 257 Taps 8-bit No Missing Codes

129 Taps 7-bit No Missing Codes

Step Resistance R

—RAB /

S

— Ω 8-bit Note 6

(256)

—R

AB

/

— Ω 7-bit Note 6

(128)

- R

|

Nominal

Resistance Match

Wiper Resistance

(Note 3, Note 4)

Nominal

Resistance

Tempco

Ratiometeric

|R

AB0

AB1

/ RAB

|R

- R

BW0

BW1

/ R

BW

R

W

ΔRAB/ΔT — 50 — ppm/°C TA = -20°C to +70°C

/ΔT — 15 — ppm/°C Code = Midscale (80h or 40h)

ΔV

WB

— 0.2 1.25 % MCP42X1 devices only

—0.251.5%MCP42X2 devices only,

|

— 75 160 Ω VDD = 5.5 V, IW = 2.0 mA, code = 00h

— 75 300 Ω V

— 100 — ppm/°C T

— 150 — ppm/°C TA = -40°C to +125°C

Tempco

Resistor Terminal

V

A,VW,VB

Vss — V

DD

Input Voltage

Range (Terminals

A, B and W)

Maximum current

I

W

——2.5mANote 6, Worst case current through

through A, W or B

Leakage current

into A, W or B

I

WL

—100—nAMCP4XX1 PxA = PxW = PxB = V

—100—nAMCP4XX2 PxB = PxW = VSS

Note 1: Resistance is defined as the resistance between terminal A to terminal B.

2: INL and DNL are measured at V

with VA = VDD and VB = VSS.

W

3: MCP4XX1 only.

4: MCP4XX2 only, inclu des V

WZSE

and V

WFSE

.

5: Resistor terminals A, W and B’s polarity with respect to each other is not restricted.

6: This specification by design.

7: Non-linearity is affected by wiper resistance (R

), which changes significantly over voltage and

W

temperature.

8: The MCP4XX1 is externally connected to match the configurations of the MCP41X2 and MCP42X2, and

then tested.

9: POR/BOR is not rate dependent.

10: Supply current is independent of current through the resistor network

≤ +125°C (extended)

A

= 5.5V, TA = +25°C.

DD

Code = Full-Scale

= 2.7 V, IW = 2.0 mA, code = 00h

DD

= -40°C to +85°C

A

V Note 5, Note 6

wiper when wiper is either Full Scale or

Zero Scale.

SS

© 2007 Microchip Technology Inc. DS22059A-page 5

Page 6

MCP414X/416X/424X/426X

AC/DC CHARACTERISTICS (CONTINUED)

Standard Operating Conditions (unless otherwise specified)

Operating Temperature –40°C ≤ T

DC Characteristics

All parameters apply across the specified operating ranges unless noted.

= +2.7V to 5.5V, 5 kΩ, 10 kΩ, 50 kΩ, 100 kΩ devices.

V

DD

Typical specifications represent values for V

Parameters Sym Min Typ Max Units Conditions

Full-Scale Error

(MCP4XX1 only)

(8-bit code =

100h,

7-bit code = 80h)

V

WFSE

-6.0 -0.1 — LSb 5 kΩ 8-bit 3.0V ≤ VDD ≤ 5.5V

-4.0 -0.1 — LSb 7-bit 3.0V ≤ VDD ≤ 5.5V

-3.5 -0.1 — LSb 10 kΩ 8-bit 3.0V ≤ VDD ≤ 5.5V

-2.0 -0.1 — LSb 7-bit 3.0V ≤ VDD ≤ 5.5V

-0.8 -0.1 — LSb 50 kΩ 8-bit 3.0V ≤ V

-0.5 -0.1 — LSb 7-bit 3.0V ≤ VDD ≤ 5.5V

-0.5 -0.1 — LSb 100 kΩ 8-bit 3.0V ≤ VDD ≤ 5.5V

-0.5 -0.1 — LSb 7-bit 3.0V ≤ VDD ≤ 5.5V

Zero-Scale Error

(MCP4XX1 only)

(8-bit code = 00h,

7-bit code = 00h)

V

WZSE

—+0.1+6.0LSb5kΩ 8-bit 3.0V ≤ VDD ≤ 5.5V

— +0.1 +3.0 LSb 7-bit

— +0.1 +3.5 LSb 10 kΩ 8-bit 3.0V ≤ VDD ≤ 5.5V

— +0.1 +2.0 LSb 7-bit

— +0.1 +0.8 LSb 50 kΩ 8-bit 3.0V ≤ V

— +0.1 +0.5 LSb 7-bit

— +0.1 +0.5 LSb 100kΩ 8-bit 3.0V ≤ VDD ≤ 5.5V

— +0.1 +0.5 LSb 7-bit

Potentiometer

Integral

Non-linearity

Potentiometer

Differential

Non-linearity

Bandwidth -3 dB

(See Figure 2-58,

load = 30 pF)

INL -1 ±0.5 +1 LSb 8-bit 3.0V ≤ V

-0.5 ±0.25 +0.5 LSb 7-bit

DNL -0.5 ±0.25 +0.5 LSb 8-bit 3.0V ≤ V

-0.25 ±0.125 +0.25 LSb 7-bit

BW — 2 — MHz 5 kΩ 8-bit Code = 80h

— 2 — MHz 7-bit Code = 40h

—1—MHz10kΩ 8-bit Code = 80h

— 1 — MHz 7-bit Code = 40h

—200—kHz50kΩ 8-bit Code = 80h

— 200 — kHz 7-bit Code = 40h

—100—kHz100kΩ 8-bit Code = 80h

— 100 — kHz 7-bit Code = 40h

Note 1: Resistance is defined as the resistance between terminal A to terminal B.

2: INL and DNL are measured at V

with VA = VDD and VB = VSS.

W

3: MCP4XX1 only.

4: MCP4XX2 only, includes V

WZSE

and V

WFSE

.

5: Resistor terminals A, W and B’s polarity with respect to each other is not restricted.

6: This specification by design.

7: Non-linearity is affected by wiper resistance (R

), which changes significantly over voltage and

W

temperature.

8: The MCP4XX1 is externally connected to match the configura tions of the MCP41X2 and MCP42X2, and

then tested.

9: POR/BOR is not rate dependent.

10: Supply current is independent of current through the resistor network

≤ +125°C (extended)

A

= 5.5V, TA = +25°C.

DD

MCP4XX1 devices only

(Note 2)

MCP4XX1 devices only

(Note 2)

≤ 5.5V

DD

≤ 5.5V

DD

DD

DD

≤ 5.5V

≤ 5.5V

DS22059A-page 6 © 2007 Microchip Technology Inc.

Page 7

MCP414X/416X/424X/426X

AC/DC CHARACTERISTICS (CONTINUED)

Standard Operating Conditions (unless otherwise specified)

Operating Temperature –40°C ≤ T

DC Characteristics

All parameters apply across the specified operating ranges unless noted.

= +2.7V to 5.5V, 5 kΩ, 10 kΩ, 50 kΩ, 100 kΩ devices.

V

DD

Typical specifications represent values for V

Parameters Sym Min Typ Max Units Conditions

Rheostat Integral

Non-linearity

MCP41X1

(Note 4, Note 8)

MCP4XX2

devices only

R-INL -1.5 ±0.5 +1.5 LSb 5 kΩ 8-bit 5.5V, I

-8.25 +4.5 +8.25 LSb 3.0V, IW = 480 µA

-1.125 ±0.5 +1.125 LSb 7-bit 5.5V, I

-6.0 +4.5 +6.0 LSb 3.0V, IW = 480 µA

(Note 4)

-1.5 ±0.5 +1.5 LSb 10 kΩ 8-bit 5.5V, I

-5.5 +2.5 +5.5 LSb 3.0V, IW = 240 µA

-1.125 ±0.5 +1.125 LSb 7-bit 5.5V, I

-4.0 +2.5 +4.0 LSb 3.0V, IW = 240 µA

-1.5 ±0.5 +1.5 LSb 50 kΩ 8-bit 5.5V, I

-2.0 +1 +2.0 LSb 3.0V, IW = 48 µA

-1.125 ±0.5 +1.125 LSb 7-bit 5.5V, I

-1.5 +1 +1.5 LSb 3.0V, IW = 48 µA

-1.0 ±0.5 +1.0 LSb 100 kΩ 8-bit 5.5V, I

-1.5 +0.25 +1.5 LSb 3.0V, IW = 24 µA

-0.8 ±0.5 +0.8 LSb 7-bit 5.5V, IW = 45 µA

-1.125 +0.25 +1.125 LSb 3.0V, IW = 24 µA

Note 1: Resistance is defined as the resistance between terminal A to terminal B.

2: INL and DNL are measured at V

with VA = VDD and VB = VSS.

W

3: MCP4XX1 only.

4: MCP4XX2 only, includes V

WZSE

and V

WFSE

.

5: Resistor terminals A, W and B’s polarity with respect to each other is not restricted.

6: This specification by design.

7: Non-linearity is affected by wiper resistance (R

), which changes significantly over voltage and

W

temperature.

8: The MCP4XX1 is externally connected to match the configura tions of the MCP41X2 and MCP42X2, and

then tested.

9: POR/BOR is not rate dependent.

10: Supply current is independent of current through the resistor network

≤ +125°C (extended)

A

= 5.5V, TA = +25°C.

DD

W

(Note 7)

W

(Note 7)

W

(Note 7)

W

(Note 7)

W

(Note 7)

W

(Note 7)

W

(Note 7)

(Note 7)

= 900 µA

= 900 µA

= 450 µA

= 450 µA

= 90 µA

= 90 µA

= 45 µA

© 2007 Microchip Technology Inc. DS22059A-page 7

Page 8

MCP414X/416X/424X/426X

AC/DC CHARACTERISTICS (CONTINUED)

Standard Operating Conditions (unless otherwise specified)

Operating Temperature –40°C ≤ T

DC Characteristics

All parameters apply across the specified operating ranges unless noted.

= +2.7V to 5.5V, 5 kΩ, 10 kΩ, 50 kΩ, 100 kΩ devices.

V

DD

Typical specifications represent values for V

Parameters Sym Min Typ Max Units Conditions

Rheostat

Differential

Non-linearity

MCP41X1

(Note 4, Note 8)

MCP4XX2

devices only

(Note 4)

R-DNL -0.5 ±0.25 +0.5 LSb 5 kΩ 8-bit 5.5V, I

-1.0 +0.5 +1.0 LSb 3.0V (Note 7)

-0.375 ±0.25 +0.375 LSb 7-bit 5.5V, I

-0.75 +0.5 +0.75 LSb 3.0V (Note 7)

-0.5 ±0.25 +0.5 LSb 10 kΩ 8-bit 5.5V, I

-1.0 +0.25 +1.0 LSb 3.0V (Note 7)

-0.375 ±0.25 +0.375 LSb 7-bit 5.5V, I

-0.75 +0.5 +0.75 LSb 3.0V (Note 7)

-0.5 ±0.25 +0.5 LSb 50 kΩ 8-bit 5.5V, I

-0.5 ±0.25 +0.5 LSb 3.0V (Note 7)

-0.375 ±0.25 +0.375 LSb 7-bit 5.5V, I

-0.375 ±0.25 +0.375 LSb 3.0V (Note 7)

-0.5 ±0.25 +0.5 LSb 100kΩ 8-bit 5.5V, I

-0.5 ±0.25 +0.5 LSb 3.0V (Note 7)

-0.375 ±0.25 +0.375 LSb 7-bit 5.5V, I

-0.375 ±0.25 +0.375 LSb 3.0V (Note 7)

Capacitance (P

Capacitance (P

Capacitance (PB)C

)C

A

)CW— 120 — pF f =1 MHz, Code = Full-Scale

w

AW

BW

— 75 — pF f =1 MHz, Code = Full-Scale

— 75 — pF f =1 MHz, Code = Full-Scale

Note 1: Resistance is defined as the resistance between terminal A to terminal B.

2: INL and DNL are measured at V

with VA = VDD and VB = VSS.

W

3: MCP4XX1 only.

4: MCP4XX2 only, includes V

WZSE

and V

WFSE

.

5: Resistor terminals A, W and B’s polarity with respect to each other is not restricted.

6: This specification by design.

7: Non-linearity is affected by wiper resistance (R

), which changes significantly over voltage and

W

temperature.

8: The MCP4XX1 is externally connected to match the configura tions of the MCP41X2 and MCP42X2, and

then tested.

9: POR/BOR is not rate dependent.

10: Supply current is independent of current through the resistor network

≤ +125°C (extended)

A

= 5.5V, TA = +25°C.

DD

W

W

W

W

W

W

W

W

= 900 µA

= 900 µA

= 450 µA

= 450 µA

= 90 µA

= 90 µA

= 45 µA

= 45 µA

DS22059A-page 8 © 2007 Microchip Technology Inc.

Page 9

MCP414X/416X/424X/426X

AC/DC CHARACTERISTICS (CONTINUED)

Standard Operating Conditions (unless otherwise specified)

Operating Temperature –40°C ≤ T

DC Characteristics

All parameters apply across the specified operating ranges unless noted.

= +2.7V to 5.5V, 5 kΩ, 10 kΩ, 50 kΩ, 100 kΩ devices.

V

DD

Typical specifications represent values for V

Parameters Sym Min Typ Max Units Conditions

Digital Inputs/Outputs (CS, SDI, SDO, SCK, WP, SHDN)

Schmitt Trigger

V

IH

0.45 V

——V2.7V ≤ VDD ≤ 5.5V

DD

High Input

Threshold

——V1.8V ≤ VDD ≤ 2.7V

DD

Schmitt Trigger

0.5 V

DD

V

IL

— — 0.2V

Low Input

Threshold

Hysteresis of

V

HYS

—0.1VDD—V

Schmitt Trigger

Inputs

High Voltage Input

V

IHH

8.5 — 12.5

(6)

V Threshold for WiperLock™ Technolog y

Entry Voltage

High Voltage Input

Exit Voltage

High Voltage Limit V

Output Low

Voltage (SDO)

Output High

Voltage (SDO)

Weak Pull-up /

Pull-down Current

Pull-up /

CS

——V

V

IHH

MAX

V

V

OL

——12.5

—0.3VDD VIOL = 5 mA, VDD = 5.5V

SS

VSS —0.3VDD VIOL = 1 mA, VDD = 1.8V

0.7VDD —VDD VIOH = -2.5 mA, VDD = 5.5V

V

OH

0.7VDD —VDD VIOL = -1 mA, VDD = 1.8V

I

PU

— — 375 uA Internal VDD pull-up, V

—170—µACS pin, V

R

CS

—16—kΩ V

+

DD

(6)

0.8V

(6)

V Pin can tolerate V

Pull-down

Resistance

Input Leakage

I

IL

-1 — 1 µA VIN = VDD and VIN = VSS

Current

Pin Capacitance C

, C

IN

OUT

—10—pFf

RAM (Wiper) Value

Value Range N 0h — 1FFh hex 8-bit device

0h — 1FFh hex 7-bit device

Note 1: Resistance is defined as the resistance between terminal A to terminal B.

2: INL and DNL are measured at V

with VA = VDD and VB = VSS.

W

3: MCP4XX1 only.

4: MCP4XX2 only, includes V

WZSE

and V

WFSE

.

5: Resistor terminals A, W and B’s polarity with respect to each other is not restricted.

6: This specification by design.

7: Non-linearity is affected by wiper resistance (R

), which changes significantly over voltage and

W

temperature.

8: The MCP4XX1 is externally connected to match the configura tions of the MCP41X2 and MCP42X2, and

then tested.

9: POR/BOR is not rate dependent.

10: Supply current is independent of current through the resistor network

≤ +125°C (extended)

A

= 5.5V, TA = +25°C.

DD

(Allows 2.7V Digital V

5V Analog VDD)

V

V

= 5.5V, VCS = 3V

DD

= 20 MHz

C

DD

or less.

MAX

= 5.5V, VCS = 3V

DD

IHH

with

pull-down

© 2007 Microchip Technology Inc. DS22059A-page 9

Page 10

MCP414X/416X/424X/426X

AC/DC CHARACTERISTICS (CONTINUED)

Standard Operating Conditions (unless otherwise specified)

Operating Temperature –40°C ≤ T

DC Characteristics

All parameters apply across the specified operating ranges unless noted.

= +2.7V to 5.5V, 5 kΩ, 10 kΩ, 50 kΩ, 100 kΩ devices.

V

DD

Typical specifications represent values for V

Parameters Sym Min Typ Max Units Conditions

EEPROM

Endurance E

ndurance

— 1M — Cycles

EEPROM Range N 0h — 1FFh hex

Initial Factory

Setting

EEPROM Pro-

N 80h hex 8-bit WiperLock Technology = Off

40h hex 7-bit WiperLock Technology = Off

—510ms

t

WC

gramming Write

Cycle Time

Power Requirements

Power Supply

PSS — 0.0015 0.0035 %/% 8-bit V

Sensitivity

(MCP41X2 and

MCP42X2 only)

— 0.0015 0.0035 %/% 7-bit V

Note 1: Resistance is defined as the resistance between terminal A to terminal B.

2: INL and DNL are measured at V

with VA = VDD and VB = VSS.

W

3: MCP4XX1 only.

4: MCP4XX2 only, includes V

WZSE

and V

WFSE

.

5: Resistor terminals A, W and B’s polarity with respect to each other is not restricted.

6: This specification by design.

7: Non-linearity is affected by wiper resistance (R

), which changes significantly over voltage and

W

temperature.

8: The MCP4XX1 is externally connected to match the configura tions of the MCP41X2 and MCP42X2, and

then tested.

9: POR/BOR is not rate dependent.

10: Supply current is independent of current through the resistor network

≤ +125°C (extended)

A

= 5.5V, TA = +25°C.

DD

= 2.7V to 5.5V,

DD

VA = 2.7V, Code = 80h

= 2.7V to 5.5V,

DD

VA = 2.7V, Code = 40h

DS22059A-page 10 © 2007 Microchip Technology Inc.

Page 11

MCP414X/416X/424X/426X

CS

SCK

SDO

SDI

70

71

72

73

74

75, 76

77

78

79

80

SDI

MSb LSb

BIT6 - - - - - -1

MSb IN BIT6 - - - -1 LSb IN

83

84

V

IH

V

IL

V

IHH

V

IH

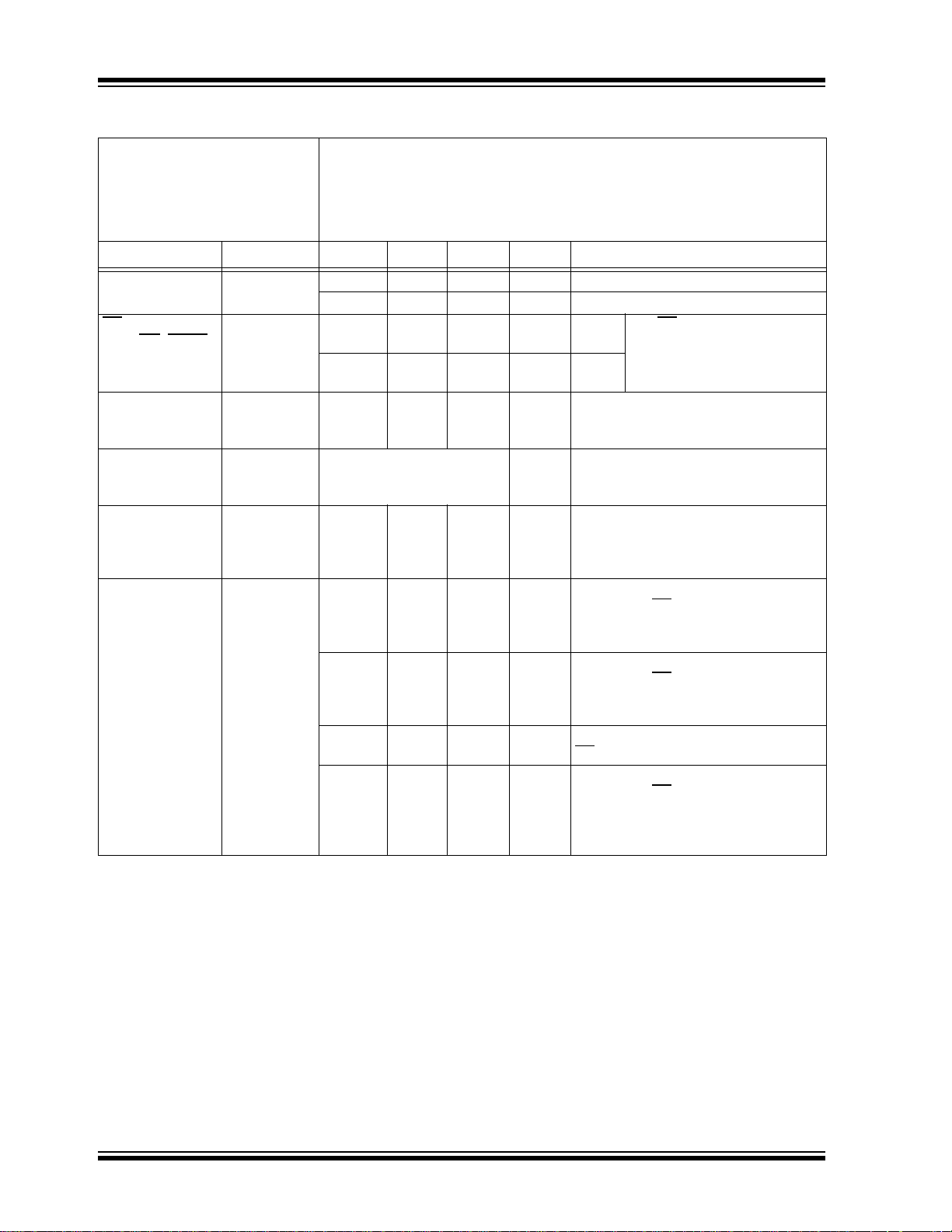

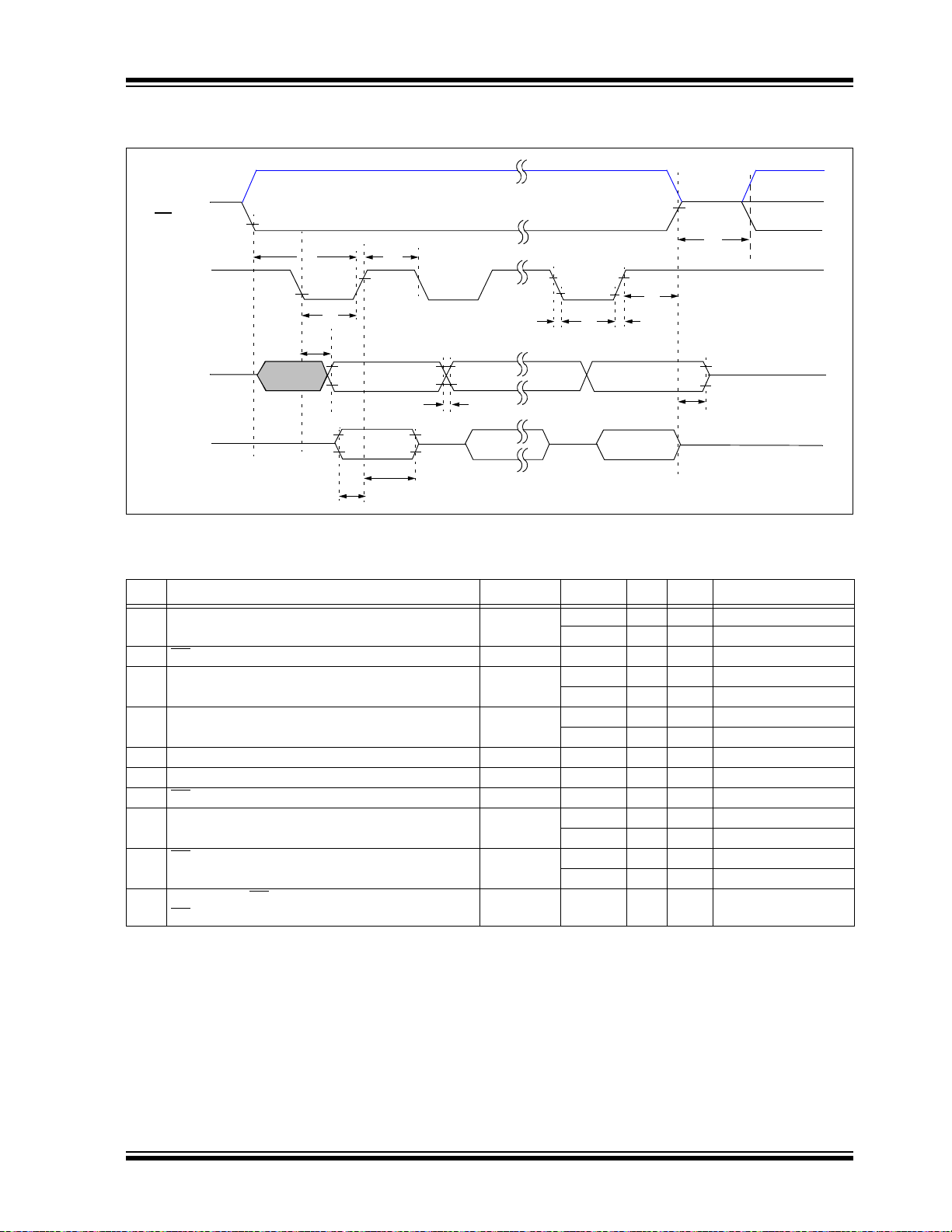

1.1 SPI Mode Timing Waveforms and Requirements

FIGURE 1-1: SPI Timing Waveform (Mode = 11).

TABLE 1-1: SPI REQUIREMENTS (MODE =

# Characteristic Symbol Min Max Units Conditions

SCK Input Frequency F

70 CS

Active (VIL or V

71 SCK input high time TscH 45 — ns VDD = 2.7V to 5.5V

72 SCK input low time TscL 45 — ns V

73 Setup time of SDI input to SCK↑ edge T

74 Hold time of SDI input from SCK↑ edge TscH2

77 CS Inactive (VIH) to SDO output hi-impedance TcsH2DOZ — 50 ns Note 1

80 SDO data output valid after SCK↓ edge TscL2

83 CS

84 Hold time of CS

Inactive (VIH) after SCK↑ edge TscH2csI 100 — ns VDD = 2.7V to 5.5V

CS Active (VIL or V

Note 1: This specification by design.

) to SCK↑ input TcsA2scH 60 — ns

IHH

Inactive (VIH) to

)

IHH

11)

—10MHzVDD = 2.7V to 5.5V

SCK

—1MHzV

500 — ns V

500 — ns VDD = 1.8V to 2.7V

DIV2scH 10 — ns

DIL20—ns

DOV — 70 ns V

1msV

TcsA2csI 50 — ns

170 ns V

DD

DD

DD

DD

DD

DD

= 1.8V to 2.7V

= 1.8V to 2.7V

= 2.7V to 5.5V

= 2.7V to 5.5V

= 1.8V to 2.7V

= 1.8V to 2.7V

© 2007 Microchip Technology Inc. DS22059A-page 11

Page 12

MCP414X/416X/424X/426X

CS

SCK

SDO

SDI

70

71 72

82

SDI

74

75, 76

MSb BIT6 - - - - - -1 LSb

77

MSb IN BIT6 - - - -1 LSb IN

80

83

84

73

V

IH

V

IL

V

IHH

V

IH

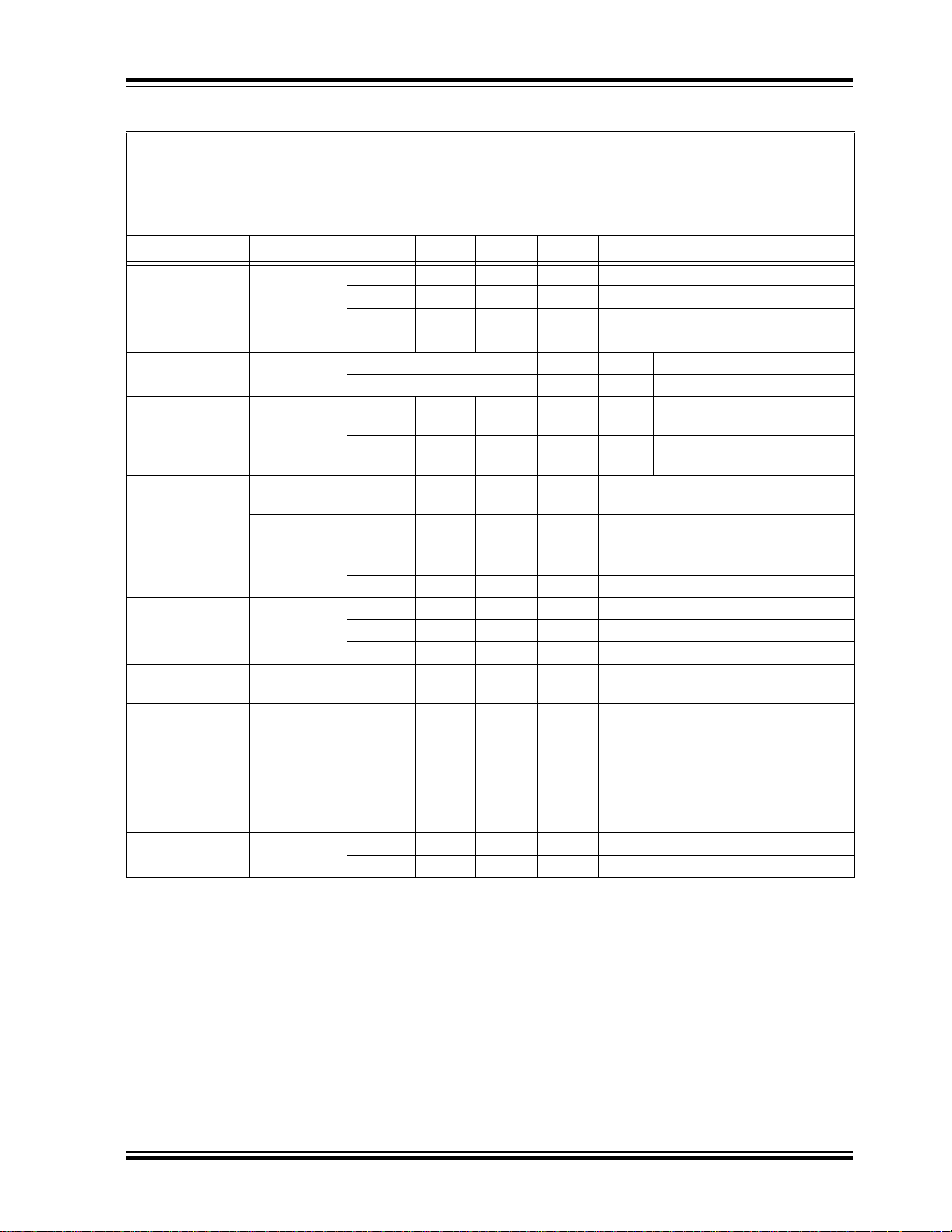

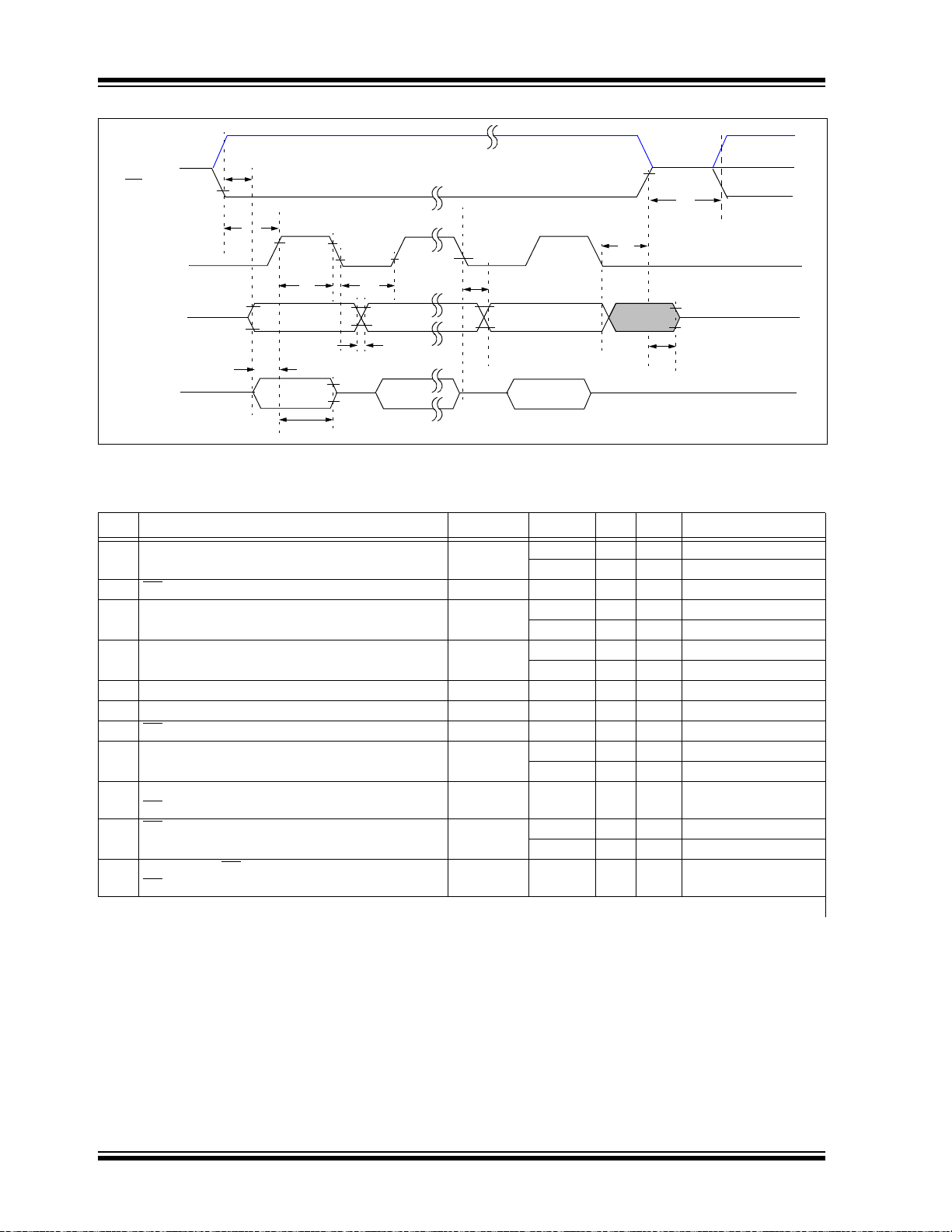

FIGURE 1-2: SPI Timing Waveform (Mode = 00).

TABLE 1-2: SPI REQUIREMENTS (MODE =

00)

# Characteristic Symbol Min Max Units Conditions

SCK Input Frequency F

—10MHzVDD = 2.7V to 5.5V

SCK

—1MHzVDD = 1.8V to 2.7V

70 CS

Active (VIL or V

71 SCK input high time TscH 45 — ns V

) to SCK↑ input TcsA2scH 60 — ns

IHH

= 2.7V to 5.5V

DD

500 — ns VDD = 1.8V to 2.7V

72 SCK input low time TscL 45 — ns V

500 — ns V

73 Setup time of SDI input to SCK↑ edge T

DIV2scH 10 — ns

= 2.7V to 5.5V

DD

= 1.8V to 2.7V

DD

74 Hold time of SDI input from SCK↑ edge TscH2DIL20—ns

77 CS

80 SDO data output valid after SCK↓ edge TscL2

82 SDO data output valid after

83 CS

84 Hold time of CS

Inactive (VIH) to SDO output hi-impedance TcsH2DOZ — 50 ns Note 1

DOV— 70nsV

170 ns V

= 2.7V to 5.5V

DD

= 1.8V to 2.7V

DD

TssL2doV — 70 ns

Active (VIL or V

CS

IHH

)

Inactive (VIH) after SCK↓ edge TscH2csI 100 — ns VDD = 2.7V to 5.5V

= 1.8V to 2.7V

DD

Active (VIL or V

CS

Inactive (VIH) to

)

IHH

1msV

TcsA2csI 50 — ns

Note 1: This specification by design.

DS22059A-page 12 © 2007 Microchip Technology Inc.

Page 13

MCP414X/416X/424X/426X

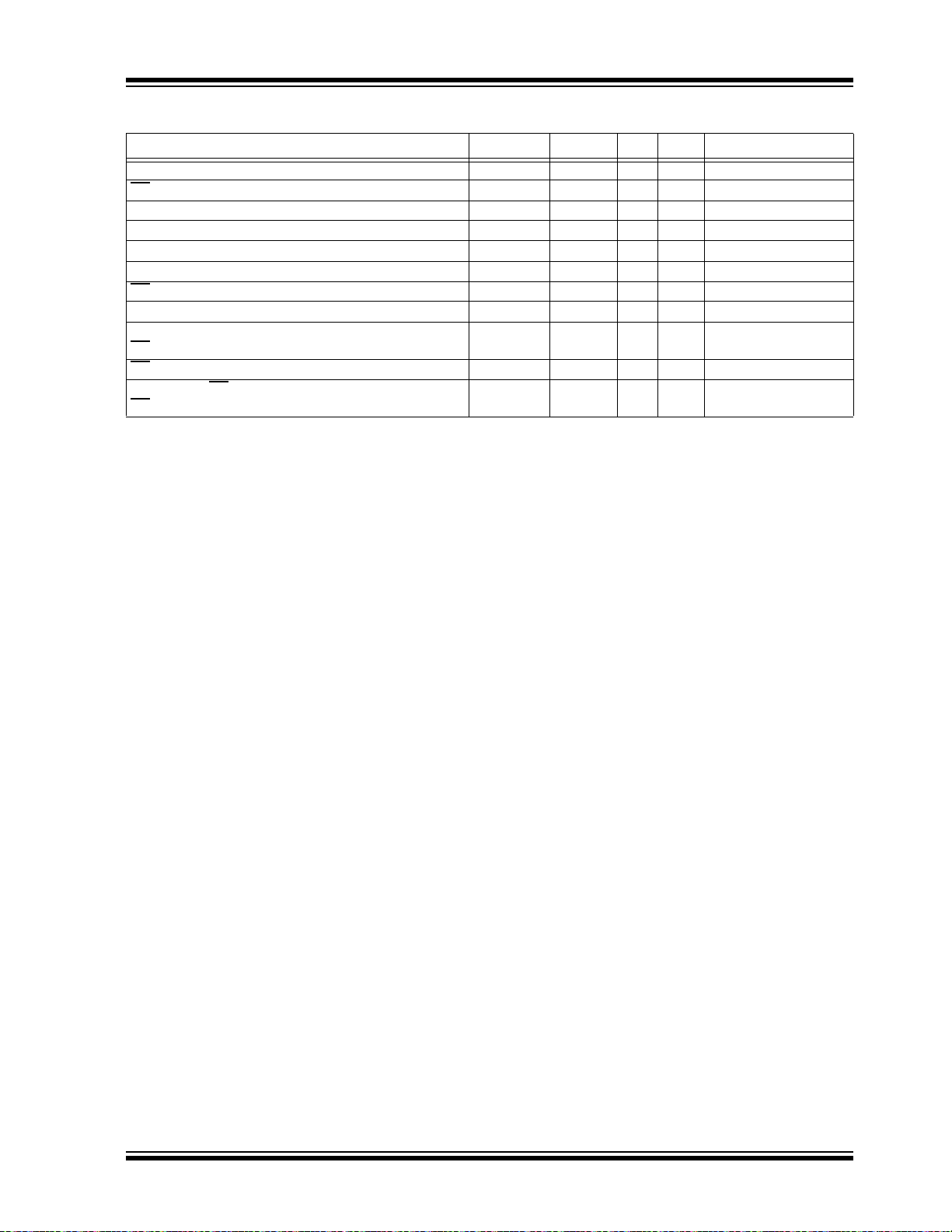

T ABLE 1-3: SPI REQUIREMENTS FOR SDI/SDO MULTIPLEXED (READ OPERATION ONLY)

Characteristic Symbol Min Max Units Conditions

SCK Input Frequency F

Active (VIL or V

CS

SCK input high time TscH 1.8 — us

SCK input low time TscL 1.8 — ns

Setup time of SDI input to SCK↑ edge T

Hold time of SDI input from SCK↑ edge TscH2

CS Inactive (VIH) to SDO output hi-impedance TcsH2DOZ — 50 ns Note 1

SDO data output valid after SCK↓ edge TscL2

SDO data output valid after

Active (VIL or V

CS

Inactive (VIH) after SCK↓ edge TscH2csI 100 — ns

CS

Hold time of CS Inactive (VIH) to

Active (VIL or V

CS

Note 1: This specification by design

2: This table is for the devices where the SPI’s SDI and SDO pins are multiplexed (SDI/SDO) and a Read

command is issued. This is NOT required for SDI/SDO operation with the Increment, Decrement, or Write

commands. This data rate can be increased by having external pull-up resistors to increase the rising

edges of each bit.

) to SCK↑ input TcsA2scH 60 — ns

IHH

TssL2doV — 50 ns

)

IHH

)

IHH

—250kHzVDD = 2.7V to 5.5V

SCK

DIV2scH 40 — ns

DIL40—ns

DOV—1.6us

TcsA2csI 50 — ns

(2)

© 2007 Microchip Technology Inc. DS22059A-page 13

Page 14

MCP414X/416X/424X/426X

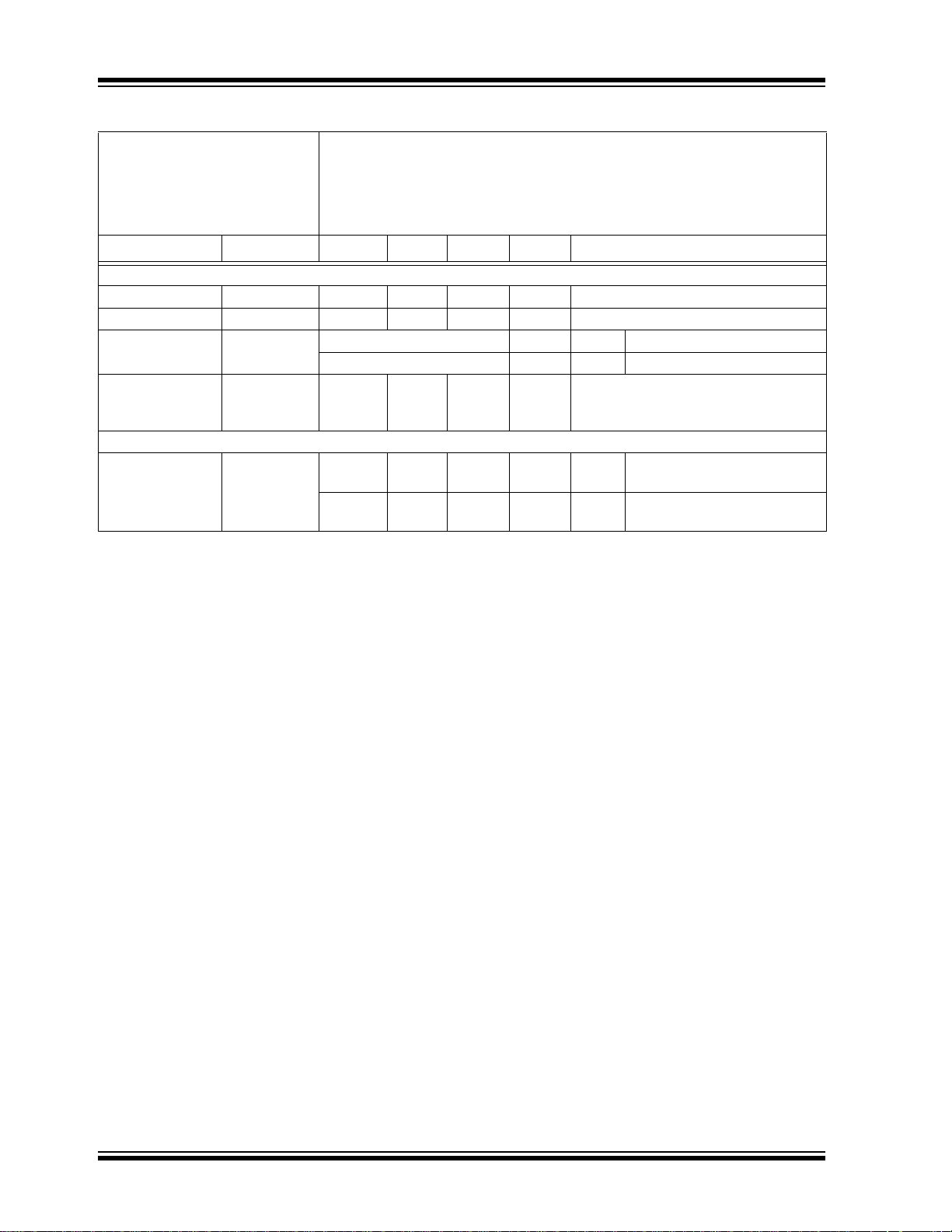

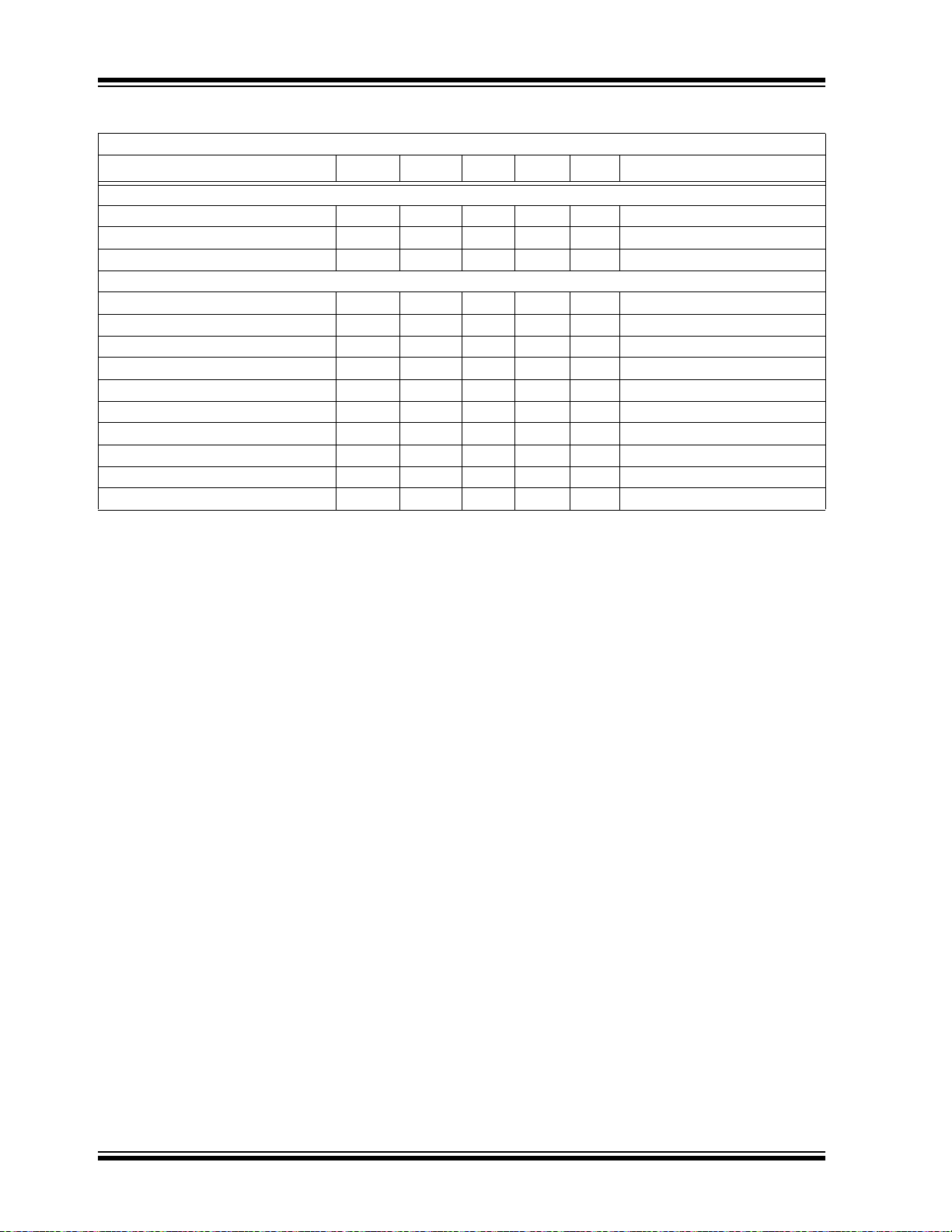

TEMPERATURE CHARACTERISTICS

Electrical Specifications: Unless otherwise indicated, VDD= +2.7V to +5.5V, VSS=GND.

Parameters Sym Min Typ Max Units Conditions

Temperature Ranges

Specified Temperature Range T

Operating Temperature Range T

Storage Temperature Range T

Thermal Package Resistances

Thermal Resistance, 8L-PDIP θ

Thermal Resistance, 8L-SOIC θ

Thermal Resistance, 8L-MSOP θ

Thermal Resistance, 8L-DFN (3x3) θ

Thermal Resistance, 10L-PDIP θ

Thermal Resistance, 10L-MSOP θ

Thermal Resistance, 14L-PDIP θ

Thermal Resistance, 14L-SOIC θ

Thermal Resistance, 14L-MSOP θ

Thermal Resistance, 16L-QFN θ

A

A

A

JA

JA

JA

JA

JA

JA

JA

JA

JA

JA

-40 — +125 °C

-40 — +125 °C

-65 — +150 °C

— 84.6 — °C/W

— 145.5 — °C/W

—211—°C/W

— 68.5 — °C/W

—82—°C/W

—202—°C/W

—70—°C/W

—85—°C/W

—N/A—°C/W

—50—°C/W

DS22059A-page 14 © 2007 Microchip Technology Inc.

Page 15

MCP414X/416X/424X/426X

0

50

100

150

200

250

300

350

400

450

500

550

600

650

0.00 2.00 4.00 6.00 8.00 10.00 12.00

f

SCK

(MHz)

Operating Current (I

DD

) (µA)

2.7V -40°C

2.7V 25°C

2.7V 85°C

2.7V 125°C

5.5V -40°C

5.5V 25°C

5.5V 85°C

5.5V 125°C

0.0

0.5

1.0

1.5

2.0

2.5

3.0

-40 25 85 125

Ambient Temperature (°C)

Standby Current (Istby) (µA)

5.5V

2.7V

300.0

400.0

500.0

600.0

700.0

800.0

900.0

-40 25 85 125

Ambient Temperature (°C)

EE Write Current (Iwrite) (µA)

5.5V

0

50

100

150

200

250

2345678910

V

CS

(V)

R

CS

(kOhms)

-1000

-800

-600

-400

-200

0

200

400

600

800

1000

I

CS

(µA)

I

CS

R

CS

0

2

4

6

8

10

12

-40-200 20406080100120

Ambient Temperature (°C)

CS V

PP

Threshold (V)

2.7V Exit

5.5V Exit

2.7V Entry

5.5V Entry

2.0 TYPICAL PERFORMANCE CURVES

Note: The graphs and tables provided following this note are a statistical summary based on a limited number of

samples and are provided for informational purposes only. The performance characteristics listed herein

are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified

operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

Note: Unless otherwise indicated, TA = +25°C, VDD = 5V, VSS = 0V.

FIGURE 2-1: Device Current (IDD) vs. SPI

Frequency (f

(V

= 2.7V and 5.5V).

DD

FIGURE 2-2: Device Current (I

V

. (CS = VDD) vs. Ambient Temperature.

DD

) and Ambient Temperature

SCK

SHDN

) and

FIGURE 2-4: CS

Resistance (R

Voltage (V

) and Current (ICS) vs. CS Input

CS

) (V

CS

DD

FIGURE 2-5: CS

Pull-up/Pull-down

= 5.5V).

High Input Entry/Exit

Threshold vs. Ambient Temperature and V

DD

.

FIGURE 2-3: Write Current (I

Ambient Temperature and V

© 2007 Microchip Technology Inc. DS22059A-page 15

) vs.

WRITE

.

DD

Page 16

MCP414X/416X/424X/426X

20

60

100

140

180

220

260

300

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

Wiper Resistance (R

W

(ohms)

-0.3

-0.2

-0.1

0

0.1

0.2

0.3

Error (LSb)

-40C Rw 25C Rw 85C Rw 125C Rw

-40C INL 25C INL 85C INL 125C INL

-40C DNL 25C DNL 85C DNL 125C DNL

INL

DNL

-40°C

25°C

85°C

R

W

125°C

20

40

60

80

100

120

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

Wiper Resistance (R

W

(ohms)

-0.3

-0.2

-0.1

0

0.1

0.2

0.3

Error (LSb)

-40C Rw 25C Rw 85C Rw 125C Rw

-40C INL 25C INL 85C INL 125C INL

-40C DNL 25C DNL 85C DNL 125C DNL

INL

DNL

R

W

-40°C 25°C

85°C

125°C

5050

5100

5150

5200

5250

5300

-40 0 40 80 120

Ambient Temperature (°C)

Nominal Resistance (R

AB

(Ohms)

2.7V

5.5V

20

60

100

140

180

220

260

300

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

Wiper Resistance (R

W

(ohms)

-2

0

2

4

6

Error (LSb)

-40C Rw 25C Rw 85C Rw 125C Rw

-40C INL 25C INL 85C INL 125C INL

-40C DNL 25C DNL 85C DNL 125C DNL

INL

DNL

R

W

-40°C

25°C

85°C125°C

20

40

60

80

100

120

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

Wiper Resistance (R

W

(ohms)

-1.25

-0.75

-0.25

0.25

0.75

1.25

Error (LSb)

-40C Rw 25C Rw 85C Rw 125C Rw

-40C INL 25C INL 85C INL 125C INL

-40C DNL 25C DNL 85C DNL 125C DNL

INL

DNL

R

-40°C

25°C

85°C

125°C

0

1000

2000

3000

4000

5000

6000

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

R

WB

(Ohms)

-40°C

25°C

85°C

125°C

Note: Unless otherwise indicated, TA = +25°C, VDD = 5V, VSS = 0V.

)

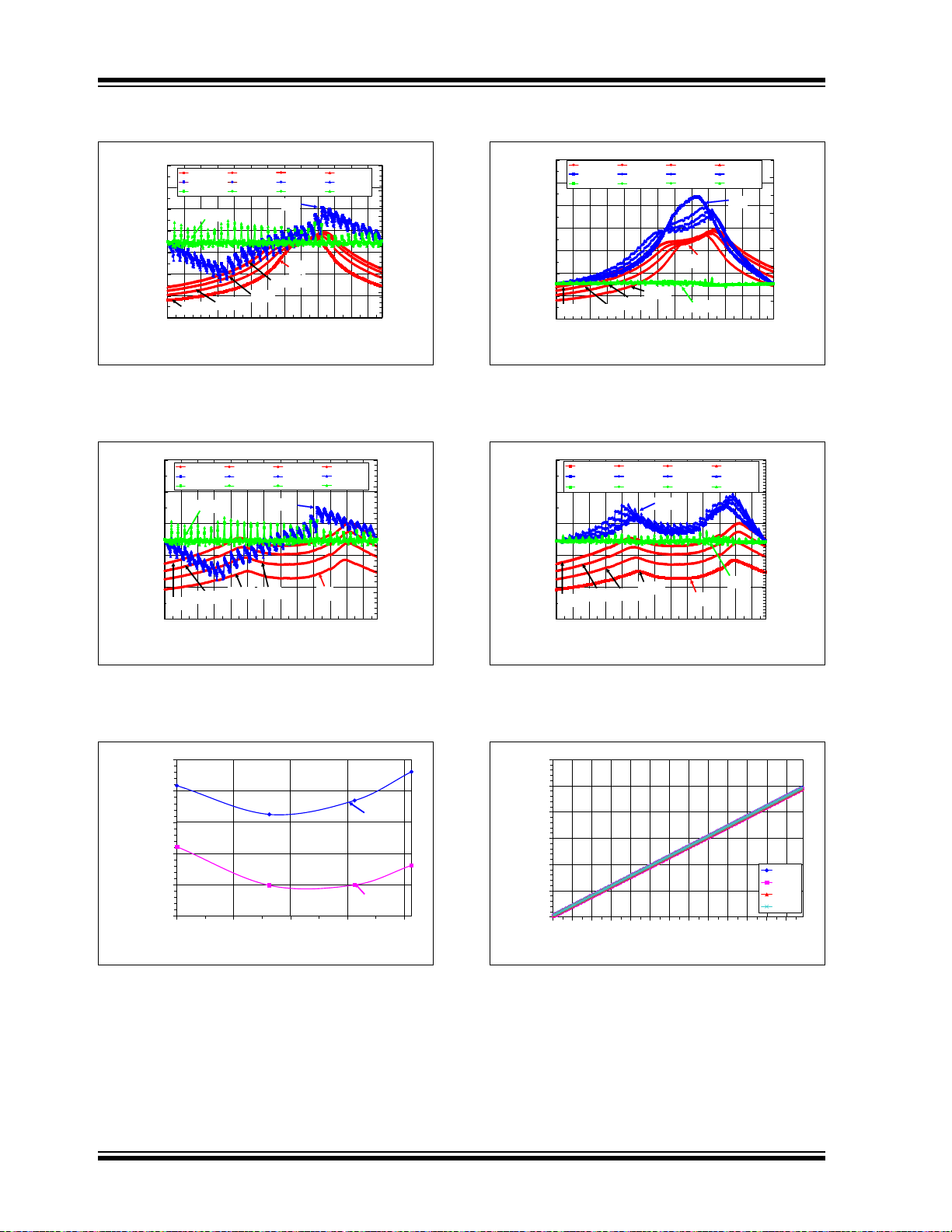

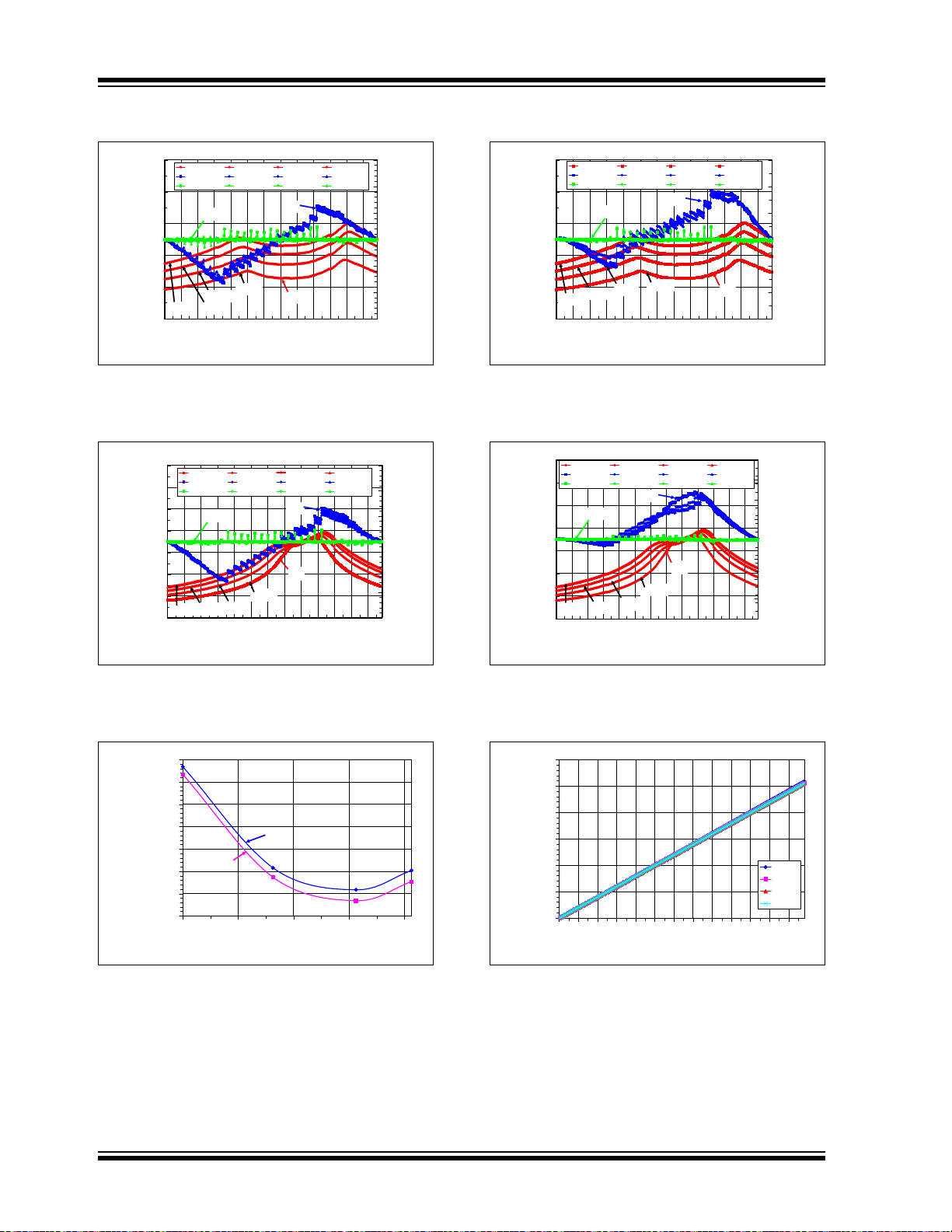

FIGURE 2-6: 5kΩ Pot Mode – RW (Ω),

INL (LSb), DNL (LSb) vs. Wiper Setting and

Ambient Temperature (V

)

= 5.5V).

DD

)

FIGURE 2-9: 5k

Ω

Rheo Mode – RW (Ω),

INL (LSb), DNL (LSb) vs. Wiper Setting and

Ambient Temperature (V

)

= 5.5V).

DD

W

FIGURE 2-7: 5k

INL (LSb), DNL (LSb) vs. Wiper Setting and

Ambient Temperature (V

)

FIGURE 2-8: 5k

(

Ω

) vs. Ambient Temperature and VDD.

DS22059A-page 16 © 2007 Microchip Technology Inc.

Ω

Pot Mode – RW (Ω),

= 3.0V).

DD

Ω

– Nominal Resistance

Ω

FIGURE 2-10: 5k

Rheo Mode – RW (Ω),

INL (LSb), DNL (LSb) vs. Wiper Setting and

Ambient Temperature (V

FIGURE 2-11: 5k

= 3.0V).

DD

Ω

– RWB (Ω) vs. Wiper

Setting and Ambient Temperature.

Page 17

MCP414X/416X/424X/426X

Note: Unless otherwise indicated, TA = +25°C, VDD = 5V, VSS = 0V.

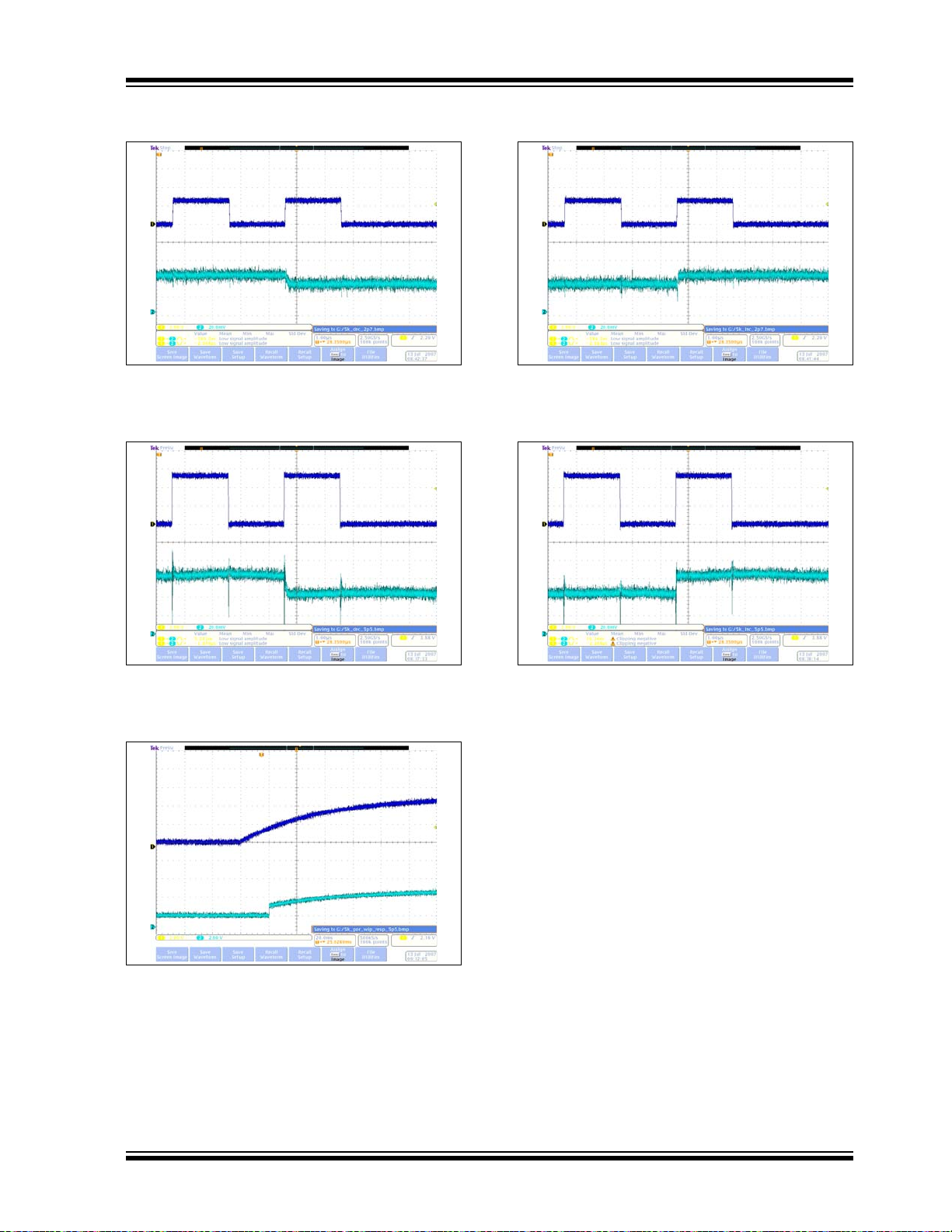

FIGURE 2-12: 5kΩ – Low-Voltage

Decrement Wiper Settling Time (V

(1 µs/Div).

Ω

FIGURE 2-13: 5k

Decrement Wiper Settling Time (V

(1 µs/Div).

– Low-Voltage

= 2.7V)

DD

= 5.5V)

DD

FIGURE 2-15: 5k

Increment Wiper Settling Time (V

(1 µs/Div).

FIGURE 2-16: 5k

Increment Wiper Settling Time (V

(1 µs/Div).

Ω

– Low-Voltage

Ω

– Low-Voltage

= 2.7V)

DD

= 5.5V)

DD

Ω

FIGURE 2-14: 5k

Response Time (20 ms/Div).

© 2007 Microchip Technology Inc. DS22059A-page 17

– Power-Up Wiper

Page 18

MCP414X/416X/424X/426X

20

40

60

80

100

120

0 25 50 75 100 125 150 175 200 225 250

Wiper Setting (decimal)

Wiper Resistance (R

W

(ohms)

-0.3

-0.2

-0.1

0

0.1

0.2

0.3

Error (LSb)

-40C Rw 25C Rw 85C Rw 125C Rw

-40C INL 25C INL 85C INL 125C INL

-40C DNL 25C DNL 85C DNL 125C DNL

INL

DNL

R

W

-40°C

25°C

85°C

125°C

20

60

100

140

180

220

260

300

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

Wiper Resistance (R

W

(ohms)

-0.3

-0.2

-0.1

0

0.1

0.2

0.3

Error (LSb)

-40C Rw 25C Rw 85C Rw 125C Rw

-40C INL 25C INL 85C INL 125C INL

-40C DNL 25C DNL 85C DNL 125C DNL

INL

DNL

R

W

-40°C

25°C

85°C

125°C

10000

10050

10100

10150

10200

10250

-40 0 40 80 120

Ambient Temperature (°C)

Nominal Resistance (R

AB

(Ohms)

5.5V

2.7V

20

40

60

80

100

120

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

Wiper Resistance (R

W

(ohms)

-1

-0.5

0

0.5

1

Error (LSb)

-40C Rw 25C Rw 85C Rw 125C Rw

-40C INL 25C INL 85C INL 125C INL

-40C DNL 25C DNL 85C DNL 125C DNL

INL

DNL

R

W

-40°C

25°C85°C

125°C

20

60

100

140

180

220

260

300

0 25 50 75 100125150175200225250

Wiper Setting (decimal)

Wiper Resistance (R

W

(ohms)

-2

-1

0

1

2

3

4

Error (LSb)

-40C Rw 25C Rw 85C Rw 125C Rw

-40C INL 25C INL 85C INL 125C INL

-40C DNL 25C DNL 85C DNL 125C DNL

INL

DNL R

W

-40°C

25°C85°C

125°C

0

2000

4000

6000

8000

10000

12000

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

R

WB

(Ohms)

-40°C

25°C

85°C

125°C

Note: Unless otherwise indicated, TA = +25°C, VDD = 5V, VSS = 0V.

)

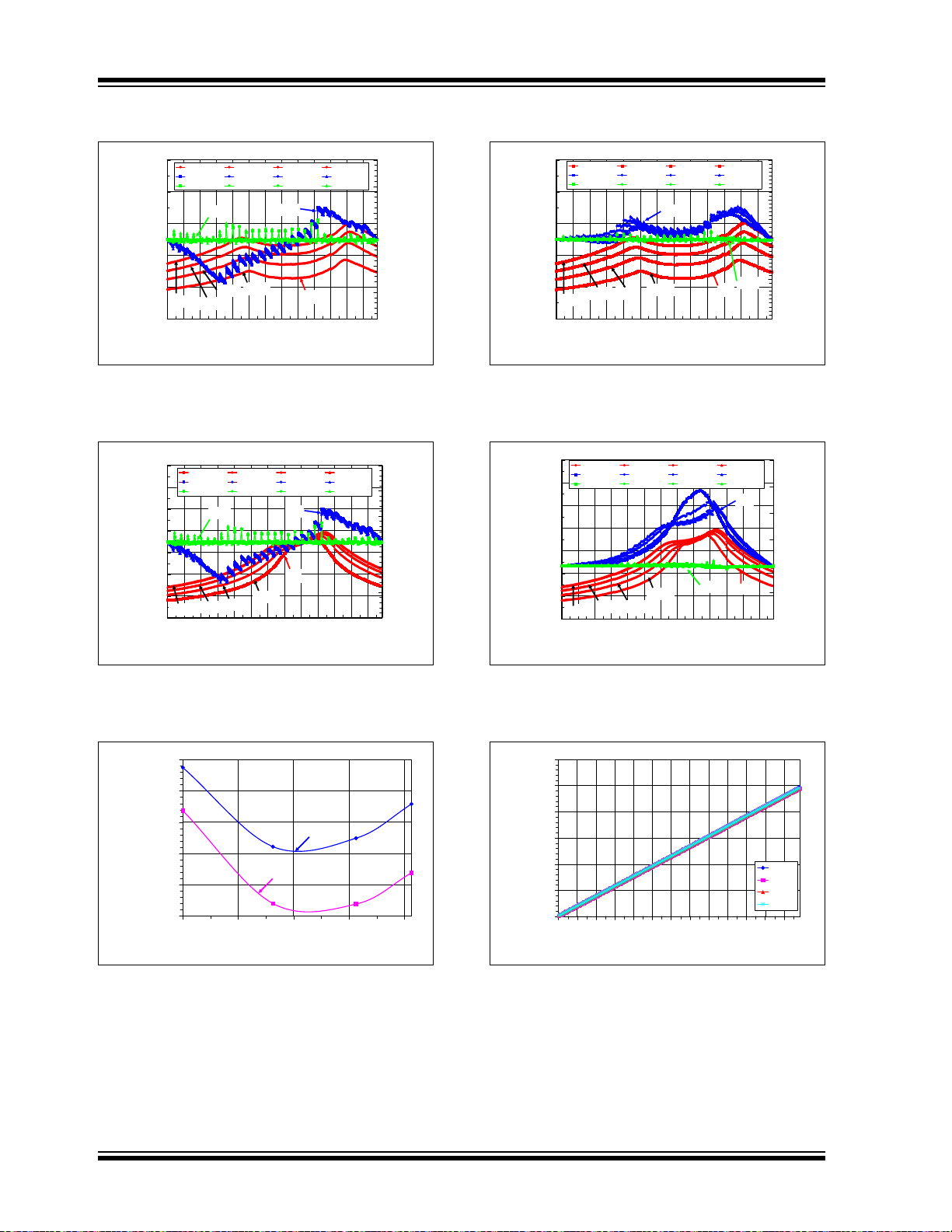

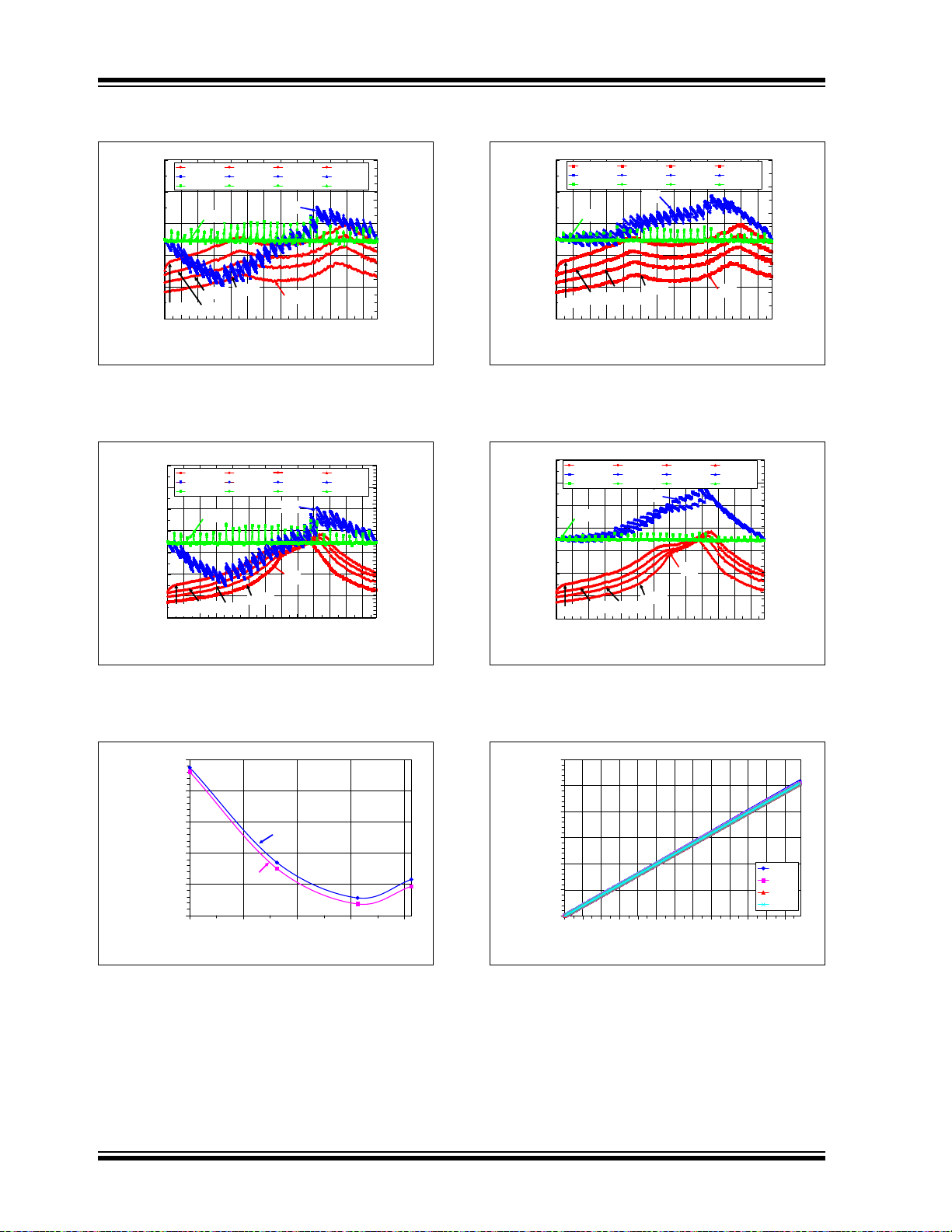

FIGURE 2-17: 10 kΩ Pot Mode – RW (Ω),

INL (LSb), DNL (LSb) vs. Wiper Setting and

Ambient Temperature (V

)

= 5.5V).

DD

)

FIGURE 2-20: 10 k

Ω

Rheo Mode – RW (Ω),

INL (LSb), DNL (LSb) vs. Wiper Setting and

Ambient Temperature (V

)

= 5.5V).

DD

FIGURE 2-18: 10 k

INL (LSb), DNL (LSb) vs. Wiper Setting and

Ambient Temperature (V

)

FIGURE 2-19: 10 k

(

Ω

) vs. Ambient Temperature and VDD.

DS22059A-page 18 © 2007 Microchip Technology Inc.

Ω

Pot Mode – RW (Ω),

FIGURE 2-21: 10 k

Ω

Rheo Mode – RW (Ω),

INL (LSb), DNL (LSb) vs. Wiper Setting and

= 3.0V).

DD

Ω

– Nominal Resistance

Ambient Temperature (V

FIGURE 2-22: 10 k

= 3.0V).

DD

Ω

– RWB (Ω) vs. Wiper

Setting and Ambient Temperature.

Page 19

MCP414X/416X/424X/426X

Note: Unless otherwise indicated, TA = +25°C, VDD = 5V, VSS = 0V.

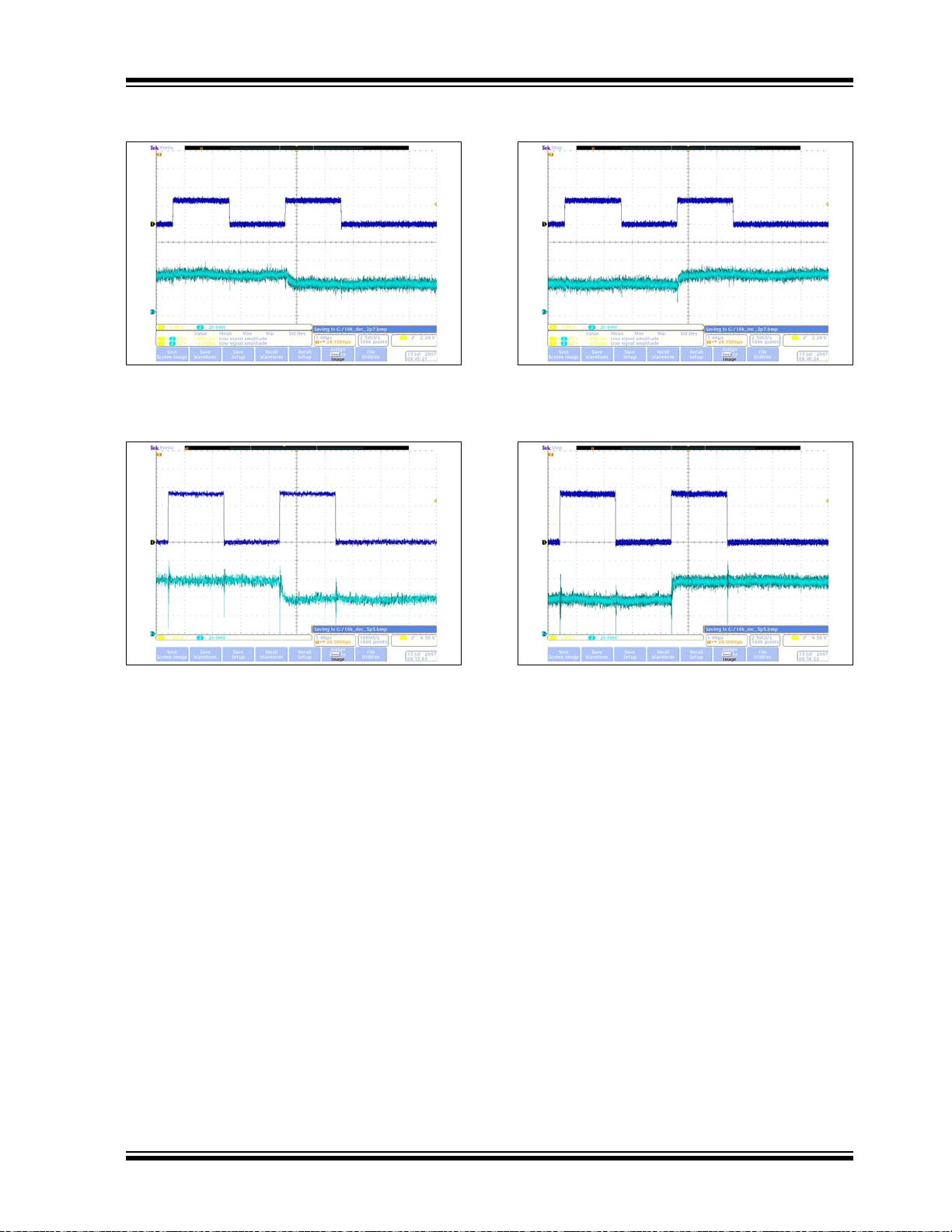

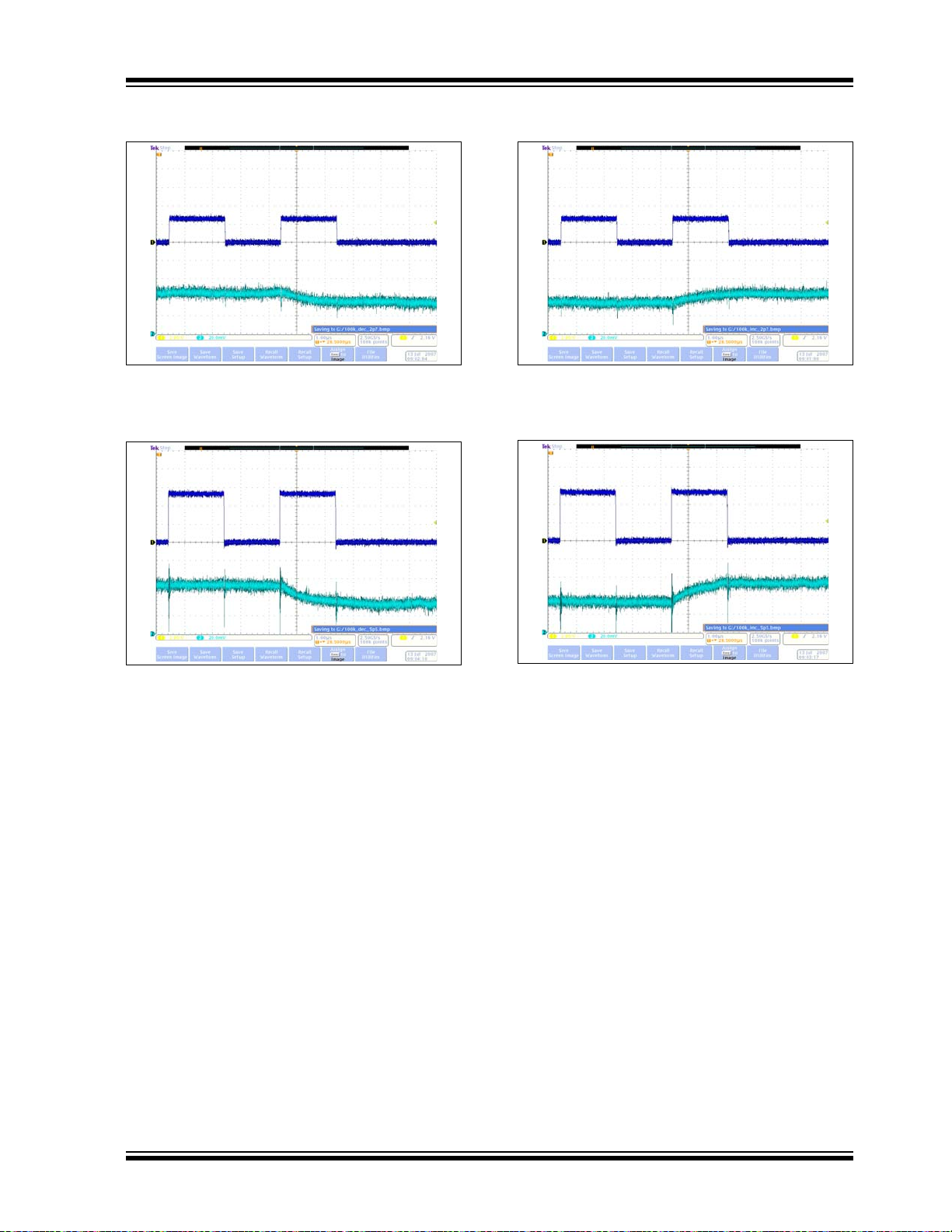

FIGURE 2-23: 10 kΩ – Low-Voltage

Decrement Wiper Settling Time (V

(1 µs/Div).

Ω

FIGURE 2-24: 10 k

Decrement Wiper Settling Time (V

(1 µs/Div).

– Low-Voltage

= 2.7V)

DD

= 5.5V)

DD

FIGURE 2-25: 10 k

Increment Wiper Settling Time (V

(1 µs/Div).

FIGURE 2-26: 10 k

Increment Wiper Settling Time (V

(1 µs/Div).

Ω

– Low-Voltage

Ω

– Low-Voltage

= 2.7V)

DD

= 5.5V)

DD

© 2007 Microchip Technology Inc. DS22059A-page 19

Page 20

MCP414X/416X/424X/426X

20

40

60

80

100

120

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

Wiper Resistance (R

W

)

(ohms)

-0.3

-0.2

-0.1

0

0.1

0.2

0.3

Error (LSb)

-40C Rw 25C Rw 85C Rw 125C Rw

-40C INL 25C INL 85C INL 125C INL

-40C DNL 25C DNL 85C DNL 125C DNL

INL

DNL

R

W

-40°C

25°C

85°C

125°C

20

60

100

140

180

220

260

300

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

Wiper Resistance (R

W

)

(ohms)

-0.3

-0.2

-0.1

0

0.1

0.2

0.3

Error (LSb)

-40C Rw 25C Rw 85C Rw 125C Rw

-40C INL 25C INL 85C INL 125C INL

-40C DNL 25C DNL 85C DNL 125C DNL

INL

DNL

R

W

-40°C

25°C

85°C

125°C

49400

49600

49800

50000

50200

50400

50600

50800

-40 0 40 80 120

Ambient Temperature (°C)

Nominal Resistance (R

AB

(Ohms)

2.7V

5.5V

20

40

60

80

100

120

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

Wiper Resistance (R

W

)

(ohms)

-0.3

-0.2

-0.1

0

0.1

0.2

0.3

Error (LSb)

-40C Rw 25C Rw 85C Rw 125C Rw

-40C INL 25C INL 85C INL 125C INL

-40C DNL 25C DNL 85C DNL 125C DNL

INL

DNL

R

W

-40°C

25°C

85°C

125°C

20

60

100

140

180

220

260

300

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

Wiper Resistance (R

W

(ohms)

-1

-0.75

-0.5

-0.25

0

0.25

0.5

0.75

1

Error (LSb)

-40C Rw 25C Rw 85C Rw 125C Rw

-40C INL 25C INL 85C INL 125C INL

-40C DNL 25C DNL 85C DNL 125C DNL

INL

DNL

R

W

-40°C

25°C

85°C

125°C

0

10000

20000

30000

40000

50000

60000

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

R

WB

(Ohms)

-40°C

25°C

85°C

125°C

Note: Unless otherwise indicated, TA = +25°C, VDD = 5V, VSS = 0V.

FIGURE 2-27: 50 kΩ Pot Mode – RW (Ω),

INL (LSb), DNL (LSb) vs. Wiper Setting and

Ambient Temperature (V

FIGURE 2-28: 50 k

= 5.5V).

DD

Ω

Pot Mode – RW (Ω),

INL (LSb), DNL (LSb) vs. Wiper Setting and

Ambient Temperature (V

)

= 3.0V).

DD

FIGURE 2-30: 50 k

Ω

Rheo Mode – RW (Ω),

INL (LSb), DNL (LSb) vs. Wiper Setting and

Ambient Temperature (V

)

FIGURE 2-31: 50 k

= 5.5V).

DD

Ω

Rheo Mode – RW (Ω),

INL (LSb), DNL (LSb) vs. Wiper Setting and

Ambient Temperature (V

= 3.0V).

DD

FIGURE 2-29: 50 k

(

Ω

) vs. Ambient Temperature and VDD.

DS22059A-page 20 © 2007 Microchip Technology Inc.

Ω

– Nominal Resistance

FIGURE 2-32: 50 k

Ω

– RWB (Ω) vs. Wiper

Setting and Ambient Temperature.

Page 21

MCP414X/416X/424X/426X

Note: Unless otherwise indicated, TA = +25°C, VDD = 5V, VSS = 0V.

FIGURE 2-33: 50 kΩ – Low-Voltage

Decrement Wiper Settling Time (V

(1 µs/Div).

Ω

FIGURE 2-34: 50 k

Decrement Wiper Settling Time (V

(1 µs/Div).

– Low-Voltage

= 2.7V)

DD

= 5.5V)

DD

FIGURE 2-35: 50 k

Increment Wiper Settling Time (V

(1 µs/Div).

FIGURE 2-36: 50 k

Increment Wiper Settling Time (V

(1 µs/Div).

Ω

– Low-Voltage

Ω

– Low-Voltage

DD

DD

= 2.7V)

= 5.5V)

© 2007 Microchip Technology Inc. DS22059A-page 21

Page 22

MCP414X/416X/424X/426X

20

40

60

80

100

120

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

Wiper Resistance (R

W

(ohms)

-0.2

-0.1

0

0.1

0.2

Error (LSb)

-40C Rw 25C Rw 85C Rw 125C Rw

-40C INL 25C INL 85C INL 125C INL

-40C DNL 25C DNL 85C DNL 125C DNL

INL

DNL

R

W

-40°C

25°C

85°C

125°C

20

60

100

140

180

220

260

300

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

Wiper Resistance (R

W

(ohms)

-0.2

-0.15

-0.1

-0.05

0

0.05

0.1

0.15

0.2

Error (LSb)

-40C Rw 25C Rw 85C Rw 125C Rw

-40C INL 25C INL 85C INL 125C INL

-40C DNL 25C DNL 85C DNL 125C DNL

INL

DNL

R

W

-40°C

25°C

85°C

125°C

99000

99500

100000

100500

101000

101500

-40 0 40 80 120

Ambient Temperature (°C)

Nominal Resistance (R

AB

(Ohms)

5.5V

2.7V

20

40

60

80

100

120

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

Wiper Resistance (R

W

(ohms)

-0.3

-0.2

-0.1

0

0.1

0.2

0.3

Error (LSb)

-40C Rw 25C Rw 85C Rw 125C Rw

-40C INL 25C INL 85C INL 125C INL

-40C DNL 25C DNL 85C DNL 125C DNL

INL

DNL

R

W

-40°C

25°C85°C

125°C

20

60

100

140

180

220

260

300

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

Wiper Resistance (Rw)

(ohms)

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

Error (LSb)

-40C Rw 25C Rw 85C Rw 125C Rw

-40C INL 25C IN L 85C INL 125C INL

-40C DNL 25C DNL 85C DNL 125C DNL

INL

DNL

R

W

-40°C

25°C85°C

125°C

0

20000

40000

60000

80000

100000

120000

0 32 64 96 128 160 192 224 256

Wiper Setting (decimal)

Rwb (Ohms)

-40°C

25°C

85°C

125°C

Note: Unless otherwise indicated, TA = +25°C, VDD = 5V, VSS = 0V.

)

FIGURE 2-37: 100 kΩ Pot Mode – RW (Ω),

INL (LSb), DNL (LSb) vs. Wiper Setting and

Ambient Temperature (V

)

= 5.5V).

DD

)

FIGURE 2-40: 100 k

(

Ω

), INL (LSb), DNL (LSb) vs. Wiper Setting and

Ambient Temperature (V

Ω

Rheo Mode – RW

= 5.5V).

DD

FIGURE 2-38: 100 k

INL (LSb), DNL (LSb) vs. Wiper Setting and

Ambient Temperature (V

)

FIGURE 2-39: 100 k

Resistance (

V

.

DD

DS22059A-page 22 © 2007 Microchip Technology Inc.

Ω

Ω

Pot Mode – RW (Ω),

= 3.0V).

DD

Ω

– Nominal

) vs. Ambient Temperature and

Ω

FIGURE 2-41: 100 k

(

Ω

), INL (LSb), DNL (LSb) vs. Wiper Setting and

Ambient Temperature (V

FIGURE 2-42: 100 k

Rheo Mode – RW

= 3.0V).

DD

Ω

– RWB (Ω) vs. Wiper

Setting and Ambient Temperature.

Page 23

MCP414X/416X/424X/426X

Note: Unless otherwise indicated, TA = +25°C, VDD = 5V, VSS = 0V.

M

FIGURE 2-43: 100 kΩ – Low-Voltage

Decrement Wiper Settling Time (V

= 2.7V)

DD

(1 µs/Div).

Ω

FIGURE 2-44: 100 k

Decrement Wiper Settling Time (V

– Low-Voltage

= 5.5V)

DD

(1 µs/Div).

FIGURE 2-45: 100 kΩ – Power-Up Wiper

Response Time (1 µs/Div).

FIGURE 2-46: 100 k

Increment Wiper Settling Time (V

Ω

– Low-Voltage

= 2.7V)

DD

(1 µs/Div).

© 2007 Microchip Technology Inc. DS22059A-page 23

Page 24

MCP414X/416X/424X/426X

0

0.01

0.02

0.03

0.04

0.05

0.06

0.07

0.08

0.09

0.1

-40 0 40 80 120

Temperature (°C)

%

5.5V

3.0V

-0.04

-0.03

-0.02

-0.01

0

0.01

0.02

0.03

0.04

-40 0 40 80 120

Temperature (°C)

%

5.5V

3.0V

0

0.02

0.04

0.06

0.08

0.1

0.12

-40 0 40 80 120

Temperature (°C)

%

5.5V

3.0V

-0.03

-0.02

-0.01

0

0.01

0.02

0.03

0.04

0.05

-40 10 60 110

Temperature (°C)

%

5.5V

3.0V

Note: Unless otherwise indicated, TA = +25°C, VDD = 5V, VSS = 0V.

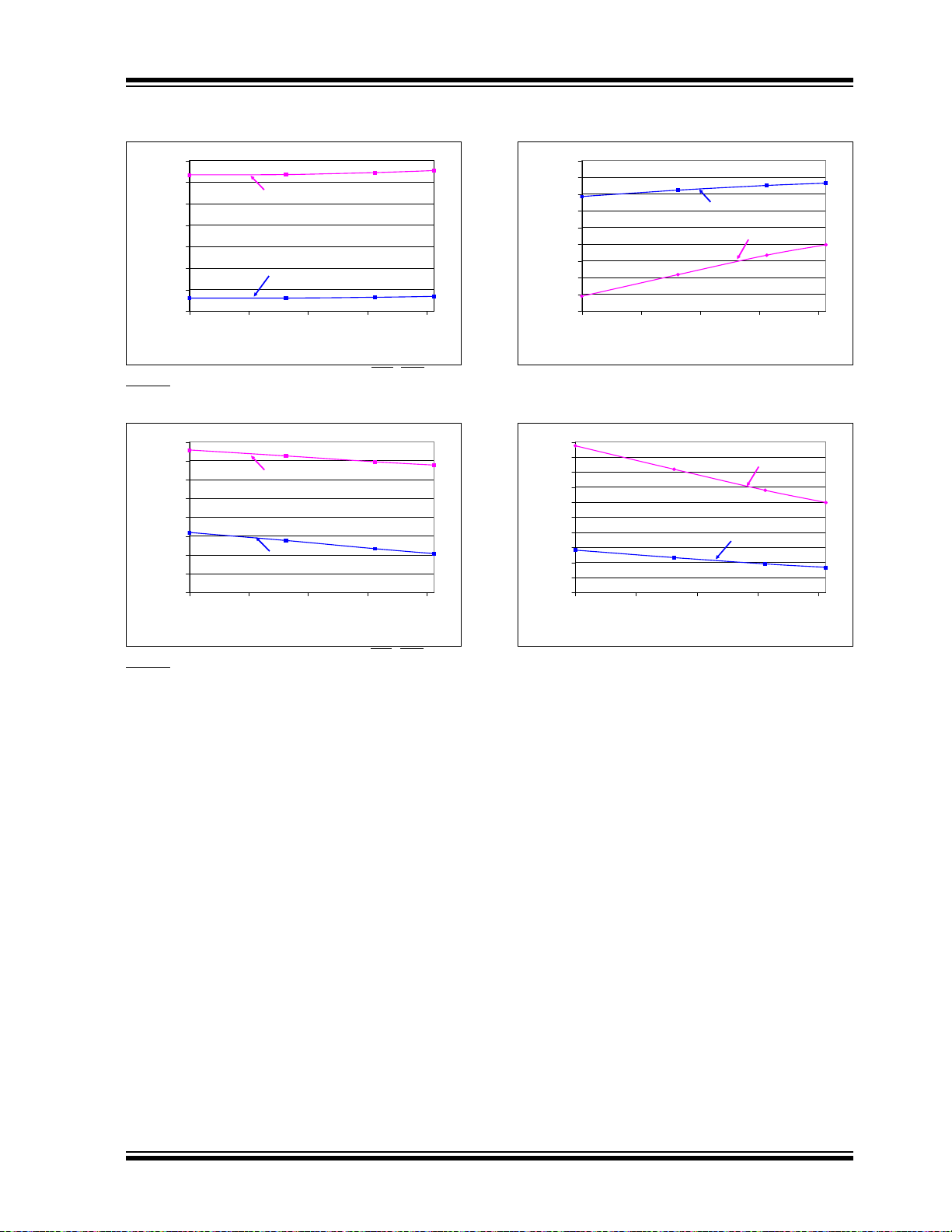

FIGURE 2-47: Resistor Network 0 to

Resistor Network 1 R

(5 kΩ) Mismatch vs. VDD

AB

and Temperature.

FIGURE 2-48: Resistor Network 0 to

Resistor Network 1 R

V

and Temperature.

DD

(10 kΩ) Mismatch vs.

AB

FIGURE 2-49: Resistor Network 0 to

Resistor Network 1 R

V

and Temperature.

DD

(50 kΩ) Mismatch vs.

AB

FIGURE 2-50: Resistor Network 0 to

Resistor Network 1 R

V

and Temperature.

DD

(100 kΩ) Mismatch vs.

AB

DS22059A-page 24 © 2007 Microchip Technology Inc.

Page 25

MCP414X/416X/424X/426X

1

1.2

1.4

1.6

1.8

2

2.2

2.4

-40 0 40 80 120

Temperature (°C)

V

IH

(V)

5.5V

2.7V

0.6

0.7

0.8

0.9

1

1.1

1.2

1.3

1.4

-40 0 40 80 120

Temperature (°C)

V

IL

(V)

5.5V

2.7V

-45

-40

-35

-30

-25

-20

-15

-10

-5

0

-40 0 40 80 120

Temperature (°C)

I

OH

(mA)

5.5V

2.7V

0

5

10

15

20

25

30

35

40

45

50

-40 0 40 80 120

Temperature (°C)

I

OL

(mA)

5.5V

2.7V

Note: Unless otherwise indicated, TA = +25°C, VDD = 5V, VSS = 0V.

FIGURE 2-51: VIH (SDI, SCK, CS, WP, and

SHDN

) vs. VDD and Temperature.

FIGURE 2-52: V

SHDN

) vs. VDD and Temperature.

(SDI, SCK, CS, WP, and

IL

FIGURE 2-53: I

Temperature.

FIGURE 2-54: I

Temperature.

(SDO) vs. VDD and

OH

(SDO) vs. VDD and

OL

© 2007 Microchip Technology Inc. DS22059A-page 25

Page 26

MCP414X/416X/424X/426X

3.0

3.2

3.4

3.6

3.8

4.0

4.2

-40 0 40 80 120

Temperature (°C)

t

WC

(ms)

0

0.2

0.4

0.6

0.8

1

1.2

-40 0 40 80 120

Temperature (°C)

V

DD

(V)

2.7V

5.5V

12.0

12.5

13.0

13.5

14.0

14.5

15.0

-40 0 40 80 120

Temperature (°C)

fsck (MHz)

2.7V

5.5V

+

-

V

OUT

2.5V DC

+5V

A

B

W

Offset

GND

V

IN

Note: Unless otherwise indicated, TA = +25°C, VDD =

5V, VSS = 0V.

FIGURE 2-55: Nominal EEPROM Write

Cycle Time vs. V

and Temperature.

DD

2.1 Test Circuits

FIGURE 2-58: -3 db Gain vs. Frequency

Test.

FIGURE 2-56: POR/BOR T rip point vs. V

and Temperature.

FIGURE 2-57: SCK Input Frequency vs.

Voltage and Temperature.

DS22059A-page 26 © 2007 Microchip Technology Inc.

DD

Page 27

MCP414X/416X/424X/426X

3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

Additional descriptions of the device pins follows.

TABLE 3-1: PINOUT DESCRIPTION FOR THE MCP414X/416X/424X/426X

Pin

Single Dual

Rheo Pot

(1)

Rheo Pot

8L 8L 10L 14L 16L

Symbol I/O

Buffer

Type

Weak

Pull-up/

down

(2)

Standard Function

111116

CS

I HV w/ST “smart” SPI Chip Select Input

2 2 2 2 1 SCK I HV w/ST “smart” SPI Clock Input

3 — 3 3 2 SDI I HV w/ST “smart” SPI Serial Data Input

— 3 — — — SDI/SDO

44443, 4V

SS

(1, 3)

I/O HV w/ST “smart” SPI Serial Data Input/Output

— P — Ground

— — 5 5 5 P1B A Analog No Potentiometer 1 Terminal B

— — 6 6 6 P1W A Analog No Potentiometer 1 Wiper Terminal

— — — 7 7 P1A A Analog No Potentiometer 1 Terminal A

— 5 — 8 8 P0A A Analog No Potentiomete r 0 Terminal A

5 6 7 9 9 P0W A Analog No Potentiometer 0 Wiper Terminal

6 7 8 10 10 P0B A Analog No Potentiometer 0 Terminal B

———1112

WP

I I “smart” Hardware EEPROM Write

Protect

———1213

SHDN

I HV w/ST “smart” Hardware Shutdown

7 — 9 13 14 SDO O O No SPI Serial Data Out

8 8 10 14 15 V

— P — Positive Power Supply Input

DD

— — — — 11 NC — — — No Connection

(4)

(4)

(4)

—

(4)

Exposed Pad — — — Note 4

Legend: HV w/ST = High Voltage tolerant input (with Schmidtt trigger input)

A = Analog pins (Potentiometer terminals) I = digital input (high Z)

O = digital output I/O = Input / Output

P = Power

Note 1: The 8-lea d Single Potentiometer devices are pin limited so the SDO pin is multiplexed with the SDI pin

(SDI/SDO pin). After the Address/Command (first 6-bits) are received, If a valid Read command has been

requested, the SDO pin starts driving the requested read data onto the SDI/SDO pin.

2: The pin’s “smart” pull-up shuts off while the pin is forced low. This is done to reduce the standby and shut-

down current.

3: The SDO is an open drain outp ut, which uses the internal “smart” pull-up. The SDI input data rate can be

at the maximum SPI frequency. the SDO output data rate will be limited by the “speed” of the pull-up, customers can increase the rate with external pull-up resistors.

4: The DFN and QFN packages have a contact on the bott om of the package. This contact is conductively

connected to the die substrate, and therefore should be unconnected or connected to the same ground as

the device’s V

SS

pin.

© 2007 Microchip Technology Inc. DS22059A-page 27

Page 28

MCP414X/416X/424X/426X

3.1 Chip Select (CS)

The CS pin is the serial interface’s chip select input.

Forcing the CS

Forcing the CS pin to V

serial commands.

pin to VIL enables the serial commands.

enables the high-voltage

IHH

3.2 Serial Data In (SDI)

The SDI pin is the serial interfaces Serial Data In pin.

This pin is connected to the Host Controllers SDO pin.

3.3 Serial Data In / Serial Data Out

(SDI/SDO)

On the MCP41X1 devices, pin-out limitations do not

allow for individual SDI and SDO pins. On these

devices, the SDI and SDO pins are multiplexed.

The MCP41X1 serial interface knows when the pin

needs to change from being an input (SDI) to being an

output (SDO). The Host Controller’s SDO pin must be

properly protected from a drive conflict.

3.4 Ground (VSS)

The VSS pin is the device ground reference.

3.5 Potentiometer Terminal B

3.7 Potentiometer Terminal A

The terminal A pin is available on the MCP4XX1

devices, and is connected to the internal potentiometer’s terminal A.

The potentiometer’s terminal A is the fixed connection

to the Full Scale wiper value of the digital potentiometer. This corresponds to a wiper value of 0x100 for 8-bit

devices or 0x80 for 7-bit devices.

The terminal A pin does not have a polarity relative to

the terminal W or B pins. The terminal A pin can

support both positive and negative current. The voltage

on terminal A must be between V

The terminal A pin is not available on the MCP4XX2

devices, and the internally terminal A signal is floating.

MCP42X1 devices have two terminal A pins, one for

each resistor network.

and VDD.

SS

3.8 Write Protect (WP)

The WP pin is used to force the non-volatile memory to

be write protected.

3.9 Shutdown (SHDN)

The SHDN pin is used to force the resistor network

terminals into the hardware shutdown state.

The terminal B pin is connected to the internal potentiometer’s terminal B.

The potentiometer’s terminal B is the fixed connection

to the Zero Scale wiper value of the digital potentiometer. This corresponds to a wiper value of 0x00 for both

7-bit and 8-bit devices.

The terminal B pin does not have a polarity relative to

the terminal W or A pins. The terminal B pin can

support both positive and negative current. The voltage

on terminal B must be between V

MCP42XX devices have two terminal B pins, one for

each resistor network.

and VDD.

SS

3.6 Potentiometer Wiper (W) Terminal

The terminal W pin is connected to the internal potentiometer’s terminal W (the wiper). The wiper terminal is

the adjustable terminal of the digital potentiometer. The

terminal W pin does not have a polarity relative to

terminals A or B pins. The terminal W pin can support

both positive and negative current. The voltage on

terminal W must be between V

MCP42XX devices have two terminal W pins, one for

each resistor network.

and VDD.

SS

3.10 Serial Data Out (SDO)

The SDO pin is the serial interfaces Serial Data Out pin.

This pin is connected to the Host Controllers SDI pin.

This pin allows the Host Controller to read the digital

potentiometers registers, or monitor the state of the

command error bit.

3.11 Positive Power Supply Input (VDD)

The VDD pin is the device’s positive po wer supply input.

The input power supply is relative to V

While the device V

performance of the device may not meet the data sheet

specifications.

DD

< V

(2.7V), the electrical

min

SS

.

DS22059A-page 28 © 2007 Microchip Technology Inc.

Page 29

MCP414X/416X/424X/426X

4.0 FUNCTIONAL OVERVIEW

This Data Sheet covers a family of thirty-two Digital

Potentiometer and Rheostat devices that will be

referred to as MCP4XXX. The MCP4XX1 devices are

the Potentiometer configuration, while the MCP4XX2

devices are the Rheostat configuration.

As the Device Block Diagram shows, there are four

main functional blocks. These are:

• POR/BOR Operation

• Memory Map

• Resistor Network

• Serial Interface (SPI)

The POR/BOR operation and the Memory Map are

discussed in this section and the Resistor Network and

SPI operation are described in their own sections. The

Device Commands commands are discussed in

Section 7.0.

4.1 POR/BOR Operation

The Power-on Reset is the case where the device is

having power applied to it from V

Reset occurs when a device had power applied to it,

and that power (voltage) drops below the specified

range.

The devices RAM retention voltage (V

than the POR/BOR voltage trip point (V

maximum V

When V

POR/VBOR

POR/VBOR

voltage is less then 1.8V.

< VDD < 2.7V, the electrical

performance may not meet the data sheet

specifications. In this region, the device is capable of

reading and writing to its EEPROM and incrementing,

decrementing, reading and writing to its volatile

memory if the proper serial command is executed.

4.1.1 POWER-ON RESET

When the device powers up, the device VDD will cross

the V

POR/VBOR

the V

POR/VBOR

• Volatile wiper register is loaded with value in the

corresponding non-volatile wiper register

• The TCON register is loaded it’s default value

• The device is capable of digital operation

voltage. Once the VDD voltage crosses

voltage the following happens:

. The Brown-out

SS

) is lower

RAM

POR/VBOR

). The

4.1.2 BROWN-OUT RESET

When the device powers down, the device VDD will

cross the V

Once the V

POR/VBOR

DD

voltage.

voltage decreases below the V

POR/VBOR

voltage the following happens:

• Serial Interface is disabled

• EEPROM Writes are disabled

If the V

voltage decreases below the V

DD

RAM

voltage

the following happens:

• Volatile wiper registers may become corrupted

• TCON register may become corrupted

As the voltage recovers above the V

POR/VBOR

voltage

see Section 4.1.1 “Power-on Reset”.

Serial commands not completed due to a brown-out

condition may cause the memory location (volatile and

non-volatile) to become corrupted.

4.2 Memory Map

The device memory is 16 locations that are 9-bits wide

(16x9 bits). This memory space contains both volatile

and non-volatile locations (see Table 4-1).

TABLE 4-1: MEMORY MAP

Address Function Memory Type

00h Volatile Wiper 0 RAM

01h Volatile Wiper 1 RAM

02h Non-Volatile Wiper 0 EEPROM

03h Non-Volatile Wiper 1 EEPROM

04h Volatile TCON Register RAM

05h Status Register RAM

06h Data EEPROM EEPROM

07h Data EEPROM EEPROM

08h Data EEPROM EEPROM

09h Data EEPROM EEPROM

0Ah Data EEPROM EEPROM

0Bh Data EEPROM EEPROM

0Ch Data EEPROM EEPROM

0Dh Data EEPROM EEPROM

0Eh Data EEPROM EEPROM

0Fh Data EEPROM EEPROM

© 2007 Microchip Technology Inc. DS22059A-page 29

Page 30

MCP414X/416X/424X/426X

4.2.1 NON-VOLATILE MEMORY

(EEPROM)

This memory can be grouped into two uses of non-volatile memory. These are:

• General Purpose Registers

• Non-V olatile W iper Registers

The non-volatile wipers starts functioning below the

devices V

POR/VBOR

trip point.

4.2.1.1 General Purpose Registers

These locations allow the user to store up to 10 (9-bit)

locations worth of information.

4.2.1.2 Non-Volatile Wiper Registers

These locations contain the wiper values that are

loaded into the corresponding volatile wiper register

whenever the device has a POR/BOR event. There are

up to two registers, one for each resistor network.

The non-volatile wiper register enables stand-alone

operation of the device (without Microcontroller control)

after being programmed to the desired value.

4.2.1.3 Factory Initialization of Non-Volatile

Memory (EEPROM)

The Non-Volatile Wiper values will be initialized to

mid-scale value. This is shown in Table 4-2.

The General purpose EEPROM memory will be

programmed to a default value of 0xFF.

It is good practice in the manufacturing flow to

configure the device to your desired settings.

TABLE 4-2: DEFAULT FACTORY

SETTINGS SELECTION

Wiper

Code

Code

Resistance

-502 5.0 kΩ Mid-scale 80h 40h Disabled

-103 10.0 kΩ Mid-scale 80h 40h Disabled

-503 50.0 kΩ Mid-scale 80h 40h Disabled

-104 100.0 kΩ Mid-scale 80h 40h Disabled

Value

AB

Typical

R

8-bit 7-bit

Default POR

Wiper Setting

WiperLock™

Technology and

4.2.1.4 Special Features

There are 3 non-volatile bits that are not directly

mapped into the address space. These bits control the

following functions:

• EEPROM Write Protect

• WiperLock Technology for Non-Volatile Wiper 0

• WiperLock Technology for Non-Volatile Wiper 1

The operation of WiperLock T echnology is discussed in

Section 5.3. The state of the WL0, WL1, and WP bits

is reflected in the STATUS register (see Register 4-1).

EEPROM Write Protect

All internal EEPROM memory can be Write Protected.

When EEPROM memory is Write Protected, Write

commands to the internal EEPROM are prevented.

Write Protect (WP

methods. These are:

• External WP

only)

• Non-Volatile configuration bit

High Voltage commands are required to enable and

disable the nonvolatile WP bit. These commands are

shown in Section 7.9 “Modify Write Protect or Wip-

erLock Technology (High Voltage)”.

To write to EEPROM, both the external WP

internal WP EEPROM bit must be disabled. Write

Protect does not block commands to the volatile

registers.

4.2.2 VOLATILE MEMORY (RAM)

There are four Volatile Memory locations. Th e se are:

• Volatile Wiper 0

• Volatile Wiper 1

(Dual Resistor Network devices only)

• Status Register

• Terminal Control (TCON) Register

The volatile memory starts functioning at the RAM

retention voltage (V

Write Protect Setting

) can be enabled/disabled by two

Hardware pin (MCP42X1 devices

pin and the

).

RAM

DS22059A-page 30 © 2007 Microchip Technology Inc.

Page 31

MCP414X/416X/424X/426X

4.2.2.1 Status (STATUS) Register

This register contains 5 status bits. These bits show the

state of the WiperLock bits, the Shutdown bit the Write

Protect bit, and if an EEPROM write cycle is active. The

STATUS register can be accessed via the READ

commands. Register 4-1 describes each STATUS

register bit.

The STATUS register is placed at Address 05h.

REGISTER 4-1: STATUS REGISTER

R-1 R-1 R-1 R-1 R-0 R-x R-x R-x R-x

D8:D5 EEWA WL1

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 8-5 D8:D5: Reserved. Forced to “1”

bit 4 EEWA: EEPROM Write Active Status bit

This bit indicates if the EEPROM Write Cycle is occurring.

1 = An EEPROM Write cycle is currently occurring. Only serial commands to the Volatile memory

locations are allowed (addresses 00h, 01h, 04h, and 05h)

0 = An EEPROM Write cycle is NOT currently occurring

bit 3 WL1: WiperLock Status bit for Resistor Network 1 (Refer to Section 5.3 “WiperLock™ Technology”

for further information)

WiperLock (WL) prevents the Volatile and Non-Volatile Wiper 1 addresses and the TCON register bits

R1HW, R1A, R1W, and R1B from being written to. High Voltage commands are required to enable and

disable WiperLock Technology.

1 = Wi per and TCON register bits R1HW, R1A, R1W, and R1B of Resistor Network 1 (Pot 1) are

“Locked” (Write Protected)

0 = Wiper and TCON of Resistor Network 1 (Pot 1) can be modified

Note: The WL1 bit always reflects the result of the last programming cycle to the non-volatile WL1

bit. After a POR or BOR event, the WL1 bit is loaded with the non-volatile WL1 bit value.

bit 2 WL0: WiperLock Status bit for Resistor Network 0 (Refer to Section 5.3 “WiperLock™ Technology”

for further information)

The WiperLock T echnology bits (WLx) prevents the V olatile and Non-V olatile Wiper 0 addresses and the

TCON register bits R0HW, R0A, R0W, and R0B from being written to. High Voltage commands are

required to enable and disable WiperLock Technology.

1 = Wi per and TCON register bits R0HW, R0A, R0W, and R0B of Resistor Network 0 (Pot 0) are

“Locked” (Write Protected)

0 = Wiper and TCON of Resistor Network 0 (Pot 0) can be modified

Note: The WL0 bit always reflects the result of the last programming cycle to the non-volatile WL0

bit. After a POR or BOR event, the WL0 bit is loaded with the non-volatile WL0 bit value.

bit 1 SHDN: Hardware Shutdown pin Status bit (Refer to Section 5.4 “Shutdown” for further information)

This bit indicates if the Hardware shutdown pin (SHDN

T erminal A and forces the wiper (Terminal W) to T erminal B (see Figure 5-2). While the device is in Hardware Shutdown (the SHDN

read.

1 = MCP4XXX is in the Hardware Shutdown state

0 = MCP4XXX is NOT in the Hardware Shutdown state

Note 1: Requires a High Voltage command to modify the st ate of this bit (for Non-V olatile devices only). This bit is

Not directly written, but reflects the system state (for this feature).

pin is low) the serial interface is operational so the STATUS register may be

(1)

) is low. A hardware shutdown disconnects the

WL0

(1)

SHDN WP

(1)

© 2007 Microchip Technology Inc. DS22059A-page 31

Page 32

MCP414X/416X/424X/426X

REGISTER 4-1: STATUS REGISTER (CONTINUED)

bit 0 WP: EEPROM Write Protect Status bit (Refer to Section “EEPROM Write Protect” for further infor-

mation)

This bit indicates the status of the write protection on the EEPROM memory. When Write Protect is

enabled, writes to all non-volatile memory are prevented. This includes the General Purpose EEPROM

memory, and the non-volatile Wiper registers. Write Protect does not block modification of the volatile

wiper register values or the volatile TCON register value (via Increment, Decrement, or Write

commands).

This status bit is an OR of the devices Write Protect pin (WP

Voltage commands are required to enable and disable the internal WP EEPROM bit.

1 = EEPROM memory is Write Protected

0 = EEPROM memory can be written

Note 1: Requires a High Voltage command to modify the st ate of this bit (for Non-V olatile devices only). This bit is

Not directly written, but reflects the system state (for this feature).

) and the internal non-volatile WP bit. High

DS22059A-page 32 © 2007 Microchip Technology Inc.

Page 33

MCP414X/416X/424X/426X

4.2.2.2 Terminal Control (TCON) Register

This register contains 8 control bits. Four bits are for

Wiper 0, and four bits are for Wiper 1. Register 4-2

describes each bit of the TCON register.

The state of each resistor network terminal connection

is individually controlled. That is, each terminal connection (A, B and W) can be individually connected/disconnected from the resistor network. This allows the

system to minimize the currents through the digital

potentiometer.

REGISTER 4-2: TCON BITS

R-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1

D8 R1HW R1A R1W R1B R0HW R0A R0W R0B

bit 8 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 8 D8: Reserved. Forced to “1”

bit 7 R1HW: Resistor 1 Hardware Configuration Control bit

This bit forces Resistor 1 into the “shutdown” configuration of the Hardware pin

1 = Resistor 1 is NOT forced to the hardware pin “shutdown” configuration

0 = Resistor 1 is forced to the hardware pin “shutdown” configuration

bit 6 R1A: Resistor 1 Terminal A (P1A pin) Connect Control bit

This bit connects/disconnects the Resistor 1 Terminal A to the Resisto r 1 Network

1 = P1A pin is connected to the Resistor 1 Network

0 = P1A pin is disconnected from the Resistor 1 Network

bit 5 R1W: Resistor 1 Wiper (P1W pin) Connect Control bit

This bit connects/disconnects the Resistor 1 Wiper to the Resistor 1 Network

1 = P1W pin is connected to the Resistor 1 Network

0 = P1W pin is disconnected from the Resistor 1 Network

bit 4 R1B: Resistor 1 Terminal B (P1B pin) Connect Control bit

This bit connects/disconnects the Resistor 1 Terminal B to the Resisto r 1 Network

1 = P1B pin is connected to the Resistor 1 Network

0 = P1B pin is disconnected from the Resistor 1 Network

bit 3 R0HW: Resistor 0 Hardware Configuration Control bit

This bit forces Resistor 0 into the “shutdown” configuration of the Hardware pin

1 = Resistor 0 is NOT forced to the hardware pin “shutdown” configuration

0 = Resistor 0 is forced to the hardware pin “shutdown” configuration

bit 2 R0A: Resistor 0 Terminal A (P0A pin) Connect Control bit

This bit connects/disconnects the Resistor 0 Terminal A to the Resisto r 0 Network

1 = P0A pin is connected to the Resistor 0 Network