Page 1

MCP2515

带有 SPI 接口的独立 CAN 控制器

特性

• 完全支持 CAN V2.0B 技术规范,通讯速率为

1Mb/s:

-0-8 字节长的数据字段

- 标准和扩展数据帧及远程帧

• 接收缓冲器、验收屏蔽寄存器和验收滤波寄存器:

- 两个接收缓冲器,可优先存储报文

- 六个 29 位验收滤波寄存器

- 二个 29 位验收屏蔽寄存器

• 对头两个数据字节进行滤波 (针对标准数据帧)

• 三个发送缓冲器,具有优先级设定及发送中止功能

• 高速 SPI 接口 (10 MHz):

- 支持 0,0 和 1,1 的 SPI 模式

• 单触发模式确保报文发送只尝试一次

• 带有可编程预分频器的时钟输出引脚:

- 可用作其他器件的时钟源

• 可用起始帧信号 (Start-of-Frame, SOF),用于

监控 SOF 信号:

- 可用于时隙协议和/或总线诊断以检测早期总

线性能退化

• 带有可选使能设定的中断输出引脚

• “缓冲器满”输出引脚可配置为:

- 各接收缓冲器的中断引脚

- 通用数字输出引脚

• “请求发送 (Request-to-Send, RTS)”输入引

脚可各自配置为:

- 各发送缓冲器的控制引脚,用于请求立即发送

报文

- 通用数字输入引脚

• 低功耗的 CMOS 技术:

- 工作电压范围 2.7V 至 5.5V

-5mA典型工作电流

-1µA典型待机电流 (休眠模式)

• 工作温度范围:

- 工业级 (I):-40°C 至 +85°C

- 扩展级 (E): -40°C 至 +125°C

说明

Microchip 的 MCP2515 是一款独立控制器局域网络

(Controller Area Network, CAN)协议控制器,完全

支持 CAN V2.0B 技术规范。该器件能发送和接收标准

和扩展数据帧以及远程帧。 MCP2515 自带的两个验收

屏蔽寄存器和六个验收滤波寄存器可以过滤掉不想要的

报文,因此减少了主单片机(MCU)的开销。MCP2515

与 MCU 的连接是通过业界标准串行外设接口 (Searial

Peripheral Interface, SPI)来实现的。

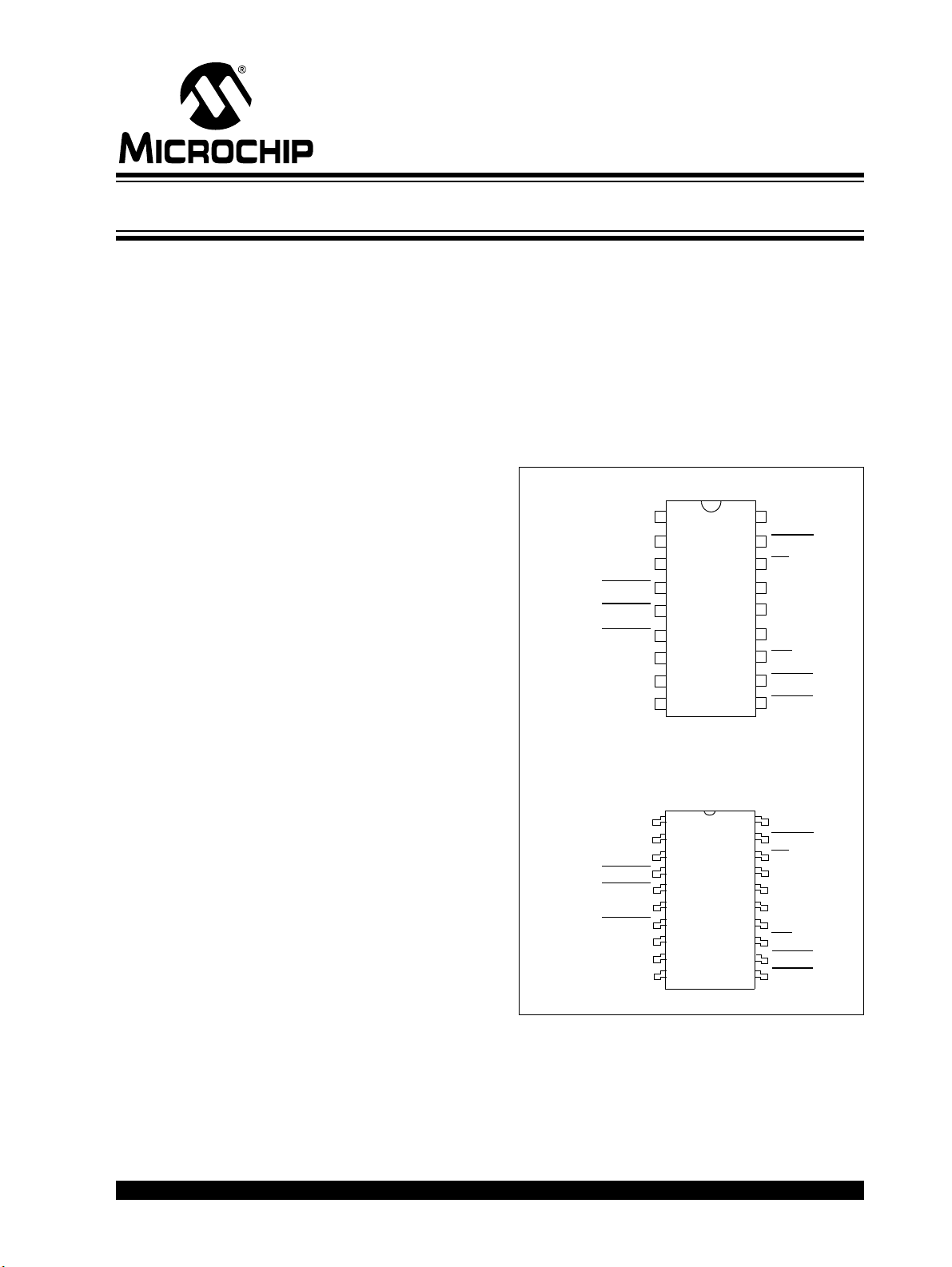

封装类型

18 引脚 PDIP/SOIC

TXCAN

RXCAN

CLKOUT/SOF

TX0RTS

TX1RTS

TX2RTS

OSC2

OSC1

20 引脚 TSSOP

TXCAN

RXCAN

CLKOUT/SOF

TX0RTS

TX1RTS

TX2RTS

OSC2

OSC1

VSS

Vss

NC

10

1

2

3

4

5

6

MCP2515

7

8

9

1

2

3

4

5

6

7

8

MCP2515

9

18

17

16

15

14

13

12

11

10

20

19

18

17

16

15

14

13

12

11

DD

V

RESET

CS

SO

SI

SCK

INT

RX0BF

RX1BF

VDD

RESET

CS

SO

SI

NC

SCK

INT

RX0BF

RX1BF

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 1 页

Page 2

MCP2515

注:

DS21801D_CN 第 2 页 初稿 2005 Microchip Technology Inc.

Page 3

MCP2515

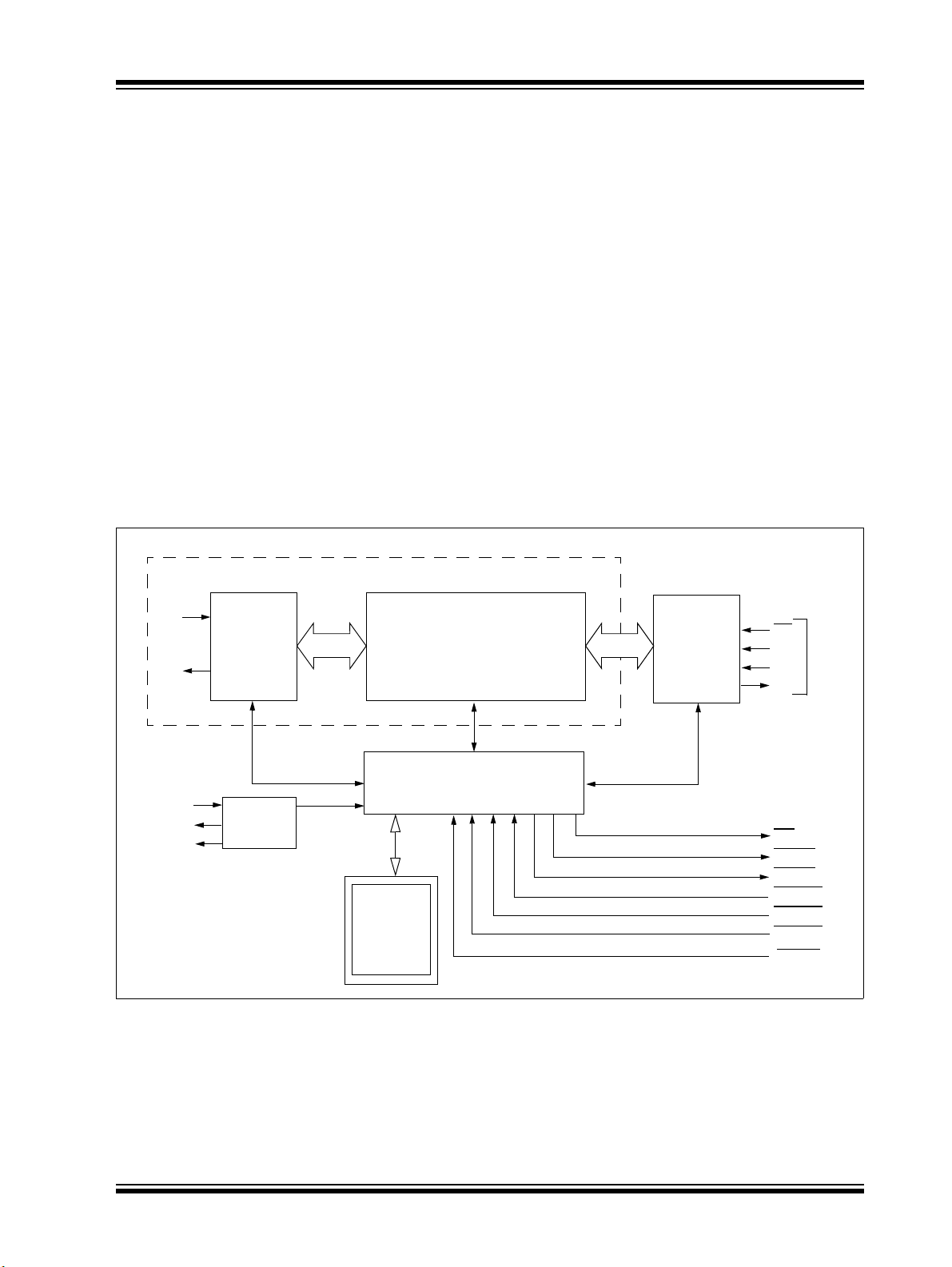

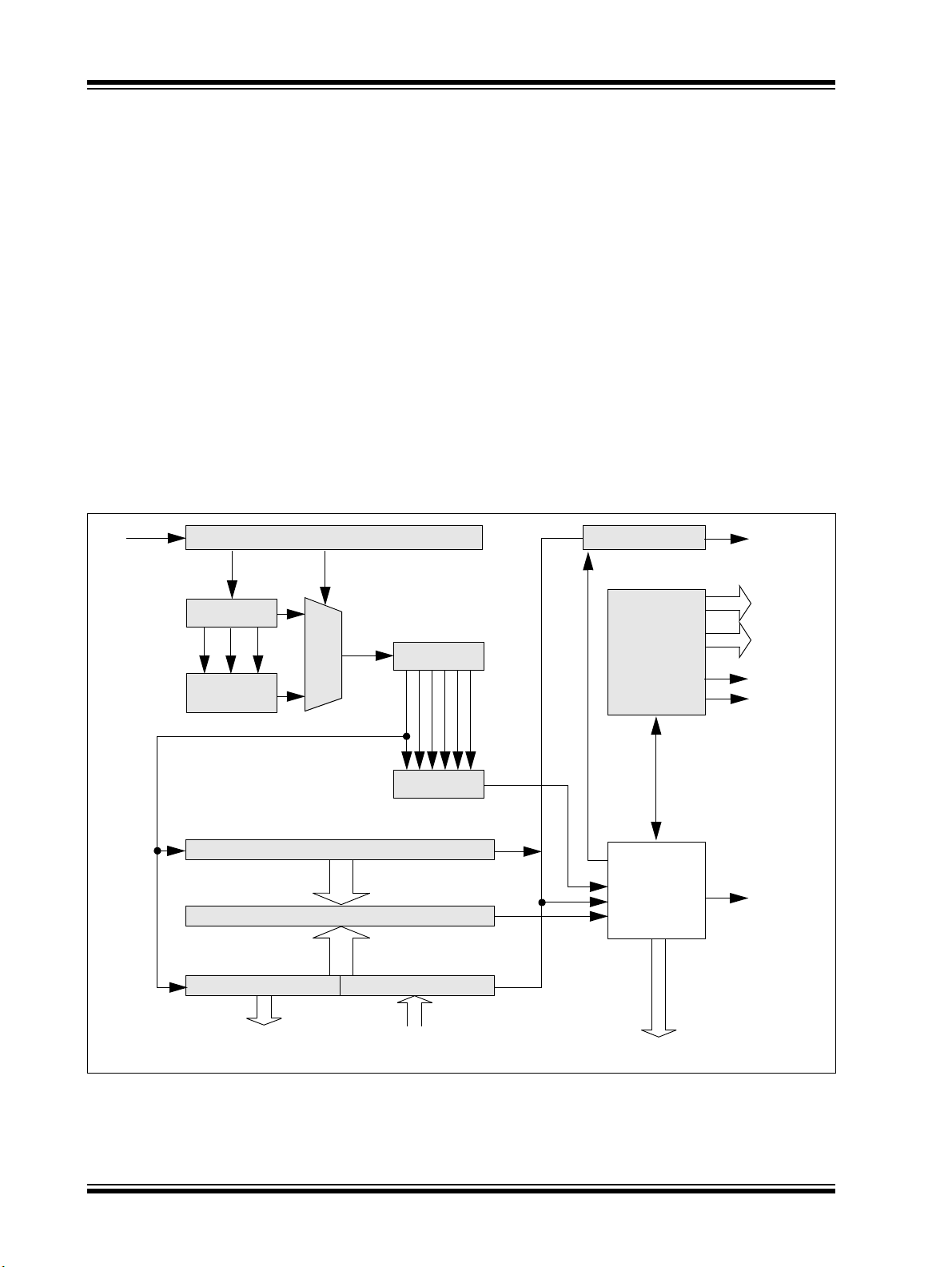

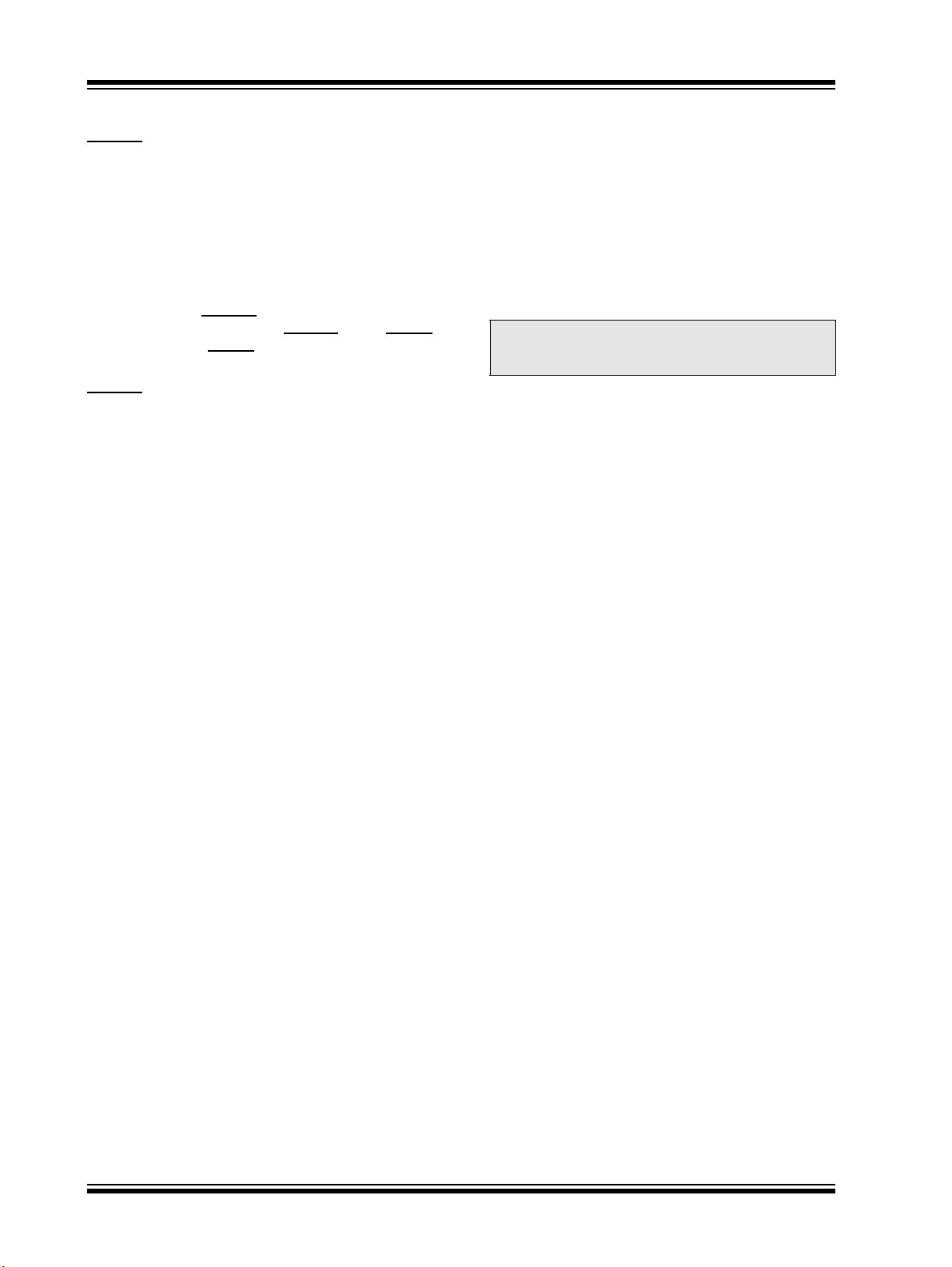

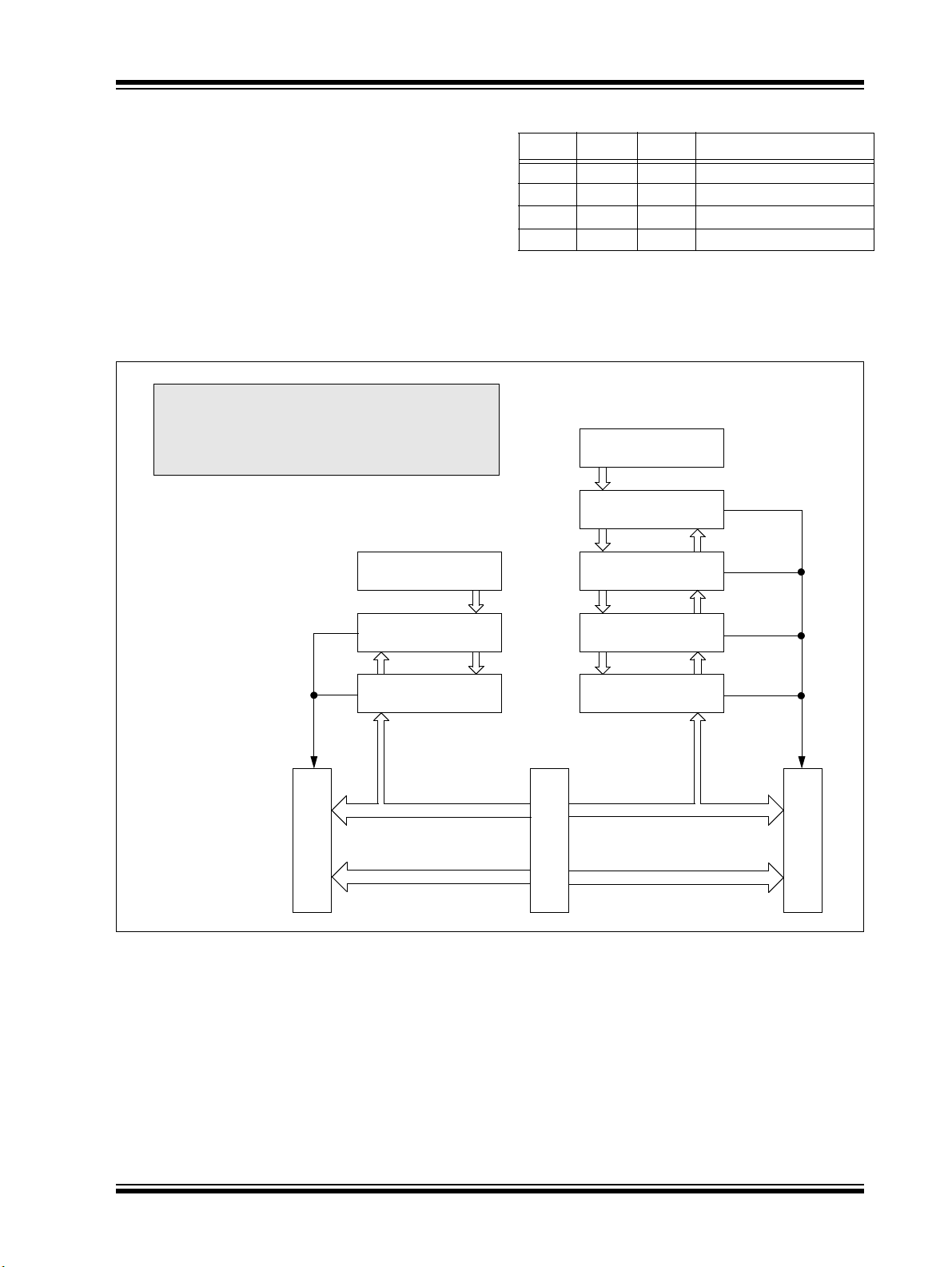

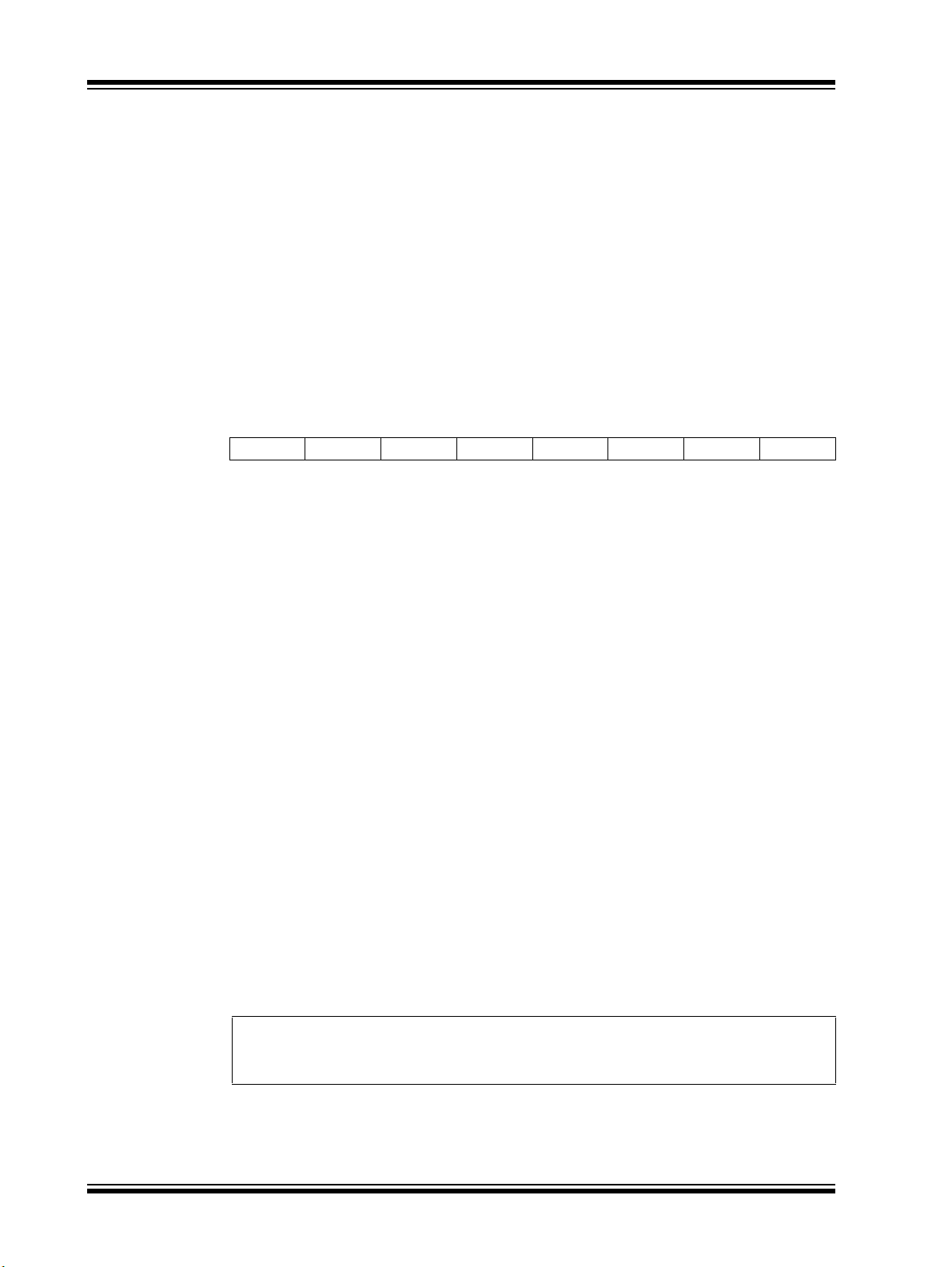

1.0 器件概述

MCP2515 是一款独立CAN 控制器,可简化需要与 CAN

总线连接的应用。图 1-1 简要显示了 MCP2515 的结构

框图。该器件主要由三个部分组成:

1. CAN 模块,包括 CAN 协议引擎、验收滤波寄存

器、验收屏蔽寄存器、发送和接收缓冲器。

2. 用于配置该器件及其运行的控制逻辑和寄存器。

3. SPI 协议模块。

图 1-2 显示了该器件的典型系统应用。

1.1 CAN 模块

CAN 模块的功能是处理所有 CAN 总线上的报文接收和

发送。报文发送时,首先将报文装载到正确的报文缓冲

器和控制寄存器中。通过 SPI 接口设置控制寄存器中的

相应位或使用发送使能引脚均可启动发送操作。通过读

取相应的寄存器可以检查通讯状态和错误。会对在 CAN

总线上检测到的任何报文进行错误检查,然后与用户定

义的滤波器进行匹配,以确定是否将报文移到两个接收

缓冲器中的一个。

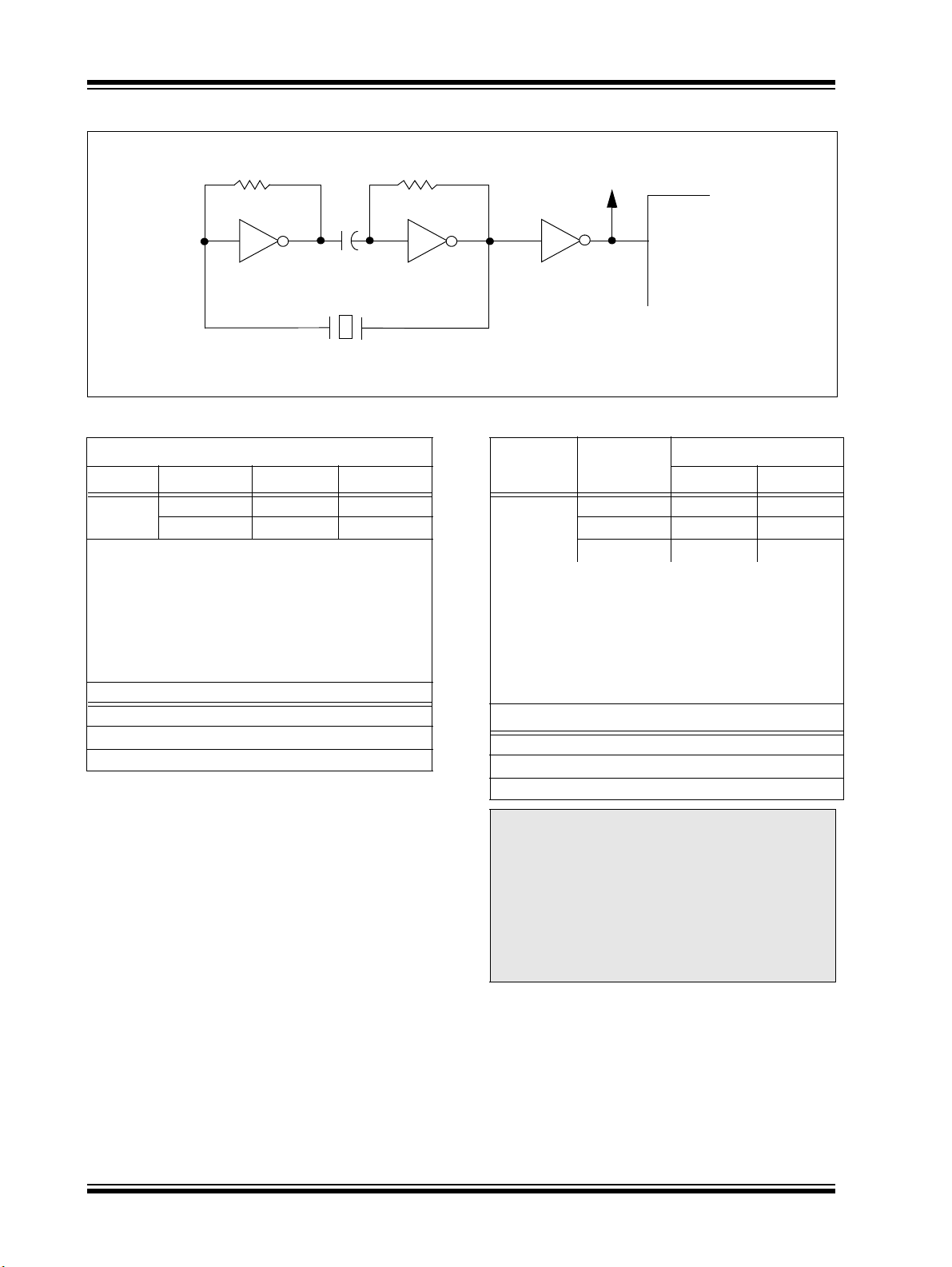

图 1-1: 结构框图

CAN 模块

1.2 控制逻辑

通过与其他模块连接,控制逻辑模块控制 MCP2515 的

设置和运行,以便传输信息与控制。

所提供的中断引脚提高了系统的灵活性。器件上有一个

多用途中断引脚及各接收缓冲器的专用中断引脚,用于

指示有效报文是否被接收并载入接收缓冲器。可选择使

用专用中断引脚。通用中断引脚和状态寄存器 (通过

SPI 接口访问)也可用来确定何时接收了有效报文。

器件还有三个引脚,用来启动将装载在三个发送缓冲器

之一中的报文立即发送出去。是否使用这些引脚由用户

决定;若不使用,也可利用控制寄存器(通过 SPI 接口

访问)来启动报文发送。

1.3 SPI 协议模块

MCU通过SPI接口与该器件连接。使用标准的SPI读/写

指令以及专门的 SPI 命令来读 / 写所有的寄存器。

RXCAN

TXCAN

OSC1

OSC2

CLKOUT

CAN

协议

引擎

时序

发生器

控制

和

中断

寄存器

发送和接收缓冲器

验收屏蔽寄存器和

验收滤波器

控制逻辑

SPI

接口

逻辑

CS

SCK

SI

SO

INT

RX0BF

RX1BF

TX0RTS

TX1RTS

TX2RTS

RESET

SPI

总线

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 3 页

Page 4

MCP2515

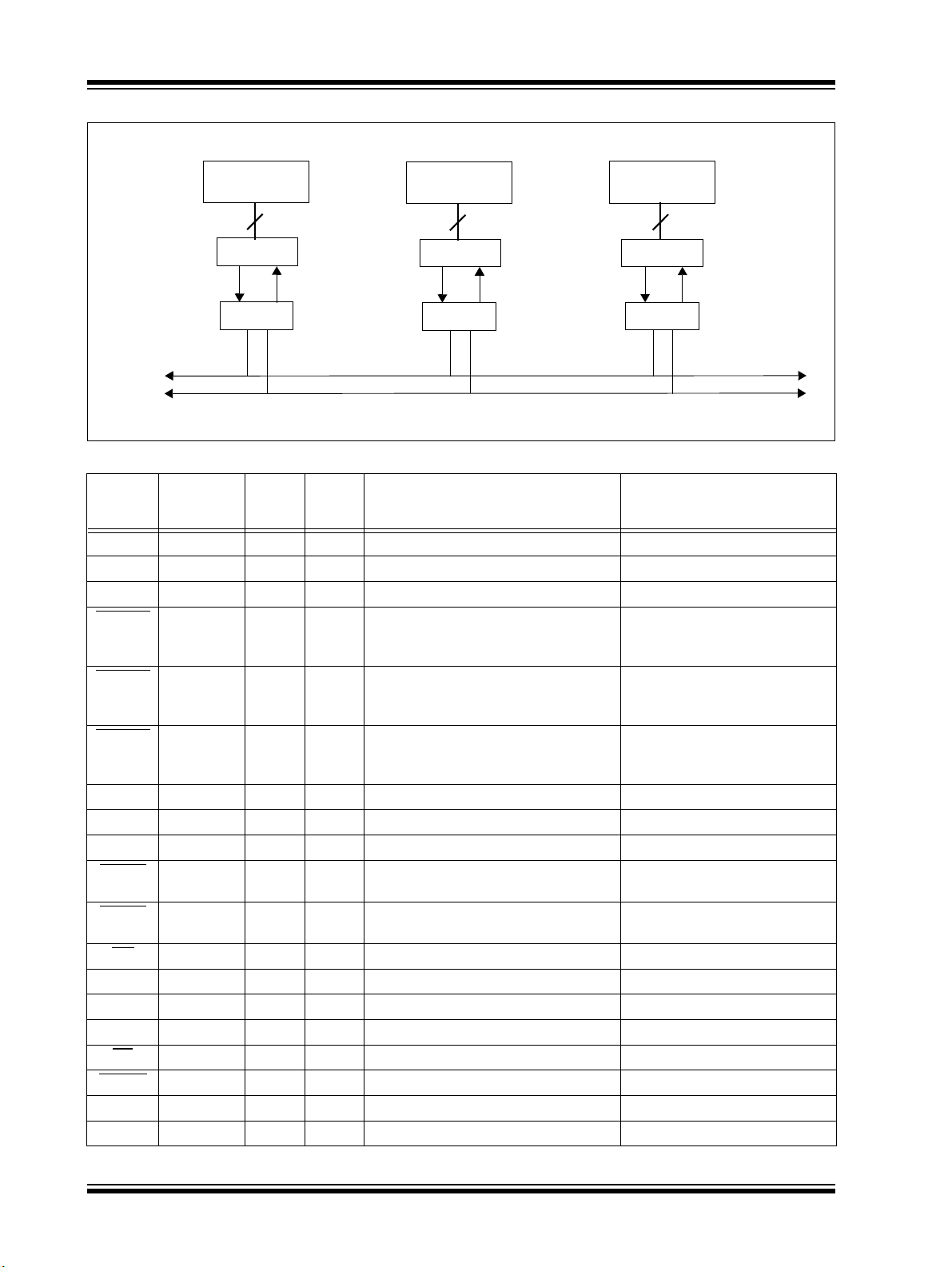

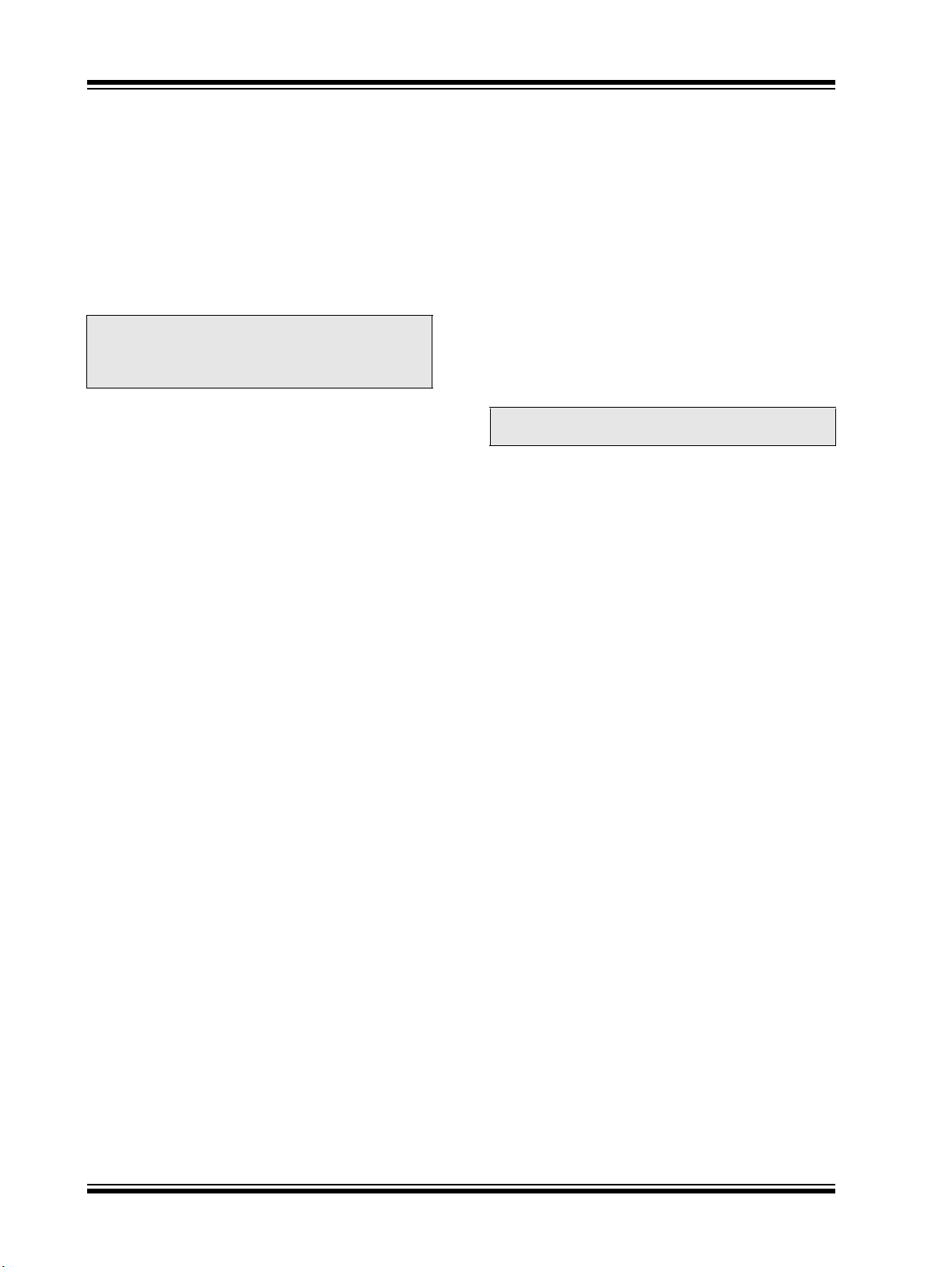

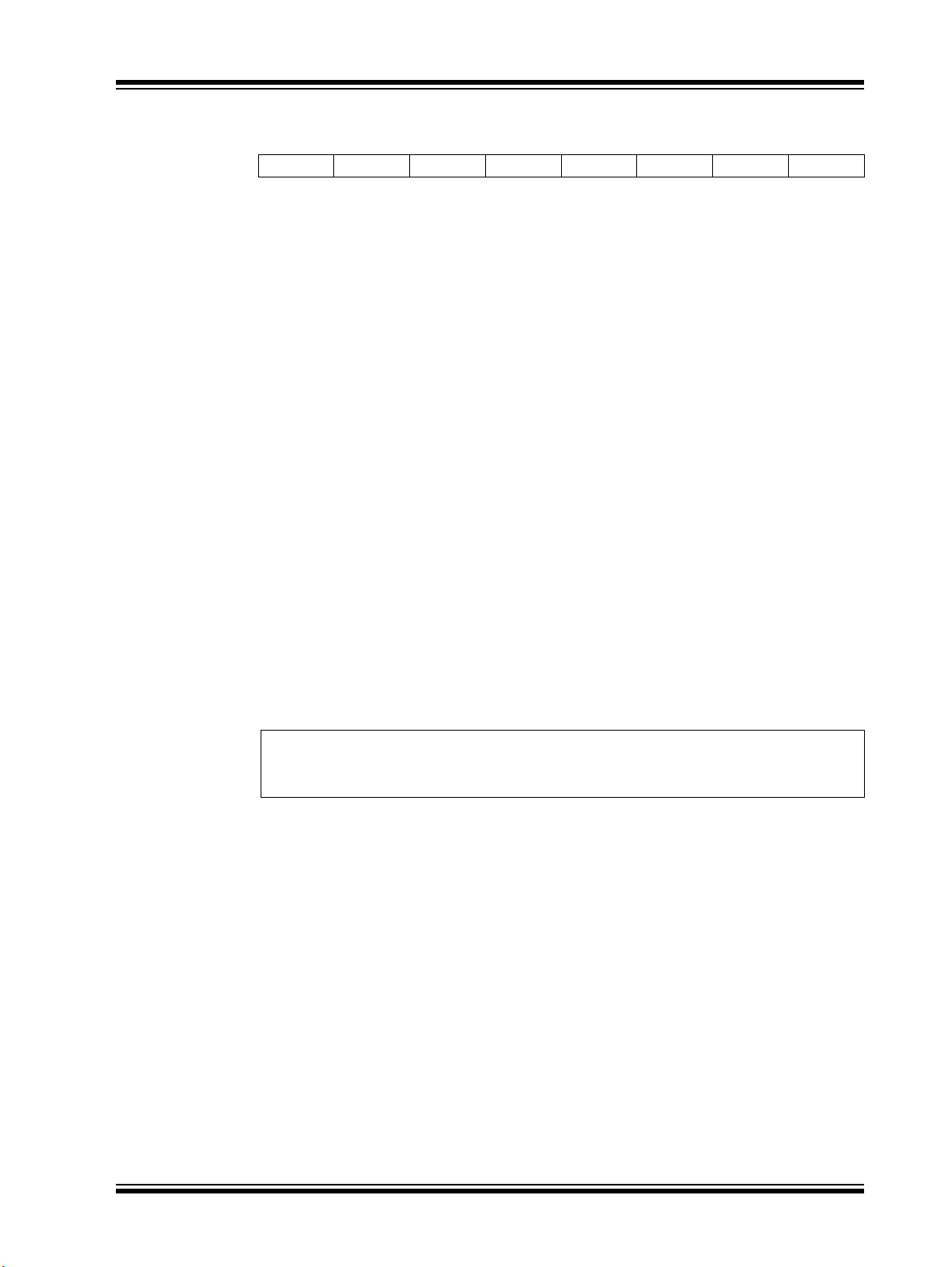

图 1-2: 典型系统实现方法图

CANH

CANL

节点

控制器

SPI

MCP2515

TX

XCVR

RX

节点

控制器

SPI

MCP2515

TX

XCVR

RX

节点

控制器

SPI

MCP2515

TX

XCVR

RX

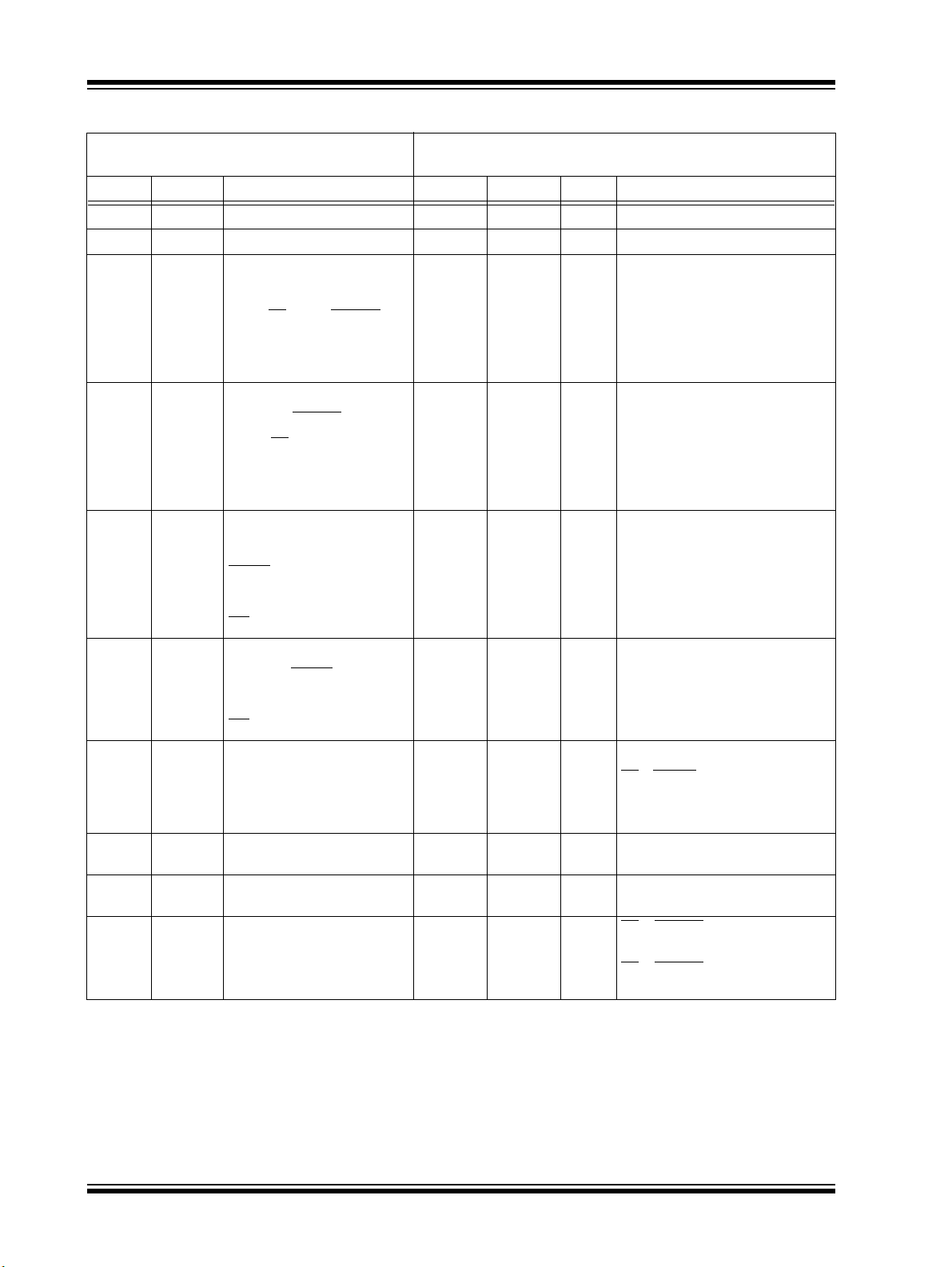

表 1-1: 引脚说明

名称

TXCAN 1 1 O 连接到 CAN 总线的发送输出引脚 —

RXCAN 2 2 I 连接到 CAN 总线的接收输入引脚 —

CLKOUT 3 3 O 带可编程预分频器的时钟输出引脚 起始帧信号

TX0RTS

TX1RTS

TX2RTS

OSC2 7 8 O 振荡器输出 —

OSC1 8 9 I 振荡器输入 外部时钟输入引脚

V

RX1BF 10 11 O 接收缓冲器 RXB1 中断引脚或通用数字

RX0BF

INT

SCK 13 14 I SPI 接口的时钟输入引脚 —

SI 14 16 I SPI 接口的数据输入引脚 —

SO 15 17 O SPI 接口的数据输出引脚 —

CS 16 18 I SPI 接口的片选输入引脚 —

RESET

VDD 18 20 P 逻辑和 I/O 引脚的正电源 —

NC — 6,15 — 无内部连接

PDIP/SOIC

引脚号

44I发送缓冲器 TXB0 请求发送引脚或通用

55I发送缓冲器 TXB1 请求发送引脚或通用

67I发送缓冲器 TXB2 请求发送引脚或或通

SS 910P逻辑和 I/O 引脚的参考地 —

11 1 2 O 接收缓冲器 RXB0 中断引脚或通用数字

12 13 O 中断输出引脚 —

17 19 I 低电平有效的器件复位输入引脚 —

TSSOP

引脚号

I/O/P

类型

说明 备选引脚功能

数字输入引脚。 V

上拉电阻

数字输入引脚。 V

上拉电阻

用数字输入引脚。 V

部上拉电阻

输出引脚

输出引脚

DD

DD

上连 100kΩ 内部

上连 100kΩ 内部

上连 100kΩ 内

DD

通用数字输入引脚。

VDD 上连 100 kΩ 内部上拉电阻

通用数字输入引脚。

VDD 上连 100 kΩ 内部上拉电阻

通用数字输入引脚。

VDD 上连 100 kΩ 内部上拉电阻

通用数字输出引脚

通用数字输出引脚

注: 类型标识:I = 输入; O = 输出; P = 电源

DS21801D_CN 第 4 页 初稿 2005 Microchip Technology Inc.

Page 5

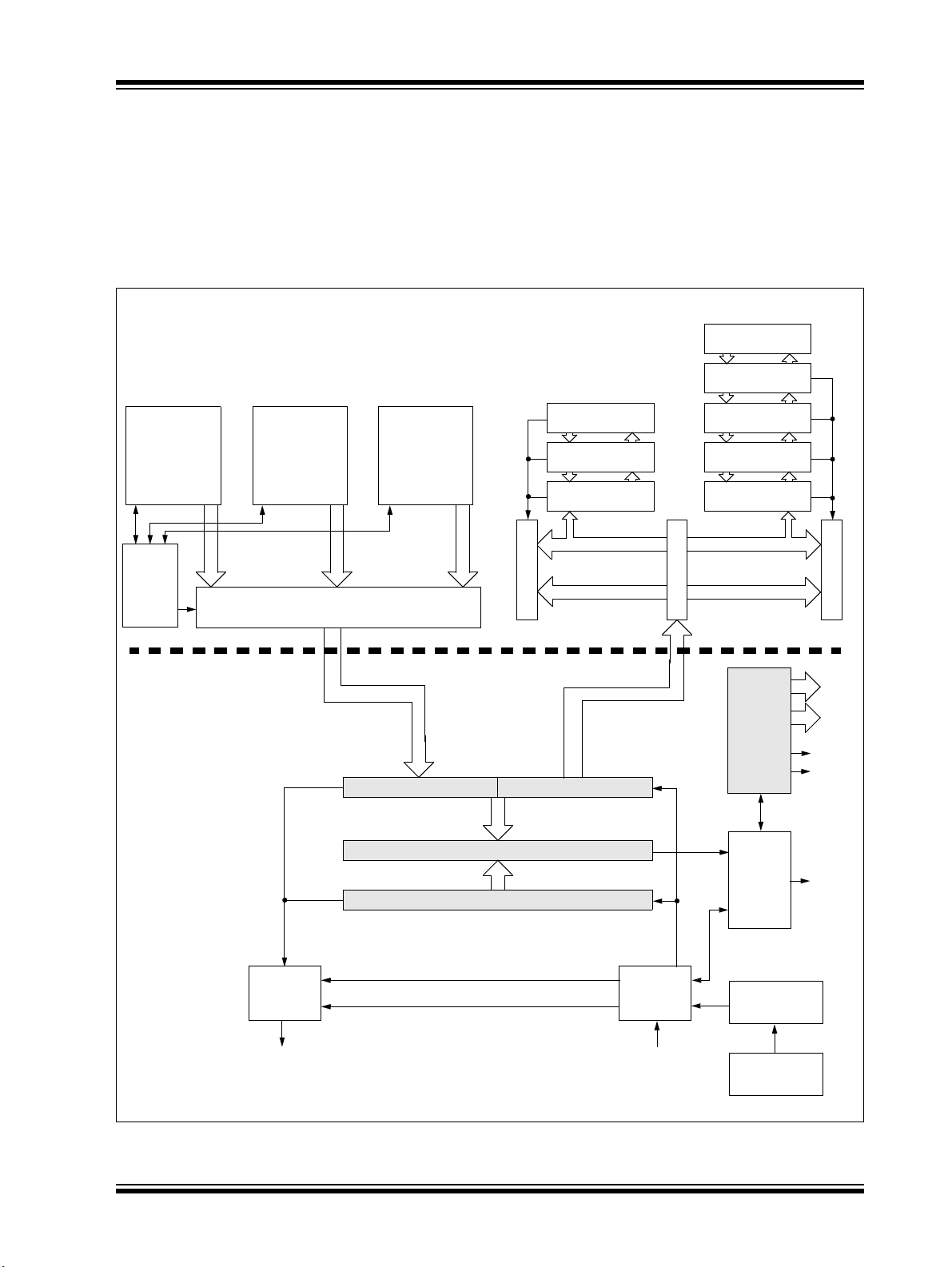

1.4 发送 / 接收缓冲器/验收屏蔽寄存器

/验收滤波寄存器

MCP2515 有三个发送缓冲器和两个接收缓冲器,两个

验收屏蔽寄存器(分别对应不同的接收缓冲器)以及六

个验收滤波寄存器。图 1-3 的框图显示了这些缓冲器及

它们与 CAN 协议引擎的连接方法。

图 1-3: CAN 缓冲器和协议引擎框图

MCP2515

缓冲器

TXB0

TXREQ

ABTF

MLOA

TXERR

报文

队列

控制

协议

引擎

验收屏蔽寄存器

RXM1

验收滤波寄存器

RXF2

M

A

B

验收滤波寄存器

RXF3

验收滤波寄存器

RXF4

验收滤波寄存器

RXF5

标识符

接收

错误

计数器

发送

错误

计数器

协议

有限

状态

机

TXB1

TXB2

接

受

TXREQ

ABTF

MLOA

TXERR

MESSAGE

TXREQ

ABTF

MLOA

TXERR

MESSAGE

发送字节序列发生器

{ 发送 <5:0>,接 收 <8:0>}

移位 <14:0>

MESSAGE

比较器

CRC<14:0>

验收屏蔽寄存器

验收滤波寄存器

验收滤波寄存器

R

X

B

0

接收 <7:0> 发送 <7:0>

RXM0

RXF0

RXF1

标识符

数据字段 数据字段

接

受

R

X

B

1

REC

TEC

ErrPas

BusOff

SOF

发送

逻辑

TX RX

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 5 页

位

时序

逻辑

时钟

发生器

配置

寄存器

Page 6

MCP2515

1.5 CAN 协议引擎

CAN 协议引擎包含数个功能模块,见图 1-4。下面将对

这些模块及其功能进行介绍。

1.5.1 协议有限状态机

协议引擎的核心是有限状态机 (Finite State Machine,

FSM)。FSM 是一个定序器,对 TX/RX 移位寄存器、循

环冗余校验 (Cyclic Redundancy Check, CRC)寄存

器和总线之间的顺序数据流进行控制。 FSM 还对错误

管理逻辑(Error Management Logic,EML)及 TX/RX

移位寄存器和缓冲器之间的并行数据流进行控制。FSM

确保了依据 CAN 协议,进行报文接收、总线仲裁、报

文发送以及错误信号发生等操作过程。 FSM 还对总线

上报文的自动重发进行处理。

1.5.2 循环冗余校验

循环冗余校验寄存器产生循环冗余校验 (CRC)代码。

该代码在控制字段(数据字节数为 0 的报文)或数据字

段之后被发送,并用来检查进入报文的 CRC 字段。

图 1-4: CAN 协议引擎框图

RX

采样 <2:0>

多数

决定

位时序逻辑

SAM

StuffReg<5:0>

1.5.3 错误管理逻辑

错误管理逻辑 (EML)负责将 CAN 器件的故障进行隔

离。该逻辑有两个计数器,即接收错误计数器(Receive

Error Counter, REC)和发送错误计数器 (Transmit

Error Counter, TEC)。这两个计数器根据来自位流处

理器的命令进行增减计数。根据错误计数器的计数值,

CAN 控制器将被设定为错误主动、错误被动或总线关闭

三种状态。

1.5.4 位时序逻辑

位时序逻辑 (Bit Timing Logic, BTL)可监控总线输

入,并根据 CAN 协议处理与总线相关的位时序操作。

BTL 在起始帧时,对从隐性状态到显性状态的总线过渡

进行同步操作 (称为硬同步)。如果 CAN 控制器本身

不发送显性位,则在以后的隐性状态到显性状态总线过

渡时会再进行同步操作(称为再同步)。BTL 还提供可

编程时间段以补偿传播延迟时间和相位位移,并对位时

段内的采样点位置进行定义。对 BTL 的编程取决于波特

率和外部物理延迟时间。

发送逻辑

接收

错误计数器

发送

错误计数器

TX

REC

TEC

ErrPas

BusOff

BusMon

比较器

CRC<14:0>

比较器

(发送 <5:0>,接 收 <7:0>)

接收 <7:0> 发送 <7:0>

RecData<7:0>

连接到标准缓冲器

移位 <14:0>

TrmData<7:0>

协议

FSM

接收 / 发送地址

SOF

DS21801D_CN 第 6 页 初稿 2005 Microchip Technology Inc.

Page 7

MCP2515

2.0 CAN 报文帧

MCP2515支持 CAN 2.0B 技术规范中所定义的标准数据

帧、扩展数据帧和远程帧 (标准和扩展)。

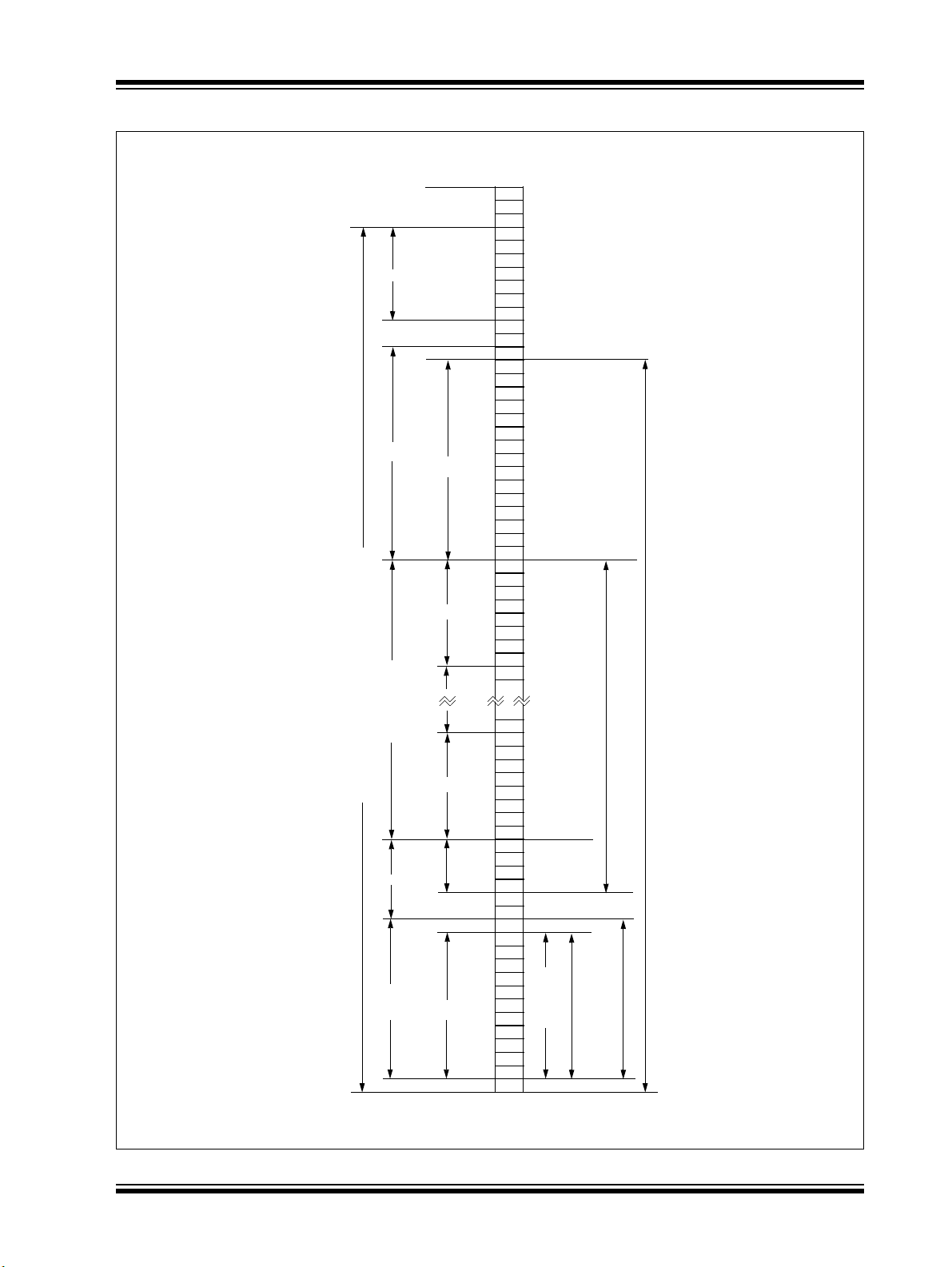

2.1 标准数据帧

CAN 标准数据帧如图 2-1 所示。与其他所有帧一样,帧

以起始帧 (SOF)位开始, SOF 为显性状态,允许所

有节点的硬同步。

SOF之后是仲裁字段,由12个位组成,分别为 11 个标识

位和一个远程发送请求 (Remote Transmission

Request, RTR)位。 RTR 位用于区分报文是数据帧

(RTR 位为显性状态)还是远程帧 (RTR 位为隐性状

态)。

仲裁字段之后是控制字段,由 6 个位组成。控制字段的

第一位为标识扩展(Identifier Extension, IDE)位 ,该

位应是显性状态来指定标准帧。标识扩展位的下一位为

零保留位(RB0),CAN 协议将其定义为显性位。控制

字段的其余 4 位为数据长度码 (Data Length Code,

DLC),用来指定报文中包含的数据字节数 (0 到 8 字

节)。

控制字段之后为数据字段,包含要发送的任何数据字

节。数据字段长度由上述 DLC 定义 (0 到 8 字节)。

数据字段之后为循环冗余校验(CRC)字段,用来检测

报文传输错误。CRC 字段包含一个 15 位的 CRC 序列,

之后是隐性的 CRC 定界位。

最后一个字段是确认字段 (ACK), 由 2 个位组成。在

确认时隙(ACK Slot)位执行期间,发送节点发出一个

隐性位。任何收到无错误帧的节点会发回一个显性位

(无论该节点是否配置为接受该报文与否)来确认帧收

到无误。确认字段以隐性确认定界符结束,该定界符可

能不允许被改写为显性位。

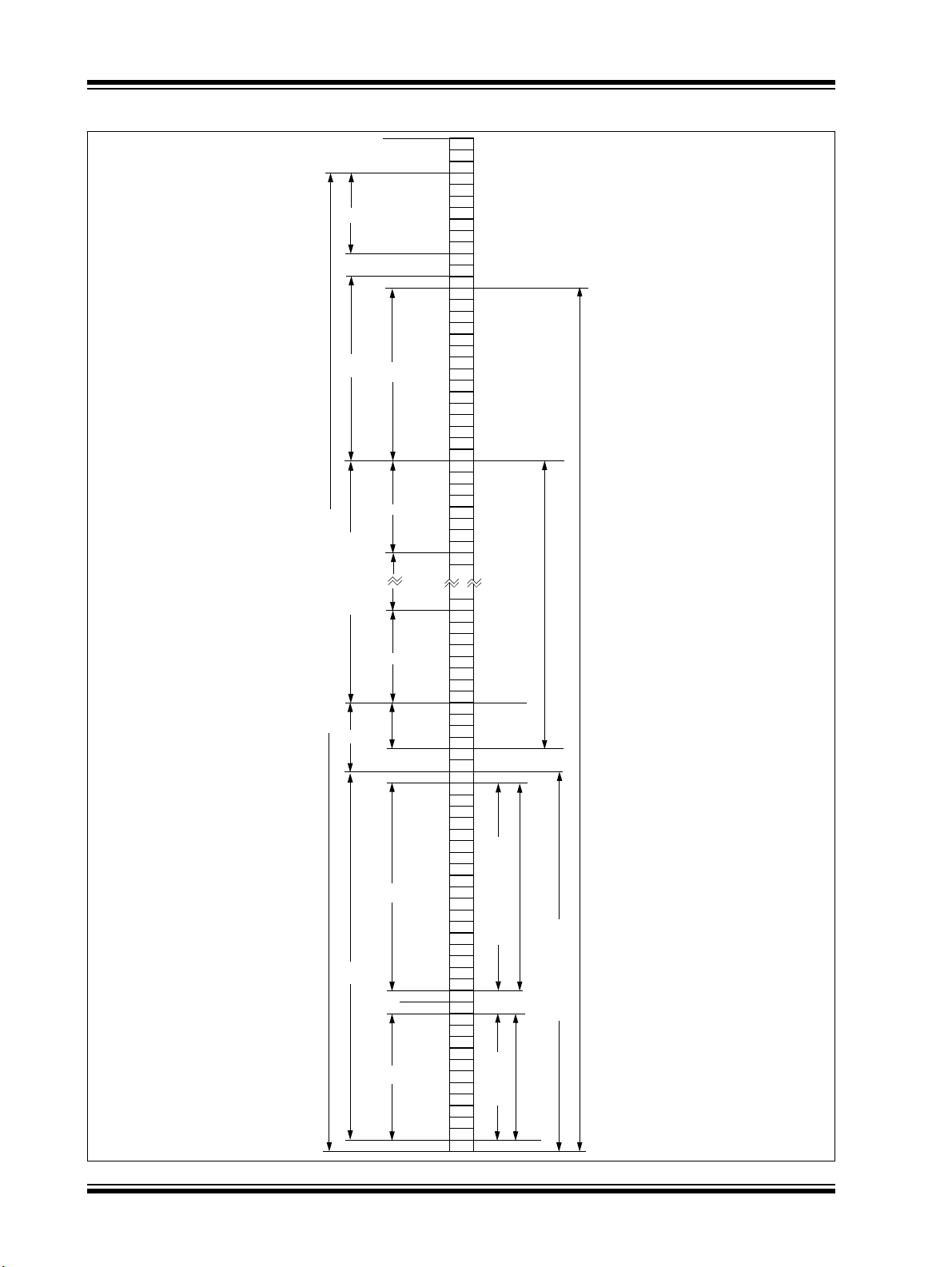

SRR 和 lDE位之后是标识符的其余 18 位(扩展lD)及一

个远程发送请求位。

为使标准帧和扩展帧都能在共享网络上发送,应将29位

扩展报文标识符拆成高 11 位和低 18 位两部分。拆分后

可确保 lDE 位在标准数据帧和扩展数据帧中的位置保持

一致。

仲裁字段之后是 6 位控制字段。控制字段前两位为保留

位,必须定义为显性位。其余 4 位为 DLC,用来指定报

文中包含的数据字节数。

扩展数据帧的其他部分 (数据字段、 CRC 字段、确认

字段、帧结尾和间断)与标准数据帧的结构相同 (见第

2.1 节 “标准数据帧”)。

2.3 远程帧

通常,数据传输是由数据源节点(例如,传感器发出数

据帧)自主完成的。但也可能存在目标节点向源节点请

求发送数据的情况。要做到这一点,目标节点需发送一

个远程帧,其中的标识符应与所需数据帧的标识符相匹

配。随后,相应的数据源节点会发送一个数据帧以响应

远程帧请求。

远程帧 (如图 2-3 所示)与数据帧存在两点不同:1)

远程帧的 RTR 位为隐性状态; 2)远程帧没有数据字

段。当带有相同标识符的数据帧和远程帧同时发出时,

数据帧将赢得仲裁,因为其标识符后面的 RTR 位为显

性。这样,可使发送远程帧的节点立即收到所需数据。

2.4 错误帧

错误帧是由检测到总线错误的任一节点产生。如图 2-4

所示,错误帧包含两个字段:错误标志字段及紧随其后

的错误定界字段。错误标志字段有两种类型。节点发送

哪种类型的错误标志字段,取决于检测到错误并产生错

误标志字段的节点的错误状态。

2.2 扩展数据帧

在扩展 CAN 数据帧中(如图 2-2 所示),紧随 SOF 位

的是 32 位的仲裁字段。仲裁字段的前 11 位为 29 位标

识符的最高有效位(Most Significant bit,MSb)(基本

lD)。紧随这 11 位的是替代远程请求 (Substitute

Remote Request, SRR)位,定义为隐性状态。 SRR

位之后是 lDE 位,该位为隐性状态时表示这是扩展的

CAN 帧。

应该注意的是,如果发送完扩展帧标识符的前 11 位后,

总线仲裁无果,而此时其中一个等待仲裁的节点发出标

准 CAN 数据帧 (11 位标识符),那么,由于节点发出

了显性 lDE 位而使标准 CAN 帧赢得总线仲裁。另外,

扩展 CAN 帧的 SRR 位应为隐性,以允许正在发送标准

CAN 远程帧的节点发出显性 RTR 位。

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 7 页

Page 8

MCP2515

2.4.1 主动错误

当错误主动节点检测到一个总线错误时,这个节点将产

生一个主动错误标志来中断当前的报文发送。主动错误

标志由 6 个连续的显性位构成。这种位序列主动打破了

位填充规则。所有其他节点在识别到所生成的位填充错

误后,会自行产生错误帧,称为错误反射标志。

错误标志字段因此包含 6 到 12 个连续显性位 (由 1 个

或多个节点产生)。错误定界字段 (8 个隐性位)为错

误帧划上句号。在错误帧发送完毕后,总线主动恢复正

常状态,被中断的节点会尝试重新发送被中止的报文。

注: 在局部干扰导致一个或多个 (但非全部)

节点发送错误标志时通常会产生错误反射

标志。其他节点产生错误标志作为对最初

错误标志的响应 (反射)。 .

2.4.2 被动错误

当错误被动节点检测到一个总线错误时,该节点将发送

一个被动错误标志,并紧接着发送错误定界字段。错误

被动标志由 6 个连续的隐性位构成,而错误被动节点发

出的错误帧包含 14 个隐性位。由此可知,除非总线错误

被错误主动节点或正在发送报文的节点检测到,否则由

于错误被动标志不会影响总线运行,将继续发送报文。

如果发送节点产生一个错误被动标志,那么,由于位填

充规则被打破,将导致其他节点产生错误帧。错误帧发

送完毕后,错误被动节点必须等待总线上出现 6 个连续

隐性位后,才能尝试重新参与总线通讯。

错误定界符由 8 个隐性位组成,允许总线节点在错误发

生后重新启动总线通讯。

2.5 过载帧

如图 2-5 所示,过载帧与主动错误帧具有相同的格式。

但是,过载帧只能在帧间间隔产生,因此可通过这种方

式区分过载帧和错误帧 (错误帧是在帧传输时发出

的)。过载帧由两个字段组成,即过载标志和随后的过

载定界符。过载标志由 6 个显性位和紧随其后的其他节

点产生的过载标志构成 (而主动错误标志最多包含 12

个显性位)。过载定界符包含 8 个隐性位。节点在两种

情况下会产生过载帧:

1. 节点在帧间间隔检测到非法显性位。在 IFS 的第

三位期间检测到显性位除外。这种情况下,接收

器会把它看作一个 SOF 信号。

2. 由于内部原因,节点尚无法开始接收下一条报

文。节点最多可产生两条连续的过载帧来延迟下

一条报文的发送。

注: 由于内部延迟时间非常短,MCP2515 不会

发生第二种情况。

2.6 帧间间隔

帧间间隔将前一条帧(无论何种类型)与其后的数据帧

或远程帧间隔开。帧间间隔至少由 3 个隐性位构成,又

称为间断。间断使节点在发送下一条报文之前有时间进

行内部处理。在间断之后, CAN 总线将保持隐性状态

(总线空闲),直至下一条报文开始发送。

DS21801D_CN 第 8 页 初稿 2005 Microchip Technology Inc.

Page 9

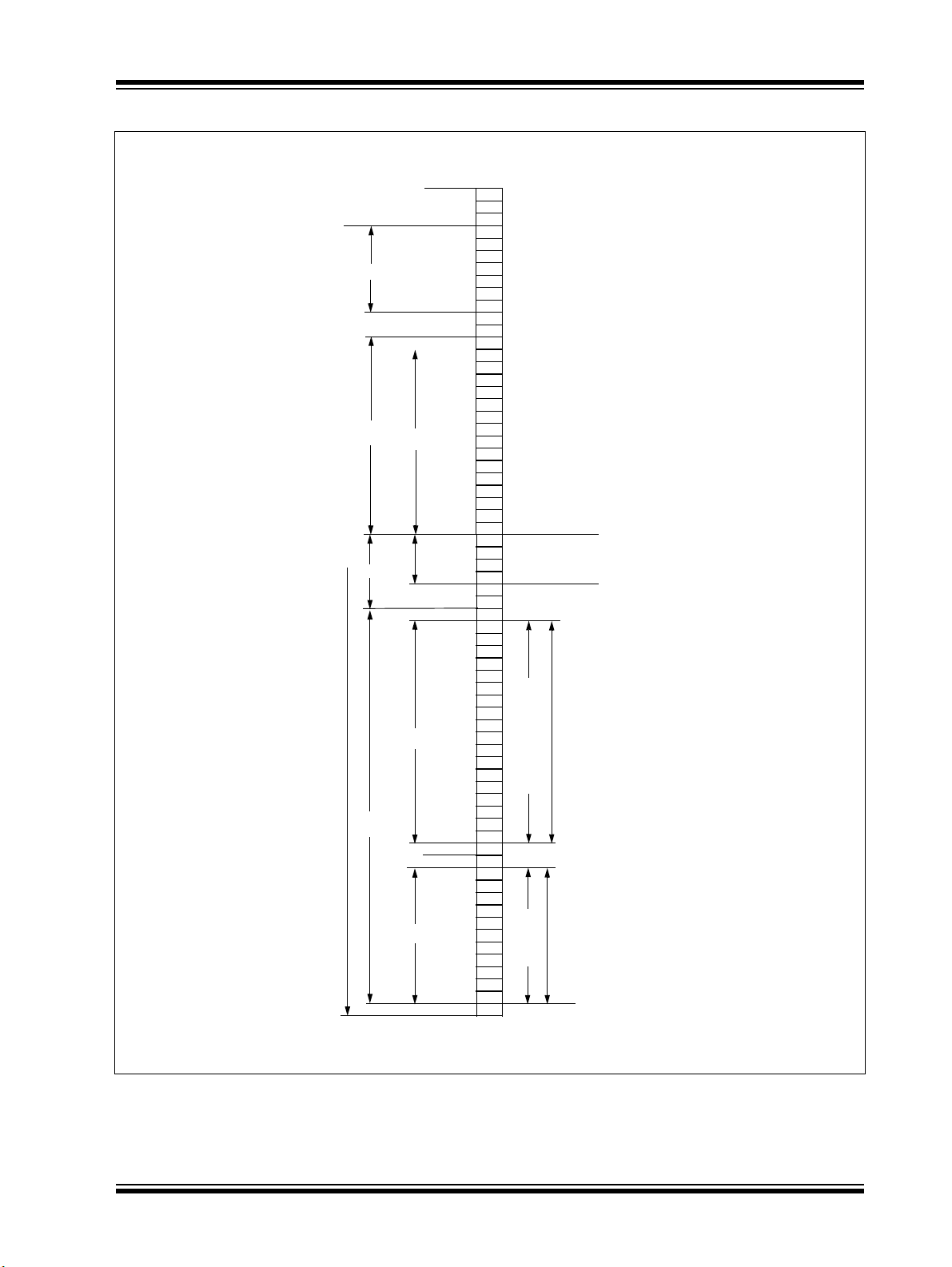

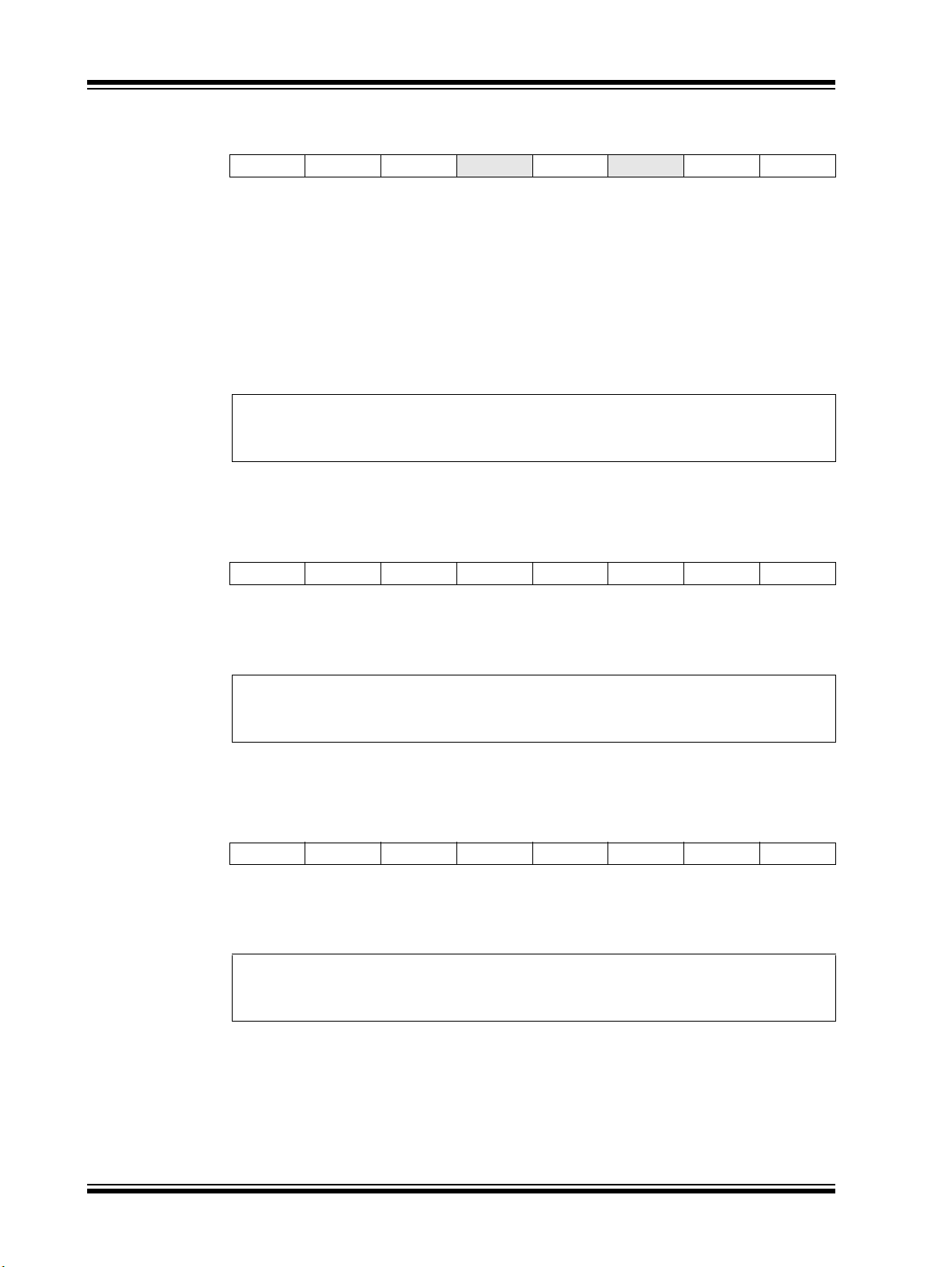

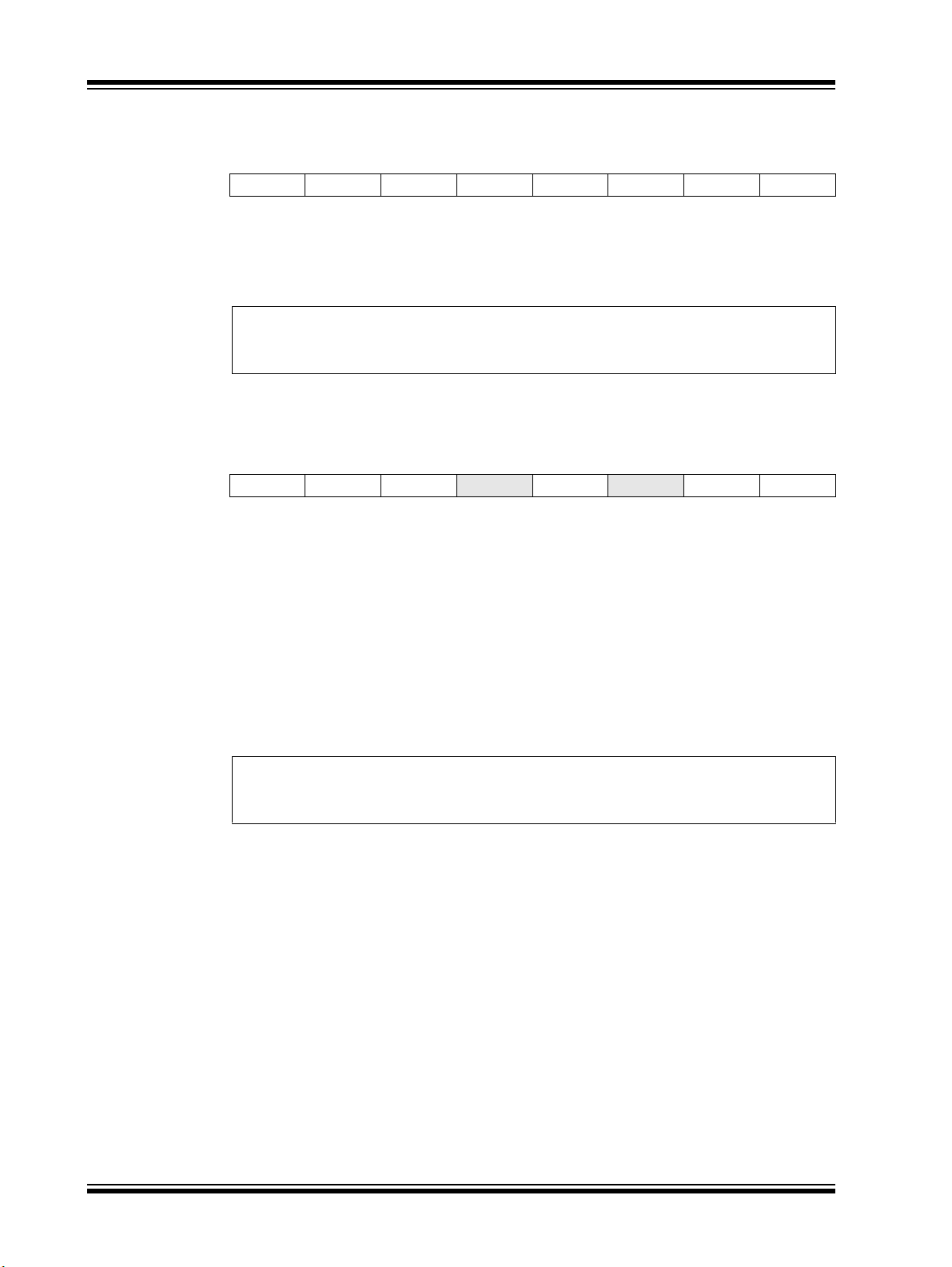

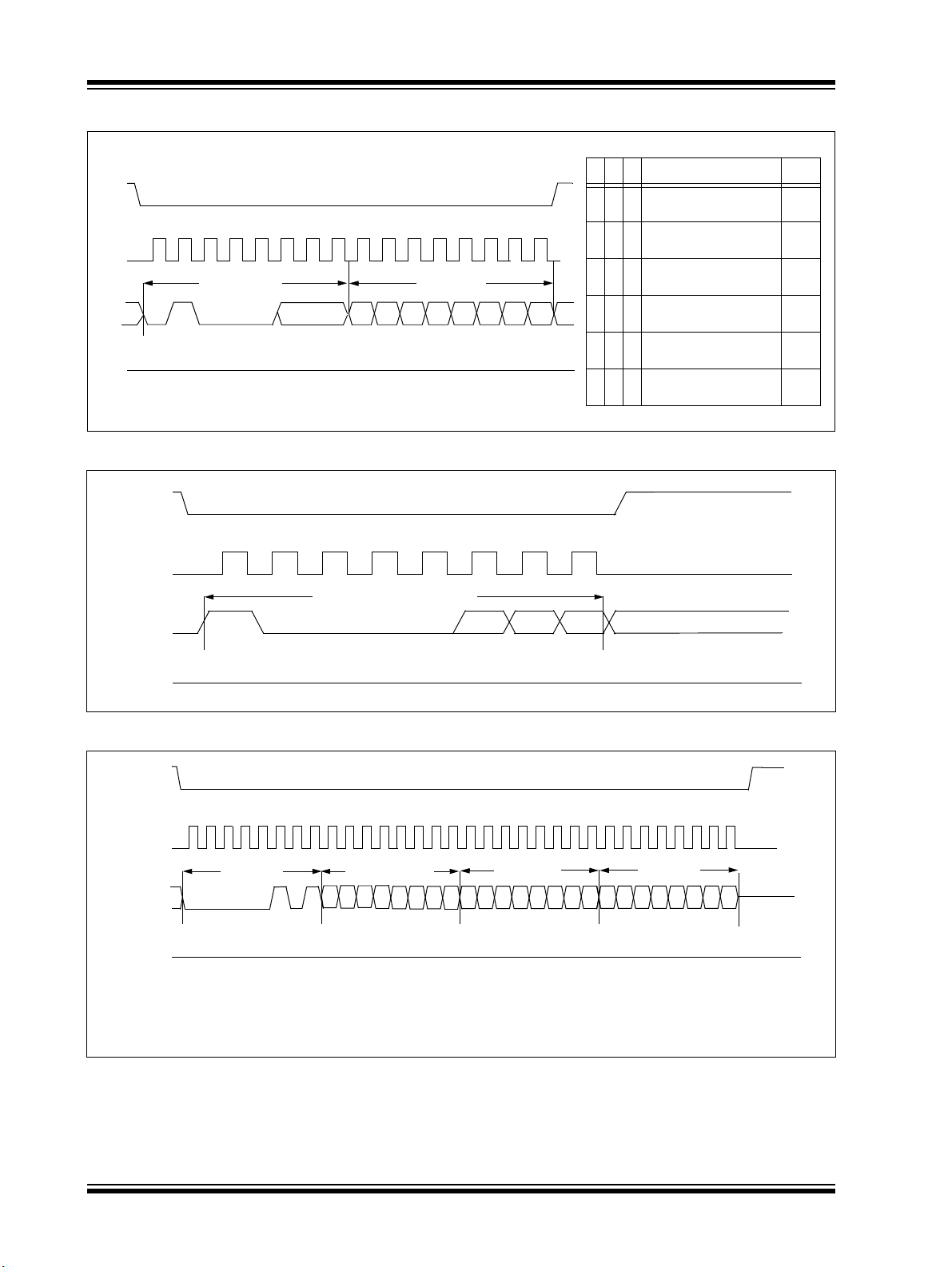

图 2-1: 标准数据帧

MCP2515

IFS

1 1 11

7

帧结束

确认定界符

1 1 1 1 1 1 1

确认间隙位

CRC 定界符

1

数据帧(位数 = 44 + 8N)

16

CRC 字段

8N (0≤N≤8)

数据字段

6

控制

4

字段

8

8

15

CRC

DLC0

DLC3

RB0

IDE

RTR

ID0

位填充

存储于发送 / 接收缓冲器中

数据

长度码

0

0

保留位

ID3

12

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 9 页

11

仲裁字段

ID 10

帧起始

标识符

报文滤波

0 0

存储于缓冲器中

Page 10

MCP2515

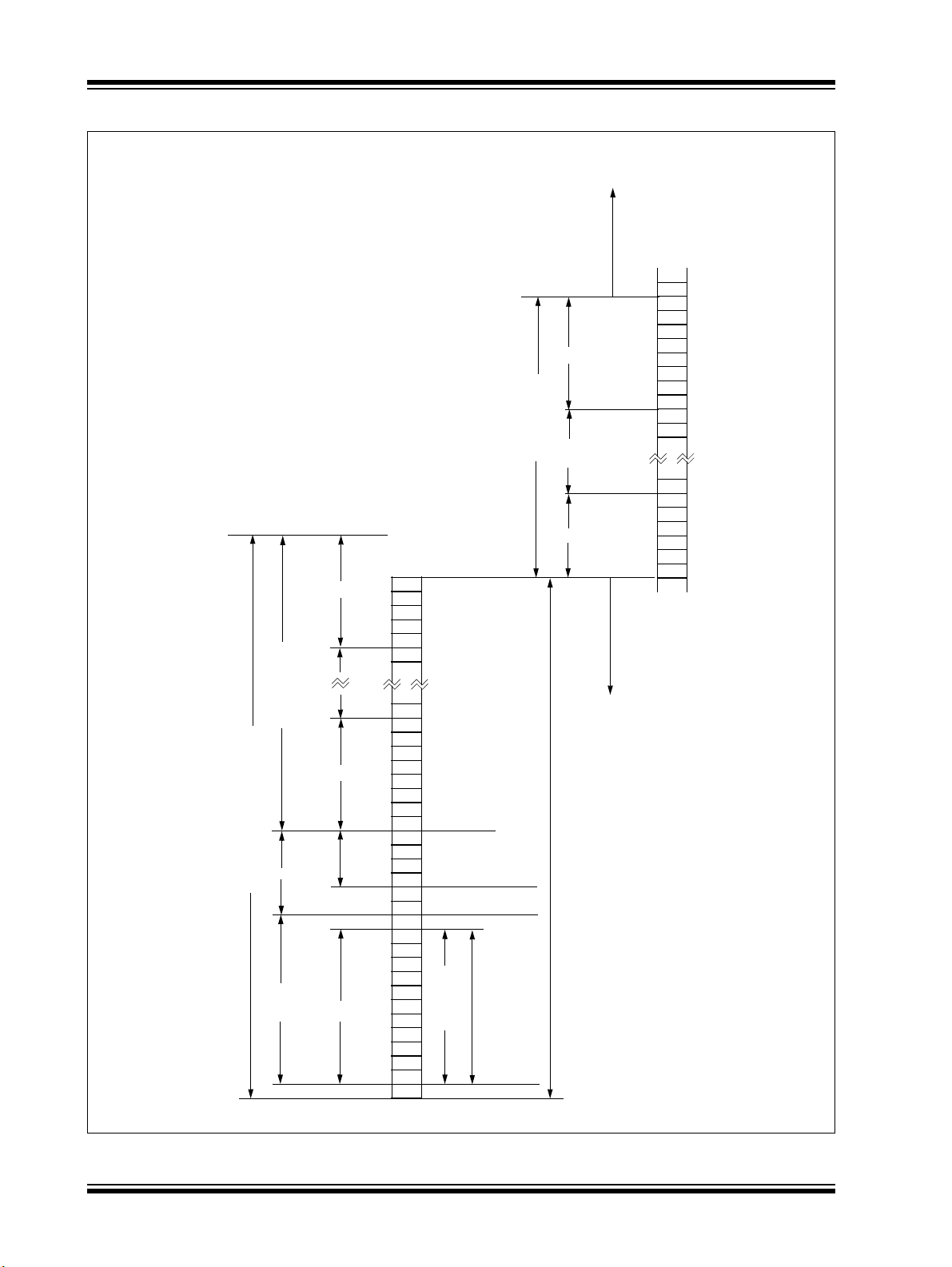

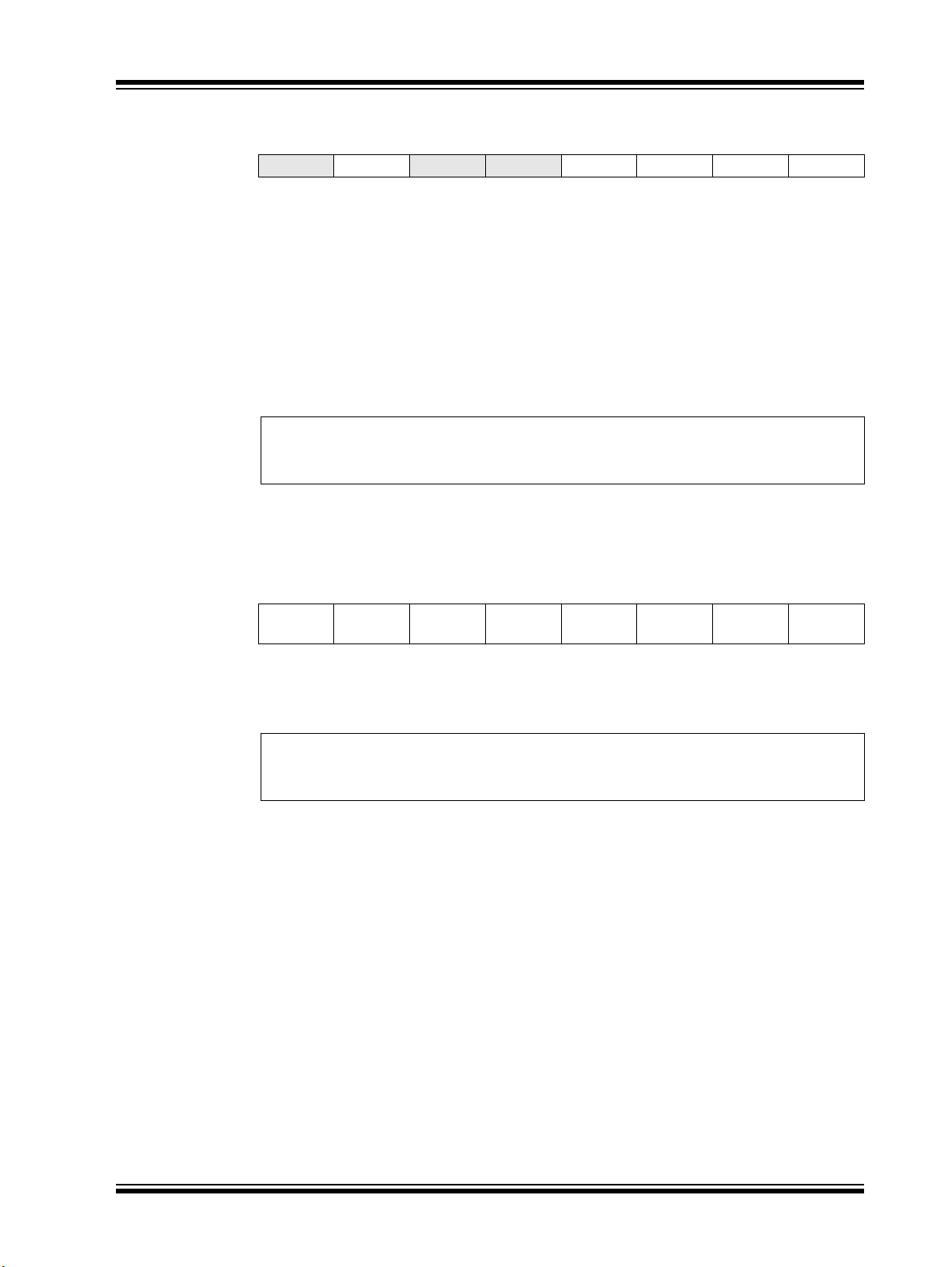

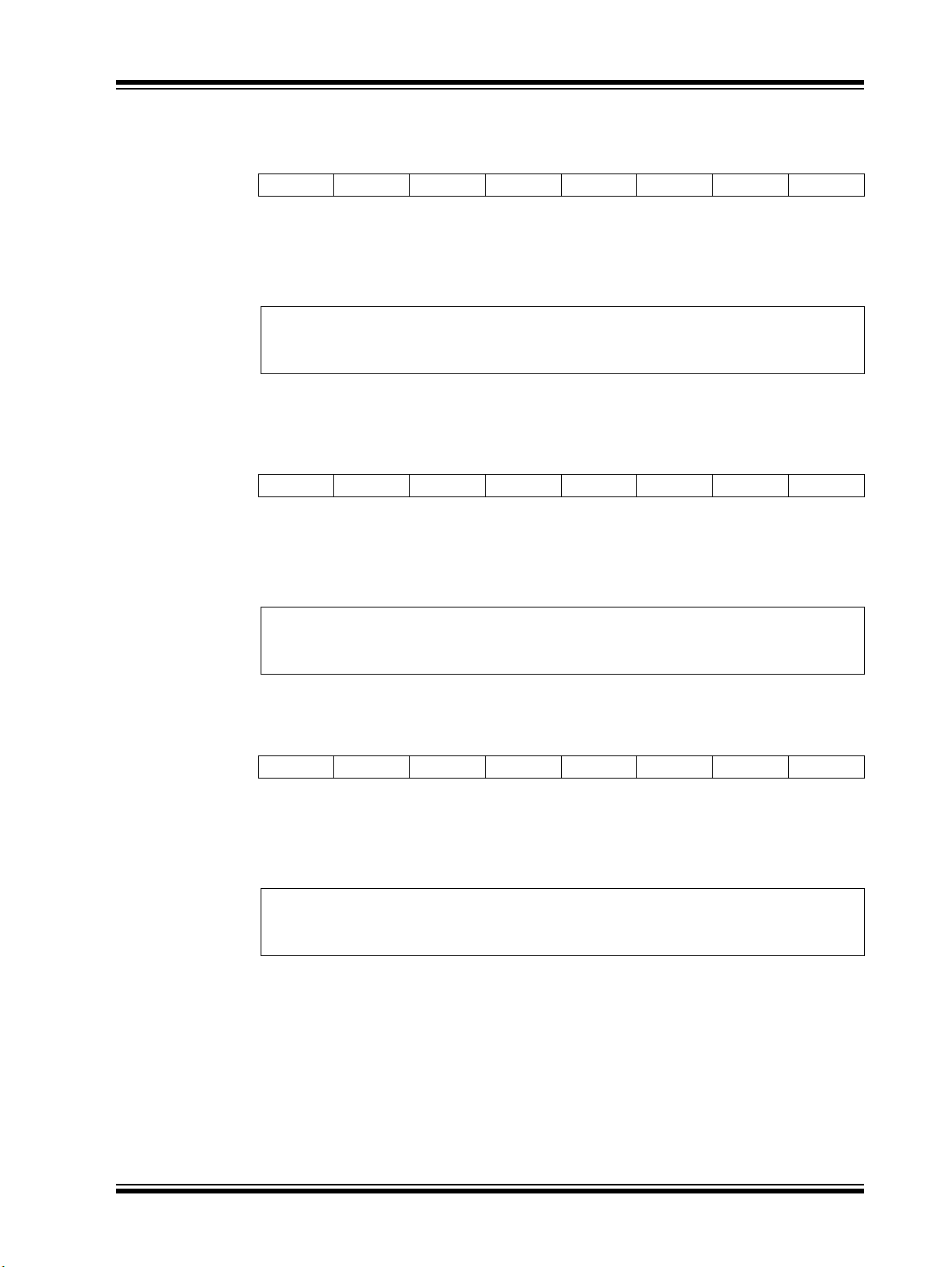

图 2-2: 扩展数据帧

16

IFS

1 1 1

7

帧结束

确认定界符

1 1 1 1 1 1 1 1

确认间隙位

CRC 定界符

15

CRC

CRC 字段

数据帧(位数 = 64 + 8N)

8N (0 ≤ N ≤ 8)

数据字段

6

控制

32

仲裁字段

8 8

DLC0

4

DLC3

字段

18

RB0

RB1

RTR

EID0

EID17

IDE

SRR

ID0

ID3

数据

长度码

扩展标识符

存储在发送/接收缓冲器中

保留位

位填充

存储在缓冲器中

11

报文滤波

标识符

ID10

帧起始

0 1 1 0 0 0 1

DS21801D_CN 第 10 页 初稿 2005 Microchip Technology Inc.

Page 11

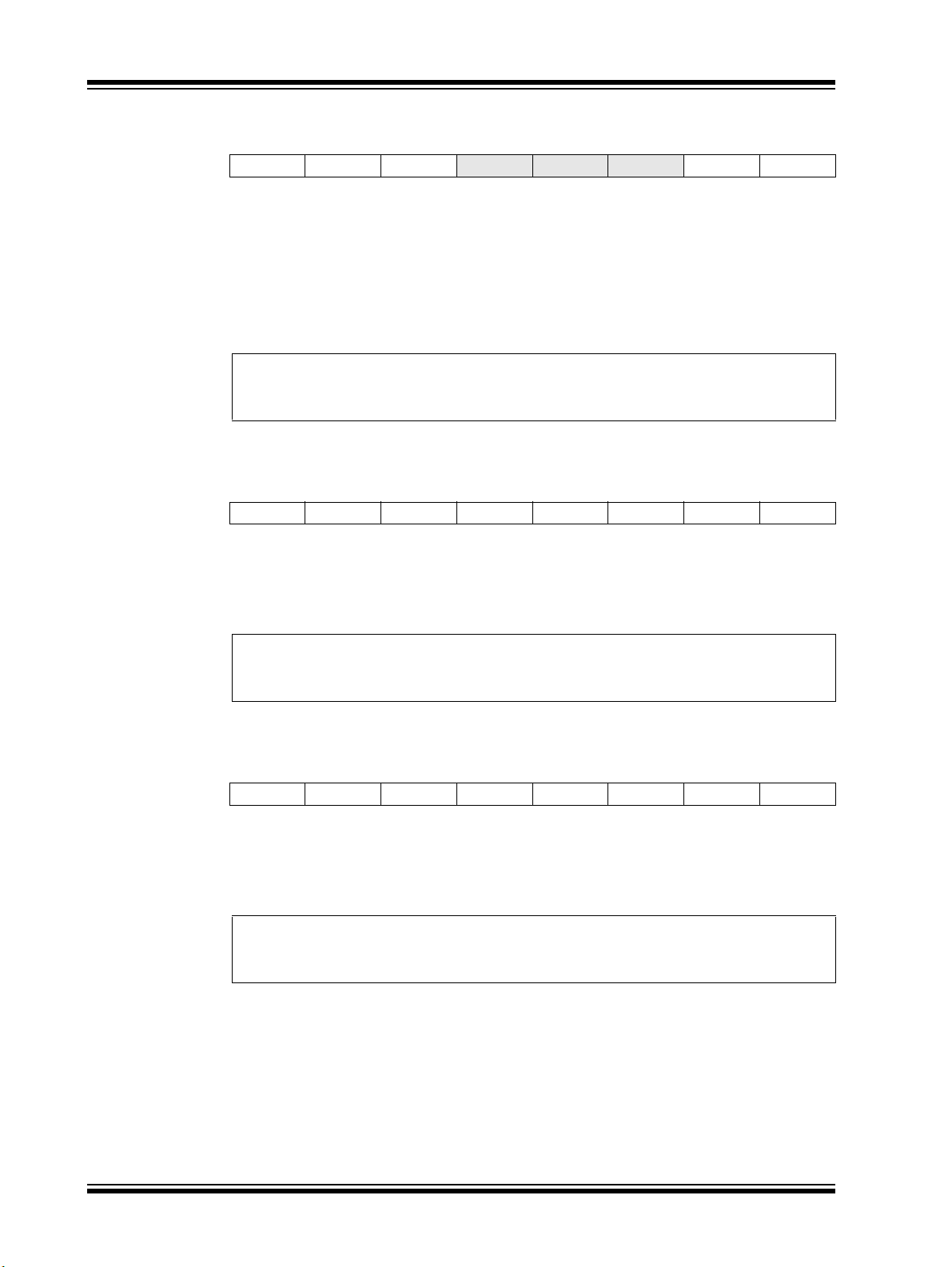

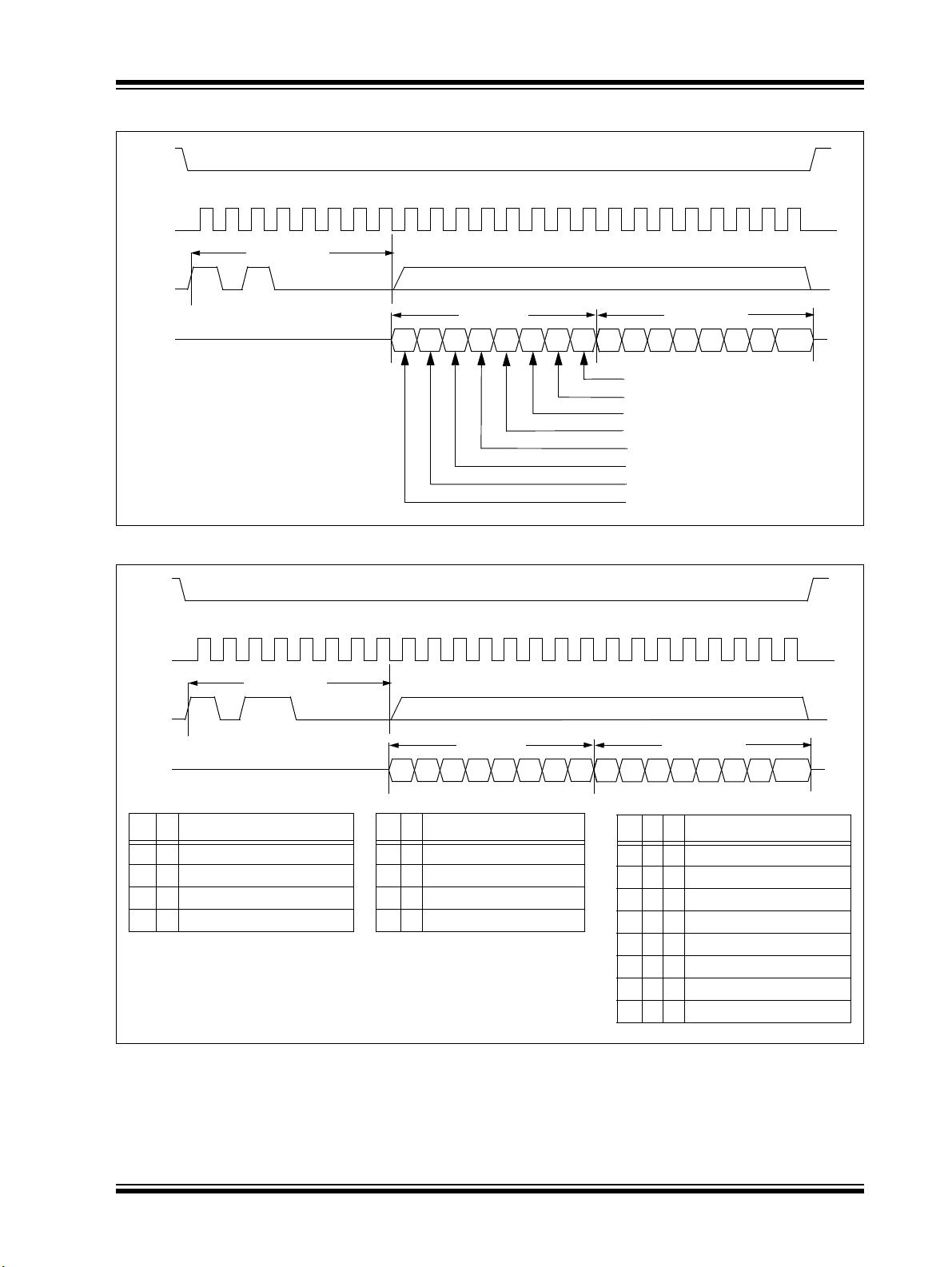

图 2-3:远程帧

7

16

CRC 字段

MCP2515

IFS

1 1 1

帧结束

确认定界符

确认间隙位

CRC 定界符

1 1 1 1 1 1 1 1 1

15

CRC

6

32

控制字段

仲裁字段

DLC0

无数据字段

4

DLC3

18

11

RB0

RB1

RTR

EID0

EID17

IDE

SRR

ID0

ID3

数据

长度码

扩展标识符

报文滤波

标识符

保留位

ID10

帧起始

0 1 1 1 0 0

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 11 页

带扩展标识符的远程帧

Page 12

MCP2515

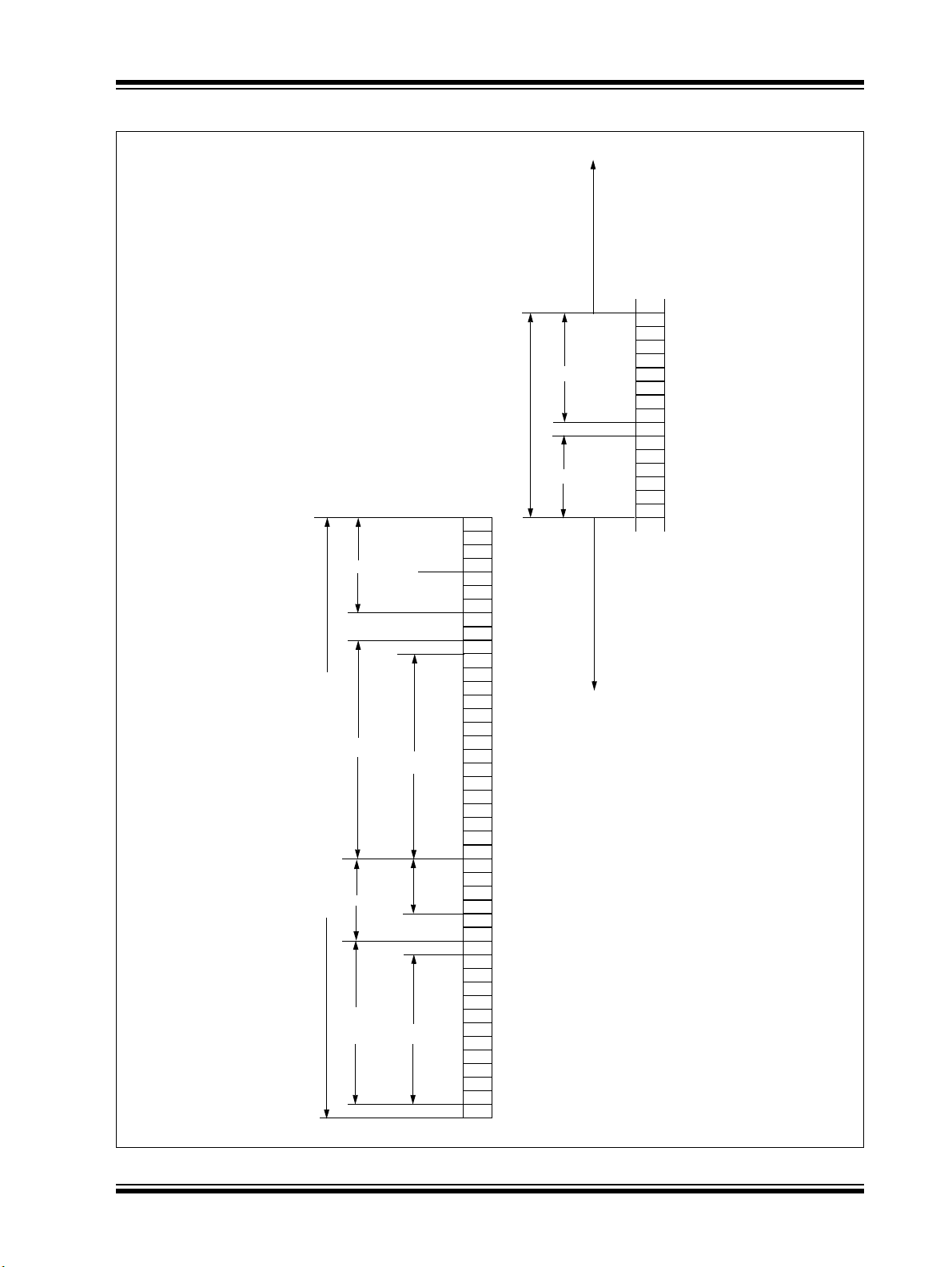

图 2-4: 主动错误帧

8

错误帧

£ 6

帧间间隔或

过载帧

错误定界符

反射错误标志

0 1 1 1 1 1 1 1 1 0

0

被中断的数据帧

8N (0≤N≤8)

数据字段

6

控制字段

6

错误

标志

0 0 0 0 0 0 0

8

数据帧或远程帧

8

DLC0

4

DLC3

RB0

IDE

RTR

ID0

ID3

数据

长度码

0

0

位填充

保留位

12

DS21801D_CN 第 12 页 初稿 2005 Microchip Technology Inc.

11

仲裁字段

ID 10

帧起始

标识符

报文滤波

0 0

Page 13

图 2-5:过载帧

帧间间隔或错误帧

过载帧

MCP2515

8

过载定界符

6

过载标志

0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

7

帧结束

确认定界符

1 1 1 1 1 1 1 1

确认间隙位

CRC 定界符

1

帧结束或

错误定界符或

过载定界符

16

远程帧(位数 = 44)

6

12

CRC 字段

控制字段

15

CRC

DLC0

4

DLC3

RB0

0

IDE

0

RTR

ID0

11

仲裁字段

ID 10

帧起始

0 1

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 13 页

Page 14

MCP2515

注:

DS21801D_CN 第 14 页 初稿 2005 Microchip Technology Inc.

Page 15

MCP2515

3.0 报文发送

3.1 发送缓冲器

MCP2515 采用三个发送缓冲器。每个发送缓冲器占用

14 字节的 SRAM,并映射到器件存储器中。

其中第一个字节 TXBnCTRL 是与报文缓冲器相关的控

制寄存器。该寄存器中的信息决定了报文在何种条件下

发送,并在报文发送时指示其状态 (见寄存器 3-1)。

用 5 个字节来装载标准和扩展标识符以及其他报文仲裁

信息 (见寄存器 3-3 到寄存器 3-7)。最后 8 个字节用

于装载等待发送报文的 8 个可能的数据字节 (见寄存

器 3-8)。

至少须将 TXBnSIDH、TXBnSIDL 和 TXBnDLC 寄存器

装载数据。如果报文包含数据字节,还需要对 TXBnDm

寄存器进行装载。若报文采用扩展标识符,应对 TXB-

nEIDm 寄存器进行装载,并将 TXBnSIDL.EXIDE 位置

1。

在报文发送之前, MCU 应对 CANINTE.TXInE 位进行

初始化,以便在报文发送时使能或禁止中断的产生。

注: 在写入发送缓冲器之前,必须将

TXBnCTRL.TXREQ 位清零 (表明发送缓

冲器无等待发送的报文)。

3.2 发送优先级

发送优先级是指 MCP2515 内部等待发送报文的优先

级。它与 CAN 协议中固有的报文仲裁优先级无关。

在发送起始帧 SOF 之前,器件将所有等待发送报文的

发送缓冲器的优先级进行比较。具有较高优先级的发送

缓冲器将首先发送。例如,发送缓冲器 0 的优先级比发

送缓冲器 1 高,发送缓冲器 0 将首先发送。

如果两个发送缓冲器的优先级相同,编号较高的发送缓

冲器将优先发送。例如,发送缓冲器 1 与发送缓冲器 0

的优先级相同,缓冲器 1 将优先发送。

发送优先级的设定共有 4 个等级。如果某个发送缓冲器

的 TXBnCTRL.TXP<1:0> 设定为 11,该发送缓冲器具

有最高的发送优先级。如果 TXBnCTRL.TXP<1:0> 设定

为 00,该发送缓冲器的发送优先级最低。

3.3 启动发送

通过将 TXBnCTRL.TXREQ 位置 1,可以启动相应缓冲

器的报文发送。它可以按如下方式设定:

• 利用 SPI 写命令写寄存器

• 发送 SPI RTS 命令

• 将要发送报文的发送缓冲器的T

电平

通过 SPI 接口启动报文发送后,可以同时将 TXREQ 位

和 TXP 优先级控制位置 1。

当 TXBnCTRL.TXREQ 位置 1 后, TXBnCTRL.ABTF、

TXBnCTRL.MLOA 和 TXBnCTRL.TXERR位都将被自动

清零。

注: 将 TXBnCTRL.TXREQ 位置 1 不会启动报

文发送。仅会将报文缓冲器标记为准备发

送。当器件检测到总线空闲时,才会启动

报文发送。

报文发送成功后, TXBnCTRL.TXREQ 位将被清零,

CANINTF.TXnIF 位置1,若 CANINTE.TXnIE 位被置 1,

将产生中断。

如果报文发送失败, TXBnCTRL.TXREQ 将保持置 1,

表明该报文仍在等待发送。此时以下条件标志之一将被

置 1:

• 如果报文已开始发送但发生错误,

TXBnCTRL.TXERR和CANINTF.MERRF位将被置

1,此时在 CANINTE.MERRE 位置 1 后,器件将

NT 引脚产生中断

在 I

• 若发送报文总线仲裁失败, TXBnCTRL.MLOA 位

将被置 1

注: 如果使能了单触发模式

(CANCTRL.OSM) ,以上所述的条件仍

然有效。然而,TXREQ 位会被清零,并且

报文不会尝试再次发送。

XnRTS 引脚置为低

3.4 单触发模式

单触发模式确保了报文只会发送一次。正常情况下,如

果 CAN 报文仲裁失败或被错误帧损坏,报文会尝试再

次发送。一旦单触发模式使能,报文只会发送一次,而

不管仲裁失败或产生错误帧与否。

单触发模式需要在确定性系统中保持时间间隙,如

TTCAN。

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 15 页

Page 16

MCP2515

3.5 TXnRTS 引脚

TXnRTS 为输入引脚,可配置为:

• 请求发送输入引脚,作为启动任一发送缓冲器中报

文发送的备用方法

• 标准数字输入引脚

通过设定 TXRTSCTRL 寄存器(见寄存器 3-2)可对这

些引脚进行配置和控制。只有在 MCP2515 处于配置模

式时才可对 TXRTSCTRL 寄存器内容进行修改 (见第

10.0 节 “工作模式”)。如果该引脚配置为请求发送引

脚,该引脚将被映射为发送缓冲器中相应的 TXBnC-

TRL.TXREQ 位。TX

可将锁定 TXREQ位。用户可将 TXnRTS 引脚同 RXnBF

引脚直接相连,在 RXnBF 引脚变为低电平时自动启动

报文发送。

XnRTS 引脚具有 100 kΩ(标称值)的内部上拉电阻。

T

nRTS 引脚的下降沿电平跳变信号

3.6 中止发送

MCU 可通过将特定报文缓冲器中对应的 TXBnCTRL.TXREQ 位清零,请求中止该缓冲器中的报文发

送。

也可通过将 CANCTRL.ABAT 位置 1 来请求中止所有等

待发送的报文。用户必须复位该位才可继续发送报文

(通常须先确认所有的 TXREQ位都已清零)。只有通过

设定 CANCTRL.ABAT 位中止报文发送时,CAN-

CTRL.ABTF 标志才会被置 1。通过复位 TXREQ 位来中

止报文发送,将不会使 ABTF 位置 1。

注: 只有尚未开始发送的报文可被中止。报文

一旦没有发送成功 (如,仲裁失败或因错

误帧而中断),就会中止发送。

DS21801D_CN 第 16 页 初稿 2005 Microchip Technology Inc.

Page 17

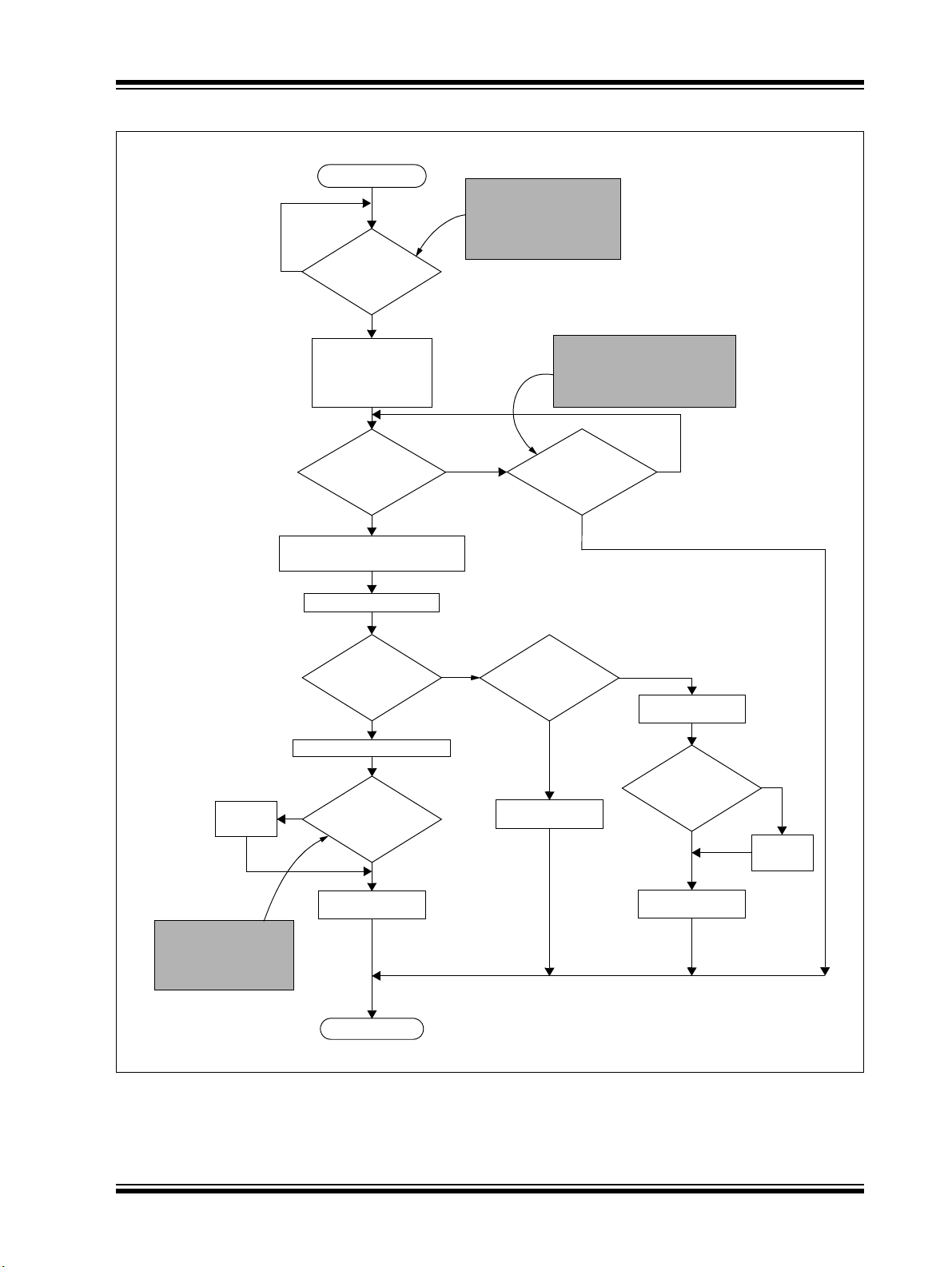

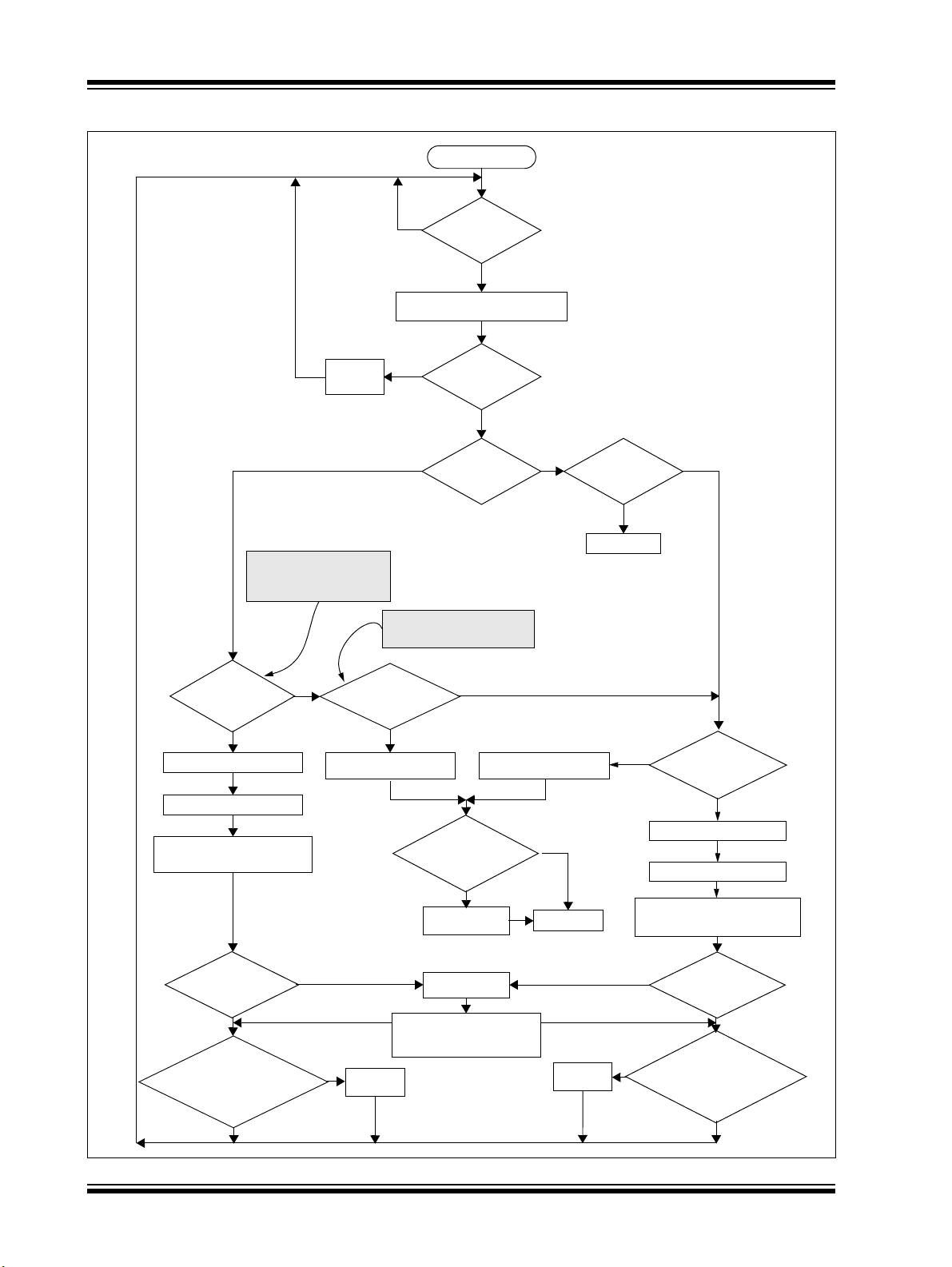

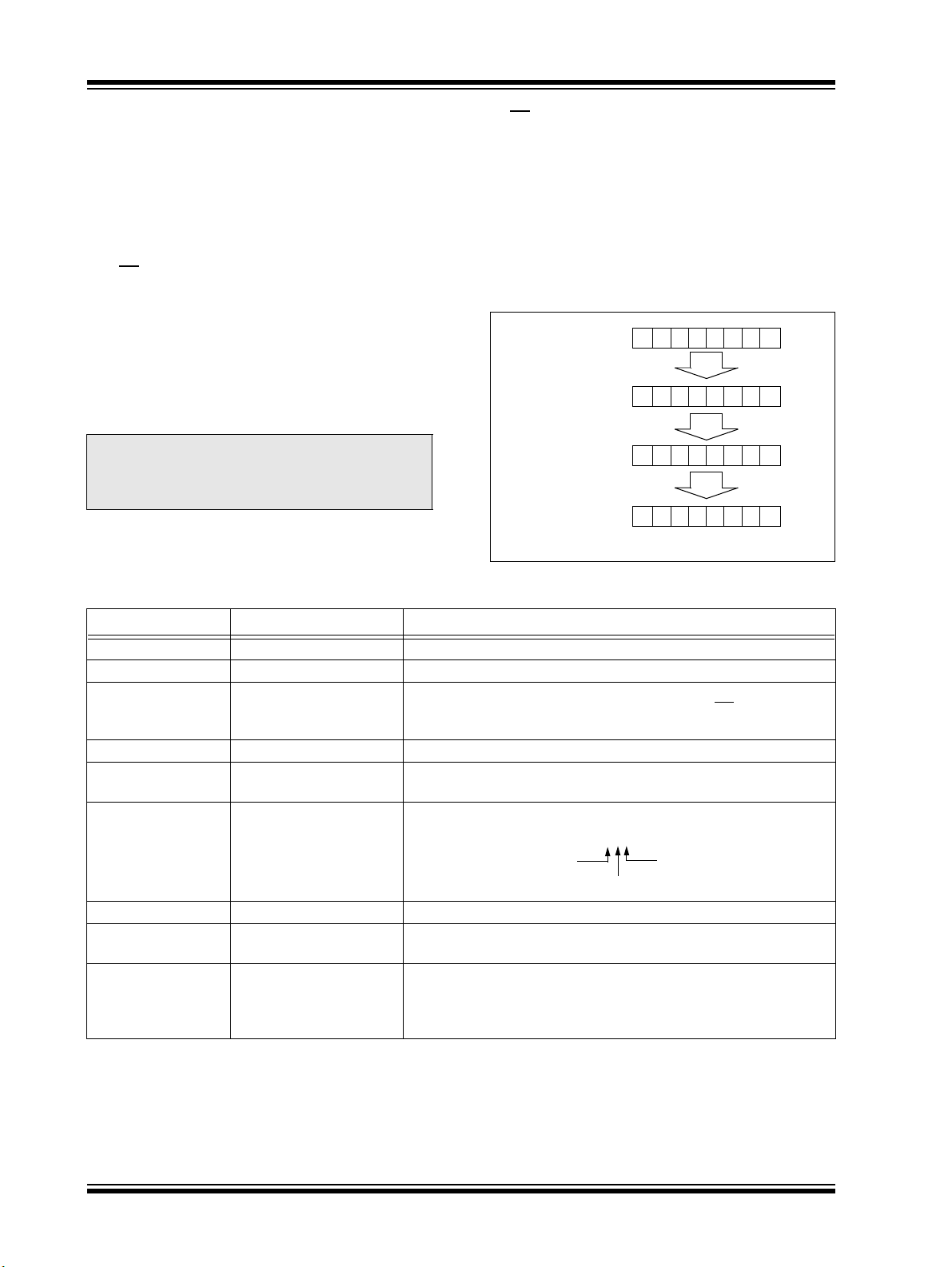

图 3-1: 报文发送流程图

MCP2515

开始

否

检查 TXBnCTRL.TXP <1:0>

以确定最高优先级的报文

任一

TXBnCTRL.TXREQ

位 = 1

?

是

清零:

TXBnCTRL.ABTF

TXBnCTRL.MLOA

TXBnCTRL.TXERR

CAN 总线是否

可进行报文发送?

是

报文发送

当器件确定任一发送控制寄存

器 TXBnCTRL.TXREQ 位被置

1 后,开始报文发送序列。

将置 1 的 TxBnCTRL.TXREQ 位清

零或在报文发送之前 CAN-

CTRL.ABAT 位置 1 将会中止报文发

送。

否

TXBnCTRL.TXREQ=0

或 CANCTRL.ABAT=1

?

是

否

产生

中断

CANINTE.TXnIE 位决定在

报文发送成功后是否产生

中断。

报文成功发送?

是

TxBnCTRL.TXREQ 位清零

是

CANINTE.TXnIE=1?

否

CANTINF.TXnIF

置 1

返回开始

否

报文出错

或

仲裁失败?

仲裁失败

TxBNCTRL.MLOA

置 1

报文出错

TxBnCTRL.TXERR

置 1

CANINTE.MEERE?

否

CANTINF.MERRF

置 1

是

产生

中断

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 17 页

Page 18

MCP2515

寄存器 3-1: TXBnCTRL——发送缓冲器 n 控制寄存器 (地址:30h, 40h, 50h)

U-0 R-0 R-0 R-0 R/W-0 U-0 R/W-0 R/W-0

— ABTF MLOA TXERR TXREQ — TXP1 TXP0

bit 7 bit 0

bit 7 未用:读为 0

bit 6 ABTF:报文发送中止标志位

1 = 报文中止

0 = 报文发送成功完成

bit 5 MLOA:报文仲裁失败位

1 = 报文发送期间仲裁失败

0 = 报文发送期间仲裁未失败

bit 4 TXERR:检测到发送错误位

1 = 报文发送期间发生总线错误

0 = 报文发送期间未发生总线错误

bit 3 TXREQ:报文发送请求位

1 = 缓冲器等待报文发送

(MCU 将此位置 1 以请求报文发送-报文发送后该位自动清零)

0 = 缓冲器无等待发送报文

(MCU 将此位清零以请求中止报文发送)

bit 2 未用:读为 0

bit 1-0 TXP:发送缓冲器优先级 <1:0> 位

11 = 最高的报文发送优先级

10 = 中偏高的报文发送优先级

11 = 中偏低的报文发送优先级

00 = 最低的报文发送优先级

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

DS21801D_CN 第 18 页 初稿 2005 Microchip Technology Inc.

Page 19

MCP2515

寄存器 3-2: TXRTSCTRL——TXnRTS 引脚控制和状态寄存器 (地址:0Dh)

U-0 U-0 R-x R-x R-x R/W-0 R/W-0 R/W-0

— — B2RTS B1RTS B0RTS B2RTSM B1RTSM B0RTSM

bit 7 bit 0

bit 7 未用:读为 0

bit 6 未用:读为 0

bit 5 B2RTS: T

- TX2RTS

- TX2RTS 为请求发送模式时,读为 0

bit 4 B1RTS:TX1RTX 引脚状态位

- TX1RTX 为数字输入模式时,读出值为该引脚的电平

- TX1RTX

bit 3 B0RTS:TX0RTS

-TX0RTS

- TX0RTS 为请求发送模式时,读为 0

bit 2 B2RTSM:T

1 = 该引脚用来请求 TXB2 缓冲器发送报文 (在下降沿)

0 = 数字输入

bit 1 B1RTSM:T

1 = 该引脚用来请求 TXB1 缓冲器发送报文 (在下降沿)

0 = 数字输入

bit 0 B0RTSM:TX0RTS 引脚模式位

1 = 该引脚用来请求 TXB0 缓冲器发送报文 (在下降沿)

0 = 数字输入

X2RTS 引脚状态位

为数字输入模式时,读出值为该引脚的电平

为请求发送模式时,读为 0

引脚状态位

为数字输入模式时,读出值为该引脚的电平

X2RTS 引脚模式位

X1RTS 引脚模式位

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

寄存器 3-3: TXBnSIDH——发送缓冲器 n 标准标识符高位 (地址:31h, 41h, 51h)

R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x

SID10 SID9 SID8 SID7 SID6 SID5 SID4 SID3

bit 7 bit 0

bit 7-0 SID:标准标识符位 <10:3>

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 19 页

Page 20

MCP2515

寄存器 3-4: TXBnSIDL——发送缓冲器 n 标准标识符低位 (地址:32h, 42h, 52h)

R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x

SID2 SID1 SID0 — EXIDE —EID17EID16

bit 7 bit 0

bit 7-5 SID:标准标识符位 <2:0>

bit 4 未用:读为 0

bit 3 EXIDE:扩展标识符使能位

1 = 报文将发送扩展标识符

0 = 报文将发送标准标识符

bit 2 未用:读为 0

bit 1-0 EID:扩展标识符位 <17:16>

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

寄存器 3-5: TXBnEID8——发送缓冲器 n 扩展标识符高位 (地址:33h, 43h, 53h)

R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x

EID15 EID14 EID13 EID12 EID11 EID10 EID9 EID8

bit 7 bit 0

bit 7-0 EID:扩展标识符位 <15:8>

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

寄存器 3-6: TXBnEID0——发送缓冲器 n 扩展标识符低位 (地址:34h, 44h, 54h)

R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x

EID7 EID6 EID5 EID4 EID3 EID2 EID1 EID0

bit 7 bit 0

bit 7-0 EID:扩展标识符位 <7:0>

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

DS21801D_CN 第 20 页 初稿 2005 Microchip Technology Inc.

Page 21

MCP2515

寄存器 3-7: TXBnDLC——发送缓冲器 n 数据长度码 (地址:35h, 45h, 55h)

R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x

—RTR— — DLC3 DLC2 DLC1 DLC0

bit 7 bit 0

bit 7 未用:读为 0

bit 6 RTR:远程发送请求位

1 = 发送的报文为远程发送请求

0 = 发送的报文为数据帧

bit 5-4 未用:读为 0

bit 3-0 DLC:数据长度码位 <3:0>

设定要发送的数据长度 (0 到 8 字节)

注: 可以将 DLC 设定为大于 8 的值,但只发送 8 个字节。

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

寄存器 3-8: TXBnDm——发送缓冲器 n 数据字节 m

(地址:36h - 3Dh, 46h - 4Dh, 56h - 5Dh)

R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x

TXBnDm7TXBnDm6TXBnDm5TXBnDm4TXBnDm3TXBnDm2TXBnDm1TXBnDm

bit 7 bit 0

bit 7-0 TXBnD

M7:TXBnDM0:发送缓冲器 n 数据字段字节 m

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

0

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 21 页

Page 22

MCP2515

注:

DS21801D_CN 第 22 页 初稿 2005 Microchip Technology Inc.

Page 23

MCP2515

4.0 报文接收

4.1 报文接收缓冲

MCP2515 具有两个全接收缓冲器。每个接收缓冲器配

备有多个验收滤波器。除上述专用接收缓冲器外,

MCP2515 还具有单独的报文集成缓冲器 (Message

Assembly Buffer, MAB) ,可作为第三个接收缓冲器

(见图 4-2)。

4.1.1 报文集成缓冲器

在三个接收缓冲器中,报文集成缓冲器(MAB)总能够

接收来自总线的下一条报文。 MAB 对接收到的报文进

行组合,并将满足验收滤波器条件的报文传送至 RXBn

缓冲器 (见寄存器 4-4 到寄存器 4-9)。

4.1.2 RXB0 和 RXB1 缓冲器

其余的两个接收缓冲器为 RXB0 和 RXB1。通 过 MAB,

它们能够接收来自协议引擎的完整报文。当其中一个缓

冲器处于接收等待或保存着上一条接收到的报文时,

MCU 可访问另一缓冲器。

注: 一旦报文被验收,MAB 中所有的内容将传

送到接收缓冲器。这表明无论标识符为何

种类型 (标准还是扩展标识符)或接收到

多少字节的数据,整个接收缓冲器都将被

MAB 的内容所改写。因此,在接收任何报

文后,必须断定接收缓冲器中所有寄存器

中的内容都被修改了。

4.1.3 接收标志 / 中断

当报文传送至某一接收缓冲器时,与该接收缓冲器对应

的 CANINTF.RXnIF 位将置 1。一旦缓冲器中的报文处

理完毕,MCU 就必须将该位清零以接收下一条报文。该

控制位提供的锁定功能确保 MCU 尚未处理完上一条报

文前, MCP2515 不会将新的报文载入接收缓冲器。

如果 CANINTE.RXnIE 位被置 1,器件会在 I

生一个中断,显示接收到报文有效。另外,如果被配置

为接收缓冲器满中断引脚,与之相应的 RXnBF 引脚会

被拉低。请查阅第 4.4 节“RX0BF 和 RX1BF 引脚”了

解详细信息。

NT 引脚产

4.2 接收优先级

RXB0 是具有较高优先级的缓冲器,配置有一个屏蔽滤

波寄存器和两个验收滤波寄存器。接收到的报文首先在

RXB0 中进行屏蔽滤波。

RXB1 是优先级较低的缓冲器,配置有一个屏蔽滤波寄

存器和 4 个验收滤波寄存器。

报文除了首先在 RB0 中进行屏蔽滤波外,由于 RB0 的

验收滤波寄存器数量较少,因此 RB0 接受匹配条件更为

严格,表明 RB0 具有较高的优先级。

当报文被接收时,RXBnCTRL<3:0> 位将显示使能该接

收操作的验收滤波器的编号,以及接收到的报文是否为

远程传输请求。

4.2.1 滚存

另外,可对 RXB0CTRL 寄存器进行配置,如果 RXB0

已包含一条有效报文并且接收到另一条有效报文,不会

发生溢出错误,新的报文会滚存到 RXB1 而不管 RXB1

是何种验收标准。

4.2.2 RXM 位

RXBnCTRL.RXM 位可以设定特殊的接收工作模式。这

些位通常置为00,以接收所有被验收滤波器认可的有效

报文。在这种情况下,标准或扩展报文的接收与否取决

于验收滤波寄存器中的 RFXnSIDL.EXIDE 控制位。

如果 RXBnCTRL.RXM 位置为 01 或 10,接收缓冲器将

分别只接收标准帧或扩展帧。如果验收滤波寄存器的

RFXnSIDL.EXIDE位的设置不对应RXBnCTRL.RXM工

作模式,验收滤波器将不起作用。上述两种由 RXBnC-

TRL.RXM 控制位决定的接收模式可用于总线上仅传输

标准帧或扩展帧的系统。

如果 RXBnCTRL.RXM 位置为 11,无论验收滤波器的

值是什么,缓冲器都将接收所有的报文。同样,如果报

文在帧结束前出错,在 MAB 中组合的出错前的那部分

报文将被移入到缓冲器。该工作模式可在 CAN 系统调

试时使用,一般不在实际系统环境中使用。

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 23 页

Page 24

MCP2515

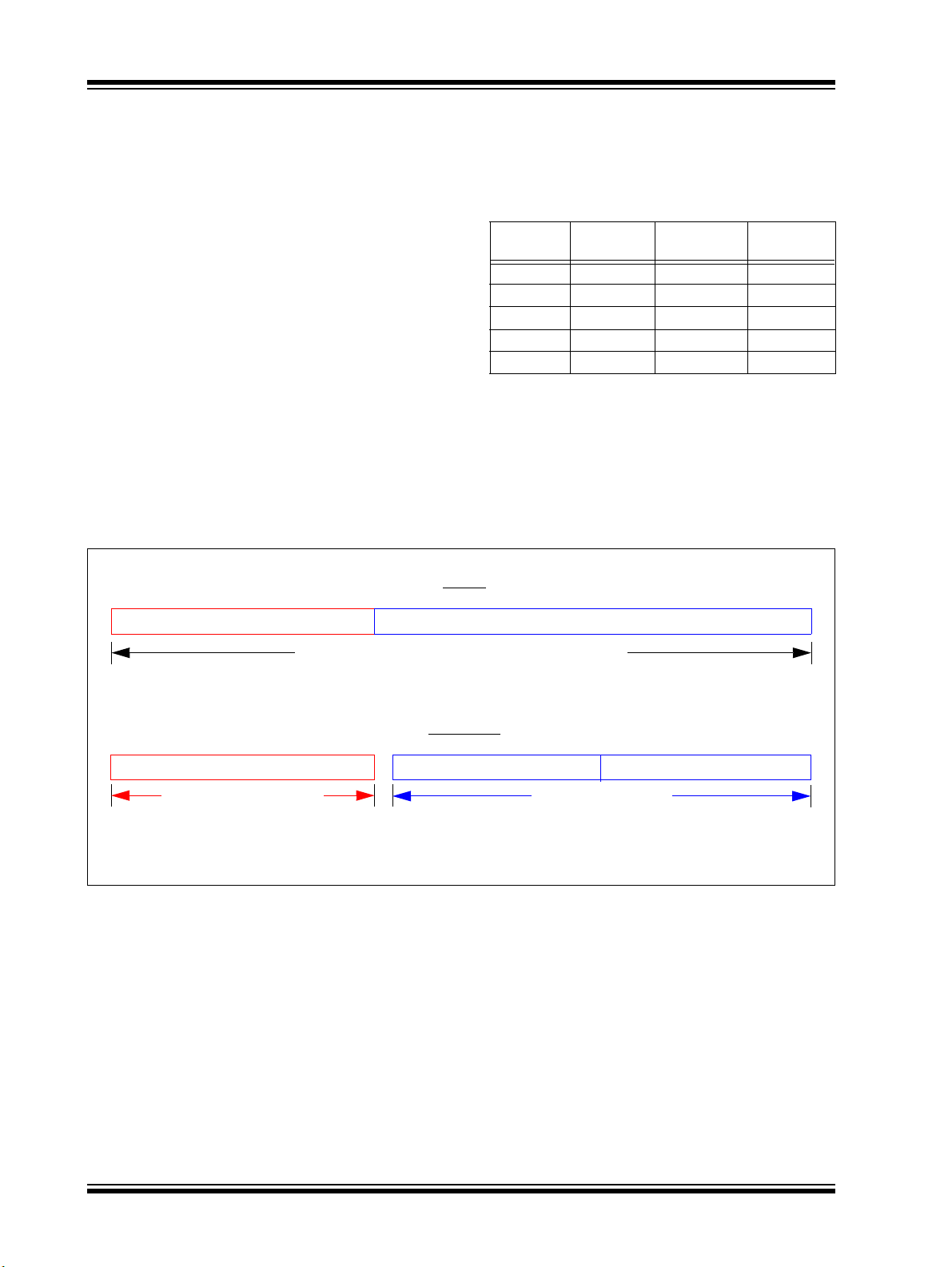

4.3 起始帧信号

使能之后,一旦 RXCAN 引脚检测到任一 CAN 报文开

始,起始帧信号便会在 SOF 引脚上产生。

RXCAN 引脚监控空闲总线上出现的从隐性位到显性位

的变化边沿。如果显性条件始终保持直至采样点发生,

MCP2515 视之为 SOF 信号并产生一个SOF 脉冲。如果

显性条件没有保持到采样点便发生, MCP2515 视之为

总线干扰,不产生 SOF 信号。图 4-1 说明了 SOF 信号

的发生和干扰过滤。

对于单触发工作模式, SOF 信号的一个用途是用于

TTCAN 系统。另外,通过监控 RXCAN 引脚和 SOF 引

脚, MCU 能够检测到总线上出现的小干扰,从而在它

们影响 CAN 通讯之前发现早期总线物理故障。

4.4 RX0BF 和 RX1BF 引脚

INT引脚可在多种情况下向 MCU提供中断信号。除此之

外,接收缓冲器满中断引脚(RX0BF 和 RX1BF)也可

用来分别指示有效报文载入 RXB0 或 RXB1。这两个引

脚有三种配置 (寄存器 4-1):

1. 禁止

2. 缓冲器满中断引脚

3. 数字输出引脚

4.4.1 禁止

BFPCTRL.BnBFE 位清零后,RXBnBF 引脚被禁止,呈

现高阻态。

4.4.2 配置为缓冲器满中断引脚

RXBnBF可配置为缓冲器满中断引脚或标准数字输出引

脚。通过 BFPCTRL 寄存器(寄存器 4-3)可对这些引

脚进行配置和状态查询。当设定为中断工作模式

(BFPCTRL.BxBFE 和 BFPCTRL.BxBFM 位置 1), 这

些引脚为低电平有效,并且被映射到相应接收缓冲器的

CANINTF.RXnIF 位。当其中一个接收缓冲器 CAN-

INTF.RXnIF位变为高电平,表明有效报文已被载入接收

缓冲器,相应的 R

CANINTF.RXnIF 位被 MCU 清零,相应的中断引脚进入

逻辑高电平状态,直到下一条报文载入接收缓冲器。

XBnBF 引脚将变为低电平。如果

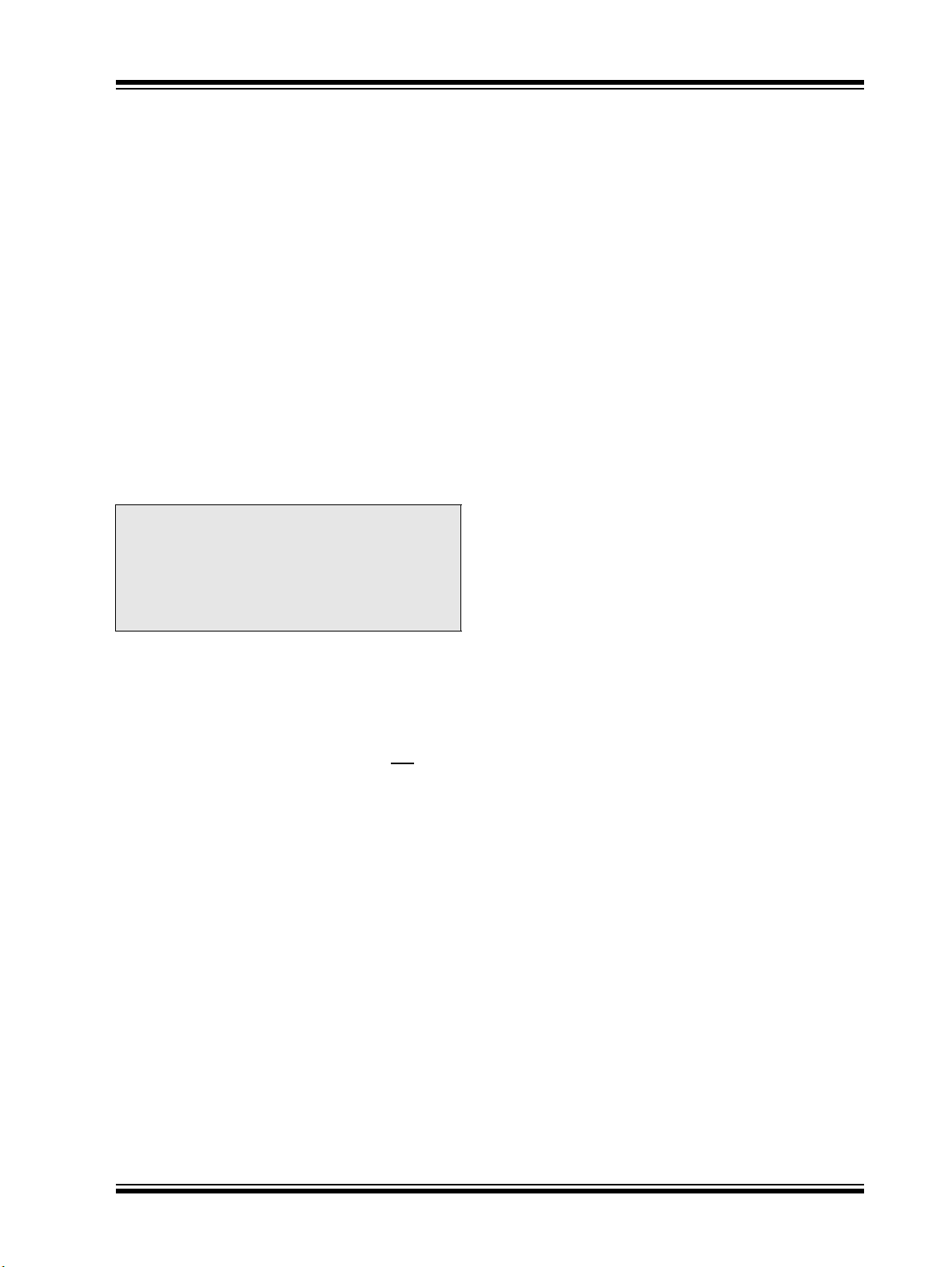

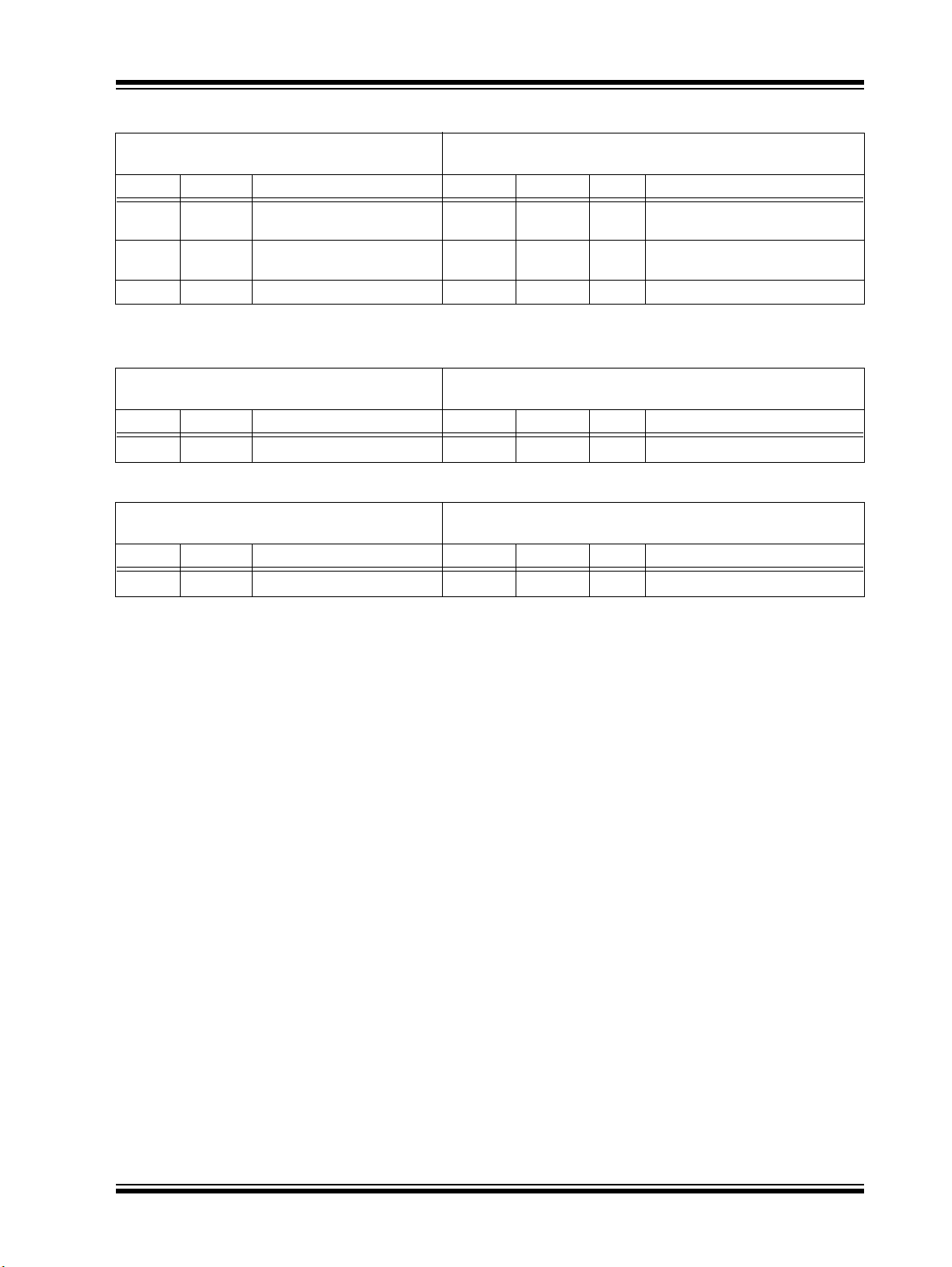

图 4-1: 起始帧信号

正常 SOF 信号

RXCAN

SOF

干扰过滤

期望起始帧位

RXCAN

SOF

起始帧位

期望

采样点

采样点

ID 位

总线空闲

DS21801D_CN 第 24 页 初稿 2005 Microchip Technology Inc.

Page 25

MCP2515

4.4.3 配置为数字输出引脚

当引脚配置为数字输出引脚时,相应的接收缓冲器中的

BFPCTRL.BxBFM位应被清零,而BFPCTRL.BnBFE位

应被置 1。在这种工作模式下,引脚的状态由 BFPC-

TRL.BnBFS位控制。BnBFS 位写入1时,将使相应的缓

冲器满中断引脚输出高电平,写入 0 将使该引脚输出低

电平。当引脚处于这种模式时,该引脚的状态只应通过

位修改 SPI 命令来修改,以避免任何缓冲器满中断引脚

出现干扰。

图 4-2: 接收缓冲器框图

注: MAB 中接收到的报文首先在 RXB0 中进行

屏蔽滤波。另外,仅会出现一个滤波器

匹配 (如,一旦报文与 RXF0 和 RXF2 均

匹配,则最终匹配的为 RXF0,报文将被移

入 RXB0)。

验收屏蔽寄存器

RXM0

验收滤波寄存器

RXF0

接

收

验收滤波寄存器

RXF1

表 4-1:配置RXNBF 引脚

BnBFE BnBFM BnBFS 引脚状态

0XX禁止,高阻态

11X接收缓冲器中断

100数字输出 = 0

101数字输出 = 1

验收屏蔽寄存器

RXM1

验收滤波寄存器

RXF2

验收滤波寄存器

RXF3

验收滤波寄存器

RXF4

验收滤波寄存器

RXF5

接

收

R

X

B

0

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 25 页

标识符

数据字段 数据字段

M

A

B

标识符

R

X

B

1

Page 26

MCP2515

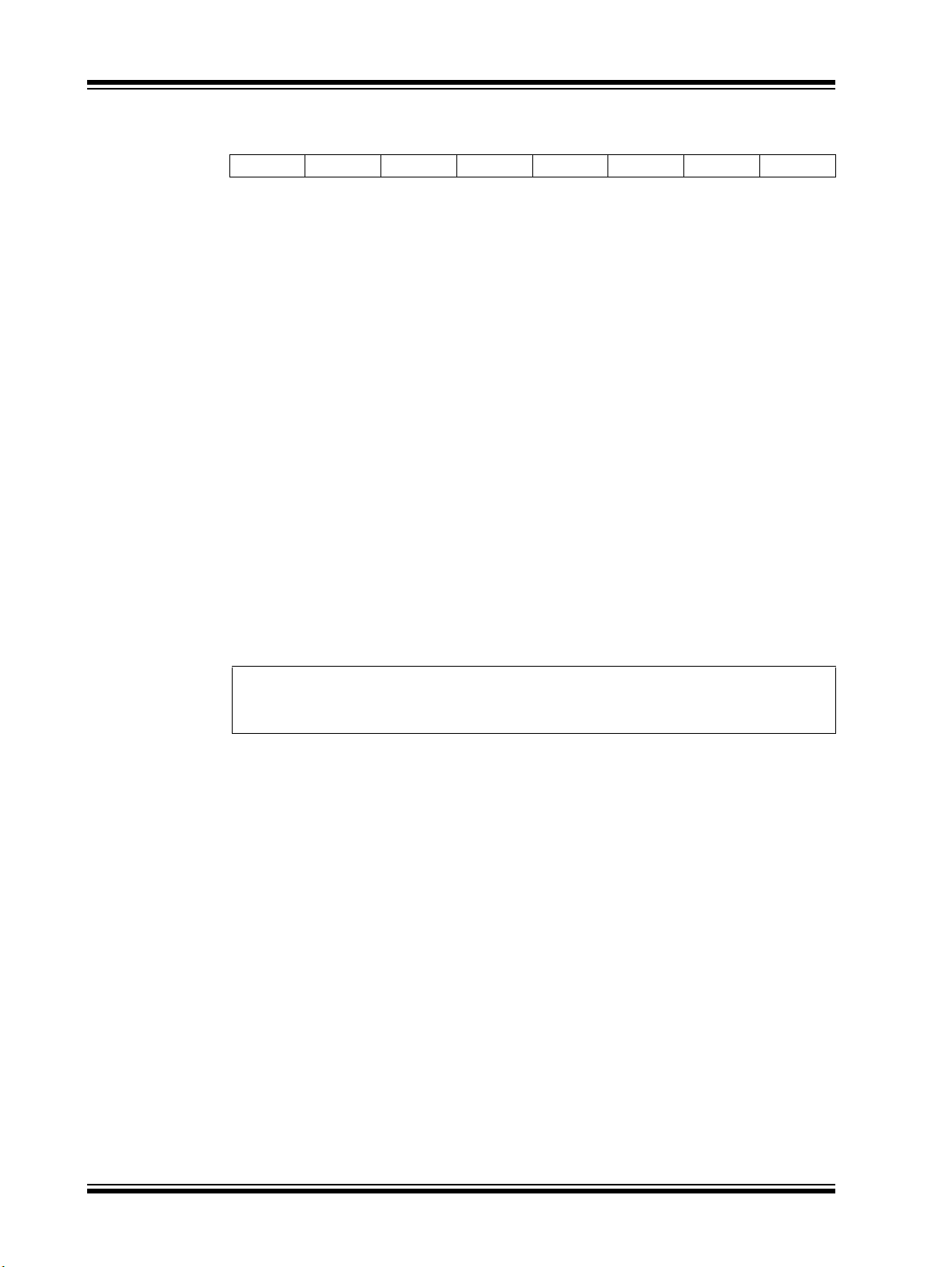

图 4-3: 报文接收流程图

开始

产生错误帧

CANINTF.RX0IF 位决定

接收缓冲器是否为空以及

是否可以接收新的报文

否

否

是

RXB0CTRL.BUKT 位决定在

RXB0 满时,新的报文是否

可滚存到 RXB1 中

检测到

起始帧吗?

是

开始将报文载入

报文集成缓冲器(MAB)

收到的

报文有效吗?

是

报文

符合滤波器

RXB0 条件吗?

否

报文

符合滤波器

RXB1 条件吗?

否

返回开始

是

CANINTF.RX0IF =

将报文移入 RXB0

CANINTF.RX0IF =

根据满足的验收滤波器条件,

将 RXB0CTRL.FILHIT <0> 置 1

CANINTE.RX0IE = 1?

BFPCTRL.B0BFM =

BF1CTRL.B0BFE = 1?

是

否

且

否

0?

1

是

1

否

RXB0CTRL.BUKT =

是

产生溢出错误:

EFLG.RX0OVR 置 1

RXB0

RXBF0

引脚 = 0

是

1?

否

产生溢出错误:

EFLG.RX1OVR 置 1

CANINTE.ERRIE =

根据报文载入哪个接收缓冲

器,将 CANSTAT <3:0> 置 1

是

在 INT 引脚上

产生中断

在 INT 引脚上

产生中断

否

1?

返回开始

RXB1

RXBF1

引脚 = 0

否

CANINTF.RX1IF =

根据满足的验收滤波器条件,

将 RXB0CTRL.FILHIT <2:0> 置 1

是

CANINTE.RX1IE =

是

BFPCTRL.B1BFM =

BF1CTRL.B1BFE = 1?

是

将报文移入 RXB1

CANINTF.RX1IF = 1

否

且

否

0?

1?

1

DS21801D_CN 第 26 页 初稿 2005 Microchip Technology Inc.

Page 27

寄存器 4-1: RXB0CTRL——接收缓冲器 0 控制寄存器 (地址:60h)

U-0 R/W-0 R/W-0 U-0 R-0 R/W-0 R-0 R-0

— RXM1 RXM0 — RXRTR BUKT BUKT1 FILHIT0

bit 7 bit 0

bit 7 未用:读为 0

bit 6-5 RXM:接收缓冲器工作模式位

11 = 关闭屏蔽/滤波功能;接收所有报文

10 = 只接收符合滤波器条件的带有扩展标识符的有效报文

01 = 只接收符合滤波器条件的带有标准标识符的有效报文

00 = 接收符合滤波器条件的所有带扩展标识符或标准标识符的有效报文

bit 4 未用:读为 0

bit 3 RXRTR:接收到远程传送请求位

1 = 接收到远程传送请求

0 = 没有接收到远程传送请求

bit 2 BUKT:滚存使能位

1 = 如果 RXB0 满, RXB0 接收到的报文将被滚存至 RXB1

0 = 滚存禁止

bit 1 BUKT1:只读位, BUKT 位备份 (仅供 MCP2515 器件内部使用)

bit 0 FILHIT:滤波器命中位——指明使能报文接收的验收滤波寄存器编号

1 = 验收滤波寄存器 1 (RXF1)

0 = 验收滤波寄存器 0 (RXF0)

注: 如果发生从 RXB0 到 RXB1 的滚存, FILHIT 位将反映接收滚存报文的滤波器

MCP2515

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 27 页

Page 28

MCP2515

寄存器 4-2: RXB1CTRL——接收缓冲器 1 控制寄存器 (地址:70h)

U-0 R/W-0 R/W-0 U-0 R-0 R-0 R-0 R-0

— RXM1 RXM0 — RXRTR FILHIT2 FILHIT1 FILHIT0

bit 7 bit 0

bit 7 未用:读为 0

bit 6-5 RXM:接收缓冲器工作模式位

11 = 关闭屏蔽 / 滤波功能;接收所有报文

10 = 只接收符合滤波器条件的带有扩展标识符的有效报文

01 = 只接收符合滤波器条件的带有标准标识符的有效报文

00 = 接收符合滤波器条件的所有带扩展标识符或标准标识符的有效报文

bit 4 未用:读为 0

bit 3 RXRTR:接收到远程传送请求位

1 = 接收到远程传送请求

0 = 没有接收到远程传送请求

bit 2-0 FILHIT:滤波器命中位——指明使能报文接收的验收滤波寄存器编号

101 = 验收滤波寄存器 5 (RXF5)

100 = 验收滤波寄存器 4 (RXF4)

011 = 验收滤波寄存器 3 (RXF3)

010 = 验收滤波寄存器 2 (RXF2)

001 = 验收滤波寄存器 1 (RXF1)(只有当 RXB0CTRL 中的 BUKT 位置 1 时)

000 = 验收滤波寄存器 0 (RXF0)(只有当 RXB0CTRL 中的 BUKT 位置 1 时)

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

DS21801D_CN 第 28 页 初稿 2005 Microchip Technology Inc.

Page 29

MCP2515

寄存器 4-3: BFPCTRL——RXnBF 引脚控制寄存器和状态寄存器 (地址:0Ch)

U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

— — B1BFS B0BFS B1BFE B0BFE B1BFM B0BFM

bit 7 bit 0

bit 7 未用:读为 0

bit 6 未用:读为 0

bit 5 B1BFS:R

- 当 RX1B 配置为中断引脚时,读为 0

bit 4 B0BFS:RX0BF 引脚状态位 (只限数字输出工作模式)

- 当 RX0BF 配置为中断引脚时,读为 0

bit 3 B1BFE:RX1BF 引脚功能使能位

1 = 引脚功能使能,工作模式由 B1BFM 位决定

0 = 引脚功能禁止,引脚为高阻态

bit 2 B0BFE:R

1 = 引脚功能使能,工作模式由 B0BFM 位决定

0 = 引脚功能禁止,引脚为高阻态

bit 1 B1BFM:RX1BF 引脚工作模式位

1 = 当有效报文载入 RXB1 时,该引脚用来产生中断

0 = 数字输出模式

bit 0 B0BFM:R

1 = 当有效报文载入 RXB0 时,该引脚用来产生中断

0 = 数字输出模式

X1BF 引脚状态位 (只限数字输出工作模式)

X0BF 引脚功能使能位

X0BF 引脚工作模式位

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

寄存器 4-4: RXBnSIDH——接收缓冲器 n 标准标识符高位 (地址:61h, 71h)

R-xR-xR-xR-xR-xR-xR-xR-x

SID10 SID9 SID8 SID7 SID6 SID5 SID4 SID3

bit 7 bit 0

bit 7-0 SID:标准标识符位 <10:3>

这些位装载接收报文标准标识符中最高 8 位

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 29 页

Page 30

MCP2515

寄存器 4-5: RXBnSIDL——接收缓冲器 n 标准标识符低位 (地址:62h, 72h)

R-x R-x R-x R-x R-x U-0 R-x R-x

SID2 SID1 SID0 SRR IDE —EID17EID16

bit 7 bit 0

bit 7-5 SID:标准标识符位 <2:0>

这些位装载接收报文中标准标识符的最低 3 位

bit 4 SRR:远程发送请求位 (只有当 IDE 位 = 0 时有效)

1 = 收到标准远程发送请求帧

0 = 收到标准数据帧

bit 3 IDE:扩展标识符标志位

该位表明收到的报文是标准帧还是扩展帧

1 = 收到的报文是扩展帧

0 = 收到的报文是标准帧

bit 2 未用:读为 0

bit 1-0 EID:扩展标识符位 <17:16>

这些位装载接收报文中扩展标识符的最高 2 位

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

寄存器 4-6: RXBnEID8——接收缓冲器 n 扩展标识符高位 (地址:63h, 73h)

R-xR-xR-xR-xR-xR-xR-xR-x

EID15 EID14 EID13 EID12 EID11 EID10 EID9 EID8

bit 7 bit 0

bit 7-0 EID:扩展标志符位 <15:8>

这些位装载接收报文扩展标识符中的第 8 到 15 位

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

DS21801D_CN 第 30 页 初稿 2005 Microchip Technology Inc.

Page 31

MCP2515

寄存器 4-7: RXBnEID0——接收缓冲器 n 扩展标识符低位 (地址:64h, 74h)

R-xR-xR-xR-xR-xR-xR-xR-x

EID7 EID6 EID5 EID4 EID3 EID2 EID1 EID0

bit 7 bit 0

bit 7-0 EID:扩展标识符位 <7:0>

这些位装载接收报文扩展标识符的最低 8 位

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

寄存器 4-8: RXBnDLC——接收缓冲器 n 数据长度码 (地址:65h, 75h)

U-0 R-x R-x R-x R-x R-x R-x R-x

— RTR RB1 RB0 DLC3 DLC2 DLC1 DLC0

bit 7 bit 0

bit 7 未用:读为 0

bit 6 RTR:扩展帧远程发送请求位

(只有当 RXBnSIDL.IDE = 1 时有效)

1 = 接收到扩展远程 (发送请求)帧

0 = 接收到扩展数据帧

bit 5 RB1:保留位 1

bit 4 RB0:保留位 0

bit 3-0 DLC:数据长度码位 <3:0>

表明接收到的数据字节个数

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

寄存器 4-9: RXBnDM——接收缓冲器 n 数据字段字节 M

(地址:66h - 6Dh, 76h - 7Dh)

R-xR-xR-xR-xR-xR-xR-xR-x

RBnDm7 RBnDm6 RBnDm5 RBnDm4 RBnDm3 RBnDm2 RBnDm1 RBnDm0

bit 7 bit 0

bit 7-0 RBnDm7:RBnDm0:接收缓冲器 n 数据字段字节 m

这 8 个字节包含接收报文的数据信息

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 31 页

Page 32

MCP2515

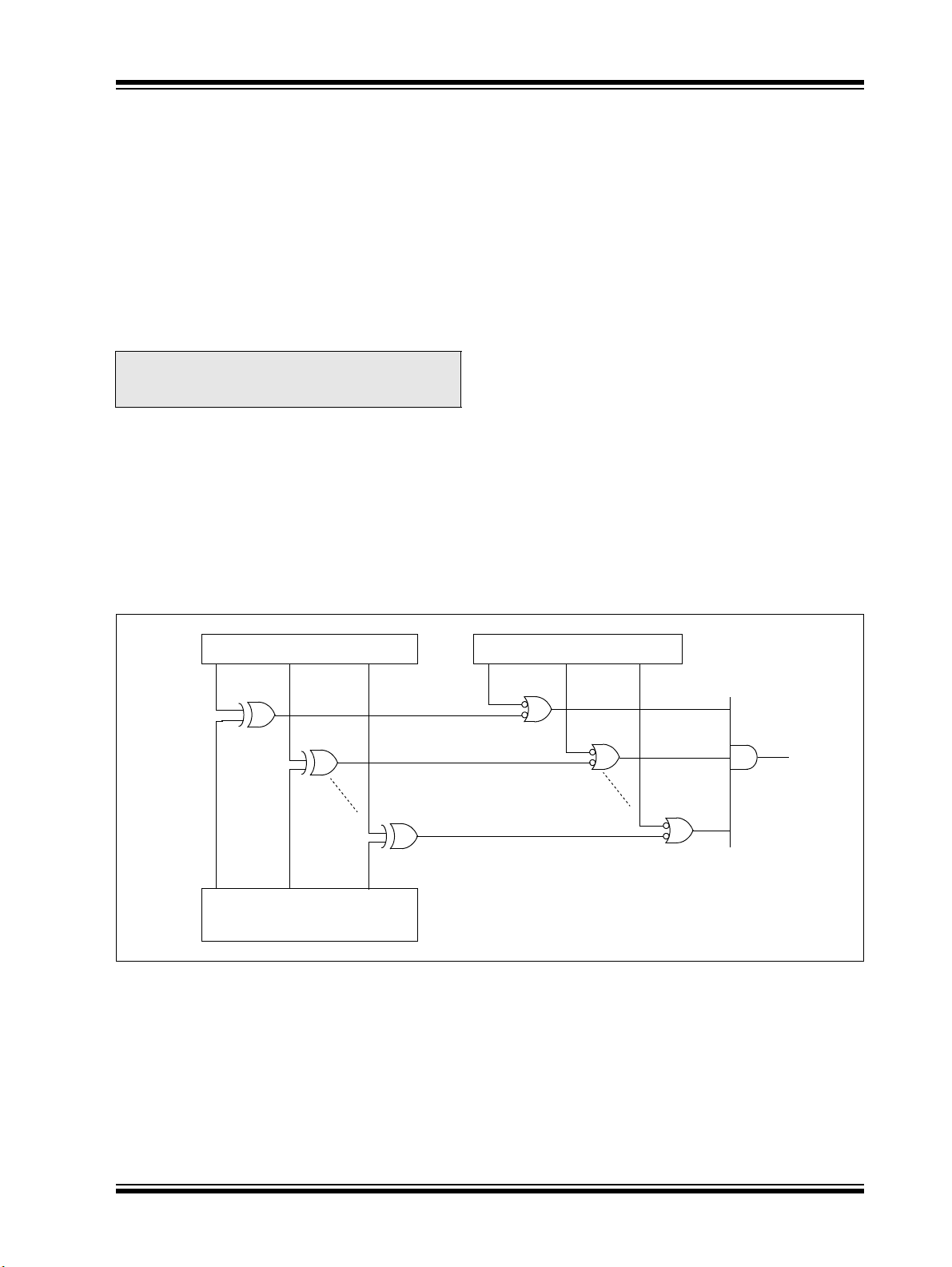

4.5 报文验收滤波器及屏蔽寄存器

报文验收滤波器及屏蔽寄存器用来确定报文集成缓冲器

中的报文是否应被载入接收缓冲器 (见图 4-5)。一旦

MAB接收到有效报文,报文中的标识符字段将与过滤寄

存器中的值进行比较。如果两者匹配,该报文将被载入

相应的接收缓冲器。

4.5.1 数据字节滤波

当接收到标准数据帧 (11 位标识符), MCP2515 自动

将通常与扩展标识符有关的 16 位屏蔽寄存器和滤波器

应用于数据字段的头 16 位(数据字节 0 和 1)。图 4-4

说明了屏蔽寄存器和滤波器如何应用到扩展和标准数据

帧。

在执行高层协议 (Higher Layer Protocol, HLP)对头

个数据字节进行滤波时 (如, DeviceNet™),数据字

节滤波减轻了 MCU 的负载。

4.5.2 滤波器匹配

滤波屏蔽寄存器(见寄存器 4-14 到寄存器 4-17)用 于

确定滤波器对标识符中的哪些位进行校验。表 4-2 所示

的真值表显示了标识符中的每一位是如何与验收屏蔽寄

图 4-4:对CAN 帧进行验收屏蔽及滤波

存器和滤波器进行比较,以确定该报文是否应被载入接

收缓冲器。屏蔽寄存器主要确定对标识符中的哪些位进

行滤波。如果某屏蔽位设置为零,对应的标识符位将被

自动接收而不进行滤波。

表 4-2:滤波/ 屏蔽寄存器真值表

屏蔽位 n 过滤位 n

0X X

10 0

10 1

11 0

11 1

注: X = 任意值

正如接收缓冲器方框图 (图 4-2)所示,RXB0 接收缓

冲器配备有验收滤波寄存器 RXF0 和 RXF1 (以及过滤

屏蔽寄存器 RXM0)。RXB1 配备有验收滤波寄存器

RXF2、RXF3、RXF4、RXF5和滤波屏蔽寄存器RXM1。

扩展帧

报文

标识符位

接受或拒绝

位 n

接受

接受

拒绝

拒绝

接受

ID10 ID0 EID17 EID0

对全部 29 位 ID 字段进行屏蔽滤波

标准数据帧

ID10 ID0 数据字节 0 数据字节 1

11 位 ID 标准帧

* 两个 MSb(EID17 和 EID16)屏蔽滤波位未使用。

*

16 位数据滤波 *

DS21801D_CN 第 32 页 初稿 2005 Microchip Technology Inc.

Page 33

MCP2515

4.5.3 FILHIT 位

接收到的报文与滤波器匹配与否取决于 RXBnCTRL 寄

存器中的 FILHIT 位。 RXB0CTRL.FILHIT0 位用于缓冲

器 0, RXB1CTRL.FILHIT<2:0> 用于缓冲器 1。

用于接收缓冲器 1(RXB1)的三个 FILHIT 位编码如下:

- 101 = 验收滤波寄存器 5 (RXF5)

- 100 = 验收滤波寄存器 4 (RXF4)

- 011 = 验收滤波寄存器 3 (RXF3)

- 010 = 验收滤波寄存器 2 (RXF2)

- 001 = 验收滤波寄存器 1 (RXF1)

- 000 = 验收滤波寄存器 0 (RXF0)

注: 只有在 RXB0CTRL 中的 BUKT 位置 1 时,

才会出现 000 和 001,从而允许 RXB0 中

的报文滚存到 RXB1 中。

RXB0CTRL 包含 BUKT 位和 FILHIT<0> 位的备份。

BUKT 位的编码方式使得这三位的用法类似于

RXB1CTRL.FILHIT 位,并且可区分无滚存发生和滚存

发生时滤波器 RXF0 和 RXF1 接收报文的情况。

- 111 = 验收滤波寄存器 1 (RXB1)

- 110 = 验收滤波寄存器 0 (RXB1)

- 001 = 验收滤波寄存器 1 (RXB0)

- 000 = 验收滤波寄存器 0 (RXB0)

如果 BUKT 位清零,对应 6 个滤波寄存器就有 6 种编码

状态。如果 BUKT 位置 1,除了上述 6 种编码状态外,

还有 2 种编码状态分别对应滚存到 RXB1 的 RXF0 和

RXF1。

4.5.4 多滤波器匹配

如果接收报文符合一个以上滤波寄存器的接受条件,

FILHIT 位中的二进制代码将反映其中编号最小的滤波

寄存器。例如,如果滤波器 RXF2 和 RXF4 同时与接收

报文匹配, FILHIT 中将装载 RXF2 编码值。这实际上

为编号较小的验收滤波寄存器赋予了较高的优先级。接

收报文将按照编号升序依次与滤波寄存器进行匹配比

较。这意味着 RXB0 的优先级比 RXB1 高。

4.5.5 配置屏蔽寄存器和滤波寄存器

只有在 MCP2515 处于配置模式时,才能对屏蔽和滤波

寄存器中的内容进行修改(见第 10.0 节“工作模式”)。

图 4-5: 报文验收屏蔽及滤波操作

验收滤波寄存器 验收屏蔽寄存器

RXFn

0

RXFn

1

RXFn

n

报文集成缓冲器

标识符

RXMn

0

RXMn

1

RXMn

n

RxRqst

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 33 页

Page 34

MCP2515

寄存器 4-10: RXFnSIDH——验收滤波寄存器 n 标准标识符高位

(地址:00h, 04h, 08h, 10h, 14h, 18h)

R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x

SID10 SID9 SID8 SID7 SID6 SID5 SID4 SID3

bit 7 bit 0

bit 7-0 SID:标准标识符滤波位 <10:3>

这些位装载了用来对接收报文中标准标识符位 <10:3> 进行滤波判断的滤波位

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

寄存器 4-11: RXFnSIDL——验收滤波寄存器 n 标准标识符低位

(地址:01h, 05h, 09h, 11h, 15h, 19h)

R/W-x R/W-x R/W-x U-0 R/W-x U-0 R/W-x R/W-x

SID2 SID1 SID0

bit 7 bit 0

— EXIDE —EID17EID16

bit 7-5 SID:标准标识符滤波位 <2:0>

这些位装载了用来对接收报文中标准标识符位 <2:0> 进行滤波判断的滤波位

bit 4 未用:读为 0

bit 3 EXIDE:扩展标识符使能位

1 = 报文滤波仅应用于扩展帧

0 = 报文滤波仅应用于标准帧

bit 2 未用:读为 0

bit 1-0 EID:扩展标识符滤波位 <17:16>

这些位装载了用来对接收报文中扩展标识符位 <17:16> 进行滤波判断的滤波位

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

DS21801D_CN 第 34 页 初稿 2005 Microchip Technology Inc.

Page 35

寄存器 4-12: RXFnEID8——验收滤波寄存器 n 扩展标识符高位

(地址:02h, 06h, 0Ah, 12h, 16h, 1Ah)

R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x

EID15 EID14 EID13 EID12 EID11 EID10 EID9 EID8

bit 7 bit 0

bit 7-0 EID:扩展标识符滤波位 <15:8>

这些位装载了用来对接收报文中扩展标识符位 <15:8> 进行滤波判断的滤波位

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

寄存器 4-13: RXFnEID0——验收滤波寄存器 n 扩展标识符低位

(地址:03h, 07h, 0Bh, 13h, 17h, 1Bh)

R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x

EID7 EID6 EID5 EID4 EID3 EID2 EID1 EID0

bit 7 bit 0

MCP2515

bit 7-0 EID:扩展标识符滤波位 <7:0>

这些位装载了用来对接收报文中扩展标识符位 <7:0> 进行滤波判断的滤波位

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

寄存器 4-14: RXMnSIDH——验收屏蔽寄存器 n 标准标识符高位 (地址:20h, 24h)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

SID10 SID9 SID8 SID7 SID6 SID5 SID4 SID3

bit 7 bit 0

bit 7-0 SID:标准标识符屏蔽位 <10:3>

这些位装载了用来对接收报文中标准标识符位 <10:3> 进行屏蔽判断的屏蔽位

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 35 页

Page 36

MCP2515

寄存器 4-15: RXMnSIDL——验收屏蔽滤波器 n 标准标识符低位 (地址:21h, 25h)

R/W-0 R/W-0 R/W-0 U-0 U-0 U-0 R/W-0 R/W-0

SID2 SID1 SID0 — — —EID17EID16

bit 7 bit 0

bit 7-5 SID:标准标识符屏蔽位 <2:0>

这些位装载了用来对接收报文中标准标识符位 <2:0> 进行屏蔽判断的屏蔽位

bit 4-2 未用:读为 0

bit 1-0 EID:扩展标识符屏蔽位 <17:16>

这些位装载了用来对接收报文中扩展标识符位 <17:16> 进行屏蔽判断的屏蔽位

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

寄存器 4-16: RXMnEID8——验收屏蔽寄存器 n 扩展标识符高位 (地址:22h, 26h)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

EID15 EID14 EID13 EID12 EID11 EID10 EID9 EID8

bit 7 bit 0

bit 7-0 EID:扩展标识符屏蔽位 <15:8>

这些位装载了用来对接收报文中扩展标识符位 <15:8> 进行屏蔽判断的屏蔽位

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

寄存器 4-17: RXMnEID0——验收屏蔽寄存器 n 扩展标识符低位 (地址:23h, 27h)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

EID7 EID6 EID5 EID4 EID3 EID2 EID1 EID0

bit 7 bit 0

bit 7-0 EID:扩展标识符屏蔽位 <7:0>

这些位装载了用来对接收报文中扩展标识符位 <7:0> 进行屏蔽判断的屏蔽位

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

DS21801D_CN 第 36 页 初稿 2005 Microchip Technology Inc.

Page 37

MCP2515

5.0 位定时

CAN 总线上的所有节点都必须具有相同的标称比特率。

CAN 协议采用不归零(Non Return to Zero,NRZ)编

码方式,在数据流中不对时钟信号进行编码。因此,接

收时钟信号必须由接收节点恢复并与发送器的时钟同

步。

由于不同节点的振荡器频率和传输时间不同,接收器应

具有某种能与数据传输边沿同步的锁相环(Phase Lock

Loop, PLL)来同步时钟并保持这种同步。鉴于数据采

用 NRZ 编码,有必要进行位填充以确保至少每 6 位时

间发生一次边沿,使数字锁相环 (Digital Phase Lock

Loop, DPLL)同步。

MCP2515 通过 DPLL 实现位定时。DPLL 被配置成同输

入数据同步,并为发送数据提供标称定时。 DPLL 将每

一个位时间分割为由最小单位为时间份额(Time

Quanta, TQ)所组成的多个时间段。

在位时间帧中执行的总线定时功能,例如与本地振荡器

同步、网络传输延迟补偿和采样点定位等,都是由

DPLL 的可编程位定时逻辑来规定的。

5.1 CAN 位时间

CAN 总线上的所有器件都必须使用相同的比特率。然

而,并非所有器件都要求具有相同的主振荡器时钟频

率。对于采用不同时钟频率的器件,应通过适当设置波

特率预分频比以及每一时间段中的时间份额的数量来对

比特率进行调整。

CAN 位时间由互不重叠的时间段组成。每个时间段又由

时间份额 (TQ)组成,在本数据手册的后面部分将对

此进行解释。在 CAN 规范中,标称比特率 (Nominal

Bit Rate, NBR)定义为在不需要再同步的情况下,理

想发送器每秒发送的位数,它可用下面的公式来表示:

公式 5-1:

NBR f

bit

1

-------==

t

bit

标称位时间:

标称位时间 (Nominal Bit Time, NBT)( t

重叠的段时间段组成(图 5-1)。因此 NBT 为下列时间

段之和:

t

bittSyncSegtPropSegtPS1tPS2

+++=

)由互不

bit

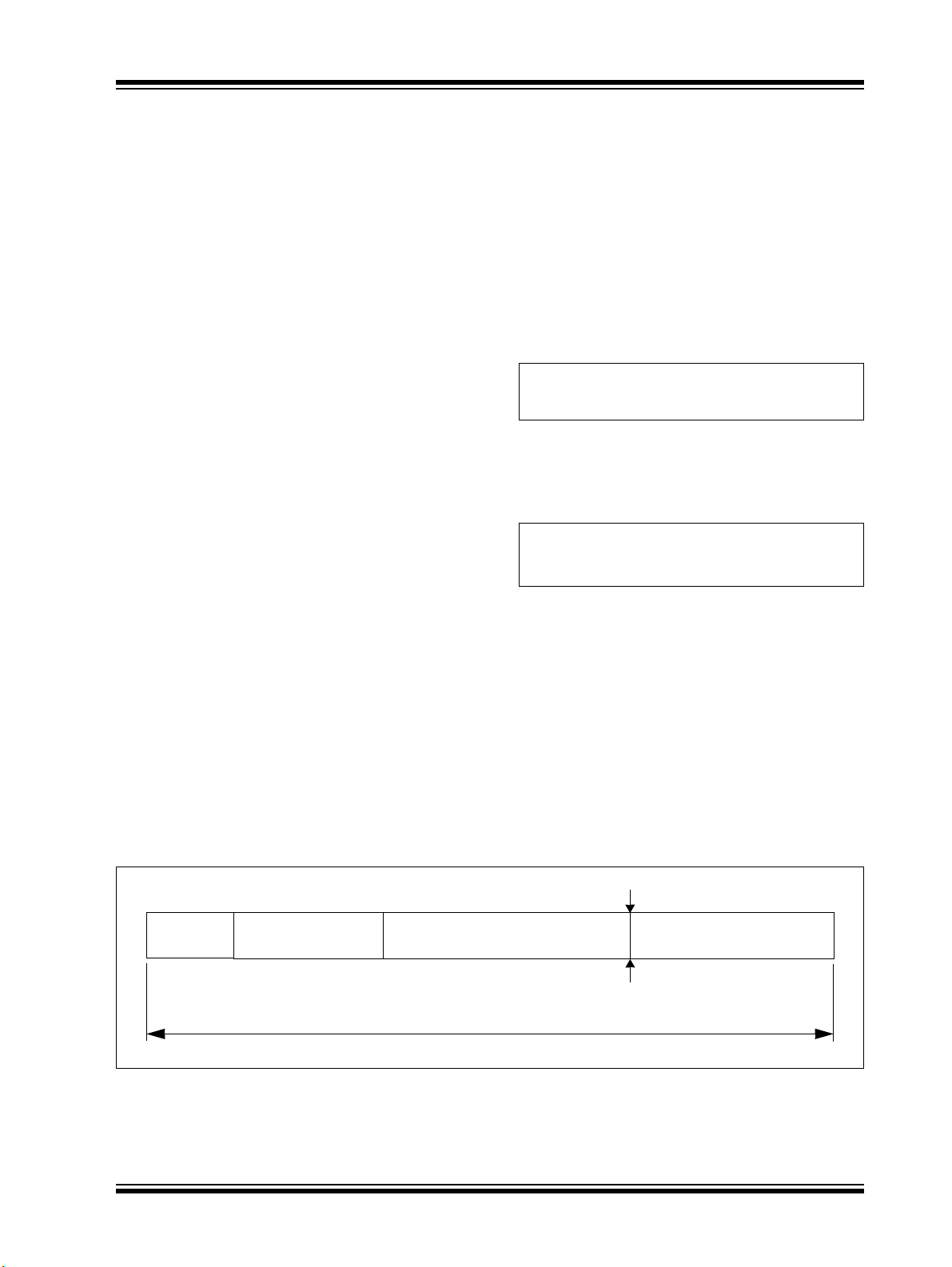

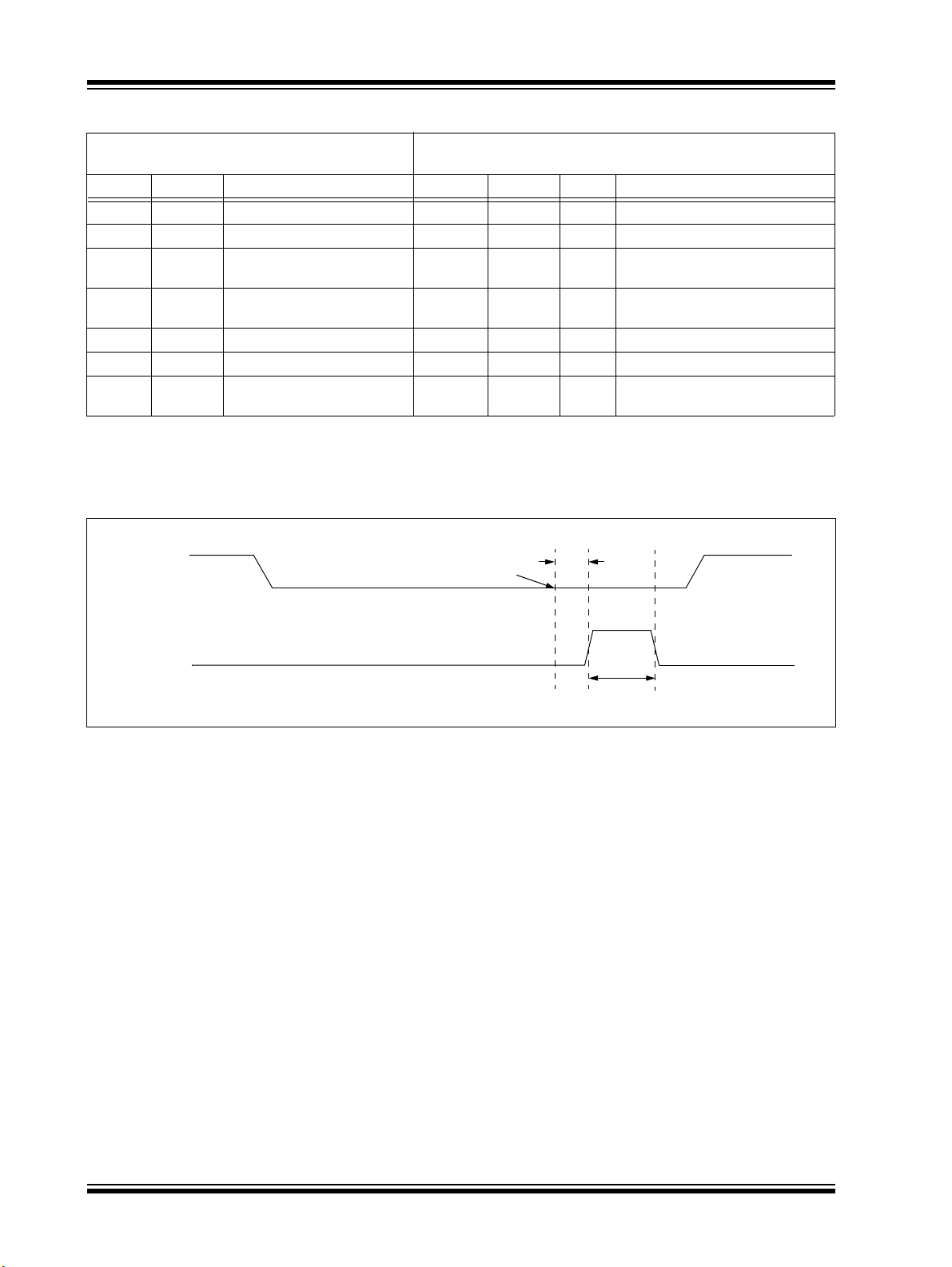

图 5-1: CAN 位时间各段

同步段 传播段

与 NBT 相关的参数是采样点、同步跳转宽度

(Synchronization Jump Width, SJW)和信息处理时

间(Information Processing Time,IPT),在后面会对

此进行解释。

同步段

同步段 (SyncSeg)为 NBT 中的首段,用于同步 CAN

总线上的各个节点。输入信号的跳变沿就发生在同步

段,该段持续时间为 1TQ。

相位缓冲段(PS1)

标称位时间(NBT),t

相位缓冲段(PS2)

采样点

bit

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 37 页

Page 38

MCP2515

传播段

传播段 (PropSeg)用于补偿各节点之间的物理传输延

迟时间。传输延迟时间为信号在总线上传播时间的两

倍,包括总线驱动器延迟时间。传播段的长度可编程设

定为 1 – 8 TQ。

相位缓冲段 1 (PS1)和相位缓冲段 2 (PS2)

两个相位缓冲段 PS1 和 PS2 用于补偿总线上的边沿相

位误差。通过再同步,可以延长 PS1 (或缩短 PS2)。

PS1 可编程设定为 1 – 8 TQ,而 PS2 可编程设定为 2 –

8TQ。

采样点

采样点是位时间内的一个时间点。在该时间点,读取总

线电平并进行分析。采样点位于相位缓冲段 PS1 的终

点。但当采样模式设置为每位采样 3 次时例外。这种情

况下,在 PS1 的终点仍然对某一位进行采样时,前两次

的采样时间间隔为TQ/2,而该位的值将根据三个采样值

中至少两次采样的相同值决定。

信息处理时间

信息处理时间 (IPT)是确定采样点的位电平值所需要

的时间。 IPT 从采样点开始,以 TQ 计量, Microchip

CAN 模块将该时间长度定义为 2 TQ。PS2 同样开始于

采样点,且为位时间的最后一个时间段,因此 PS2 的最

小值不能小于 IPT。

故:

PS2

min

IPT 2TQ==

同步跳转宽度

同步跳转宽度(SJW)可通过编程设定为 1 – 4 TQ,它

可对位时钟进行必要的调整来保持与发送报文同步。本

数据手册的后面部分将涉及有关同步的更多详细内容。

时间份额

组成位时间的每个段都由时间份额 (TQ)组成。每个

时间份额的长度取决于振荡器周期 (t

为两个振荡器周期。图 5-2 显示了如何从 T

推导出位周期。 TQ 的长度等于一个 TQ 时钟周期

(t

程预分频器对它进行编程设置。以下公式对此进行了阐

述:

),利用称为波特率预分频器(BRP)的可编

BRPCLK

公式 5-2:

TQ 2 BRP T

其中:BRP 为寄存器 5-1 中所列的配置值。

⋅⋅

OSC

)。通常 TQ

OSC

2 BRP⋅

------------------ -==

F

OSC

OSC

和 TQ

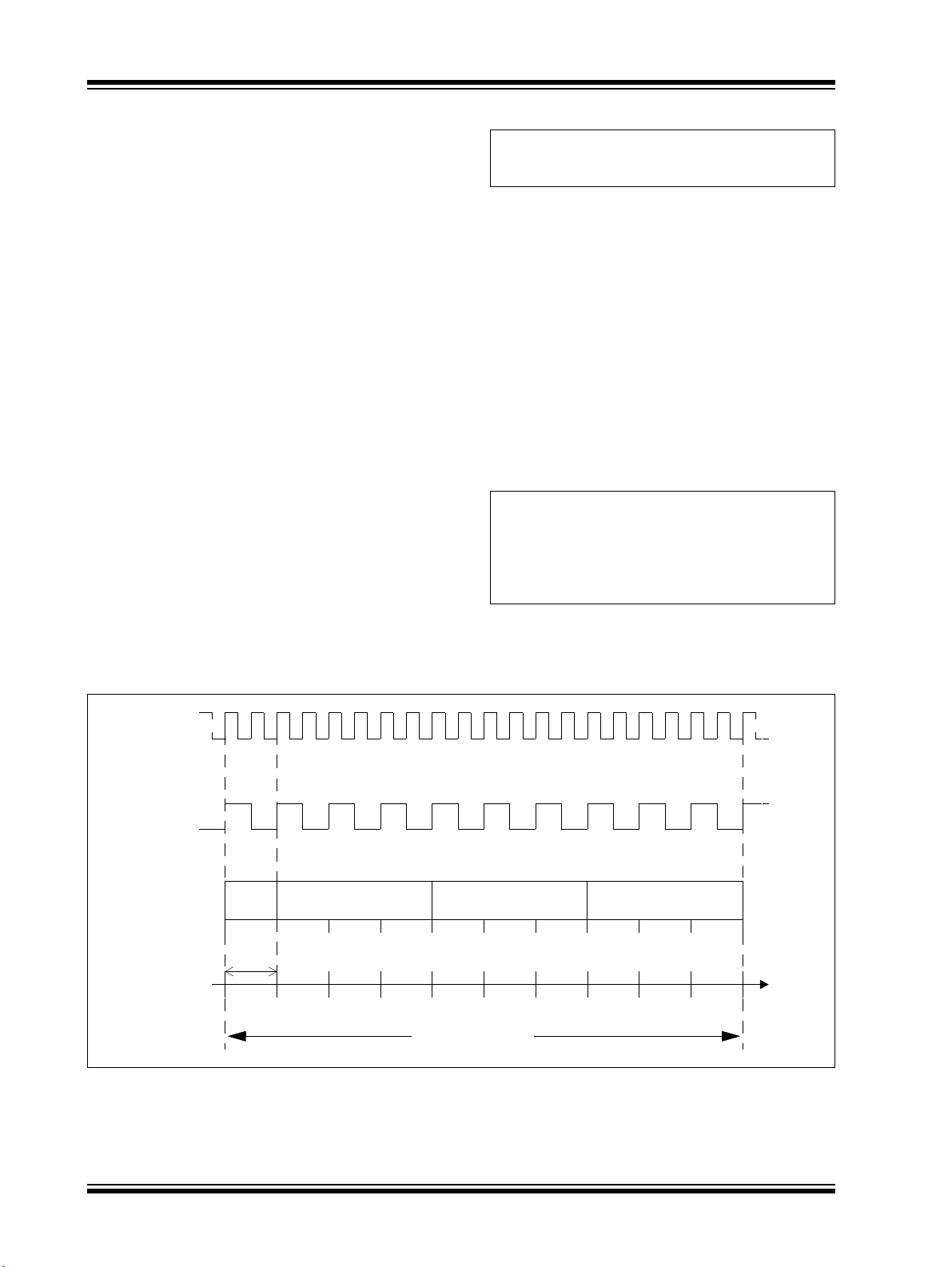

图 5-2: TQ 和位周期

tOSC

TBRPCLK

tBIT

同步段

(固定值)

TQ

(t

TQ)

传播段

(可编程)

相位缓冲段 PS1

(可编程)

CAN 位时间

相位缓冲段 PS2

(可编程)

DS21801D_CN 第 38 页 初稿 2005 Microchip Technology Inc.

Page 39

MCP2515

5.2 同步

为补偿总线上各节点振荡器频率之间的相移,每个 CAN

控制器必须能够与输入信号的相关信号沿同步。同步过

程是实现 DPLL 功能的过程。

当检测到发送数据中的跳变沿,逻辑电路将跳变沿的位

置与所期望的时间段 (同步段)进行比较,随后电路将

对相位缓冲段 PS1 和相位缓冲段 PS2 的值进行必要的

调整。

存在两种同步机制:

1. 硬同步。

2. 再同步。

5.2.1 硬同步

只有在总线空闲条件下发生隐性位到显性位的跳变边沿

时才进行硬同步,表明报文传输开始。在硬同步之后,

位时间计数器随同步段重新开始计数。

硬同步强行将已发生的跳变沿置于重新开始的位时间同

步段内。根据同步规则,如果某一位时间内已有一个硬

同步出现,该位时间将不会发生再同步。

5.2.2 再同步

再同步可能导致相位缓冲段 PS1 延长或相位缓冲段

PS2 缩短。这两个相位缓冲段的延长时间或缩短时间上

限由同步跳转宽度 (SJW)给定。

如图 5-3 所示,相位缓冲段 PS1 加上 SJW 值,而相位

缓冲段 PS2 减去 SJW 值。 SJW 代表了 DPLL 的循环

过滤功能。 SJW 可通过编程设定为 1 - 4 TQ。

5.2.2.2 无相位误差 (e = 0)

如果相位误差的幅度小于等于同步跳变宽度(SJW)的

编程值,再同步的作用与硬同步相同。

5.2.2.3 正相位误差 (e > 0)

如果相位误差的幅度大于同步跳变宽度(SJW)且相位

误差为正值,相位缓冲段 PS1 延长同步跳变宽度。

5.2.2.4 负相位误差 (e < 0)

如果相位误差的幅度大于同步跳变宽度(SJW)且相位

误差为负值,相位缓冲段 PS2 缩短同步跳变宽度。

5.2.3 同步规则

1. 只有从隐性位到显性位的跳变沿才可用于同步。

2. 一个位时间内仅允许同步一次。

3. 只有在前一个采样点测得的值(上一次读取的总

线值)与紧接跳变沿之后的总线值不同,该边沿

才可用于同步。

4. 如果相位误差为正(e > 0),发送节点不会发生

再同步。

5. 如果相位误差的绝对幅度大于同步跳变宽度

(SJW),将会调整相应的相位缓冲段与 SJW 相

等。

5.2.2.1 相位误差

NRZ 位编码方式没有在报文中编码时钟。时钟信息只可

由隐性位到显性位的跳变沿获得。由于总线上最多可出

现的连续相同值 (位填充)的位数是固定的,应确保发

送一帧期间与位流的再同步。

跳变沿的相位误差由相应同步段的跳变沿位置给定,并

以 TQ 计量。相位误差定义如下:

• 如果跳变沿位于同步段内,则 e = 0。

• 如果跳变沿位于采样点之前,则 e > 0

(PS1 增加 TQ)。

• 如果跳变沿位于前一位的采样点之后,则 e < 0

(PS2 减去 TQ)。

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 39 页

Page 40

MCP2515

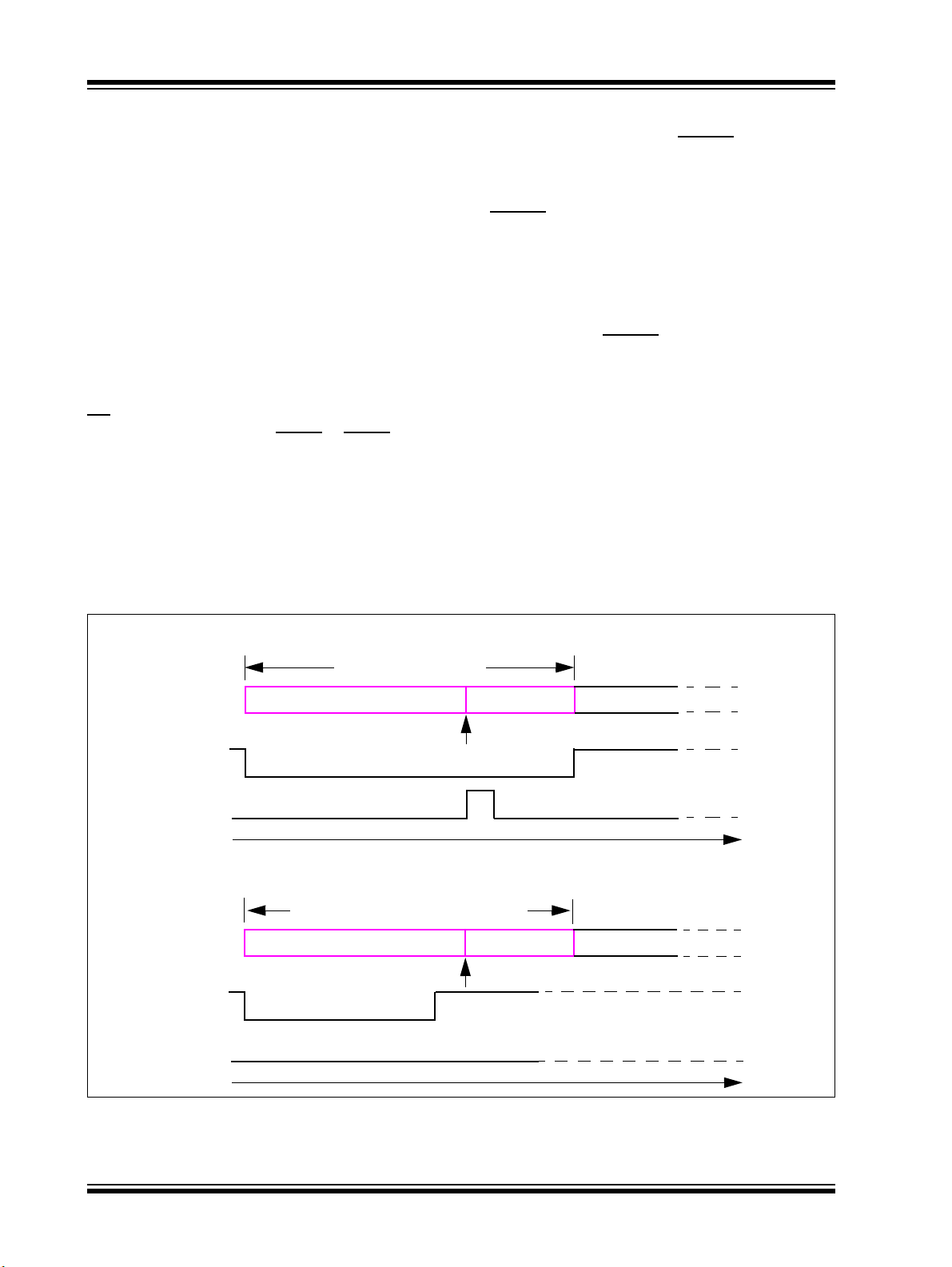

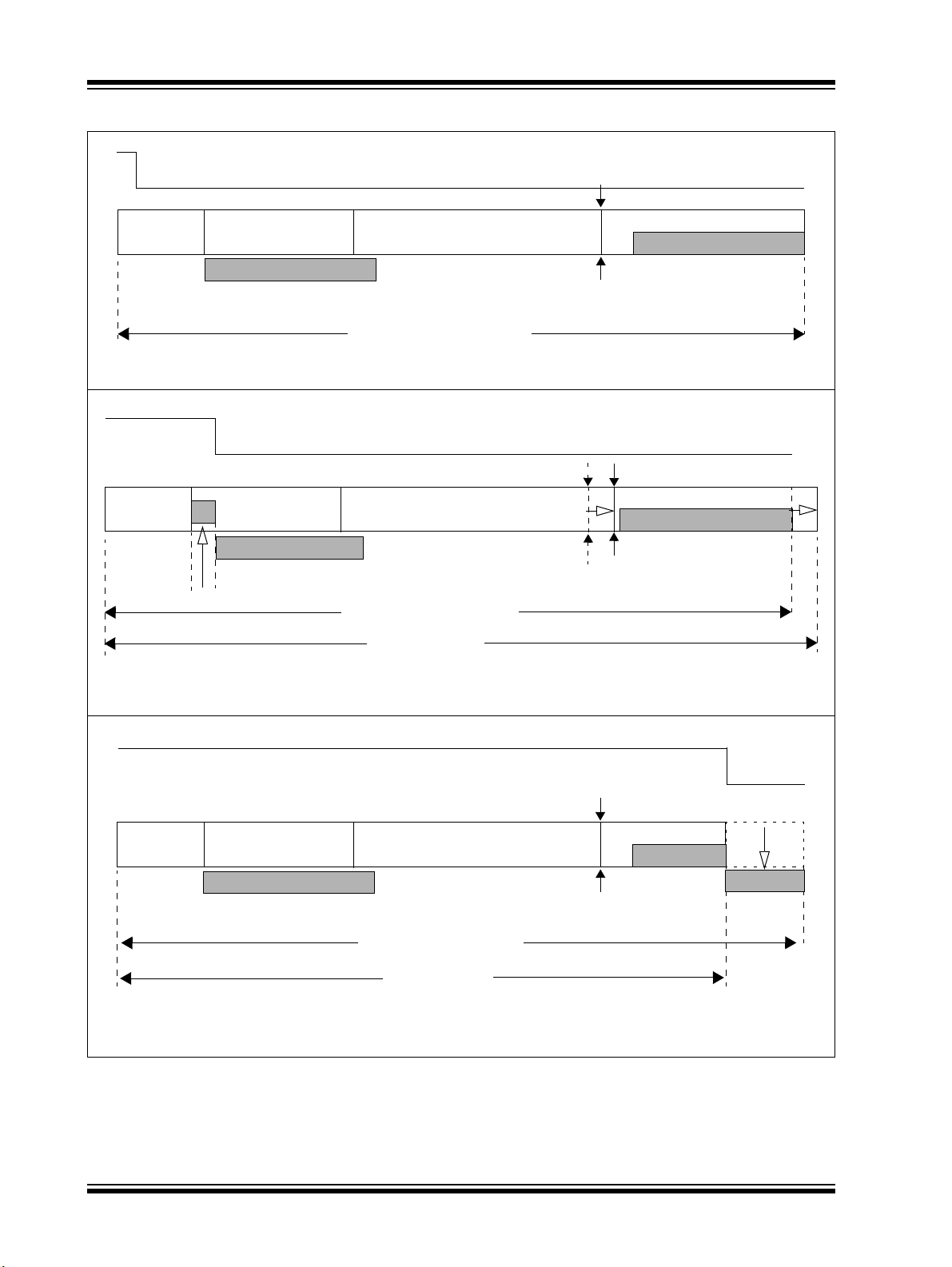

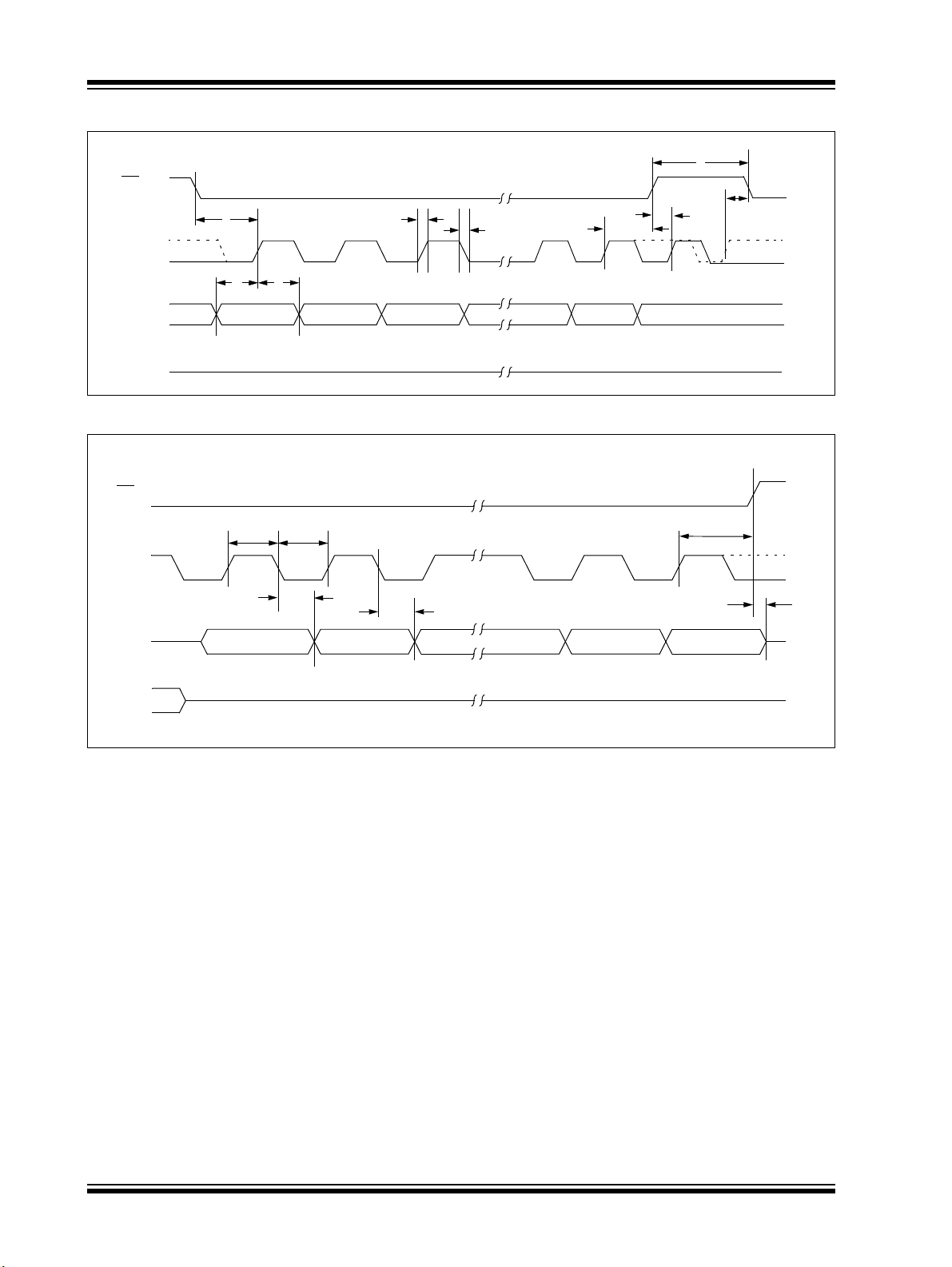

图 5-3: 同步位时间

输入信号(e = 0)

同步段

输入信号

(e > 0)

同步段

传播段

SJW(PS1)

传播段

SJW(PS1)

相位缓冲段(PS1)

标称位时间(NBT)

不发生再同步(e = 0)

相位缓冲段(PS1)

标称位时间(NBT)

实际位时间

与一个较慢的发送器再同步(e > 0)

相位缓冲段(PS2)

SJW(PS2)

采样点

相位缓冲段(PS2)

SJW(PS2)

采样点

输入信号(e < 0)

同步段

DS21801D_CN 第 40 页 初稿 2005 Microchip Technology Inc.

传播段

SJW(PS1)

标称位时间(NBT)

与一个较快的发送器再同步(e < 0)

相位缓冲段(PS1)

实际位时间

相位缓冲段(PS2)

SJW(PS2)

采样点

Page 41

MCP2515

5.3 对时间段编程

对时间段的编程设定必须满足以下要求:

• 传播段 + 相位缓冲段 PS1 >= 相位缓冲段 PS2

• 传播段 + 相位缓冲段 PS1 >= T

DELAY

• 相位缓冲段 PS2 > 同步跳转宽度 SJW

例如,假设 F

OSC = 20 MHz 时欲实现 125 kHz 的 CAN

波特率:

OSC = 50 ns,选择 BRP<5:0> = 04h,则 TQ = 500 ns。

T

欲达到 125 kHz,位时间应为 16 TQ。

位的采样时刻取决于系统参数,通常应发生在位时间的

60-70% 处。同时, T

同步段 = 1 T

Q,传播段 = 2 TQ,这种情况下设置相位缓

冲段 PS1 = 7 T

样。此时相位缓冲段 PS2 长度为 6 T

由于相位缓冲段 PS2 长度为 6 T

DELAY 典型值为 1-2 TQ。

Q,将会在跳变之后的 10 TQ 时进行采

Q。

Q,根据规则, SJW 最

大值为 4 TQ。然而通常状况下,只有当不同节点的时钟

发生不够精确或不稳定 (如采用陶瓷谐振器)时,才需

要较大的 SJW。一般情况下,SJW 取值 1 T

Q 即可满足

要求。

5.4 振荡器容差

位定时要求允许传输速率最高达 125 千位 / 秒的应用应

采用陶瓷谐振器。要满足 CAN 协议的整个总线速度范

围的要求,应采用石英振荡器。节点与节点间的振荡器

频率偏差最多不应超过 1.7%。

5.5 位定时配置寄存器

CAN 总线接口的位定时由配置寄存器 (CNF1、 CNF2

和 CNF3)控制。只有当 MCP2515 处于配置模式时,

才能对这些寄存器进行修改 (见第 10.0 节“工作模

式”)。

5.5.1 CNF1

BRP<5:0> 控制波特率预分频比的设置。这些位根据

OSC1 输入频率设置 TQ 的时间长度。当 BRP<5:0> =

‘b000000’,T

以 TQ 计的同步跳转宽度。

5.5.2 CNF2

PRSEG<2:0> 位设定以 TQ 计的传播段时间长度。

PHSEG1<2:0>位设定以 TQ 计的相位缓冲段PS1的时间

长度。

SAM 控制 RXCAN 引脚的采样次数。将该位置为 1 将对

总线采样 3 次,其中前两次发生在采样点前 T

点,而第三次发生在正常采样时间点 (即相位缓冲段

PS1 终点)。总线数值由至少两次采样的相同值确定。

如果 SAM 位设定为 0,则只在采样点对 RXCAN 引脚

状态采样一次。

BTLMODE 位控制如何确定相位缓冲段 PS2 的时间长

度。如果该位为 1, PS2 的时间长度由 CNF3 的

PHSEG2<2:0> 位设定(见第 5.5.3 节“ CNF3”)。如 果

BTLMODE位为0,PS2的时间长度为相位缓冲段PS1和

信息处理时间(MCP2515 中固定为 2T

值。

Q 最小值取 2TOSC。通 过 SJW<1:0> 选择

Q/2 时间

Q)两者的较大

5.5.3 CNF3

如果 CNF2.BTLMODE 位为 1,则相位缓冲段 PS2 的时

间长度将由 PHSEG2<2:0> 位设定,以 T

BTLMODE 位为 0,则 PHSEG2<2:0> 位不起作用。

Q 计。如果

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 41 页

Page 42

MCP2515

寄存器 5-1: CNF1——配置寄存器 1 (地址:2Ah)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

SJW1 SJW0 BRP5 BRP4 BRP3 BRP2 BRP1 BRP0

bit 7 bit 0

bit 7-6 SJW:同步跳转宽度位 <1:0>

11 = 长度 = 4 x T

10 = 长度 = 3 x TQ

01 = 长度 = 2 x TQ

00 = 长度 = 1 x TQ

bit 5-0 BRP:波特率预分频比位 <5:0>

TQ = 2 x (BRP + 1)/FOSC

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

寄存器 5-2: CNF2——配置寄存器 2 (地址:29h)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

BTLMODE SAM PHSEG12 PHSEG11 PHSEG10 PRSEG2 PRSEG1 PRSEG0

bit 7 bit 0

Q

bit 7 BTLMODE:相位缓冲段 PS2 位时间长度位

1 = PS2 时间长度由 CNF3 的 PHSEG22:PHSEG20 位决定

0 = PS2 时间长度为 PS1 和 IPT (2 T

bit 6 SAM:采样点配置位

1 = 在采样点对总线进行三次采样

0 = 在采样点对总线进行一次采样

bit 5-3 PHSEG1:相位缓冲段 PS1 位时间长度位 <2:0>

(PHSEG1 + 1) x TQ

bit 2-0 PRSEG:传播段长度位 <2:0>

(PRSEG + 1) x T

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

Q

Q)两者的较大值

DS21801D_CN 第 42 页 初稿 2005 Microchip Technology Inc.

Page 43

寄存器 5-3: CNF3——配置寄存器 3 (地址:28h)

R/W-0 R/W-0 U-0 U-0 U-0 R/W-0 R/W-0 R/W-0

SOF WAKFIL — — — PHSEG22 PHSEG21 PHSEG20

bit 7 bit 0

bit 7 SOF:起始帧信号位

如果 CANCTRL.CLKEN = 1:

1 = CLKOUT 引脚使能为 SOF 信号

0 = CLKOUT 引脚使能为时间输出功能

如果 CANCTRL.CLKEN = 0,该位为任意状态 .

bit 6 WAKFI L:唤醒滤波使能位

1 = 唤醒滤波器使能

0 = 唤醒滤波器禁止

bit 5-3 未用:读为 0

bit 2-0 PHSEG2:相位缓冲段 PS2 长度 <2:0>

(PHSEG2 + 1) x T

注: PS2 的最小有效值为 2 TQ

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

Q

MCP2515

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 43 页

Page 44

MCP2515

注:

DS21801D_CN 第 44 页 初稿 2005 Microchip Technology Inc.

Page 45

MCP2515

6.0 错误检测

CAN 协议提供了完备的错误检测机制,可以检测到以下

错误。

6.1 CRC 错误

发送器通过循环冗余校验(CRC)计算特殊校验位来确

定从帧起始到数据字段结束为止的位序列。 CRC 序列

在 CRC 字段发送。接收节点采用相同公式计算 CRC 序

列,并将计算结果与接收到的 CRC 序列相比较。如果

两者不匹配,即发生 CRC 错误,并产生错误帧。将重

新发送报文。

6.2 确认错误

在报文的确认字段,发送器检查确认间隙(已作为隐性

位发送)是否包含一个显性位。如果没有,表明没有任

何其他节点正确接收到此帧。这时便表明发生确认错

误,并产生错误帧,而将重新发送报文。

6.3 格式错误

如果节点在帧结尾、帧间空间、确认定界符或 CRC 定

界符等四个位段中的任一位段中检测到显性位,即发生

格式错误,并产生错误帧。将重新发送报文。

6.4 位错误

当发送器检测到的位电平与其发送的位电平极性相反

(即,发送了一个显性位而检测到的是一个隐性位,或

发送了一个隐性位而检测到的是一个显性位)时,便产

生位错误。

例外:

如果发送器发送了一个隐性位,却在仲裁字段和

确认间隙期间检测到一个显性位,由于正在进行正常的

仲裁,所以这种情况下不会产生位错误。

6.5 位填充错误

在帧起始和 CRC 定界符之间,如果节点检测到六个连

续且极性相同的位,说明违反了位填充规则。此时便发

生位填充错误,并产生错误帧。将重新发送报文。

6.6 错误状态

当某个节点检测到错误时,将以错误帧的形式通知所有

其他节点。尽可能早地中止出错报文的发送并重新发

送。而且,根据内部错误计数器的计数值,每个 CAN 节

点可设定为三种错误状态之一:

1. 主动错误。

2. 被动错误。

3. 总线关闭 (仅发送器)。

主动错误状态是通常的状态,处于该状态的节点可以不

受任何限制地发送报文和主动错误帧 (由显性位构

成)。

处于被动错误状态的节点可以发送报文和被动错误帧

(由隐性位构成)。

处于总线关闭状态的节点暂时不能参与总线通讯。这一

状态下,既无法发送报文,也无法接收报文。只有发送

器能够进入总线关闭状态。

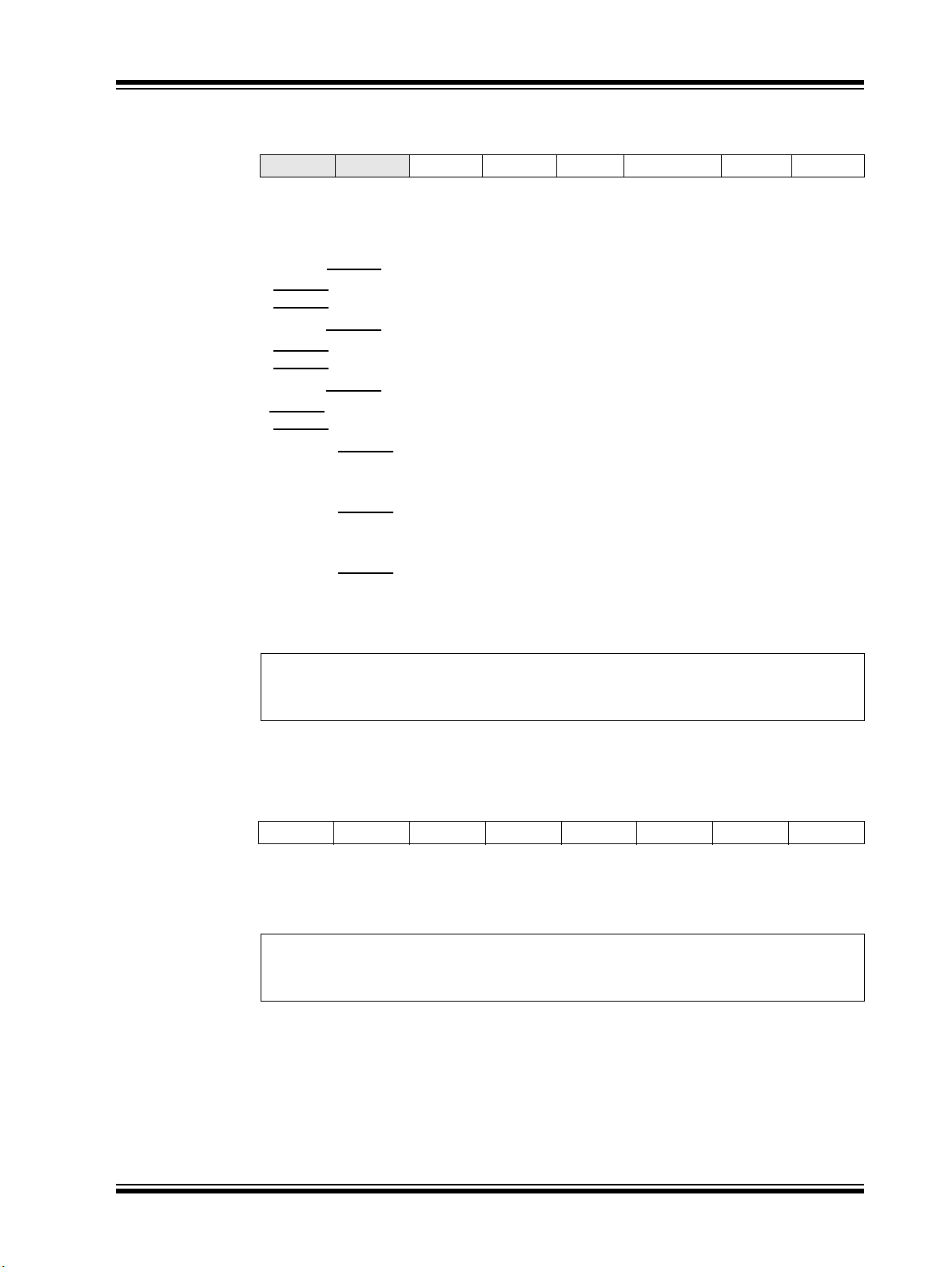

6.7 错误模式和错误计数器

MCP2515 包含两个错误计数器:接收错误计数器

(REC)(见寄存器 6-2)和发送错误计数器 (TEC)

(见寄存器 6-1)。 MCU 可以读取这两个计数器的值。

计数器根据 CAN 总线规范进行增减计数。

如果这两个错误计数器的值同时低于被动错误限定值

128, MCP2515 将处于主动错误状态。

当至少有一个错误计数器的值大于等于 128 时,器件将

处于被动错误状态。

如果 TEC 的值超过总线关闭限定值 255,器件将转为总

线关闭状态,直至接收到总线关闭恢复序列。总线关闭

恢复系列由重复 128 次的 11 个连续隐性位组成 (见

图 6-1)。

注: 如果转入总线关闭状态后,总线有长达128

x 11 位的时间为空闲状态,MCP2515 会在

无需MCU的干预下自动恢复至主动错误状

态。如果不希望自动恢复,应通过错误中

断服务程序来实现。

MCU 可通过 EFLG 寄存器 (见寄存器 6-3)读取

MCP2515 器件的当前错误状态。

此外,在至少有一个错误计数器的值大于等于错误警告

限定值 96 时,错误状态警告标志位(EFLG:EWARN)

将被置 1。当两个错误计数器都小于错误警告限定值

时, EWARN 将复位。

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 45 页

Page 46

MCP2515

图 6-1: 错误模式状态图

复位

REC < 127 或

TEC < 127

REC > 127 或

TEC > 127

被动错误

TEC > 255

主动错误

总线关闭

寄存器 6-1: TEC——发送错误计数器 (地址:1Ch)

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

TEC7 TEC6 TEC5 TEC4 TEC3 TEC2 TEC1 TEC0

bit 7 bit 0

bit 7-0 TEC:发送错误计数值 <7:0>

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

接收到重复 128 次的

11 个连续隐性位

寄存器 6-2: REC——接收错误计数器 (地址:1Dh)

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

REC7 REC6 REC5 REC4 REC3 REC2 REC1 REC0

bit 7 bit 0

bit 7-0 REC:接收错误计数值 <7:0>

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

DS21801D_CN 第 46 页 初稿 2005 Microchip Technology Inc.

Page 47

寄存器 6-3: EFLG——错误标志寄存器 (地址:2Dh)

R/W-0 R/W-0 R-0 R-0 R-0 R-0 R-0 R-0

RX1OVR RX0OVR TXBO TXEP RXEP TXWAR RXWAR EWARN

bit 7 bit 0

bit 7 RX1OVR:接收缓冲器 1 溢出标志位

- 当 RXB1 接收到有效报文且 CANINTF.RX1IF = 1 时置 1

- 必须由 MCU 复位

bit 6 RX0OVR:接收缓冲器 0 溢出标志位

- 当 RXB0 接收到有效报文且 CANINTF.RX0IF = 1 时置 1

- 必须由 MCU 复位

bit 5 TXBO:总线关闭错误标志位

- 当 TEC 达到 255 时,该位置 1

- 当成功接收到总线恢复序列时复位

bit 4 TXEP:发送被动错误标志位

- 当 TEC 大于等于 128 时,该位置 1

- 当 TEC 小于 128 时复位

bit 3 RXEP:接收被动错误标志位

- 当 REC 大于等于 128 时,该位置 1

- 当 TEC 小于 128 时复位

bit 2 TXWAR:发送错误警告标志位

- 当 TEC 大于等于 96 时,该位置 1

- 当 TEC 小于 96 时复位

bit 1 RXWAR:接收错误警告标志位

- 当 REC 大于等于 96 时,该位置 1

- 当 REC 小于 96 时复位

bit 0 EWARN:错误警告标志位

- 当 TEC 或 REC 大于等于 96 时(TXWAR 或 RXWAR = 1)时,该位置 1

- 当 TEC 和 REC 同时小于 96 时复位

MCP2515

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 47 页

Page 48

MCP2515

注:

DS21801D_CN 第 48 页 初稿 2005 Microchip Technology Inc.

Page 49

MCP2515

7.0 中断

MCP2515 有八个中断源。CANINTE 寄存器包含了使能

各中断源的中断使能位。 CANINTF 寄存器包含了各中

断源的中断标志位。当发生中断时,INT 引脚将被

MCP2515 拉为低电平,并保持低电平状态直至 MCU 清

除中断。中断只有在引起相应中断的条件消失后,才会

被清除。

建议在对 CANINTF 寄存器中的标志位进行复位操作

时,采用位修改命令而不要使用一般的写操作。这是为

了避免在写命令执行过程中无意间修改了标志位,进而

导致中断丢失。

应该注意的是,CANINTF 中的中断标志位是可读写位,

因此在相关 CANINTE 中断使能位置 1 的前提下,对上

述任一位置 1 均可使 MCU 产生中断请求。

7.1 中断代码位

如寄存器 10-2 所示,CANSTAT.ICOD(中断代码)位

的编码反映等待处理的中断源。如果同时发生多个中

NT 引脚将保持低电平状态直至 MCU 复位所有中

断, I

断。 CANSTAT.ICOD 位将反映当前等待处理的优先级

最高的中断代码。中断源之间存在内部优先级, ICOD

编码值越低,其中断优先级越高。一旦优先级最高的中

断条件被清除, ICOD 位(见表 7-1)将反映等待处理

的次高优先级中断 (如果存在)的代码。 ICOD 位仅反

映那些其 CANINTE 中断使能位置 1 的中断源。

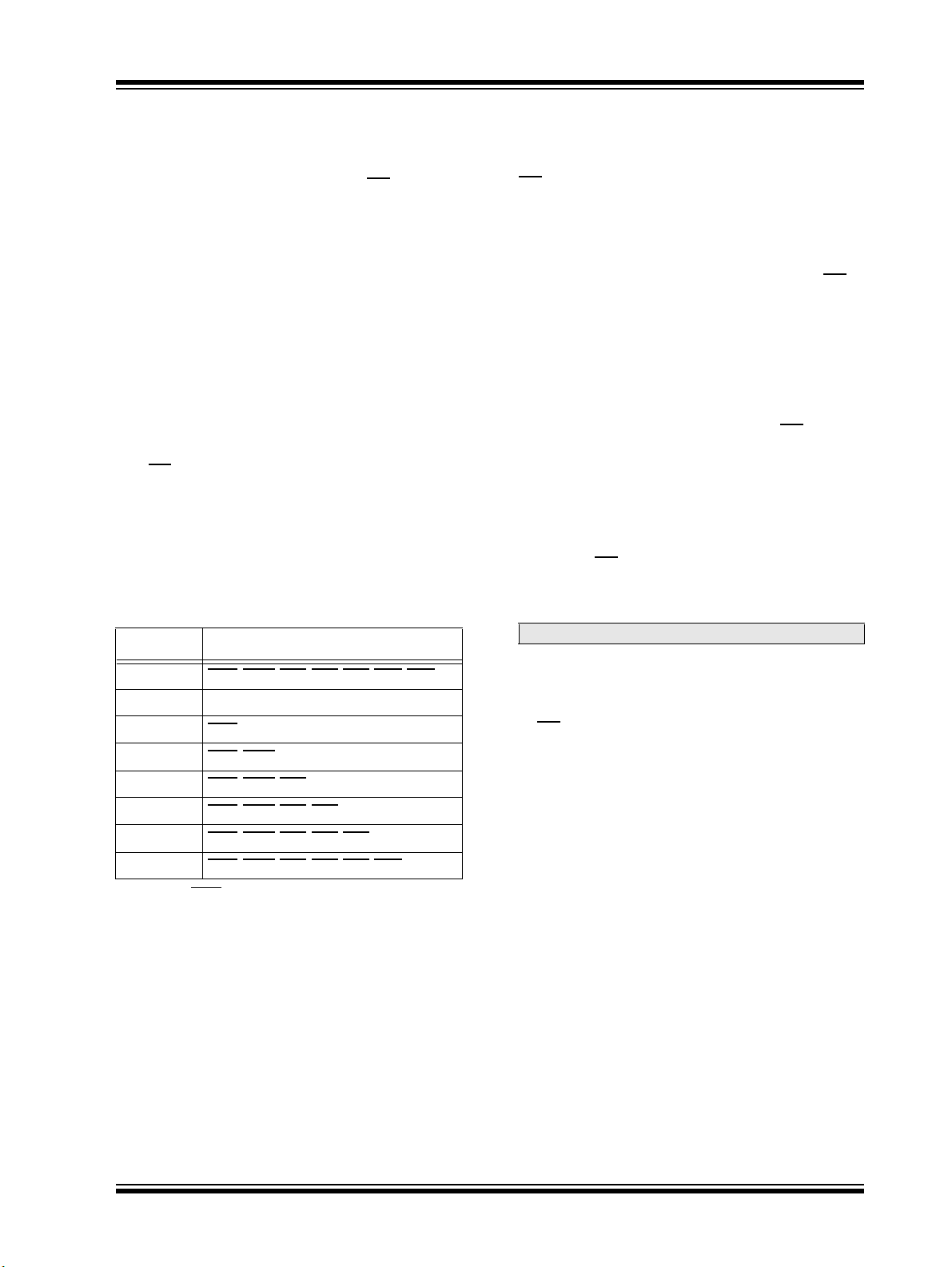

表 7-1: ICOD<2:0> 解码

ICOD<2:0> 布尔表达式

000

001

010

011

100

101

110

111

ERR•WAK•TX0•TX1•TX2•RX0•RX1

ERR

ERR•WAK

ERR•WAK•TX0

ERR•WAK•TX0•TX1

ERR•WAK•TX0•TX1•TX2

ERR•WAK•TX0•TX1•TX2•RX0

ERR•WAK•TX0•TX1•TX2•RX0•RX1

7.2 发送中断

在发送中断使能 (CANINTE.TXnIE = 1)时,如果相关

发送缓冲器为空并处于新报文装载就绪状态,器件会在

NT引脚产生中断。CANINTF.TXnIF位将被置1来表示中

I

断源。通过将 TXnIF 位清零来清除中断。

7.3 接收中断

在接收中断使能 (CANINTE.RXnIE = 1)时,如果报

文被成功接收并载入相关接收缓冲器,器件会在 INT 引

脚产生中断。在接收到 EOF 字段后,会立即激活该中

断。 CANINTF.RXnIF 位将被置 1 来表示中断源。通过

将 RXnIF 位清零来清除中断。

7.4 报文错误中断

如果报文发送和接收过程中出现错误,报文错误标志位

(CANINTF.MERRF)将被置 1,此时若相应的

CANINTE.MERRE 位也被置 1,器件将在 INT

中断。该中断旨在与仅监听模式结合使用时来加快波特

率的确定。

引脚产生

7.5 总线活动唤醒中断

如果 MCP2515 处于休眠模式且总线活动唤醒中断被使

能(CANINTE.WAKIE = 1),当 CAN 总线上检测到有

活动时会在 INT 引脚上产生中断,将 CANINTF.WAKIF

位置 1。该中断会使 MCP2515 退出休眠模式。通过将

WAKIF 位清零来复位该中断。

注: MCP2515 唤醒后进入仅监听模式。 .

7.6 错误中断

当错误中断使能 (CANINTE.ERRIE = 1)时,如果发

生溢出或发送器/接收器的错误状态发生改变,器件将

NT 引脚产生中断。错误标志 (EFLG)寄存器将会

在 I

表明以下错误中断状况之一。

7.6.1 接收器溢出

当 MAB 组合好收到的有效报文 (该报文符合验收滤波

器的接收条件),而与该滤波器相关的接收缓冲器尚无

法装载新报文时,将发生溢出。相应的 EFLG.RXnOVR

位将被置 1,表明发生溢出。该位必须由 MCU 清零。

注: ERR 与 CANINTE、 ERRIE 有关。

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 49 页

Page 50

MCP2515

7.6.2 接收器警告

REC 达到 MCU 警告限定值 96。

7.6.3 发送器警告

TEC 达到 MCU 警告限定值 96。

7.6.4 接收器被动错误

REC 超出被动错误限定值 127,且器件进入被动错误状

态。

7.6.6 总线关闭

TEC 超出 255 且器件进入总线关闭状态。

7.7 中断确认

中断直接与 CANINTF 寄存器中的一个或多个状态标志

位相关。只要其中一个标志位置 1,所有中断就将保持

等待状态。一旦器件将中断标志位置 1,在中断条件消

除之后 MCU 才能将标志位复位。

7.6.5 发送器被动错误

TEC 超出被动错误限定值 127,且器件进入被动错误状

态。

寄存器 7-1: CANINTE——中断使能寄存器 (地址:2Bh)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

MERRE WAKIE ERRIE TX2IE TX1IE TX0IE RX1IE RX0IE

bit 7 bit 0

bit 7 MERRE:报文错误中断使能位

1 = 报文接收或发送期间发生错误时中断

0 = 禁止

bit 6 WAKIE:唤醒中断使能位

1 =CAN总线上有活动时中断

0 = 禁止

bit 5 ERRIE:错误中断使能位 (EFLG 寄存器中有多个中断源)

1 =EFLG错误条件变化时中断

0 = 禁止

bit 4 TX2IE:发送缓冲器 2 空中断使能位

1 = TXB2 为空时中断

0 = 禁止

bit 3 TX1IE:发送缓冲器 1 空中断使能位

1 = TXB1 为空时中断

0 = 禁止

bit 2 TX0IE:发送缓冲器 0 空中断使能位

1 = TXB0 为空时中断

0 = 禁止

bit 1 RX1IE:接收缓冲器 1 满中断使能位

1 = RXB1 装载报文时中断

0 = 禁止

bit 0 RX0IE:接收缓冲器 0 满中断使能位

1 = RXB0 装载报文时中断

0 = 禁止

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

DS21801D_CN 第 50 页 初稿 2005 Microchip Technology Inc.

Page 51

寄存器 7-2: CANINTF——中断标志寄存器 (地址:2Ch)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

MERRF WAKIF ERRIF TX2IF TX1IF TX0IF RX1IF RX0IF

bit 7 bit 0

bit 7 MERRF:报文错误中断标志位

1 = 有等待处理的中断 (必须由 MCU 清零才可使中断复位)

0 = 无等待处理的中断

bit 6 WAKIF :唤醒中断标志位

1 = 有等待处理的中断 (必须由 MCU 清零才可使中断复位)

0 = 无等待处理的中断

bit 5 ERRIF:错误中断标志位 (EFLG 寄存器中有多个中断源)

1 = 有等待处理的中断 (必须由 MCU 清零才可使中断复位)

0 = 无等待处理的中断

bit 4 TX2IF:发送缓冲器 2 空中断标志位

1 = 有等待处理的中断 (必须由 MCU 清零才可使中断复位)

0 = 无等待处理的中断

bit 3 TX1IF:发送缓冲器 1 空中断标志位

1 = 有等待处理的中断 (必须由 MCU 清零才可使中断复位)

0 = 无等待处理的中断

bit 2 TX0IF:发送缓冲器 0 空中断标志位

1 = 有等待处理的中断 (必须由 MCU 清零才可使中断复位)

0 = 无等待处理的中断

bit 1 RX1IF:接收缓冲器 1 满中断标志位

1 = 有等待处理的中断 (必须由 MCU 清零才可使中断复位)

0 = 无等待处理的中断

bit 0 RX0IF:接收缓冲器 0 满中断标志位

1 = 有等待处理的中断 (必须由 MCU 清零才可使中断复位)

0 = 无等待处理的中断

MCP2515

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 51 页

Page 52

MCP2515

注:

DS21801D_CN 第 52 页 初稿 2005 Microchip Technology Inc.

Page 53

MCP2515

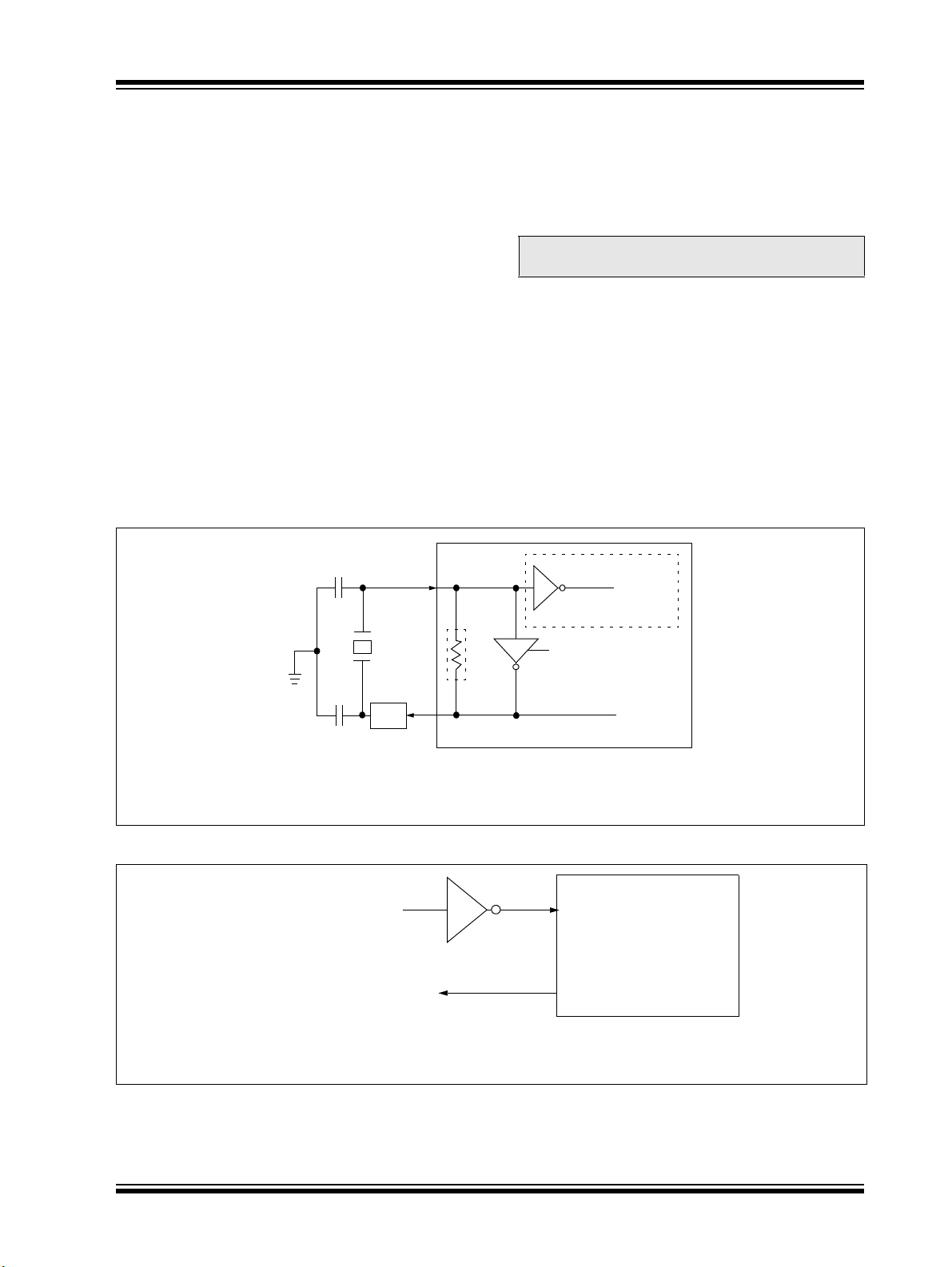

8.0 振荡器

MCP2515通过将晶体或陶瓷谐振器连在OSC1和OSC2

引脚上作为振荡器来工作。 MCP2515 的振荡器设计要

求选用并联切割晶体。若采用串联切割晶体,其产生的

时钟频率可能超出厂商规定值。图 8-1 显示了一个典型

的振荡电路。MCP2515 也可由连接在 OSC1 引脚上的

外部时钟源来驱动,如图 8-2 和图 8-3。

8.1 振荡器起振定时器

MCP2515 使用了一个振荡器起振定时器 (Oscillator

Startup Timer,OST),它使 MCP2515 处于复位状态以

保证振荡器在内部状态机开始运行之前已处于稳定状

态。上电或从休眠模式唤醒后的最初 128 OSC1 时钟周

期内, OST 将保持复位状态。应注意,只有在 OST 超

时后才能进行 SPI 协议操作。

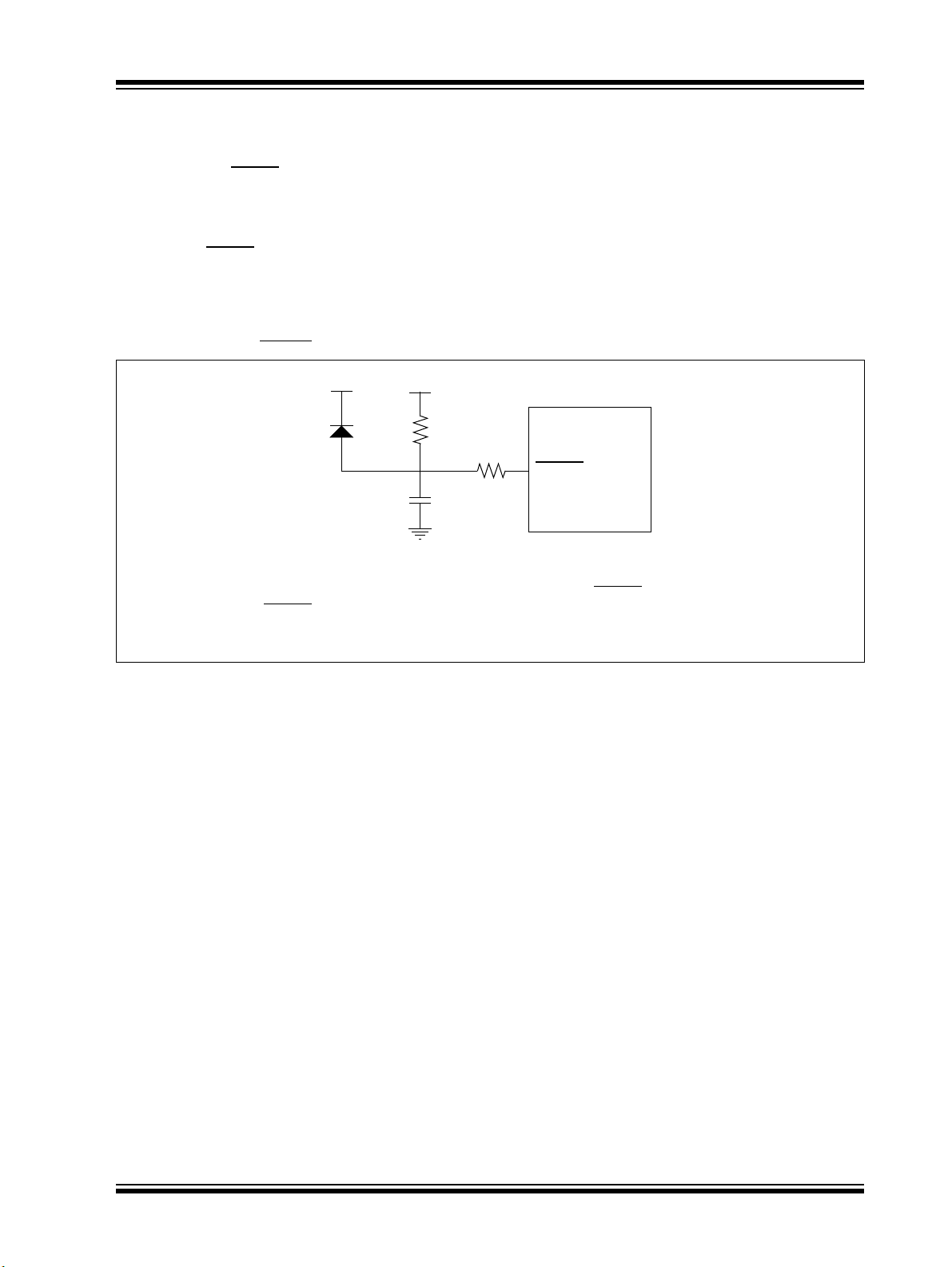

图 8-1:晶振/ 陶瓷谐振器工作原理图

OSC1

8.2 CLKOUT 引脚

CLKOUT 引脚供系统设计人员用作主系统时钟,或作为

系统中其他器件的时钟输入。 CLKOUT 有一个内部预

分频器,可将 F

CANCNTRL 寄存器来使能 CLKOUT 功能和选择预分频

比 (见寄存器 10-1)。

注: CLKOUT 的最大输出时钟频率为 25 MHz

(见表 13-5)。

系统复位时, CLKOUT 引脚被激活,其缺省设置为最

低频率的时钟输出 (8 分频),从而可作为 MCU 的时

钟信号。

当要求器件进入休眠模式时,MCP2515 会在 CLKOUT

引脚上额外驱动 16 个时钟周期,才进入休眠模式。处

于休眠模式的 CLKOUT 引脚空闲状态为低电平。如果

CLKOUT 功能被禁止 (CANCNTRL.CLKEN = 0),

CLKOUT 引脚处于高阻态。

CLKOUT 设计具备的功能可以保证无论 CLKOUT 引脚

功能处于使能、禁止或改变预分频比时, t

t

lCLKOUT

的时序设定都能得以保持。

除以 1、 2、 4 和 8。可通过设定

OSC

hCLKOUT

和

注 1: 采用 AT 条形切割晶体时,可如图接入一个串联电阻 (RS)。

2: 图中的反馈电阻 (R

图 8-2: 外部时钟源

来自外部系统的

时钟信号

注 1: 在此引脚接入一个接地电阻可减少系统噪音,但同时会加大系统电流。

2: 应注意占空比的限制 (见表 12-2)。

C

1

XTAL

(1)

RS

C

OSC2

2

(1)

开路

(2)

RF

F )典型值为 2 至 10 MΩ。

接到内部逻辑电路

休眠

OSC1

OSC2

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 53 页

Page 54

MCP2515

图 8-3: 外部串联谐振晶振电路

330 kΩ

74AS04

0.1 mF

XTAL

注 1: 应注意占空比的限制 (见表 12-2)。

(1)

330 kΩ

74AS04

74AS04

接到其他器件

MCP2510

OSC1

表 8-1: 陶瓷谐振器的电容选择 表 8-2: 晶振的电容选择

所用电容的典型值:

模式 频率 OSC1 OSC2

HS 8.0 MHz 27 pF 27 pF

16.0 MHz 22 pF 22 pF

上述电容值仅供设计参考:

这些电容均已采用下面列出的谐振器通过了对基本起

振和运行的测试,但这些电容值未经优化。

为产生可接受的振荡器工作频率,可能要求不同的电

容值。用户应在期望的应用环境 (VDD 和温度范围)

下对振荡器的性能进行测试。

请查看表 8-2 下面的注释,以获取更多信息。

所用的谐振器:

4.0 MHz

8.0 MHz

16.0 MHz

振荡

(1)(4)

类型

HS 4 MHz 27 pF 27 pF

上述电容值仅供设计参考:

这些电容均已采用下面列出的晶体通过了对基本起振

和运行的测试,但这些电容值未经优化。

为产生可接受的振荡器工作频率,可能要求不同的电

容值。用户应在期望的应用环境 (V

下对振荡器的性能进行测试。

请查看表下面的注释,以获取更多信息。

晶体

(2)

频率

8 MHz 22 pF 22 pF

20MHz 15pF 15pF

所用的晶体

20.0 MHz

经测试的电容典型值:

(3)

4.0 MHz

8.0 MHz

C1 C2

DD 和温度范围)

:

注 1: 电容值越大,振荡器就越稳定,但起振时

间会越长。

2: 由于每个谐振器 / 晶体都有其固有特性,

用户应向谐振器 / 晶体厂商咨询外围元件

的适当值。

3: 可能需要 R

造成过驱动。

4: 切记要在期望的应用环境 (V

围)下检验振荡器的性能。

DS21801D_CN 第 54 页 初稿 2005 Microchip Technology Inc.

S 来避免对低驱动规格的晶体

DD 和温度范

Page 55

9.0 复位

MCP2515 有两种复位方式:

1. 硬件复位——R

2. SPI 复位——通过 SPI 命令复位。

这两种复位方式效果一样。上电后要采用其中一种方式

复位器件,以确保逻辑和寄存器处于缺省状态。这一点

非常重要。在 RESET

进行硬件复位(见图 9-1)。照电气规范(tRL)指定的

那样,选择的 RC 值必须确保在 V

器件至少有 2µs处于复位状态。

图 9-1: RESET 引脚配置示例

ESET 引脚为低电平。

引脚上连一个 RC 电路,可自动

DD 达到工作电压后,

MCP2515

VDD

注 1: 在 VDD 掉电时,二极管 D 有助于电容快速放电。

2: R1 = 1 kΩ 至 10 kΩ 将限制从外部电容 C 流入 RESET

RESET

(Electrical Overstress, EOS)而击穿。

引脚因静电放电 (Electrostatic Discharge, ESD)或过度电性应力

(1)

D

VDD

R

C

R1

(2)

RESET

引脚的电流,以避免

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 55 页

Page 56

MCP2515

注:

DS21801D_CN 第 56 页 初稿 2005 Microchip Technology Inc.

Page 57

MCP2515

10.0 工作模式

MCP2515 有五种工作模式,分别为:

1. 配置模式。

2. 正常模式。

3. 休眠模式。

4. 仅监听模式。

5. 环回模式。

利用 CANCTRL. REQOP 位可进行工作模式的选择(见

寄存器 10-1)。

改变工作模式时,新的工作模式须等到所有当前报文发

送完毕之后才生效。必须通过读取 CANSTAT.OPMODE

位来验证新的工作模式 (见寄存器 10-2)。

10.1 配置模式

MCP2515 在正常运行之前必须进行初始化。只有在配

置模式下,才能对器件进行初始化。在上电或复位时,

器件会自动进入配置模式,或通过 CANTRL.REQOP 位

设置成 “100”也可使器件从任何模式进入配置模式。

当进入配置模式时,所有错误计数器都被清零。只有在

配置模式下,才能对以下寄存器进行修改:

• CNF1、 CNF2 和 CNF3

• TXRTSCTRL

• 验收过滤寄存器

• 验收屏蔽寄存器

10.2 休眠模式

MCP2515 具有内部休眠模式,使器件功耗最少。即使

MCP2515处于休眠模式,SPI 接口仍然保持正常的读操

作,以允许访问器件内的所有寄存器。

只需设置 CANCTRL 寄存器的模式请求位

(REQOP<2:0>)即可进入休眠模式。CAN-

STAT.OPMODE 位指示器件的工作模式。在向

MCP2515 发送休眠命令后必须读取这些位。MCP2515

仍然保持工作,但直至这些位指示器件已经进入休眠模

式,才真正处于休眠模式。

当处于内部休眠模式时,唤醒中断仍然工作(如果被使

能)。因此,可将 MCU 置于休眠模式,在检测到总线

上有活动时,就唤醒 MCP2515。

处于休眠模式时,MCP2515 内部振荡器停止工作。当总

线发生活动或 MCU 通过 SPI 接口将 CANINTF.WAKIF 位

置 1 来 “产生”唤醒尝试 (CANINTE.WAKIE 位也必须

置 1 以便产生唤醒中断)时,将唤醒 MCP2515。

当 MCP2515 处于休眠模式时, TXCAN 引脚保持隐性

状态。

10.2.1 唤醒功能

处于休眠模式下的器件将监视 RXCAN 引脚的总线活动

情况。如果 CANINTE.WAKIE 位置 1,将唤醒器件并产

生中断。由于休眠模式下内部振荡器关闭,因此唤醒后

需要一段时间让振荡器起振,并使器件能够接收报文。

振荡器起振定时器(OST)设定为 128 T

器件将忽略导致器件从休眠模式中唤醒的报文,以及器

件唤醒过程中的任何报文。器件在仅监听模式下唤醒。

因此 MCU 应先将器件设为正常工作模式,然后

MCP2515 才能进行总线通讯。

当器件处于内部休眠模式时,对器件进行编程可以在

RXCAN 输入引脚中加入低通滤波功能。该功能可以避

免因CAN 总线上的短时脉冲干扰而导致器件被误唤醒。

CNF3.WAKFIL 位可以使能或禁止该滤波器。

OSC 时钟周期。

10.3 仅监听模式

通过配置 RXBnCTRL.RXM<1:0> 位,仅监听模式使

MCP2515 可以接收包括错误报文在内的所有报文。这

种模式可用于总线监视应用或热插拔状况下的波特率检

测。

进行自动波特率检测时,网络中应至少有两个其他正在

互相通讯的节点。通过对不同的取值进行测试直至接收

到有效报文,以经验法来检测波特率。

仅监听模式是一种安静模式,即器件在此模式下不会发

送任何报文 (包括错误标志或确认信号)。可通过过滤

器和屏蔽器仅将特定的报文载入接收寄存器。如果屏蔽

器全部设为零,则可接收任何报文。在此模式下,错误

计数器将被复位并设置为无效。通过设定 CANCTRL 寄

存器中的模式请求位,可以激活仅监听模式。

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 57 页

Page 58

MCP2515

10.4 环回模式

环回模式允许器件内部的发送缓冲器和接收缓冲器之间

进行报文的自发自收,而无需通过 CAN 总线。此模式

可用于系统开发和测试。

环回模式下,确认位 ACK 无效,器件接收自己发送的

报文就象在接收来自其他节点的报文。环回模式是一种

安静模式,即器件在此模式下不会发送任何报文(包括

错误标志或确认信号)。该模式下 TXCAN 引脚处于隐

性状态。

可通过过滤器和屏蔽器仅将特定的报文载入接收寄存

器。如果屏蔽器全部设为零,则可接收任何报文。通过

设定 CANCTRL 寄存器中的模式请求位,可以激活环回

模式。

10.5 正常模式

该模式为 MCP2515 的标准工作模式。器件处于此模式

下,会主动监视总线上的所有报文,并产生确认位和错

误帧等。只有在正常模式下,MCP2515 才能在 CAN 总

线上进行报文的传输。

寄存器 10-1: CANCTRL——CAN 控制寄存器 (地址:XFh)

R/W-1 R/W-0 R/W-0 R/W-0 R/W-0 R/W-1 R/W-1 R/W-1

REQOP2 REQOP1 REQOP0 ABAT OSM CLKEN CLKPRE1 CLKPRE0

bit 7 bit 0

bit 7-5 REQOP<2:0>:请求工作模式的位

000 = 设定为正常工作模式

001 = 设定为休眠模式

010 = 设定为环回模式

011 = 设定为仅监听模式

100 = 设定为配置模式

REQOP 位不应设置为其他值,因为这些值都是无效的。

注: 上电时, REQOP = b’111’

bit 4 ABAT:中止所有当前报文发送的位

1 = 请求中止所有当前报文发送的缓冲器

0 = 终止对所有报文发送中止的请求

bit 3 OSM:单触发模式位

1 = 使能。报文仅尝试发送一次

0 = 禁止。如有需要,报文会重新发送。

bit 2 CLKEN:CLKOUT 引脚使能位

1 =CLKOUT引脚使能

0 =CLKOUT引脚禁止 (引脚处于高阻态)

bit 1-0 CLKPRE<1:0>:CLKOUT 引脚预分频比位

CLKOUT = 系统时钟频率 /1

00 =F

01 =FCLKOUT = 系统时钟频率 /2

CLKOUT = 系统时钟频率 /4

10 =F

11 =F

CLKOUT = 系统时钟频率 /8

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

DS21801D_CN 第 58 页 初稿 2005 Microchip Technology Inc.

Page 59

寄存器 10-2: CANSTAT——CAN 状态寄存器 (地址:XEh)

R-1 R-0 R-0 U-0 R-0 R-0 R-0 U-0

OPMOD2 OPMOD1 OPMOD0 — ICOD2 ICOD1 ICOD0 —

bit 7 bit 0

bit 7-5 OPMOD:工作模式位 <2:0>

000 = 器件处于正常工作模式

001 = 器件处于休眠模式

010 = 器件处于环回模式

011 = 器件处于仅监听模式

100 = 器件处于配置模式

bit 4 未用:读为 0

bit 3-1 ICOD:中断标志代码位 <2:0>

000 = 无中断

001 = 出错中断

010 = 唤醒中断

011 = TXB0 中断

100 = TXB1 中断

101 = TXB2 中断

110 = RXB0 中断

111 = RXB1 中断

bit 0 未用:读为 0

MCP2515

图注:

R = 可读位 W = 可写位 U = 未用位,读为 0

-n = 上电复位时的值 1 = 置 1 0 = 清零 x = 未知值

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 59 页

Page 60

MCP2515

注:

DS21801D_CN 第 60 页 初稿 2005 Microchip Technology Inc.

Page 61

MCP2515

11.0 寄存器映射表

定控制和状态寄存器允许使用SPI位修改命令对个别位

进行修改。可以对表 11-1 中阴影单元格中的寄存器应

表 11-1 是 MCP2515 的寄存器映射表。利用行 (低 4

位)列 (高 4 位)值可确定各寄存器的地址单元。寄

用位修改命令。表 11-2 对 MCP2515 的所有控制寄存

器作了汇总。

存器的地址排列优化了寄存器数据的顺序读写。一些特

表 11- 1: CAN 控制器的寄存器映射表

低地址位

0000 RXF0SIDH RXF3SIDH RXM0SIDH

0001 RXF0SIDL RXF3SIDL RXM0SIDL TXB0SIDH TXB1SIDH TXB2SIDH RXB0SIDH RXB1SIDH

0010 RXF0EID8 RXF3EID8 RXM0EID8 TXB0SIDL TXB1SIDL TXB2SIDL RXB0SIDL RXB1SIDL

0011 RXF0EID0 RXF3EID0 RXM0EID0 TXB0EID8 TXB1EID8 TXB2EID8 RXB0EID8 RXB1EID8

0100 RXF1SIDH RXF4SIDH RXM1SIDH TXB0EID0 TXB1EID0 TXB2EID0 RXB0EID0 RXB1EID0

0101 RXF1SIDL RXF4SIDL RXM1SIDL TXB0DLC TXB1DLC TXB2DLC RXB0DLC RXB1DLC

0110 RXF1EID8 RXF4EID8 RXM1EID8 TXB0D0 TXB1D0 TXB2D0 RXB0D0 RXB1D0

0111 RXF1EID0 RXF4EID0 RXM1EID0 TXB0D1 TXB1D1 TXB2D1 RXB0D1 RXB1D1

1000 RXF2SIDH RXF5SIDH

1001 RXF2SIDL RXF5SIDL

1010 RXF2EID8 RXF5EID8

1011 RXF2EID0 RXF5EID0

1100

1101

1110 CANSTAT CANSTAT CANSTAT CANSTAT CANSTAT CANSTAT CANSTAT CANSTAT

1111

注: 阴影单元格中的寄存器可以采用位修改命令对其中的个别位进行修改。

0000 xxxx 0001 xxxx 0010 xxxx 0011 xxxx 0100 xxxx 0101 xxxx 0110 xxxx 0111 xxxx

CNF3 TXB0D2 TXB1D2 TXB2D2 RXB0D2 RXB1D2

CNF2 TXB0D3 TXB1D3 TXB2D3 RXB0D3 RXB1D3

CNF1 TXB0D4 TXB1D4 TXB2D4 RXB0D4 RXB1D4

CANINTE TXB0D5 TXB1D5 TXB2D5 RXB0D5 RXB1D5

BFPCTRL TEC CANINTF TXB0D6 TXB1D6 TXB2D6 RXB0D6 RXB1D6

TXRTSCTRL REC EFLG TXB0D7 TXB1D7 TXB2D7 RXB0D7 RXB1D7

CANCTRL CANCTRL CANCTRL CANCTRL CANCTRL CANCTRL CANCTRL CANCTRL

高地址位

TXB0CTRL TXB1CTRL TXB2CTRL RXB0CTRL RXB1CTRL

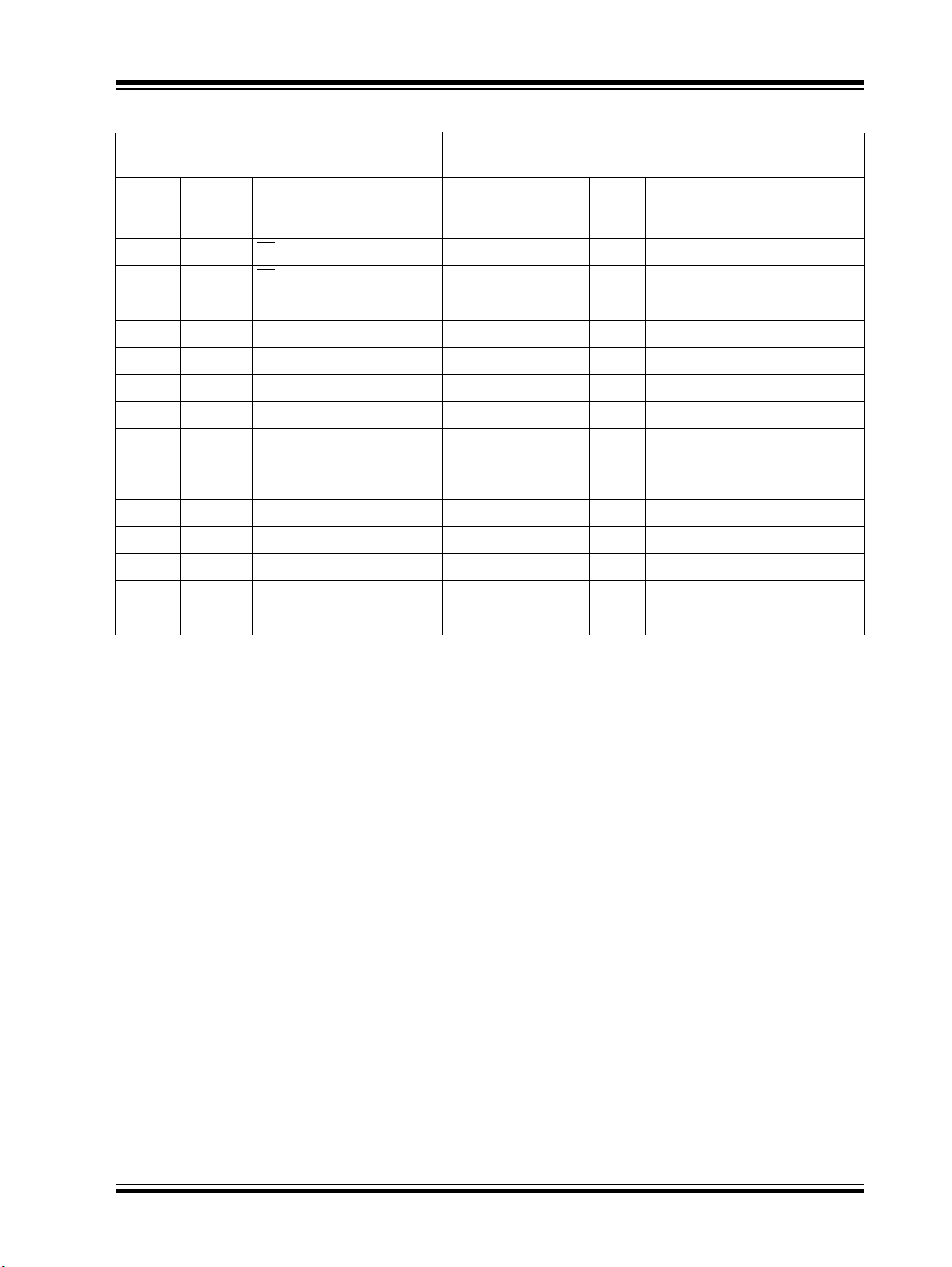

表 11- 2: 控制寄存器汇总

寄存器

名称

BFPCTRL 0C — — B1BFS B0BFS B1BFE B0BFE B1BFM B0BFM --00 0000

TXRTSCTRL 0D — — B2RTS B1RTS B0RTS B2RTSM B1RTSM B0RTSM --xx x000

CANSTAT xE OPMOD2 OPMOD1 OPMOD0 — ICOD2 ICOD1 ICOD0 — 100- 000-

CANCTRL xF REQOP2 REQOP1 REQOP0 ABAT OSM CLKEN CLKPRE1 CLKPRE0 1110 0111

TEC 1C 发送错误计数器 (TEC) 0000 0000

REC 1D 接收错误计数器 (REC) 0000 0000

CNF3 28 SOF WAKFIL — — — PHSEG22 PHSEG21 PHSEG20 00-- -000

CNF2 29 BTLMODE SAM PHSEG12 PHSEG11 PHSEG10 PRSEG2 PRSEG1 PRSEG0 0000 0000

CNF1 2A SJW1 SJW0 BRP5 BRP4 BRP3 BRP2 BRP1 BRP0 0000 0000

CANINTE 2B MERRE WAKIE ERRIE TX2IE TX1IE TX0IE RX1IE RX0IE 0000 0000

CANINTF 2C MERRF WAKIF ERRIF TX2IF TX1IF TX0IF RX1IF RX0IF 0000 0000

EFLG 2D RX1OVR RX0OVR TXBO TXEP RXEP TXWAR RXWAR EWARN 0000 0000

TXB0CTRL 30 — ABTF MLOA TXERR TXREQ — TXP1 TXP0 -000 0-00

TXB1CTRL 40 — ABTF MLOA TXERR TXREQ — TXP1 TXP0 -000 0-00

TXB2CTRL 50 — ABTF MLOA TXERR TXREQ — TXP1 TXP0 -000 0-00

RXB0CTRL 60 — RXM1 RXM0 — RXRTR BUKT BUKT FILHIT0 -00- 0000

RXB1CTRL 70 — RSM1 RXM0 — RXRTR FILHIT2 FILHIT1 FILHIT0 -00- 0000

地址

(Hex)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

POR/RST

值

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 61 页

Page 62

MCP2515

注:

DS21801D_CN 第 62 页 初稿 2005 Microchip Technology Inc.

Page 63

MCP2515

12.0 SPI 接口

12.1 概述

MCP2515 设计可与许多单片机的串行外设接口(SPI)

直接相连,支持 0,0 和 1,1 运行模式。外部数据和命令

通过 SI 引脚传送到器件中,且数据在 SCK 时钟信号的

上升沿传送进去。MCP2515 在 SCK 的下降沿通过 SO

引脚传送出去。在进行任何操作时, C

持为低电平。表 12-1 列出了所有操作的指令字节。有

关两种运行模式下详细的输入输出时序,请参见图 12-

10 和图 12-11。

注: CS 引脚被设置为低电平后, MCP2515 希

望收到的第一个字节是指令 / 命令字节。这

意味着CS

降为低电平以调用另外一个命令。

引脚必须先拉升为高电平然后再

12.2 复位指令

复位指令可以重新初始化 MCP2515 的内部寄存器,并

设置配置模式。该命令通过 SPI 接口发送到 MCP2515,

其功能与 R

复位指令为单字节指令。应先将 C

选中器件,随后发送命令字节,发送完毕之后再将 CS

引脚拉升为高电平。强烈建议将发送复位指令 (或将

RESET 引脚置为低电平)作为器件上电初始化过程中

的一部分。

ESET 引脚相同。

12.3 读指令

将 CS 引脚置为低电平来启动读指令。随后向 MCP2515

依次发送读指令和 8 位地址码 (A7 至 A0)。在接收到

读指令和地址码之后, MCP2515 会将指定地址寄存器

中的数据通过 SO 引脚移出。

每一数据字节移出后,器件内部的地址指针将自动加一

以指向下一个地址。因此,通过持续提供时钟脉冲,可

以对下一个连续地址寄存器进行读操作。通过该方法可

以顺序读取任意个连续地址寄存器中的数据。通过拉高

S 引脚电平可以结束读操作 (见图 12-2)。

C

12.4 读 RX 缓冲器指令

S 引脚都必须保

S 引脚置为低电平来

12.5 写指令

将 CS 引脚置为低电平来启动写操作。随后向 MCP2515

依次发送写指令、地址码和至少一个字节的数据。

只要 CS

连续地址寄存器进行顺序写操作。在 SCK 引脚的上升

沿,数据字节从 D0 位开始依次写入寄存器。如果 CS

引脚在字节的 8 位数据尚未装载完毕之前就拉升到高电

平,该字节的写操作将被中止,而命令中之前的字节已

经写入。有关详细的字节写操作时序,请参见图 12-4。

保持低电平,通过持续移入数据字节就可以对

12.6 装载 TX 缓冲器指令

装载 TX 缓冲器指令(图 12-5)取消了一般写命令所需

要的 8 位地址。该 8 位指令将地址指针设置为 6 个地址

之一,以便快速地将数据写入发送缓冲器,该地址指向

3 个发送缓冲器之一的 “ID”或 “数据”地址。

12.7 请求发送 (RTS)指令

使用RTS命令可以启动一个或多个发送缓冲器的报文发

送。

S 引脚置为低电平来选中 MCP2515。之后向其发送

将 C

RTS 命令字节。如图 12-6 所示,该命令的后 3 位显示了

哪些发送缓冲器被使能发送。

该命令将缓冲器对应的 TxBnCTRL.TXREQ 位置 1。用

一条 RTS 命令即可对这三位中的一位或全部三位置 1。

如果发送的 RTS 命令中 nnn = 000,将忽略该命令。

12.8 读状态指令

读状态指令允许单条指令访问常用的报文接收和发送状

态位。

S 引脚置为低电平来选中 MCP2515,然后向

将 C

MCP2515 发送读状态指令字节 (如图 12-8)。 命 令 字

节发送后, MCP2515 将返回一个包含状态信息的 8 位

数据。

在发送完最初 8 位数据之后,如果还有时钟信号发出,

只要 CS

提供的, MCP2515 将继续输出状态位。

引脚保持低电平并且时钟信号是通过 SCK 引脚

读 RX 缓冲器指令(图 12-3)可以快速寻址要读取的接

收缓冲器。该指令使 SPI 开销减少了一个字节(地址字

节)。读 RX 缓冲器指令实际上有四个可能值用于确定

地址指针的位置。一旦发送完命令字节后,控制器把与

读指令相同的地址中的数据移出(即,可能进行连续读

操作)。在命令结束时如果拉高了 CS

相关接收标志位(CANINTF.RXnIF)清零,读 RX 缓冲

器指令进一步减少了 SPI 开销。

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 63 页

引脚,会自动将

Page 64

MCP2515

该命令中返回的每个状态位也可通过带相应寄存器地址

的标准读命令读取。

12.9 RX 状态指令

RX 状态指令(图 12-9)用于快速确定与报文和报文类

型 (标准帧、扩展帧或远程帧)相匹配的滤波器。命令

字节发送后,控制器会返回包含状态信息的 8 位数据。

在发送完最初 8 位数据之后,如果还有时钟信号发出,

只要 CS

将继续输出相同的状态位。

引脚保持低电平并且提供时钟信号,MCP2515

12.10 位修改指令

位修改指令可对特定状态和控制寄存器中单独的位进行

置 1 或清零。该命令并非对所有寄存器有效。如需确定

哪些寄存器允许进行位修改,请参见第 11.0 节“寄存

器映射表”。

注: 对不允许位修改的寄存器执行位修改指令

会将屏蔽字节强行设为 FFh。这将允许对

寄存器进行字节写入操作,而不是位修改

操作。

将 CS 引脚置为低电平来选择器件,之后向 MCP2515

发送位修改命令字节。命令字节发送后,依次发送寄存

器地址、屏蔽字节以及数据字节。

屏蔽字节确定允许修改寄存器中的哪一位。屏蔽字节中

的“1”表示允许对寄存器中的相应位进行修改;而

“0”则禁止修改。

数据字节确定寄存器位修改的最终结果。如果屏蔽字节

相应位置为“1”,数据字节中的“1”表示将寄存器对

应位设置为 1,而 “0”将对该位清零 (见图 12-7)。

图 12-1:位修改

屏蔽字节

数据字节

修改前的

寄存器内容

修改后的

寄存器内容

001 11100

XX1 100XX

010 11000

011 10000

表 12-1: SPI 指令集

指令名称 指令格式 说明

复位 1100 0000 将内部寄存器复位为缺省状态,并将器件设定为配置模式。

读 0000 0011 从指定地址起始的寄存器读取数据。

读 RX 缓冲器 1001 0nm0 读取接收缓冲器时,在 “n,m”所指示的四个地址中的一个放置地

址指针可以减轻一般读命令的开销。注:在拉升 CS

后,相关的 RX 标志位 (CANINTF.RXnIF)将被清零。

写 0000 0010 将数据写入指定地址起始的寄存器。

装载 TX 缓冲器 0100 0abc 装载发送缓冲器时,在 “a,b,c”所指示的六个地址中的一个放置

地址指针可以减轻一般写命令的开销。

RTS

(请求发送报文)

读状态 1010 0000 快速查询命令,可读取有关发送和接收功能的一些状态位。

RX 状态 1011 0000 快速查询命令,确定匹配的滤波器和接收报文的类型 (标准帧、扩

位修改 0000 0101 允许用户将特殊寄存器中的单独位置 1 或清零。注:该命令并非适

1000 0nnn 指示控制器开始发送任一发送缓冲器中的报文发送序列。

1000 0nnn

TXB2 请求发送

TXB1 请求发送

展帧和 / 或远程帧)。

用于所有的寄存器。对不允许位修改操作的寄存器执行该命令会将

屏蔽字节强行设为 FFh。请参见第 11 .0 节 “寄存器映射表”中的

寄存器映射表,以了解适用的寄存器。

TXBO 请求发送

引脚为高电平

DS21801D_CN 第 64 页 初稿 2005 Microchip Technology Inc.

Page 65

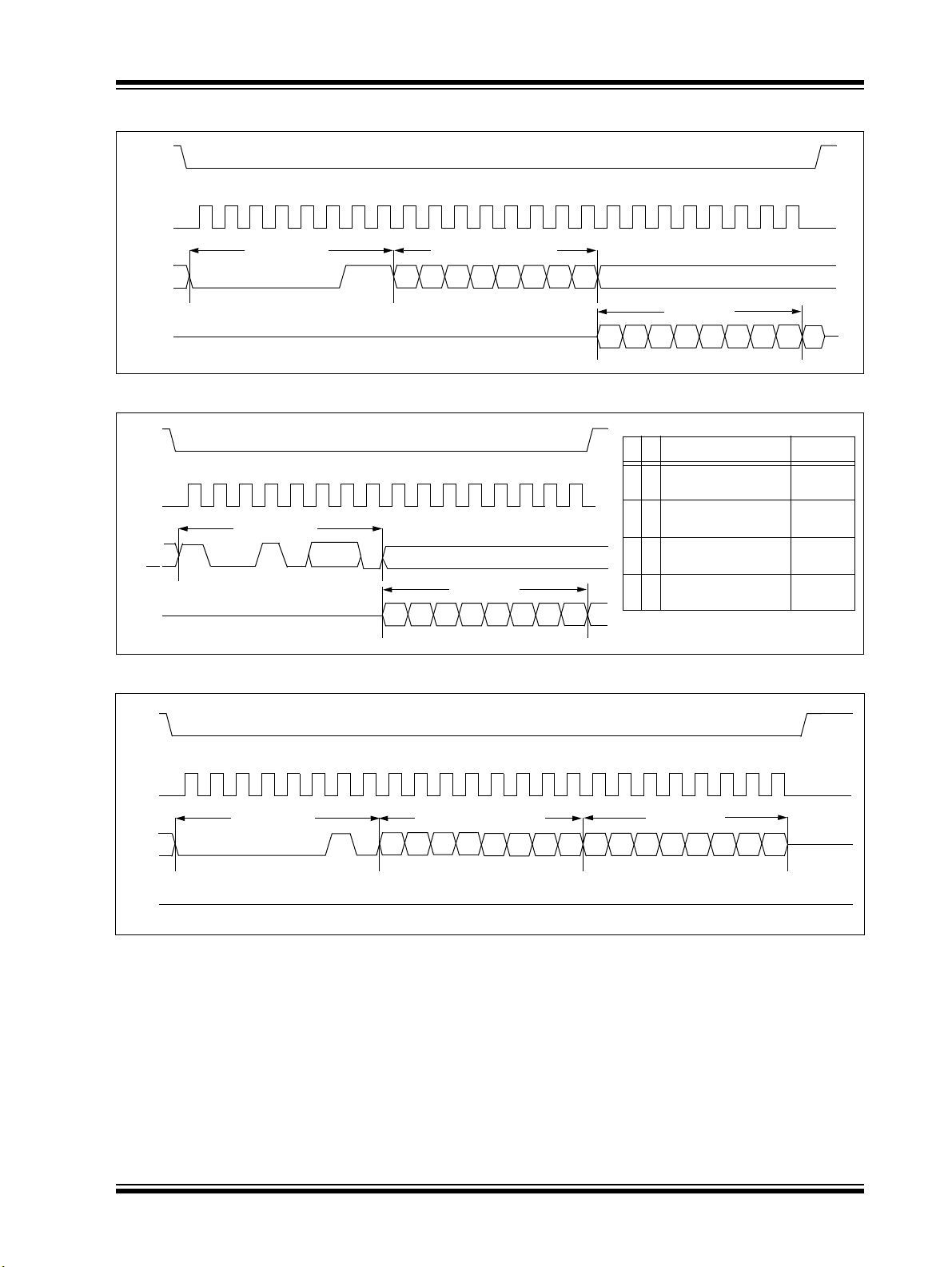

图 12-2:读指令

CS

MCP2515

0 23456789101112131415161718192021221

SCK

指令 地址字节

SI

SO

01000001

高阻态

图 12-3:读RX 缓冲器指令

CS

0 234567891011121314151

SCK

指令

mn

0

SO

SI

高阻态

01001

A7 6 5 4

任意状态

76543210

32

输出数据

1A0

23

任意状态

输出数据

76543210

nm 地址指针指向 地址

00接收缓冲器 0,开始

于 RXB0SIDH

01接收缓冲器 0,开始

于 RXB0D0

10接收缓冲器 1,开始

于 RXB1SIDH

11接收缓冲器 1,开始

于 RXB1D0

0x61

0x66

0x71

0x76

图 12-4: 字节写指令

CS

0 23456789101112131415161718192021221

SCK

指令

SI

SO

0000000

23

地址字节

1

A7 6 5 4

高阻态

32

1A0

76543210

数据字节

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 65 页

Page 66

MCP2515

图 12-5:装载TX 缓冲器

CS

0 234567891011121314151

SCK

指令

SI

SO

ac00010b

高阻态

图 12-6:请求发送(RTS)指令

CS

76543210

输入数据

abc 地址指针指向 地址

000TX 缓冲器 0,开始于

TXB0SIDH

001TX 缓冲器 0,开始于

TXB0D0

010TX 缓冲器 1,开始于

TXB1SIDH

011TX 缓冲器 1,开始于

TXB1D0

100TX 缓冲器 2,开始于

TXB2SIDH

101TX 缓冲器 2,开始于

TXB2D0

0x31

0x36

0x41

0x46

0x51

0x56

0 23456 71

SCK

SI

SO

01

图 12-7: 位修改指令

CS

0 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 221

SCK

指令

1100000

SI

SO

注: 该指令并非适用于所有寄存器。请参考寄

存器映射表以了解适用的寄存器。

0

指令

0

高阻态

地址字节

A7 6 5 4

32

T2 T000

屏蔽字节

76543210

1

A0

高阻态

T1

23 24 25 26 27 28 29 30 31

数据字节

76543210

DS21801D_CN 第 66 页 初稿 2005 Microchip Technology Inc.

Page 67

图 12-8: 读状态指令

CS

MCP2515

0 23456789101112131415161718192021221

SCK

指令

SI

高阻态

SO

00001010

图 12-9: RX 状态指令

CS

0 23456789101112131415161718192021221

SCK

任意状态

输出数据

76543210

23

重复输出数据

76543210

CANINTF.RX0IF

CANINTFL.RX1IF

TXB0CNTRL.TXREQ

CANINTF.TX0IF

TXB1CNTRL.TXREQ

CANINTF.TX1IF

TXB2CNTRL.TXREQ

CANINTF.TX2IF

23

指令

SI

高阻态

SO

76 接收到的报文

00没有 RX 报文

01RXB0 中的报文

10RXB1 中的报文

11两个缓冲器中的报文 *

CANINTF.RXnIF位映射为bit 7和6。

00011010

输出数据

76543210

43 接收到的报文类型

00标准数据帧

01标准远程帧

10扩展数据帧

11扩展远程帧

扩展 ID 位映射为 bit 4。 RTR 位

映射为 bit 3。

* 缓冲器 0 的优先级较高,因此 bit 4:0 反映 RXB0 状态。

任意状态

重复输出数据

76543210

210 滤波器匹配

000RXF0

001RXF1

010RXF2

011RXF3

100RXF4

101RXF5

110RXF0 (滚存到 RXB1)

111RXF1 (滚存到 RXB1)

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 67 页

Page 68

MCP2515

图 12-10: SPI 输入时序

CS

1

4

MSB 输入

5

SCK

模式 1,1

模式 0,0

SI

3

11

6

7

2

LSB 输入

10

SO

图 12-11: SPI 输出时序

CS

SCK

SO

SI

8

12

MSB 输出

9

高阻态

任意状态

13

2

模式 1,1

模式 0,0

14

LSB 输出

DS21801D_CN 第 68 页 初稿 2005 Microchip Technology Inc.

Page 69

MCP2515

13.0 电气特性

13.1 绝对最大额定值 †

VDD............................................................................................................................................................................. 7.0V

所有相对于 VSS 的输入输出 ............................................................................................................... -0.6V 至 VDD +1.0V

存储温度................................................................................................................................................. -65°C 至 +150°C

带电时的环境温度 .................................................................................................................................. -65°C 至 +125°C

引脚的焊接温度 (10 秒)..................................................................................................................................... +300°C

† 注意:如果器件运行条件超过上述各项绝对最大额定值,即可能对器件造成永久性损坏。上述参数仅是运行条件的极

大值。我们不建议器件运行在技术规范以外的条件下。器件长时间工作在绝对最大额定值下,其稳定性可能受到影响。

2005 Microchip Technology Inc. 初稿 DS21801D_CN 第 69 页

Page 70

MCP2515

表 13-1: 直流特性

直流特性

参数号 符号 特性 最小值 最大值 单位 条件

V

DD 电源电压 2.7 5.5 V

V

RET 寄存器保持电压 2.4 — V

高电平输入电压

V

IH RXCAN 2 VDD + 1 V