Datasheet dsPIC33FJ32MC302, dsPIC33FJ32MC3304, dsPIC33FJ64MCX02, dsPIC33FJ64MCX04, dsPIC33FJ128MCX02 Datasheet (MICROCHIP)

...Page 1

dsPIC33FJ32MC302/304、

深圳市粤原点科技有限公司(丽智电子:www.LZmcu.com)

(Microchip Authorized Design Partner)指定授权

总部地址:深圳市福田区福虹路世贸广场C座1103室

Add:Room 1103,Block C,World Trade Plaza,

Fuhong Road,Futian District Shen Zhen City

电话(tel) :86-755-83666320,83685176,83666321,83666325

传真(fax) :86-755-83666329,83681854

Web: Http://www.origin-gd.com or Http://www.LZmcu.com

E-mail:01@LZmcu.com

联系人:马先生,王小姐

公司在线咨询:QQ:46885145

MSN:MSN:action_tech@hotmail.com

7x24小时在线产品咨询: 13509674380 13798484366

dsPIC33FJ64MCX02/X04 和

dsPIC33FJ128MCX02/X04

数据手册

高性能

16 位数字信号控制器

2008 Microchip Technology Inc. 超前信息 DS70291A_CN

Page 2

请注意以下有关 Microchip 器件代码保护功能的要点:

• Microchip 的产品均达到 Microchip 数据手册中所述的技术指标。

• Microchip 确信:在正常使用的情况下, Microchip 系列产品是当今市场上同类产品中最安全的产品之一。

• 目前,仍存在着恶意、甚至是非法破坏代码保护功能的行为。就我们所知,所有这些行为都不是以 Microchip 数据手册中规定的

操作规范来使用 Microchip 产品的。这样做的人极可能侵犯了知识产权。

• Microchip 愿与那些注重代码完整性的客户合作。

• Microchip 或任何其他半导体厂商均无法保证其代码的安全性。代码保护并不意味着我们保证产品是 “牢不可破”的。

代码保护功能处于持续发展中。 Microchip 承诺将不断改进产品的代码保护功能。任何试图破坏 Microchip 代码保护功能的行为均可视

为违反了 《数字器件千年版权法案 (Digital Millennium Copyright Act)》。如果这种行为导致他人在未经授权的情况下,能访问您的

软件或其他受版权保护的成果,您有权依据该法案提起诉讼,从而制止这种行为。

提供本文档的中文版本仅为了便于理解。请勿忽视文档中包含

的英文部分,因为其中提供了有关 Microchip 产品性能和使用

情况的有用信息。Microchip Technology Inc. 及其分公司和相

关公司、各级主管与员工及事务代理机构对译文中可能存在的

任何差错不承担任何责任。建议参考 Microchip Technology

Inc. 的英文原版文档。

本出版物中所述的器件应用信息及其他类似内容仅为您提供便

利,它们可能由更新之信息所替代。确保应用符合技术规范,

是您自身应负的责任。Microchip 对这些信息不作任何明示或

暗示、书面或口头、法定或其他形式的声明或担保,包括但不

限于针对其使用情况、质量、性能、适销性或特定用途的适用

性的声明或担保。 Microchip 对因这些信息及使用这些信息而

引起的后果不承担任何责任。如果将 Microchip 器件用于生命

维持和 / 或生命安全应用,一切风险由买方自负。买方同意在

由此引发任何一切伤害、索赔、诉讼或费用时,会维护和保障

Microchip 免于承担法律责任,并加以赔偿。在 Microchip 知识

产权保护下,不得暗中或以其他方式转让任何许可证。

商标

Microchip 的名称和徽标组合、 Microchip 徽标、 Accuron、

dsPIC、 K

EELOQ、 KEELOQ 徽标、 MPLAB、 PIC、

PICmicro、 PICSTART、 PRO MATE、 rfPIC 和 SmartShunt

均为 Microchip Technology Inc. 在美国和其他国家或地区的

注册商标。

FilterLab、 Linear Active Thermistor、 MXDEV、 MXLAB、

SEEVAL、SmartSensor 和 The Embedded Control Solutions

Company 均为 Microchip Technology Inc.在美国的注册商

标。

Analog-for-the-Digital Age、 Application Maestro、

CodeGuard、 dsPICDEM、 dsPICDEM.net、 dsPICworks、

dsSPEAK、 ECAN、 ECONOMONITOR、 FanSense、

In-Circuit Serial Programming、 ICSP、 ICEPIC、 Mindi、

MiWi、MPASM、MPLAB Certified 徽标、MPLIB、MPLINK、

mTouch、 PICkit、 PICDEM、 PICDEM.net、 PICtail、 PIC

32

徽标、 PowerCal、 PowerInfo、 PowerMate、 PowerTool、

REAL ICE、rfLAB、Select Mode、 Total Endurance、UNI/O、

WiperLock和ZENA均为Microchip Technology Inc.在美国和其

他国家或地区的商标。

SQTP 是 Microchip Technology Inc. 在美国的服务标记。

在此提及的所有其他商标均为各持有公司所有。

© 2008, Microchip Technology Inc.版权所有。

Microchip

Gresham

印度的设计中心均通过了

MCU与dsPIC® DSC、KEELOQ

设、非易失性存储器和模拟产品方面的质量体系流程均符合

16949:2002

系也已通过了

位于美国亚利桑那州

的全球总部、设计和晶圆生产厂及位于美国加利福尼亚州和

。此外,

ISO 9001:2000

Chandler和Te mp e

ISO/TS-16949:2002

®

跳码器件、串行

Microchip

在开发系统的设计和生产方面的质量体

认证。

与位于俄勒冈州

认证。公司在

EEPROM

®

PIC

、单片机外

ISO/TS-

DS70291A_CN 第ii 页 超前信息 2008 Microchip Technology Inc.

Page 3

dsPIC33FJ32MC302/304、

dsPIC33FJ64MCX02/X04 和

dsPIC33FJ128MCX02/X04

高性能 16 位数字信号控制器

工作范围:

• 最高 40 MIPS 的工作速度 (3.0-3.6V 时):

- 工业级温度范围

(-40°C 至 +85°C)

- 扩展级温度范围

(-40°C 至 +125°C)

高性能 DSC CPU:

• 改进型哈佛架构

• C 编译器优化指令集

• 16 位宽数据总线

• 24 位宽指令

• 可寻址最大 4M 指令字的线性程序存储空间

• 可寻址最大 64 KB 的线性数据存储空间

• 83 条基本指令:多为单字 / 单周期指令

• 两个带舍入和饱和选项的 40 位累加器

• 灵活而强大的寻址模式:

- 间接寻址

- 模寻址

- 位反转寻址

• 软件堆栈

• 16 x 16 位小数 / 整数乘法运算

• 32/16 位和 16/16 位除法运算

• 单周期乘 - 累加运算:

-DSP运算的累加器回写操作

- 双数据取操作

• 可将最多 40 位的数据左移或右移最多 16 位

直接存储器访问 (Direct Memory

Access, DMA):

• 8 通道硬件 DMA

• 最大 2 KB 的双端口 DMA 缓冲区 (DMA RAM)

用于存储通过 DMA 传输的数据:

- 允许 CPU 执行代码时在 RAM 和外设之间传

输数据 (不占用周期)

• 大部分外设都支持 DMA

定时器 / 捕捉 / 比较 /PWM:

• 定时器 / 计数器,最多 5 个 16 位定时器

- 可以配对作为最多 2 个 32 位定时器使用

-1个定时器依靠外部 32.768 kHz 振荡器作为

实时时钟运行

- 可编程预分频器

• 输入捕捉 (最多 4 路通道):

- 上升沿捕捉、下降沿捕捉或上升 / 下降沿捕捉

-16位捕捉输入功能

- 每路捕捉通道都带有 4 字深度的 FIFO 缓冲区

• 输出比较 (最多 4 路通道):

-1个或 2 个 16 位比较模式

-16位无毛刺 PWM 模式

• 硬件实时时钟 / 日历 (Real-Time Clock/

Calendar, RTCC):

- 提供时钟、日历和闹钟功能

中断控制器:

• 中断响应延时为 5 个周期

• 118 个中断向量

• 最多 53 个中断源

• 最多 3 个外部中断

• 7 个可编程优先级

• 5 个处理器异常

数字 I/O:

• 外设引脚选择功能

• 最多 35 个可编程数字 I/O 引脚

• 最多 21 个引脚上具有唤醒 / 电平变化中断功能

• 输出引脚可驱动 3.0V 至 3.6V 的电压

• 漏极开路配置、最高 5V 的输出

• 所有数字输入引脚可承受 5V 的电压

• 所有 I/O 引脚的最大拉 / 灌电流为 4 mA

片上闪存和 SRAM:

• 闪存程序存储器 (最大 128 KB)

• 数据 SRAM (最大 16 KB)

• 闪存程序存储器的引导、安全和通用安全性

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第1 页

Page 4

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

系统管理:

• 灵活的时钟选择:

- 外部振荡器、晶振、谐振器和内部 RC 振荡器

- 全集成锁相环 (Phase-Locked Loop, PLL)

- 极低抖动 PLL

• 上电延时定时器

• 振荡器起振定时器 / 稳定器

• 自带 RC 振荡器的看门狗定时器

• 故障保护时钟监视器

• 多个复位源

功耗管理:

• 片上 2.5V 稳压器

• 实时时钟源切换

• 可快速唤醒的空闲、休眠和打盹模式

模数转换器 (Analog-to-Digital

Converter, ADC):

• 10 位 1.1 Msps 或 12 位 500 ksps 转换:

-2路或 4 路输入同时采样 (10 位 ADC)

- 最多 9 路带自动扫描功能的输入通道

- 可手动启动转换或与 4 个触发源中的一个同

步

- 休眠模式下仍可进行转换

- 最大积分非线性误差为 ±2 LSb

- 最大微分非线性误差为 ±1 LSb

音频数模转换器 (Digital-to-Analog

Converter, DAC):

-16位双通道 DAC 模块

- 最大 100 ksps 采样速率

- 二阶数字Δ -Σ 调制器

比较器模块:

• 带可编程输入 / 输出配置的两个模拟比较器

电机控制外设:

• 6 通道 16 位电机控制 PWM

-3个占空比发生器

- 独立或互补模式

- 可编程死区和输出极性

- 边沿对齐或中心对齐

- 手动输出改写控制

-1路故障输入

-ADC转换触发

-16位分辨率时的 PWM 频率

(@ 40 MIPS):边沿对齐模式为 1220 Hz,

中心对齐模式为 610 Hz

-11位分辨率时的 PWM 频率

(@ 40 MIPS):边沿对齐模式为 39.1 kHz,

中心对齐模式为 19.55 kHz

• 2 通道 16 位电机控制 PWM

-1个占空比发生器

- 独立或互补模式

- 可编程死区和输出极性

- 边沿对齐或中心对齐

- 手动输出改写控制

-1路故障输入

-ADC转换触发

-16位分辨率时的 PWM 频率

(@ 40 MIPS):边沿对齐模式为 1220 Hz,

中心对齐模式为 610 Hz

-11位分辨率时的 PWM 频率

(@ 40 MIPS):边沿对齐模式为 39.1 kHz,

中心对齐模式为 19.55 kHz

• 双正交编码器接口模块:

-A相、 B 相和索引脉冲输入

-16位递增 / 递减位置计数器

- 计数方向状态

- 位置测量 (x2 和 x4)模式

- 输入端上的可编程数字噪声滤波器

- 备用 16 位定时器 / 计数器模式

- 位置计数器计满返回 / 下溢中断

CMOS 闪存技术:

• 低功耗高速闪存技术

• 全静态设计

• 3.3V (±10%)工作电压

• 工业级和扩展级温度

• 低功耗

DS70291A_CN 第2 页 超前信息 2008 Microchip Technology Inc.

Page 5

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

通信模块:

• 4 线 SPI (最多 2 个模块):

- 帧支持与简单编解码器的 I/O 接口

- 支持 8 位和 16 位数据

- 支持所有串行时钟格式和采样模式

2

• I

C™:

- 完全支持多主机从模式

-7位和 10 位寻址

- 总线冲突检测和仲裁

- 集成信号调理

- 从地址掩码

• UART (最多 2 个模块):

- 检测到地址位时产生中断

- 出现 UART 错误时产生中断

- 检测到启动位时将器件从休眠模式唤醒

-4字符深的发送和接收 FIFO 缓冲区

-LIN总线支持

- 硬件 IrDA

- 高速波特率模式

- 使用 CTS 和 RTS 的硬件流控制

• 增强型 CAN (ECAN™模块) 2.0B active:

- 最多 8 个发送缓冲区、最多 32 个接收缓冲区

-16个接收过滤器和 3 个屏蔽器

- 环回、监听和监听所有报文模式

- 用于诊断和总线监视的报文模式

- 接收到 CAN 报文时唤醒

- 远程发送请求的自动处理

- 使用 DMA 的 FIFO 模式

- 支持 DeviceNet™寻址模式

• 并行主从端口 (PMP/EPSP):

- 支持 8 位或 16 位数据

- 支持 16 根地址线

• 可编程循环冗余校验 (Cyclic Redundancy

Check, CRC)

- CRC 发生器多项式的可编程位长度 (最大

16 位长度)

- 用于数据输入的 8 级深 16 位或 16 级深 8 位

FIFO

®

编解码器

封装:

• 28 引脚 SPDIP/SOIC/QFN-S

• 44 引脚 TQFP/QFN

注: 关于每个器件的具体外设特性,请参见相

应的器件数据表。

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第3 页

Page 6

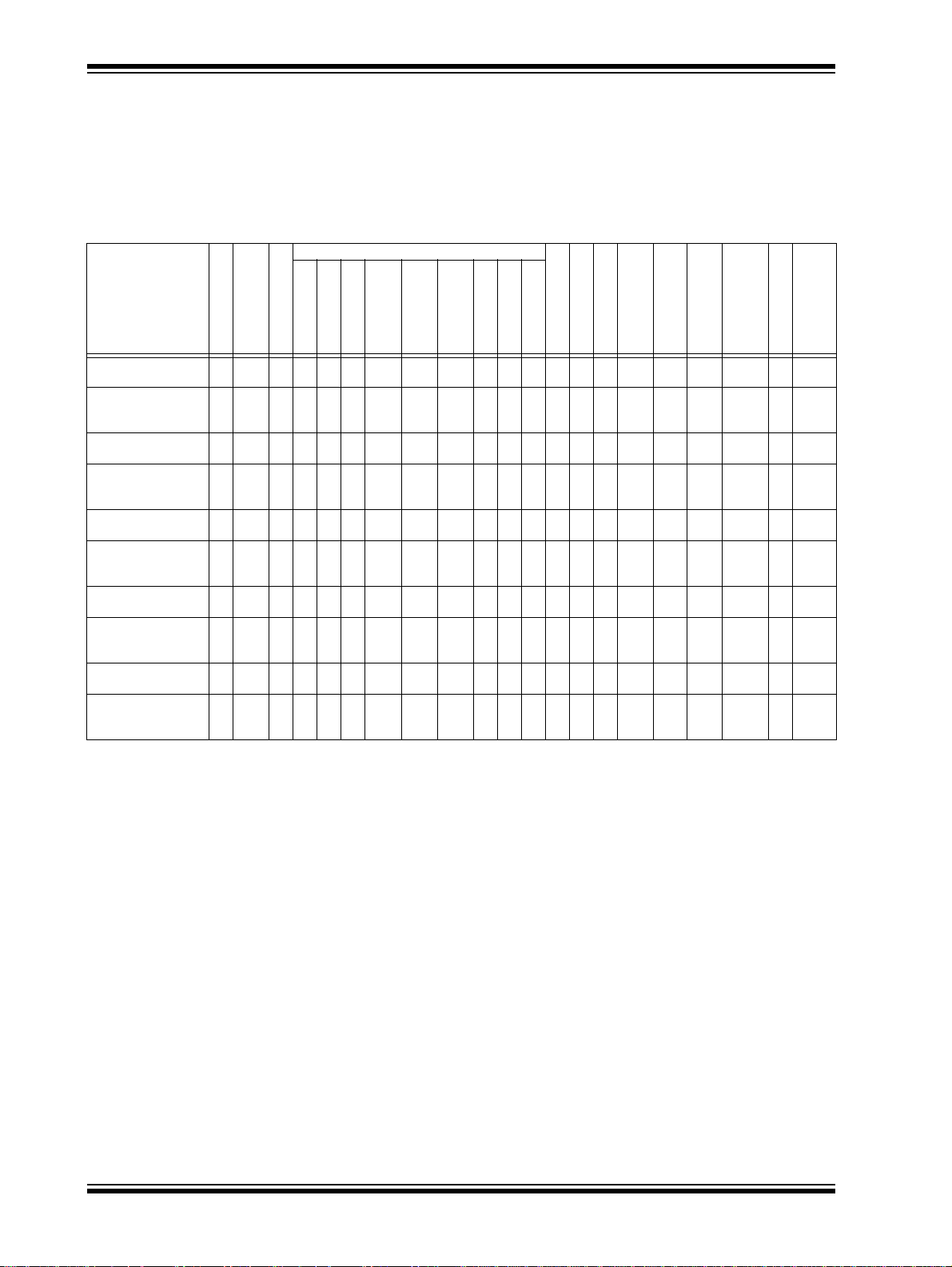

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

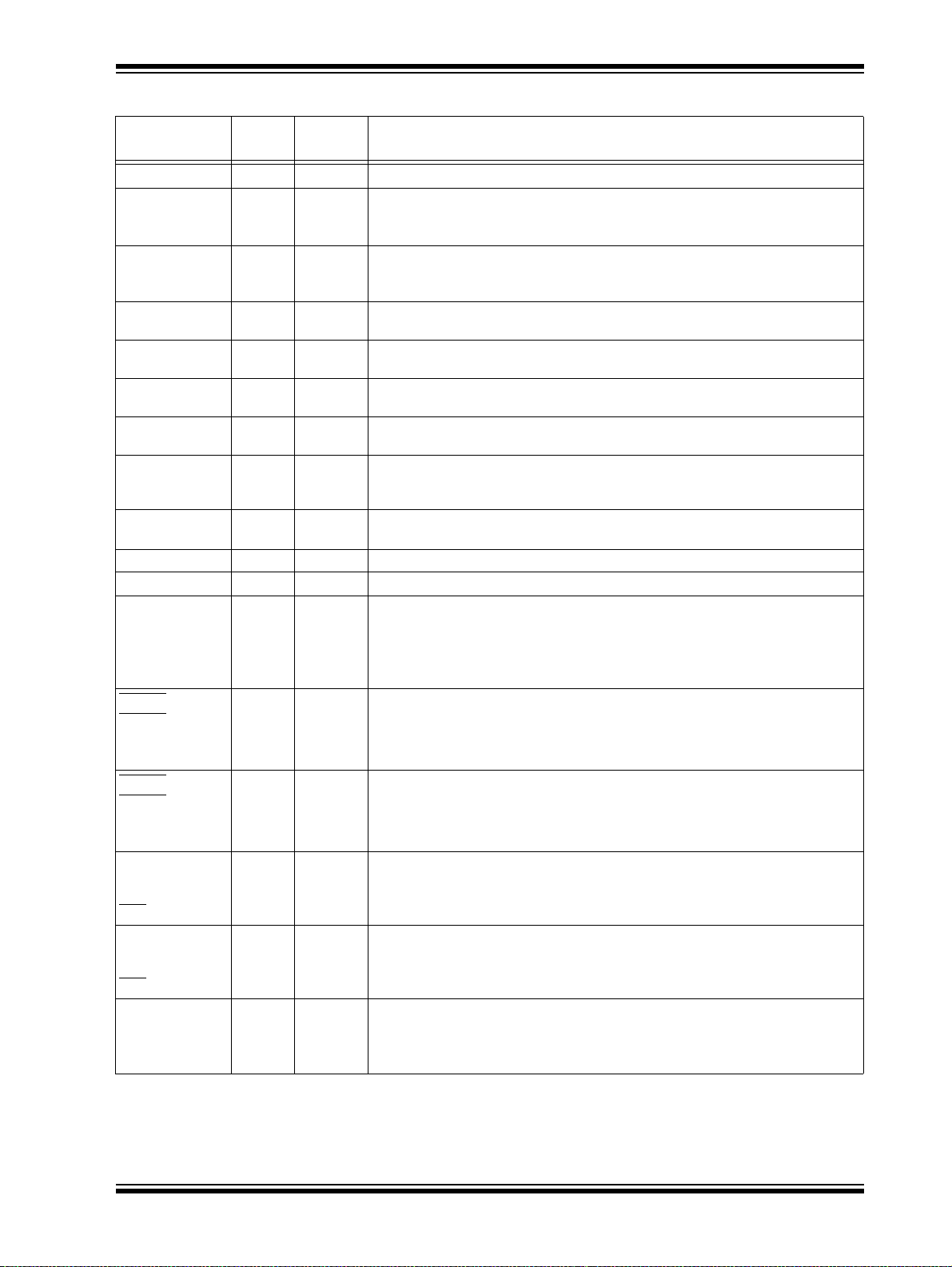

dsPIC33FJ32MC302/304、

dsPIC33FJ64MCX02/X04 和

dsPIC33FJ128MCX02/X04 产品系列

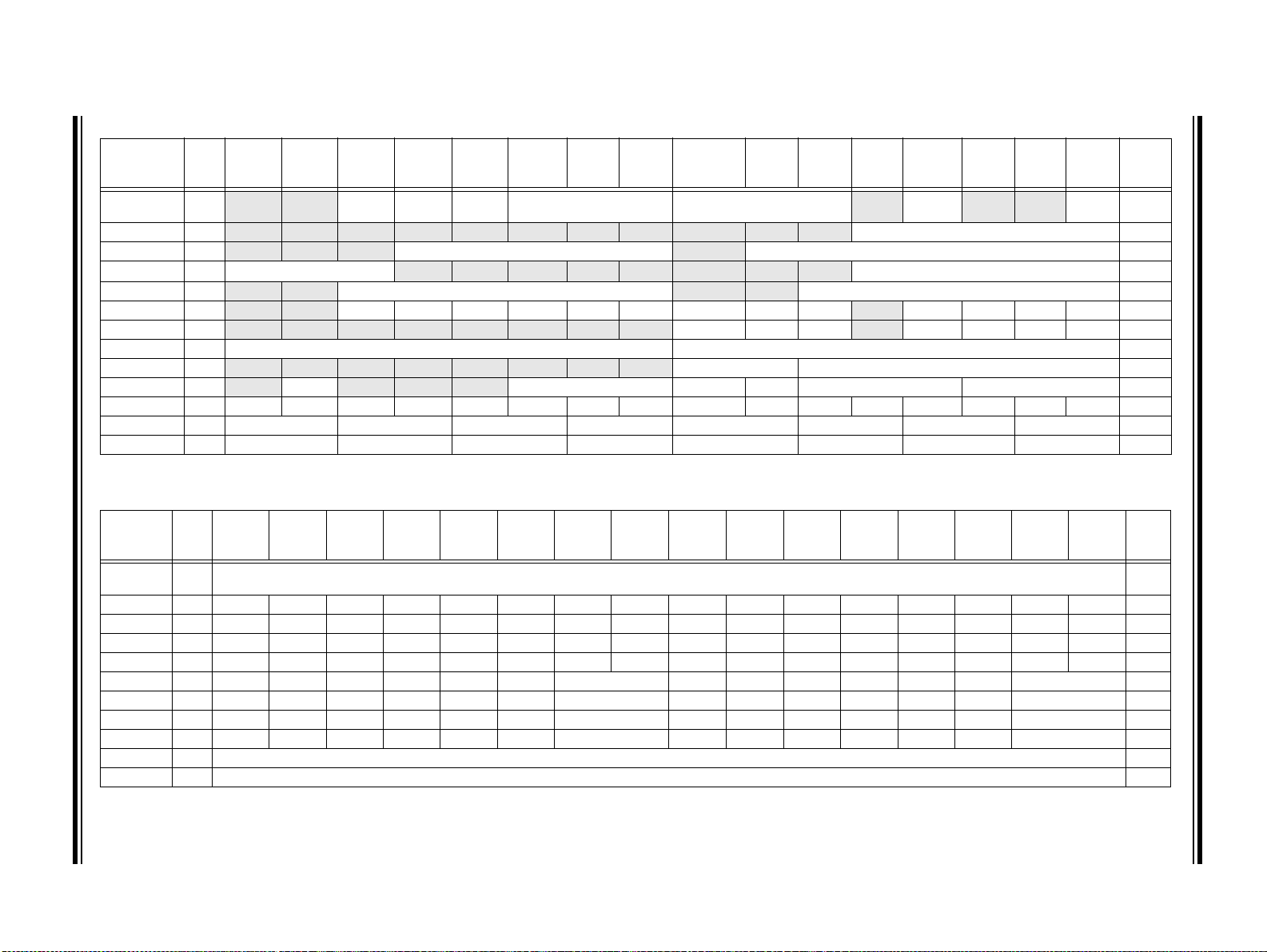

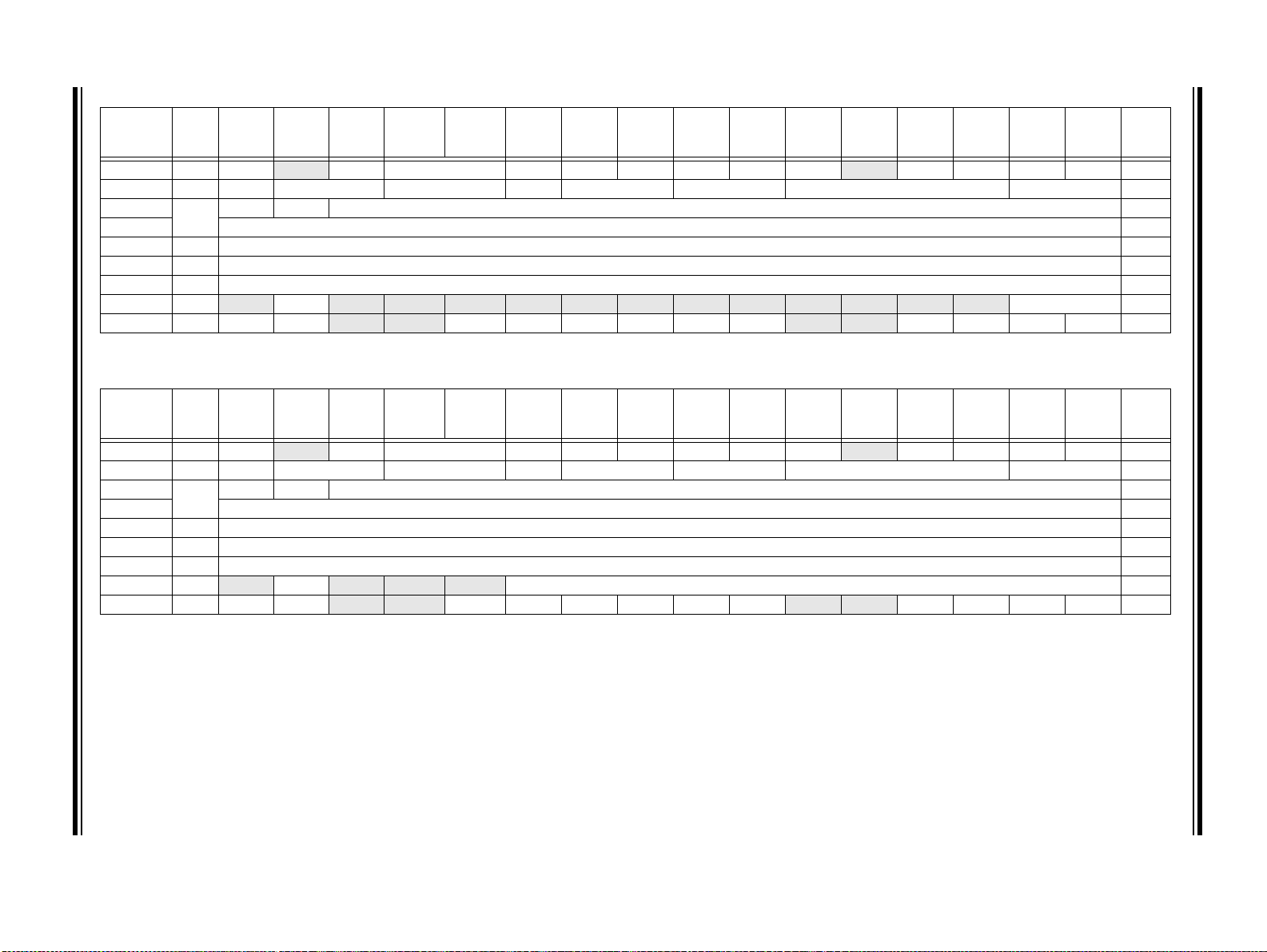

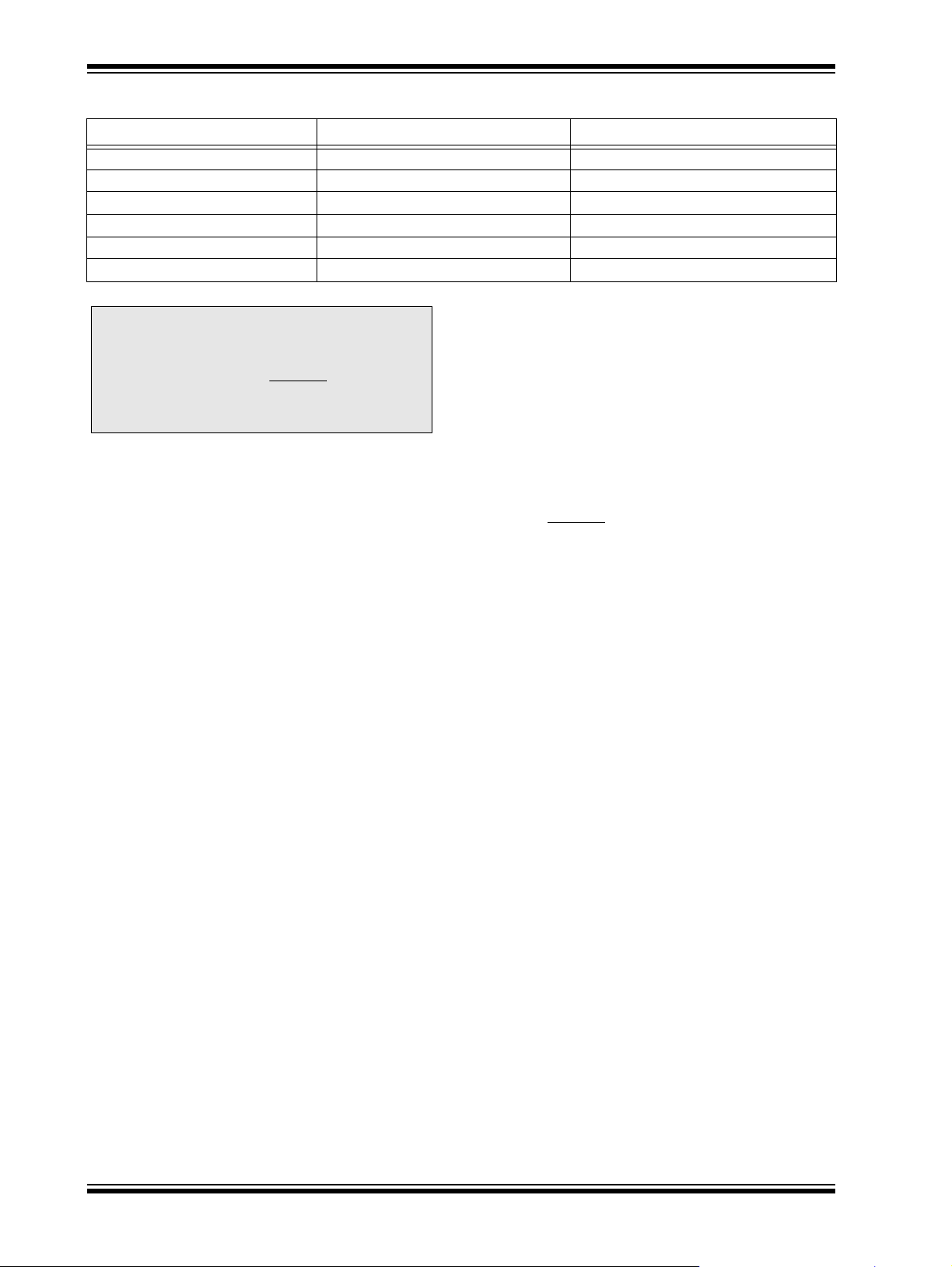

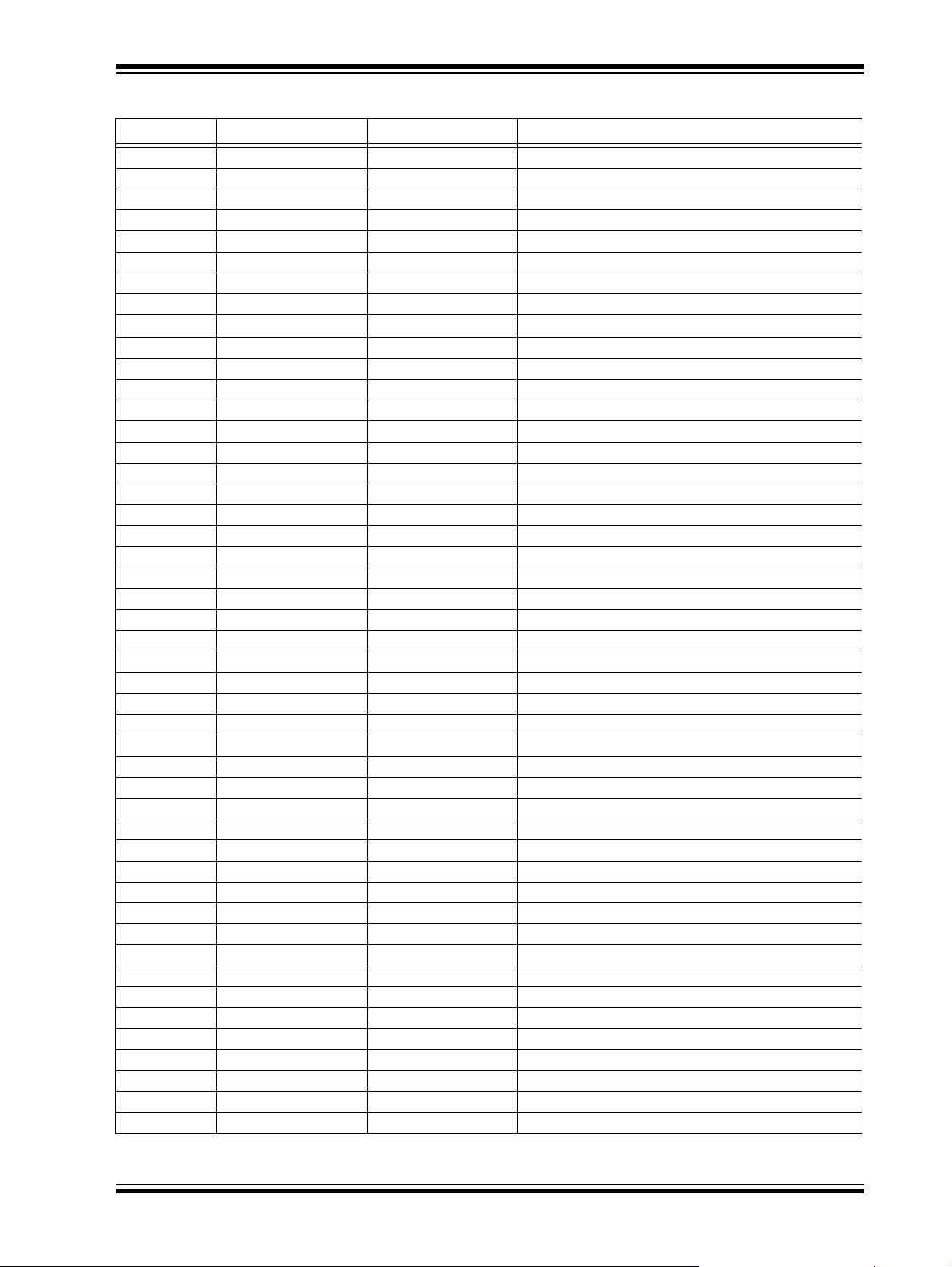

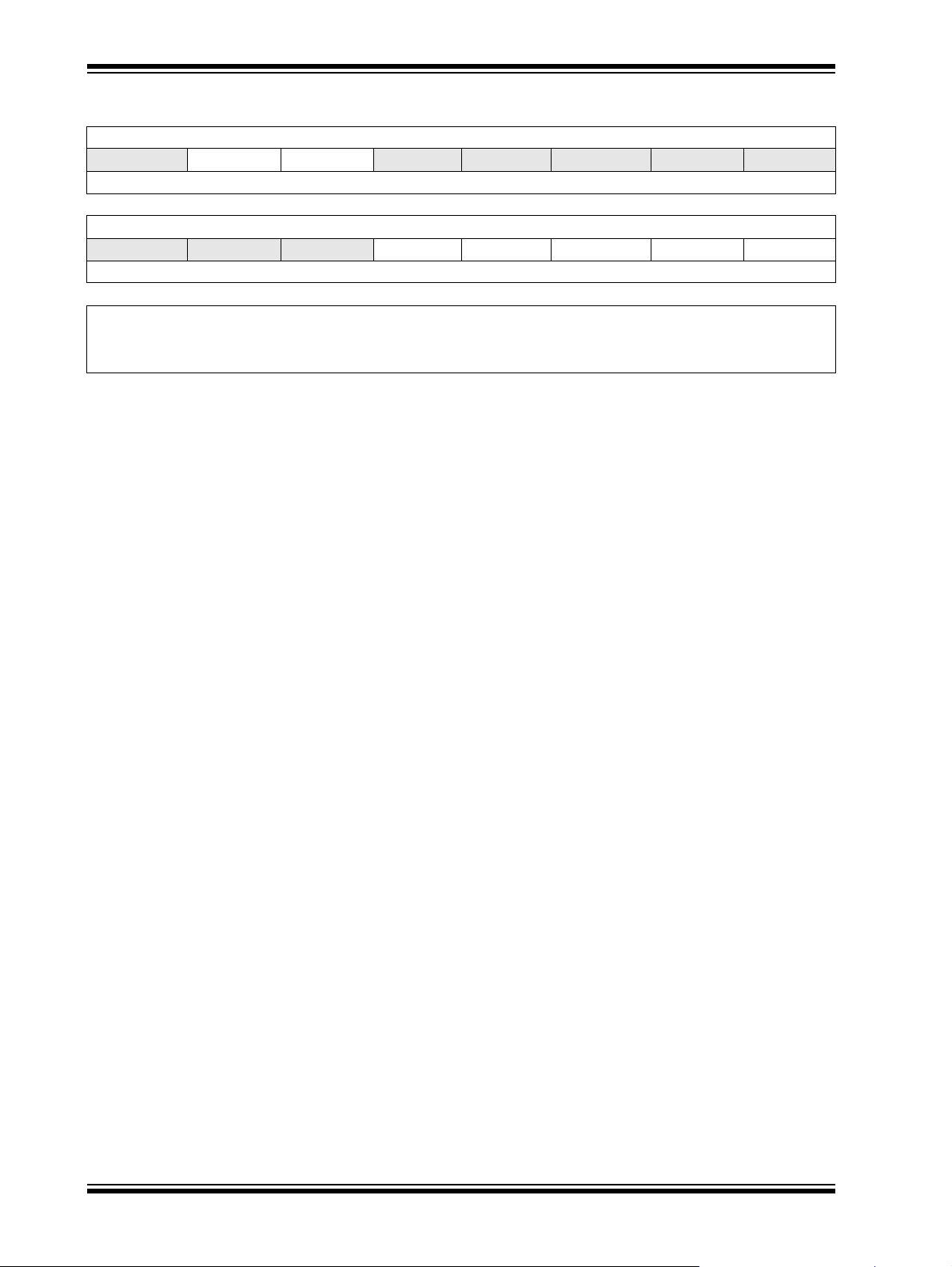

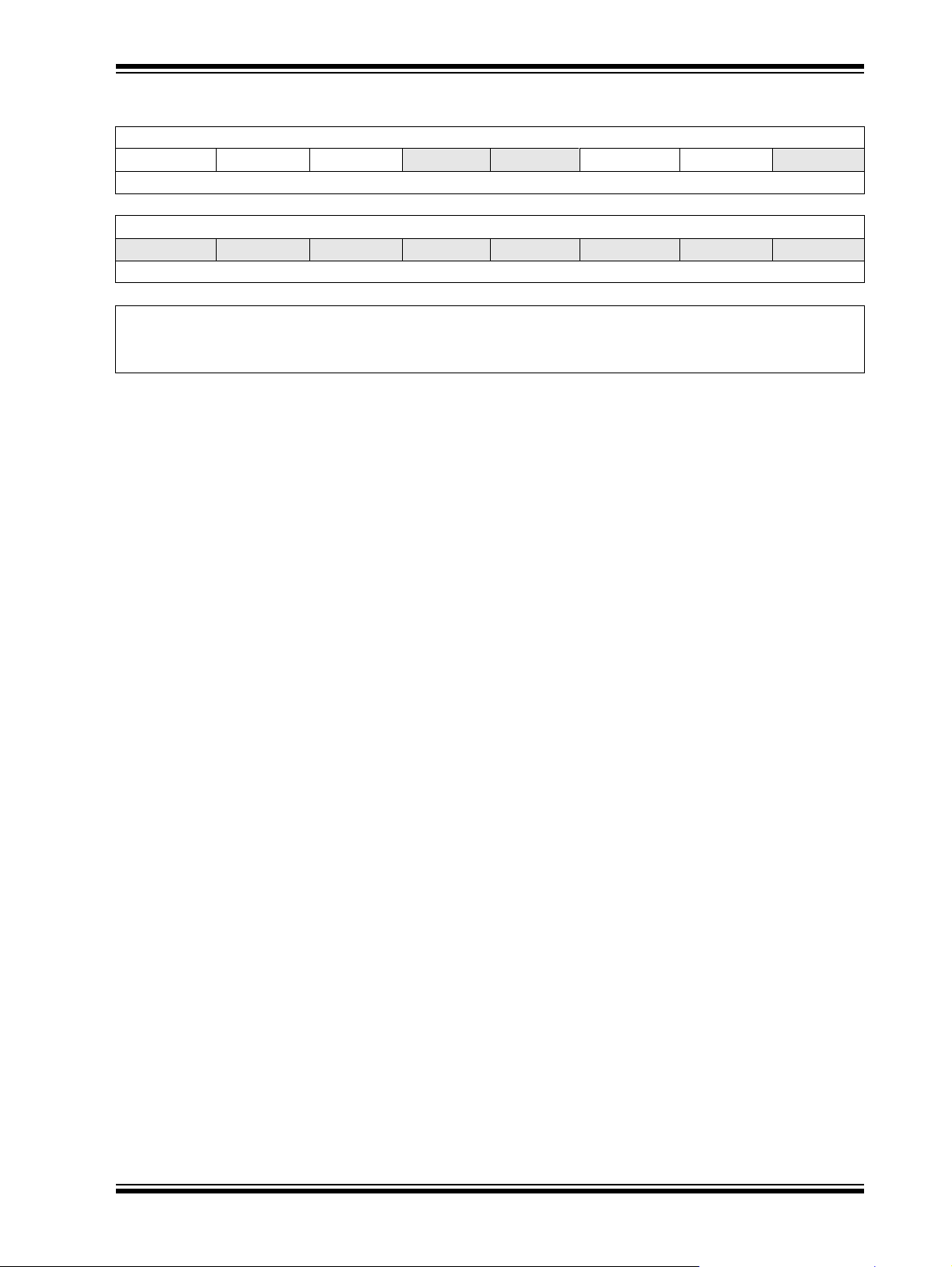

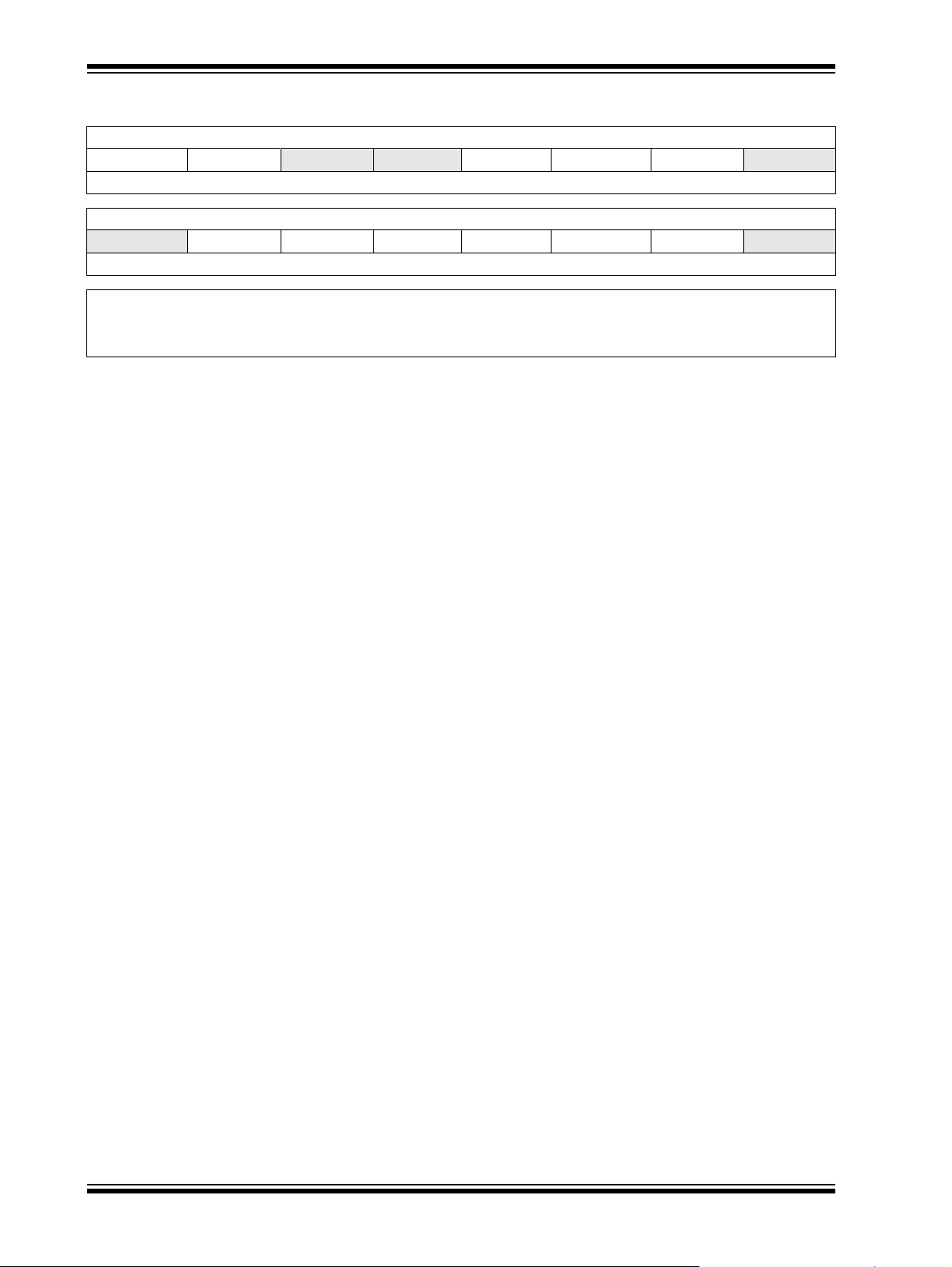

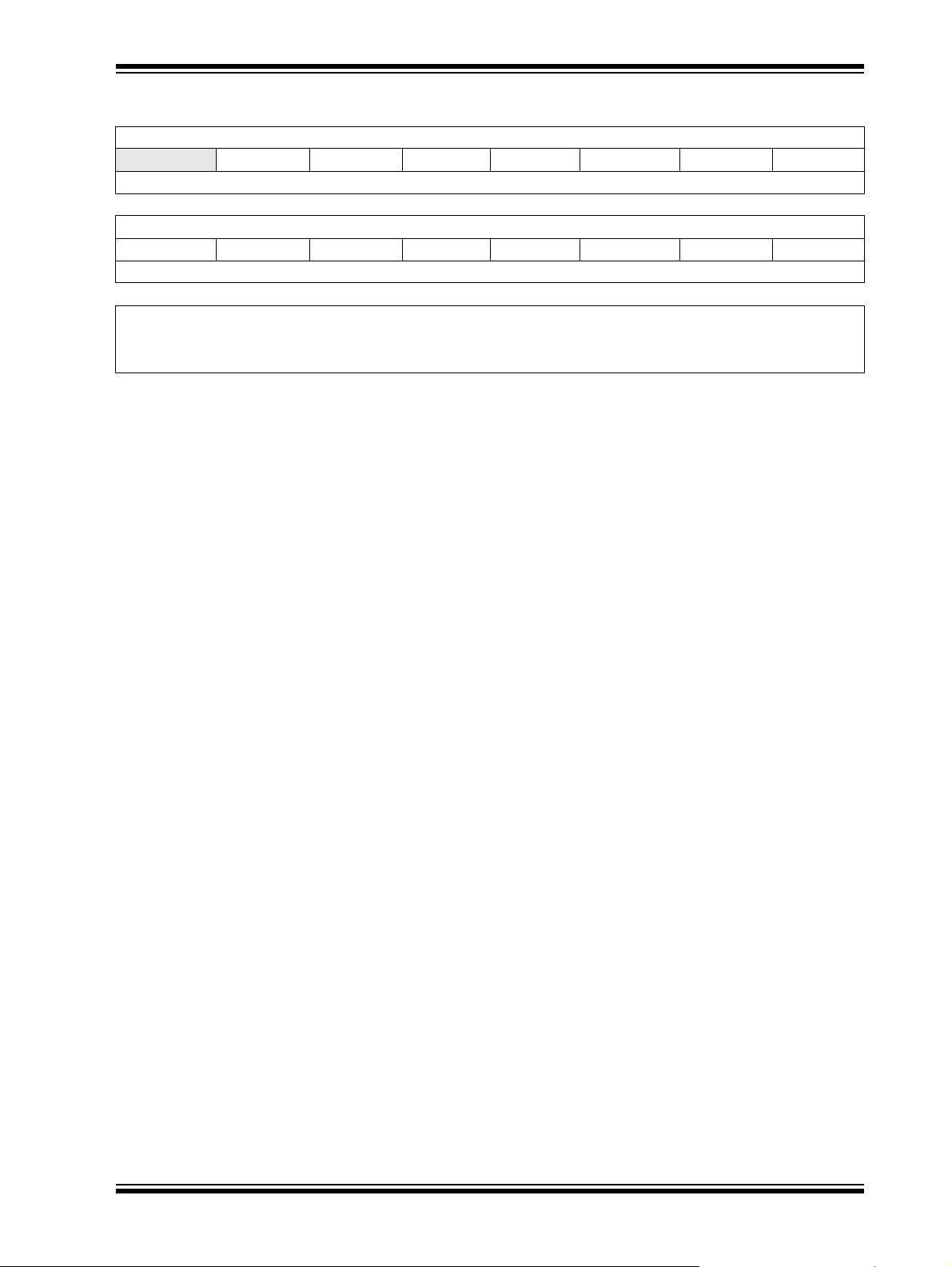

下表列出了每个器件的器件名、引脚数、存储容量和可

用的外设。表后各页还附有它们的引脚图。

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04 控制器系列

16 位定时器

可重映射的外设

输出比较

输入捕捉

标准 PWM

(3)

(通道)

电机控制 PWM

正交编码器

接口

UART

SPI

RTCC

ECAN™

2

C™

I

封装

(通道数)

CRC 发生器

10 位 /12 位 ADC

6 引脚 16 位 DAC

模拟比较器

(2 通道 / 稳压器)

8 位并行主

端口 (地址线)

I/O 引脚

TQFP

SOIC

QFN-S

TQFP

SOIC

QFN-S

TQFP

SOIC

QFN-S

TQFP

SOIC

QFN-S

TQFP

SOIC

QFN-S

(1)

器件

dsPIC33FJ128MC80444128162654 4 6, 2 2 221111 9 1 1/1 11 35QFN

dsPIC33FJ128MC80228128161654 4 6, 2 2 221111 6 0 1/0 2 21SPDIP

dsPIC33FJ128MC2044412882654 4 6, 2 2 220111 9 0 1/1 11 35QFN

dsPIC33FJ128MC2022812881654 4 6, 2 2 220111 6 0 1/0 2 21SPDIP

dsPIC33FJ64MC804 4464162654 4 6, 2 2 221111 9 1 1/1 11 35QFN

dsPIC33FJ64MC802 2864161654 4 6, 2 2 221111 6 0 1/0 2 21SPDIP

dsPIC33FJ64MC204 4464 82654 4 6, 2 2 220111 9 0 1/1 11 35QFN

dsPIC33FJ64MC202 2864 81654 4 6, 2 2 220111 6 0 1/0 2 21SPDIP

dsPIC33FJ32MC304 4432 42654 4 6, 2 2 220111 9 0 1/1 11 35QFN

dsPIC33FJ32MC302 2832 41654 4 6, 2 2 220111 6 0 1/0 2 21SPDIP

注 1: 所有器件的 RAM 大小包括 2KB的 DMA RAM, dsPIC33FJ32MC302/304 除外,它包含 1KB的 DMA RAM。

2: 5 个定时器中只有 4 个是可重映射的。

3: 只有 PWM 故障引脚是可重映射的。

引脚数

(KB)

闪存程序存储器

(2)

RAM (KB)

可重映射的引脚数

DS70291A_CN 第4 页 超前信息 2008 Microchip Technology Inc.

Page 7

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

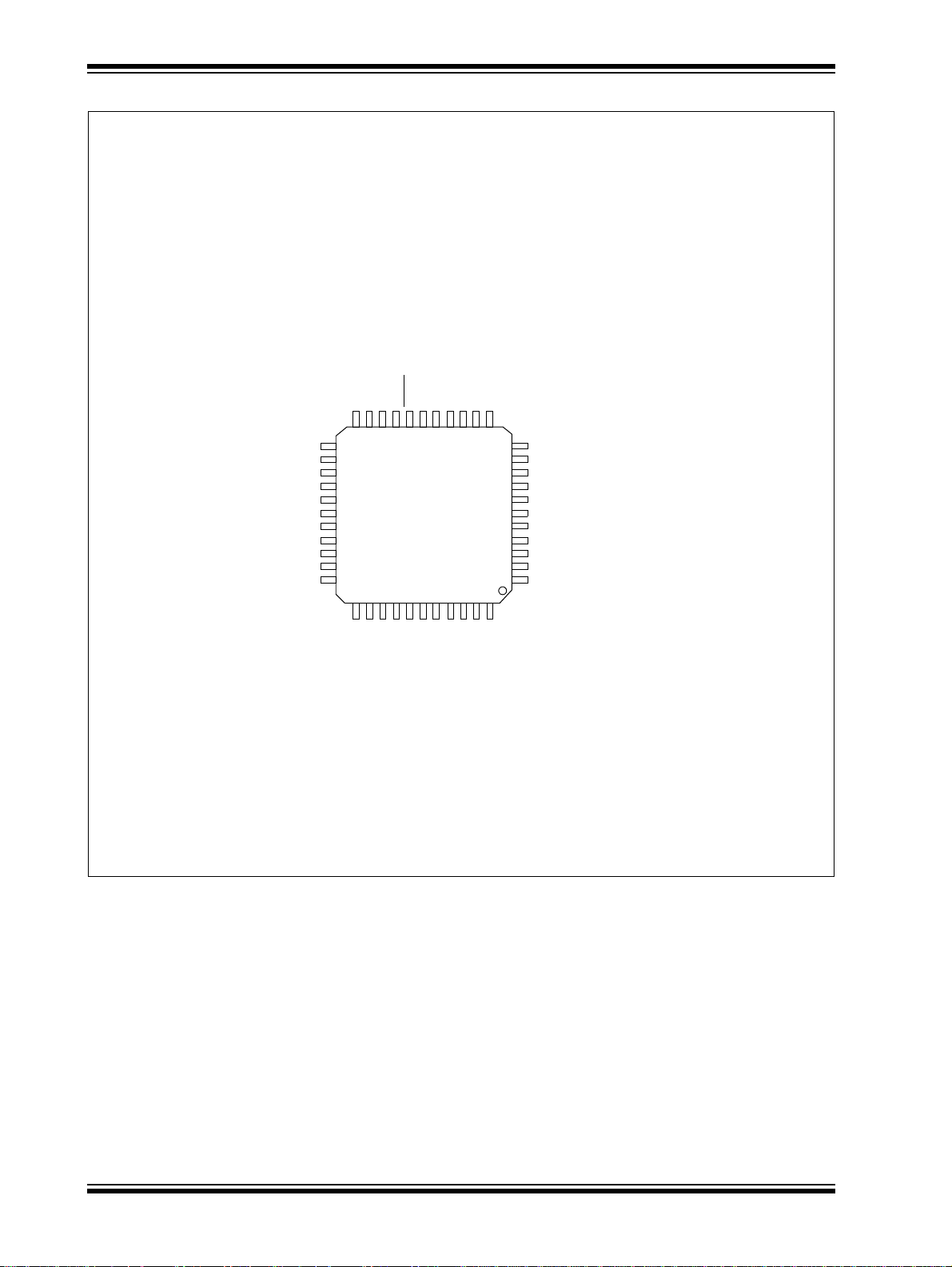

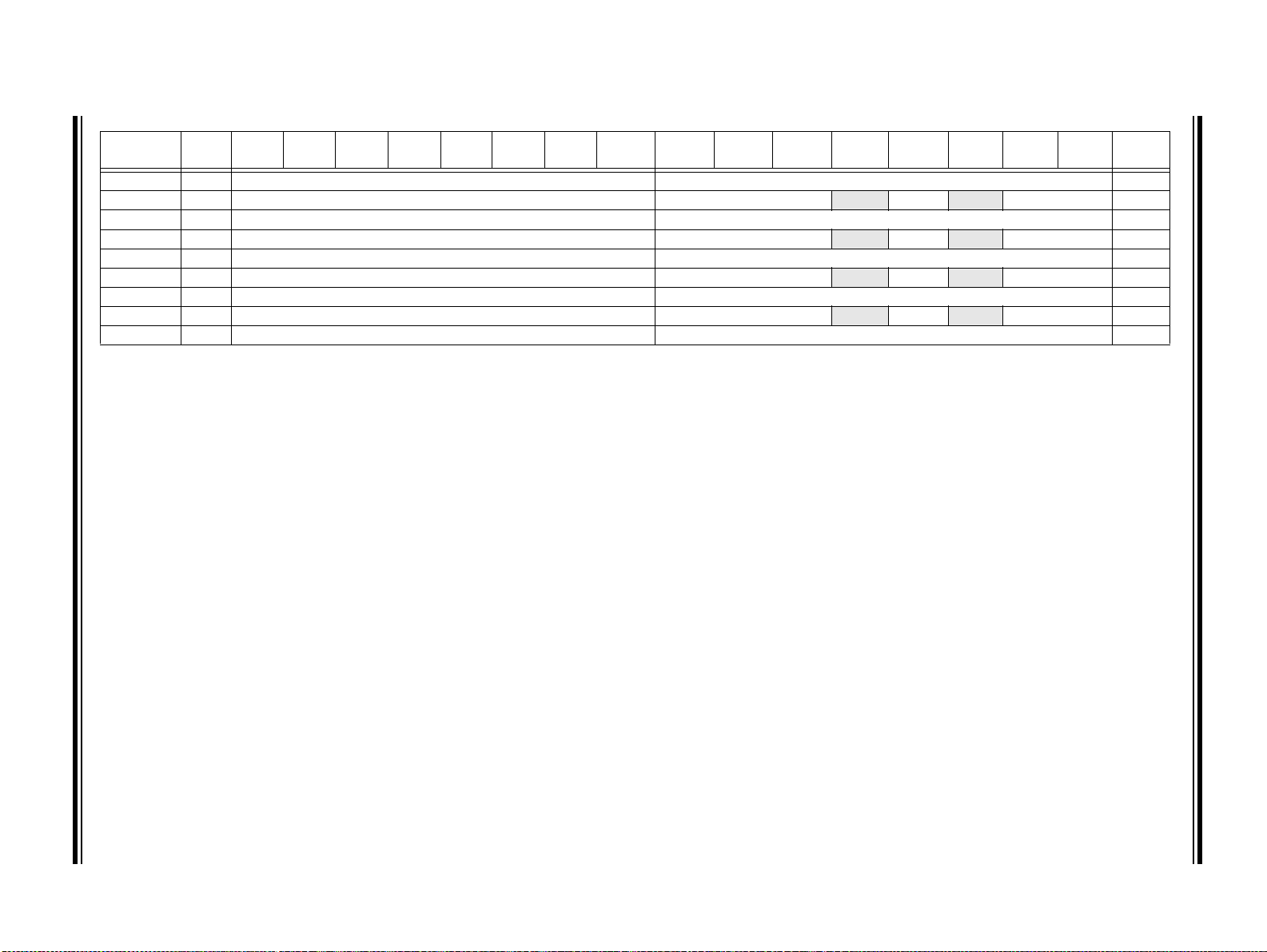

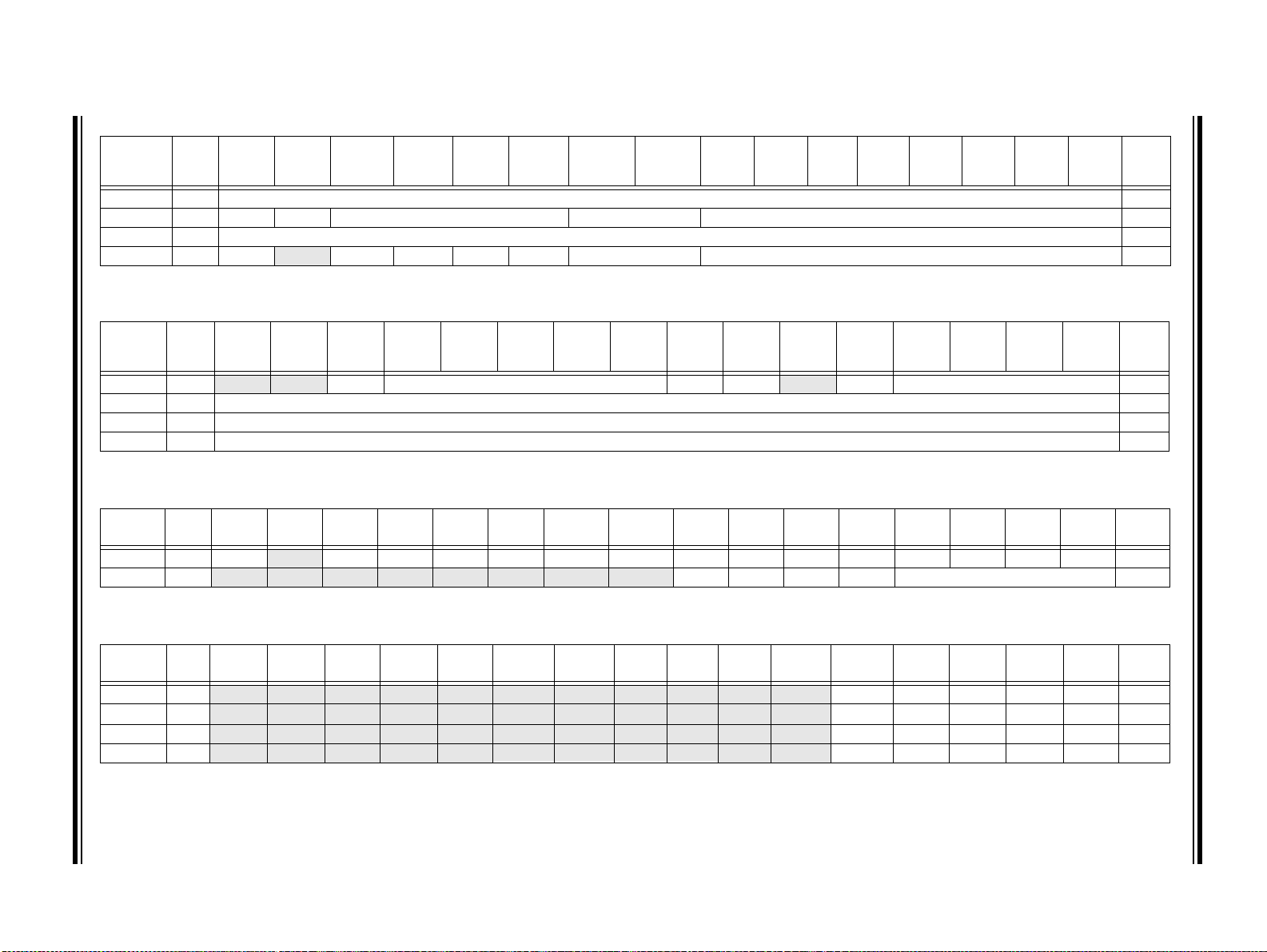

引脚图

28 引脚 SPDIP 和 SOIC

AN0/VREF+/CN2/RA0

AN1/V

REF-/CN3/RA1

PGD1/EMUD1/AN2/C2IN-/RP0/CN4/RB0

PGC1/EMUC1/ AN3/C2IN+/RP1/CN5/RB1

AN4/C1IN-/RP2/CN6/RB2

AN5/C1IN+/RP3/CN7/RB3

OSCI/CLKI/CN30/RA2

OSCO/CLKO/CN29/PMA0/RA3

SOSCI/RP4/CN1/PMBE/RB4

SOSCO/T1CK/CN0/PMA1/RA4

PGD3/EMUD3/ASDA1/RP5/CN27/PMD7/RB5

28 引脚 QFN-S

MCLR

VSS

VDD

1

2

3

dsPIC33FJ128MC802

4

5

6

7

8

9

10

11

12

13

14

dsPIC33FJ32MC302

dsPIC33FJ64MC202

dsPIC33FJ64MC802

dsPIC33FJ128MC202

AVDD

28

AVSS

27

PWM1L1/RP15/CN11/PMCS1/RB15

26

PWM1H1/RTCC/RP14/CN12/PMWR/RB14

25

PWM1L2/RP13/CN13/PMRD/RB13

24

PWM1H2/RP12/CN14/PMD0/RB12

23

PGC2/EMUC2/TMS/PWM1L3/RP11/CN15/PMD1/RB11

22

PGD2/EMUD2/TDI/PWM1H3/RP10/CN16/PMD2/RB10

21

VCAP/VDDCORE

20

SS

V

19

TDO/PWM2L1/SDA1/RP9/CN21/PMD3/RB9

18

TCK/PWM2H1/SCL1/RP8/CN22/PMD4/RB8

17

INT0/RP7/CN23/PMD5/RB7

16

PGC3/EMUC3/ASCL1/RP6/CN24/PMD6/RB6

15

PGD1/EMUD1/AN2/C2IN-/RP0/CN4/RB0

PGC1/EMUC1/AN3/C2IN+/RP1/CN5/RB1

AN4/C1IN-/RP2/CN6/RB2

AN5/C1IN+/RP3/CN7/RB3

VSS

OSCI/CLKI/CN30/RA2

OSCO/CLKO/CN29/PMA0/RA3

REF-/CN3/RA1

DD

AN1/V

AV

MCLR

AN0/VREF+/CN2/RA0

8

6

7

5

2

2

2

2

1

2

dsPIC33FJ32MC302

3

dsPIC33FJ64MC202

4

dsPIC33FJ64MC802

dsPIC33FJ128MC202

5

dsPIC33FJ128MC802

6

7

9

10

8

11

VDD

SOSCI/RP4/CN1/PMBE/RB4

SOSCO/T1CK/CN0/PMA1/RA4

PGD3/EMUD3/ASDA1/RP5/CN27/PMD7/RB5

AVSS

4

2

12

PGC3/ EMUC3/ASCL1/RP6/CN24/PMD6/RB6

PWM1L1/RP15/CN11/PMCS1/RB15

PWM1H1/RTCC/RP14/CN12/PMWR/RB14

2

3

2

2

PWM1L2/RP13/CN13/PMRD/RB13

21

PWM1H2/RP12/CN14/PMD0/RB12

20

PGC2/EMUC2/TMS/PWM1L3/RP11/CN15/PMD1/RB11

19

PGD2/EMUD2/TDI/PWM1H3/RP10/CN16/PMD2/RB10

18

CAP/VDDCORE

V

17

VSS

16

TDO/PWM2L1/SDA1/RP9/CN21/PMD3/RB9

15

14

13

INT0/RP7/CN23/PMD5/RB7

TCK/PWM2H1/SCL1/RP8/CN22/PMD4/RB8

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第5 页

Page 8

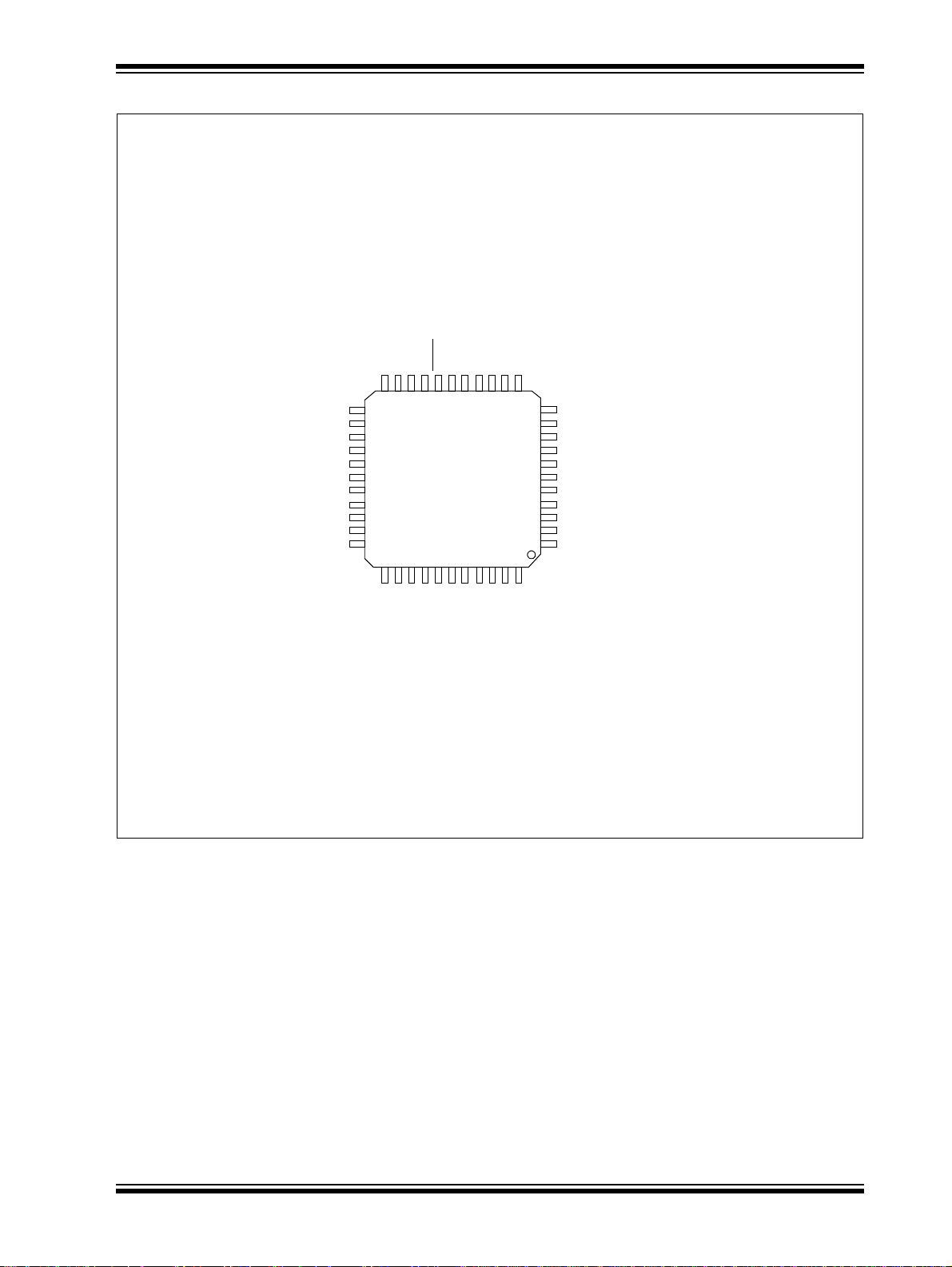

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

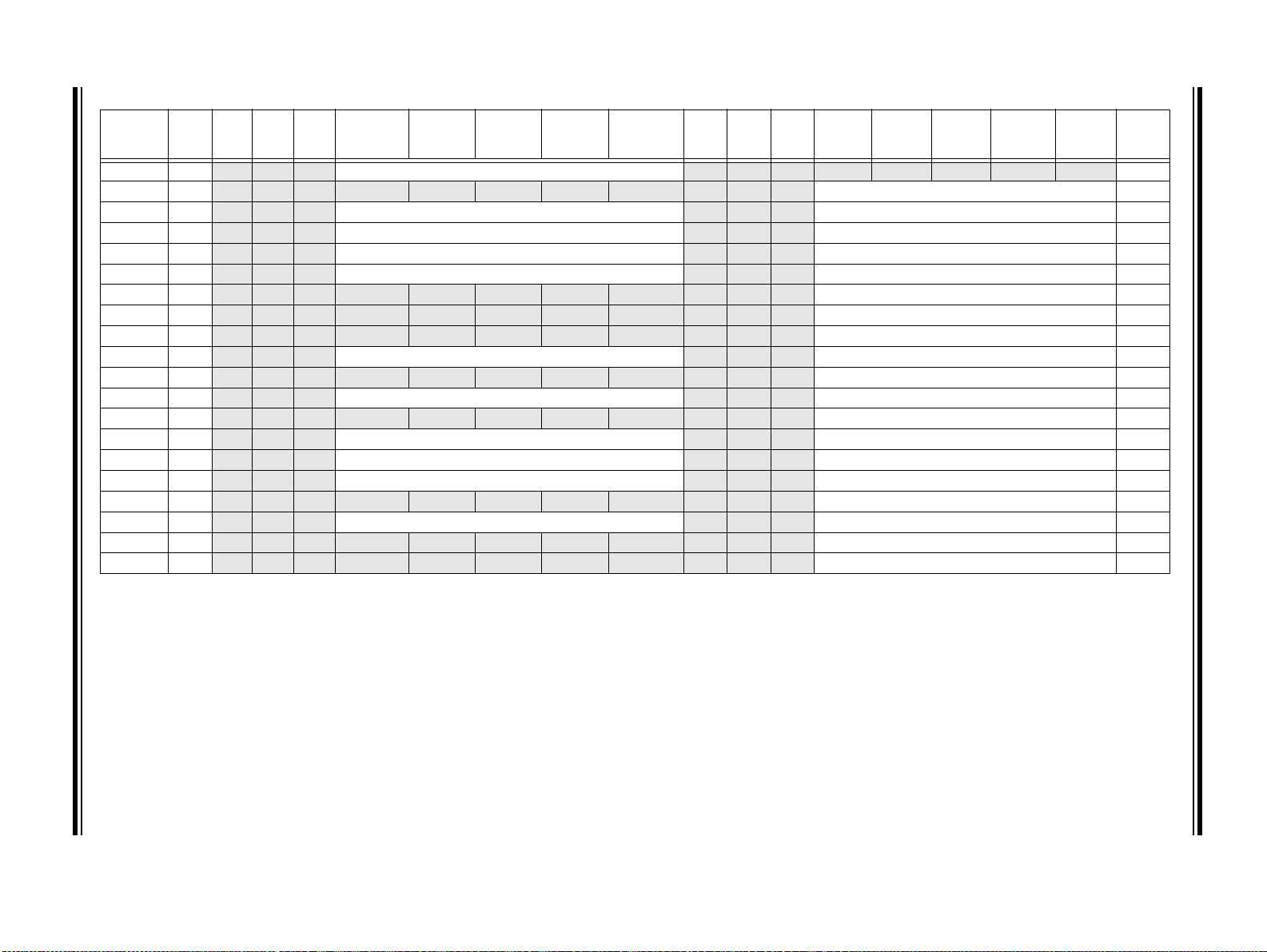

引脚图 (续)

44 引脚 QFN

REF-/CN3/RA1

REF+/CN2/RA0

PGC1/EMUC1/AN3/C2IN+/RP1/CN5/RB1

PGD1/EMUD1/AN2/C2IN-/RP0/CN4/RB0

AN5/C1IN+/RP3/CN7/RB3

AN6/DAC1RM/RP16/CN8/RC0

AN7/DAC1LM/RP17/CN9/RC1

AN8/CV

REF/RP18/PMA2/CN10/RC2

OSCI/CLKI/CN30/RA2

OSCO/CLKO/CN29/RA3

TDO/PMA8/RA8

SOSCI/RP4/CN1/RB4

V

VSS

DD

AN1/V

AVDDAVSS

AN0/V

MCLR

23

24

25

26

27

28

29

30

31

33

20

21

22

17

18

19

dsPIC33FJ64MC804

dsPIC33FJ128MC804

39

38

37

36

35

34

SS

V

40

DD

V

16

TMS/PMA10/RA10

PWM1L1/DAC1LN/RP15/CN11/PMCS1/RB15

PWM1H1/DAC1LP/RTCC/RP14/CN12/PMWR/RB14

TCK/PMA7/RA7

PWM1L2/DAC1RN/RP13/CN13/PMRD/RB13AN4/C1IN-/RP2/CN6/RB2

11

13

14

15

12

PWM1H2/DAC1RP/RP12/CN14/PMD0/RB12

10

PGC2/EMUC2/PWM1L3/RP11/CN15/PMD1/RB11

9

PGD2/EMUD2/PWM1H3/RP10/CN16/PMD2/RB10

8

V

CAP/VDDCORE

7

VSS

6

RP25/CN19/PMA6/RC9

5

RP24/CN20/PMA5/RC8

4

PWM2L1/RP23/CN17/PMA0/RC7

3

PWM2H1/RP22/CN18/PMA1/RC6

232

SDA1/RP9/CN21/PMD3/RB9

41

1

44

43

42

SOSCO/T1CK/CN0/RA4

TDI/PMA9/RA9

RP19/CN28/PMBE/RC3

RP20/CN25/PMA4/RC4

RP21/CN26/PMA3/RC5

PGD3/EMUD3/ASDA1/RP5/CN27/PMD7/RB5

PGC3/EMUC3/ASCL1/RP6/CN24/PMD6/RB6

INT0/RP7/CN23/PMD5/RB7

SCL1/RP8/CN22/PMD4/RB8

DS70291A_CN 第6 页 超前信息 2008 Microchip Technology Inc.

Page 9

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

引脚图 (续)

44 引脚 QFN

REF-/CN3/RA1

REF+/CN2/RA0

AN0/V

MCLR

PGD1/EMUD1/AN2/C2IN-/RP0/CN4/RB0

AN1/V

AVDDAVSS

20

21

36

35

16

17

18

19

40

39

38

37

SS

DD

V

V

TMS/PMA10/RA10

PWM1L1/RP15/CN11/PMCS1/RB15

PWM1H1/RTCC/RP14/CN12/PMWR/RB14

TCK/PMA7/RA7

PWM1L2/RP13/CN13/PMRD/RB13

11

13

14

15

12

PWM1H2/RP12/CN14/PMD0/RB12

10

PGC2/EMUC2/PWM1L3/RP11/CN15/PMD1/RB11

9

PGD2/EMUD2/PWM1H3/RP10/CN16/PMD2/RB10

8

V

CAP/VDDCORE

7

VSS

6

RP25/CN19/PMA6/RC9

5

RP24/CN20/PMA5/RC8

4

PWM2L1/RP23/CN17/PMA0/RC7

3

PWM2H1/RP22/CN18/PMA1/RC6

232

SDA1/RP9/CN21/PMD3/RB9

41

1

44

43

42

AN4/C1IN-/RP2/CN6/RB2

AN5/C1IN+/RP3/CN7/RB3

AN6/RP16/CN8/RC0

AN7/RP17/CN9/RC1

AN8/CV

REF/RP18/PMA2/CN10/RC2

OSCI/CLKI/CN30/RA2

OSCO/CLKO/CN29/RA3

SOSCI/RP4/CN1/RB4

V

VSS

TDO/PMA8/RA8

DD

PGC1/EMUC1/AN3/C2IN+/RP1/CN5/RB1

23

22

24

25

26

dsPIC33FJ32MC304

27

dsPIC33FJ64MC204

28

29

dsPIC33FJ128MC204

30

31

33

34

SOSCO/T1CK/CN0/RA4

TDI/PMA9/RA9

RP21/CN26/PMA3/RC5

RP20/CN25/PMA4/RC4

RP19/CN28/PMBE/RC3

INT0/RP7/CN23/PMD5/RB7

SCL1/RP8/CN22/PMD4/RB8

PGC3/EMUC3/ASCL1/RP6/CN24/PMD6/RB6

PGD3/EMUD3/ASDA1/RP5/CN27/PMD7/RB5

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第7 页

Page 10

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

引脚图 (续)

44 引脚 TQFP

REF-/CN3/RA1

REF+/CN2/RA0

PGC1/EMUC1/AN3/C2IN+/RP1/CN5/RB1

PGD1/EMUD1/AN2/C2IN-/RP0/CN4/RB0

AN4/C1IN-/RP2/CN6/RB2

AN5/C1IN+/RP3/CN7/RB3

AN6/DAC1RM/RP16/CN8/RC0

AN7/DAC1LM/RP17/CN9/RC1

AN8/CV

REF/RP18/PMA2/CN10/RC2

OSCI/CLKI/CN30/RA2

OSCO/CLKO/CN29/RA3

TDO/PMA8/RA8

SOSCI/RP4/CN1/RB4

V

VSS

DD

AN1/V

AVDDAVSS

AN0/V

MCLR

18

19

20

21

22

23

24

25

26

27

dsPIC33FJ64MC804

28

dsPIC33FJ128MC804

29

30

31

32

33

363435937

17

39

38

16

40

TMS/PMA10/RA10

PWM1L1/DAC1LN/RP15/CN11/PMCS1/RB15

TCK/PMA7/RA7

PWM1H1/DAC1LP/RTCC/RP14/CN12/PMWR/RB14

12

13

14

15

11

PWM1L2/DAC1RN/RP13/CN13/PMRD/RB13

10

PWM1H2/DAC1RP/RP12/CN14/PMD0/RB12

PGC2/EMUC2/PWM1L3/RP11/CN15/PMD1/RB11

8

PGD2/EMCD2/PWM1H3/RP10/CN16/PMD2/RB10

7

CAP/VDDCORE

V

6

VSS

5

RP25/CN19/PMA6/RC9

4

RP24/CN20/PMA5/RC8

3

PWM2L1/RP23/CN17/PMA0/RC7

2

PWM2H1/RP22/CN18/PMA1/RC6

1

SDA1/RP9/CN21/PMD3/RB9

44

43

42

41

SOSCO/T1CK/CN0/RA4

TDI/PMA9/RA9

RP19/CN28/PMBE/RC3

RP20/CN25/PMA4/RC4

SS

V

RP21/CN26/PMA3/RC5

DD

V

PGD3/EMUD3/ASDA1/RP5/CN27/PMD7/RB5

PGC3/EMUC3/ASCL1/RP6/CN24/PMD6/RB6

INT0/RP7/CN23/PMD5/RB7

SCL1/RP8/CN22/PMD4/RB8

DS70291A_CN 第8 页 超前信息 2008 Microchip Technology Inc.

Page 11

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

引脚图 (续)

44 引脚 TQFP

REF-/CN3/RA1

REF+/CN2/RA0

AN0/V

AN4/C1IN-/RP2/CN6/RB2

AN5/C1IN+/RP3/CN7/RB3

AN6/RP16/CN8/RC0

AN8/CV

AN7/RP17/CN9/RC1

REF/RP18/PMA2/CN10/RC2

OSCI/CLKI/CN30/RA2

OSCO/CLKO/CN29/RA3

SOSCI/RP4/CN1/RB4

V

DD

VSS

TDO/PMA8/RA8

PGC1/EMUC1/AN3/C2IN+/RP1/CN5/RB1

22

23

24

25

26

dsPIC33FJ32MC304

27

28

dsPIC33FJ64MC204

29

dsPIC33FJ128MC204

30

31

32

33

MCLR

PGD1/EMUD1/AN2/C2IN-/RP0/CN4/RB0

AN1/V

17

18

19

20

21

39

363435937

38

AVDDAVSS

16

40

TMS/PMA10/RA10

PWM1L1/RP15/CN11/PMCS1/RB15

TCK/PMA7/RA7

PWM1H1/RTCC/RP14/CN12/PMWR/RB14

12

13

14

15

11

PWM1L2/RP13/CN13/PMRD/RB13

10

PWM1H2/RP12/CN14/PMD0/RB12

PGC2/EMUC2/PWM1L3/RP11/CN15/PMD1/RB11

8

PGD2/EMCD2/PWM1H3/RP10/CN16/PMD2/RB10

7

CAP/VDDCORE

V

6

VSS

5

RP25/CN19/PMA6/RC9

4

RP24/CN20/PMA5/RC8

3

PWM2L1/RP23/CN17/PMA0/RC7

2

PWM2H1/RP22/CN18/PMA1/RC6

1

SDA1/RP9/CN21/PMD3/RB9

44

43

42

41

SOSCO/T1CK/CN0/RA4

TDI/PMA9/RA9

RP19/CN28/PMBE/RC3

RP20/CN25/PMA4/RC4

RP21/CN26/PMA3/RC5

SS

DD

V

V

INT0/RP7/CN23/PMD5/RB7

SCL1/RP8/CN22/PMD4/RB8

PGC3/EMUC3/ASCL1/RP6/CN24/PMD6/RB6

PGD3/EMUD3/ASDA1/RP5/CN27/PMD7/RB5

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第9 页

Page 12

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

目录

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04 产品系列 ......................................................... 4

1.0 器件概述 ..................................................................................................................................................................................... 13

2.0 CPU............................................................................................................................................................................................ 19

3.0 存储器构成 ................................................................................................................................................................................. 31

4.0 闪存程序存储器 .......................................................................................................................................................................... 67

5.0 复位 ............................................................................................................................................................................................ 73

6.0 中断控制器 ................................................................................................................................................................................. 81

7.0 直接存储器访问 (DMA)......................................................................................................................................................... 123

8.0 振荡器配置 ............................................................................................................................................................................... 135

9.0 节能特性 ................................................................................................................................................................................... 147

10.0 I/O 端口..................................................................................................................................................................................... 149

11.0 Timer2/3 和 Timer4/5 特性........................................................................................................................................................ 181

12.0 Timer1 ...................................................................................................................................................................................... 187

13.0 输入捕捉 ................................................................................................................................................................................... 189

14.0 输出比较 ................................................................................................................................................................................... 191

15.0 电机控制 PWM 模块 ................................................................................................................................................................. 195

16.0 正交编码器接口 (QEI)模块................................................................................................................................................... 217

17.0 串行外设接口 (SPI)............................................................................................................................................................... 225

2

18.0 I

C™ ........................................................................................................................................................................................ 233

19.0 通用异步收发器 (UART)....................................................................................................................................................... 243

20.0 增强型 CAN (ECAN™)模块 ................................................................................................................................................. 251

21.0 10 位 /12 位模数转换器 (ADC1)............................................................................................................................................ 281

22.0 音频数模转换器 (DAC)......................................................................................................................................................... 295

23.0 比较器模块 ............................................................................................................................................................................... 301

24.0 实时时钟和日历 (RTCC)....................................................................................................................................................... 307

25.0 可编程循环冗余校验 (CRC)发生器 ...................................................................................................................................... 319

26.0 并行主端口 (PMP)................................................................................................................................................................ 323

27.0 特殊功能 ................................................................................................................................................................................... 333

28.0 指令集汇总 ............................................................................................................................................................................... 343

29.0 开发支持 ................................................................................................................................................................................... 351

30.0 电气特性 ................................................................................................................................................................................... 355

31.0 封装信息 ................................................................................................................................................................................... 399

Microchip 网站.................................................................................................................................................................................... 413

变更通知客户服务 .............................................................................................................................................................................. 413

客户支持............................................................................................................................................................................................. 413

读者反馈表 ......................................................................................................................................................................................... 414

产品标识体系...................................................................................................................................................................................... 415

DS70291A_CN 第10 页 超前信息 2008 Microchip Technology Inc.

Page 13

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

致客户

我们旨在提供最佳文档供客户正确使用 Microchip 产品。为此,我们将不断改进出版物的内容和质量,使之更好地满足您的要求。

出版物的质量将随新文档及更新版本的推出而得到提升。

如果您对本出版物有任何问题和建议,请通过电子邮件联系我公司 TRC 经理,电子邮件地址为 CTRC@microchip.com,或将本

数据手册后附的 《读者反馈表》传真到 86-21-5407 5066。我们期待您的反馈。

最新数据手册

欲获得本数据手册的最新版本,请查询我公司的网站:

http://www.microchip.com

查看数据手册中任意一页下边角处的文献编号即可确定其版本。文献编号中数字串后的字母是版本号,例如:DS30000A 是DS30000

的 A 版本。

勘误表

现有器件可能带有一份勘误表,描述了实际运行与数据手册中记载内容之间存在的细微差异以及建议的变通方法。一旦我们了解到

器件 / 文档存在某些差异时,就会发布勘误表。勘误表上将注明其所适用的硅片版本和文件版本。

欲了解某一器件是否存在勘误表,请通过以下方式之一查询:

• Microchip 网站, http://www.microchip.com

• 当地 Microchip 销售办事处 (见最后一页)

在联络销售办事处时,请说明您所使用的器件型号、硅片版本和数据手册版本 (包括文献编号)。

客户通知系统

欲及时获知 Microchip 产品的最新信息,请到我公司网站 www.microchip.com 上注册。

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第 11 页

Page 14

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

注:

DS70291A_CN 第12 页 超前信息 2008 Microchip Technology Inc.

Page 15

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

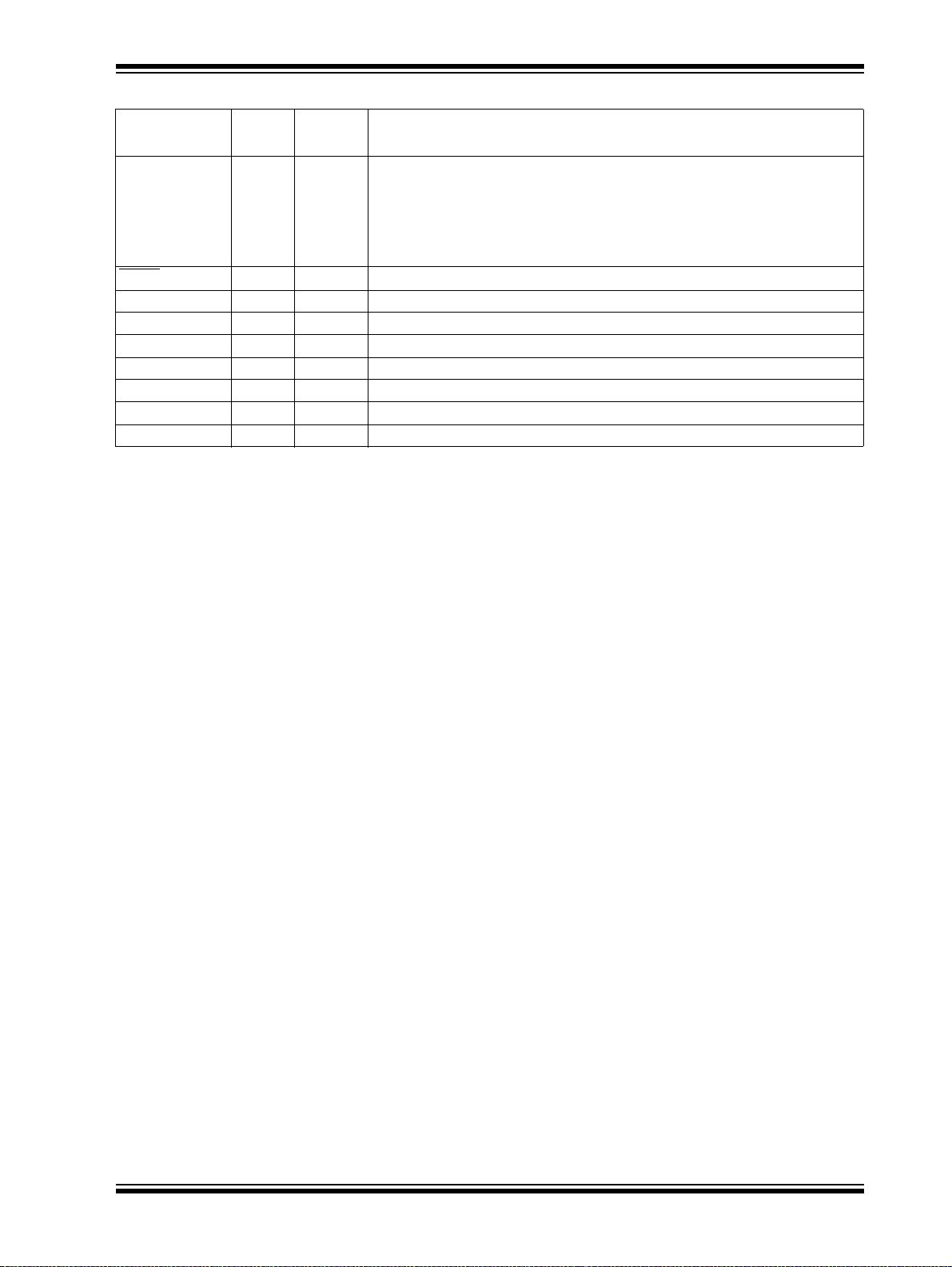

1.0 器件概述

注: 本数据手册总结了 dsPIC33FJ32MC302/

304、 dsPIC33FJ64MCX02/X04 和

dsPIC33FJ128MCX02/X04 系列器件的特

性。但是不应把本手册当作无所不包的参

考手册来使用。如需了解本数据手册的补

充信 息,请 参 考 “dsPIC33F Family

Reference Manual”的相关章节,该文档

可从 Microchip 网站

(www.microchip.com)下载。

本文档包含 dsPIC33FJ32MC302/304、

dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/

X04 数字信号控制器(Digital Signal Controller,DSC)

器件的特定信息。dsPIC33F 器件在高性能 16 位单片机

(MCU)架构中,融合了丰富的数字信号处理器

(Digital Signal Processor, DSP)功能。

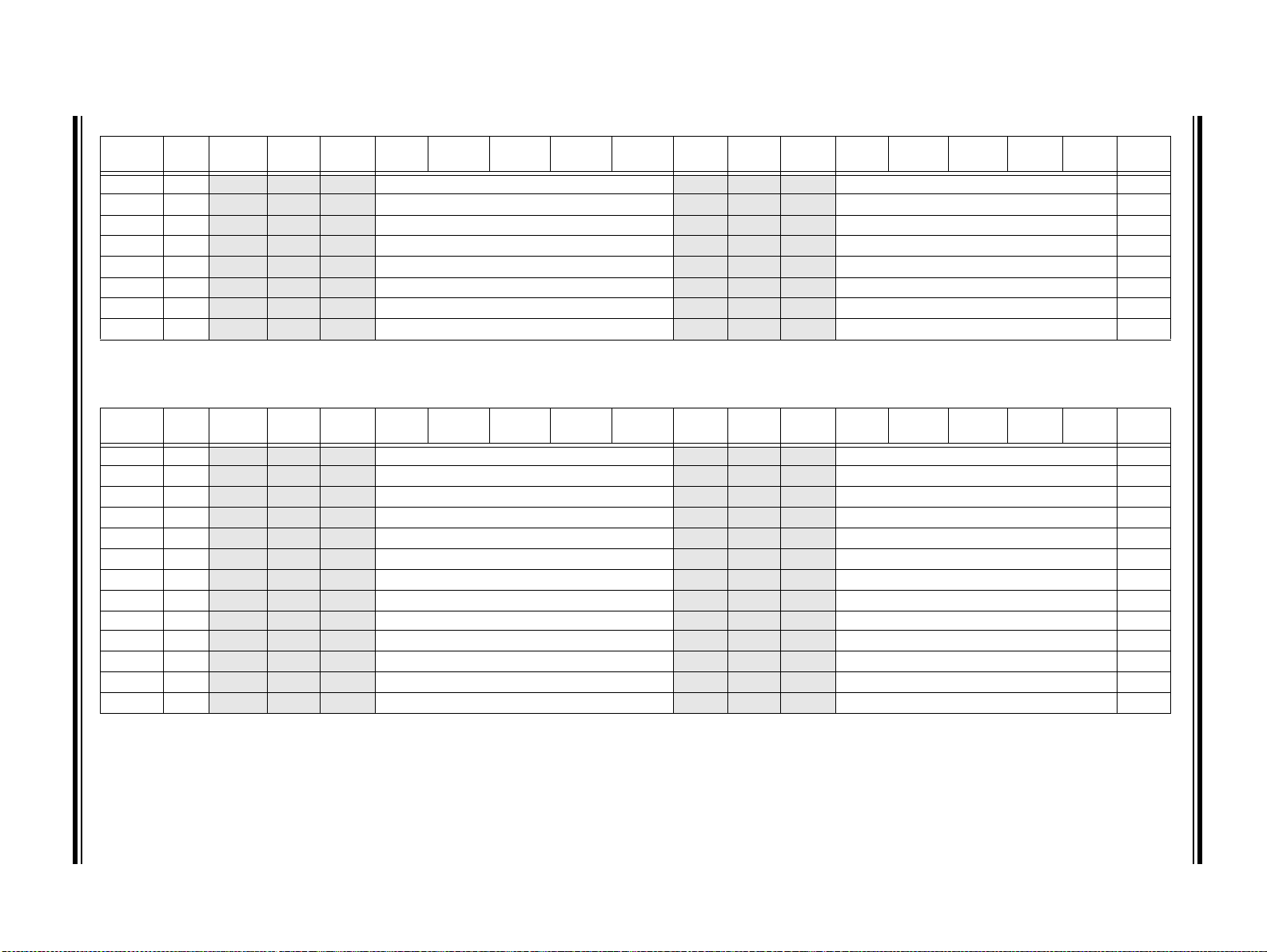

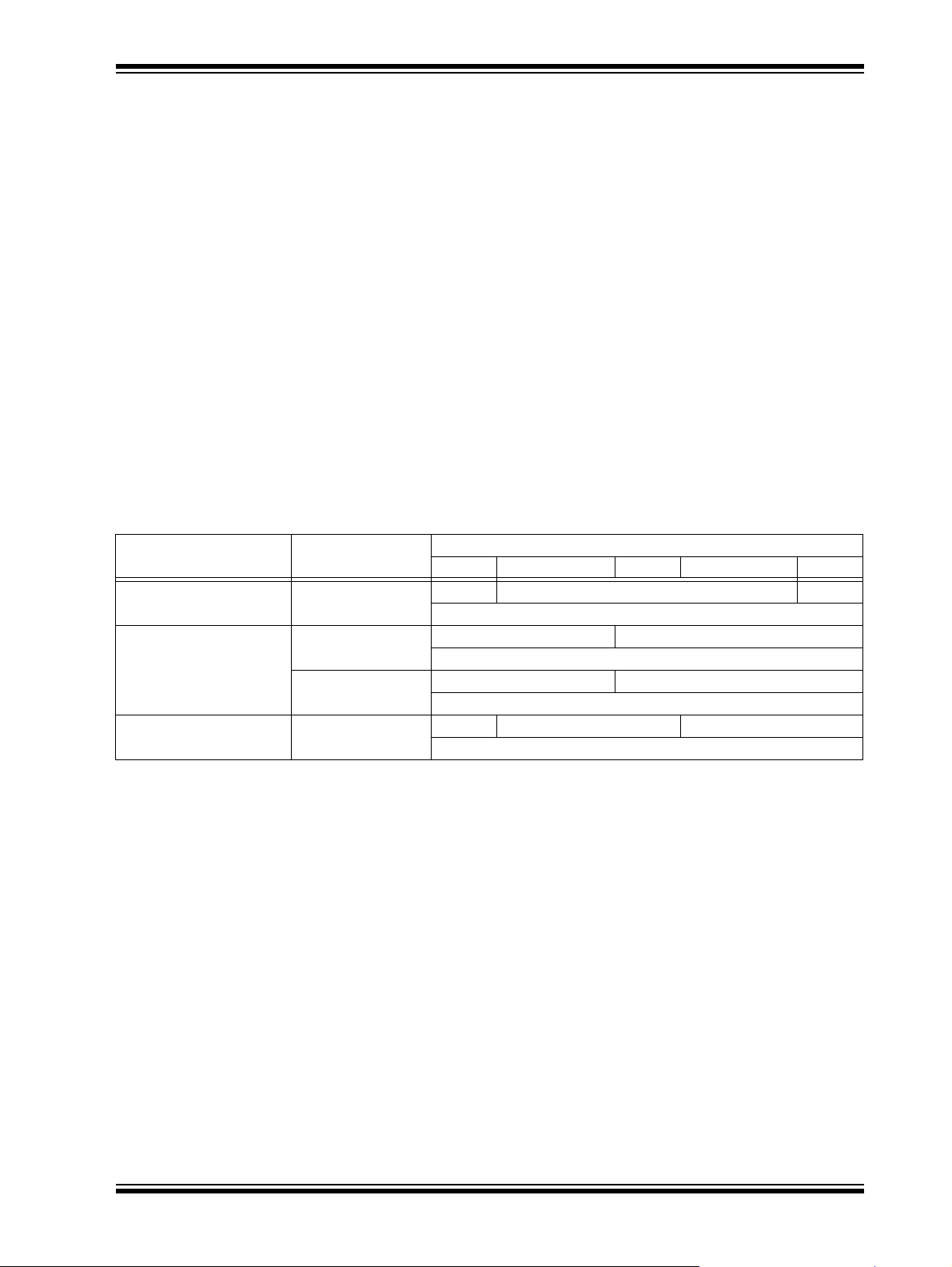

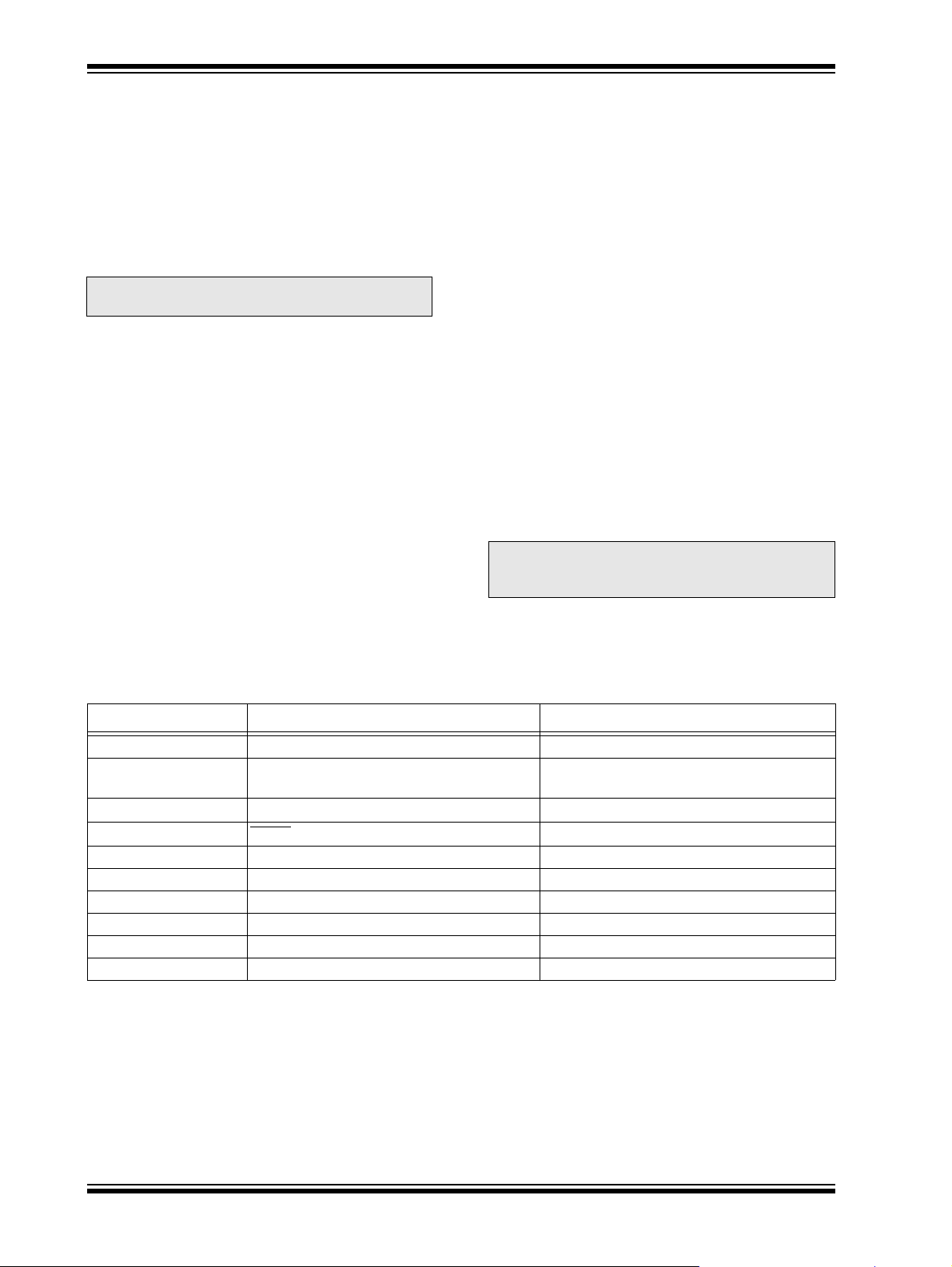

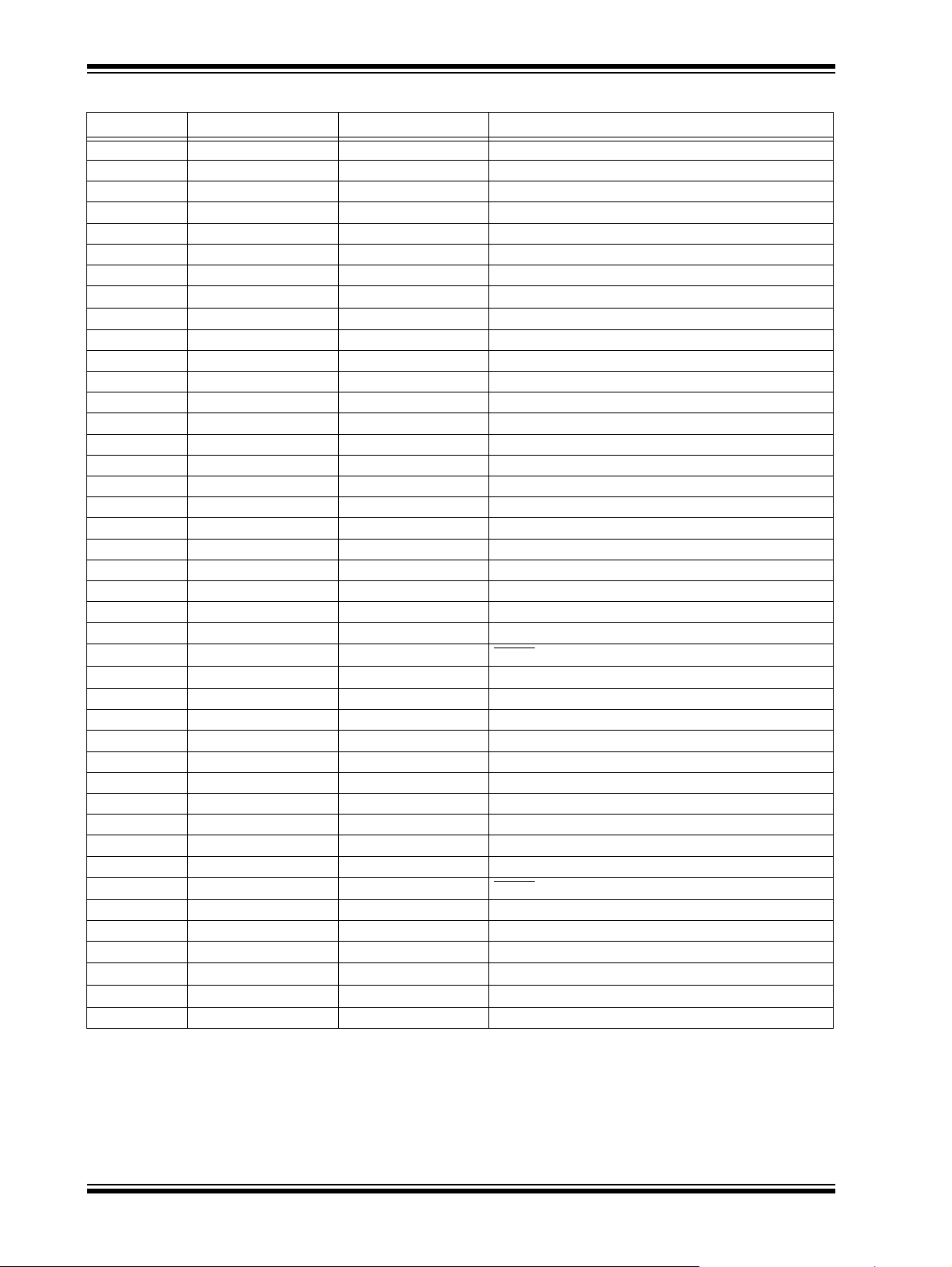

图 1-1 给出了 dsPIC33FJ32MC302/304、

dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/

X04 系列器件内核和外设模块的通用框图。表 1-1 列出

了引脚图中所示各引脚的功能。

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第 13 页

Page 16

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

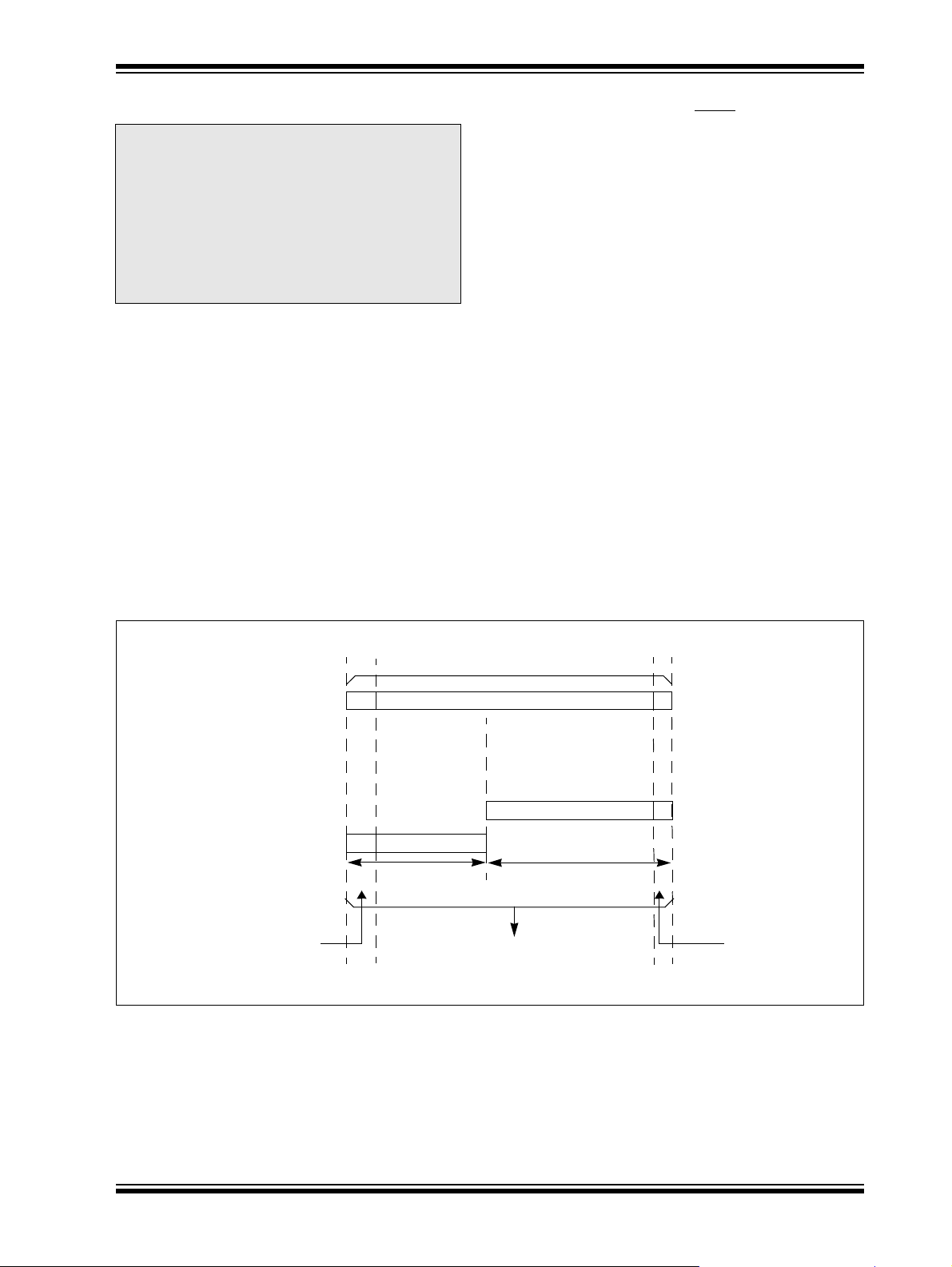

图 1-1: dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

框图

PSV

和表

数据访问

控制模块

23

23

地址锁存器

中断

控制器

23

8

PCU

程序计数器

堆栈

控制

逻辑

16

PCH PCL

循环

控制

逻辑

Y

数据总线

X

数据总线

16

16

数据锁存器

X RAM

地址

锁存器

16

地址发生器单元

数据锁存器

Y RAM

地址

锁存器

16

16

PORTA

DMA

RAM

PORTB

DMA

控制器

16

PORTC

程序存储器

数据锁存器

OSC2/CLKO

OSC1/CLKI

时序

发生

FRC/LPRC

振荡器

高精度

带隙

参考

稳压器

VDDCORE/VCAP

地址总线

至各模块的

控制信号

DD 和 VSS

V

24

指令

译码和

控制

上电延时

定时器

振荡器

起振定时器

上电

复位

看门狗

定时器

欠压

复位

MCLR

DSP

除法支持

ROM

指令寄存器

引擎

锁存器

EA

多路开关

16

立即数数据

16 x 16

W

寄存器阵列

可重映射的

引脚

16

16

16

16位ALU

16

PMP/

EPSP

RTCC

注: 并非所有器件的引脚配置中都实现了全部的引脚或特性。请参见引脚图了解每个器件上的特定引脚和特性的信息。

比较器

1, 2

DAC1

ECAN1

SPI1, 2

定时器

1-5

IC1, 2, 7, 8

UART1, 2

CNx

ADC1

I2C1

输出比较 /

PWM1-4

QEI1, 2

PWM

2 通道

PWM

6 通道

DS70291A_CN 第14 页 超前信息 2008 Microchip Technology Inc.

Page 17

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

表 1-1: 引脚输入 / 输出说明

引脚名称

AN0-AN8

CLKI

CLKO

OSC1

OSC2

SOSCI

SOSCO

CN0-CN30 I ST

IC1-IC2

IC7-IC8

OCFA

OC1-OC4

INT0

INT1

INT2

RA0-RA4

RA7-RA10

RB0-RB15 I/O ST

RC0-RC9 I/O ST

T1CK

T2CK

T3CK

T4CK

T5CK

U1CTS

U1RTS

U1RX

U1TX

U2CTS

U2RTS

U2RX

U2TX

SCK1

SDI1

SDO1

SS1

SCK2

SDI2

SDO2

SS2

SCL1

SDA1

ASCL1

ASDA1

图注: CMOS = CMOS 兼容输入或输出 Analog = 模拟输入 P = 电源

ST = CMOS 电平的施密特触发器输入 O = 输出 I = 输入

引脚类型缓冲器

类型

IAnalog

I

ST/CMOS

O

I

I/O

I

O

I

I

I

O

I

I

I

I/O

I/O

I

I

I

I

I

I

O

I

O

I

O

I

O

I/O

I

O

I/O

I/O

I

O

I/O

I/O

I/O

I/O

I/O

—

ST/CMOS

—

ST/CMOS

—

ST

ST

ST

—

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

—

ST

—

ST

—

ST

—

ST

ST

—

ST

ST

ST

—

ST

ST

ST

ST

ST

说明

模拟输入通道。

外部时钟源输入。总是与 OSC1 引脚功能相关联。

晶振输出。在晶振模式下,连接到晶振或谐振器。也可选择在 RC 和 EC 模式

下用作 CLKO。总是与 OSC2 引脚功能相关联。

晶振输入。配置为 RC 模式时为 ST 缓冲器输入;否则为 CMOS 缓冲器输入。

晶振输出。在晶振模式下,连接到晶振或谐振器。也可选择在 RC 和 EC 模式

下用作 CLKO。

32.768 kHz 低功耗晶振输入;否则为 CMOS 输入。

32.768 kHz 低功耗晶振输出。

电平变化通知输入。

可将所有输入用软件编程为内部弱上拉。

捕捉输入 1/2

捕捉输入 7/8。

比较故障 A 输入 (用于比较通道 1、 2、 3 和 4)。

比较输出 1 至 4。

外部中断 0。

外部中断 1。

外部中断 2。

PORTA 是双向 I/O 端口。

PORTA 是双向 I/O 端口。

PORTB 是双向 I/O 端口。

PORTC 是双向 I/O 端口。

Timer1 外部时钟输入。

Timer2 外部时钟输入。

Timer3 外部时钟输入。

Timer4 外部时钟输入。

Timer5 外部时钟输入。

UART1 允许发送。

UART1 请求发送。

UART1 接收。

UART1 发送。

UART2 允许发送。

UART2 请求发送。

UART2 接收。

UART2 发送。

SPI1 的同步串行时钟输入 / 输出。

SPI1 数据输入。

SPI1 数据输出。

SPI1 从同步或帧脉冲 I/O。

SPI2 的同步串行时钟输入 / 输出。

SPI2 数据输入。

SPI2 数据输出。

SPI2 从同步或帧脉冲 I/O。

I2C1 的同步串行时钟输入 / 输出。

I2C1 的同步串行数据输入 / 输出。

I2C1 的备用同步串行时钟输入 / 输出。

I2C1 的备用同步串行数据输入 / 输出。

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第 15 页

Page 18

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

表 1-1: 引脚输入 / 输出说明 (续)

引脚名称

TMS

TCK

TDI

TDO

INDX1

QEA1

QEB1

UPDN1

INDX2

QEA2

QEB2

UPDN2

C1RX

C1TX

RTCC O —

REF OANA

CV

C1IN-

C1IN+

C1OUT

C2INC2IN+

C2OUT

PMA0

PMA1

PMA2 -PMPA10

PMBE

PMCS1

PMD0-PMPD7

PMRD

PMWR

DAC1RN

DAC1RP

DAC1RM

DAC2RN

DAC2RP

DAC2RM

FLTA1

PWM1L1

PWM1H1

PWM1L2

PWM1H2

PWM1L3

PWM1H3

FLTA2

PWM2L1

PWM2H1

图注: CMOS = CMOS 兼容输入或输出 Analog = 模拟输入 P = 电源

ST = CMOS 电平的施密特触发器输入 O = 输出 I = 输入

引脚

类型

I

I

I

O

I

I

I

O

I

I

I

O

I

O

I

I

O

I

I

O

I/O

I/O

O

O

O

I/O

O

O

O

O

O

O

O

O

I

O

O

O

O

O

O

I

O

O

缓冲器

类型

CMOS

CMOS

ANA

ANA

ANA

ANA

ST

—

—

—

—

—

—

ST

—

—

ST

ST

ST

—

ST

ST

ST

ST

ST

ST

ST

—

—

—

ST

ST

—

—

—

ST

—

—

—

—

—

—

—

—

说明

JTAG 测试模式选择引脚。

JTAG 测试时钟输入引脚。

JTAG 测试数据输入引脚。

JTAG 测试数据输出引脚。

正交编码器索引 1 脉冲输入。

在 QEI1 模式下为正交编码器 A 相输入。

在定时器模式下为辅助定时器外部时钟 / 门控输入。

在 QEI1 模式下为正交编码器 B 相输入。

在定时器模式下为辅助定时器外部时钟 / 门控输入。

位置递增 / 递减计数器方向状态。

正交编码器索引 2 脉冲输入。

在 QEI2 模式下为正交编码器 A 相输入。

在定时器模式下为辅助定时器外部时钟 / 门控输入。

在 QEI2 模式下为正交编码器 B 相输入。

在定时器模式下为辅助定时器外部时钟 / 门控输入。

位置递增 / 递减计数器方向状态。

ECAN1 总线接收引脚。

ECAN1 总线发送引脚。

实时时钟闹钟输出。

比较器参考电压输出。

比较器 1 反相输入。

比较器 1 同相输入。

比较器 1 输出。

比较器 2 反相输入。

比较器 2 同相输入。

比较器 2 输出。

并行主端口地址 Bit 0 输入 (缓冲从模式下)和输出 (主模式下)。

并行主端口地址 Bit 1 输入 (缓冲从模式下)和输出 (主模式下)。

并行主端口地址线 (非复用主模式)。

并行主端口字节使能选通。

并行主端口片选 1 选通。

并行主端口数据线 (非复用主模式下)或者地址 / 数据线 (复用主模式下)。

并行主端口读选通。

并行主端口写选通。

DAC1 负输出。

DAC1 正输出。

DAC1 中点电压值输出 (典型值为 1.65V)。

DAC2 负输出。

DAC2 正输出。

DAC2 中点电压值输出 (典型值为 1.65V)。

PWM1 故障 A 输入。

PWM1 低端输出 1

PWM1 高端输出 1

PWM1 低端输出 2

PWM1 高端输出 2

PWM1 低端输出 3

PWM1 高端输出 3

PWM2 故障 A 输入。

PWM2 低端输出 1

PWM2 高端输出 1

DS70291A_CN 第16 页 超前信息 2008 Microchip Technology Inc.

Page 19

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

表 1-1: 引脚输入 / 输出说明 (续)

引脚名称

PGD1/EMUD1

PGC1/EMUC1

PGD2/EMUD2

PGC2/EMUC2

PGD3/EMUD3

PGC3/EMUC3

MCLR

AVDD PP

AVSS PP

V

DD P—

VDDCORE P—

Vss P —

V

REF+IAnalog

VREF-IAnalog

图注: CMOS = CMOS 兼容输入或输出 Analog = 模拟输入 P = 电源

ST = CMOS 电平的施密特触发器输入 O = 输出 I = 输入

引脚类型缓冲器

类型

I/O

I

I/O

I

I/O

I

ST

ST

ST

ST

ST

ST

I/P ST

说明

编程 / 调试通信通道 1 使用的数据 I/O 引脚。

编程 / 调试通信通道 1 使用的时钟输入引脚。

编程 / 调试通信通道 2 使用的数据 I/O 引脚。

编程 / 调试通信通道 2 使用的时钟输入引脚。

编程 / 调试通信通道 3 使用的数据 I/O 引脚。

编程 / 调试通信通道 3 使用的时钟输入引脚。

主复位输入。此引脚为低电平有效的器件复位输入。

模拟模块的正电源。

模拟模块的参考地。

外设逻辑和 I/O 引脚的正电源。

CPU 逻辑滤波电容连接。

逻辑和 I/O 引脚的参考地。

模拟参考电压 (高电压)输入。

模拟参考电压 (低电压)输入。

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第 17 页

Page 20

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

注:

DS70291A_CN 第18 页 超前信息 2008 Microchip Technology Inc.

Page 21

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

2.0 CPU

注: 本数据手册总结了 dsPIC33FJ32MC302/

304、 dsPIC33FJ64MCX02/X04 和

dsPIC33FJ128MCX02/X04 系列器件的特

性。但是不应把本手册当作无所不包的参

考手册来使用。如需了解本数据手册的补

充信 息,请 参 考 “dsPIC33F Family

Reference Manual”的 “ Section 2. CPU”

(DS70204),该文档可从 Microchip 网站

(www.microchip.com)下载。

2.1 概述

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04

和 dsPIC33FJ128MCX02/X04 的 CPU 模块采用 16 位

(数据)的改进型哈佛架构,具有增强指令集,包括对

DSP 的强大支持。CPU 具有 24 位指令字,指令字带有

长度可变的操作码字段。程序计数器(Program

Counter, PC)为 23 位宽,可寻址最大 4M x 24 位的

用户程序存储空间。实际实现的程序存储容量因器件而

异。单周期指令预取机制可帮助维持吞吐量并提供指令

的预测执行功能。除了改变程序流的指令、双字传送

(MOV.D)指令和表指令以外,所有指令都在单个周期

内执行。使用 DO 和 REPEAT 指令支持无开销的程序循

环结构,这两条指令在任何时间都可以被中断。

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04

和 dsPIC33FJ128MCX02/X04 器件的编程模型中有 16

个 16 位工作寄存器。每个工作寄存器都可以充当数据、

地址或地址偏移量寄存器。第 16 个工作寄存器(W15)

作为软件堆栈指针(Stack Pointer,SP),用于中断和

调用。

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04

和 dsPIC33FJ128MCX02/X04 器件具有两类指令:MCU

类指令和 DSP 类指令。这两类指令无缝地集成到单个

CPU 中。指令集包括很多寻址模式,指令的设计可使 C

编译器的效率达到最优。对于大多数指令,

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04

和dsPIC33FJ128MCX02/X04能够在每个指令周期内执

行一次数据 (或程序数据)存储器读取、一次工作寄存

器 (数据)读取、一次数据存储器写入以及一次程序

(指令)存储器读取操作。因此,支持三操作数指令,

允许在单个周期内执行 A + B = C 这样的操作。

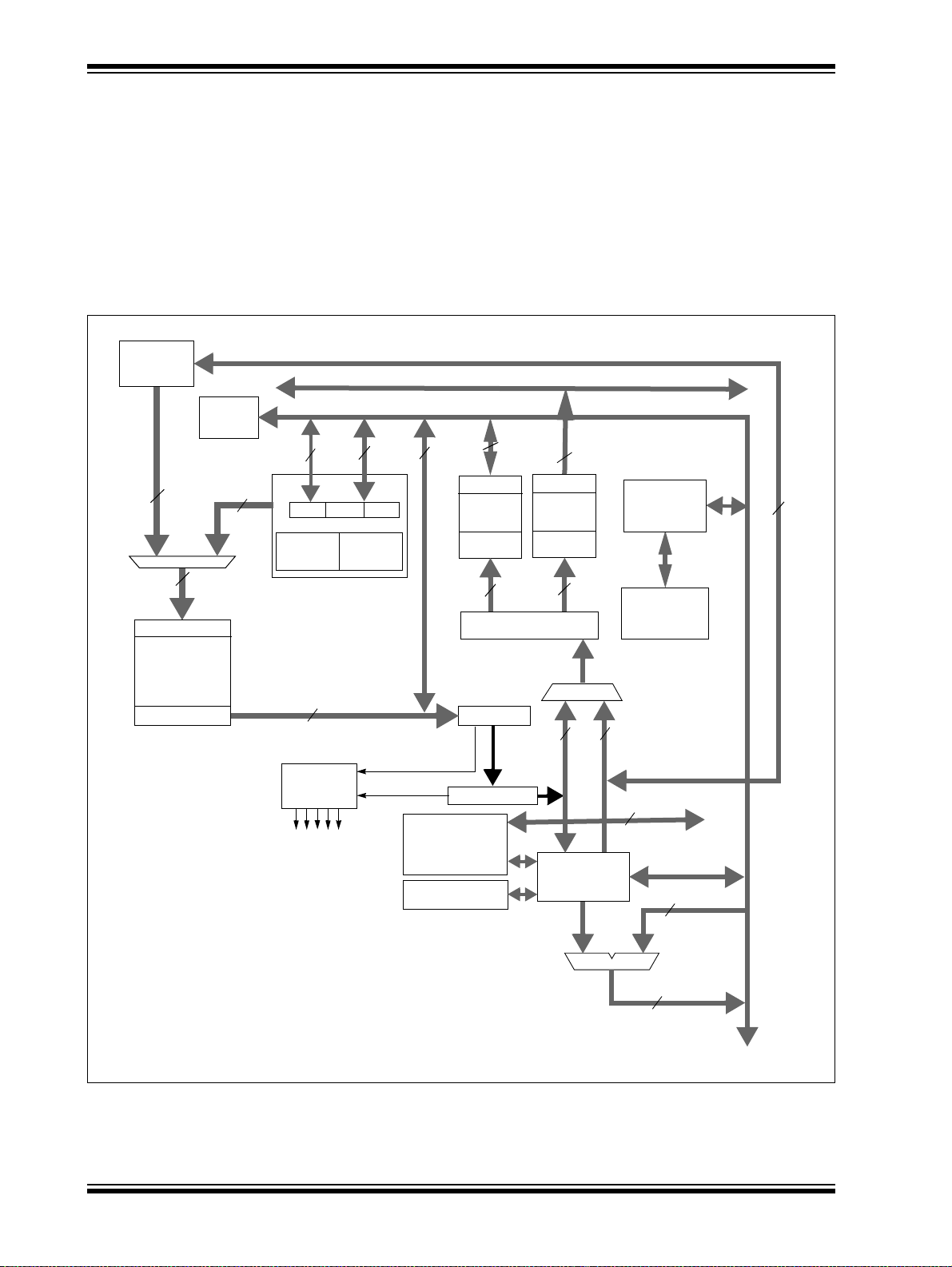

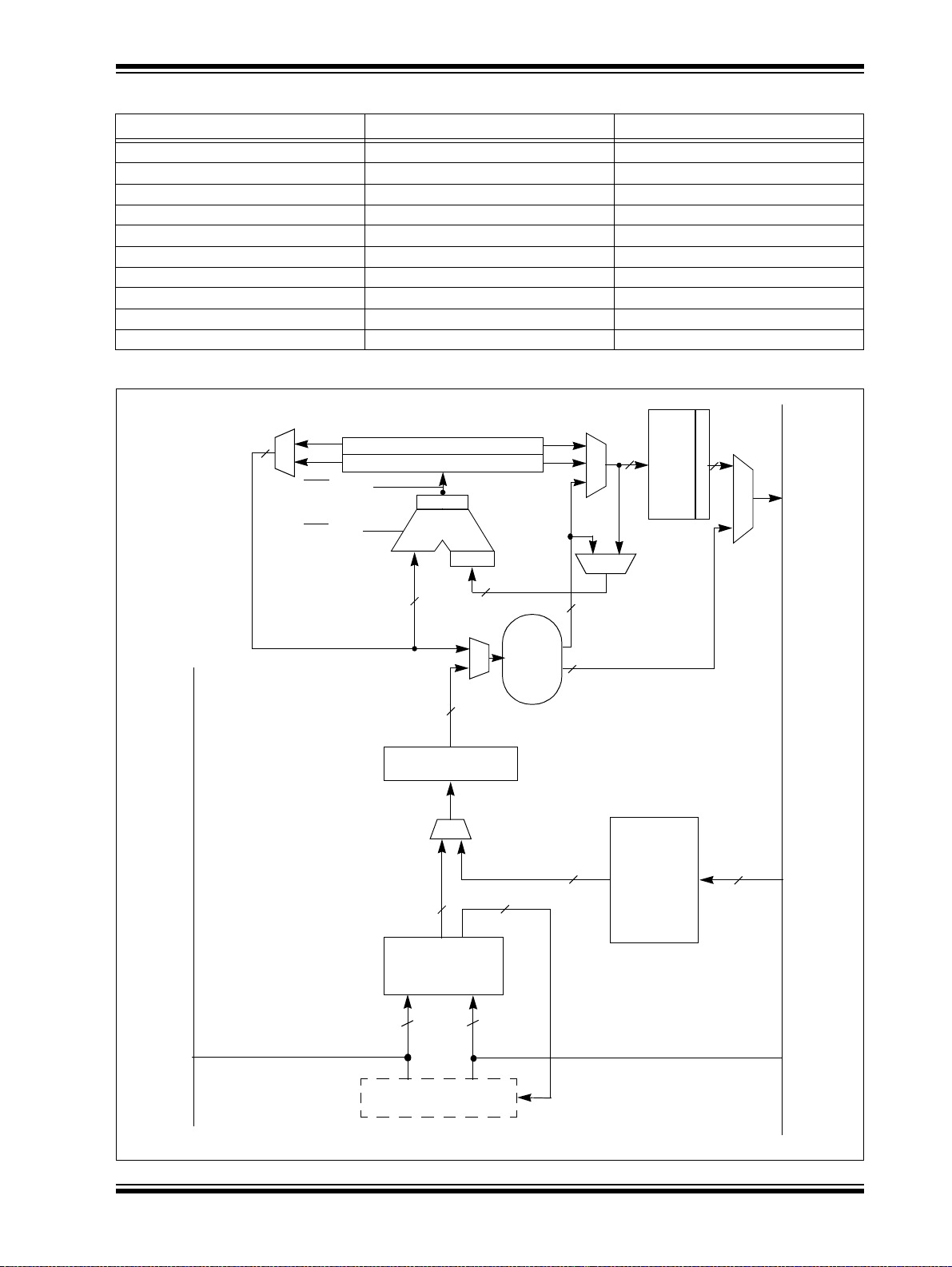

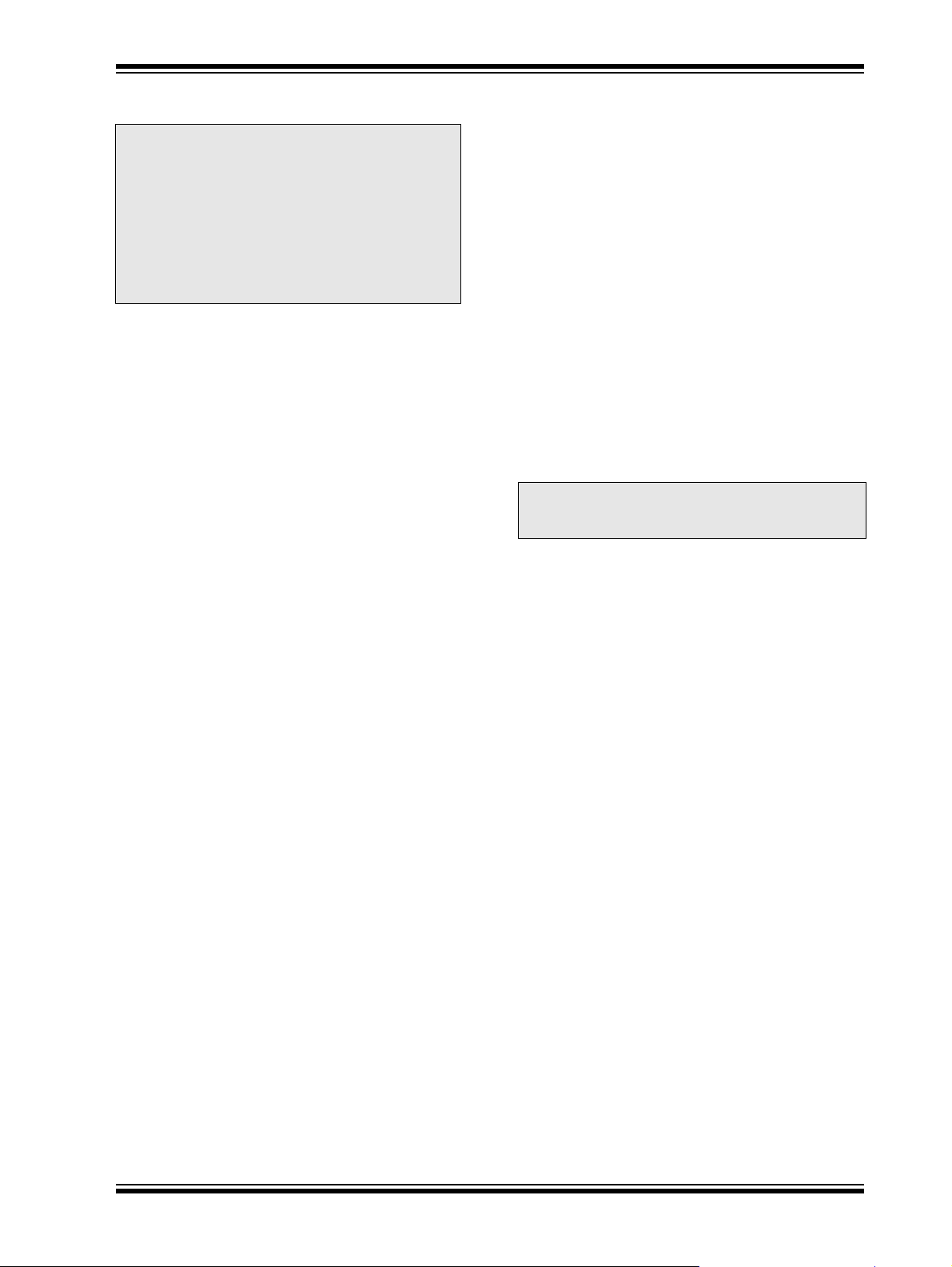

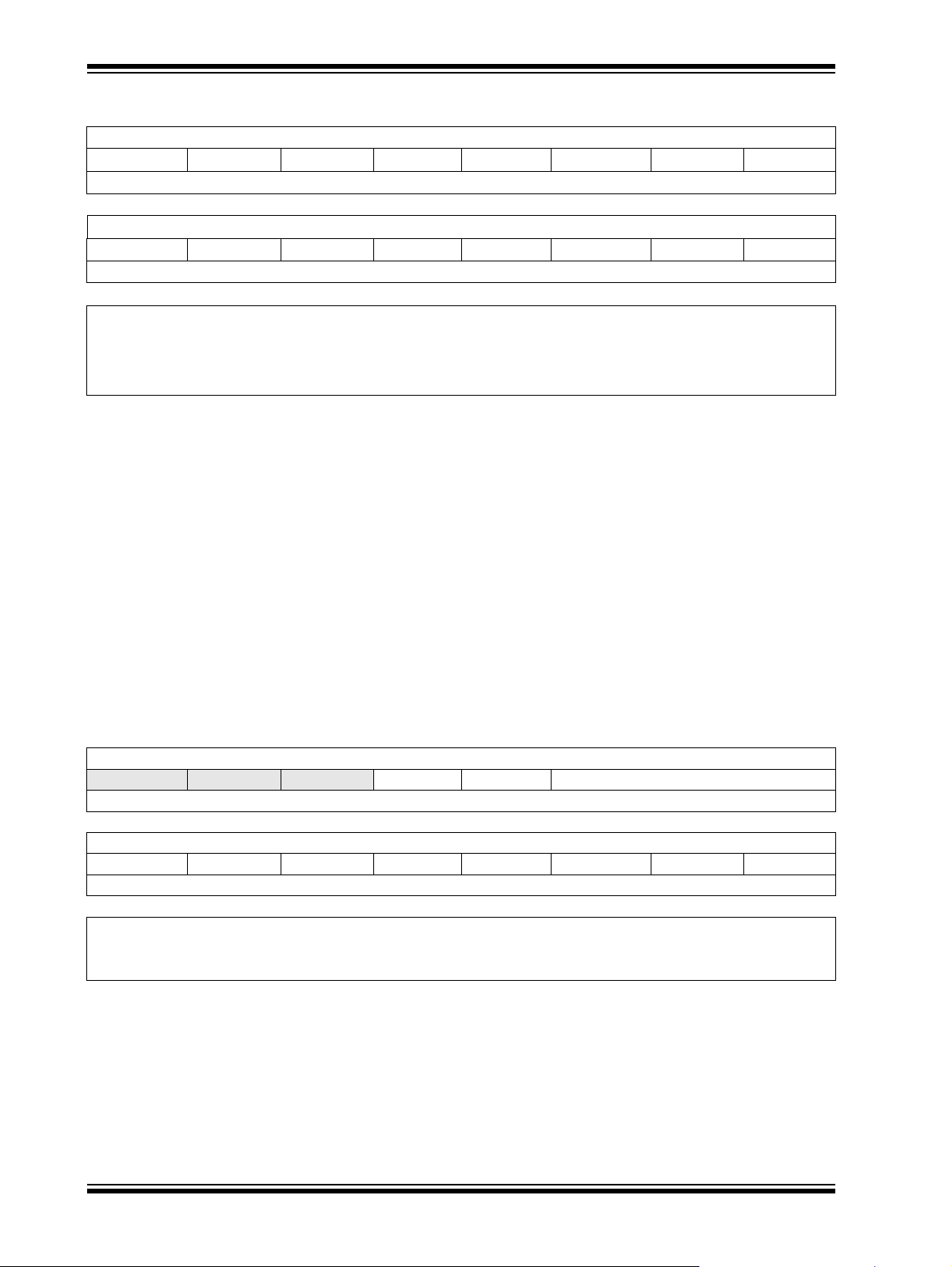

CPU 的框图如图 2-1 所示,dsPIC33FJ32MC302/304、

dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/

X04 的编程模型如图 2-2 所示。

2.2 数据寻址概述

数据空间可以作为 32K 字或 64 KB 寻址,并被分成两

块,称为 X 和 Y 数据存储区。每个存储区有各自独立的

地址发生单元 (Address Generation Unit, AGU)。

MCU 类指令只通过 X 存储空间 AGU 进行操作,可将整

个存储器映射作为一个线性数据空间访问。某些 DSP指

令通过 X 和 Y 的 AGU 进行操作以支持双操作数读操作,

这样会将数据地址空间分成两个部分。X 和 Y 数据空间

的边界视具体器件而定。

X 和 Y 地址空间都支持无开销循环缓冲区 (模寻址模

式)。模寻址省去了 DSP 算法的软件边界检查开销。此

外,X AGU 的循环寻址可以用于任何 MCU 类指令。X

AGU 还支持位反转寻址,大幅简化了基为 2 的 FFT 算

法对输入或输出数据的重新排序。

可以选择将数据存储空间的高 32 KB 映射到由 8 位程序

空间可视性页 (Program Space Visibility Page,

PSVPAG)寄存器定义的任何 16K 程序字边界内的程序

空间内。程序空间到数据空间的映射功能让任何指令都

能像访问数据空间一样访问程序空间。

2.3 DSP 引擎概述

DSP 引擎具有一个高速 17 位 x 17 位乘法器、一个 40

位 ALU、两个 40 位饱和累加器和一个 40 位双向桶形移

位寄存器。该桶形移位寄存器能在单个周期内将一个 40

位的值右移或左移最多 16 位。DSP 指令可以无缝地与

所有其他指令一起操作,且设计为能获得最佳实时性

能。MAC 指令和其他相关指令可以在同一个周期内,同

时完成从存储器中取两个数据操作数,将两个 W 寄存器

相乘并累加,且可选择使结果饱和。这要求 RAM 数据空

间对于这些指令拆分为两块,但对于所有其他指令保持

线性。数据空间分块是通过将某些工作寄存器专用于每

个地址空间,以透明和灵活的方式实现的。

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第 19 页

Page 22

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

2.4 MCU 的特性

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04

和 dsPIC33FJ128MCX02/X04 支持小数和整数的 16/16

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04

和 dsPIC33FJ128MCX02/X04 具有一个由 MCU ALU 和

DSP 引擎共用的 17 位 x 17 位单周期乘法器。此乘法器

可以进行有符号、无符号和混合符号的乘法运算。使用

17 位 x 17 位乘法器进行 16 位 x 16 位乘法运算不仅允

许您执行混合符号的乘法运算,而且对于 (-1.0) x (-1.0)

这样的特殊运算也可以得到准确结果。

位和32/16位除法运算。所有的除法指令都是迭代操作。

它们必须在一个 REPEAT 循环内执行,总执行时间为 19

个指令周期。在这 19 个周期的任一周期内可以中断除

法运算而不会丢失数据。

一个 40 位桶形移位寄存器用于在单个周期内将数据左

移或右移最多 16 位。 MCU 和 DSP 指令都可以使用该

桶形移位寄存器。

图 2-1: dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

的 CPU 内核框图

PSV 和表

数据访问

控制模块

地址锁存器

中断

控制器

8

23

23

23

PCU

程序计数器

堆栈

控制

逻辑

16

PCH PCL

循环

控制

逻辑

Y 数据总线

X 数据总线

16

16

数据锁存器

X RAM

地址

锁存器

地址发生器单元

数据锁存器

16

16

Y RAM

地址

锁存器

16

DMA

RAM

16

DMA

控制器

程序存储器

数据锁存器

地址总线

24

指令

译码和

控制

至各模块的

控制信号

指令寄存器

DSP 引擎

除法支持

ROM 锁存器

EA 多路开关

16

16

立即数数据

16 x 16

W 寄存器阵列

16 位 ALU

16

16

16

至外设模块

DS70291A_CN 第20 页 超前信息 2008 Microchip Technology Inc.

Page 23

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

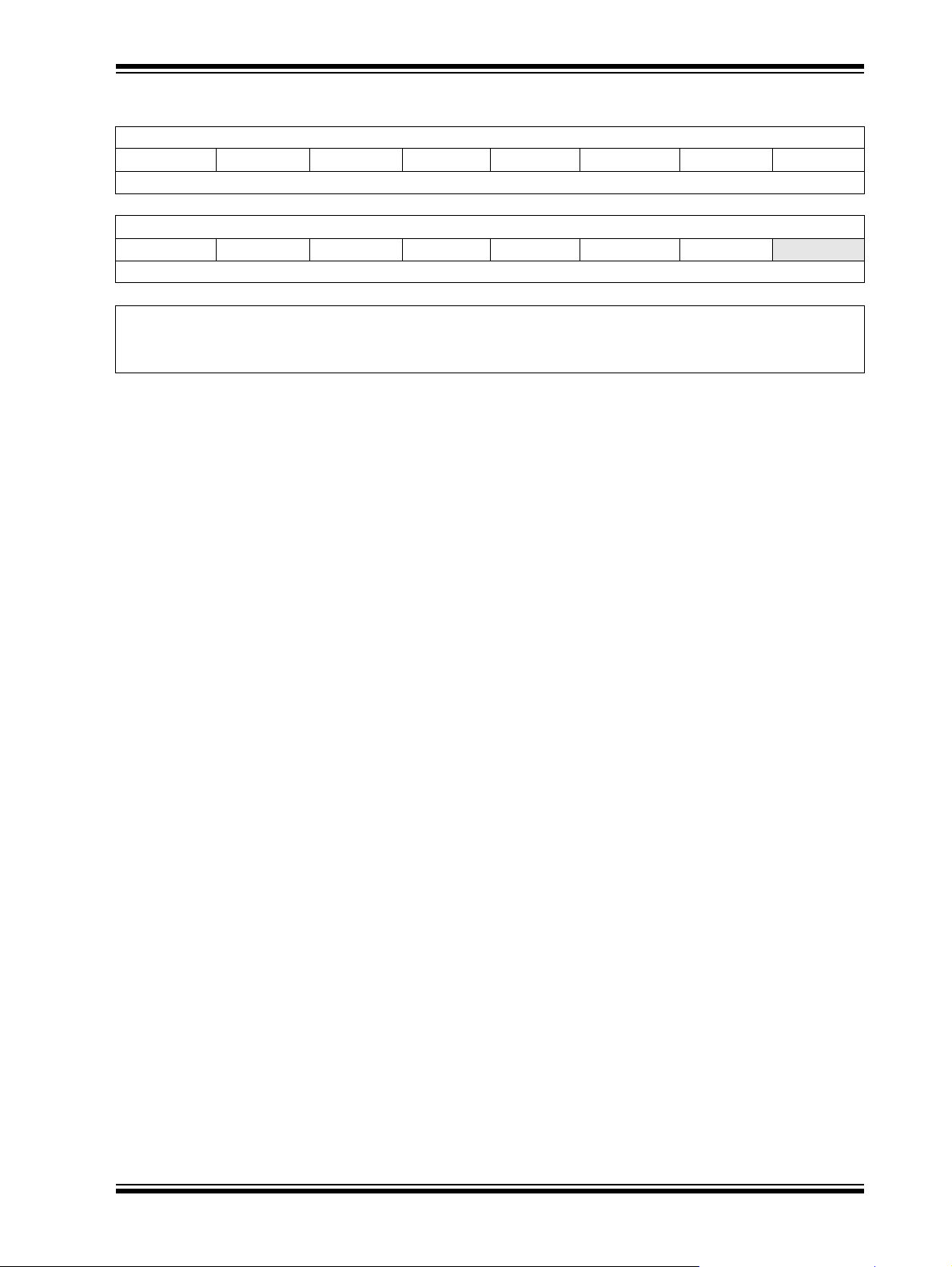

图 2-2: dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

的编程模型

D0D15

DSP 操作数

寄存器

DSP 地址

寄存器

W0/WREG

W1

W2

W3

W4

W5

W6

W7

W8

W9

W10

W11

W12/DSP 偏移量

W13/DSP 回写

W14/ 帧指针

W15/ 堆栈指针

工作寄存器

PUSH.S 影子寄存器

DO 影子寄存器

图注

DSP

累加器

PC22

7

22

22

TBLPAG

7

PSVPAG

AD39 AD0AD31

ACCA

ACCB

0

数据表页地址

0

程序空间可视性页地址

15

15

DOSTART

DOEND

SPLIM 堆栈指针限制寄存器

AD15

PC0

程序计数器

0

0

RCOUNT

DCOUNT

REPEAT 循环计数器

0

DO 循环计数器

0

DO 循环起始地址

DO 循环结束地址

15

CORCON

OA OB SA SB

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第 21 页

OAB SAB

SRH

DA DC

IPL2 IPL1

RA

IPL0 OV

SRL

0

内核控制寄存器

N

C

Z

状态寄存器

Page 24

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

2.5 CPU 控制寄存器

寄存器 2-1: SR:CPU 状态寄存器

R-0 R-0 R/C-0 R/C-0 R-0 R/C-0 R -0 R/W-0

OA OB SA

(1)

bit 15 bit 8

SB

(1)

OAB SAB DA DC

R/W-0

(3)

IPL<2:0>

R/W-0

(3)

(2)

R/W-0

(3)

R-0 R/W-0 R/W-0 R/W-0 R/W-0

RA N OV Z C

bit 7 bit 0

图注:

C = 只可清零位 R = 可读位 U = 未实现位,读为 0

S = 只可置 1 位 W = 可写位 -n = POR 时的值

1 = 置 10 = 清零 x = 未知

bit 15

OA: 累加器 A 溢出状态位

1 = 累加器 A 溢出

0 = 累加器 A 未溢出

bit 14

OB: 累加器 B 溢出状态位

1 = 累加器 B 溢出

0 = 累加器 B 未溢出

bit 13

SA:累加器 A 饱和 “粘住”状态位

(1)

1 = 累加器 A 饱和或在某时已经饱和

0 = 累加器 A 未饱和

bit 12

SB:累加器 B 饱和 “粘住”状态位

(1)

1 = 累加器 B 饱和或在某时已经饱和

0 = 累加器 B 未饱和

bit 11

OAB: OA || OB 组合的累加器溢出状态位

1 = 累加器 A 或 B 已经溢出

0 = 累加器 A 和 B 都未溢出

bit 10

SAB: SA || SB 组合的累加器饱和 (粘住)状态位

(4)

1 = 累加器 A 或 B 饱和或在过去某时已经饱和

0 = 累加器 A 和 B 都未饱和

bit 9

DA: DO 循环活动位

1 = 正在进行 DO 循环

0 = 不在进行 DO 循环

bit 8

DC:MCU ALU 半进位 / 借位标志位

1 = 结果的第 4 个低位 (对于字节大小的数据)或第 8 个低位 (对于字大小的数据)发生了进位

0 = 结果的第 4 个低位 (对于字节大小的数据)或第 8 个低位 (对于字大小的数据)未发生进位

注 1: 此位可被读取或清零 (但不能置 1)。

2: IPL<2:0> 位与 IPL<3> 位(CORCON<3>)组合形成 CPU 中断优先级。如果 IPL<3> = 1,那么括号中的

值表示 IPL。当 IPL<3> = 1 时,禁止用户中断。

3: 当 NSTDIS (INTCON1<15>) = 1 时, IPL<2:0> 状态位是只读的。

4: 此位可被读取或清零 (但不能置 1)。清零此位的同时将清零 SA 和 SB。

DS70291A_CN 第22 页 超前信息 2008 Microchip Technology Inc.

Page 25

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

寄存器 2-1: SR:CPU 状态寄存器 (续)

bit 7-5

bit 4

bit 3

bit 2

bit 1

bit 0

IPL<2:0>:CPU 中断优先级状态位

111 = CPU 中断优先级为 7 (15),禁止用户中断

110 = CPU 中断优先级为 6 (14)

101 = CPU 中断优先级为 5 (13)

100 = CPU 中断优先级为 4 (12)

011 = CPU 中断优先级为 3 (11)

010 = CPU 中断优先级为 2 (10)

001 = CPU 中断优先级为 1 (9)

000 = CPU 中断优先级为 0 (8)

RA: REPEAT 循环活动位

1 = 正在进行 REPEAT 循环

0 = 不在进行 REPEAT 循环

N:MCU ALU 负标志位

1 = 结果为负

0 = 结果为非负 (零或正值)

OV: MCU ALU 溢出标志位

此位用于有符号的算术运算 (以二进制补码方式进行) 。它表示量值上的溢出,这种溢出将导致符号

位改变状态。

1 = 有符号算术运算中发生溢出 (本次运算)

0 = 未发生溢出

Z:MCU ALU 全零标志位

1 = 影响 Z 位的任何运算在过去某时已将该位置 1

0 = 影响 Z 位的最近一次运算已将该位清零 (即运算结果非零)

C:MCU ALU 进位 / 借位

1 = 结果的最高位发生了进位

0 = 结果的最高位未发生进位

标志位

(2)

注 1: 此位可被读取或清零 (但不能置 1)。

2: IPL<2:0> 位与 IPL<3> 位(CORCON<3>)组合形成 CPU 中断优先级。如果 IPL<3> = 1,那么括号中的

值表示 IPL。当 IPL<3> = 1 时,禁止用户中断。

3: 当 NSTDIS (INTCON1<15>) = 1 时, IPL<2:0> 状态位是只读的。

4: 此位可被读取或清零 (但不能置 1)。清零此位的同时将清零 SA 和 SB。

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第 23 页

Page 26

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

寄存器 2-2: CORCON:内核控制寄存器

U-0 U-0 U-0 R/W-0 R/W-0 R-0 R-0 R-0

— — —USEDT

(1)

DL<2:0>

bit 15 bit 8

R/W-0 R/W-0 R/W-1 R/W-0 R/C-0 R/W-0 R/W-0 R/W-0

SATA SATB SATDW ACCSAT IPL3

(2)

PSV RND IF

bit 7 bit 0

图注:

C = 只可清零位

R = 可读位 W = 可写位 -n = POR 时的值 1 = 置 1

0 = 清零 x = 未知 U = 未实现位,读为 0

bit 15-13

bit 12

未实现:读为 0

US: DSP 乘法无符号 / 有符号控制位

1 = DSP 引擎执行无符号乘法运算

0 = DSP 引擎执行有符号乘法运算

bit 11

EDT: DO 循环提前终止控制位

(1)

1 = 在当前循环迭代结束时终止执行 DO 循环

0 = 无影响

bit 10-8

DL<2:0>:DO 循环嵌套层级状态位

111 = 正在进行 7 层 DO 循环嵌套

•

•

•

001 = 正在进行 1 层 DO 循环嵌套

000 = 无 DO 循环嵌套

bit 7

SATA: ACCA 饱和使能位

1 = 使能累加器 A 饱和

0 = 禁止累加器 A 饱和

bit 6

SATB: ACCB 饱和使能位

1 = 使能累加器 B 饱和

0 = 禁止累加器 B 饱和

bit 5

SATDW: DSP 引擎的数据空间写饱和使能位

1 = 使能数据空间写饱和

0 = 禁止数据空间写饱和

bit 4

ACCSAT: 累加器饱和模式选择位

1 = 9.31 饱和 (超饱和)

0 = 1.31 饱和 (正常饱和)

bit 3

IPL3:CPU 中断优先级状态位 3

(2)

1 = CPU 中断优先级大于 7

0 = CPU 中断优先级等于或小于 7

bit 2

PSV: 数据空间中程序空间可视性使能位

1 = 程序空间在数据空间中可视

0 = 程序空间在数据空间中不可视

注 1: 此位总是读为 0。

2: IPL3 位与 IPL<2:0> 位(SR<7:5>)组合形成 CPU 中断优先级。

DS70291A_CN 第24 页 超前信息 2008 Microchip Technology Inc.

Page 27

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

寄存器 2-2: CORCON:内核控制寄存器 (续)

bit 1

bit 0

注 1: 此位总是读为 0。

2: IPL3 位与 IPL<2:0> 位(SR<7:5>)组合形成 CPU 中断优先级。

RND: 舍入模式选择位

1 = 使能有偏 (常规)舍入

0 = 使能无偏 (收敛)舍入

IF: 整数或小数乘法器模式选择位

1 = 使能 DSP 乘法运算的整数模式

0 = 使能 DSP 乘法运算的小数模式

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第 25 页

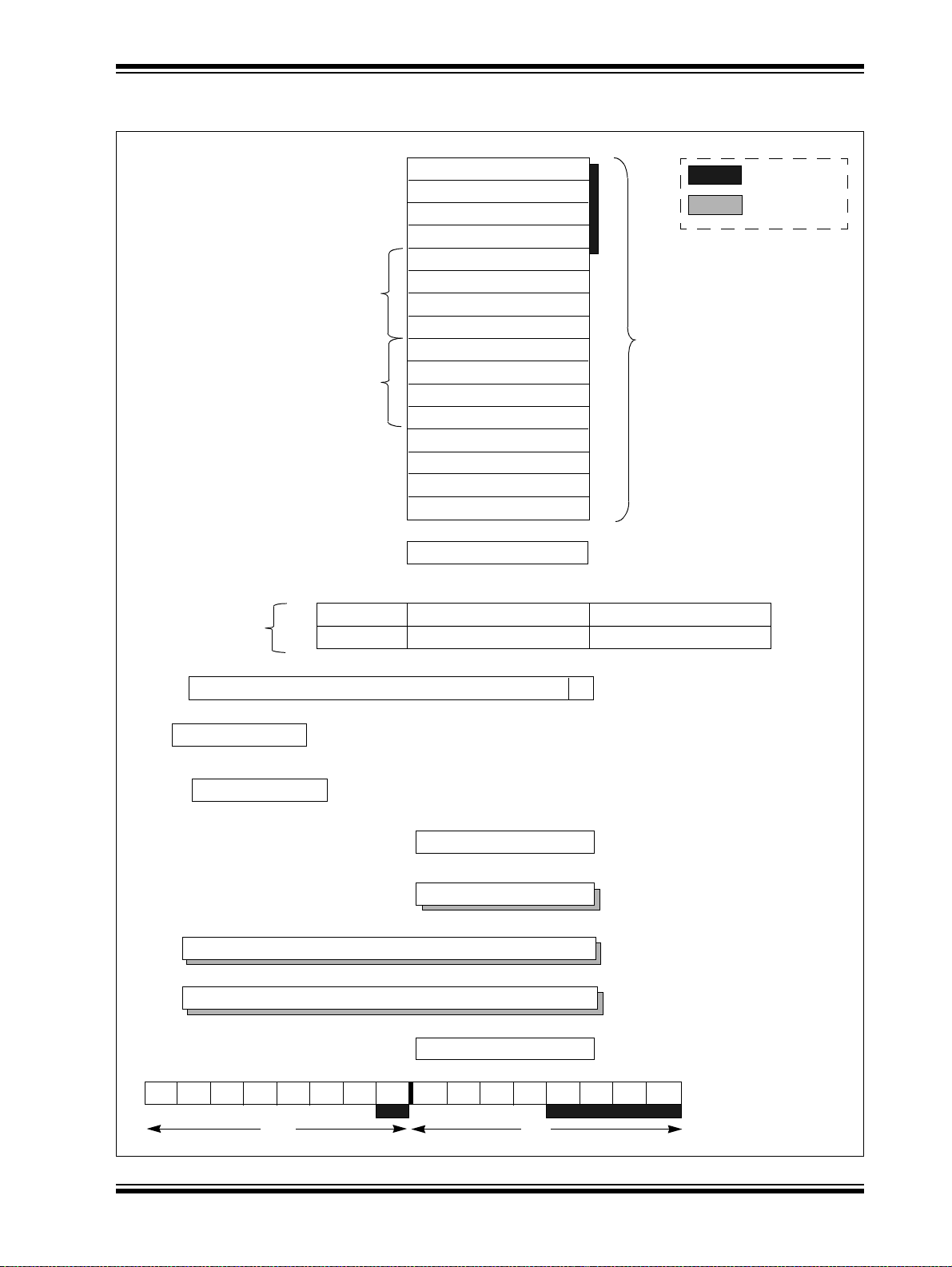

Page 28

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

2.6 算术逻辑单元 (ALU)

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04

和 dsPIC33FJ128MCX02/X04 的 ALU 为 16 位宽,可

进行加法、减法、移位和逻辑运算。除非另外指明,算

术运算实际上采用二进制补码形式进行。根据不同的运

算,ALU 可能会影响 SR 寄存器中的进位标志位(C)、

全零标志位(Z)、负标志位(N)、溢出标志位(OV)

和半进位状态位(DC)的值。在减法运算中, C 和 DC

状态位分别作为借位

根据所使用的指令模式,ALU 可执行 8 位或 16 位运算。

根据指令的寻址模式, ALU 运算的数据可以来自 W 寄

存器阵列或数据存储器。同样地,ALU 的输出数据可被

写入 W 寄存器阵列或数据存储单元。

有关每条指令所影响的 SR 位的信息,请参见

《dsPIC30F/33F 程序员参考手册》(DS70157B_CN)。

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04

和 dsPIC33FJ128MCX02/X04 的 CPU 融入了对乘法和

除法的硬件支持。它包含了专门的硬件乘法器以及支持

16 位除数除法的硬件。

2.6.1 乘法器

通过使用 DSP 引擎的高速 17 位 x 17 位乘法器, ALU

支持各种无符号、有符号或混合符号的 MCU 乘法运算:

• 16 位 x 16 位有符号

• 16 位 x 16 位无符号

• 16 位有符号 x 5 位 (立即数)无符号

• 16 位无符号 x 16 位无符号

• 16 位无符号 x 5 位 (立即数)无符号

• 16 位无符号 x 16 位有符号

• 8 位无符号 x 8 位无符号

标志位和半借位标志位。

2.6.2 除法器

除法模块支持以下数据长度的 32 位 /16 位和 16 位 /16

位有符号和无符号整数除法运算:

1. 32 位有符号 /16 位有符号除法

2. 32 位无符号 /16 位无符号除法

3. 16 位有符号 /16 位有符号除法

4. 16 位无符号 /16 位无符号除法

所有除法指令的商都被放在 W0 中,余数放在 W1 中。

16 位有符号和无符号 DIV 指令可为 16 位除数指定任一

W 寄存器 (Wn),为 32 位被除数指定任意连续的 W

寄存器对 (W(m + 1):Wm)。除法运算中处理除数的每

一位需要一个周期,因此执行 32 位 /16 位和 16 位 /16

位指令所需的周期数相同。

2.7 DSP 引擎

DSP 引擎由一个高速 17 位 x 17 位乘法器、一个桶形移

位寄存器和一个 40 位加法器 / 减法器 (两个目标累加

器、舍入逻辑和饱和逻辑)组成。

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04

和dsPIC33FJ128MCX02/X04采用单周期指令流架构;

因此 DSP 引擎的工作不能与 MCU 指令流同时进行。但

是,某些 MCU ALU 和 DSP 引擎资源可由同一条指令

(如 ED 和 EDAC)同时使用。

DSP 引擎还可以执行固有的不需要其他数据的累加器

-累加器操作。这些指令是 ADD、 SUB 和 NEG。

通过 CPU 内核控制寄存器 (CORCON)中的各个位,

可以对 DSP 引擎的操作进行多种选择,这些选择如下:

• 小数或整数 DSP 乘法 (IF)

• 有符号或无符号 DSP 乘法 (US)

• 常规或收敛舍入 (RND)

• ACCA 自动饱和使能 / 禁止 (SATA)

• ACCB 自动饱和使能 / 禁止 (SATB)

• 对于写数据存储器,自动饱和使能 / 禁止

(SATDW)

• 累加器饱和模式选择 (ACCSAT)

DSP 引擎的框图如图 2-3 所示。

DS70291A_CN 第26 页 超前信息 2008 Microchip Technology Inc.

Page 29

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

表 2-1: DSP 指令汇总

指令 代数运算 ACC 回写

CLR A = 0

ED A = (x – y)2

EDAC A = A + (x – y)2

MAC A = A + (x • y)

MAC A = A + x2

MOVSAC

A 中内容将不发生改变 有

MPY A = x • y

MPY A = x 2

MPY.N A = – x • y

MSC A = A – x • y

图 2-3: DSP 引擎框图

有

无

无

有

无

无

无

无

有

40

进位 / 借位输出

进位 / 借位输入

Y 数据总线

40 位累加器 A

40 位累加器 B

饱和

加法器

取补

40

40

符号扩展

33

40

桶形移位

寄存器

32

40

40

16

32

补零

舍入

逻辑

饱

16

和

X 数据总线

16

17 位

乘法器 / 定标器

16

至 / 来自 W 阵列

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第 27 页

16

Page 30

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

2.7.1 乘法器

17 位 x17 位乘法器可以进行有符号或无符号运算,其输

出经过定标器进行换算后可支持 1.31 小数 (Q31)或

32 位整数结果。无符号操作数经过零扩展后,送入乘法

器输入值的第 17 位。有符号操作数经过符号扩展后,送

入乘法器输入值的第 17 位。 17 位 x17 位乘法器 / 定标

器的输出是 33 位值,它将被符号扩展为 40 位。整型数

据的固有表示形式为有符号的二进制补码值,其中最高

有效位(MSb)定义为符号位。N 位二进制补码整数的

范围为 -2

N-1

到 2

N-1

– 1。

• 对于 16 位整数,数据范围为 -32768 (0x8000)

到 32767 (0x7FFF),包括 0 在内。

• 对于 32 位整数,数据范围为 -2,147,483,648

(0x8000 0000)到 2,147,483,647 (0x7FFF

FFFF)。

当乘法器配置为小数乘法时,数据表示为二进制补码小

数,其中 MSb 定义为符号位,小数点暗含在符号位之

后(QX 格式)。暗含小数点的 N 位二进制补码小数的

范围为 -1.0 到(1 – 2

1-N

)。对于 16 位小数, Q15 数

据范围为 -1.0(0x8000)到 0.999969482(0x7FFF),

包括 0 在内,其精度为 3.01518x10-5。在小数模式下,

16 x 16 乘法运算将产生 1.31 乘积,其精度为 4.65661

-10

x 10

。

同一个乘法器还用来支持 MCU 乘法指令,包括整数的

16 位有符号、无符号和混合符号乘法。

MUL 指令可以使用字节或字长度的操作数。字节操作数

将产生 16 位结果,而字操作数将产生 32 位结果,结果

存放在 W 寄存器阵列的指定寄存器中。

2.7.2 数据累加器和加法器 / 减法器

数据累加器包含一个 40 位加法器 / 减法器,它带有自动

符号扩展逻辑。它可以选择两个累加器 (A 或 B)之一

作为其累加前的源累加器和累加后的目标累加器。对于

ADD 和 LAC 指令,可选择通过桶形移位器在累加之前将

要累加或装入的数据进行换算。

2.7.2.1 加法器 / 减法器、溢出和饱和

加法器 / 减法器是一个 40 位加法器,一侧输入可以选择

为零,而另一侧输入可以是原数据或求补后的数据。

• 对于加法,进位 / 借位

输入是原数据 (没有求补的)。

• 对于减法,进位 / 借位

输入是求补后的数据。

输入为高电平有效,另一侧

输入为低电平有效,另一侧

加法器 / 减法器产生溢出状态位 SA/SB 和 OA/OB,这

些状态位被锁存在状态寄存器中并在其中得到反映。

• 从 bit 39 溢出:这是灾难性溢出,会破坏累加器的

符号位。

• 溢出到警戒位 (bit 32 到 bit 39):这是可恢复的

溢出。每当警戒位彼此不完全一致时,就将把这个

状态位置 1。

加法器有一个额外的饱和模块,如果选取的话,饱和模

块将控制累加器的数据饱和。饱和模块使用加法器的结

果、上述的溢出状态位、SAT<A:B>(CORCON<7:6>)

和 ACCSAT (CORCON<4>)模式控制位,来确定何

时饱和、达到何值为饱和。

状态寄存器中有 6 个支持饱和与溢出的位:

• OA:ACCA 溢出到警戒位

• OB:ACCB 溢出到警戒位

• SA:ACCA 已饱和 ( bit 31 溢出并饱和)

或者

ACCA 溢出到警戒位并饱和 (bit 39 溢出并饱和)

• SB:ACCB 已饱和 ( bit 31 溢出并饱和)

或者

ACCB 溢出到警戒位并饱和 (bit 39 溢出并饱和)

• OAB:OA 和 OB 的逻辑或 (OR)

• SAB:SA 和 SB 的逻辑或 (OR)

每次数据通过加法器 / 减法器,就会修改 OA 和 OB 位。

置 1 时,它们表明最近的操作已溢出到累加器警戒位

(bit 32到 bit 39)。如果 OA 和 OB 位置 1 而且 INTCON1

寄存器中相应的溢出陷阱标志允许位 (OVATE 和

OVBTE)置 1 的话,还可以选择用 OA 和 OB 位产生算

术警告陷阱 (见第 6.0 节 “中断控制器”)。这使得用

户应用程序能够立即采取措施,例如,校正系统增益。

每次数据通过加法器 / 减法器,就会修改 SA 和 SB 位,

但用户应用程序只能对它们进行清零。置 1 时,它们表

明累加器已溢出其最大范围(对于 32 位饱和是 bit 31,

而 40 位饱和是 bit 39),并发生饱和(如果饱和使能的

话)。如果没有使能饱和, SA 和 SB 置 1 默认为 bit 39

溢出,以此指示产生了灾难性溢出。如果 INTCON1 寄

存器中的 COVTE 位置 1,当饱和被禁止时, SA 和 SB

位将产生算术警告陷阱。

DS70291A_CN 第28 页 超前信息 2008 Microchip Technology Inc.

Page 31

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

在状态寄存器 (SR)中,对于溢出和饱和状态位,可

以将 OA 和 OB 的逻辑或形成 OAB 位,将 SA 和 SB 的

逻辑或形成 SAB 位。这样,只需检查状态寄存器中的一

个位,程序员就能判断是否有累加器溢出;检查状态寄

存器中的另一个位,就可以判断是否有累加器饱和。对

于通常要使用两个累加器的复数运算而言,这很有用。

器件支持三种饱和与溢出模式:

• bit 39 溢出和饱和:

当发生 bit 39 溢出和饱和时,饱和逻辑将最大的正

9.31 值(0x7FFFFFFFFF)或最小的负 9.31 值

(0x8000000000)装入目标累加器。 SA 或 SB 位

置 1 并保持直到被用户应用程序清零。这称为

“超饱和”,为错误数据或不可预期的算法问题

(例如,增益计算)提供了保护机制。

• bit 31 溢出和饱和:

当发生 bit 31 溢出和饱和时,饱和逻辑将最大的正

1.31 值(0x007FFFFFFF)或最小的负 1.31 值

(0x0080000000)装入目标累加器。 SA 或 SB 位

置 1 并保持直到被用户应用程序清零。当这种饱

和模式生效时,不使用警戒位,因此 OA、 OB 或

OAB 位不会被置 1。

• bit 39 灾难性溢出:

加法器的 bit 39 溢出状态位用来将 SA 或 SB 位置

1 ;这两位置 1 后,将保持状态直到被用户应用程

序清零。不进行饱和操作,允许累加器溢出 (破

坏其符号位)。如果 INTCON1 寄存器中的

COVTE 位置 1,灾难性溢出会导致一个陷阱异

常。

2.7.3 累加器 “回写”

MAC 类指令(MPY、MPY.N、ED 和 EDAC 除外)可以选

择将累加器高位字 (bit 16 到 bit 31)的舍入形式写入

数据存储空间,前提是当前指令不对该累加器进行操

作。通过 X 总线寻址组合的 X 和 Y 地址空间,执行回写

操作。支持以下寻址模式:

• W13,寄存器直接寻址:

非操作目标的累加器的舍入内容以 1.15 小数形式

写入 W13。

• [W13]+ = 2,执行后递增的寄存器间接寻址:

非操作目标的累加器的舍入内容以 1.15 小数形式

写入 W13 指向的地址。然后 W13 递增 2(对于字

写入)。

2.7.3.1 舍入逻辑

舍入逻辑是一个组合模块,在累加器写 (存储)过程

中执行常规的(有偏)或收敛的(无偏)舍入功能。舍

入模式由 CORCON 寄存器中 RND 位的状态决定。它

会产生一个 16 位的 1.15 数据值,该值被送到数据空间

写饱和逻辑。如果指令不指明舍入,就会存储一个截取

的 1.15 数据值,简单地丢弃低位字。

常规舍入取累加器的 bit 15,对它进行零扩展并将扩展

后的值加到 ACCxH 字 (累加器的 bit 16 到 bit 31)。

• 如果 ACCxL 字 (累加器的 bit 0 到 bit 15)在

0x8000 和 0xFFFF 之间 (包括 0x8000),则

ACCxH 递增 1。

• 如果 ACCxL 在 0x0000 和 0x7FFF 之间,则

ACCxH 不变。

此算法的结果经过一系列随机舍入操作,值会稍稍偏大

(正偏)。

除非 ACCxL 等于 0x8000,否则收敛的(或无偏)舍入

操作方式与常规舍入相同。在这种情况下,要对 ACCxH

的最低位 (累加器的 bit 16)进行检测:

• 如果它为 1, ACCxH 递增 1。

• 如果它为 0, ACCxH 不变。

假设 bit 16 本身是随机的,这样的机制将消除任何可

能累加的舍入偏差。

通过 X 总线,SAC 和 SAC.R 指令将目标累加器内容的截

取(SAC)或舍入 (SAC.R)形式存入数据存储空间

(这受数据饱和的影响,请参见第 2.7.3.2 节 “数据空

间写饱和”)。对于 MAC 类指令,累加器回写操作将以

同样的方式进行,通过 X 总线寻址组合的 MCU (X 和

Y)数据空间。对于此类指令,数据始终要进行舍入。

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第 29 页

Page 32

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

2.7.3.2 数据空间写饱和

除了加法器 / 减法器饱和,对数据空间进行写操作也会

饱和,但不会影响源累加器的内容。数据空间写饱和逻

辑块接受来自舍入逻辑块的一个 16 位的 1.15 小数值作

为输入,还接受来自源 (累加器)和 16 位舍入加法器

的溢出状态。这些输入经过组合用来选择适当的 1.15 小

数值作为输出,写入数据存储空间中。

如果 CORCON 寄存器中的 SATDW 位置 1,将检测(经

过舍入或截取后的)数据是否溢出,并进行相应的调整:

• 如果输入数据大于 0x007FFF,则写入存储器中的

数据被强制为最大的正 1.15 值, 0x7FFF。

• 如果输入数据小于 0xFF8000,则写入存储器中的

数据被强制为最小的负 1.15 值, 0x8000。

源累加器的最高位 (bit 39)用来决定被检测的操作数

的符号。

如果 CORCON 寄存器中的 SATDW 位没有置 1,则输

入数据都将通过,在任何情况下都不会被修改。

2.7.4 桶形移位寄存器

桶形移位寄存器在单个周期内可将数据算术或逻辑右移

或左移最多 16 位。源操作数可以是两个 DSP 累加器中

的任何一个或 X 总线(支持寄存器或存储器中数据的多

位移位)。

移位寄存器需要一个有符号二进制值,用来确定移位操

作的幅度 (位数)和方向。正值将操作数右移。负值则

将操作数左移。值为 0 则不改变操作数。

桶形移位寄存器为 40 位宽,于是,它为 DSP 移位操作

提供了 40 位的结果,而为 MCU 移位操作提供 16 位的

结果。来自 X 总线的数据在桶形移位寄存器中的存放方

式是:右移则数据存放在 bit 16 到 bit 31,左移则存放

在 bit 0 到 bit 15。

DS70291A_CN 第30 页 超前信息 2008 Microchip Technology Inc.

Page 33

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

3.0 存储器构成

注: 本数据手册总结了 dsPIC33FJ32MC302/

304、 dsPIC33FJ64MCX02/X04 和

dsPIC33FJ128MCX02/X04 系列器件的特

性。但是不应把本手册当作无所不包的参

考手册来使用。如需了解本数据手册的补

充信 息,请 参 考 “dsPIC33F Family

Reference Manual”的 “Section 4.

Program Memory”(DS70203),该文档

可从 Microchip 网站

(www.microchip.com)下载。

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04

和dsPIC33FJ128MCX02/X04架构具有独立的程序和数

据存储空间 / 总线。这一架构还允许在代码执行过程中

3.1 程序地址空间

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04

和dsPIC33FJ128MCX02/X04器件的程序存储空间可存

储 4M 个指令字。可通过 24 位值寻址这一空间, 24 位

值由程序执行过程中的 23 位程序计数器 (PC)或第

3.6 节 “程序存储空间与数据存储空间的接口”中所述

的表操作或数据空间重映射得到。

用户应用程序只能访问程序存储空间的低半地址范围

(0x000000 至 0x7FFFFF)。使 用 TBLRD/TBLWT 指令

时,情况有所不同,这两条指令使用 TBLPAG<7> 来允

许访问配置存储空间中的配置位和器件 ID。

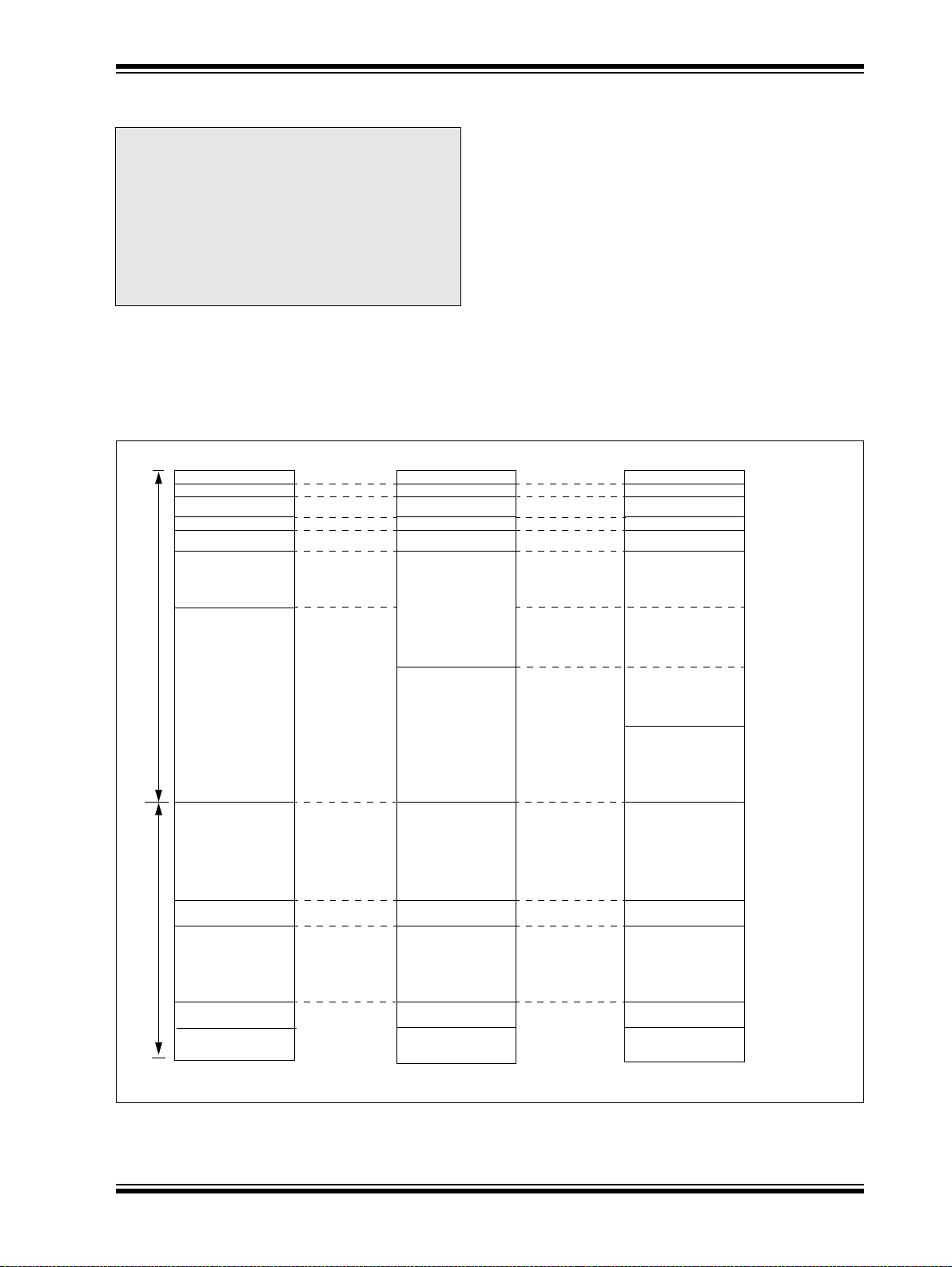

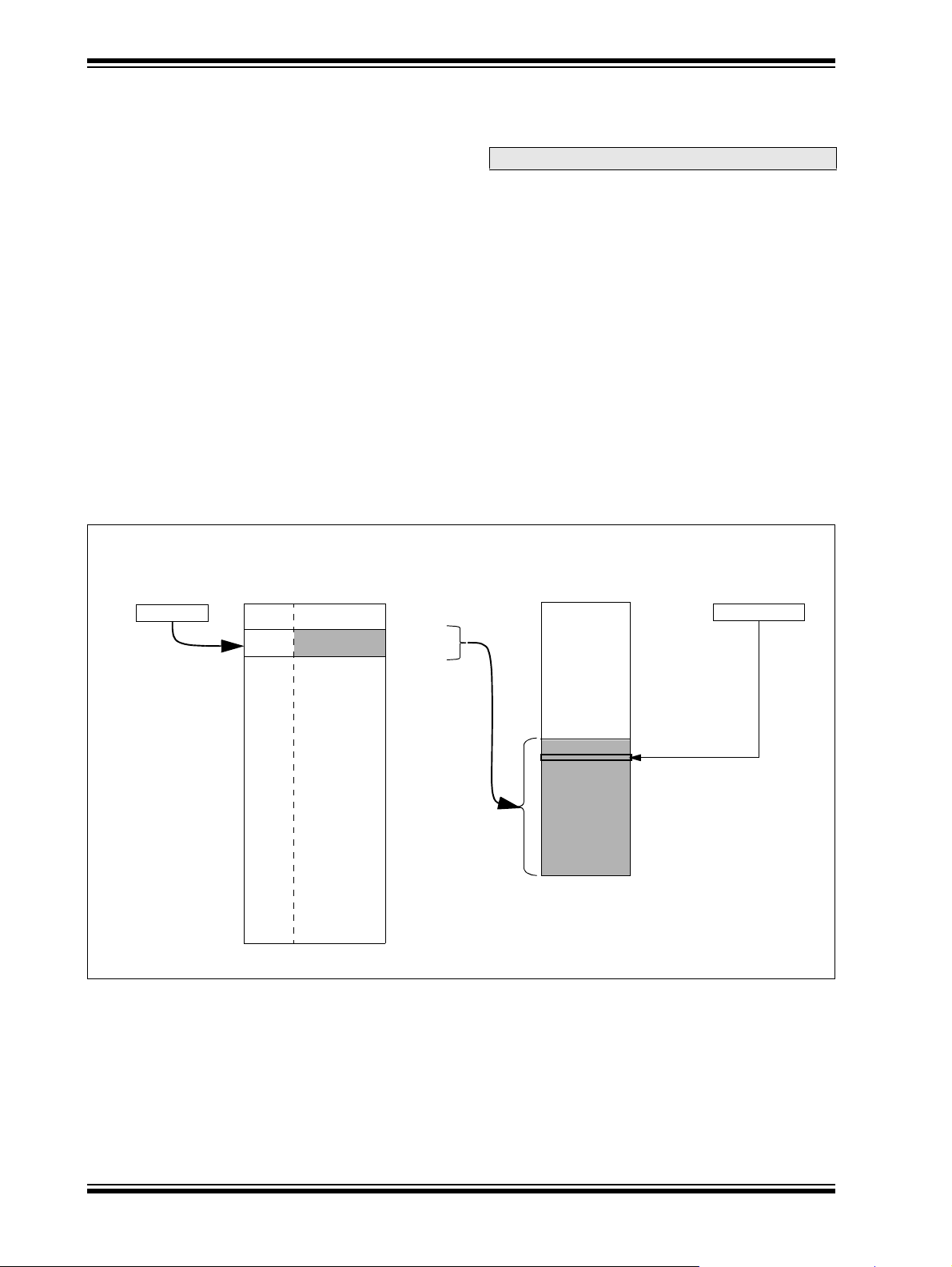

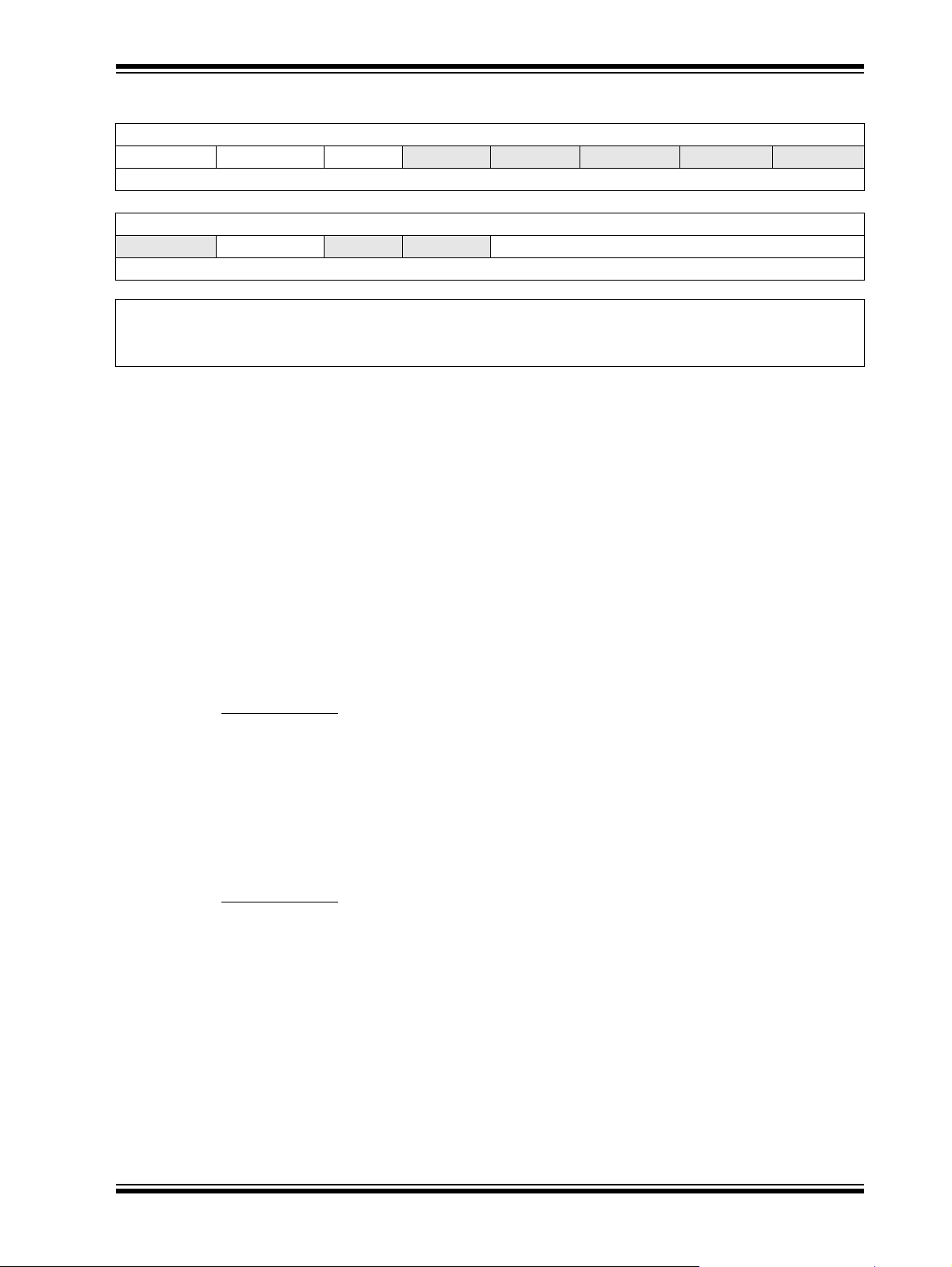

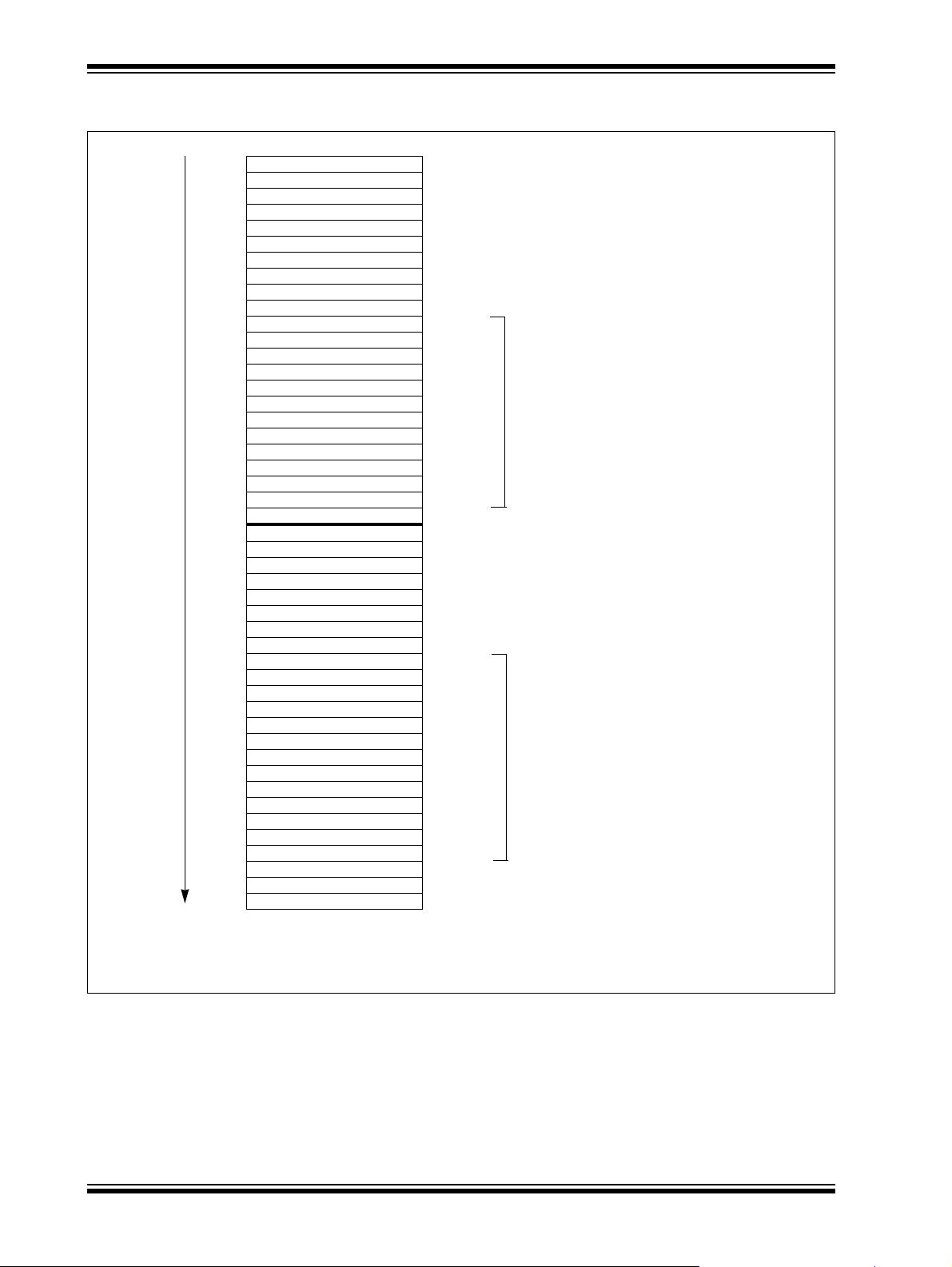

图 3-1 给出了 dsPIC33FJ32MC302/304、

dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/

X04 器件的程序存储器映射。

从数据空间直接访问程序存储器。

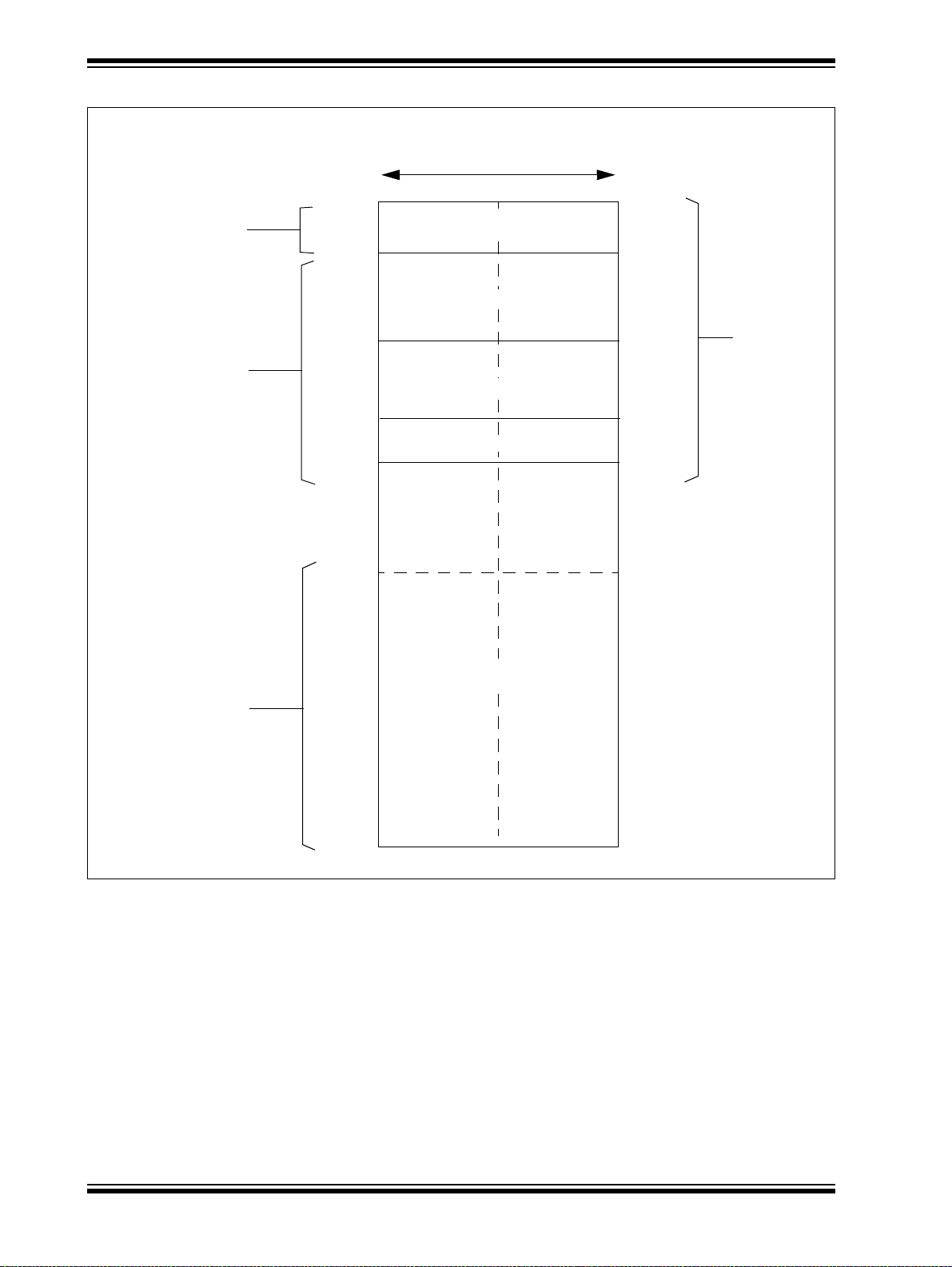

图 3-1: dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

器件的程序存储器映射

dsPIC33FJ32MC302/304

GOTO 指令

复位地址

中断向量表

保留

备用向量表

用户闪存

程序存储空间

(11264 指令字)

用户存储空间

未实现

(读为 0)

dsPIC33FJ64MCX02/X04

GOTO 指令

复位地址

中断向量表

保留

备用向量表

用户闪存

程序存储空间

(22016 指令字)

未实现

(读为 0)

dsPIC33FJ128MCX02/X04

GOTO 指令

复位地址

中断向量表

保留

备用向量表

用户闪存

程序存储空间

(44032 指令字)

未实现

(读为 0)

0x000000

0x000002

0X000004

0x0000FE

0x000100

0X000104

0X0001FE

0X000200

0X0057FE

0X005800

0X00ABFE

0X00AC00

0X0157FE

0X015800

0X7FFFFE

0x800000

保留

器件配置

寄存器

配置存储空间

注: 存储区大小未按比例绘制。

保留

DEVID (2)

保留

保留

器件配置

寄存器

保留

DEVID (2)

保留

保留

器件配置

寄存器

保留

DEVID (2)

保留

0xF7FFFE

0xF80000

0xF80017

0xF80018

0xFEFFFE

0xFF0000

0xFF0002

0XFFFFFE

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第 31 页

Page 34

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

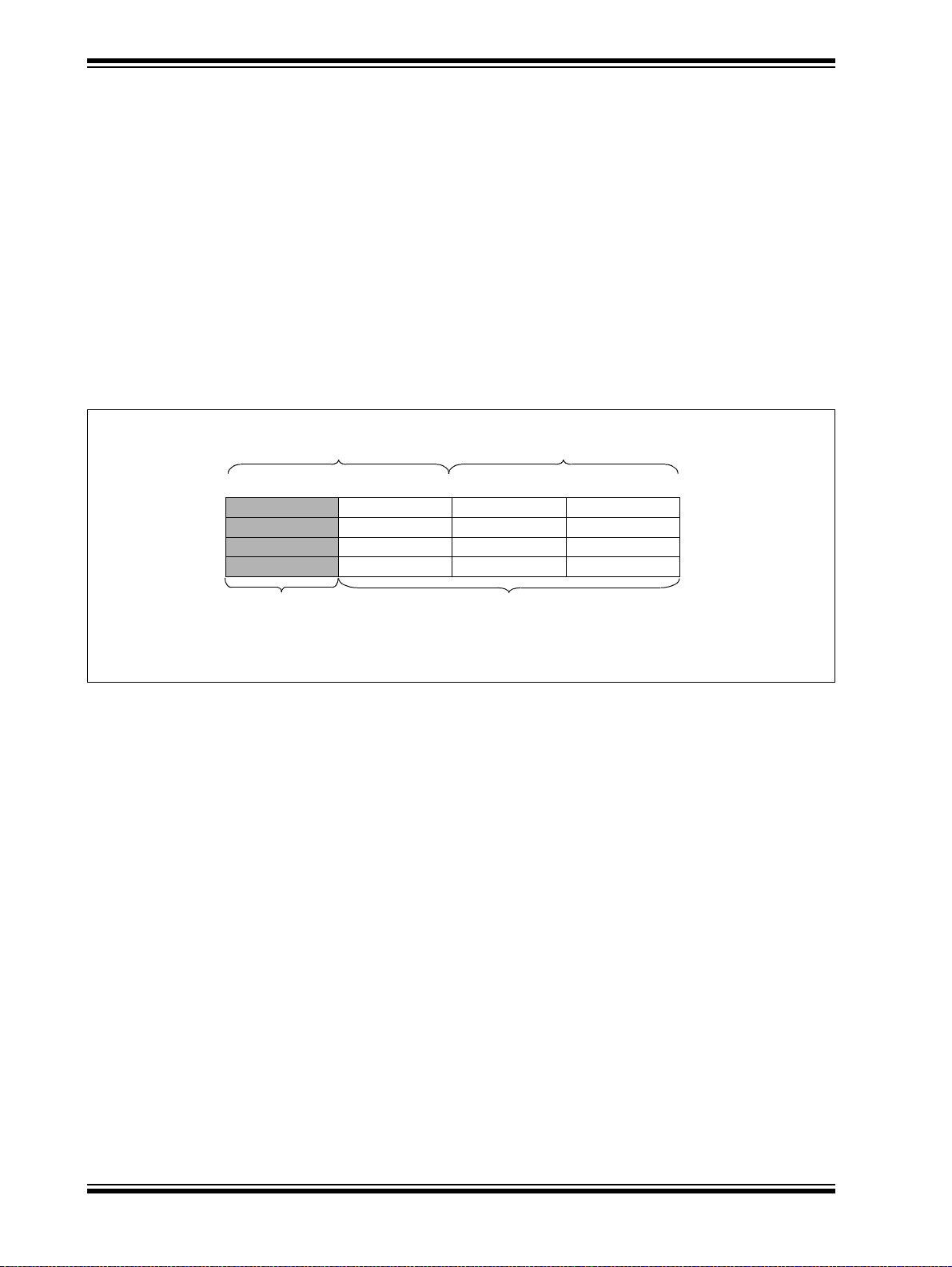

3.1.1 程序存储器构成

程序存储空间由可字寻址的块构成。虽然它被视为 24位

宽,但将程序存储器的每个地址视作一个低位字和一个

高位字的组合更加合理,其中高位字的高字节部分没有

实现。低位字的地址始终为偶数,而高位字的地址为奇

数(图3-2)。

程序存储器地址始终在低位字处按字对齐,并且在代码

执行过程中地址将递增或递减 2。这种寻址模式与数据

存储空间寻址兼容,且为访问程序存储空间中的数据提

供了可能。

3.1.2 中断向量和陷阱向量

所有 dsPIC33FJ32MC302/304、dsPIC33FJ64MCX02/

X04 和 dsPIC33FJ128MCX02/X04 器件中 0x00000 和

0x000200 之间的地址空间都是保留的,用来存储硬编

图 3-2: 程序存储器构成

msw

地址 (lsw 地址)

0x000001

0x000003

0x000005

0x000007

最高有效字

23

00000000

00000000

00000000

00000000

码的程序执行向量。提供了一个硬件复位向量将代码执

行从器件复位时 PC 的默认值重定向到代码实际起始

处。用户应用程序可在地址 0x000000 处编写一条 GOTO

指令以将代码的实际起始地址设置为 0x000002。

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04

和dsPIC33FJ128MCX02/X04器件也具有两个中断向量

表,地址分别为从 0x000004 到 0x0000FF 和 0x000100

到 0x0001FF。这两个中断向量表允许使用不同的中断

服务程序(Interrupt Service Routines,ISR)处理器件

的每个中断源。关于中断向量表更详细的讨论,请参见

第 6.1 节 “中断向量表”。

最低有效字

PC 地址

0816

0x000000

0x000002

0x000004

0x000006

程序存储器

“虚拟”字节

(读为 0)

指令宽度

DS70291A_CN 第32 页 超前信息 2008 Microchip Technology Inc.

Page 35

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

3.2 数据地址空间

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04

和 dsPIC33FJ128MCX02/X04 的 CPU 具有独立的 16

位宽数据存储空间。使用独立的地址发生单元(AGU)

对数据空间执行读写操作。数据存储器映射如图 3-4 所

示。

数据存储空间中的所有有效地址 (Effective Addresse,

EA)均为 16 位宽,并且指向数据空间内的字节。这种

构成方式使得数据空间的地址范围为 64 KB 或 32K 字。

数据存储空间的低半地址区 (即当 EA<15> = 0 时)用

作实现的存储地址,而高半地址区(EA<15> = 1)则保

留为程序空间可视性(Program Space Visibility,PSV)

区域 (见第 3.6.3 节 “使用程序空间可视性读程序存储

器中的数据”)。

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04

和 dsPIC33FJ128MCX02/X04 器件实现最大 16 KB 的

数据存储器。如果 EA 指向了该区域以外的存储单元,

则将返回一个全零的字或字节。

3.2.1 数据空间宽度

数据存储空间由可字节寻址的 16 位宽的块构成。在数

据存储器和寄存器中的数据是以16 位字为单位对齐的,

但所有数据空间 EA 都将解析为字节。每个字的低字节

(Least Significant Byte,LSB)部分具有偶地址,而高

字节 (Most Significant Byte, MSB)部分则具有奇地

址。

3.2.2 数据存储器构成和对齐方式

为维持与 PIC

空间的使用效率,dsPIC33FJ32MC302/304、

dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/

X04 的指令集同时支持字和字节操作。字节访问会在内

部对按字对齐的存储空间的所有有效地址计算进行调

整。例如,对于执行后修改寄存器间接寻址模式 [Ws++]

的结果,字节操作时,内核将其识别为值 Ws + 1,而 字

操作时,内核将其识别为值 Ws + 2。

使用任何 EA 的 LSB 来确定要选取的字节,数据字节读

取将读取包含字节的整个字。选定的字节被放在数据路

径的 LSB 处。这就是说,数据存储器和寄存器被组织为

两个并行的字节宽的实体,它们共享 (字)地址译码,

但写入线独立。数据字节写操作只写入阵列或寄存器中

与字节地址匹配的那一侧。

®

MCU 器件的后向兼容性和提高数据存储

所有字访问必须按偶地址对齐。不支持不对齐的字数据

取操作,所以在混合字节和字操作时,或者从 8 位 MCU

代码移植时,必须要小心。如果试图进行不对齐的读或

写操作,将产生地址错误陷阱。如果在读操作时产生错

误,正在执行的指令将完成。而如果在写操作时产生错

误,指令仍将执行,但不会进行写入。无论是哪种情况

都将执行陷阱,从而允许系统和 / 或用户应用程序能够

检查地址错误发生之前的机器状态。

所有装入任何 W 寄存器的字节都将装入 W 寄存器的低

字节 (LSB), W 寄存器的高字节 (MSB)不变。

提供了一条符号扩展(SE)指令,允许用户应用程序把

8 位有符号数据转换为 16 位有符号值。或者,对于 16

位无符号数据,用户应用程序可以通过在适当地址处执

行一条零扩展 (ZE)指令清零任何 W 寄存器的 MSB。

3.2.3 SFR 空间

Near 数据空间的前 2KB 存储单元 (从 0x0000 到

0x07FF)主要被特殊功能寄存器(Special Function

Registers, SFR)占 用。 dsPIC33FJ32MC302/304、

dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/

X04 的内核和外设模块使用这些寄存器来控制器件的工

作。

SFR 分布在受其控制的模块中,通常一个模块会使用一

组 SFR。大部分 SFR 空间包含未用的地址;它们读为

0。

注: 不同器件的实际外设功能集和中断也有所

不同。请参见相应器件的数据表和引脚图

了解特定器件的信息。

3.2.4 NEAR 数据空间

在 0x0000 和 0x1FFF 之间的 8 KB 区域被称为 near 数

据空间。可以使用所有存储器直接寻址指令中的 13 位

绝对地址字段直接寻址这一空间中的存储单元。此外,

还可以使用 MOV 指令寻址整个数据空间,MOV 指令支持

使用 16 位地址字段的存储器直接寻址模式或使用工

作寄存器作为地址指针的间接寻址模式。

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第 33 页

Page 36

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

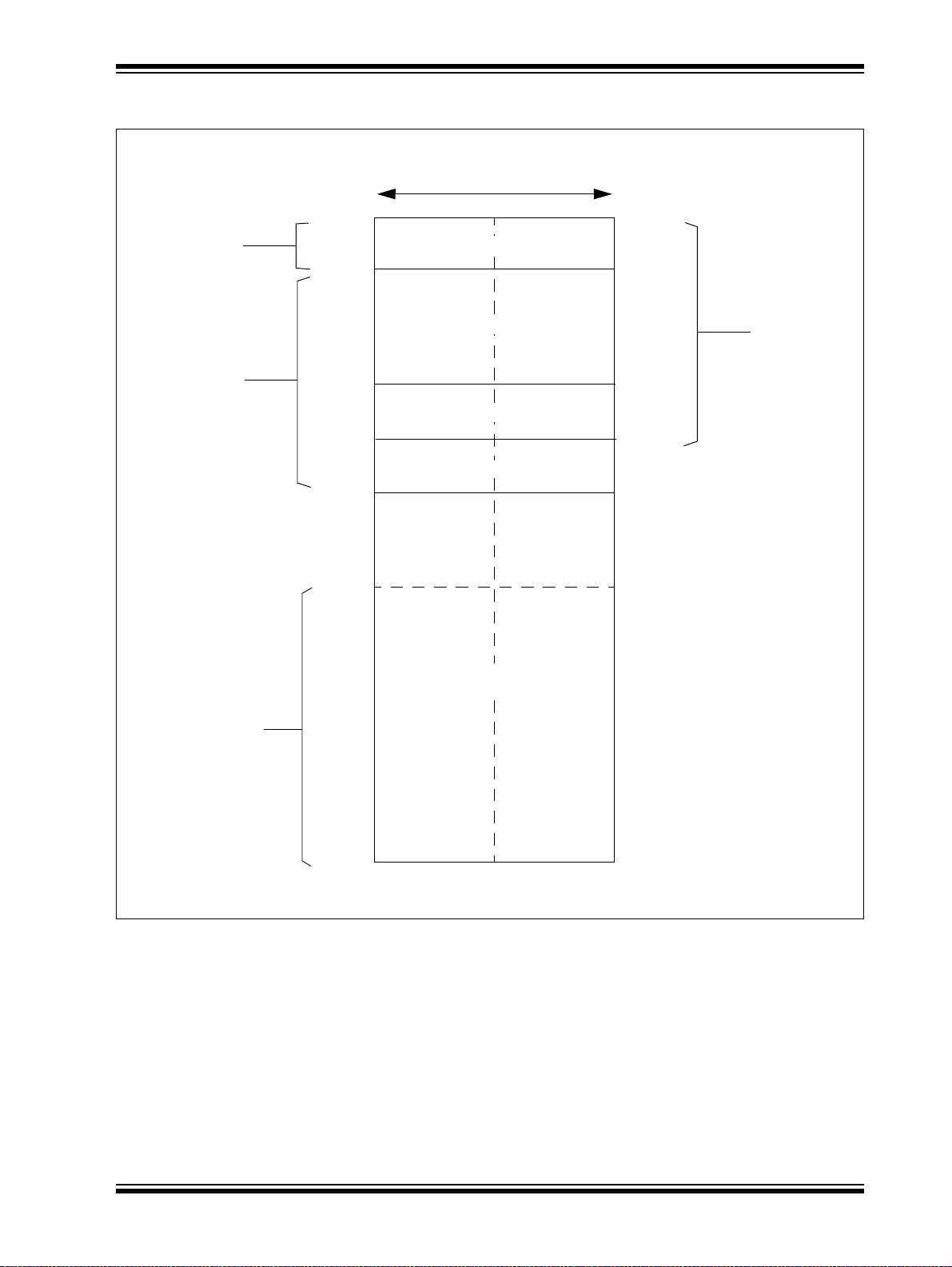

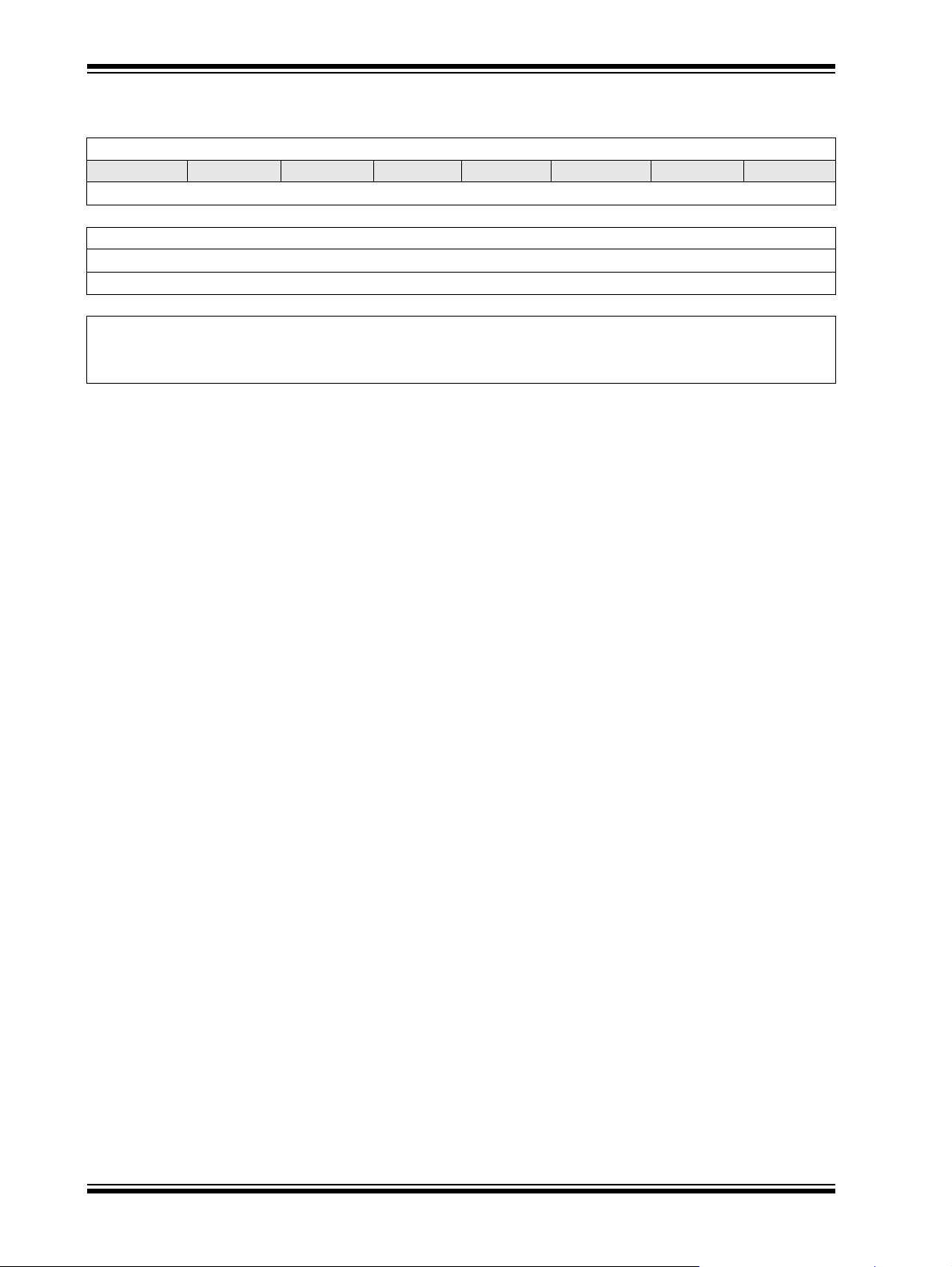

图 3-3:带4 KB RAM 的 dsPIC33FJ32MC302/304 器件的数据存储器映射

2 KB

SFR 空间

4 KB

SRAM 空间

MSB

地址

0x0001

0x07FF

0x0801

0x0FFF

0x1001

0x13FF

0x1401

0x17FF

0x1801

0x8001 0x8000

16 位

LSBMSB

SFR 空间

X 数据 RAM(X)

Y 数据 RAM(Y)

DMA RAM

LSB

地址

0x0000

0x07FE

0x0800

0x0FFE

0x1000

0x13FE

0x1400

0x17FE

0x1800

6 KB

Near

数据

空间

可选择

映射到

程序存

储器

0xFFFF

X 数据

未实现(X)

0xFFFE

DS70291A_CN 第34 页 超前信息 2008 Microchip Technology Inc.

Page 37

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

图 3-4:带8 KB RAM 的 dsPIC33FJ128MC202/204 和 dsPIC33FJ64MC202/204 器件的数据

存储器映射

2 KB

SFR 空间

8 KB

SRAM 空间

MSB

地址

0x0001

0x07FF

0x0801

0x17FF

0x1801

0x1FFF

0x2001

0x27FF 0x27FE

0x8001

16 位

LSBMSB

SFR 空间

X 数据 RAM(X)

Y 数据 RAM(Y)

DMA RAM

LSB

地址

0x0000

0x07FE

0x0800

0x17FE

0x1800

0x1FFE

0x2000

0x28000x2801

0x8000

8 KB

Near

数据

空间

可选择

映射到

程序存

储器

0xFFFF

X 数据

未实现(X)

0xFFFE

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第 35 页

Page 38

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

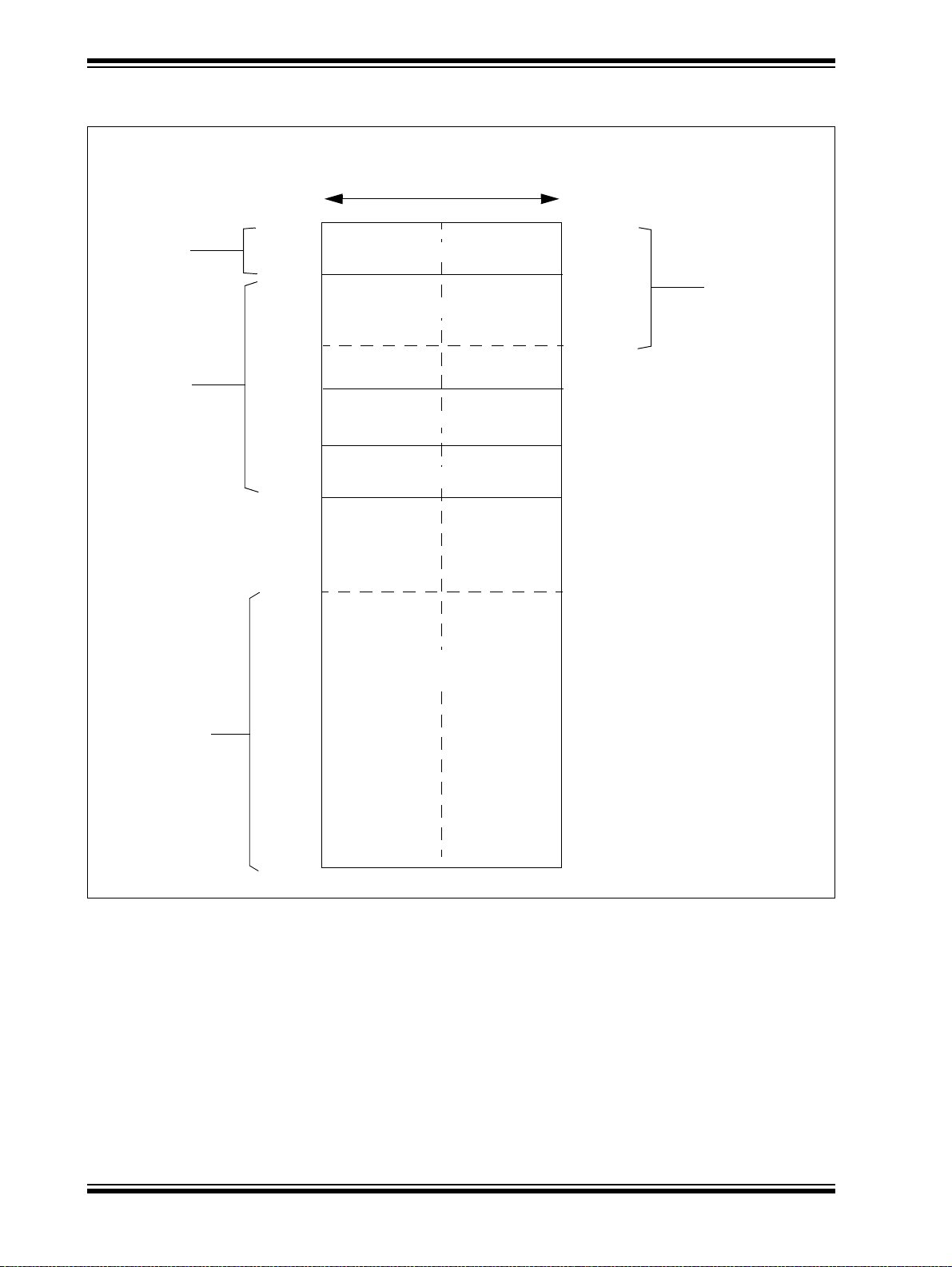

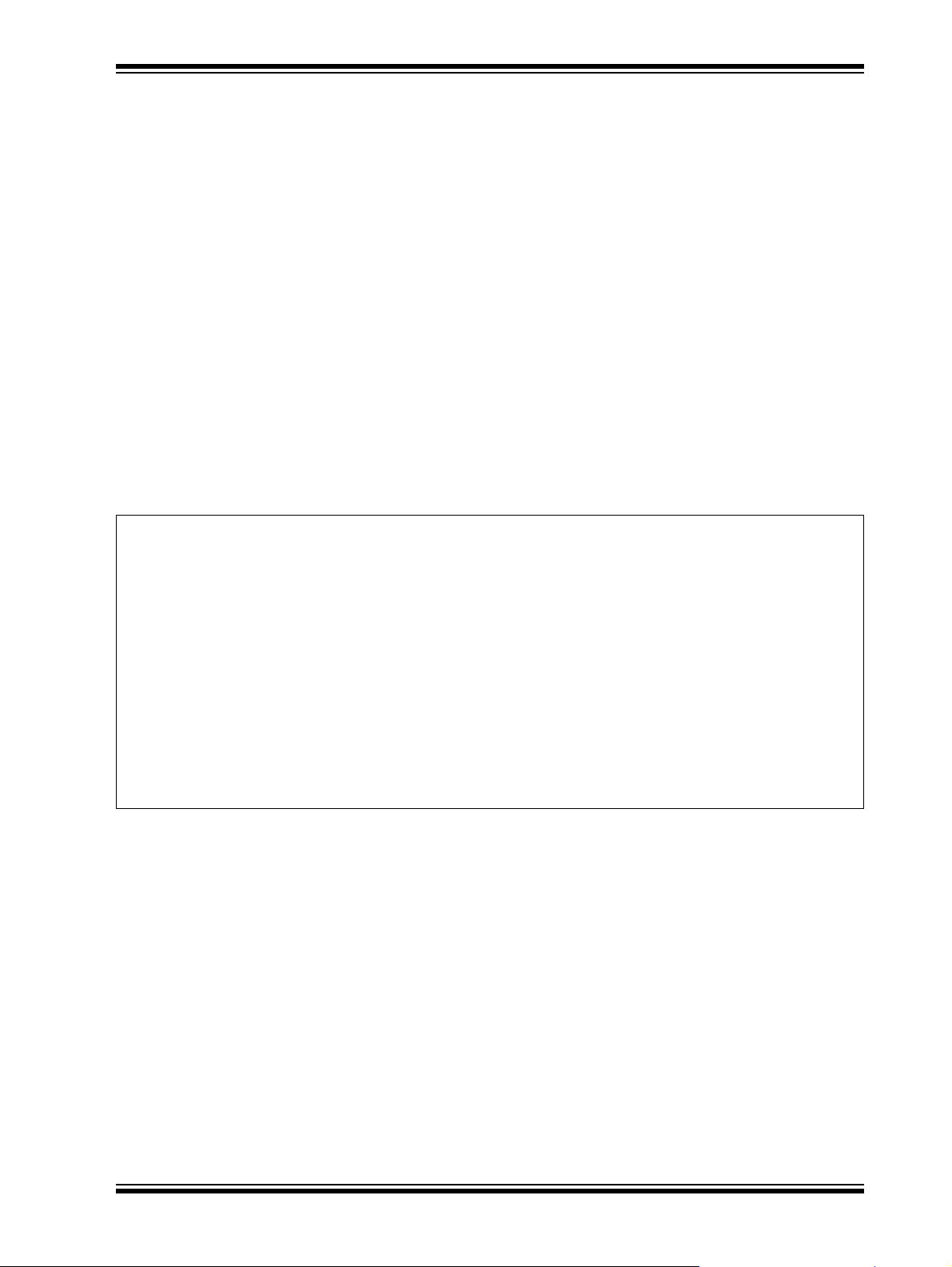

图 3-5:带16 KB RAM 的 dsPIC33FJ128MC802/804 和 dsPIC33FJ64MC802/804 器件的数

据存储器映射

2 KB

SFR 空间

16 KB

SRAM 空间

MSB

地址

0x0001

0x07FF

0x0801

0x1FFF

0x27FF

0x2801

0x3FFF

0x4001

0x47FF 0x47FE

0x8001

16 位

LSBMSB

SFR 空间

X 数据 RAM(X)

Y 数据 RAM(Y)

DMA RAM

LSB

地址

0x0000

0x07FE

0x0800

0x1FFE

0x27FE

0x2800

0x3FFE

0x4000

0x48000x4801

0x8000

8 KB

Near

数据

空间

可选择

映射到

程序存

储器

0xFFFF

X 数据

未实现(X)

0xFFFE

DS70291A_CN 第36 页 超前信息 2008 Microchip Technology Inc.

Page 39

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

3.2.5 X 和 Y 数据空间

内核有两个数据空间 X 和 Y。这些数据空间可以看作是

独立的(对于一些 DSP 指令),或者看作是统一的线性

地址范围 (对于 MCU 指令)。使用两个地址发生单元

(AGU)和独立的数据总线来访问这两个数据空间。此

特性允许某些指令同时从 RAM 中取两个字,因此提高

了某些 DSP 算法的执行效率,如有限冲激响应(Finite

Impulse Response,FIR)滤波算法和快速傅立叶变换

(Fast Fourier Transform, FFT)。

X 数据空间可用于所有指令,并且支持所有寻址模式。

X 数据空间的读 / 写数据总线相互独立。所有将数据空

间视为组合的 X 和 Y 地址空间的指令均将 X 读数据总线

作为读数据路径。X 读数据总线也可为双操作数 DSP 指

令(MAC 类)的 X 数据预取路径。

MAC 类指令(CLR、ED、EDAC、MAC、MOVSAC、MPY、

MPY.N 和 MSC)同时使用 Y 数据空间与 X 数据空间,

从而提供两条可同时对数据进行读操作的路径。

X 和 Y 数据空间都支持所有指令的模寻址,但要受到寻

址模式的限制。位反转寻址模式只是在写 X 数据空间时

才支持。

所有数据存储器写操作 (包括 DSP 指令中的数据存储

器写操作)均把数据空间视为组合的 X 和 Y 地址空间。

X 和 Y 数据空间的分界取决于具体的器件,且不能由用

户编程。

所有有效地址均为16 位宽并且指向数据空间内的字节。

因此,数据空间地址范围为 64 KB 或 32K 字,尽管不同

器件上实际实现的存储单元有所不同。

3.2.6 DMA RAM

每个 dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/

X04 和 dsPIC33FJ128MCX02/X04 器件包含最大 2 KB

的双端口 DMA RAM,位于 Y 数据空间的末端。 DMA

RAM 空间中的存储单元可被 CPU 和 DMA 控制器模块

同时访问。 DMA 控制器使用 DMA RAM 来存储要使用

DMA 传输到各外设的数据以及使用 DMA 从各外设传输

进来的数据。DMA 控制器对 DMA RAM 的访问无须占用

CPU 周期。

当 CPU 和 DMA 控制器尝试同时写同一个 DMA RAM 存

储单元时,硬件确保 CPU 具有对 DMA RAM 存储单元

的优先访问权。因此, DMA RAM 提供了传输 DMA 数

据的可靠方式,而无须暂停 CPU。

注: 在不需要使用 DMA 功能的应用中, DMA

RAM 可作为通用数据存储区使用。

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第 37 页

Page 40

DS70291A_CN 第38 页 超前信息 2008 Microchip Technology Inc.

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

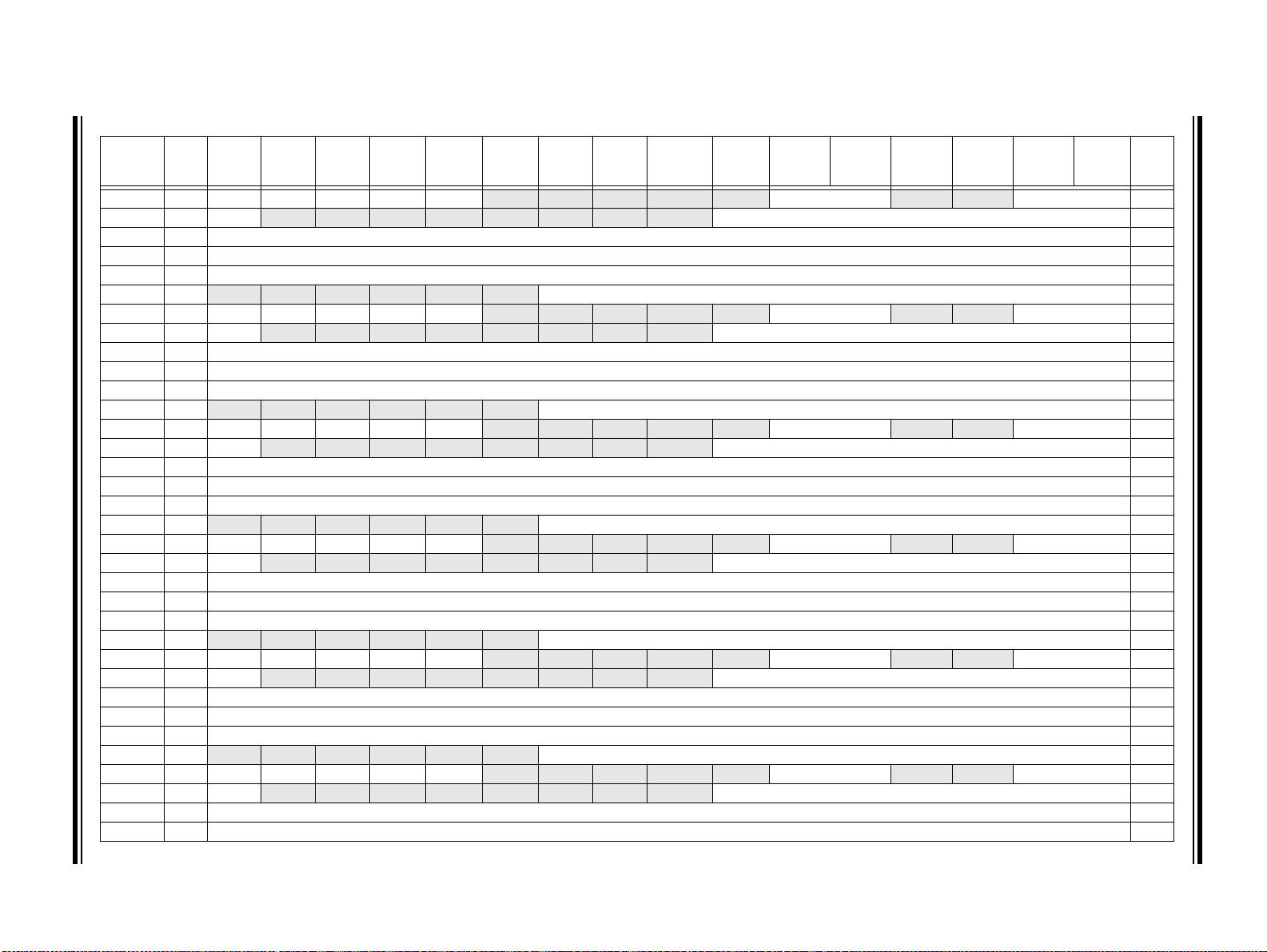

表 3-1: CPU 内核寄存器映射

SFR 名称

WREG0 0000

WREG1 0002

WREG2 0004

WREG3 0006

WREG4 0008

WREG5 000A

WREG6 000C

WREG7 000E

WREG8 0010

WREG9 0012

WREG10 0014

WREG11 0016

WREG12 0018

WREG13 001A

WREG14 001C

WREG15 001E

SPLIM 0020

ACCAL 0022 ACCAL

ACCAH 0024 ACCAH

ACCAU 0026 ACCA<39> ACCAU

ACCBL 0028 ACCBL

ACCBH 002A ACCBH

ACCBU 002C ACCB<39> ACCBU

PCL 002E

PCH 0030 — — — — — — — —

TBLPAG 0032 — — — — — — — —

PSVPAG 0034 — — — — — — — —

RCOUNT 0036

DCOUNT

DOSTARTL

DOSTARTH

DOENDL

DOENDH

SR 0042 OA OB SA SB OAB SAB DA DC IPL2 IPL1 IPL0 RA N OV Z C

CORCON 0044 — — — US EDT DL<2:0>

MODCON 0046 XMODEN YMODEN

图注: x = 复位时的未知值, — = 未实现,读为 0。复位值以 16 进制表示。

SFR

地址

0038 DCOUNT<15:0> xxxx

003A DOSTARTL<15:1> 0xxxx

003C

003E DOENDL<15:1> 0xxxx

0040

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

工作寄存器

工作寄存器

工作寄存器

工作寄存器

工作寄存器

工作寄存器

工作寄存器

工作寄存器

工作寄存器

工作寄存器

工作寄存器

工作寄存器

工作寄存器

工作寄存器

工作寄存器

工作寄存器

堆栈指针限制寄存器

程序计数器低位字寄存器

Repeat

循环计数器寄存器

— — — — — — — — — —

— — — — — — — — — —

— —

BWM<3:0> YWM<3:0> XWM<3:0> 0000

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

程序计数器高字节寄存器

表页地址指针寄存器

程序存储器可视性页地址指针寄存器

DOSTARTH<5:0> 00xx

DOENDH 00xx

SATA SATB SATDW ACCSAT IPL3 PSV RND IF

所有复位

时的状态

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0800

xxxx

xxxx

xxxx

xxxx

xxxx

xxxx

xxxx

xxxx

0000

0000

0000

xxxx

0000

0000

Page 41

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第39 页

表 3-1: CPU 内核寄存器映射 (续)

SFR 名称

XMODSRT 0048 XS<15:1> 0xxxx

XMODEND 004A XE<15:1> 1xxxx

YMODSRT 004C YS<15:1> 0xxxx

YMODEND 004E YE<15:1> 1xxxx

XBREV 0050 BREN XB<14:0> xxxx

DISICNT 0052 —

图注: x = 复位时的未知值, — = 未实现,读为 0。复位值以 16 进制表示。

SFR

地址

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

—

禁止中断计数器寄存器

所有复位

时的状态

xxxx

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

表 3-2: dsPIC33FJ128MC202/802、 dsPIC33FJ64MC202/802 和 dsPIC33FJ32MC302 的电平变化通知寄存器映射

SFR名称SFR

CNEN1

CNEN2

CNPU1

CNPU2

图注: x = 复位时的未知值, — = 未实现,读为 0。复位值以十六进制表示。

00C2

006A

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

地址

0060 CN15IE CN14IE CN13IE CN12IE CN11IE

—

CN30IE CN29IE

0068 CN15PUE CN14PUE CN13PUE CN12PUE CN11PUE

—

CN30PUE CN29PUE

—

CN27IE

—

CN27PUE

— — —

— —

— — —

— —

CN24IE CN23IE CN22IE CN21IE

CN24PUE CN23PUE CN22PUE CN21PUE

CN7IE CN6IE CN5IE CN4IE CN3IE CN2IE CN1IE CN0IE

— — — —

CN7PUE CN6PUE CN5PUE CN4PUE CN3PUE CN2PUE CN1PUE CN0PUE

— — — —

CN16IE

CN16PUE

所有复

位时的

状态

0000

0000

0000

0000

表 3-3: dsPIC33FJ128MC204/804、 dsPIC33FJ64MC204/804 和 dsPIC33FJ32MC304 的电平变化通知寄存器映射

SFR名称SFR

CNEN1

CNEN2

CNPU1

CNPU2

图注: x = 复位时的未知值, — = 未实现,读为 0。复位值以十六进制表示。

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

地址

0060 CN15IE CN14IE CN13IE CN12IE CN11IE CN10IE CN9IE CN8IE CN7IE CN6IE CN5IE CN4IE CN3IE CN2IE CN1IE CN0IE

—

00C2

0068 CN15PUE CN14PUE CN13PUE CN12PUE CN11PUE CN10PUE CN9PUE CN8PUE CN7PUE CN6PUE CN5PUE CN4PUE CN3PUE CN2PUE CN1PUE CN0PUE

006A

CN30IE CN29IE CN28IE CN27IE CN26IE CN25IE CN24IE CN23IE CN22IE CN21IE CN20IE CN19IE CN18IE CN17IE CN16IE

—

CN30PUE CN29PUE CN28PUE CN27PUE CN26PUE CN25PUE CN24PUE CN23PUE CN22PUE CN21PUE CN20PUE CN19PUE CN18PUE CN17PUE CN16PUE

所有复

位时的

状态

0000

0000

0000

0000

Page 42

DS70291A_CN 第40 页 超前信息 2008 Microchip Technology Inc.

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

表 3-4: 中断控制器寄存器映射

SFR

SFR 名称

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

地址

INTCON1 0080 NSTDIS OVAERR OVBERR COVAERR COVBERR OVATE OVBTE COVTE SFTACERR DIV0ERR DMACERR MATHERR ADDRERR STKERR OSCFAIL

INTCON2 0082 ALTIVT DISI

IFS0 0084

— DMA1IF AD1IF U1TXIF U1RXIF SPI1IF SPI1EIF T3IF T2IF OC2IF IC2IF DMA0IF T1IF OC1IF IC1IF INT0IF 0000

IFS1 0086 U2TXIF U2RXIF INT2IF T5IF T4IF OC4IF OC3IF DMA2IF IC8IF IC7IF

IFS2 0088

— DMA4IF PMPIF — — — — — — — — DMA3IF C1IF

IFS3 008A FLTA1IF RTCIF DMA5IF

IFS4 008C DAC1LIF

IEC0 0094

(2)

DAC1RIF

— DMA1IE AD1IE U1TXIE U1RXIE SPI1IE SPI1EIE T3IE T2IE OC2IE IC2IE DMA0IE T1IE OC1IE IC1IE INT0IE 0000

IEC1 0096 U2TXIE U2RXIE INT2IE T5IE T4IE OC4IE OC3IE DMA2IE IC8IE IC7IE

IEC2 0098

— DMA4IE PMPIE — — — — — — — — DMA3IE C1IE

IEC3 009A FLTA1IE RTCIE DMA5IE

IEC4 009C DAC1LIE

IPC0 00A4

IPC1 00A6

IPC2 00A8

IPC3 00AA

IPC4 00AC

IPC5 00AE

IPC6 00B0

IPC7 00B2

IPC8 00B4

IPC9 00B6

IPC11 00BA

IPC14 00C0

IPC15 00C2

IPC16 00C4

IPC17 00C6

IPC18 00C8

IPC19 00CA

INTTREG 00E0

(2)

DAC1RIE

— T1IP<2:0> —OC1IP<2:0> —IC1IP<2:0>— INT0IP<2:0> 4444

— T2IP<2:0> —OC2IP<2:0> —IC2IP<2:0>— DMA0IP<2:0> 4444

— U1RXIP<2:0> — SPI1IP<2:0> — SPI1EIP<2:0> — T3IP<2:0> 4444

— — — — — DMA1IP<2:0> —AD1IP<2:0>— U1TXIP<2:0> 0444

— CNIP<2:0> — CMIP<2:0> — MI2C1IP<2:0> — SI2C1IP<2:0> 4444

—IC8IP<2:0>—IC7IP<2:0> — — — — — INT1IP<2:0> 4404

— T4IP<2:0> —OC4IP<2:0> — OC3IP<2:0> — DMA2IP<2:0> 4444

— U2TXIP<2:0> — U2RXIP<2:0> — INT2IP<2:0> — T5IP<2:0> 4444

— C1IP<2:0>

— — — — — — — — — — — — — DMA3IP<2:0> 0004

— — — — — DMA4IP<2:0> — PMPIP<2:0> — — — — 0440

— — — — — QEI1IP<2:0> — PWM1IP<2:0> — — — — 0440

— FLTA1IP<2:0> —RTCIP<2:0> — DMA5IP<2:0> — — — — 4440

— CRCIP<2:0> — U2EIP<2:0> —U1EIP<2:0>— — — — 4440

— — — — — C1TXIP<2:0>

— QEI2IP<2:0> — FLTA2IP<2:0> — PWM2IP<2:0> — — — — 4440

— DAC1LIP<2:0>

— — — — ILR<3:0>> — VECNUM<6:0> 4444

— — — — — — — — — — — INT2EP INT1EP INT0EP 0000

— INT1IF CNIF CMIF MI2C1IF SI2C1IF 0000

(1)

C1RXIF

(1)

SPI2IF SPI2EIF 0000

— —QEI1IFPWM1IF— — — — — — — — — 0000

(2)

— — QEI2IF FLTA2IF PWM2IF — —C1TXIF

(1)

DMA7IF DMA6IF CRCIF U2EIF U1EIF — 0000

— INT1IE CNIE CMIE MI2C1IE SI2C1IE 0000

(1)

C1RXIE

(1)

SPI2IE SPI2EIE 0000

— —QEI1IEPWM1IE— — — — — — — — — 0000

(2)

— — QEI2IE FLTA2IE PWM2IE — —C1TXIE

(1)

(2)

— C1RXIP<2:0>

—DAC1RIP<2:0>

(1)

(1)

(2)

— SPI2IP<2:0> — SPI2EIP<2:0> 4444

— DMA7IP<2:0> — DMA6IP<2:0> 0444

— — — — — — — — 4400

(1)

DMA7IE DMA6IE CRCIE U2EIE U1EIE — 0000

图注: x = 复位时的未知值, — = 未实现,读为 0。复位值以十六进制表示。

注 1: 对于不带 ECAN™模块的器件禁止此类中断。

2: 对于不带 DAC 模块的器件禁止此类中断。

所有复

位时的

状态

— 0000

Page 43

2008 Microchip Technology Inc. 超前信息 DS70291A_CN 第41 页

表 3-5: 定时器寄存器映射

SFR

SFR 名称

TMR1 0100

PR1 0102

T1CON 0104 TON

TMR2 0106

TMR3HLD 0108

TMR3 010A

PR2 010C

PR3 010E

T2CON 0110 TON

T3CON 0112 TON

TMR4 0114

TMR5HLD 0116

TMR5 0118

PR4 011A

PR5 01C2

T4CON 011E TON

T5CON 0120 TON

图注: x = 复位时的未知值, — = 未实现,读为 0。复位值以十六进制表示。

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

地址

—

—

—

—

—

TSIDL

TSIDL

TSIDL

TSIDL

TSIDL

— — — — — —

— — — — — —

— — — — — —

— — — — — —

— — — — — —

Tim er1

寄存器

周期寄存器

Tim er2

Timer 3

保持寄存器 (仅适用于32位定时器操作)

Tim er3

周期寄存器

周期寄存器

Tim er4

Timer 5

保持寄存器 (仅适用于32位定时器操作)

Tim er5

周期寄存器

周期寄存器

1

寄存器

寄存器

2

3

寄存器

寄存器

4

5

TGATE TCKPS<1:0>

TGATE TCKPS<1:0> T32

TGATE TCKPS<1:0>

TGATE TCKPS<1:0> T32

TGATE TCKPS<1:0>

—

— —

— —

TSYNC TCS

—

—

TCS

TCS

TCS

TCS

所有复

位时的

状态

xxxx

FFFF

—

0000

xxxx

xxxx

xxxx

FFFF

FFFF

—

0000

—

0000

xxxx

xxxx

xxxx

FFFF

FFFF

—

0000

—

0000

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

表 3-6: 输入捕捉寄存器映射

SFR

SFR 名称

IC1BUF 0140

IC1CON 0142

IC2BUF 0144

IC2CON 0146

IC7BUF 0158

IC7CON 015A

IC8BUF 015C

IC8CON 015E

图注: x = 复位时的未知值, — = 未实现,读为 0。复位值以十六进制表示。

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

地址

— —

— —

— —

— —

ICSIDL

ICSIDL

ICSIDL

ICSIDL

— — — — —

— — — — —

— — — — —

— — — — —

输入捕捉1寄存器

ICTMR ICI<1:0> ICOV ICBNE ICM<2:0>

输入捕捉2寄存器

ICTMR ICI<1:0> ICOV ICBNE ICM<2:0>

输入捕捉7寄存器

ICTMR ICI<1:0> ICOV ICBNE ICM<2:0>

输入捕捉8寄存器

ICTMR ICI<1:0> ICOV ICBNE ICM<2:0>

所有复

位时的

状态

xxxx

0000

xxxx

0000

xxxx

0000

xxxx

0000

Page 44

DS70291A_CN 第42 页 超前信息 2008 Microchip Technology Inc.

dsPIC33FJ32MC302/304、 dsPIC33FJ64MCX02/X04 和 dsPIC33FJ128MCX02/X04

表 3-7: 输出比较寄存器映射

SFR

SFR 名称

OC1RS 0180

OC1R 0182

OC1CON 0184

OC2RS 0186

OC2R 0188

OC2CON 018A

OC3RS 018C

OC3R 018E

OC3CON 0190

OC4RS 0192

OC4R 0194

OC4CON 0196

图注: x = 复位时的未知值, — = 未实现,读为 0。复位值以十六进制表示。

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

地址

— —

— —

— —

— —

OCSIDL

OCSIDL

OCSIDL

OCSIDL

— — — — — — — —

— — — — — — — —

— — — — — — — —

— — — — — — — —

输出比较1辅助寄存器

输出比较1寄存器

OCFLT OCTSEL OCM<2:0>

输出比较2辅助寄存器

输出比较2寄存器

OCFLT OCTSEL OCM<2:0>

输出比较3辅助寄存器

输出比较3寄存器

OCFLT OCTSEL OCM<2:0>

输出比较4辅助寄存器

输出比较4寄存器

OCFLT OCTSEL OCM<2:0>

所有复位

时的状态

xxxx

xxxx