Page 1

dsPIC30F2011/2012/3012/3013

数据手册

高性能 16 位

数字信号控制器

2007 Microchip Technology Inc. DS70139E_CN

Page 2

请注意以下有关 Microchip 器件代码保护功能的要点:

•Microchip的产品均达到 Microchip 数据手册中所述的技术指标。

•Microchip确信:在正常使用的情况下, Microchip 系列产品是当今市场上同类产品中最安全的产品之一。

• 目前,仍存在着恶意、甚至是非法破坏代码保护功能的行为。就我们所知,所有这些行为都不是以 Microchip 数据手册中规定的操

作规范来使用 Microchip 产品的。这样做的人极可能侵犯了知识产权。

•Microchip愿与那些注重代码完整性的客户合作。

•Microchip或任何其他半导体厂商均无法保证其代码的安全性。代码保护并不意味着我们保证产品是 “牢不可破”的。

代码保护功能处于持续发展中。 Microchip 承诺将不断改进产品的代码保护功能。任何试图破坏 Microchip 代码保护功能的行为均可视

为违反了《数字器件千年版权法案 (Digital Millennium Copyright Act)》。如果这种行为导致他人在未经授权的情况下,能访问您的软

件或其他受版权保护的成果,您有权依据该法案提起诉讼,从而制止这种行为。

提供本文档的中文版本仅为了便于理解。请勿忽视文档中包含

的英文部分,因为其中提供了有关 Microchip 产品性能和使用

情况的有用信息。Microchip Technology Inc. 及其分公司和相

关公司、各级主管与员工及事务代理机构对译文中可能存在的

任何差错不承担任何责任。建议参考 Microchip Technology

Inc. 的英文原版文档。

本出版物中所述的器件应用信息及其他类似内容仅为您提供便

利,它们可能由更新之信息所替代。确保应用符合技术规范,

是您自身应负的责任。Microchip 对这些信息不作任何明示或

暗示、书面或口头、法定或其他形式的声明或担保,包括但不

限于针对其使用情况、质量、性能、适销性或特定用途的适用

性的声明或担保。 Microchip 对因这些信息及使用这些信息而

引起的后果不承担任何责任。如果将 Microchip 器件用于生命

维持和 / 或生命安全应用,一切风险由买方自负。买方同意在

由此引发任何一切伤害、索赔、诉讼或费用时,会维护和保障

Microchip 免于承担法律责任,并加以赔偿。在 Microchip 知识

产权保护下,不得暗中或以其他方式转让任何许可证。

商标

Microchip 的名称和徽标组合、 Microchip 徽标、 Accuron、

dsPIC、 K

EELOQ、 KEELOQ 徽标、 microID、 MPLAB、 PIC、

PICmicro、 PICSTART、 PRO MATE、 rfPIC 和 SmartShunt

均为 Microchip Technology Inc. 在美国和其他国家或地区的

注册商标。

AmpLab、 FilterLab、 Linear Active Thermistor、 Migratable

Memory、 MXDEV、 MXLAB、 SEEVAL、 SmartSensor 和

The Embedded Control Solutions Company 均为 Microchip

Technology Inc. 在美国的注册商标。

Analog-for-the-Digital Age、 Application Maestro、

CodeGuard、 dsPICDEM、 dsPICDEM.net、 dsPICworks、

dsSPEAK、 ECAN、 ECONOMONITOR、 FanSense、

FlexROM、 fuzzyLAB、 In-Circuit Serial Programming、

ICSP、 ICEPIC、 Mindi、 MiWi、 MPASM、 MPLAB Certified

徽标、MPLIB、MPLINK、PICkit、PICDEM、PICDEM.net、

PICLAB、 PICtail、 PowerCal、 PowerInfo、 PowerMate、

PowerTool、 REAL ICE、 rfLAB、 Select Mode、 Smart

Serial、 SmartTel、Total Endurance、 UNI/O、 WiperLock 和

ZENA 均为 Microchip Technology Inc. 在美国和其他国家或地

区的商标。

SQTP 是 Microchip Technology Inc. 在美国的服务标记。

在此提及的所有其他商标均为各持有公司所有。

© 2007, Microchip Technology Inc. 版权所有。

Microchip

Gresham

印度的设计中心均通过了

MCU与dsPIC® DSC、KEELOQ

设、非易失性存储器和模拟产品方面的质量体系流程均符合

16949:2002

系也已通过了

位于美国亚利桑那州

的全球总部、设计和晶圆生产厂及位于美国加利福尼亚州和

。此外,

Microchip

ISO 9001:2000

Chandler和Te mp e

ISO/TS-16949:2002

®

跳码器件、串行

在开发系统的设计和生产方面的质量体

认证。

与位于俄勒冈州

认证。公司在

EEPROM

®

PIC

、单片机外

ISO/TS-

DS70139E_CN 第 ii 页 2007 Microchip Technology Inc.

Page 3

dsPIC30F2011/2012/3012/3013

dsPIC30F201 1/2012/3012/3013

数字信号控制器

注: 本数据手册总结了 dsPIC30F 系列器件的功能,但是不

应把本手册当作无所不包的参考手册来使用。有关 CPU、外

设、寄存器说明和一般器件功能的更多信息,请参见

《dsPIC30F 系列参考手册》(DS70046E_CN)。有关器件

指令集和编程的更多信息,请参见 《dsPIC30F/33F 程序员

参考手册》(DS70157B_CN)。

高性能改进型 RISC CPU:

• 改进的哈佛架构

• 优化的 C 编译器指令集架构

• 灵活的寻址模式

• 83 条基本指令

• 24 位宽指令, 16 位宽数据总线

• 最大 24 KB 的片上闪存程序空间

• 最大 2 KB 的片上数据 RAM

• 最大 1 KB 的非易失性数据 EEPROM

• 16 x 16 位工作寄存器阵列

• 工作速度最高可达 30 MIPS :

-DC至 40 MHz 外部时钟输入

-4 MHz - 10 MHz 振荡器输入,带 PLL (4 倍

频、 8 倍频和 16 倍频)

• 最多 21 个中断源:

- 每一个中断具有 8 个用户可选择的中断优先

级

-3个外部中断源

-4个处理器陷阱源

DSP 特性:

• 双数据取操作

• 模寻址和位反转寻址模式

• 两个具备可选饱和逻辑的 40 位宽累加器

• 17 位 x 17 位单周期硬件小数 / 整数乘法器

• 所有 DSP 指令均为单周期指令

- 乘 - 累加 (MAC)操作

• 在一个周期内可将数据左右移位 16 位

外设特性:

• 高灌电流 / 拉电流 I/O 引脚:25 mA/25 mA

• 3 个 16 位定时器 / 计数器;可选择将 16 位定时器

配对组成 32 位定时器模块

• 16 位输入捕捉功能

高性能

• 16 位比较 /PWM 输出功能

• 3 线 SPI 模块 (支持 4 种帧模式)

2

• I

C™ 模块支持多主器件 / 从模式和 7 位 /10 位寻

址

• 最多两个带有 FIFO 缓冲区的可寻址 UART 模块

模拟特性:

• 12 位模数转换器 (ADC)具有以下特性:

- 转换速率为 200 ksps

- 最多 10 个输入通道

- 在休眠和空闲模式下可以进行转换

• 可编程低电压检测 (Programmable Low-Voltage

Detection , PLVD)

• 可编程欠压复位

特殊数字信号控制器特性:

• 增强型闪存程序存储器:

- 对于工业级温度范围,最少擦写次数 1 万次,

典型擦写次数 10 万次。

• 数据 EEPROM 存储器:

- 对于工业级温度范围,最少擦写次数 10 万

次,典型擦写次数 100 万次。

• 软件控制下,可自行再编程

• 上电复位 (Power-on Reset, POR)、上电延时

定时器 (Power-up Timer, PWRT)以及振荡器

起振定时器 (Oscillator Start-up Timer, OST)

• 灵活的看门狗定时器 (Watchdog Timer, WDT)

带有片上低功耗 RC 振荡器,能保证可靠的运行

• 故障保护时钟监视器操作:

- 检测时钟故障并切换到片上低功耗 RC 振荡器

• 可编程代码保护

• 在线串行编程 (In-Circuit Serial

Programming™ , ICSP™)功能

• 可选择的功耗管理模式:

- 休眠、空闲和备用时钟模式

CMOS 技术:

• 低功耗高速闪存技术

• 宽工作电压范围为 2.5V 至 5.5V

• 工业级温度范围和扩展级温度范围

• 低功耗

2007 Microchip Technology Inc. DS70139E_CN 第1 页

Page 4

dsPIC30F2011/2012/3012/3013

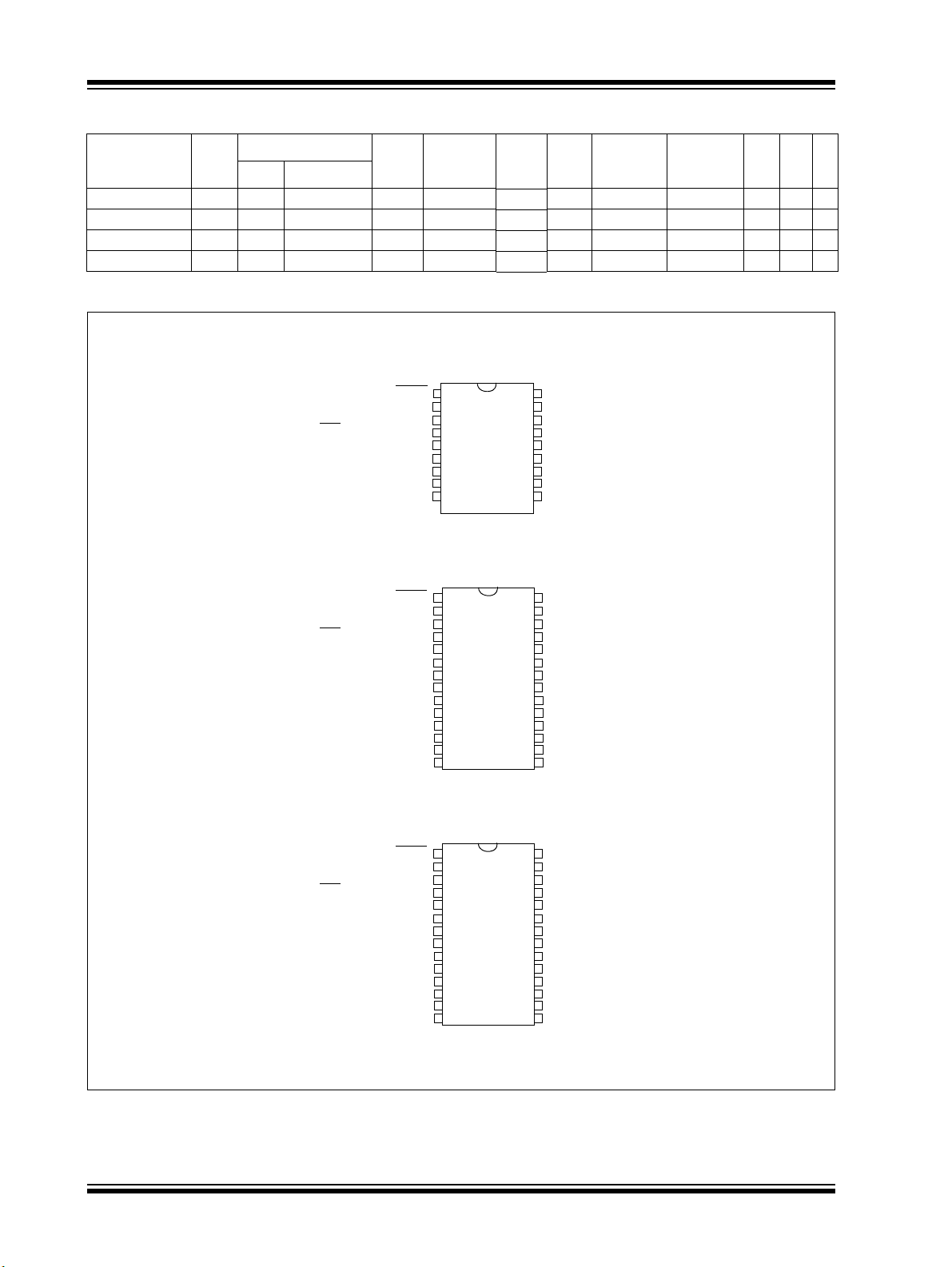

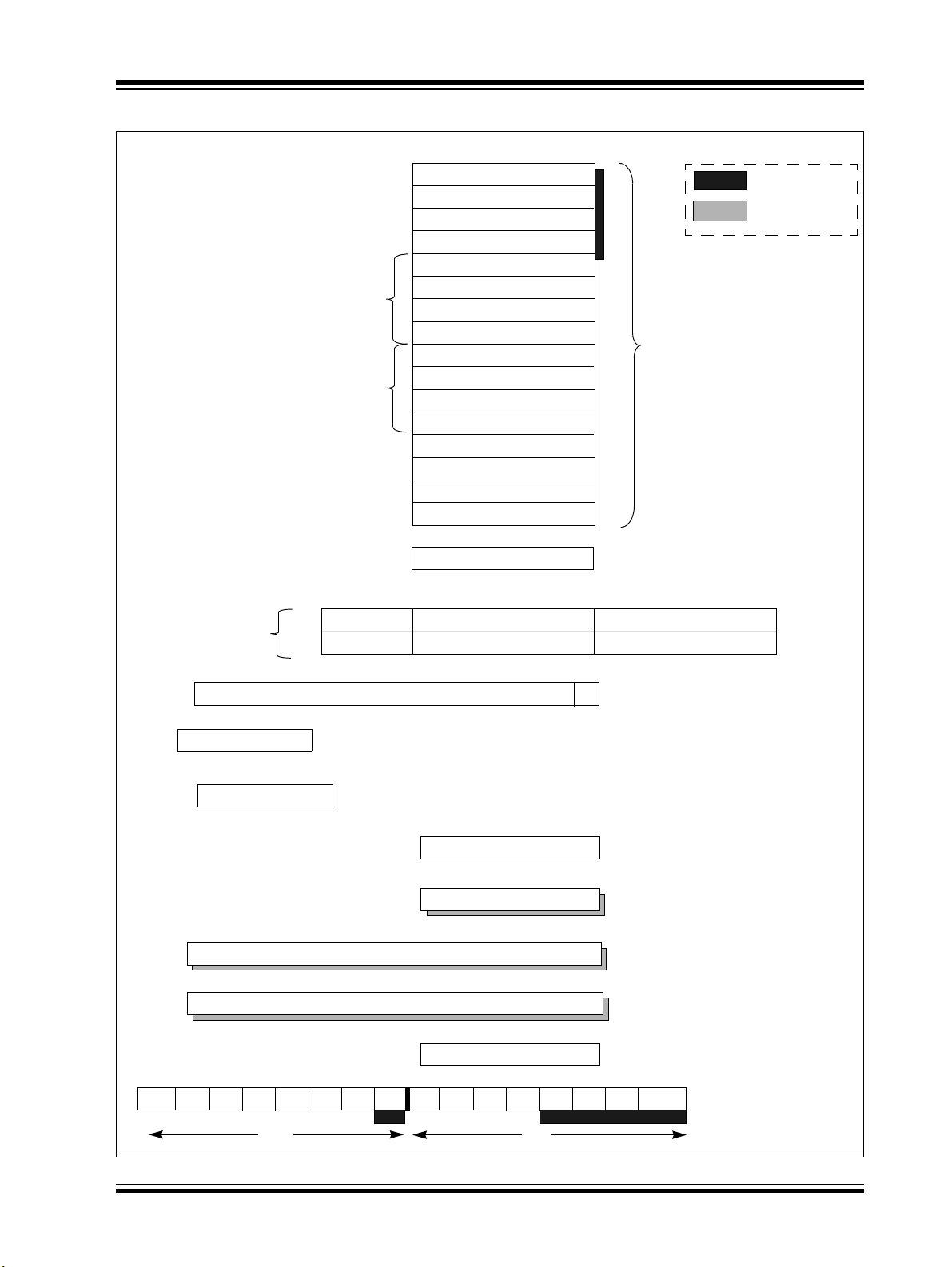

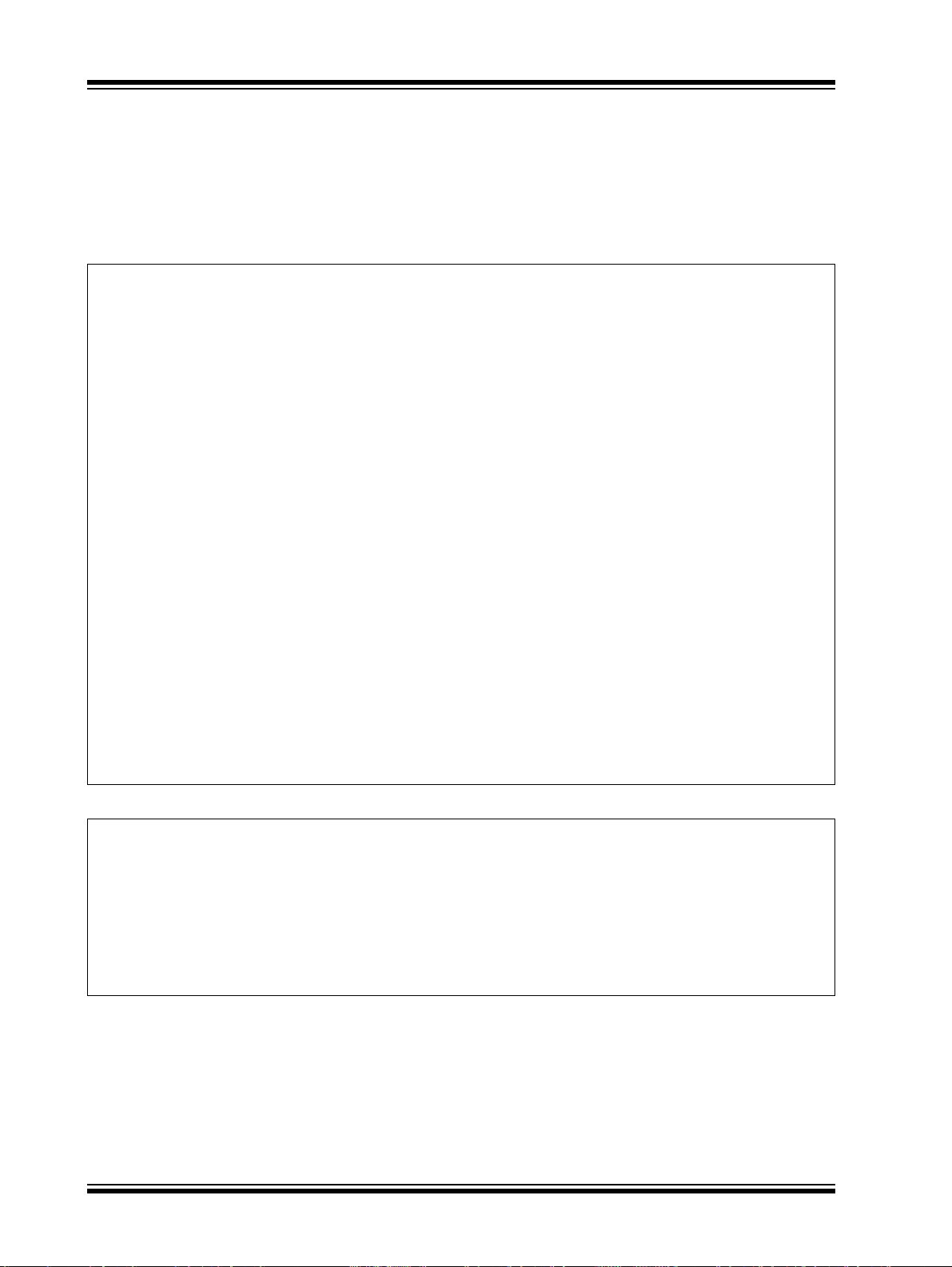

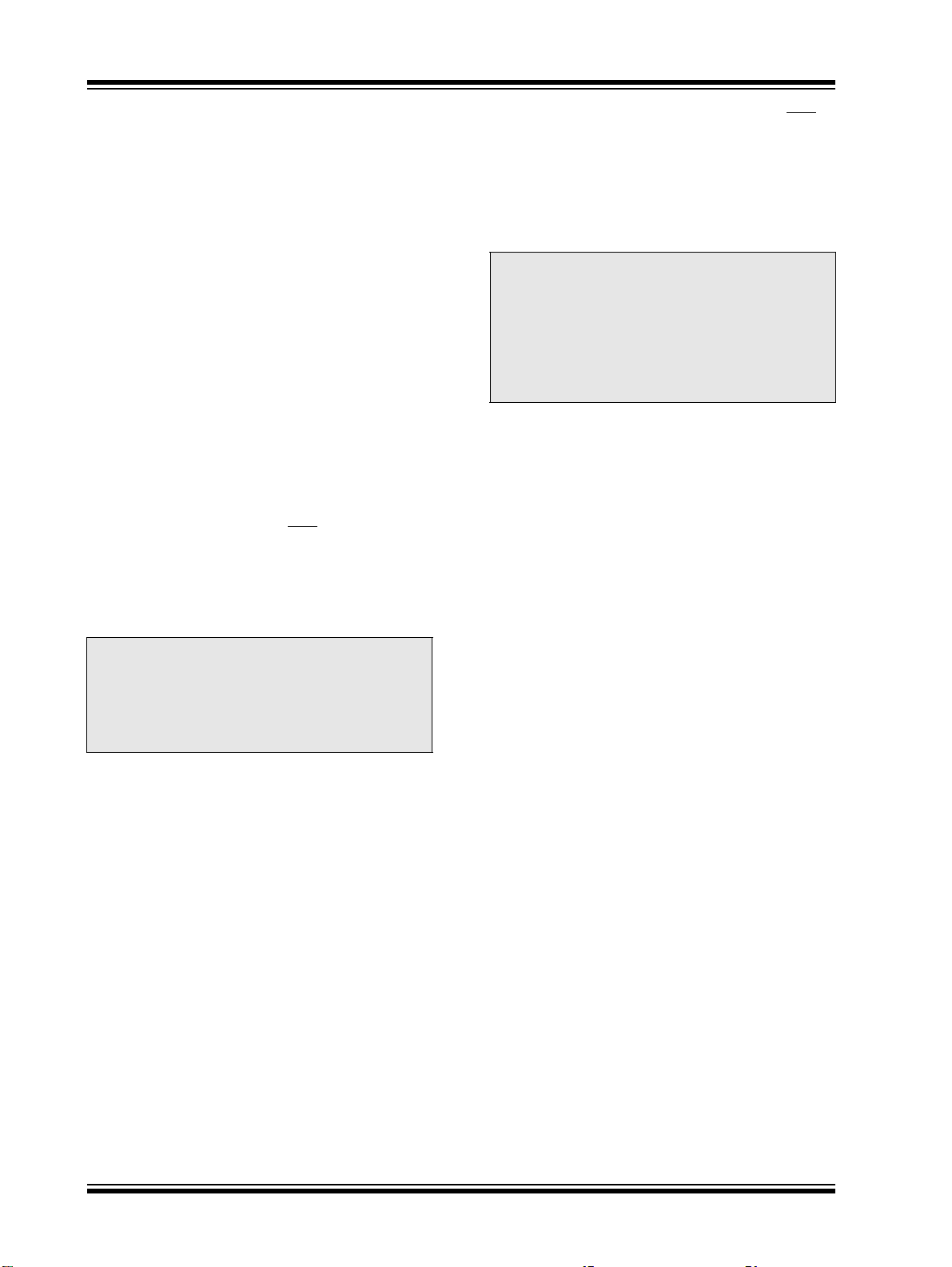

dsPIC30F2011/2012/3012/3013 传感器系列

器件 引脚

程序存储器

字节 指令

dsPIC30F2011 18 12K 4K 1024 – 3 2 2

dsPIC30F3012 18 24K 8K 2048 1024 3 2 2

dsPIC30F2012 28 12K 4K 1024 – 3 2 2

dsPIC30F3013 28 24K 8K 2048 1024 3 2 2

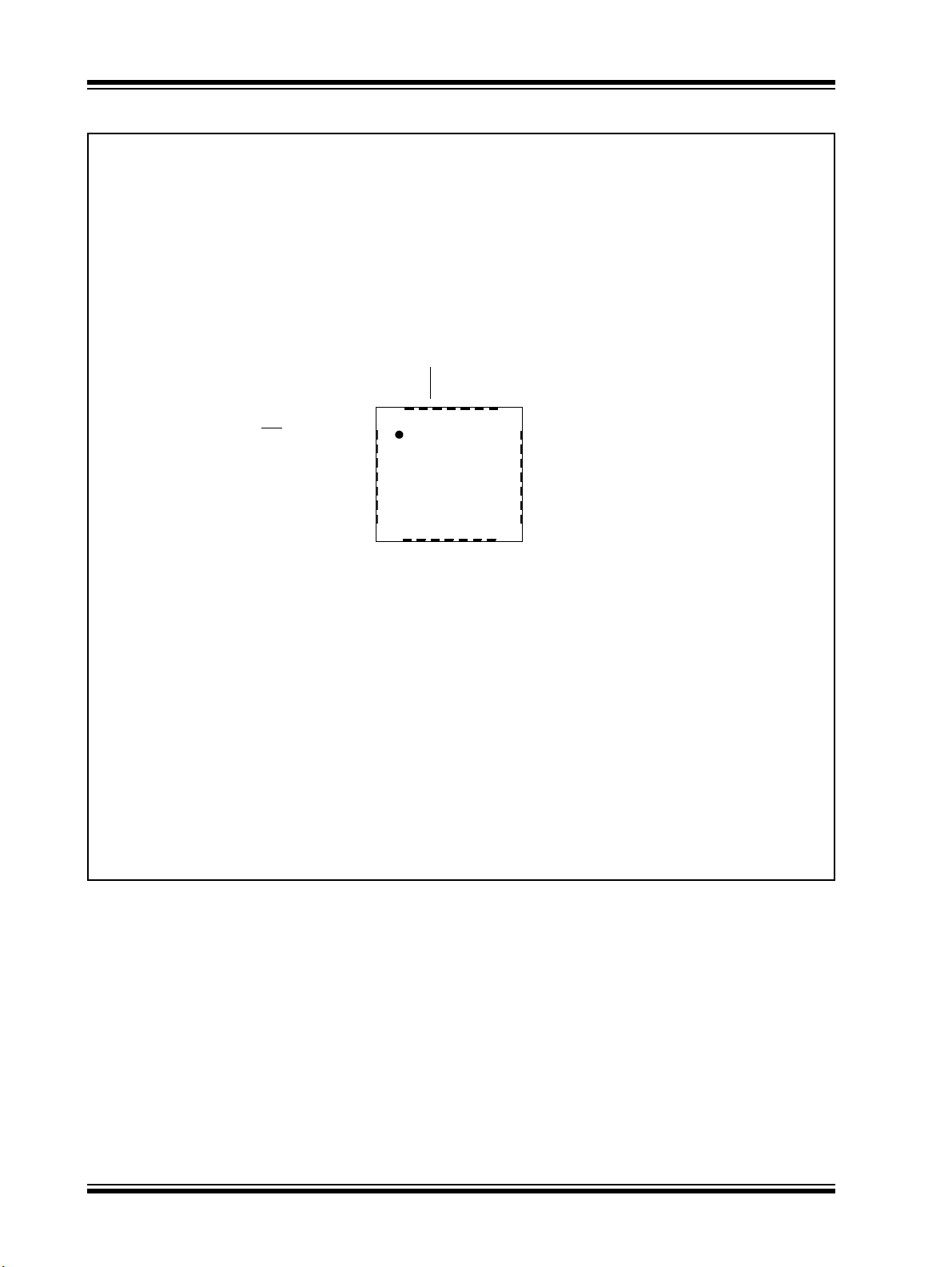

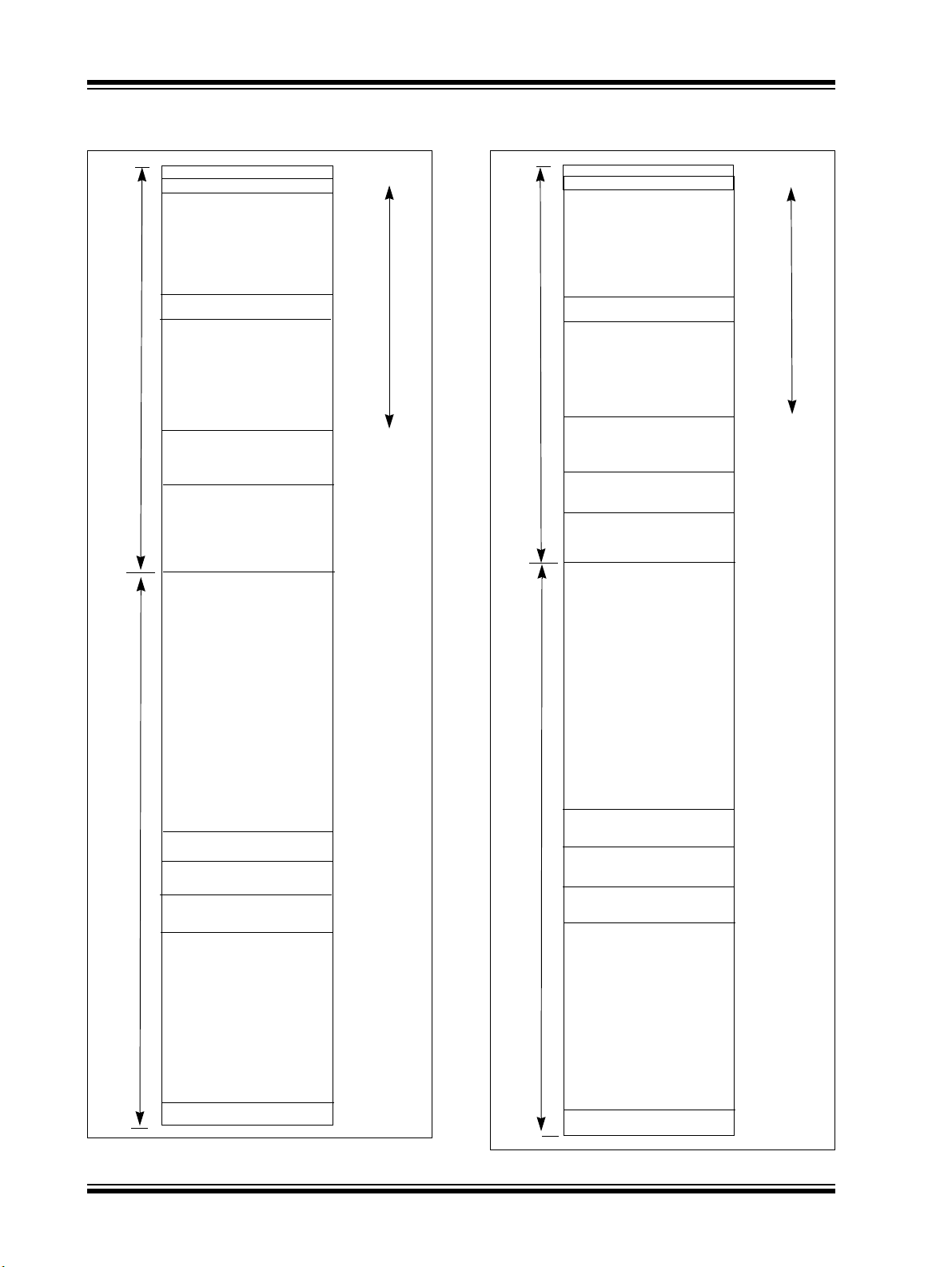

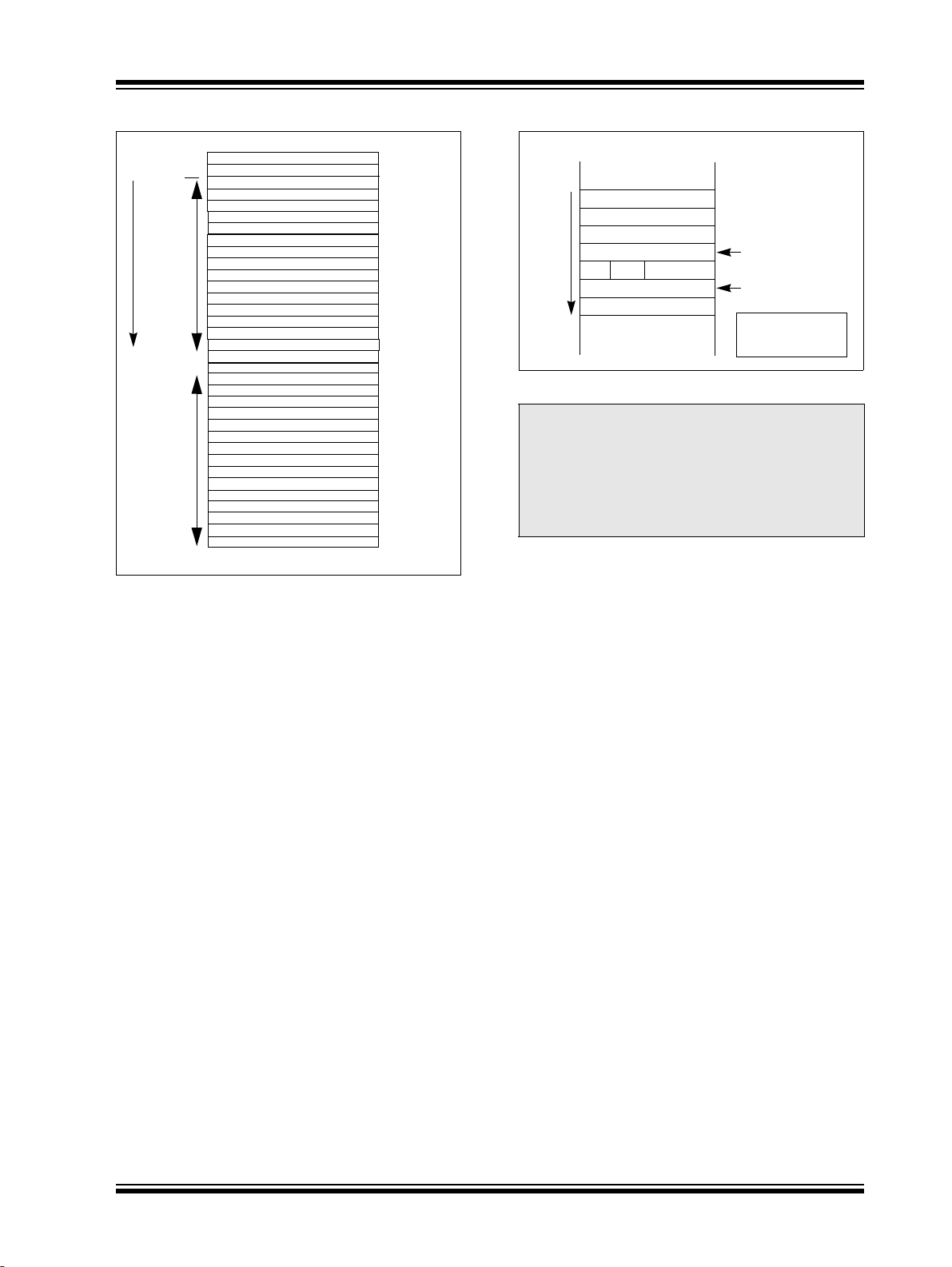

引脚图

18 引脚 PDIP 和 SOIC

SRAM字节EEPROM

字节

16 位

定时器输入捕捉

输出比较 /

标准 PWM

12 位 A/D

200 Ksps

8 通道

8 通道

10 通道

10 通道

C™

SPI

2

UART

I

111

111

111

211

EMUD3/AN0/V

EMUC3/AN1/VREF-/CN3/RB1

EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

28 引脚 PDIP 和 SOIC

EMUD3/AN0/VREF+/CN2/RB0

EMUC3/AN1/V

EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

28 引脚 SPDIP 和 SOIC

EMUD3/AN0/VREF+/CN2/RB0

EMUC3/AN1/V

EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

MCLR

REF+/CN2/RB0

/LVDIN/CN4/RB2

AN2/SS1

AN2/SS1/LVDIN/CN4/RB2

AN2/SS1/LVDIN/CN4/RB2

AN3/CN5/RB3

OSC1/CLKI

OSC2/CLKO/RC15

MCLR

REF-/CN3/RB1

AN3/CN5/RB3

AN4/CN6/RB4

AN5/CN7/RB5

OSC2/CLKO/RC15

IC2/INT2/RD9

REF-/CN3/RB1

AN3/CN5/RB3

AN4/CN6/RB4

AN5/CN7/RB5

IC2/INT2/RD9

VSS

OSC1/CLKI

VDD

MCLR

VSS

OSC1/CLKI V

VDD

1

2

3

4

5

6

7

8

9

1

2

3

4

5

6

7

8

9

10

11

12

13

14

1

2

3

4

5

6

7

8

9

10

11

12

13

14

18

17

16

15

14

V

13

12

11

10

dsPIC30F201

dsPIC30F301

AV

28

AVSS

27

AN6/OCFA/RB6

26

EMUD2/AN7/RB7

25

AN8/OC1/RB8

24

AN9/OC2/RB9

23

CN17/RF4

22

CN18/RF5

21

V

20

V

19

PGC/EMUC/U1RX/SDI1/SDA/RF2

18

dsPIC30F201

dsPIC30F301

PGD/EMUD/U1TX/SDO1/SCL/RF3

17

SCK1/INT0/RF6

16

EMUC2/IC1/INT1/RD8

15

28

AV

AVSS

27

AN6/OCFA/RB6

26

EMUD2/AN7/RB7

25

AN8/OC1/RB8

24

AN9/OC2/RB9

23

U2RX/CN17/RF4

22

U2TX/CN18/RF5

21

20

V

19

PGC/EMUC/U1RX/SDI1/SDA/RF2

18

PGD/EMUD/U1TX/SDO1/SCL/RF3

17

SCK1/INT0/RF6

16

15

EMUC2/IC1/INT1/RD8

DD

AV

SS

AV

AN6/SCK1/INT0/OCFA/RB6

EMUD2/AN7/OC2/IC2/INT2/RB7

DD

V

SS

PGC/EMUC/AN5/U1RX/SDI1/SDA/CN7/RB5

PGD/EMUD/AN4/U1TX/SDO1/SCL/CN6/RB4

EMUC2/OC1/IC1/INT1/RD0

DD

DD

SS

DD

DD

SSOSC2/CLKO/RC15

注: 关于各个引脚的详细说明,请参见第 1.0 节 “器件概述”。

DS70139E_CN 第2 页 2007 Microchip Technology Inc.

Page 5

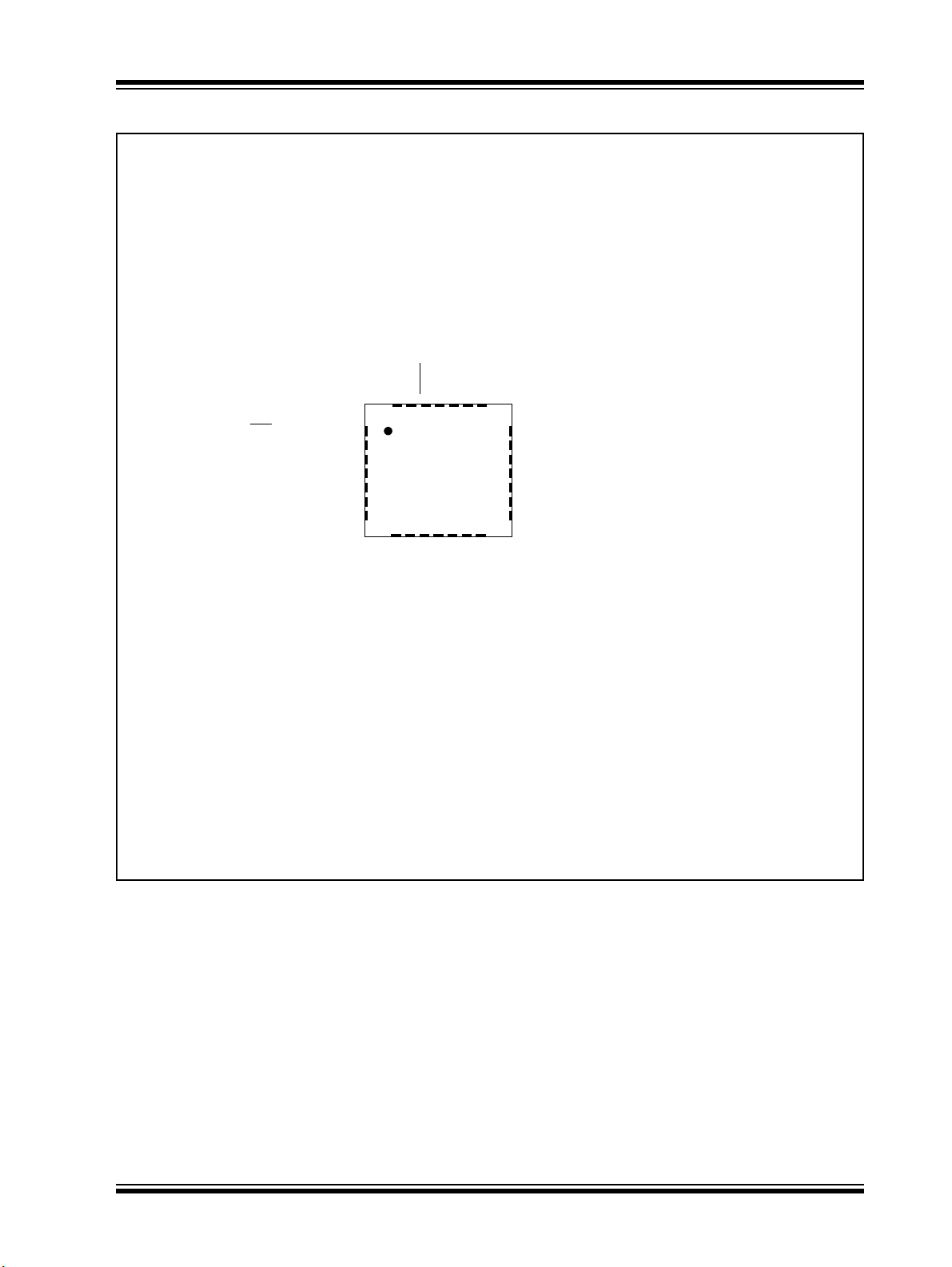

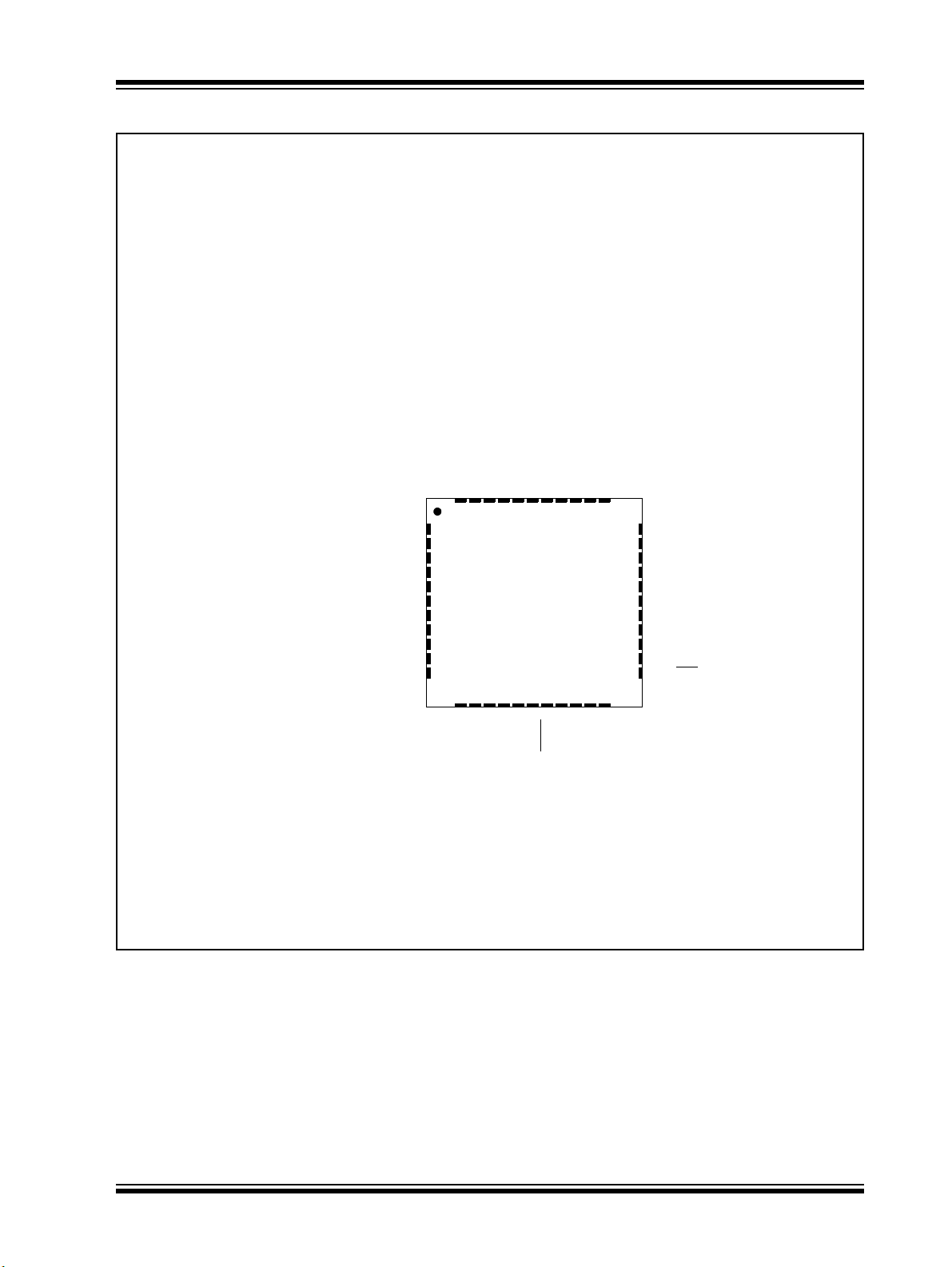

引脚图

28 引脚 QFN

dsPIC30F2011/2012/3012/3013

REF+/CN2/RB0

EMUD3/AN0/V

MCLR

EMUC3/AN1/VREF-/CN3/RB1

AVDD

AVSS

AN6/SCK1/INT0/OCFA/RB6

EMUD2/AN7/OC2/IC2/INT2/RB7

111213

NC

EMUC2/OC1/IC1/INT1/RD0

22

23

NC

21

20

NC

19

NC

NC

18

VDD

17

VSS

16

PGC/EMUC/AN5/U1RX/SDI1/SDA/CN7/RB5

15

14

NC

PGD/EMUD/AN4/U1TX/SDO1/SCL/CN6/RB4

/LVDIN/CN4/RB2

AN2/SS1

OSC2/CLKO/RC15

AN3/CN5/RB3

NC

NC

V

OSC1/CLKI

1

2

3

4

SS

5

6

7

2827262524

dsPIC30F2011

8910

DD

V

EMUD1/SOSC1/T2CK/U1ATX/CN1/RC13

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

注: 关于各个引脚的详细说明,请参见第 1.0 节 “器件概述”。

2007 Microchip Technology Inc. DS70139E_CN 第3 页

Page 6

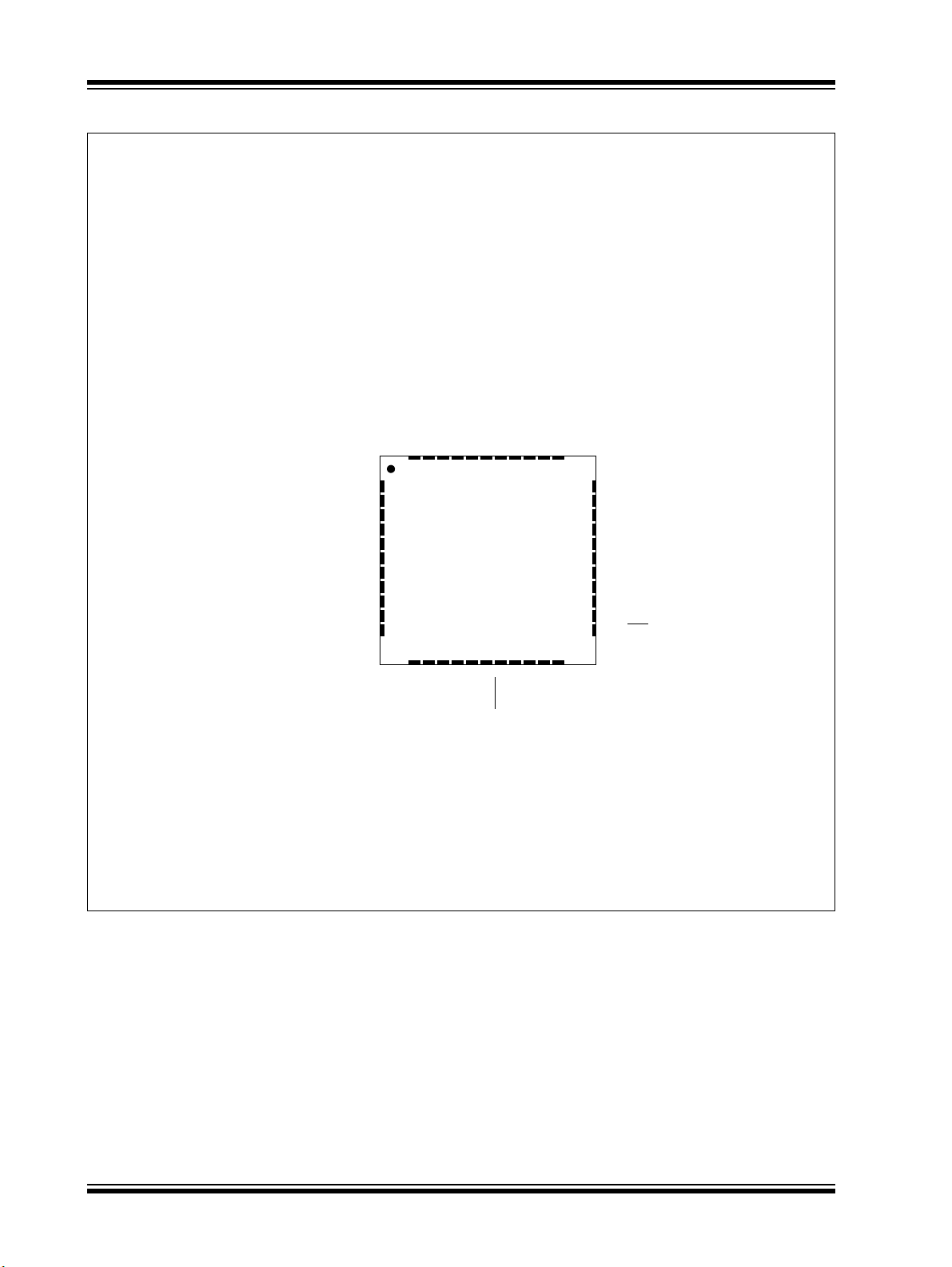

dsPIC30F2011/2012/3012/3013

引脚图

28 引脚 QFN

REF-/CN3/RB1

AVDD

AVSS

AN6/OCFA/RB6

AN2/SS1/LVDIN/CN4/RB2

AN3/CN5/RB3

AN4/CN6/RB4

AN5/CN7/RB5

V

OSC1/CLKI

OSC2/CLKO/RC15

1

2

3

4

SS

5

6

7

MCLR

EMUC3/AN1/V

EMUD3/AN0/VREF+/CN2/RB0

26

27

28

dsPIC30F2012

10

8

9

25

11

121314

EMUD2/AN7/RB7

22

23

24

21

AN8/OC1/RB8

20

AN9/OC2/RB9

CN17/RF4

19

CN18/RF5

18

V

DD

17

VSS

16

PGC/EMUC/U1RX/SDI1/SDA/RF2

15

DD

V

IC2/INT2/RD9

SCK1/INT0/RF6

EMUC2/IC1/INT1/RD8

PGD/EMUD/U1TX/SDO1/SCL/RF3

EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

注: 关于各个引脚的详细说明,请参见第 1.0 节 “器件概述”。

DS70139E_CN 第4 页 2007 Microchip Technology Inc.

Page 7

引脚图

dsPIC30F2011/2012/3012/3013

44 引脚 QFN

PGC/EMUC/AN5/U1RX/SDI1/SDA/CN7/RB5

PGD/EMUD/AN4/U1TX/SDO1/SCL/CN6/RB4NCEMUC2/OC1/IC1/INT1/RD0NCNC

44 4342 4140 3938 3736 35

1

2 32

SS

V

3

NC

4

DD

V

5

NC

NC

NC

NC

NC

NC

NC

6

7

8

9

10

11

dsPIC30F3012

12 1314 1516 1718 1920 21

NC

NCNCV

DD

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

34

22

EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13

33

OSC2/CLKO/RC15

OSC1/CLKI

VSS

31

30

SS

V

29

NC

NC

28

NC

27

NC

26

AN3/CN5/RB3

25

24

NC

23

AN2/SS1/LVDIN/CN4/RB2

NC

NC

AVSS

AVDD

MCLR

REF+/CN2/RB0

AN6/SCK1/INT0/OCFA/RB6

EMUD2/AN7/OC2/IC2/INT2/RB7

EMUD3/AN0/V

注: 关于各个引脚的详细说明,请参见第 1.0 节 “器件概述”。

NC

NC

REF-/CN3/RB1

EMUC3/AN1/V

2007 Microchip Technology Inc. DS70139E_CN 第5 页

Page 8

dsPIC30F2011/2012/3012/3013

引脚图

44 引脚 QFN

DD

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

NC

IC2/INT2/RD9

V

PGD/EMUD/U1TX/SDO1/SCL/RF3

SCK1/INT0/RF6

EMUC2/IC1/INT1/RD8NCNC

NC

EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13

PGC/EMUC/U1RX/SDI1/SDA/RF2

V

NC

V

NC

NC

U2TX/CN18/RF5

NC

U2RX/CN17/RF4

AN9/OC2/RB9

AN8/OC1/RB8

444342414039383736

1

2 32

SS

3

4

DD

5

6

dsPIC30F3013

7

8

9

10

11

121314151617181920

NC

NC

AVSS

AVDD

AN6/OCFA/RB6

EMUD2/AN7/RB7

MCLR

REF-/CN3/RB1

REF+/CN2/RB0

EMUC3/AN1/V

EMUD3/AN0/V

35

21

NC

注: 关于各个引脚的详细说明,请参见第 1.0 节 “器件概述”。

34

OSC2/CLKO/RC15

33

OSC1/CLKI

VSS

31

SS

V

30

29

NC

NC

28

AN5/CN7/RB5

27

AN4/CN6/RB4

26

AN3/CN5/RB3

25

NC

24

AN2/SS1/LVDIN/CN4/RB2

23

22

NC

DS70139E_CN 第6 页 2007 Microchip Technology Inc.

Page 9

dsPIC30F2011/2012/3012/3013

目录

1.0 器件概述 ....................................................................................................................................................................................... 9

2.0 CPU 架构概述 ............................................................................................................................................................................ 17

3.0 存储器构成 ................................................................................................................................................................................ 27

4.0 地址发生器单元 .......................................................................................................................................................................... 41

5.0 闪存程序存储器 .......................................................................................................................................................................... 47

6.0 数据 EEPROM 存储器 ................................................................................................................................................................ 53

7.0 I/O 端口 ...................................................................................................................................................................................... 57

8.0 中断 ............................................................................................................................................................................................ 63

9.0 Timer1 模块 ................................................................................................................................................................................ 71

10.0 Timer2/3 模块 ............................................................................................................................................................................. 75

11.0 输入捕捉模块.............................................................................................................................................................................. 81

12.0 输出比较模块.............................................................................................................................................................................. 85

13.0 SPI 模块 ..................................................................................................................................................................................... 89

2

14.0 I

C 模块 ...................................................................................................................................................................................... 93

15.0 通用异步收发器 (UART)模块 ............................................................................................................................................... 101

16.0 12 位模数转换器 (ADC)模块 ................................................................................................................................................ 109

17.0 系统集成 ................................................................................................................................................................................... 119

18.0 指令集汇总 ............................................................................................................................................................................... 133

19.0 开发支持 ................................................................................................................................................................................... 141

20.0 电气特性 ................................................................................................................................................................................... 145

21.0 封装信息 ................................................................................................................................................................................... 183

索引.................................................................................................................................................................................................... 193

Microchip 网站.................................................................................................................................................................................... 199

变更通知客户服务 .............................................................................................................................................................................. 199

客户支持............................................................................................................................................................................................. 199

读者反馈表 ......................................................................................................................................................................................... 200

产品标识体系 ..................................................................................................................................................................................... 201

致 客 户

我们旨在提供最佳文档供客户正确使用 Microchip 产品。 为此,我们将不断改进出版物的内容和质量,使之更好地满足您的要求。

出版物的质量将随新文档及更新版本的推出而得到提升。

如果您对本出版物有任何问题和建议,请通过电子邮件联系我公司 TRC 经理,电子邮件地址为 CTRC@microchip.com,或将本

数据手册后附的 《读者反馈表》传真到 86-21-5407 5066。我们期待您的反馈。

最新数据手册

欲获得本数据手册的最新版本,请查询我公司的网站:

http://www.microchip.com

查看数据手册中任意一页下边角处的文献编号即可确定其版本。文献编号中数字串后的字母是版本号

的 A 版本。

勘误表

现有器件可能带有一份勘误表,描述了实际运行与数据手册中记载内容之间存在的细微差异以及建议的变通方法。一旦我们了解到

器件 / 文档存在某些差异时,就会发布勘误表。勘误表上将注明其所适用的硅片版本和文件版本。

欲了解某一器件是否存在勘误表,请通过以下方式之一查询:

• Microchip 网站 http://www.microchip.com

• 当地 Microchip 销售办事处 (见最后一页)

在联络销售办事处时,请说明您所使用的器件型号、硅片版本和数据手册版本 (包括文献编号)。

客户通知系统

欲及时获知 Microchip 产品的最新信息,请到我公司网站 www.microchip.com 上注册。

,例如:DS30000A是DS30000

2007 Microchip Technology Inc. DS70139E_CN 第7 页

Page 10

dsPIC30F2011/2012/3012/3013

注:

DS70139E_CN 第8 页 2007 Microchip Technology Inc.

Page 11

dsPIC30F2011/2012/3012/3013

1.0 器件概述

注: 本数据手册总结了 dsPIC30F 系列器件的功能,但是不

应把本手册当作无所不包的参考手册来使用。有关 CPU、外

设、寄存器说明和一般器件功能的更多信息,请参见

《dsPIC30F 系列参考手册》(DS70046E_CN)。有关器件

指令集和编程的更多信息,请参见 《dsPIC30F/33F 程序员

参考手册》(DS70157B_CN)。

该数据手册包含 dsPIC30F2011、 dsPIC30F2012、

dsPIC30F3012 和 dsPIC30F3013 数字信号控制器

(Digital Signal Controller, DSC)的特定信息。

dsPIC30F 系列器件在高性能 16 位单片机 (MCU)架

构中融合了大量数字信号处理器 (Digital Signal

Processor, DSP)功能。

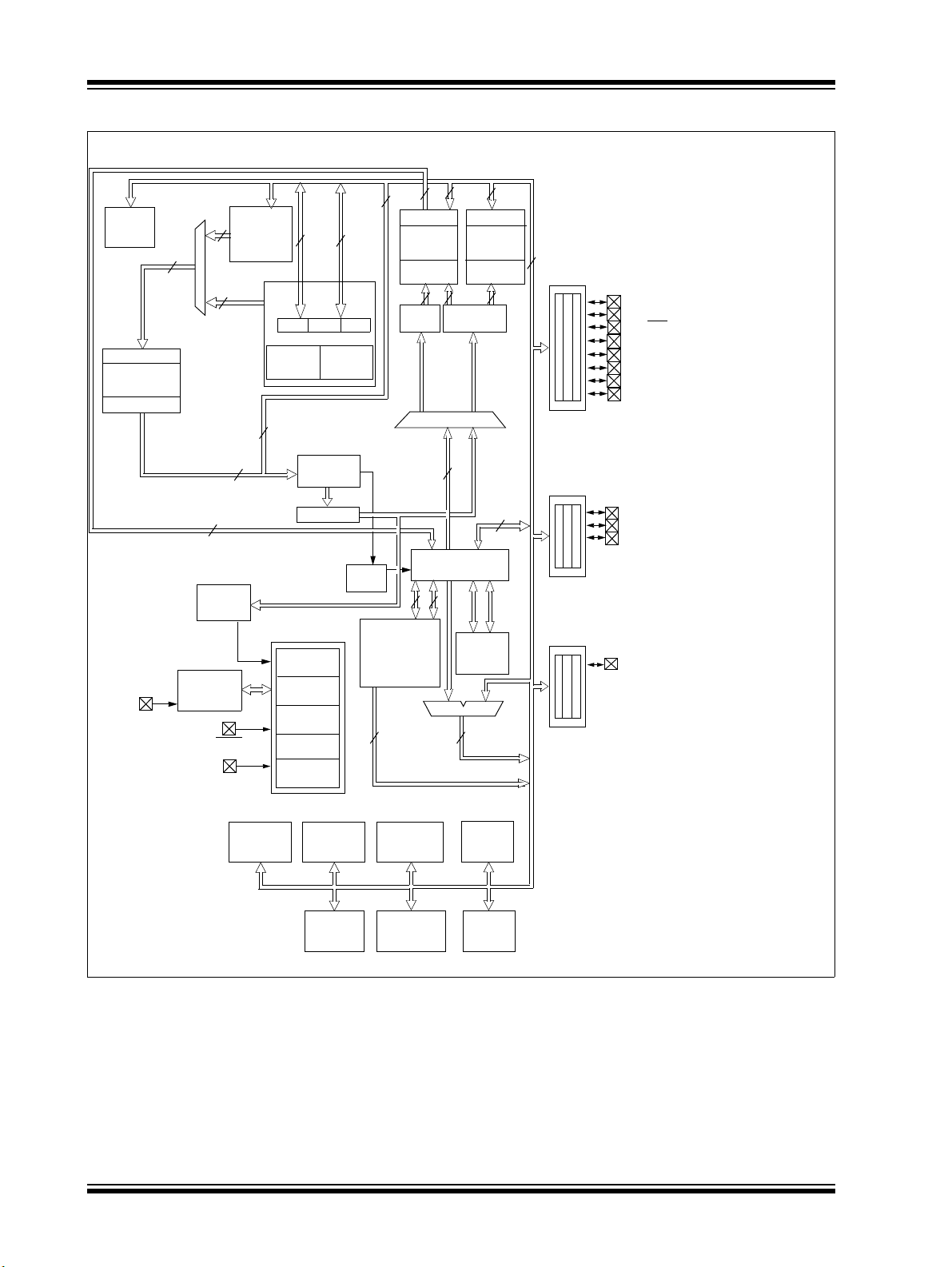

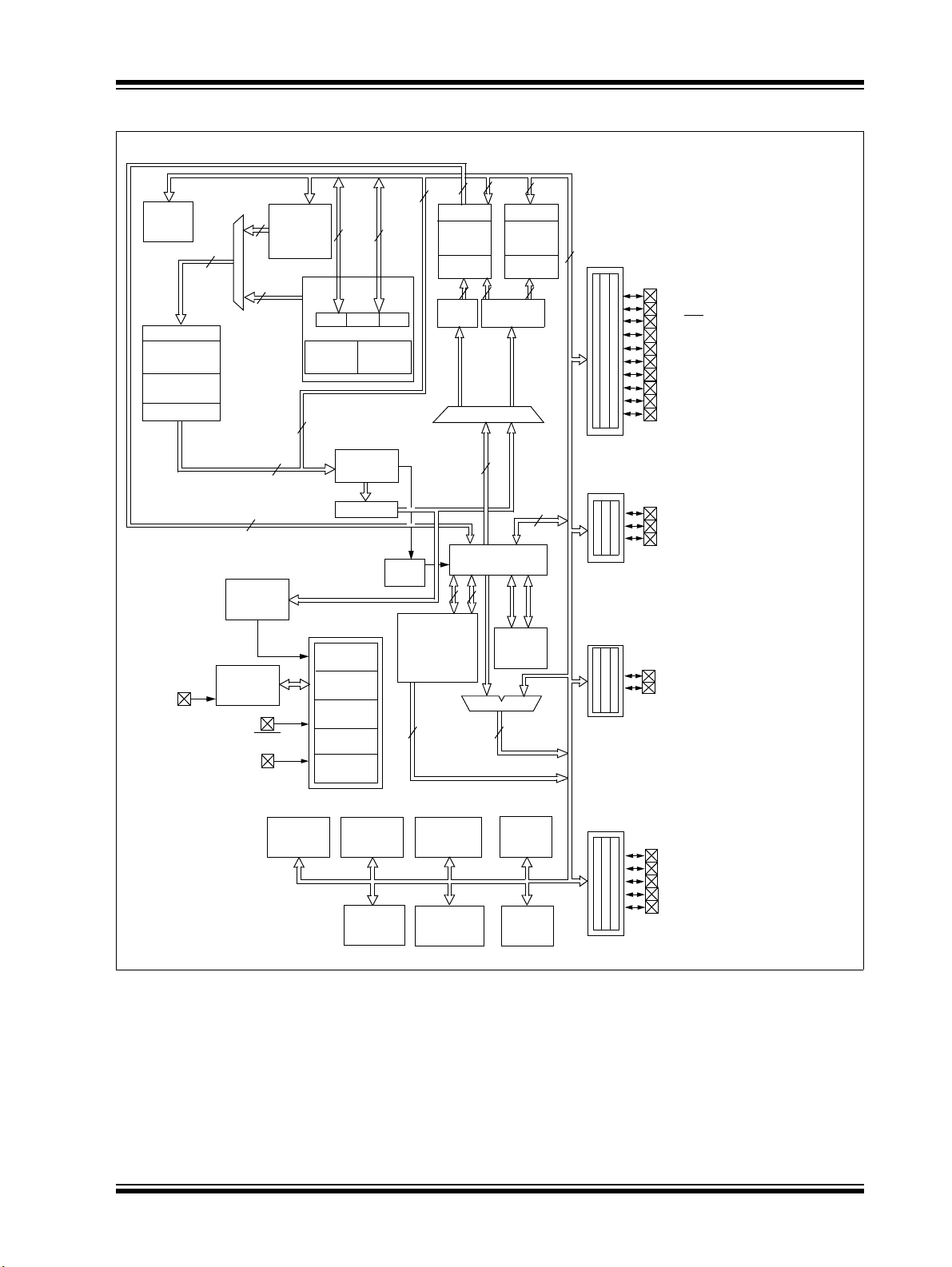

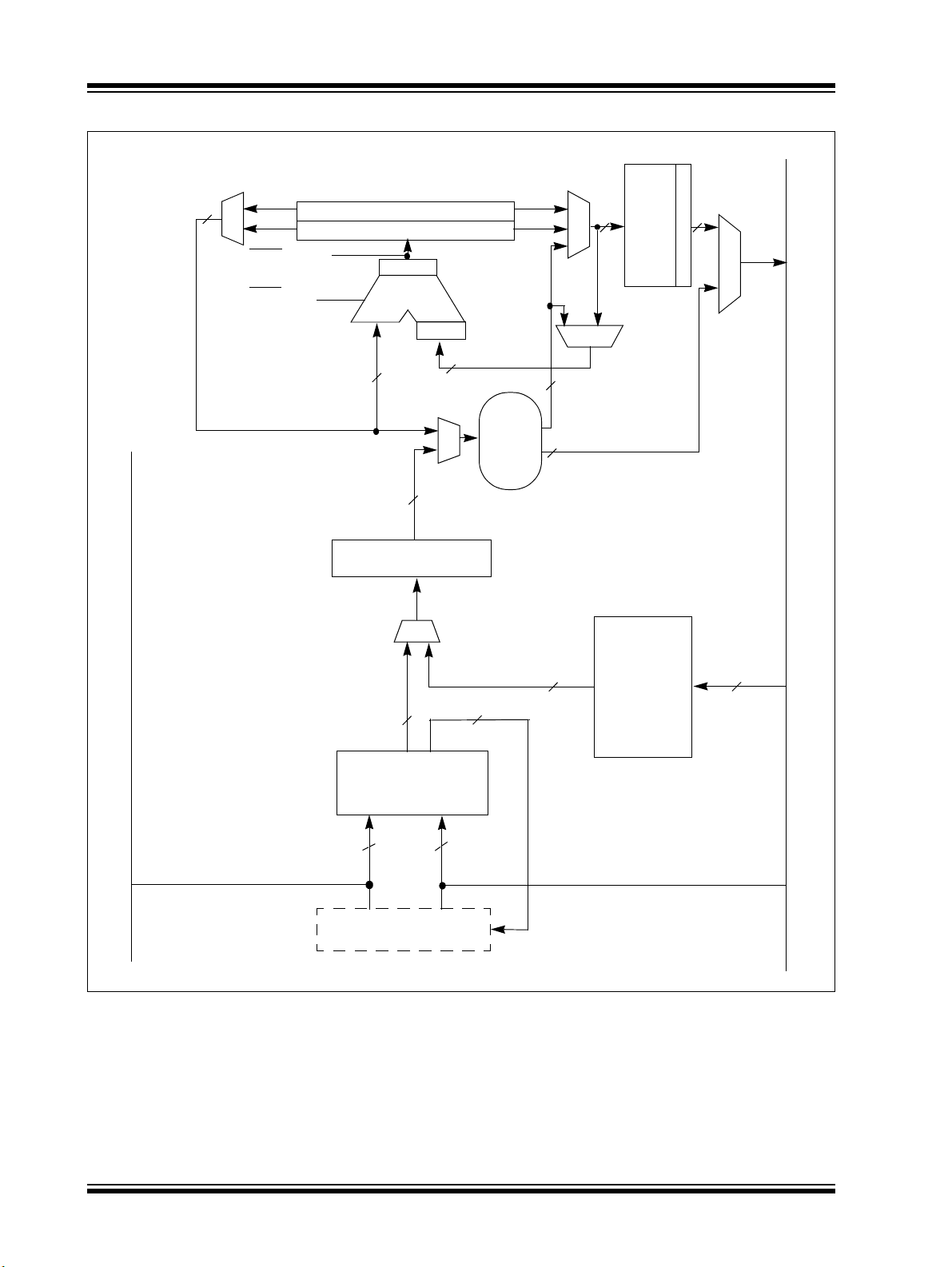

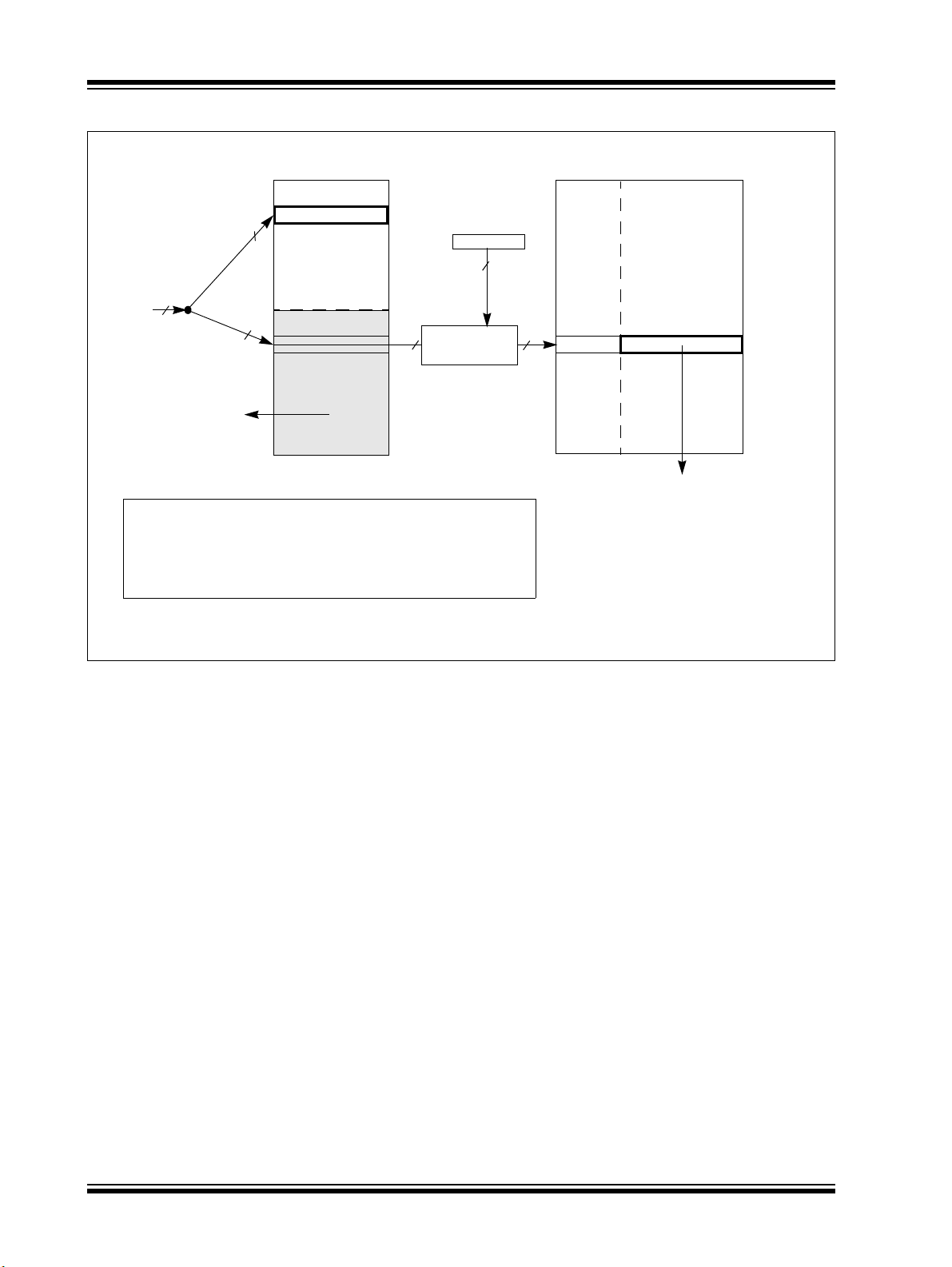

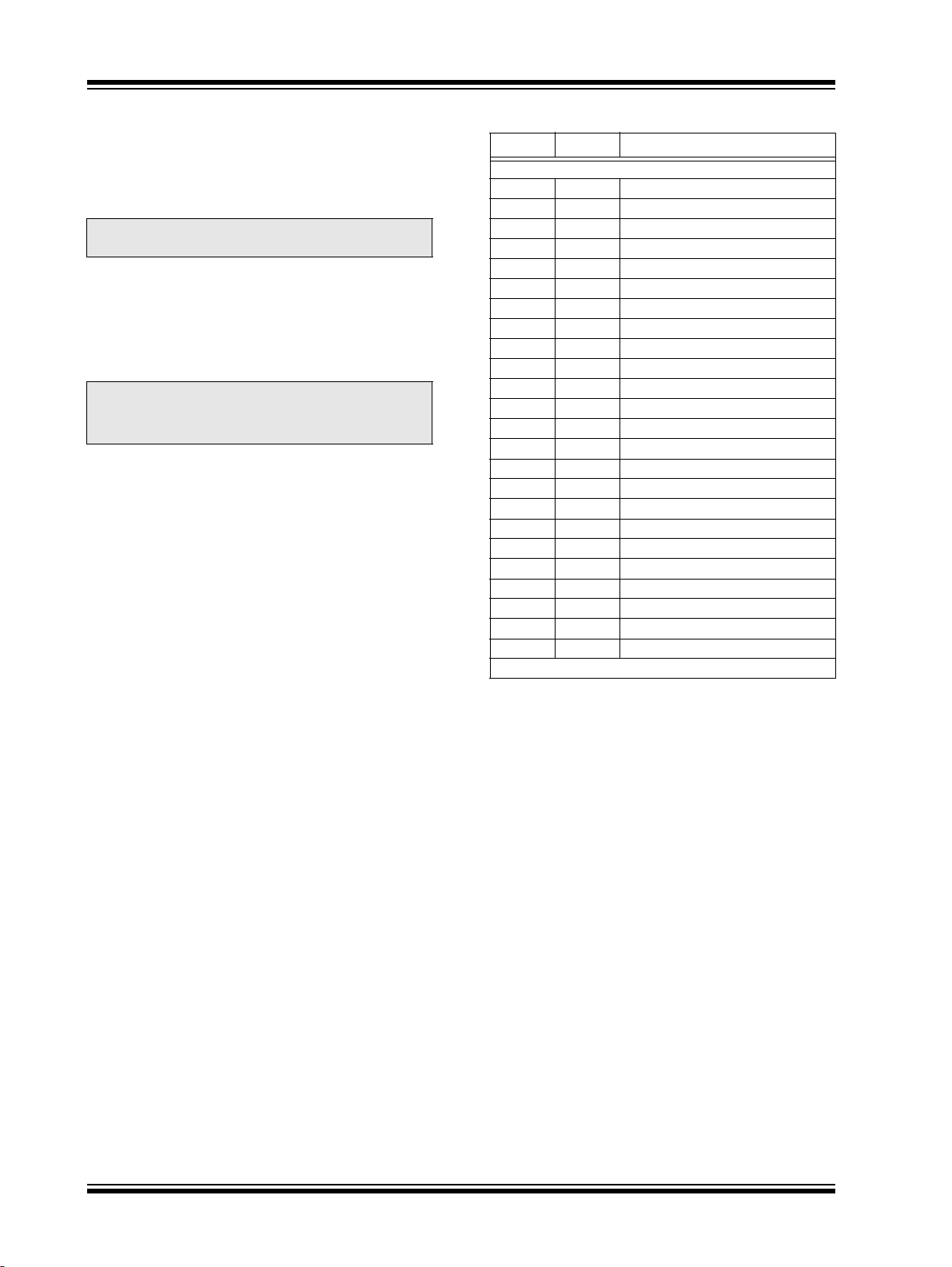

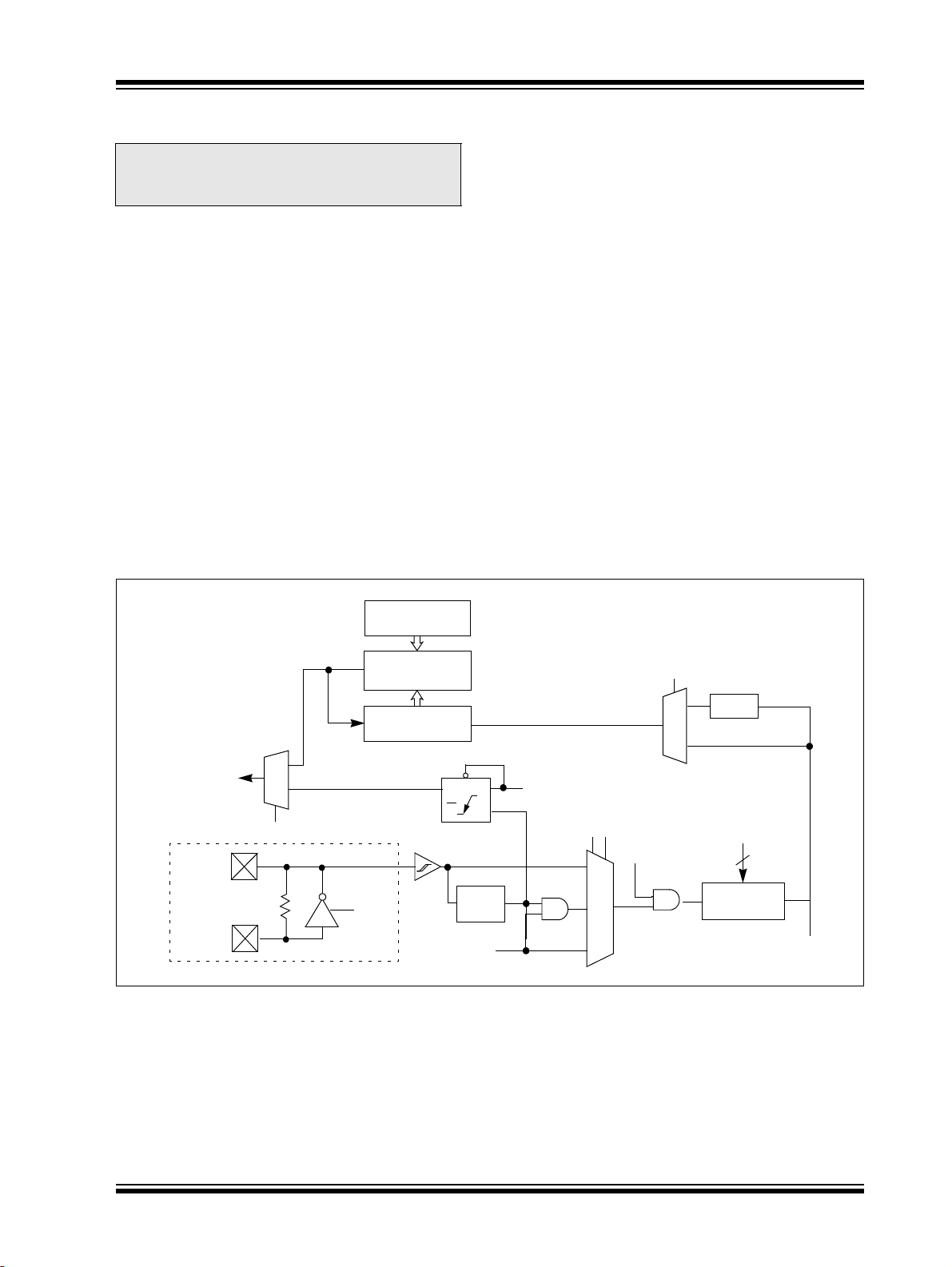

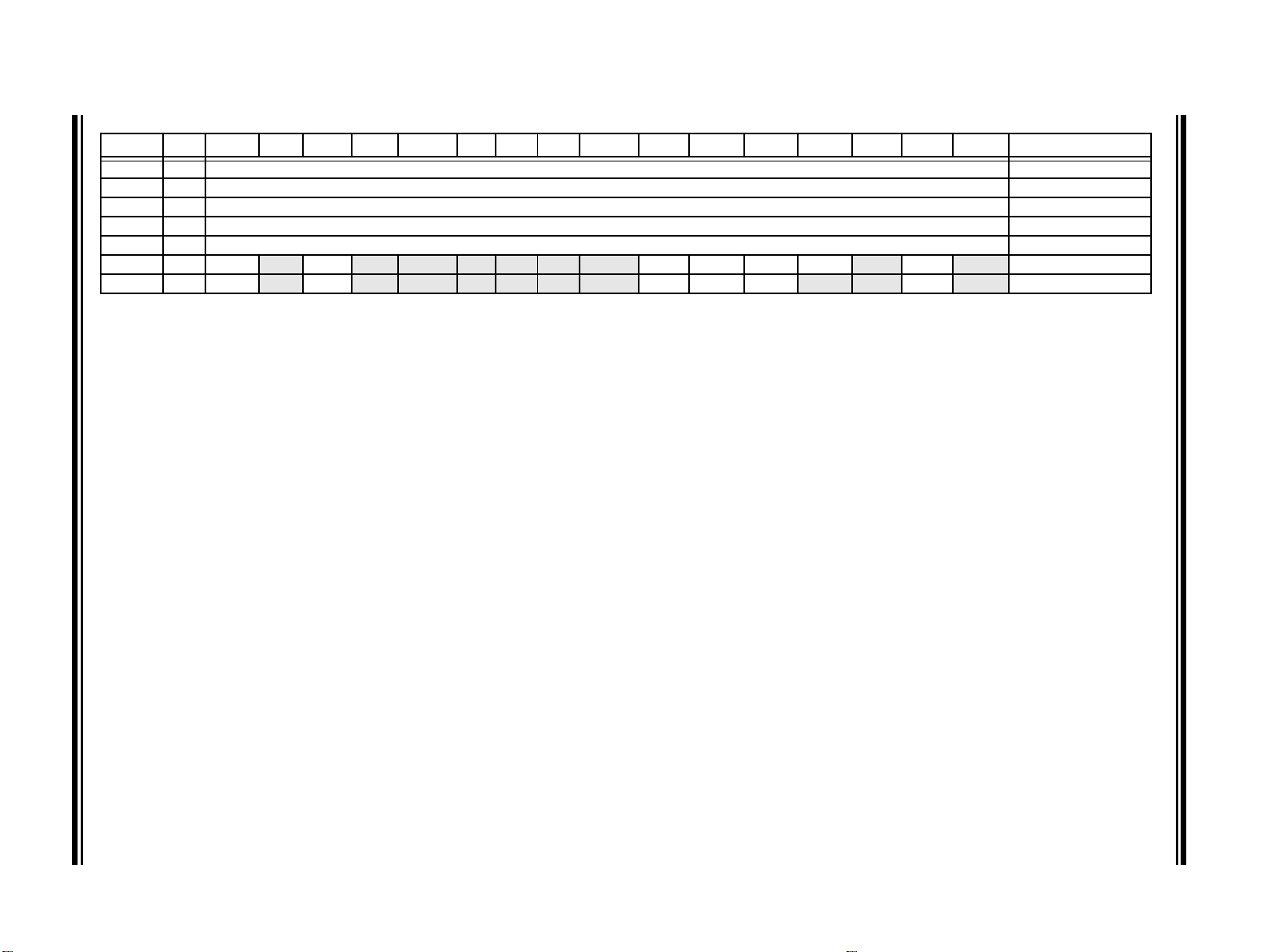

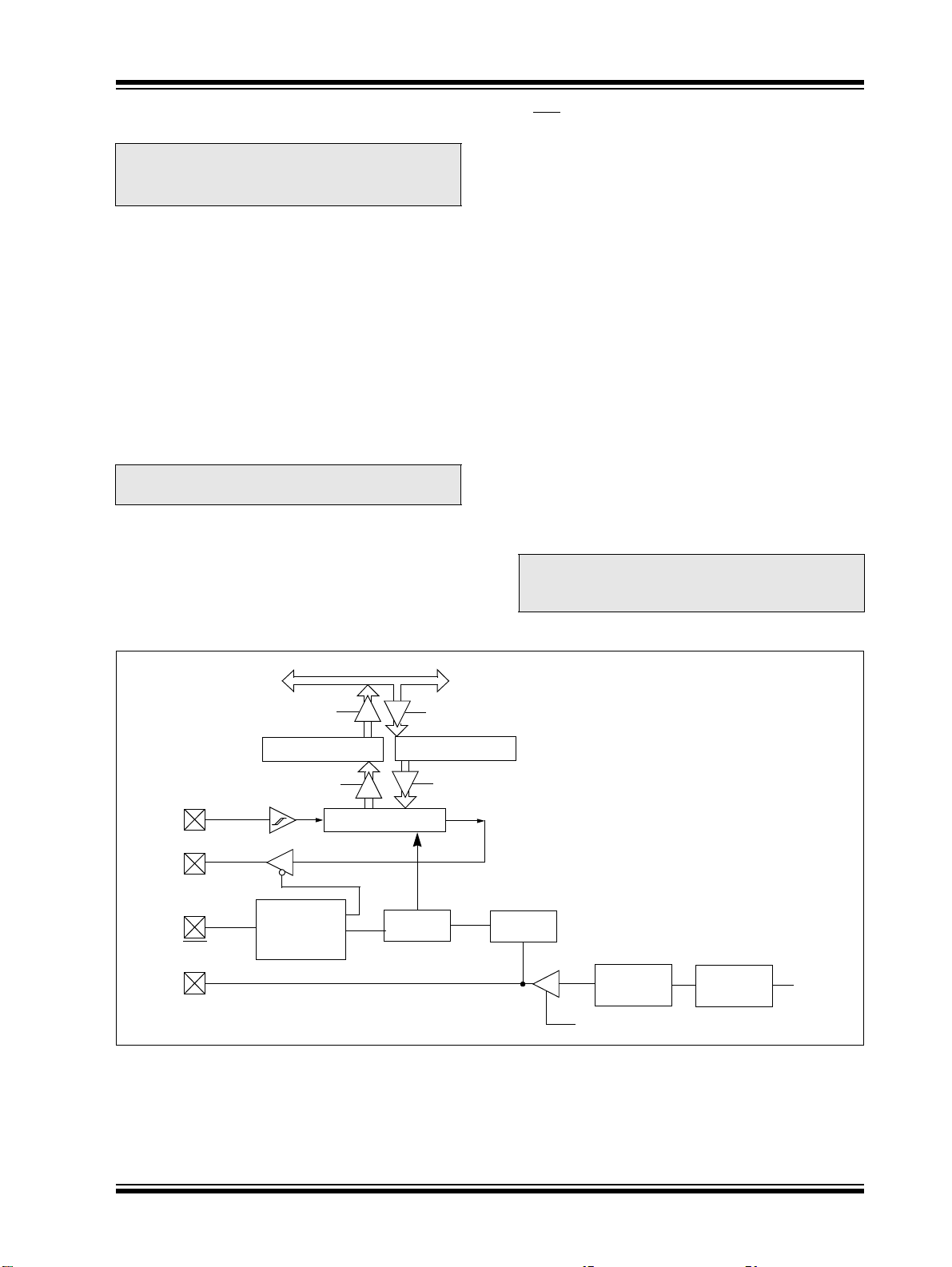

下列框图给出了 dsPIC30F 系列器件的架构:

• 图 1-1 说明 dsPIC30F2011

• 图 1-2 说明 dsPIC30F2012

• 图 1-3 说明 dsPIC30F3012

• 图 1-4 说明 dsPIC30F3013

在框图后,表 1-1 给出了引脚功能信息。

2007 Microchip Technology Inc. DS70139E_CN 第 9 页

Page 12

dsPIC30F2011/2012/3012/3013

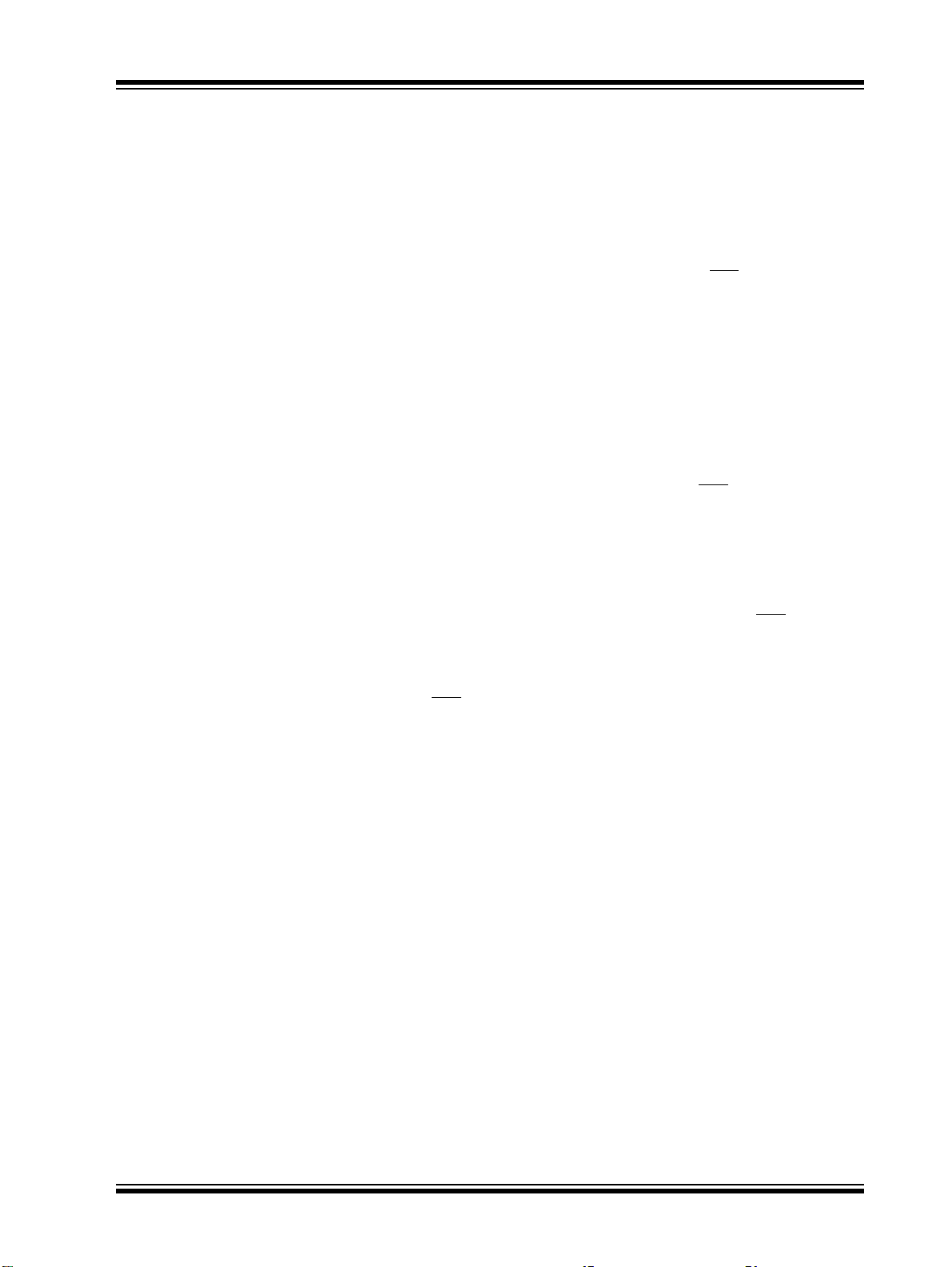

图 1-1: dsPIC30F2011 框图

Y

中断

控制器

地址锁存器

程序存储器

12 KB

)

(

数据锁存器

数据总线

16

PSV

和表

数据访问

控制模块

24

24

24

24

16

PCU

程序计数器

堆栈

控制

逻辑

8

PCH PCL

ROM

锁存器

16

循环

控制

逻辑

Y数据

(

512

Y AGU

16

RAM

字节)

地址

锁存器

16

有效地址

16

16

X RAGU

X WAGU

16

X

数据总线

数据锁存器数据锁存器

X

512

(

锁存器

16

数据

RAM

地址

字节)

16

16

PORTB

EMUD3/AN0/V

EMUC3/AN1/V

AN2/SS1/LVDIN/CN4/RB2

AN3/CN5/RB3

PGD/EMUD/AN4/U1TX/SDO1/SCL/CN6/RB4

PGC/EMUC/AN5/U1RX/SDI1/SDA/CN7/R

AN6/SCK1/INT0/OCFA/RB6

EMUD2/AN7/OC2/IC2/INT2/RB7

REF

+/CN2/RB0

REF

-/CN3/RB1

B5

OSC1/CLKI

16

指令

译码和

控制

时序

发生

MCLR

VDD, V

AVDD, AV

SS

SS

12位ADC

IR

上电延时

定时器

振荡器

起振定时器

POR/BOR

复位

看门狗

定时器

低电压

检测

定时器

输入

捕捉

模块

EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13

16

16 x 16

W

输出

比较

模块

SPI1

16

寄存器阵列

16

ALU<16>

16

除法

单元

I2C™

UART1

PORTC

PORTD

译码

DSP

引擎

16

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

OSC2/CLKO/RC15

EMUC2/OC1/IC1/INT1/RD0

DS70139E_CN 第10 页 2007 Microchip Technology Inc.

Page 13

dsPIC30F2011/2012/3012/3013

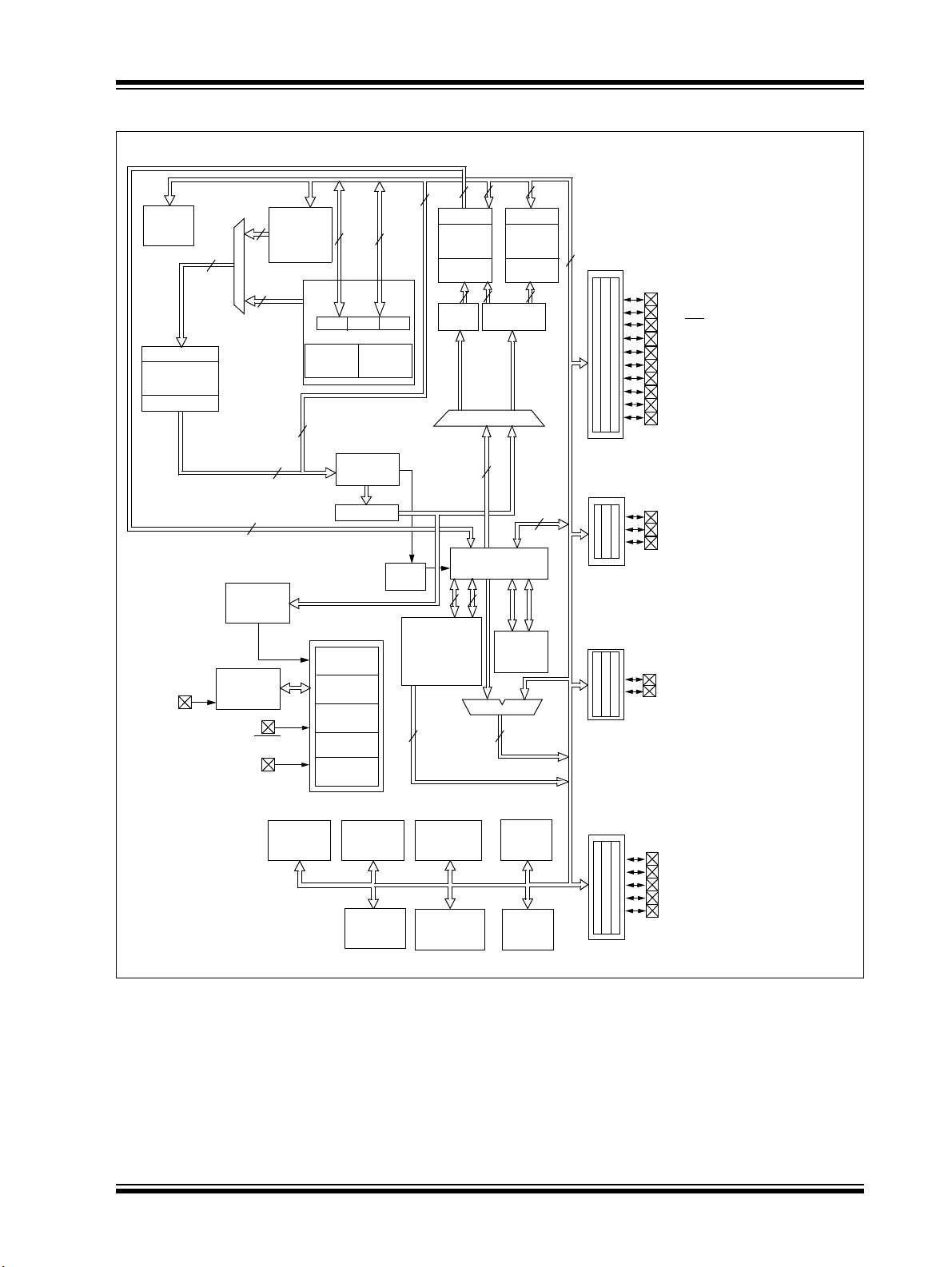

图 1-2: dsPIC30F2012 框图

Y

数据总线

中断

控制器

地址锁存器

程序存储器

12 KB

)

(

数据锁存器

24

24

24

PSV

数据访问

控制模块

24

和表

16

PCU

程序计数器

堆栈

控制

逻辑

8

PCH PCL

ROM

锁存器

16

循环

控制

逻辑

16

Y 数据

RAM

(

512

锁存器

Y AGU

16

字节)

地址

16

有效地址

X

16

16

X RAGU

X WAGU

16

数据总线

数据锁存器数据锁存器

X

RAM

(

512

地址

锁存器

16

数据

字节)

16

16

PORTB

REF

EMUD3/AN0/V

EMUC3/AN1/V

AN2/SS1/LVDIN/CN4/RB2

AN3/CN5/RB3

AN4/CN6/RB4

AN5/CN7/RB5

AN6/OCFA/RB6

EMUD2/AN7/RB7

AN8/OC1/RB8

AN9/OC2/RB9

+/CN2/RB0

REF

-/CN3/RB1

OSC1/CLKI

16

指令

译码和

控制

时序

发生

VDD, V

AV

MCLR

DD

, AV

SS

SS

12位ADC

IR

上电

延时定时器

振荡器

起振定时器

POR/BOR

复位

看门狗

定时器

低电压

检测

定时器

输入

捕捉

模块

译码

DSP

引擎

16

输出

比较

模块

SPI1

16

16 x 16

W

寄存器阵列

16

ALU<16>

除法

单元

16

UART1

I2C™

EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13

16

PORTC

PORTD

PORTF

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

OSC2/CLKO/RC15

EMUC2/IC1/INT1/RD8

IC2/INT2/RD9

PGC/EMUC/U1RX/SDI1/SDA/RF2

PGD/EMUD/U1TX/SDO1/SCL/RF3

CN17/RF4

CN18/RF5

SCK1/INT0/RF6

2007 Microchip Technology Inc. DS70139E_CN 第 11 页

Page 14

dsPIC30F2011/2012/3012/3013

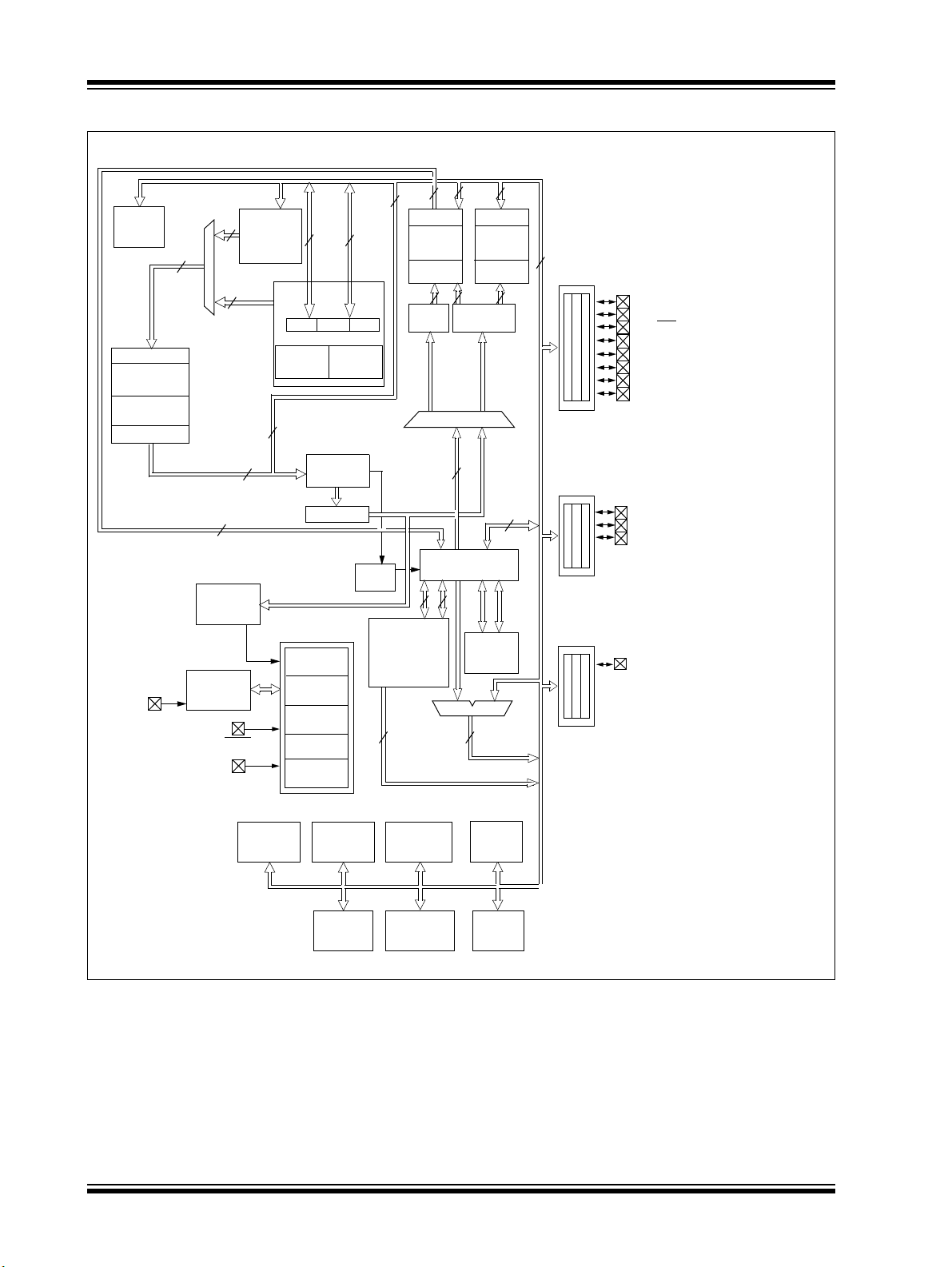

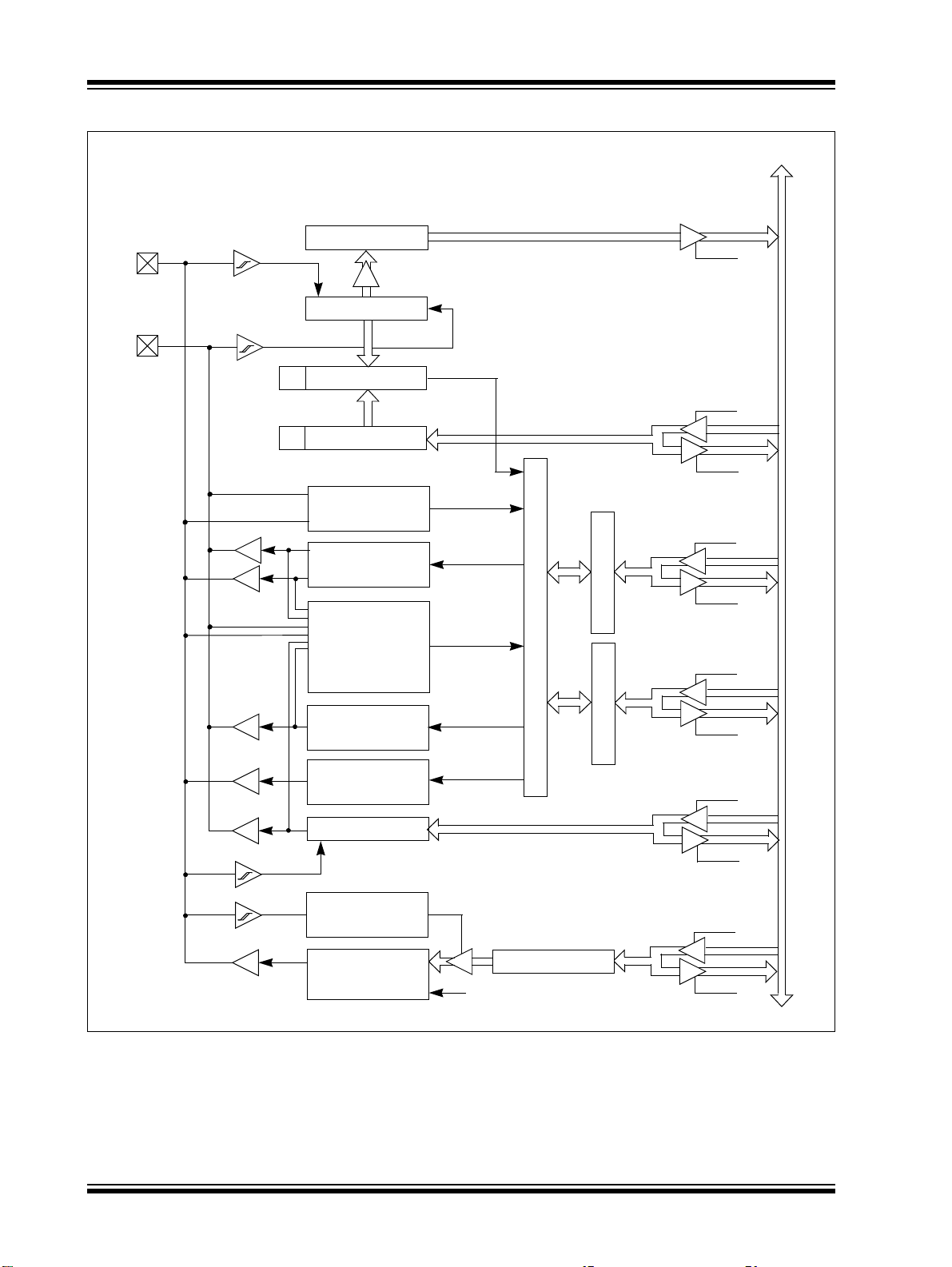

图 1-3: dsPIC30F3012 框图

Y

中断

控制器

地址锁存器

程序存储器

24 KB

(

数据

EEPROM

(

1 KB

数据锁存器

数据总线

16

PSV

和表

数据访问

24

控制模块

24

24

)

)

24

16

PCU

堆栈

控制

逻辑

8

16

PCH PCL

程序计数器

循环

控制

逻辑

ROM

锁存器

(

Y AGU

16

Y 数据

RAM

1 KB

地址

锁存器

16

有效地址

16

)

16

X

数据总线

数据锁存器数据锁存器

X

RAM

(1 KB

地址

锁存器

16

X RAGU

X WAGU

16

数据

16

)

16

PORTB

EMUD3/AN0/V

EMUC3/AN1/V

AN2/SS1/LVDIN/CN4/RB2

AN3/CN5/RB3

PGD/EMUD/AN4/U1TX/SDO1/SCL/CN6/RB4

PGC/EMUC/AN5/U1RX/SDI1/SDA/CN7/R

AN6/SCK1/INT0/OCFA/RB6

EMUD2/AN7/OC2/IC2/INT2/RB7

REF

+/CN2/RB0

REF

-/CN3/RB1

B5

OSC1/CLKI

16

指令

译码和

控制

时序

发生

MCLR

VDD, V

AVDD, AV

SS

SS

12位ADC

IR

上电

延时定时器

振荡器

起振定时器

POR/BOR

复位

看门狗

定时器

低电压

检测

定时器

输入

捕捉

模块

译码

DSP

引擎

16

输出

比较

模块

SPI1

16

16 x 16

W

寄存器阵列

16

ALU<16>

除法

单元

16

I2C™

UART1

EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13

16

PORTC

PORTD

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

OSC2/CLKO/RC15

EMUC2/OC1/IC1/INT1/RD0

DS70139E_CN 第12 页 2007 Microchip Technology Inc.

Page 15

dsPIC30F2011/2012/3012/3013

图 1-4: dsPIC30F3013 框图

Y

数据总线

中断

控制器

地址锁存器

程序存储器

24 KB

(

数据

EEPROM

(

1 KB

数据锁存器

24

)

)

24

24

PSV

数据访问

控制模块

24

和表

16

8

PCU

程序计数器

堆栈

控制

逻辑

ROM

16

PCH PCL

循环

控制

逻辑

锁存器

16

16

Y 数据

RAM

(

1 KB

地址

锁存器

Y AGU

16

)

16

16

X RAGU

X WAGU

有效地址

16

X

数据总线

数据锁存器数据锁存器

X

(

锁存器

16

数据

RAM

1 KB

地址

)

16

16

PORTB

REF

EMUD3/AN0/V

EMUC3/AN1/V

AN2/SS1/LVDIN/CN4/RB2

AN3/CN5/RB3

AN4/CN6/RB4

AN5/CN7/RB5

AN6/OCFA/RB6

EMUD2/AN7/RB7

AN8/OC1/RB8

AN9/OC2/RB9

+/CN2/RB0

REF

-/CN3/RB1

OSC1/CLKI

16

指令

译码和

控制

时序

产生

VDD, V

AV

MCLR

DD

, AV

SS

SS

12位ADC

IR

上电

延时定时器

振荡器

起振定时器

POR/BOR

复位

看门狗

定时器

低电压

检测

定时器

输入

捕捉

模块

译码

DSP

引擎

16

输出

比较

模块

SPI1

16

16 x 16

W

寄存器阵列

16

ALU<16>

除法

单元

16

I2C™

UART1,

UART2

EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13

16

PORTC

PORTD

PORTF

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

OSC2/CLKO/RC15

EMUC2/IC1/INT1/RD8

IC2/INT2/RD9

PGC/EMUC/U1RX/SDI1/SDA/RF2

PGD/EMUD/U1TX/SDO1/SCL/RF3

U2RX/CN17/RF4

U2TX/CN18/RF5

SCK1/INT0/RF6

2007 Microchip Technology Inc. DS70139E_CN 第 13 页

Page 16

dsPIC30F2011/2012/3012/3013

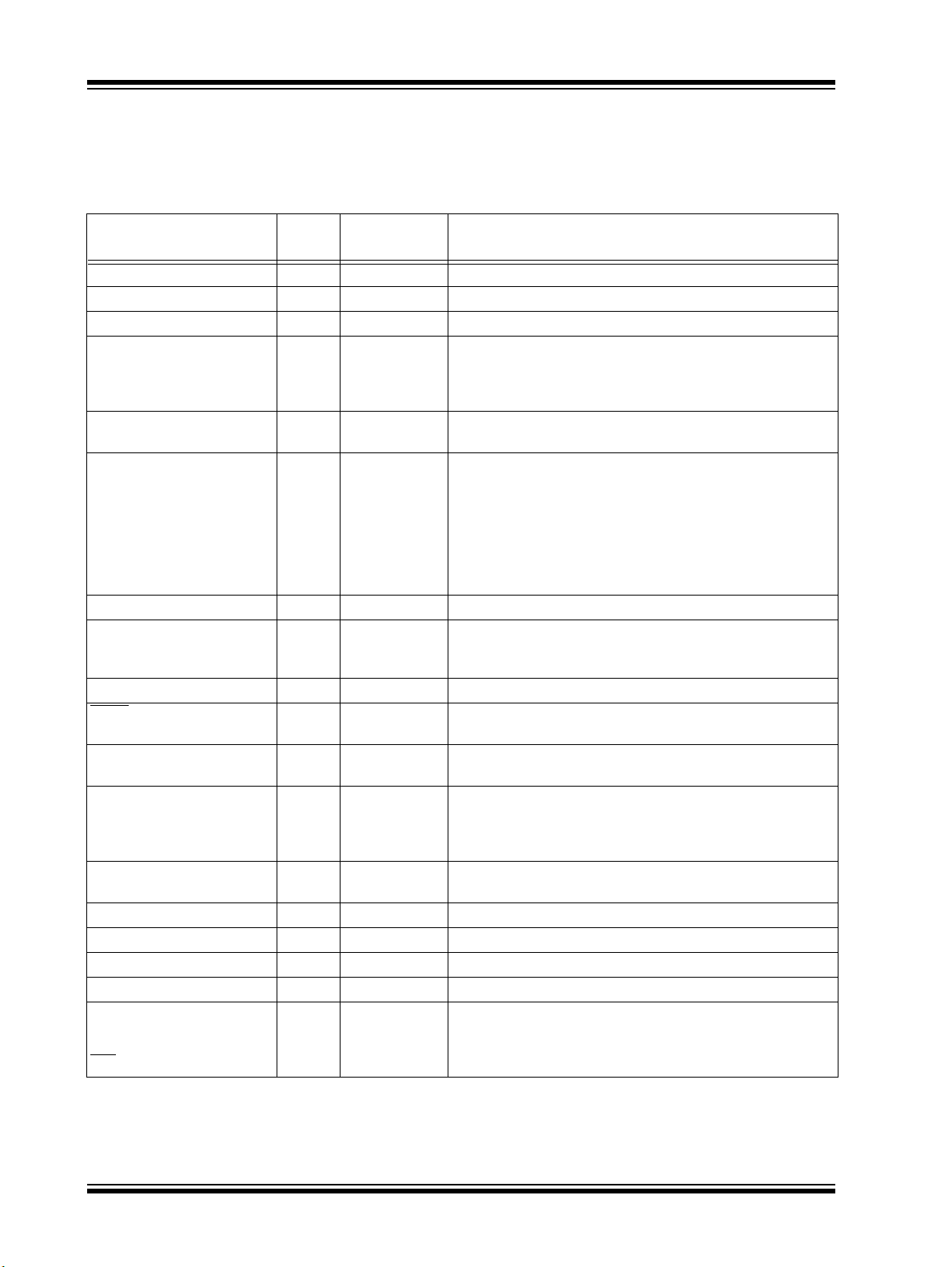

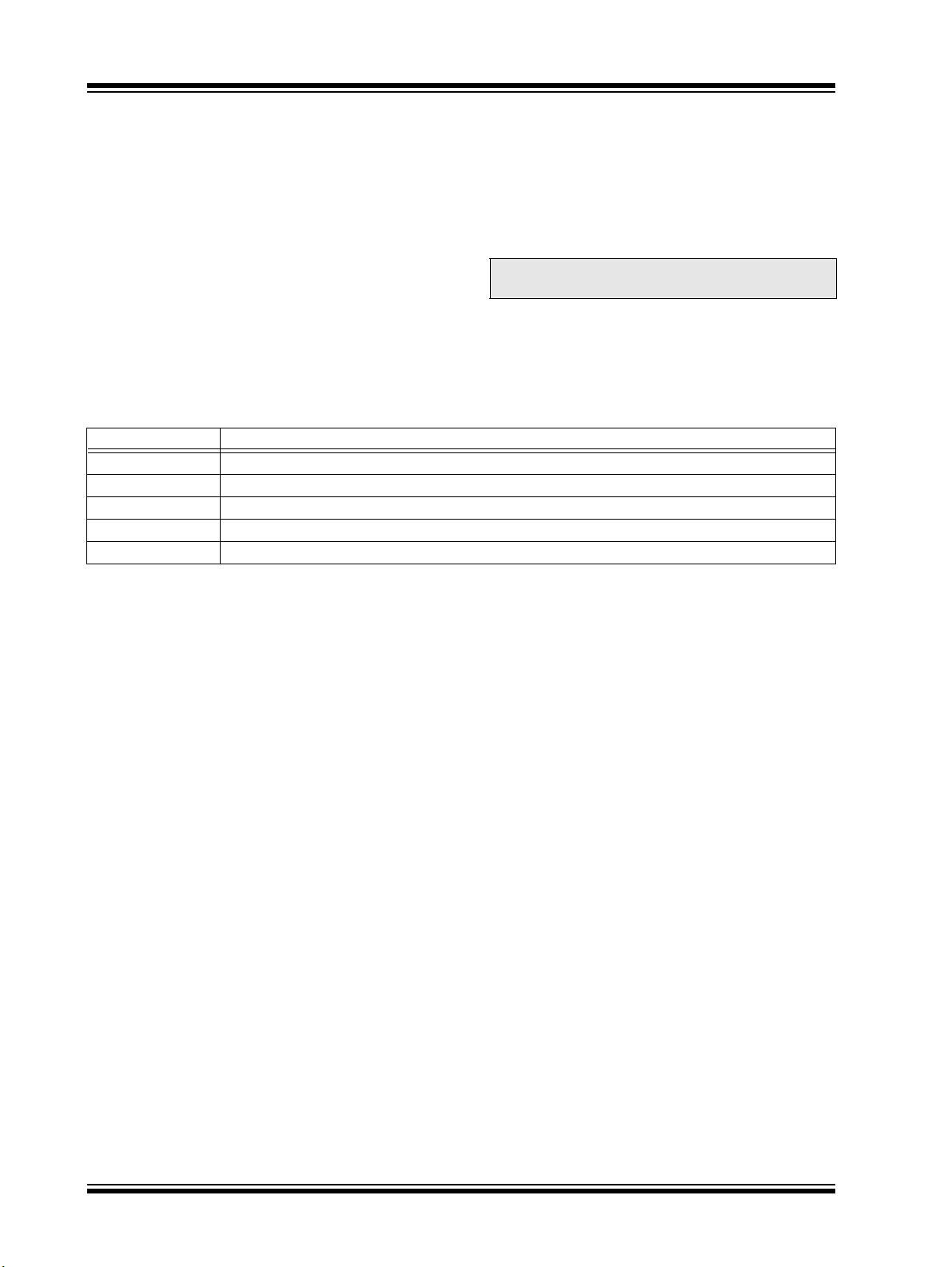

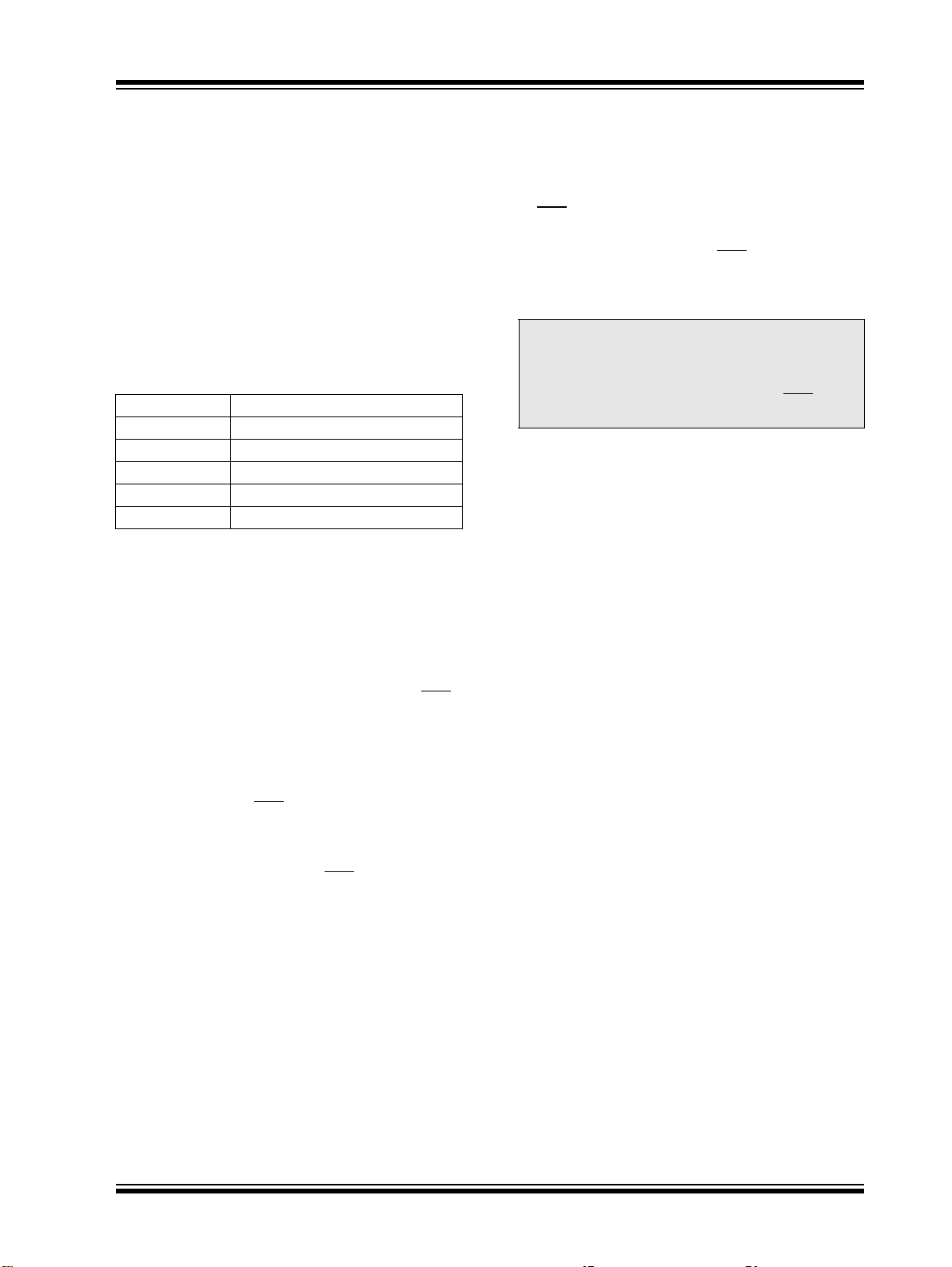

表 1-1 对器件的引脚配置和端口引脚的复用功能进行了

简要描述。端口引脚可具有多种功能。当发生复用时,

外设模块的功能要求可强制改写端口引脚的数据方向。

表 1-1: 引脚说明

引脚名称

AN0 - AN9 I Analog

DD PP

AV

AVSS PP

CLKI

CLKO

CN0 - CN7 I ST

EMUD

EMUC

EMUD1

EMUC1

EMUD2

EMUC2

EMUD3

EMUC3

IC1 - IC2 I ST

INT0

INT1

INT2

LVDI N I Anal og

MCLR

OC1-OC2

OCFA

OSC1

OSC2

PGD

PGC

RB0 - RB9 I/O ST

RC13 - RC15 I/O ST

RD0, RD8 - RD9 I/O ST

RF2 - RF5 I/O ST

SCK1

SDI1

SDO1

SS1

引脚

类型

I

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

I/P ST

O

I

I

I/O

I/O

I

I/O

I

O

I

图注: CMOS = CMOS 兼容输入或输出 Analog = 模拟输入

ST = CMOS 电平的施密特触发器输入 O=输出

I=输入 P=电源

缓冲器

类型

ST/CMOS

-

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

-

ST

ST/CMOS

-

ST

ST

ST

ST

—

ST

模拟输入通道。

模拟模块正电源。

模拟模块的参考地。

外部时钟源输入。总是与 OSC1 引脚功能相关联。

振荡器晶振输出。在晶振模式下,连接到晶振或谐振器。在 RC

和 EC 模式下,可选择作为 CLKO。总是与 OSC2 引脚功能相关

联。

输入电平变化通知输入。

可通过软件编程设定所有输入为内部弱上拉。

ICD 主通信通道数据输入 / 输出引脚。

ICD 主通信通道时钟输入 / 输出引脚。

ICD 第二通信通道数据输入 / 输出引脚。

ICD 第二通信通道时钟输入 / 输出引脚。

ICD 第三通信通道数据输入 / 输出引脚。

ICD 第三通信通道时钟输入 / 输出引脚。

ICD 第四通信通道数据输入 / 输出引脚。

ICD 第四通信通道时钟输入 / 输出引脚。

捕捉输入 1 和 2

外部中断 0

外部中断 1

外部中断 2

低电压检测参考电压输入引脚。

主复位输入或编程电压输入。本引脚为低电平有效的器件复位输

入端。

比较输出 1 和 2。

比较故障 A 输入。

振荡器晶振输入。配置为 RC 模式时,为 ST 缓冲器;否则为

CMOS。

振荡器晶振输出。在晶振模式下,连接到晶振或谐振器。在 RC

和 EC 模式下,可选择作为 CLKO。

在线串行编程数据输入/输出引脚。

在线串行编程时钟输入引脚。

PORTB 为双向 I/O 口。

PORTC 为双向 I/O 口。

PORTD 为双向 I/O 口。

PORTF 为双向 I/O 口。

SPI1 的同步串行时钟输入 / 输出。

SPI1 数据输入。

SPI1 数据输出。

SPI1 从同步。

说明

DS70139E_CN 第14 页 2007 Microchip Technology Inc.

Page 17

dsPIC30F2011/2012/3012/3013

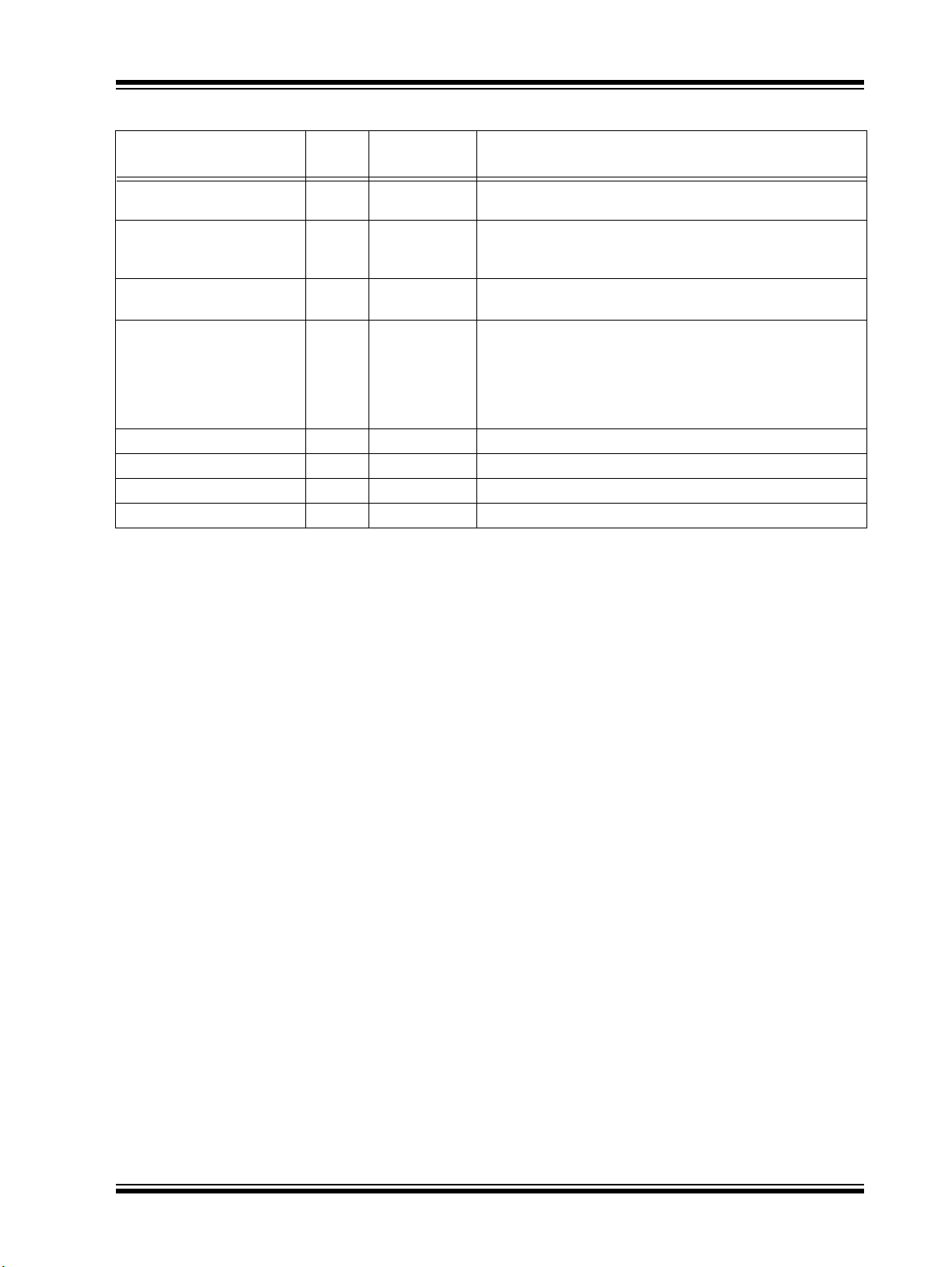

表 1-1: 引脚说明 (续)

引脚名称

SCL

SDA

SOSCO

SOSCI

T1CK

T2CK

U1RX

U1TX

U1ARX

U1ATX

U2RX

U2TX

V

DD P

V

SS P

REF+IAnalog

V

REF-IAnalog

V

引脚

类型

I/O

I/O

O

I

I

I

I

O

I

O

I

O

图注: CMOS = CMOS 兼容输入或输出 Analog = 模拟输入

ST = CMOS 电平的施密特触发器输入 O=输出

I=输入 P=电源

缓冲器

类型

ST

ST

-

ST/CMOS

ST

ST

ST

-

ST

-

ST

-

- 逻辑电路和 I/O 引脚的正电源。

- 逻辑电路和 I/O 引脚的参考地。

2

用于 I

C 的同步串行时钟输入 / 输出。

2

用于 I

C 的同步串行数据输入 / 输出。

32 kHz 低功耗晶振输出。

32 kHz 低功耗晶振输入。配置为 RC 模式时,为 ST 缓冲器;否

则为 CMOS。

Timer1 外部时钟输入。

Timer2 外部时钟输入。

UART1 接收。

UART1 发送。

UART1 备用接收。

UART1 备用发送。

UART2 接收。

UART2 发送。

模拟参考电压 (高电压)输入。

模拟参考电压 (低电压)输入。

说明

2007 Microchip Technology Inc. DS70139E_CN 第 15 页

Page 18

dsPIC30F2011/2012/3012/3013

注:

DS70139E_CN 第16 页 2007 Microchip Technology Inc.

Page 19

dsPIC30F2011/2012/3012/3013

2.0 CPU 架构概述

注: 本数据手册总结了 dsPIC30F 系列器件的功能,但是不

应把本手册当作无所不包的参考手册来使用。有关 CPU、外

设、寄存器说明和一般器件功能的更多信息,请参见

《dsPIC30F 系列参考手册》(DS70046E_CN)。有关器件

指令集和编程的更多信息,请参见 《dsPIC30F/33F 程序员

参考手册》(DS70157B_CN)。

本章概述了 dsPIC30F 的 CPU 架构,其内核具有 24 位

指令字。 程序计数器(PC)为 23 位宽,且最低有效位

(Least Significant bit, LSb)总是处于清零状态

(见第 3.1 节 “程序地址空间”)。 除某些专用指令

外,在正常程序执行期间,忽略最高有效位 (Most

Significant bit,MSb)。 鉴于此,PC 最多可寻址 4M 指

令字的用户程序空间。 它使用指令预取机制来帮助维持

吞吐量。 使用 DO 和 REPEAT 指令支持无需循环计数管

理开销的程序循环结构,这两条指令在任何时候都可被

中断。

2.1 内核概述

工作寄存器阵列由 16 个 16 位寄存器组成,每个工作寄

存器都可以充当数据、地址或地址偏移量寄存器。 工作

寄存器 (W15)用作中断和调用操作的软件堆栈指针。

数据空间为 64 KB (32K 字),它被分成两块,分别称

为 X 数据存储区和 Y 数据存储区。 每个存储区都有各自

独立的地址发生单元 (Address Generation Unit,

AGU)。 大部分指令只通过 X 存储区 AGU 进行操作,

这样对外界而言数据空间就是单独而统一的。 乘-累加

(MAC)类双源操作数 DSP 指令通过 X 和 Y 的 AGU 进

行操作,将数据地址空间分成两个部分 (见第 3.2 节

“数据地址空间”)。 X 和 Y 数据空间的边界视具体器件

而定,不能由用户修改。 每个数据字由 2 个字节组成,

大部分指令可以按字或字节对数据进行寻址。

访问程序存储器中的数据的方法有两种:

• 数据存储空间的高 32 KB 可以映射到程序空间的

下半部分 (用户空间),映射的边界可以是任何

16K 程序字边界,边界由 8 位的程序空间可视性页

( Program Space Visibility Page, PSVPAG)寄

存器定义。这种映射功能让任何指令都能像访问数

据空间一样访问程序空间。但访问需要额外占用一

个指令周期。 且使用此方法仅能访问每个指令字的

低 16 位。

• 也可以通过表读 / 表写指令使用工作寄存器对程序

空间内大小为 32K 字的页进行线性间接寻址。 可

使用表读和表写指令访问一个指令字的所有 24

位。

X和 Y 地址空间都支持无开销的循环缓冲区(模寻址)。

模寻址主要用于减少 DSP 算法的循环开销。

X AGU 还支持对目的有效地址的位反转寻址,从而大

幅简化了基 2 FFT 算法对输入或输出数据的重新排序。

欲知有关模寻址和位反转寻址的详细信息,请参见第

4.0 节 “地址发生器单元”。

内核支持固有 (无操作数)寻址、相对寻址、立即数寻

址、存储器直接寻址、寄存器直接和寄存器间接寻址,

以及寄存器偏移量和立即数偏移量寻址模式。 指令根据

其功能要求,与预定义的寻址模式相关。

对于大多数指令,在每个指令周期内,内核能执行一次

数据 (或程序数据)存储器读操作、一次工作寄存器

(数据)读操作、一次数据存储器写操作和一次程序(指

令)存储器读操作。 因此,可以支持 3 操作数的指令,

使 C=A + B操作能在单周期内执行。

内核包含一个 DSP 引擎,从而能够显著增强内核的运

算和吞吐能力。 DSP 引擎具备一个高速 17 位 x 17 位乘

法器、一个 40 位 ALU、两个 40 位饱和累加器和一个

40 位双向桶形移位寄存器。 在单个周期内,至多可将累

加器或工作寄存器中的数据右移 15 位或左移 16 位。

DSP 指令可以无缝地与所有其他指令一起操作,其设计

可实现最佳的实时性能。 MAC类指令可以同时从存储器

中取出两个数据操作数并将两个W寄存器相乘。 为了能

够同时取两个数据操作数,数据空间对于这些指令拆分

为两块,但对所有其他指令保持线性。对于 MAC 类指

令,这是通过将某些工作寄存器专用于每个地址空间,

以透明而灵活的方式实现的。

2007 Microchip Technology Inc. DS70139E_CN 第 17 页

Page 20

dsPIC30F2011/2012/3012/3013

内核不支持多级指令流水线, 它采用的是单级指令预取

机制,该机制在执行指令的前一个周期取要执行的指令

并对其部分译码,从而使可用执行时间最长。除了某些

特例外,大部分指令都在一个指令周期内执行完毕。

内核具有用于处理陷阱和中断的向量异常处理结构,提

供 62 个独立向量。 异常由最多 8 个陷阱 (其中 4 个保

留)和 54 个中断组成。 根据用户指定的 1 到 7 之间的

优先级 (1 为最低优先级, 7 为最高优先级),以及预

定义的 “自然顺序”,决定每个中断的优先级。陷阱的

优先级是固定的,其优先级范围是从 8 到 15。

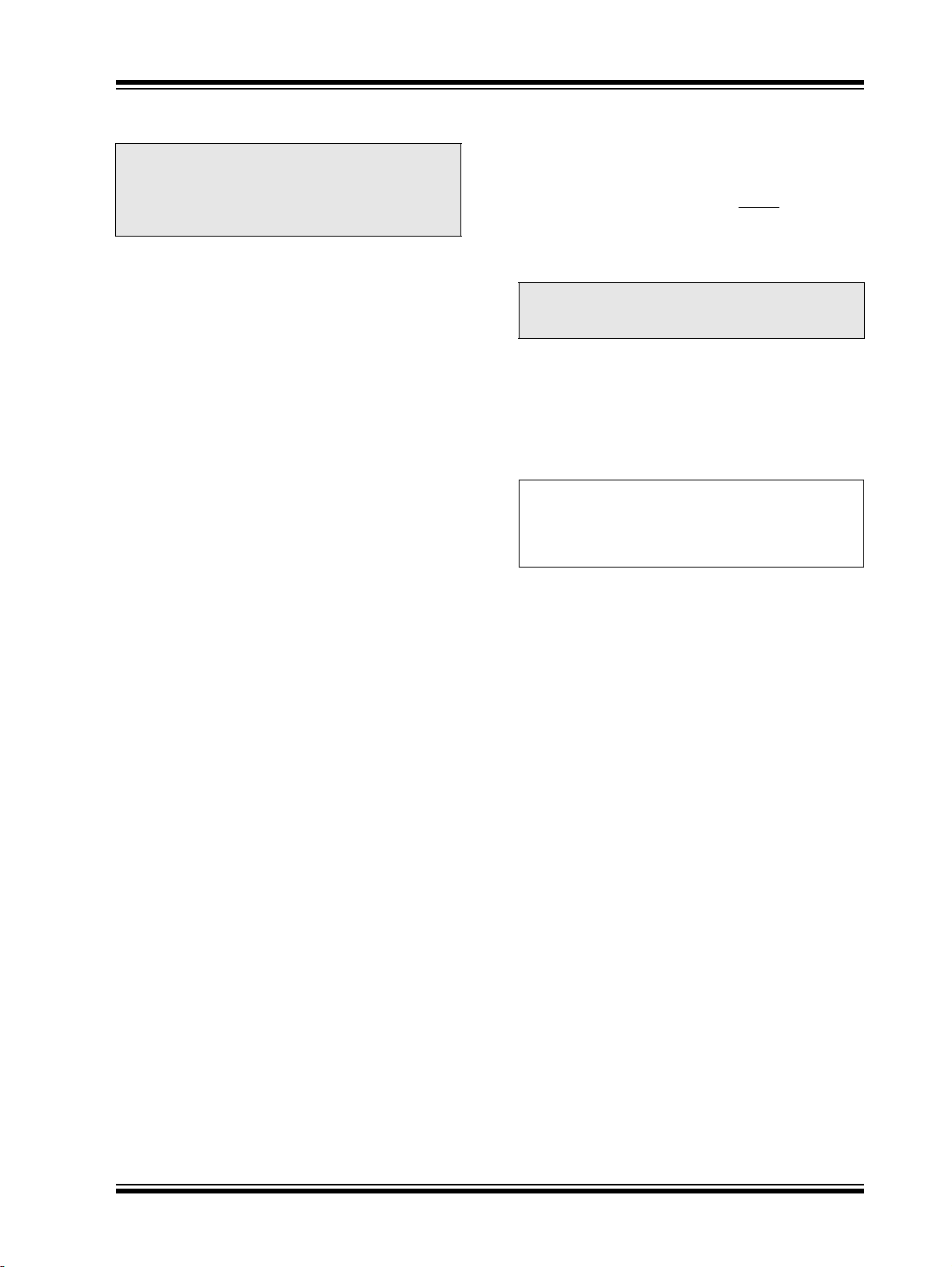

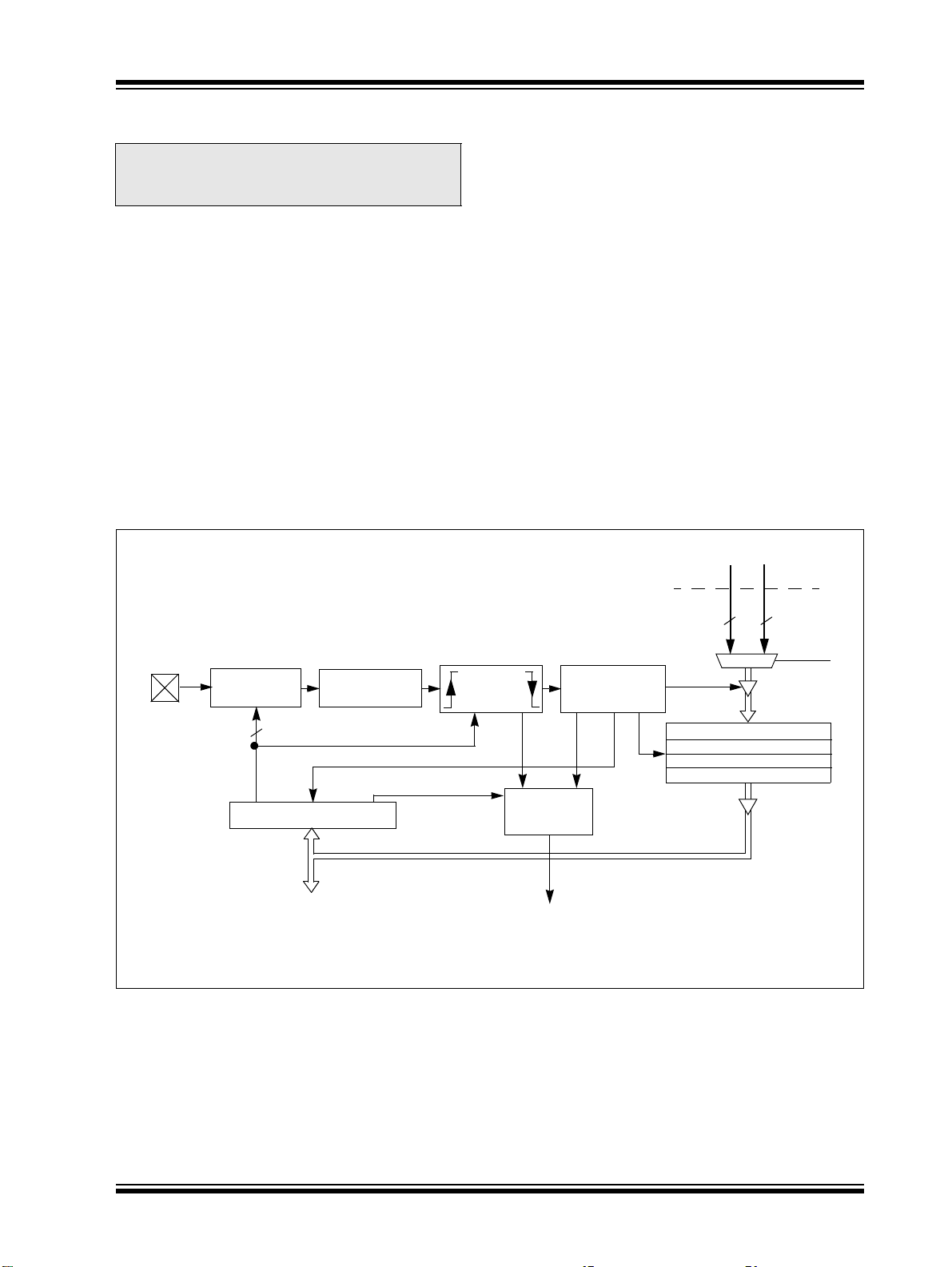

2.2 编程模型

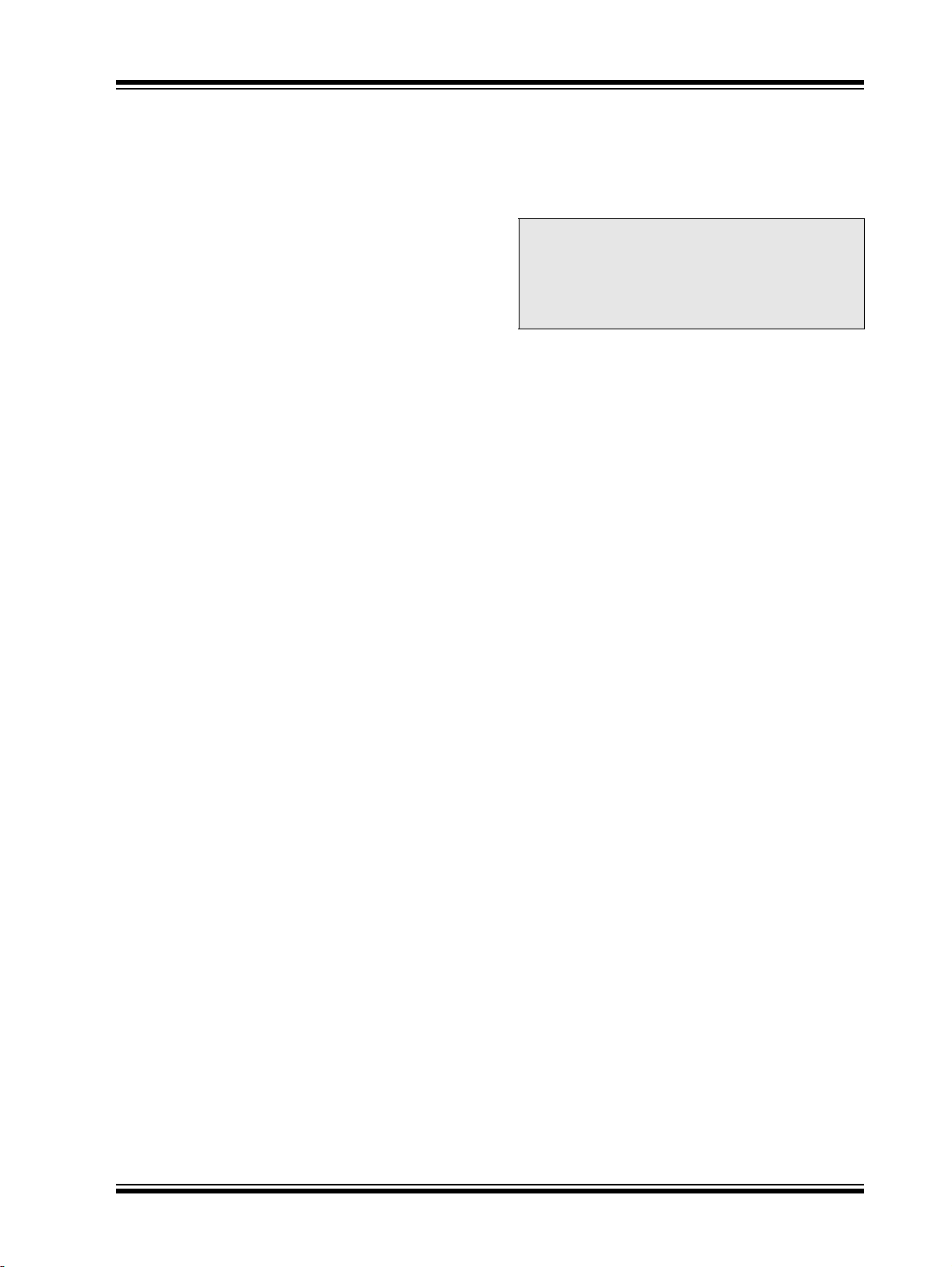

图 2-1 为编程模型,它包括 16 个 16 位工作寄存器(W0

至 W15)、 2 个 40 位累加器 (ACCA 和 ACCB)、 状

态寄存器 (SR)、数据表页寄存器 (TBLPAG)、程序

空间可视性页寄存器(PSVPAG)、 DO 和 REPEAT 寄

存器(DOSTART、DOEND、 DCOUNT 和 RCOUNT)

以及程序计数器(PC)。 工作寄存器可充当数据、地址

或偏移量寄存器。 所有寄存器均为存储器映射。 W0 用

作执行文件寄存器寻址的 W 寄存器。

其中的一些寄存器有与之关联的影子寄存器(见图2-1)。

影子寄存器被用作临时保存寄存器,它能够在事件发生

时将其主寄存器中的内容送入其中或将自身内容送回主

寄存器。 影子寄存器都是不可直接访问的。 如下指令适

用于寄存器与影子寄存器间的数据传递。

• PUSH.S 和 POP.S

W0、 W1、 W2、 W3 和 SR (仅限 DC、 N、

OV、 Z 和 C 位)与对应的影子寄存器之间进行数

据传递。

• DO 指令

循环开始时, DOSTART、 DOEND 和 DCOUNT

寄存器的内容压入影子寄存器,在循环结束时其内

容从各自的影子寄存器中弹出。

当对一个工作寄存器执行字节操作时,仅目的寄存器的

低字节 (Least Significant Byte, LSB)会受到影响。

但对于存储器映射的工作寄存器来说,可以通过对数据

存储空间进行字节宽度的访问来对工作寄存器的低字节

和高字节 (Most Significant Byte, MSB)进行操作,

这一点是很有益的。

2.2.1 软件堆栈指针 / 帧指针

dsPIC® DSC 器件具有一个软件堆栈。W15 是专用的软

件堆栈指针(Stack Pointer ,SP)。它可被异常处理、

子程序调用和返回自动修改,并且也能够被任何指令引

用 (方法与引用其他工作寄存器相同)。这样就简化了

对堆栈指针的读、写和操作 (例如,创建堆栈帧)。

注: 为了防止出现不对齐的堆栈访问,

W15<0> 始终保持为零。

复位时 W15 被初始化为 0x0800。 在初始化期间,用户

可以将 SP 重新编程以指向数据空间内的任何单元。

W14 是专用的堆栈帧指针,由 LNK 和 ULNK 指令定义。

并且也能够被任何指令引用(方法与引用其他工作寄存

器相同)。

2.2.2 状态寄存器

dsPIC DSC 内核具有一个 16 位状态寄存器(SR), 它

的低字节 (LSB)被称为 SR 低字节 (SRL),它的高

字节 (MSB)被称为 SR 高字节 (SRH)。 有关 SR 的

组成请参见图 2-1。

SRL 包含了所有的 MCU ALU 运算状态标志位(包括 Z

位),以 及 CPU中断优先级状态位IPL<2:0>和 REPEAT

有效状态位 RA。 在异常处理期间,SRL 与 PC 的 MSB

连在一起形成一个完整的字值,然后将该字的值压入堆

栈。

状态寄存器的高字节包含 DSP 加法器 / 减法器状态位、

DO 循环有效位 (DA)以及半进位 (DC)状态位。

2.2.3 程序计数器

程序计数器为 23 位宽; bit 0 总是为零。因此,PC 可

寻址最多 4M 指令字。

DS70139E_CN 第 18 页 2007 Microchip Technology Inc.

Page 21

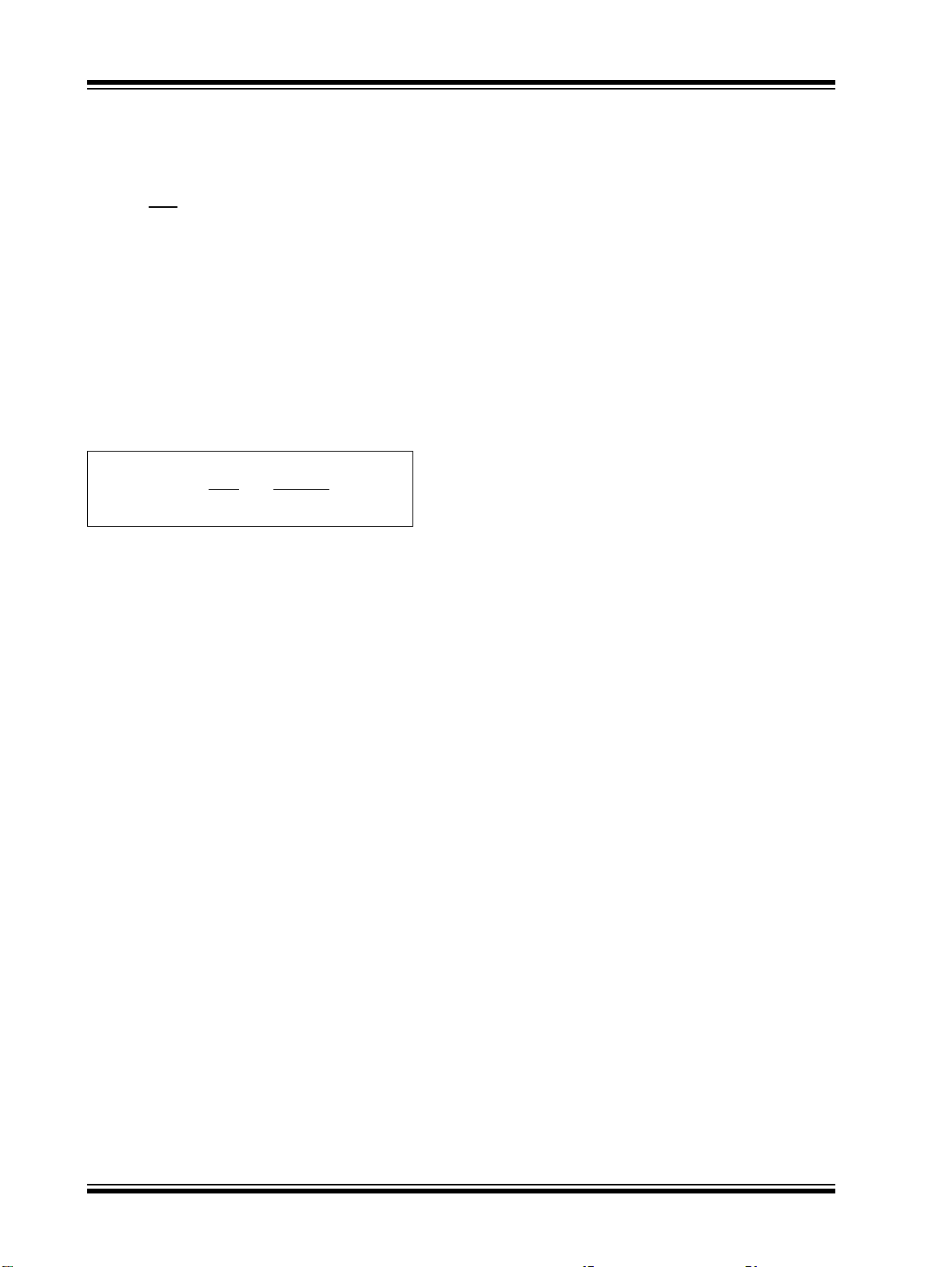

图 2-1: 编程模型

DSP 操作数

寄存器

DSP 地址

寄存器

dsPIC30F2011/2012/3012/3013

D0D15

W0/WREG

W1

W2

W3

W4

W5

W6

W7

W8

W9

W10

W11

W12/DSP 偏移量寄存器

W13/DSP 回写寄存器

W14/ 帧指针

W15/ 堆栈指针

工作寄存器

PUSH.S 影子寄存器

DO 影子寄存器

图注

DSP

累加器

PC22

7

22

22

TABPAG

TBLPAG

7

PSVPAG

PSVPAG

AD39 AD0AD31

ACCA

ACCB

0

数据表页地址

0

程序空间可视性页地址

15

15

DOSTART

DOEND

SPLIM

RCOUNT

DCOUNT

PC0

堆栈指针限制寄存器

AD15

程序计数器

0

0

REPEAT 循环计数器

0

DO 循环计数器

0

DO 循环起始地址

DO 循环结束地址

15

CORCON

OA OB SA SB

2007 Microchip Technology Inc. DS70139E_CN 第 19 页

OAB SAB

SRH

DA DC

IPL2 IPL1

RA

IPL0 OV

SRL

0

内核配置寄存器

N

C

Z

状态寄存器

Page 22

dsPIC30F2011/2012/3012/3013

2.3 除法支持

dsPIC DSC 器件支持16 位 /16 位有符号小数除法运算、

32 位 /16 位和 16 位 /16 位有符号和无符号整数除法运

算。所有除法运算都是单指令周期内的迭代操作。 支持

以下指令和数据长度:

1. DIVF — 16/16 有符号小数除法

2. DIV.sd — 32/16 有符号除法

3. DIV.ud — 32/16 无符号除法

4. DIV.s — 16/16 有符号除法

5. DIV.u — 16/16 无符号除法

16/16 除法与 32/16 除法类似(迭代次数相同),区 别 在

于发生第一次迭代时,被除数要执行零扩展或是符号扩

展。

表 2-1: 除法指令

指令 功能

DIVF

DIV.sd

DIV.s

DIV.ud

DIV.u

有符号小数除法: Wm/Wn → W0; Rem → W1

有符号除法: (Wm+1:Wm)/Wn → W0; Rem → W1

有符号除法: Wm/Wn → W0; Rem → W1

无符号除法: (Wm+1:Wm)/Wn → W0; Rem → W1

无符号除法: Wm/Wn → W0; Rem → W1

必须在一个 REPEAT 循环周期内执行除法指令。 任何其

他执行方式(例如一系列不连续的除法指令)都无法得

到正确的结果,因为指令流取决于 RCOUNT 的值。 除

法指令本身无法自动设置 RCOUNT 值,因此必须在

REPEAT 指令中明确且正确给出该值,如表 2-1 所示

(REPEAT 将执行目标指令 {操作数的值+ 1}次) 。DIV/

DIVF指令的REPEAT循环计数必须被设置为18次迭代。

因此,一个完整的除法运算需要 19 个指令周期。

注: 除法流是可中断的。但用户需要正确地保

护现场。

DS70139E_CN 第 20 页 2007 Microchip Technology Inc.

Page 23

dsPIC30F2011/2012/3012/3013

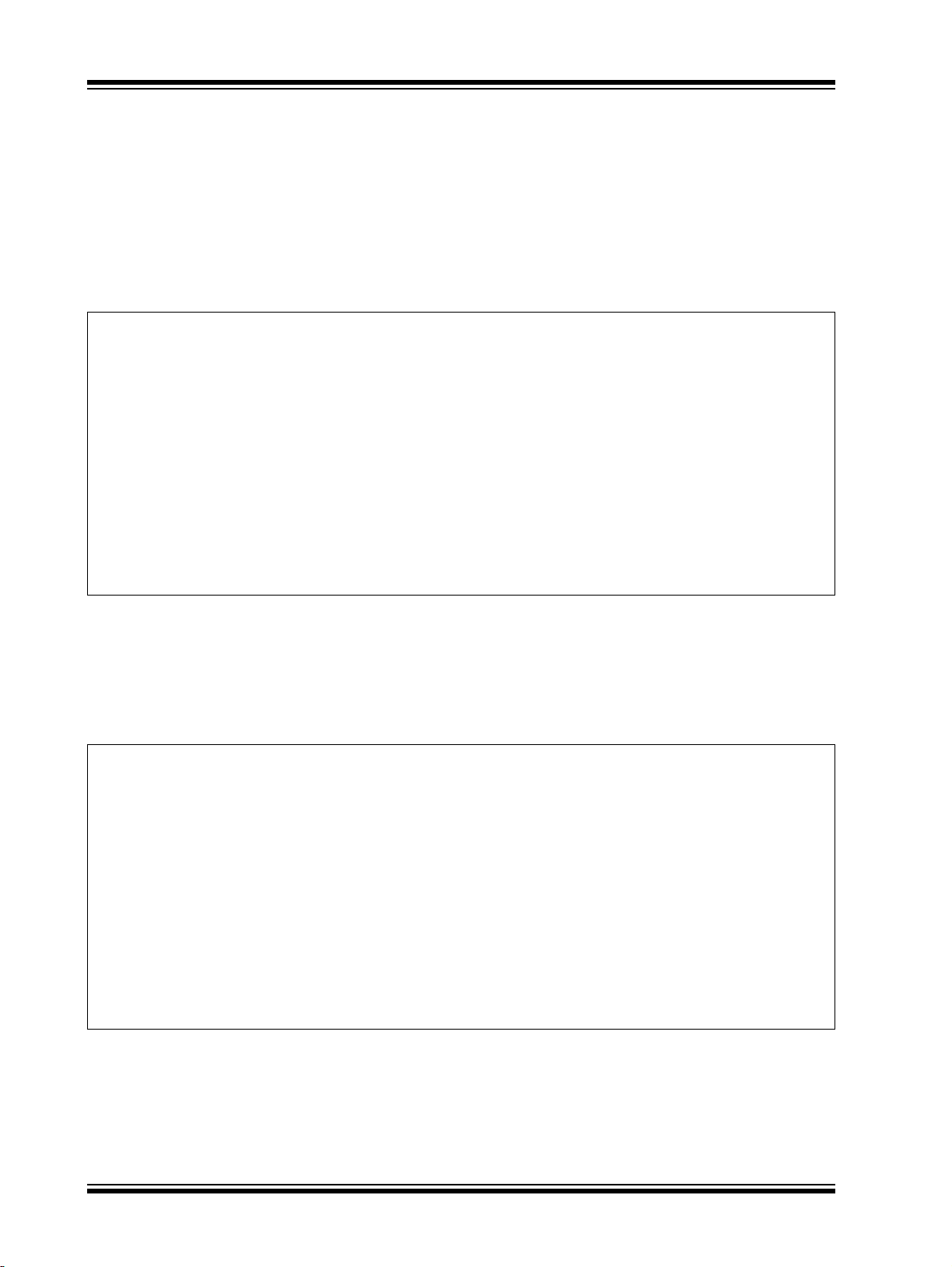

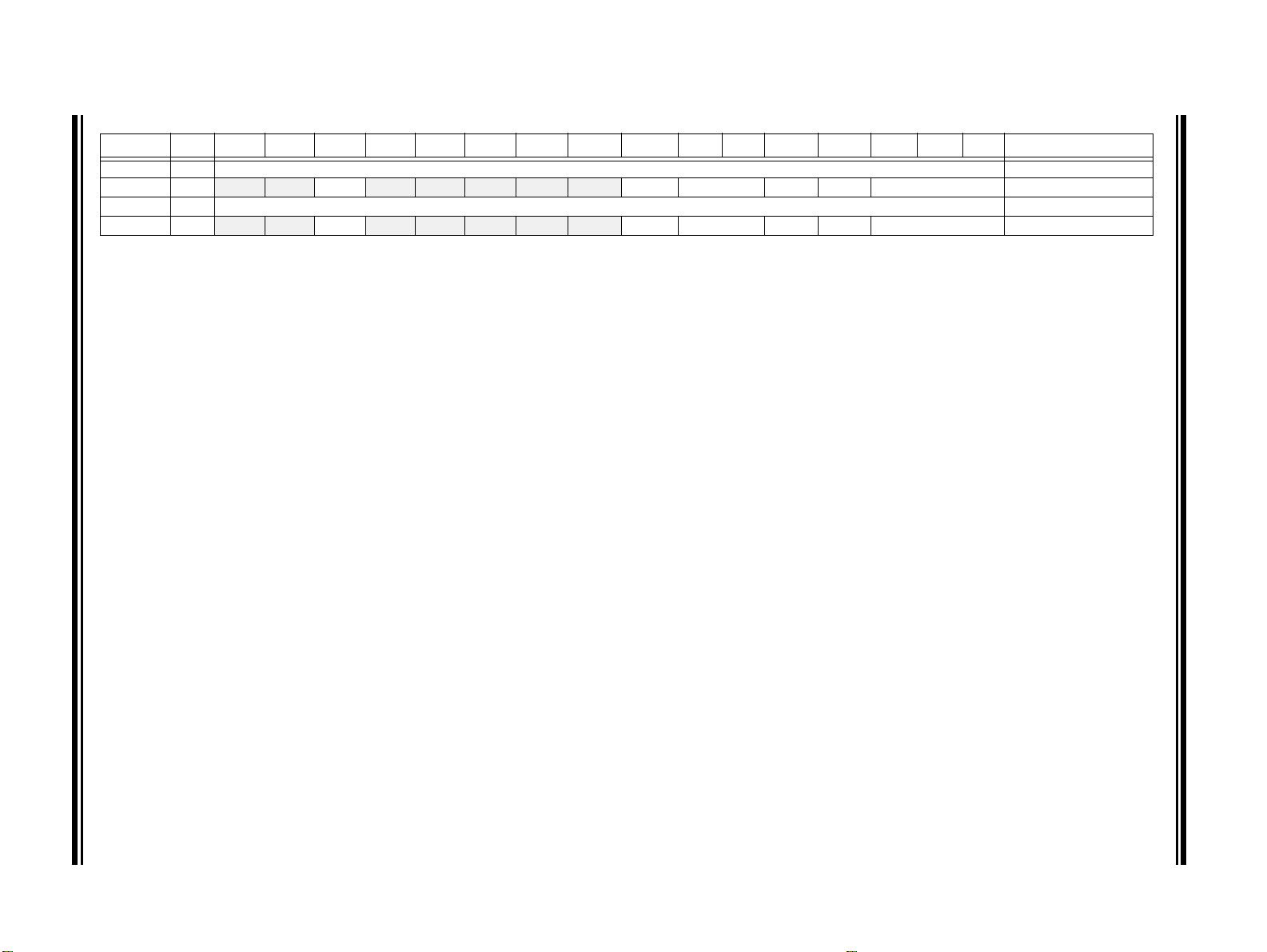

2.4 DSP 引擎

DSP 引擎由一个高速 17 位 x 17 位乘法器、一个桶形移

位寄存器和一个 40 位加法器 / 减法器 (带有两个目标

累加器以及舍入和饱和逻辑)组成。

DSP 引擎能够执行固有的“累加器—累加器”操作,而

无需额外数据。 这些指令为 ADD、 SUB 和 NEG。

dsPIC30F 采用单周期指令流架构,因此 DSP 引擎操作

和MCU指令流不能同时进行。 但某些MCU ALU和DSP

引擎资源可被同一条指令同时使用 (如 ED 和 EDAC)。

(有关 DSP 指令见表 2-2)。

表 2-2: DSP 指令汇总

指令 代数运算 ACC 回写 ?

CLR A = 0

ED A = (x – y)

EDAC A = A + (x – y)

MAC A = A + (x * y)

MAC A = A + x

MOVSAC

MPY A = x * y

MPY.N A = – x * y

MSC A = A – x * y

通过 CPU 内核配置寄存器(CORCON)的不同位可以

选择 DSP 引擎的不同功能,如下所示:

1. 小数或整数 DSP 乘法 (IF)。

2. 有符号或无符号 DSP 乘法 (US)。

3. 常规或收敛舍入 (RND)。

4. ACCA 自动饱和使能 / 禁止 (SATA)。

5. ACCB 自动饱和使能 / 禁止 (SATB)。

6. 用于写数据存储器的自动饱和使能/禁止(SATDW)。

7. 累加器饱和模式选择 (ACCSAT)。

注: 请参见表 3-3 了解 CORCON 的组成。

图 2-1 给出了 DSP 引擎的框图。

2

2

2

A 的值不发生变化 是

是

否

否

是

否

否

否

是

2007 Microchip Technology Inc. DS70139E_CN 第 21 页

Page 24

dsPIC30F2011/2012/3012/3013

图 2-2: DSP 引擎框图

40

进位 / 借位输出

进位 / 借位

输入

40 位累加器 A

40 位累加器 B

饱和

加法器

取补

40

舍入

逻辑

S

a

t

u

r

a

t

e

16

饱和

Y 数据总线

40

符号扩展

33

17 位

乘法器 / 定标器

16

40

40

16

桶形

移位

寄存器

32

32

40

16

X 数据总线

16

补零

到 / 来自 W 阵列

DS70139E_CN 第 22 页 2007 Microchip Technology Inc.

Page 25

dsPIC30F2011/2012/3012/3013

2.4.1 乘法器

17位 x 17位的乘法器可以进行有符号或无符号的运算,

其输出经过定标器进行换算后可支持 1.31 小数(Q31)

或 32 位整数结果。无符号操作数经过零扩展后,送入

乘法器输入值的第 17 位。有符号操作数经过符号扩展,

送入乘法器输入值的第 17 位。17 位 x 17 位乘法器 / 定

标器的输出是 33 位值,它将被符号扩展为 40 位。 整型

数据的固有表示形式为有符号的二进制补码值,其中,

MSb 定义为符号位。一般来说,N 位二进制补码整数的

范围为 -2

-32768 (0x8000) 至 32767 (0x7FFF),包括 0 在

内。对于 32 位整数,数据范围是 -2,147,483,648

(0x8000 0000) 至 2,147,483,645 (0x7FFF FFFF)。

当乘法器配置为小数乘法时,数据表示为二进制补码小

数,其中 MSb 定义为符号位,小数点暗含在符号位之

后(QX 格式)。暗含小数点的 N 位二进制补码小数的

范围是 -1.0 至(1 – 2

范围是 -1.0 (0x8000)至 0.999969482 (0x7FFF),

包括 0 在内,其精度为 3.01518x10

16x16 乘法运算将产生 1.31 乘积,其精度为 4.65661 x

10

同一个乘法器还用来支持 MCU 乘法指令,包括整数的

16 位有符号、无符号和混和符号乘法。

MUL 指令可以使用字节或字长度的操作数。字节操作数

将产生 16 位结果,而字操作数将产生 32 位结果,结果

存放在 W 寄存器阵列的指定寄存器中。

-10

。

N-1

N-1

到 2

– 1。对于 16 位整数,数据范围是

1-N

)。对 于 16 位小数,Q15 数据

-5

。在小数方式下,

2.4.2 数据累加器和加法器 / 减法器

数据累加器具有一个带有自动符号扩展逻辑的 40 位加

法器 / 减法器。它可以选择两个累加器 (A 或 B)之一

作为它累加前的源和累加后的目标。对于 ADD 和 LAC指

令,可选择通过桶形移位器在累加之前对将被累加或装

入的数据进行换算。

2.4.2.1 加法器 / 减法器、溢出和饱和

加法器 / 减法器为一个 40 位的加法器,一侧输入可以选

择为零,而另一侧的输入可以是数据的原码或补码。对

于加法, 进位 / 借位输入是高有效的,另一侧输入是数

据的原码 (没有求补的);对于减法,进位 / 借位

是低有效的, 另一侧输入是数据的补码。 由状态寄存器

中的 SA/SB 和 OA/OB 提供加法器 / 减法器的溢出状态:

• 从 bit 39 溢出:这是一种灾难性的溢出,因为它破

坏了累加器的符号位。

• 溢出到警戒位 bit 32 至 bit 39:这是一种可恢复的

溢出。 这些警戒位不完全相同时,该位置 1。

加法器有一个额外的饱和模块,如果选用该模块将控制

累加器的数据饱和。 饱和模块使用加法器的结果、上一

段所述的溢出状态位以及 SATA/B (CORCON<7:6>)

和 ACCSAT (CORCON<4>)模式控制位来决定何时

以及在何值达到饱和。

在状态寄存器中有 6 个支持饱和及溢出的位, 它们是:

1. OA:

ACCA 溢出至警戒位

2. OB:

ACCB 溢出至警戒位

3. SA:

ACCA 已饱和 (bit 31 溢出并饱和)

输入

或

ACCA 溢出至警戒位并饱和(bit 39溢出并饱和)

4. SB:

ACCB 已饱和 (bit 31 溢出并饱和)

或

ACCB 溢出至警戒位并饱和(bit 39溢出并饱和)

5. OAB:

OA 和 OB 的逻辑或 (OR)

6. SAB:

SA 和 SB 的逻辑或 (OR)

每次数据通过加法器 / 减法器,就会修改 OA 位和 OB

位。 置 1 时,它们表明最近的运算已经溢出到累加器警

戒位 (bit 32 到 bit 39)。 如果 OA 和 OB 位置 1 而且

INTCON1 寄存器中相应的溢出陷阱允许位(OVATE 和

OVBTE)也 置 1 的话,还可以选择用 OA 和 OB 位产生

算术警告陷阱 (见第 8.0 节 “中断”)。 这使得用户能

够立即采取措施,例如校正系统增益。

2007 Microchip Technology Inc. DS70139E_CN 第 23 页

Page 26

dsPIC30F2011/2012/3012/3013

每次数据通过加法器 / 减法器,就会修改 SA 和 SB 位,

但它们只能由用户清零。 置 1 时,它们表明累加器已经

溢出其最大范围 (32 位饱和是 bit 31,而 40 位饱和是

bit 39),将发生饱和 (如果饱和使能的话)。 如果没有

使能饱和,SA 和 SB 置 1 默认为 bit 39 溢出,即表明发

生灾难性溢出。 如果 INTCON1 寄存器中的 COVTE 位

置 1,当饱和被禁止时,SA 和 SB 位将产生算术警告陷

阱。

可选择将状态寄存器中的溢出和饱和状态位分别视作

OA 和 OB 的逻辑或 (OAB 位)以及 SA 和 SB 的逻辑

或(SAB 位)。 这样,只需要检查状态寄存器中的一个

位,编程人员就能够判断出是否有累加器溢出;检查状

态寄存器中另一个位就能判断出是否有累加器饱和。 对

于通常需要使用两个累加器的复数运算而言,这很有

用。

器件支持三种饱和及溢出模式:

1. Bit 39 溢出和饱和:

当发生 bit 39 溢出和饱和时,饱和逻辑将最大的正

数 9.31 (0x7FFFFFFFFF)或最小的负数 -9.31

值(0x8000000000)装入目标累加器。 SA 或 SB

位被置 1 且保持置 1 状态,直至被用户清零。 这

称为 “超饱和” ,为错误数据或不可预期的算法

问题 (例如,增益计算)提供了保护机制。

2. Bit 31 溢出和饱和:

当发生 bit 31 溢出和饱和时,饱和逻辑将最大的正

数 1.31 (0x007FFFFFFF)或最小的负数 -1.31

(0x0080000000)装入目标累加器。 SA 或 SB 位

被置 1 且保持置 1 状态,直至被用户清零。 当此

饱和模式生效时,不使用警戒位,因此 OA、 OB

或 OAB 位永远不会置 1。

3. Bit 39 灾难性溢出:

加法器的 bit 39 溢出会将 SA 或 SB 位置 1 并保

持该状态直至被用户清零。 不执行饱和操作,允

许累加器溢出 (破坏累加器的符号位) 。 如果

INTCON1 寄存器中的 COVTE 位置 1,则灾难性

溢出可能引发陷阱异常。

2.4.2.2 累加器 “ 回写”

MAC 类指令(MPY、 MPY.N、 ED 和 EDAC 除外)可以

选择将累加器高位字 (bit 16 至 bit 31)的舍入形式写

入数据存储空间,前提是当前指令不对该累加器进行操

作。 通过 X 总线将数据写入组合的 X 和 Y 地址空间来

执行此回写操作。 支持下列寻址模式:

1. W13,寄存器直接寻址:

非目标累加器的舍入内容以 1.15 小数形式写入

W13。

2. [W13] + = 2,带后递增的寄存器间接寻址:

非目标累加器的舍入内容以 1.15 小数形式写入

W13 指向的地址。 W13 的值递增 2 (对于字写

操作)。

2.4.2.3 舍入逻辑

舍入逻辑为一个组合的模块,在累加器写(存储)过程

中可以执行常规的 (有偏)或收敛的 (无偏)舍入功

能。 由 CORCON 寄存器的 RND 位的状态决定舍入模

式。 它会产生一个 16 位的 1.15 数据值,该值被送入到

数据空间写饱和逻辑。 如果指令没有明确指定舍入,那

么将会存储一个截取的 1.15 数据值而只丢弃低位字

(lsw)。

常规舍入取累加器 bit 15 的值,对其进行零扩展并将扩

展值加到 ACCxH 字 (累加器的 bit 16 至 bit 31) 。 如

果 ACCxL 字(累加器的 bit 0 至 bit 15)的值在 0x8000

到 0xFFFF (含 0x8000)之间, ACCxH 的值递增 1。

如果 ACCxL 字的值在0x0000 到0x7FFF 之间, ACCxH

的值不变。 此算法的结果经过一系列随机舍入操作,值

将稍稍偏大 (正偏)。

收敛 (或无偏)舍入操作与常规舍入操作相同,但

ACCxL 等于 0x8000 时例外。 在此种情况下,检查

ACCxH 的最低位 (累加器的 bit 16)。 如果该位为 1,

ACCxH 的值增 1。 如果该位为 0, ACCxH 的值不变。

假设 bit 16 本身就是一个随机数,那么此机制将消除任

何可能累加的舍入偏差。

SAC和 SAC.R指令通过X 总线将目标累加器内容的截取

值(SAC)或舍入值 (SAC.R)存储到数据存储空间。

(受数据饱和的影响,见第 2.4.2.4 节 “数据空间写饱

和”)。 注意对于 MAC 类指令,累加器回写操作以相同

的方式工作,通过 X 总线访问组合的 MCU (X 和 Y)

数据空间。 对于此类指令,总是对数据进行舍入。

DS70139E_CN 第 24 页 2007 Microchip Technology Inc.

Page 27

dsPIC30F2011/2012/3012/3013

2.4.2.4 数据空间写饱和

除加法器 / 减法器会饱和外,写数据空间也会饱和但不

影响源累加器的内容。 数据空间写饱和逻辑模块接受一

个来自舍入逻辑模块的 16 位 1.15 小数值作为其输入,

还接受来自源 (累加器)和 16 位舍入加法器的溢出状

态。 这些经过组合,用来选择恰当的 1.15 小数值作为输

出,写入至数据存储空间中。

如果 CORCON 寄存器的 SATDW 位置 1,则检测数据

(舍入和截取后的值)是否溢出并作相应调整。 针对大

于 0x007FFF 的输入数据,写入存储器的数据被强制为

最大的1.15值形式的正数0x7FFF。 针对小于0xFF8000

的输入数据,写入存储器的数据被强制为最大的1.15 值

形式的负数 0x8000。源累加器的最高位(bit 39)用来

决定被检测的操作数的符号。

如果 CORCON 寄存器中的 SATDW 位没有置 1,则输

入数据都将通过,在任何情况下都不会被修改。

2.4.3 桶形移位器

桶形移位寄存器在单个周期内可将数据逻辑或算术右移

或左移最多 16 位。 源操作数可为两个 DSP 累加器之一

或 X 总线(以支持对寄存器或存储器中的数据进行多位

移位)。

移位寄存器需要一个有符号二进制值来确定移位操作的

方向和幅度 (位的数量)。 正数将操作数右移。 负数将

操作数左移。 0 值不改变操作数。

桶形移位寄存器是 40 位宽的,于是,它为 DSP 移位操

作提供了 40 位的结果,而为 MCU 移位操作提供 16 位

的结果。来自 X 总线的数据在桶形移位寄存器中的存放

方式是:右移则数据存放在 bit 16 至 bit 31,左移则存

放在 bit 0 至 bit 15。

2007 Microchip Technology Inc. DS70139E_CN 第 25 页

Page 28

dsPIC30F2011/2012/3012/3013

注:

DS70139E_CN 第 26 页 2007 Microchip Technology Inc.

Page 29

dsPIC30F2011/2012/3012/3013

3.0 存储器构成

注: 本数据手册总结了 dsPIC30F 系列器件的功能,但是不

应把本手册当作无所不包的参考手册来使用。 有关CPU、外

设、寄存器说明和一般器件功能的更多信息,请参见

《dsPIC30F 系列参考手册》(DS70046E_CN)。 有关器件

指令集和编程的更多信息,请参见 《dsPIC30F/33F 程序员

参考手册》(DS70157B_CN)。

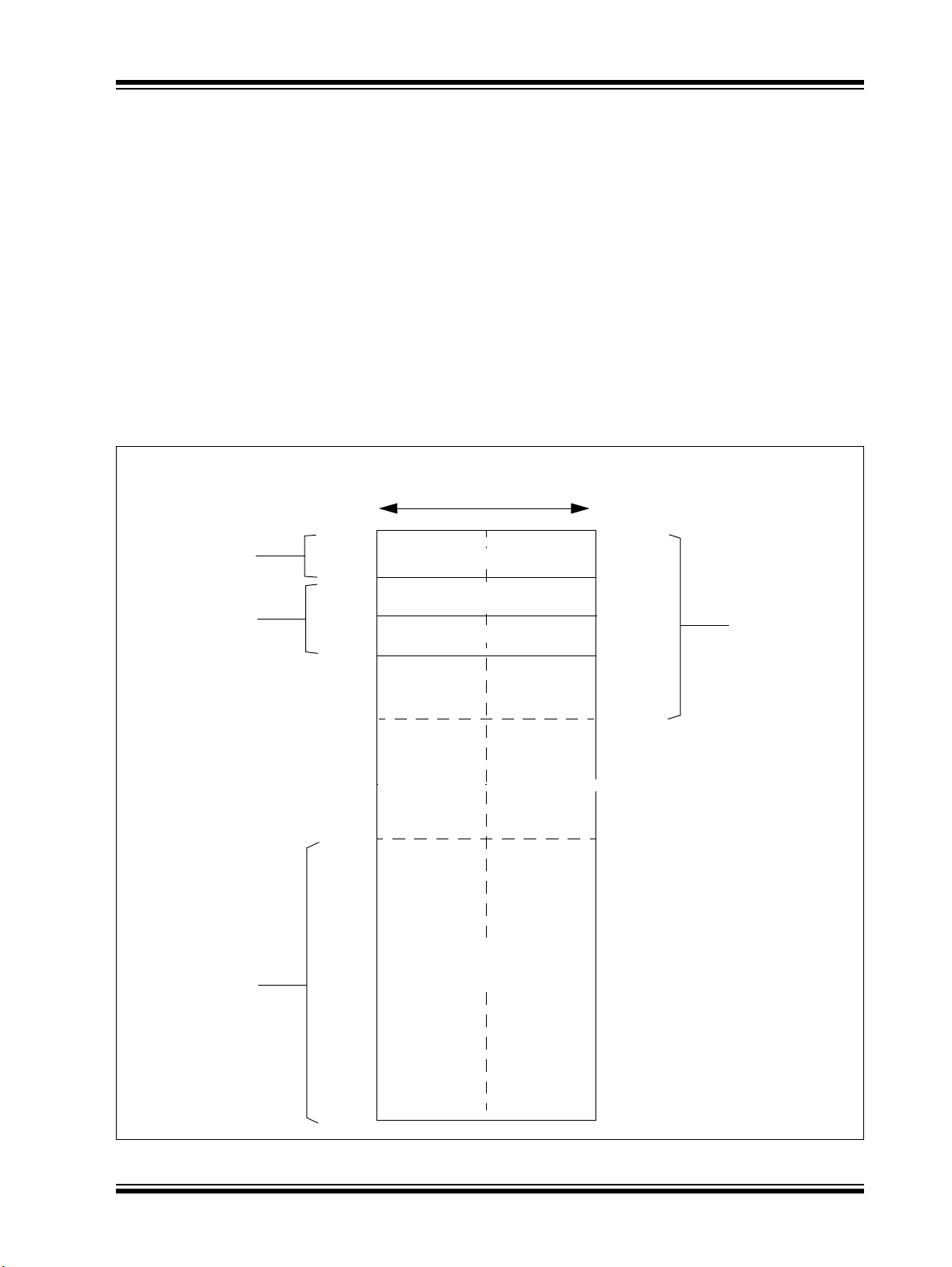

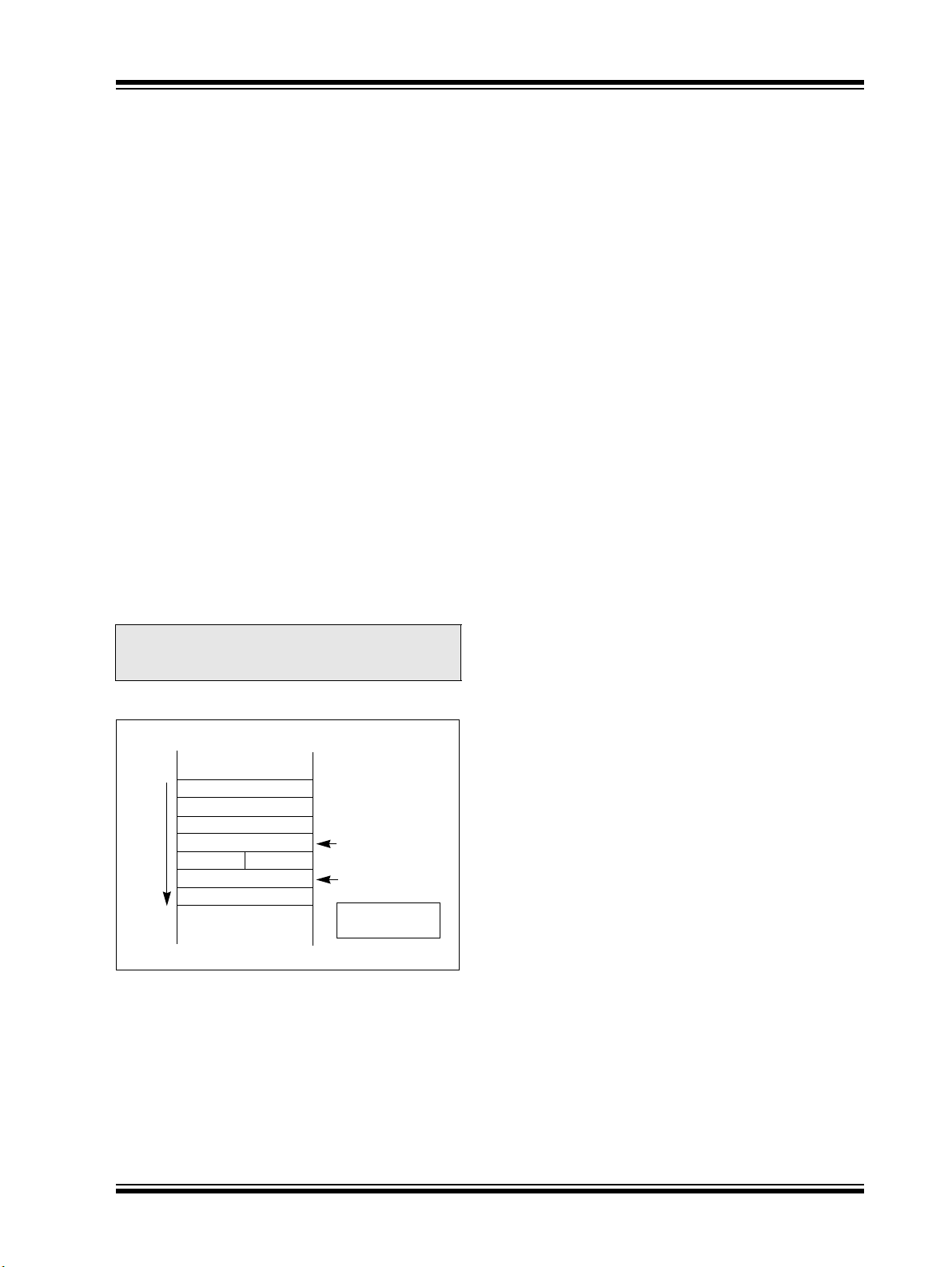

3.1 程序地址空间

程序地址空间为 4M 指令字。 dsPI30F2011/2012 的程

序存储空间映射如图 3-1 所示。 dsPI30F3012/3013 的

程序存储空间映射如图 3-2 所示。

当程序空间按表 3-1 中的定义映射到数据空间时,可由

来自 23 位 PC、表指令有效地址 (Effective Address,

EA)或数据空间 EA 的 24 位值寻址。 注意在访问连续的

程序字时,程序空间地址应该增 2 以与数据空间寻址相

一致。

用户只能访问程序存储空间的低 4M 指令字(地址范围

为 0x000000 至 0x7FFFFE);使用 TBLRD/TBLWT 指

令时情况有所不同,这两条指令使用 TBLPAG<7> 来确

定访问用户空间还是配置空间。 在表 3-1 (程序空间地

址构成)中,bit 23 为 1 允许访问器件 ID、用 户 ID 和配

置位。 否则, bit 23 总是处于清零状态。

2007 Microchip Technology Inc. DS70139E_CN 第 27 页

Page 30

dsPIC30F2011/2012/3012/3013

图 3-1: dsPIC30F2011/2012 程序存

储空间映射

空间

用户存储

复位 – GOTO 指令

复位 – 目的地址

中断向量表

保留

备用向量表

用户闪存

程序存储器

(4K 指令字)

保留

(读为 0)

000000

000002

000004

00007E

000080

000084

0000FE

000100

001FFE

002000

7FFFFE

800000

向量表

图 3-2: dsPIC30F3012/3013 程序存

储空间映射

复位 – GOTO 指令

复位 – 目的地址

中断向量表

保留

备用向量表

空间

用户存储

用户闪存

程序存储器

(8K 指令字)

保留

(读为 0)

数据 EEPROM

(1 KB)

000000

000002

000004

00007E

000080

000084

0000FE

000100

003FFE

004000

7FFBFE

7FFC00

7FFFFE

800000

向量表

配置存储

空间

保留

部件 ID(32 指令字)

保留

器件配置

寄存器

保留

DEVID(2)

8005BE

8005C0

8005FE

800600

F7FFFE

F80000

F8000E

F80010

FEFFFE

FF0000

FFFFFE

空间

配置存储

保留

部件 ID(32 指令字)

保留

器件配置

寄存器

保留

DEVID(2)

8005BE

8005C0

8005FE

800600

F7FFFE

F80000

F8000E

F80010

FEFFFE

FF0000

FFFFFE

DS70139E_CN 第 28 页 2007 Microchip Technology Inc.

Page 31

dsPIC30F2011/2012/3012/3013

表 3-1: 程序空间地址构成

访问类型

指令访问 用户

TBLRD/TBLWT

TBLRD/TBLWT

程序空间可视性 用户

用户

(TBLPAG<7> = 0)

配置

(TBLPAG<7> = 1)

图 3-3: 访问程序空间中的数据的地址生成方式

使用

程序

计数器

访问

空间

0

<23> <22:16> <15> <14:1> <0>

0 PC<22:1> 0

TBLPAG<7:0>

TBLPAG<7:0>

0 PSVPAG<7:0>

23 位

程序空间地址

数据 EA<15:0>

数据 EA<15:0>

数据 EA<14:0>

0 程序计数器

选择

使用

程序

空间

可视性

使用

表指令

用户 /

配置

空间

选择

注: 程序空间可视性不能用来对程序存储空间中字的 bit <23:16> 进行访问。

0

PSVPAG 寄存器

1/0

TBLPAG 寄存器

8 位

8 位

1

24 位 EA

EA

15 位

EA

16 位

字节

选择

2007 Microchip Technology Inc. DS70139E_CN 第 29 页

Page 32

dsPIC30F2011/2012/3012/3013

3.1.1 使用表指令访问程序存储器中的数据

由于此类器件的架构对 24 位宽的程序存储器取指。 因

此指令始终是对齐的。 由于采用的是改进的哈佛架构,

因此也可以在程序空间中存储数据。

访问程序空间的方法有 2 种: 通过特殊表指令,或通过

将16K 字大小的程序空间页重映射到数据空间的上半部

分(见第 3.1.2 节 “使用程序空间可视性访问程序存储

器中的数据”)。 TBLRDL和 TBLWTL指令提供了无需通

过数据空间,直接读写程序空间任何地址的低位字

(lsw)的方法, TBLRDH 和 TBLWTH 指令是可以把一

个程序空间字的最高 8 位作为数据存取的惟一方法。

要访问两个连续的 24 位程序字,PC 的递增量为 2。 这

使得程序存储器地址能够被直接映射到数据空间地址

中。 于是,程序存储器可以被看作是两个 16 位字宽的

地址空间,它们并排放置且具有相同的地址范围。

TBLRDL 和 TBLWTL 访问包含数据低位字的空间,

TBLRDH 和 TBLWTH 访问包含数据最高字节的空间。

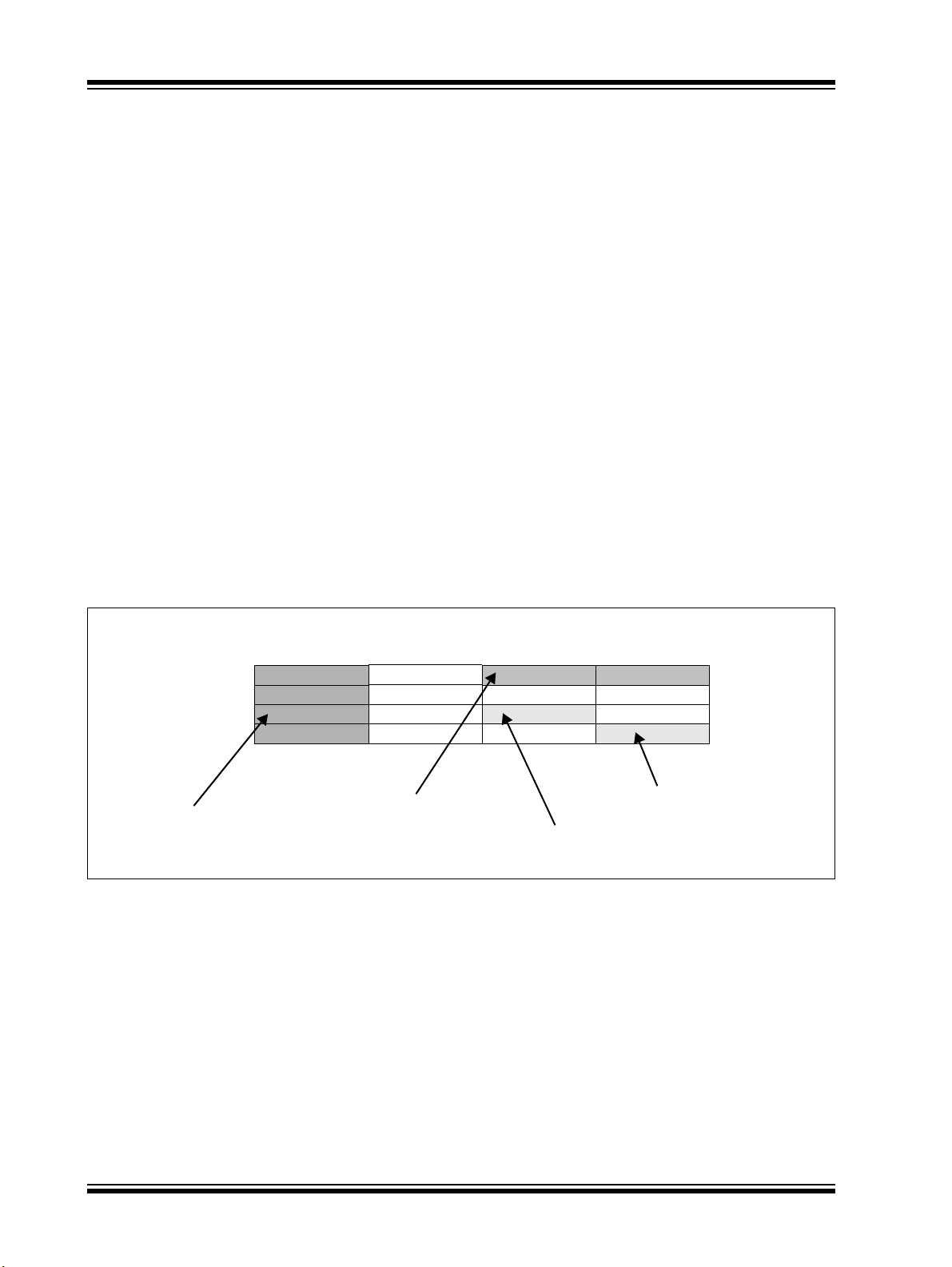

图 3-3 给出了表操作和数据空间访问(PSV = 1)时 EA

的构成方式。 在该图中, P<23:0> 指程序空间字,而

D<15:0> 指数据空间字。

提供了一组表指令,可使用它们来在程序空间和数据空

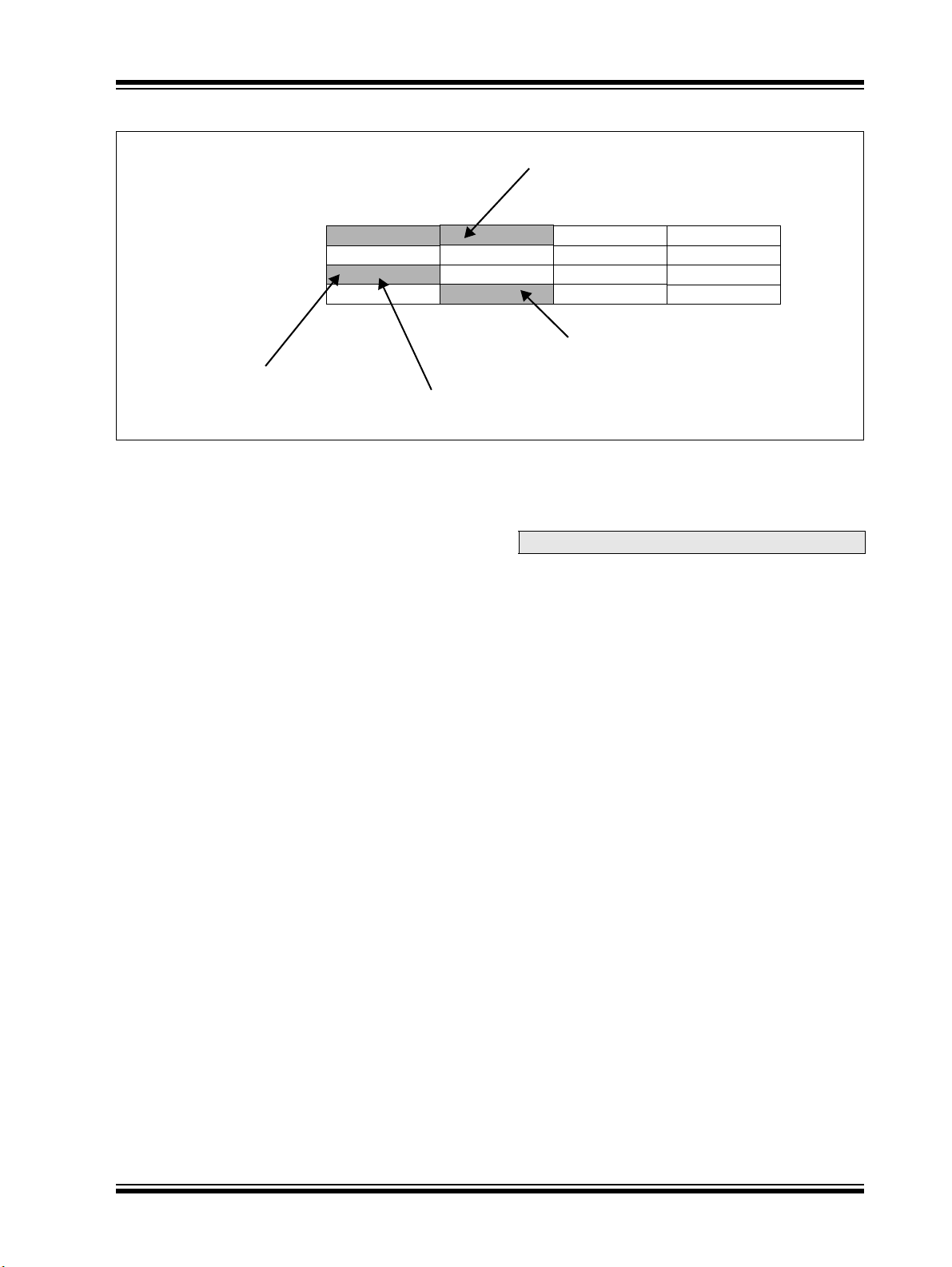

间之间传送字节或字大小的数据 (见图 3-4 和图 3-5)。

1. TBLRDL:对低位字执行表读操作

字:

读程序地址的低位字; P<15:0> 映射到

D<15:0>。

字节:

读程序地址的某个较低的字节;

当字节选择位 = 0 时,P<7:0> 映射到目标字节;

当字节选择位 = 1时,P<15:8>映射到目标字节。

2. TBLWTL:对低位字执行表写操作 (有关闪存编

程的详细信息见第 5.0 节 “闪存程序存储器”)

3. TBLRDH:对高位字执行表读操作

字:

读程序地址的高位字; P<23:16> 映射到

D<7:0> ; D<15:8> 将始终为零 (= 0)。

字节:

读程序地址的某个较高的字节;

当字节选择位 = 0 时,P<23:16> 映射到目标字

节;

当字节选择位 = 1 时,目标字节将始终为零 (=

0)。

4. TBLWTH:对高位字执行表写操作 (有关闪存编

程的详细信息见第 5.0 节 “闪存程序存储器”)

图 3-4: 程序数据表访问 (低位字)

PC 地址

0x000000

0x000002

0x000004

0x000006

程序存储器

“虚拟” 字节

(读为 0)

00000000

00000000

00000000

00000000

23

TBLRDL.W

16

8

TBLRDL.B (Wn<0> = 0)

TBLRDL.B (Wn<0> = 1)

0

DS70139E_CN 第 30 页 2007 Microchip Technology Inc.

Page 33

dsPIC30F2011/2012/3012/3013

图 3-5: 程序数据表访问 (MSB)

TBLRDH.W

PC 地址

0x000000

0x000002

0x000004

0x000006

程序存储器

“虚拟” 字节

(读为 0)

00000000

00000000

00000000

00000000

23

TBLRDH.B (Wn<0> = 1)

3.1.2 使用程序空间可视性访问程序存储器

中的数据

可选择将数据空间的高 32 KB 映射到任何 16K 字程序空

间页。 这提供了对存储在 X 数据空间的常量数据的透明

访问,而无需使用特殊指令(即 TBLRDL/H和 TBLWTL/

H 指令)。

如果数据空间 EA 的最高位置 1,且通过将内核控制寄

存器(CORCON)中的 PSV 位置 1 使能程序空间可视

性,就可以通过数据空间访问程序空间。 第2.4节“ DSP

引擎”中对 CORCON 的功能进行了讨论。

访问此区域的数据会增加一个额外的指令周期,因为需

要进行两次程序存储空间取操作。

注意,可寻址数据空间的上半部分始终位于 X 数据空间

内。 因此,当 DSP 操作使用程序空间映射来访问这个

存储区域时,Y数据空间通常应该存放 DSP 操作的状态

(变量)数据,而 X 数据空间通常应该存放系数 (常

量)数据。

尽管大于等于 0x8000 的每个数据空间地址直接映射到

对应的程序存储器地址(见图 3-6),但只使用 24 位程

序字的低 16 位来存储数据。 应对高 8 位进行编程强制

使得对其的访问为非法以维持器件的可靠性。 有关指令

编码的细节,请参见《dsPIC30F/33F 程序员参考手册》

(DS70157B_CN)。

16

TBLRDH.B (Wn<0> = 0)

注意,每访问一个程序存储字, PC 就会递增 2,数据空

间地址的低 15 位直接被映射到相应程序空间地址的低 15

位。其余位由程序空间可视性页寄存器(PSVPAG<7:0>)

提供,如图 3-6 所示。

注: 在表读 / 写操作时暂时禁止 PSV 访问。

对于在 REPEAT 循环外执行的使用 PSV 的指令:

• 以下指令除规定的执行时间外还需一个额外的指令

周期:

- 带数据操作数预取操作的 MAC 类指令

- MOV 指令

- MOV.D 指令

• 所有其他指令除规定的执行时间外还需两个额外的

指令周期。

对于在 REPEAT 循环内执行的使用 PSV 的指令:

• 以下指令除规定的执行时间外还需两个额外的指令

周期:

- 在第一次迭代时执行的指令

- 在最后一次迭代时执行的指令

- 在由于中断而退出循环前执行的指令

- 中断被处理后,在重新进入循环时执行的指令

• 对于在 REPEAT 循环的任何其他迭代中使用 PSV

访问数据的指令,其执行时间为一个周期。

8

0

2007 Microchip Technology Inc. DS70139E_CN 第 31 页

Page 34

dsPIC30F2011/2012/3012/3013

图 3-6: 将数据空间映射到程序空间的操作

数据空间

0x0000

EA<15> =

16

数据

空间

EA

EA<15> =

数据空间的上

半部分被映射

至程序空间

BSET CORCON,#2 ; PSV bit set

MOV #0x00, W0 ; Set PSVPAG register

MOV W0, PSVPAG

MOV 0x8200, W0 ; Access program memory location

15

0

15

1

; using a data space access

0x8000

15

0xFFFF

PSVPAG

0x00

地址

连接

程序空间

0x000000

(1)

8

23 15 0

23

数据读

0x001200

0x001FFF

注 1: PSVPAG 是一个 8 位寄存器,它包含了程序空间地址的 bit <22:15>。

DS70139E_CN 第 32 页 2007 Microchip Technology Inc.

Page 35

dsPIC30F2011/2012/3012/3013

3.2 数据地址空间

执行 MAC 类指令以外的任何指令时,X 空间由 64 KB 数

据地址空间 (包括了全部的 Y 空间地址)组成。 执行

内核具有两个数据空间。 可将这两个数据空间视为两个

独立的空间 (对于某些

性寻址空间(对于

DSP

指令)或是一个统一的线

MCU

指令)。 使用两个地址发生单元

(AGU)和相互独立的数据路径对这两个数据空间进行

访问。

3.2.1 数据存储空间映射

数据存储空间被分为两大块,它们是 X 数据空间和 Y 数

据空间。 该架构的关键之处在于 Y 空间是 X 空间的子

集,它完全包含在 X 空间内。 要提供一种表面看似线性

MAC类指令时,X块由不包括 Y 地址块(只用于数据读操

作)的 64 KB 数据地址空间组成。 也就是说,所有其他

指令将整个数据存储空间视作一个组合的地址空间。

MAC 类指令把 Y 地址空间从数据空间中分离出来,并使

用来自 W10 和 W11 的 EA 对 Y 空间寻址。 使用 W8 和

W9 对剩余的 X 数据空间寻址。 只有通过 MAC 类指令才

能同时访问这两个地址空间。

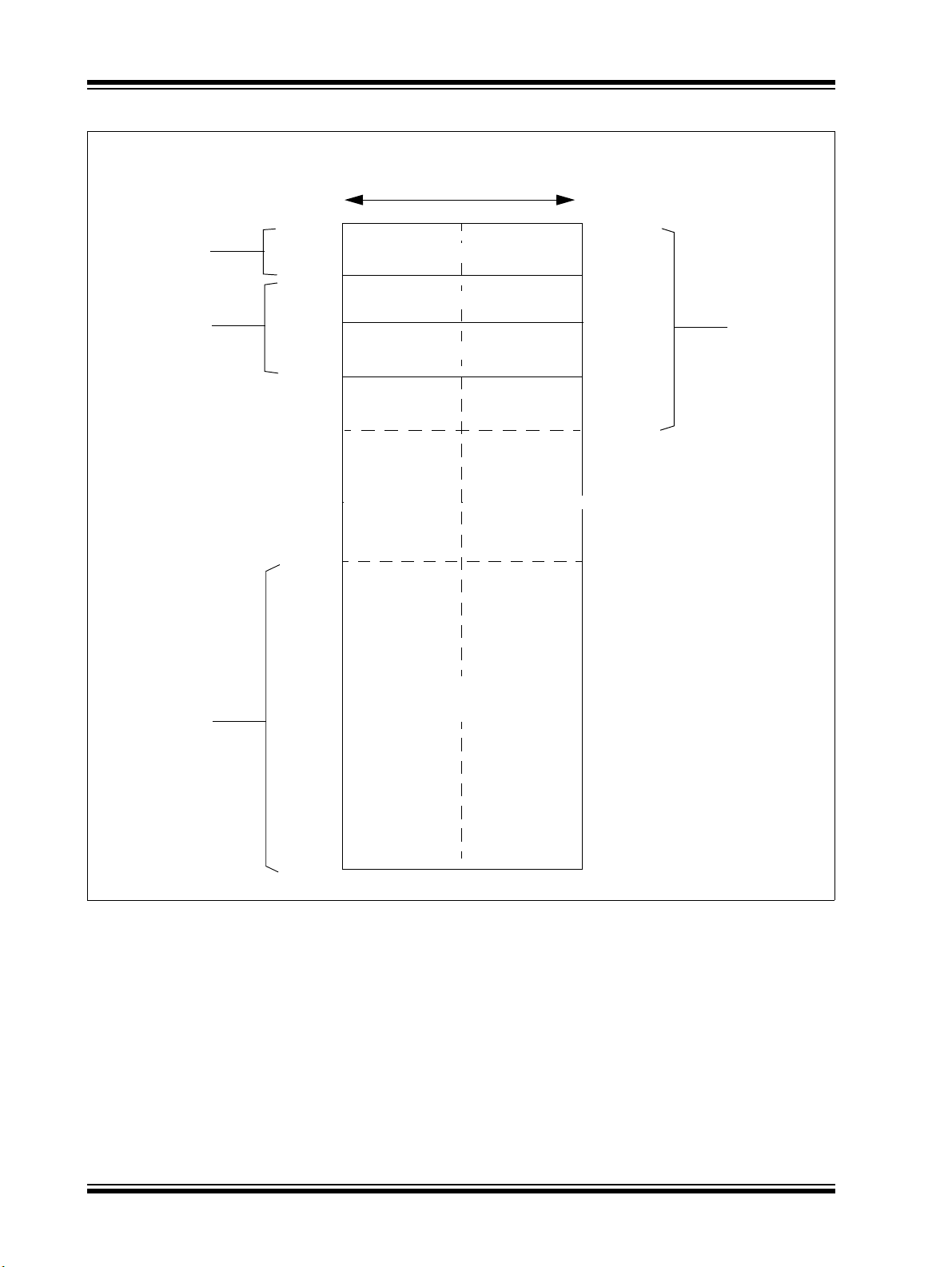

dsPI30F2011/2012的数据存储空间映射如图 3-7 所示。

dsPI30F2012/2013 的数据存储空间映射如图 3-8 所示。

的寻址空间, X 空间和 Y 空间需要具有连续的地址。

图 3-7: dsPIC30F2011/2012 数据存储空间映射

2 KB

SFR 空间

1 KB

SRAM 空间

MSB

地址

0x0001

0x07FF

0x0801

0x09FF

0x0A01

0x0BFF 0x0BFE

16 位

LSBMSB

SFR 空间

X 数据 RAM(X)

Y 数据 RAM(Y)

地址

0x0000

0x07FE

0x0800

0x09FE

0x0A00

0x0C000x0C01

LSB

8 KB

Near

数据

空间

可选择

映射至

程序

存储器

0x8001

0xFFFF

0x1FFE 0x1FFF

0x8000

X 数据

未实现(X)

0xFFFE

2007 Microchip Technology Inc. DS70139E_CN 第 33 页

Page 36

dsPIC30F2011/2012/3012/3013

图 3-8: dsPIC30F2011/3013 数据存储空间映射

2 KB

SFR 空间

2 KB

SRAM 空间

MSB

地址

0x0001

0x07FF

0x0801

0x0BFF

0x0C01

0x0FFF 0x0FFE

0x8001

16 位

LSBMSB

SFR 空间

X 数据 RAM(X)

Y 数据 RAM(Y)

LSB

地址

0x0000

0x07FE

0x0800

0x0BFE

0x0C00

0x10000x1001

0x1FFE 0x1FFF

0x8000

8 KB

Near

数据

空间

可选择

映射至

程序存储器

0xFFFF

X 数据

未实现(X)

0xFFFE

DS70139E_CN 第 34 页 2007 Microchip Technology Inc.

Page 37

dsPIC30F2011/2012/3012/3013

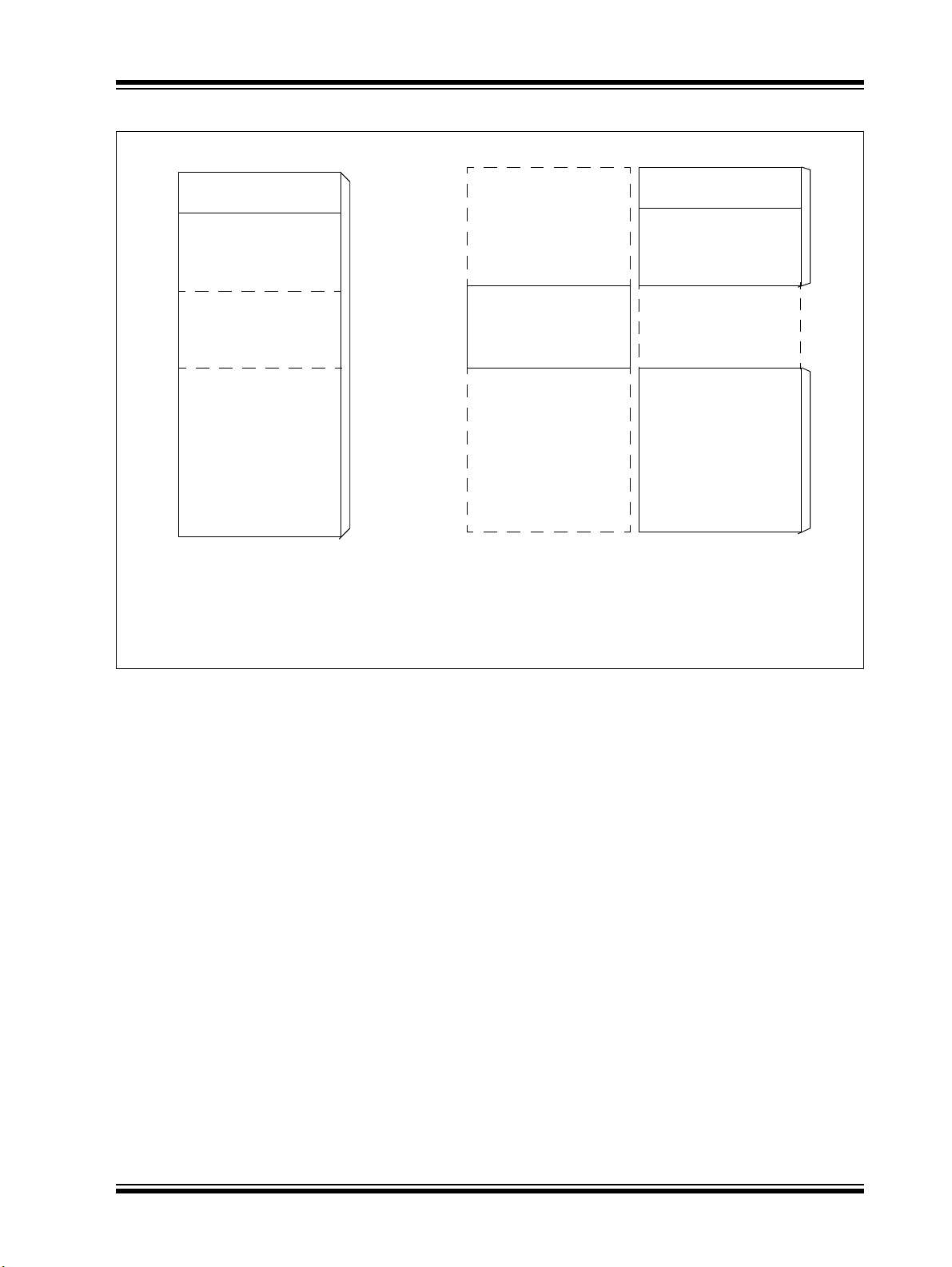

图 3-9: MCU 和 DSP (MAC 类)指令使用的数据空间的示例

SFR 空间

未用

(Y 空间)

X 空间

非 MAC 类操作(读 / 写) MAC 类操作(读)

MAC 类操作(写)

使用任何 W 寄存器的间接 EA 使用 W8 和 W9 的间接 EA 使用 W10 和 W11 的间接 EA

Y 空间

未用

SFR 空间

未用

X 空间

X 空间

2007 Microchip Technology Inc. DS70139E_CN 第 35 页

Page 38

dsPIC30F2011/2012/3012/3013

3.2.2 数据空间

X 数据空间可被所有指令使用且支持所有寻址模式。 其

读写数据总线是相互独立的。 X读数据总线是所有将数

据空间视为一个组合的 X 和 Y 地址空间的指令的数据返

回路径。 它也是双操作数读指令(MAC 类)的 X 地址空

间数据路径。 X写数据总线是所有指令对数据空间执行

写操作的惟一路径。

X 数据空间还支持所有指令的模寻址,但是会受到寻址

模式的限制。 只有写 X 数据空间的操作才支持位反转寻

址方式。

MAC 类指令(CLR、ED、EDAC、MAC、MOVSAC、MPY、

MPY.N 和 MSC)配合使用 Y 数据空间与 X数据空间以提供

两条可以同时读取数据的路径。 不能通过Y总线执行任何

写操作。此类指令专门指定 W10 和 W11 始终作为寻址 Y

数据空间的 W 寄存器指针,独立于 X 数据空间;而指定

W8 和 W9 作为寻址 X 数据空间的 W 寄存器指针。 注意,

在累加器回写操作期间,数据地址空间被认为是一个组

合的 X 和 Y 数据空间,因此写操作通过 X 总线进行。从

而可以对整个地址空间中的任何地址单元执行写操作。

Y 数据空间仅用于与 MAC 类指令相关的数据预取操作。

它也支持对自动循环缓冲区的模寻址。 当然,所有其他

指令可通过将 Y 数据地址空间视作组合线性空间的一部

分,通过 X 数据总线对其进行访问。

图 3-8 给出了 X 和 Y 数据空间之间的边界定义,用户不

能通过编程更改 X 和 Y 的数据空间边界。 如果 EA 指向

已为其分配的数据空间之外的数据或是指向物理存储器

之外的存储单元,则将返回全零的字或字节。 例如,虽

然所有使用任何寻址模式的非 MAC 类指令都能访问 Y地

址空间,但如果一条 MAC 类指令试图使用 W8 或 W9

(X 空间指针)从 Y 地址空间取数据,将返回 0x0000。

表 3-2: 非法存储器访问的后果

试图进行的操作

EA = 未实现的地址

MAC类指令中使用W8或W9来访问

Y 数据空间

MAC类指令中使用 W10或 W11来访

问 X 数据空间

所有有效地址均为16位宽,指向数据空间中的字节。 因

此,数据空间的地址范围为 64 KB 或 32K 字。

返回的数据

0x0000

0x0000

0x0000

3.2.3 数据空间宽度

内核数据宽度为 16 位。 所有内部寄存器都是以 16 位宽

字构成的。 数据存储空间以字节可寻址的 16 位宽的块

构成。

3.2.4 数据对齐

为了保持与 PIC® MCU 器件的向后兼容以及提高数据存

储空间的使用效率, dsPIC30F 指令集既支持字操作,

也支持字节操作。 在数据存储器和寄存器中,数据是按

字对齐的,但所有数据空间有效地址都被解析为字节。

使用有效地址的最低位 (LSb)决定要选择哪个字节,

读数据字节的操作将读取包含此字节的整个字。 选中的

字节将被放在 X 数据总线的 LSB 中 (不可能出现来自

Y数据路径的字节访问,因为MAC类指令只能取整字)。

也就是说,数据存储器和寄存器是由两个共享(字)地

址译码,而写入线相互独立的字节宽度的并行实体构成

的。 数据字节写操作仅写入存储阵列或寄存器中与字节

地址匹配的那一侧。

这种字节访问操作可使所有的有效地址计算(包括那些

由 DSP 操作产生的有效地址,它们只能是字长度的数

据)在内部进行换算,以适应字对齐的存储空间。例如,

内核将识别执行后修改寄存器间接寻址模式 [Ws++] 的

结果,对于字节操作产生的值是 Ws + 1,而对于字操作

产生的值是 Ws + 2。

所有字访问必须按偶地址对齐。 不支持取不对齐的字数

据的操作,因此在混合使用字节和字的操作或移植 8 位

MCU 代码时必须要小心。 任何尝试进行非对齐读或写

的操作都将产生地址错误陷阱。 如果在读操作时产生错

误,正在执行的指令将完成;如果在写操作时产生错

误,指令仍将执行,但不会进行写入。 无论上述 2 种情

况的哪一种,都将产生陷阱,从而允许系统与 / 或用户

检查地址错误发生之前的机器状态。

图 3-10: 数据对齐

15 8 7 0

0001

0003

0005

字节 1 字节 0

字节 3 字节 2

字节 5 字节 4

LSB MSB

0000

0002

0004

DS70139E_CN 第 36 页 2007 Microchip Technology Inc.

Page 39

dsPIC30F2011/2012/3012/3013

所有载入 W 寄存器的字节都将载入 W 寄存器的 LSB,

W 寄存器的 MSB 不变。

提供了一条符号扩展 (SE)指令,允许用户把 8 位的

有符号数据转换为 16 位有符号值。或者,对于 16 位无

符号数据,用户可以清零任何 W 寄存器的 MSB,方法

是在相应的地址处执行一条零扩展 (ZE)指令。

尽管大多数指令能够对字或字节大小的数据进行操作,

但应该注意的是,一些指令,包括 DSP 指令,只对字

大小的数据进行操作。

3.2.5 NEAR 数据空间

X 地址存储空间中,在 0x0000 和 0x1FFF 之间保留了一

个 8 KB 的 near 数据空间;在所有的存储器直接寻址指

令中,可以通过一个 13 位的绝对地址字段来直接访问

这个数据空间。其余的 X 地址空间和全部的 Y 地址空间

都是可间接寻址的。此外,使用 MOV 指令可以寻址整个

X 数据空间,这支持通过16 位地址字段进行存储器直接

寻址。

3.2.6 软件堆栈

dsPIC DSC 器件具有一个软件堆栈。 W15 被用作堆栈

指针。

堆栈指针总是指向堆栈顶部第一个可供使用的字,从低

地址到高地址方向增长。堆栈指针在弹出堆栈之前递

减,而在压入堆栈后递增,如图 3-11 所示。注意,对于

任何 CALL 指令时的 PC 压栈,在压入堆栈之前, PC

的MSB要进行零扩展,从而确保了MSB始终是清零的。

堆栈指针限制寄存器 (SPLIM)与堆栈指针相关联。复

位时 SPLIM 不被初始化。 与堆栈指针的情况一样,因

为所有的堆栈操作必须是字对齐的,SPLIM<0> 被强制

为 0。 每当使用 W15 作为源或目标指针生成有效地址

(EA)时,生成的地址要与 SPLIM 中的值做比较。 如

果堆栈指针 (W15)与 SPLIM 寄存器的内容相等,则

执行压栈操作,此时不会产生堆栈错误陷阱。 但在随后

的压栈操作中会产生堆栈错误陷阱。这样的话,当堆栈

增长超过 RAM 中地址 0x2000 时,如果要想产生堆栈错

误陷阱,用值 0x1FFE 来初始化 SPLIM 即可。

类似地,当堆栈指针地址小于 0x0800 时,就会产生堆

栈指针下溢 (堆栈错误)陷阱,这避免了堆栈进入特殊

功能寄存器 (SFR)空间。

对 SPLIM 寄存器执行写操作之后,不要立即使用 W15

对该寄存器执行间接读操作。

注: 在异常处理期间,在将 PC 压入堆栈之前,

要先将 PC 的 MSB 与 SRL 寄存器组合在

一起。

图 3-11: CALL 堆栈帧

0x0000

000000000

堆栈往高地址递增

PC<15:0>

PC<22:16>

< 空字 >

015

W15 ( CALL 前)

W15 ( CALL 后)

POP : [--W15]

PUSH : [W15++]

2007 Microchip Technology Inc. DS70139E_CN 第 37 页

Page 40

DS70139E_CN 第38 页 2007 Microchip Technology Inc.

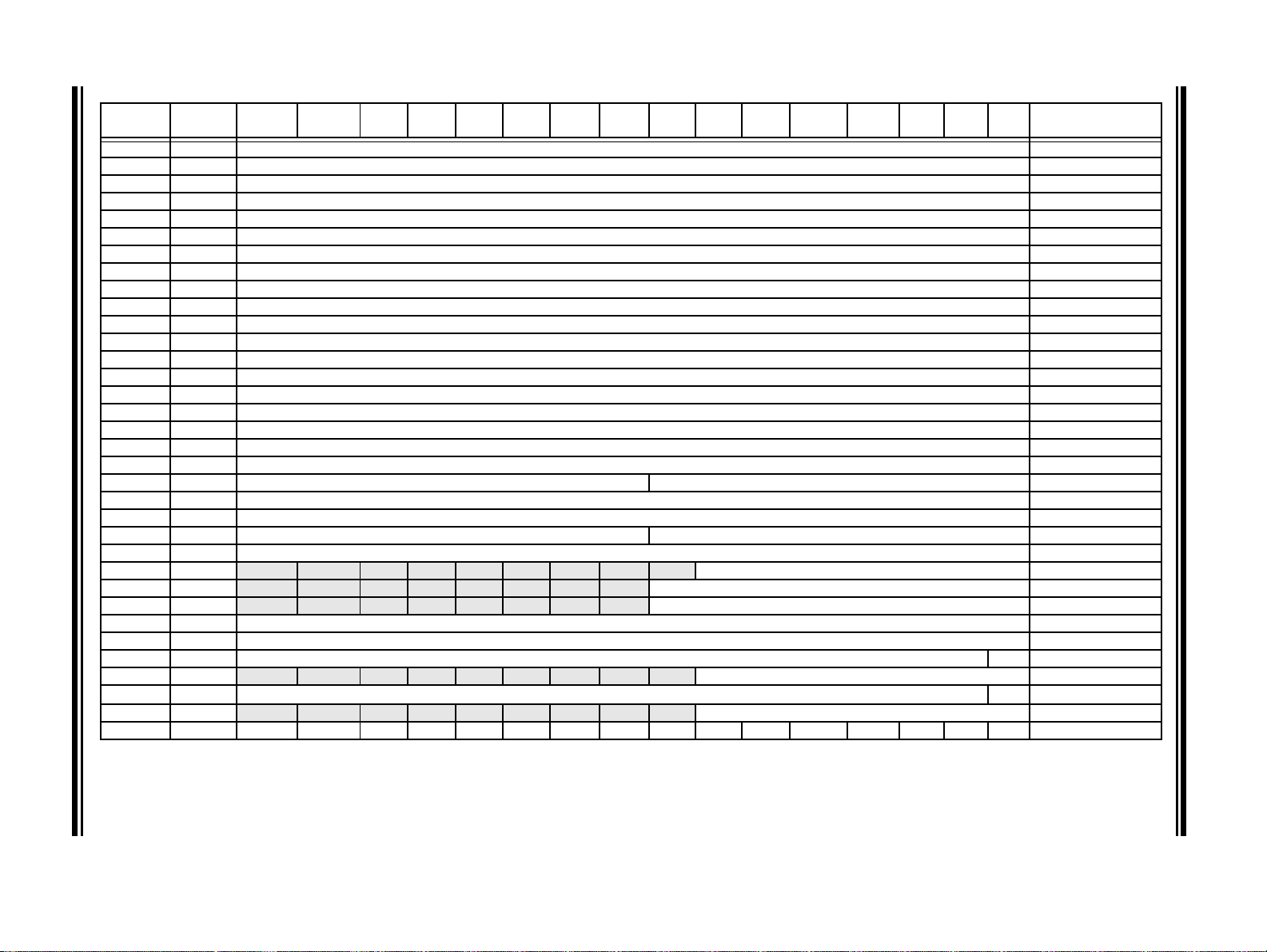

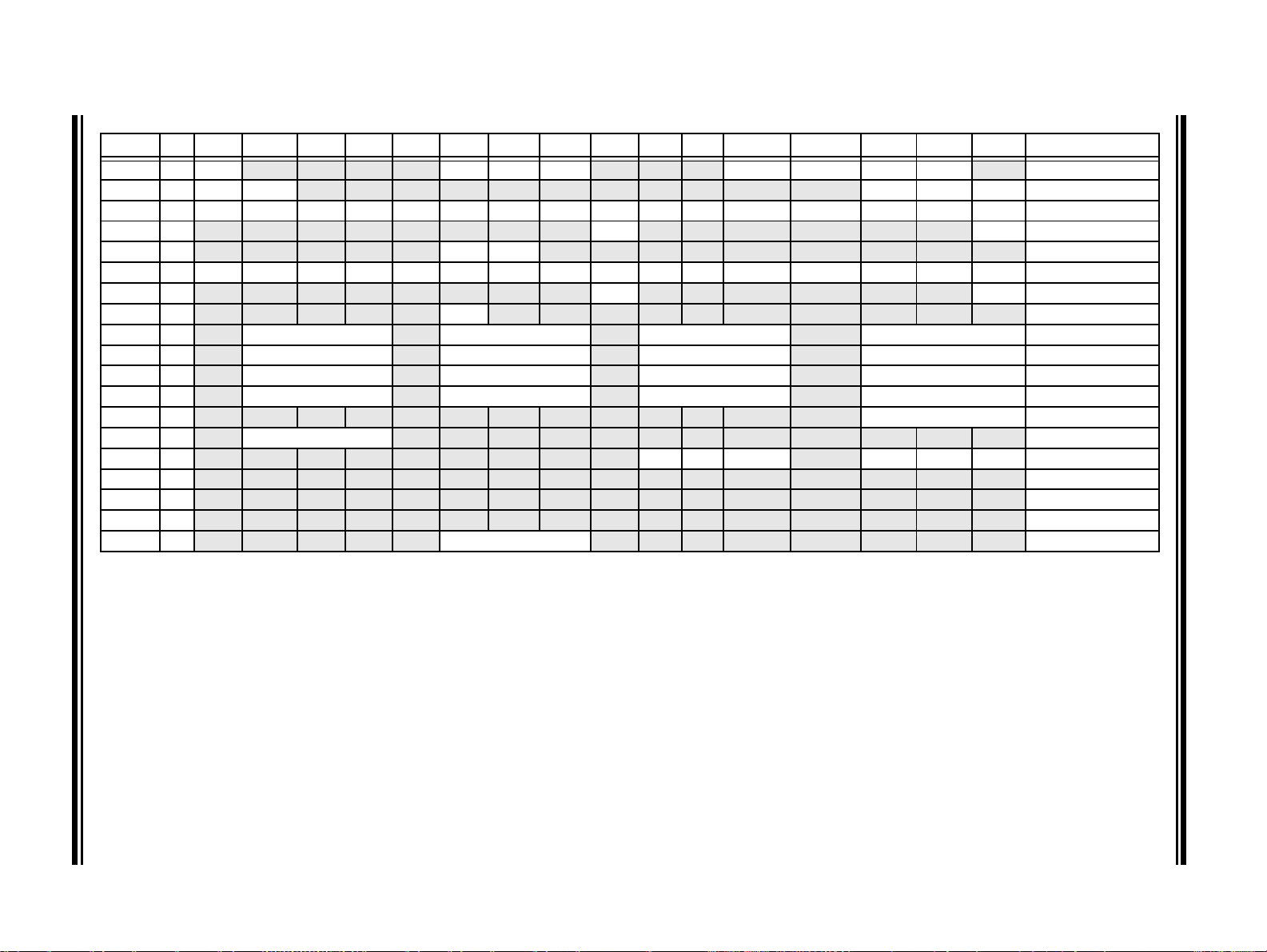

表 3-3: 内核寄存器映射

SFR 名称

W0 0000 W0/WREG 0000 0000 0000 0000

W1 0002 W1 0000 0000 0000 0000

W2 0004 W2 0000 0000 0000 0000

W3 0006 W3 0000 0000 0000 0000

W4 0008 W4 0000 0000 0000 0000

W5 000A W5 0000 0000 0000 0000

W6 000C W6 0000 0000 0000 0000

W7 000E W7 0000 0000 0000 0000

W8 0010 W8 0000 0000 0000 0000

W9 0012 W9 0000 0000 0000 0000

W10 0014 W10 00 00 0000 0000 0000

W11 0016 W11 00 00 0000 0000 0000

W12 0018 W12 00 00 0000 0000 0000

W13 001A W13 0000 0000 0000 0000

W14 001C W14 0000 0000 0000 0000

W15 001E W15 0000 1000 0000 0000

SPLIM 0020 SPLIM 0000 0000 0000 0000

ACCAL 0022 ACCAL 0000 0000 0000 0000

ACCAH 0024 ACCAH 0000 0000 0000 0000

ACCAU 0026

ACCBL 0028 ACCBL 0000 0000 0000 0000

ACCBH 002A ACCBH 0000 0000 0000 0000

ACCBU 002C

PCL 002E PCL 0000 0000 0000 0000

PCH 0030

TBLPAG 0032

PSVPAG 0034

RCOUNT 0036 RCOUNT uuuu uuuu uuuu uuuu

DCOUNT 0038 DCOUNT uuuu uuuu uuuu uuuu

DOSTARTL 003A DOSTARTL 0 uuuu uuuu uuuu uu u0

DOSTARTH 003C

DOENDL 003E DOENDL

DOENDH 0040

SR 0042 OA OB SA SB OAB SAB DA DC IPL2 IPL1 IPL0 RA N OV Z C 00 00 0000 0000 0000

图注: u = 未初始化的位

注: 有关寄存器位域的描述,请参见 《dsPIC30F 系列参考手册》(DS70046E_CN)。

地址

(低地址)

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

符号扩展 (ACCA<39>)

符号扩展 (ACCB<39>)

- - - - - - - - -

- - - - - - - -

- - - - - - - -

- - - - - - - - -

- - - - - - - - -

ACCAU 0000 0000 0000 0000

ACCBU 0000 0000 0000 0000

PCH 0000 0000 0000 0000

TBLPAG 0000 0000 0000 0000

PSVPAG 0000 0000 0000 0000

DOSTARTH 0000 0000 0uuu uuuu

0

DOENDH 0000 0000 0uuu uuuu

dsPIC30F2011/2012/3012/3013

复位状态

uuuu uuuu uuuu uuu0

Page 41

2007 Microchip Technology Inc. DS70139E_CN 第 39 页

表 3-3: 内核寄存器映射 (续)

SFR 名称

CORCON 0044

MODCON 0046 XMODEN YMODEN

XMODSRT 0048 XS<15:1> 0 uuuu uuuu uuuu uu u0

XMODEND 004A XE<15:1> 1 uuuu uuuu uuuu uuu1

YMODSRT 004C YS<15:1> 0 uuuu uuuu uuuu uuu0

YMODEND 004E YE<15:1> 1 uuuu uuuu uuuu uuu1

XBREV 0050 BREN XB<14:0> uuuu uuuu uuuu uuuu

DISICNT 0052

图注: u = 未初始化的位

注: 有关寄存器位域的描述,请参见 《dsPIC30F 系列参考手册》(DS70046E_CN)。

地址

(低地址)

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

- - -

- -

US EDT DL2 DL1 DL0 SATA SATB SATDW ACCSAT IPL3 PSV RND IF 0000 0000 0010 0000

- -

BWM<3:0> YWM<3:0> XWM<3:0> 0000 0000 0000 0000

DISICNT<13:0> 0000 0000 0000 0000

复位状态

dsPIC30F2011/2012/3012/3013

Page 42

dsPIC30F2011/2012/3012/3013

注:

DS70139E_CN 第 40 页 2007 Microchip Technology Inc.

Page 43

dsPIC30F2011/2012/3012/3013

4.0 地址发生器单元

注: 本数据手册总结了 dsPIC30F 系列器件的功能,但是不

应把本手册当作无所不包的参考手册来使用。有关 CPU、外

设、寄存器说明和一般器件功能的更多信息,请参阅

《dsPIC30F 系列参考手册》(DS70046E_CN)。有关器件

指令集和编程的更多信息,请参阅 《dsPIC30F/33F 程序

员参考手册

dsPIC DSC 内核包含两个独立的地址发生器单元: X

AGU 和 Y AGU。Y AGU 仅支持 DSP MAC类指令的字长

度数据读取。 dsPIC DSC AGU 支持如下三种数据寻址

类型 :

• 线性寻址

• 模 (循环)寻址

• 位反转寻址

线性和模数据寻址模式可应用于数据空间或程序空间。

位反转寻址只能用于数据空间地址。

4.1 指令寻址模式

寻址模式经过优化可以支持各指令的具体功能,基本的

寻址模式在表 4-1 中给出。MAC 类指令中提供的寻址模

式,与其他指令类型中的寻址模式略有不同。

》

(DS70157B_CN)。

4.1.1 文件寄存器指令

大多数文件寄存器指令使用一个 13 位地址字段 (f)来

直接寻址数据存储器中的前 8192 字节 (near 数据空

间)。大多数文件寄存器指令使用工作寄存器 W0, W0

在这些指令中表示为 WREG。目的寄存器通常是同一个

文件寄存器或者 WREG(MUL 指令除外),把结果写入

寄存器或寄存器对。使用 MOV 指令能够获得更大的灵活

性,在文件寄存器操作期间可以访问整个数据空间。

4.1.2 MCU 指令

三操作数 MCU 指令的形式是:

操作数 3 = 操作数 1< 功能 > 操作数 2

其中,操作数 1 始终是工作寄存器(即,寻址模式只能

是寄存器直接寻址),称为 Wb。操作数 2 可以是一个

W 寄存器,取自数据存储器或一个 5 位立即数。结果位

置可以是 W 寄存器或地址单元。MCU 指令支持下列寻

址模式:

• 寄存器直接寻址

• 寄存器间接寻址

• 执行后修改的寄存器间接寻址

• 执行前修改的寄存器间接寻址

• 5 位或 10 位立即数寻址

注: 并非所有的指令都支持上面给出的全部寻

址模式。各条指令可能支持这些寻址模式

的某些模式,指令不同支持的寻址模式可

能不同。

表 4-1: 支持的基本寻址模式

寻址模式 说明

文件寄存器直接寻址 明确指定文件寄存器的地址。

寄存器直接寻址 直接访问寄存器的内容。

寄存器间接寻址 Wn 的内容形成 EA。

执行后修改的寄存器间接寻址 Wn 的内容形成 EA,然后用一个常量值修改 Wn (递增或递减)。

执行前修改的寄存器间接寻址 先用一个有符号常量值修改 Wn (递增或递减),再由此时的 Wn 内容形成

EA。

带寄存器偏移量的寄存器间接寻址 Wn 和 Wb 的和形成 EA。

带立即数偏移量的寄存器间接寻址 Wn 和立即数的和形成 EA。

2007 Microchip Technology Inc. DS70139E_CN 第41 页

Page 44

dsPIC30F2011/2012/3012/3013

4.1.3 传送指令和累加器类指令

与其他指令相比,传送指令和 DSP 累加器类指令提供

了更为灵活的寻址模式。除了大多数 MCU 指令支持的

寻址模式以外,传送和累加器类指令还支持带寄存器偏

移量的寄存器间接寻址模式,这也叫做寄存器变址寻址

模式。

注: 对于 MOV 指令,指令中指定的寻址模式对

于源寄存器和目的寄存器 EA,可以是不同

的。然而,4 位 Wb(寄存器偏移量)字段

为源寄存器和目的寄存器所共用 (但通常

只由源寄存器或目的寄存器之一使用)。

概括地说,传送指令和累加器指令支持下列寻址模式:

• 寄存器直接寻址

• 寄存器间接寻址

• 执行后修改的寄存器间接寻址

• 执行前修改的寄存器间接寻址

• 寄存器偏移量的寄存器间接寻址 (变址寻址)

• 立即数偏移量的寄存器间接寻址

• 8 位立即数寻址

• 16 位立即数寻址

注: 并非所有的指令都支持上面给出的全部寻

址模式。各条指令可能支持这些寻址模式

的某些模式,指令不同支持的寻址模式可

能不同。

4.1.4 MAC 类指令

双源操作数 DSP 指令(CLR、ED、EDAC、MAC、MPY、

MPY.N、MOVSAC 和 MSC)也叫做 MAC 类指令,它们使

用一组简化的寻址模式,允许用户通过寄存器间接寻址

表有效地对数据指针进行操作。

双源操作数预取寄存器必须是集合 {W8, W9, W10,

W11} 的成员。 对于数据读取操作,W8 和 W9 始终用于

X RAGU, 而 W10 和 W11 始终用于 Y AGU。从而,产

生的有效地址(无论是在修改之前还是之后),对 于 W8

和 W9 必须是 X 数据空间中的有效地址,对于 W10 和

W11 则必须是 Y 数据空间中的有效地址。

概括地说, MAC 类指令支持下列寻址模式:

• 寄存器间接寻址

• 执行后修改 (修改量为 2)的寄存器间接寻址

• 执行后修改 (修改量为 4)的寄存器间接寻址

• 执行后修改 (修改量为 6)的寄存器间接寻址

• 寄存器偏移量的寄存器间接寻址 (变址寻址)

4.1.5 其他指令

除了上述的各种寻址模式之外,一些指令使用各种长度

的立即数常量。例如, BRA (转移)指令使用 16 位有

符号立即数来直接指定转移的目标,而 DISI 指令使用

一个 14 位无符号立即数字段。在一些指令中,比如 ADD

Acc,操作数的来源或运算结果已经暗含在操作码中。

某些操作,比如 NOP,没有任何操作数。

4.2 模寻址

模寻址模式,是一种使用硬件来自动支持循环数据缓冲

区的方法。目的是在执行紧密循环代码时 (这在许多

DSP 算法中很典型),不需要用软件来执行数据地址边

界检查。

可以在数据空间或程序空间中进行模寻址 (因为这两种

空间的数据指针机制本质上是相同的)。每个 X (也提

供指向程序空间的指针)和 Y 数据空间中都可支持一个

循环缓冲区。模寻址可以对任何 W 寄存器指针进行操

作。然而,最好不要将 W14 或 W15 用于模寻址,因为

这两个寄存器分别用作堆栈帧指针和堆栈指针。

总的来说,任何特定的循环缓冲区只能配置为单向工

作,因为根据缓冲区的方向,对缓冲区起始地址 (对于

递增缓冲区)或结束地址(对于递减缓冲区)有某些限

制。

使用限制的惟一例外是那些长度为 2 的幂的缓冲区。这

些缓冲区满足起始和结束地址判据,它们可以双向工作

(即,在低地址边界和高地址边界上都将进行地址边界

检查)。

注: 带寄存器偏移量的寄存器间接寻址,仅可

用于 W9(在 X 空间中)和 W11(在 Y 空

间中)。

DS70139E_CN 第42 页 2007 Microchip Technology Inc.

Page 45

dsPIC30F2011/2012/3012/3013

4.2.1 起始地址和结束地址

模寻址机制要求指定起始地址和结束地址,并将它们载

入 16 位模缓冲区地址寄存器中:XMODSRT、

XMODEND、YMODSRT 和 YMODEND(见表 3-3)。

注: Y 空间模寻址的EA 计算使用字长度的数据

(每个 EA 的 LSb 始终清零)。

循环缓冲区的长度没有直接指定,由相应的起始地址和

结束地址之差决定其长度。循环缓冲区最大长度为 32K

字(64 KB)。

图 4-1: 模寻址操作示例

字节

地址

0x1100

MOV #0x1100,W0

MOV W0,XMODSRT ;set modulo start address

MOV #0x1163,W0

MOV W0,MODEND ;set modulo end address

MOV #0x8001,W0

MOV W0,MODCON ;enable W1, X AGU for modulo

MOV #0x0000,W0 ;W0 holds buffer fill value

4.2.2 W 地址寄存器选择

模寻址和位反转寻址控制寄存器 MODCON<15:0> 中包

含使能标志以及指定 W 地址寄存器的 W 寄存器字段。

XWM 和 YWM 字段选择对哪些寄存器进行模寻址。如

果 XWM = 15,则禁止 X RAGU 和 X WAGU 模寻址。

类似地,如果 YWM = 15,则禁止 Y AGU 模寻址。

要对其进行模寻址的X 地址空间指针W 寄存器(XWM)

位于 MODCON<3:0> 中(见表 3-3)。当 XWM 被设置

为除15之外的任何值且XMODEN位( MODCON<15>)

置 1 时, X 数据空间的模寻址被使能。

要对其进行模寻址的Y 地址空间指针W 寄存器(YWM)

位于 MODCON<7:4> 中。当 YWM 被设置为除 15 之外

的任何值且 YMODEN 位(MODCON<14>)置 1 时,

Y 数据空间的模寻址被使能。

0x1163

起始地址 = 0x1100

结束地址 = 0x1163

长度 = 0x0032 字

MOV #0x1110,W1 ;point W1 to buffer

DO AGAIN,#0x31 ;fill the 50 buffer locations

MOV W0,[W1++] ;fill the next location

AGAIN: INC W0,W0 ;increment the fill value

2007 Microchip Technology Inc. DS70139E_CN 第43 页

Page 46

dsPIC30F2011/2012/3012/3013

4.2.3 模寻址的应用

模寻址可以应用于与任何 W 寄存器相关的有效地址

(EA)计算中。重要的是要意识到,地址边界检查功

能,不仅会检查地址是否正好在地址边界上,而且会检

查地址是否小于或大于上限 (对于递增缓冲区)、是否

低于下限 (对于递减缓冲区)。因此,地址变化可能会

越过边界,但仍然可以正确调整。

注: 只有在使用执行前修改或执行后修改寻址

模式来计算有效地址时,模修正有效地址

才被写回寄存器。如果使用了地址偏移量

(例如,[W7 + W2]),会进行模地址修正,

但寄存器的内容保持不变。

4.3 位反转寻址

位反转寻址用来简化基 2 FFT 算法的数据重新排序。位

反转寻址为 X WAGU 所支持,仅限于数据写入。

地址修改量,可以是常数或寄存器的内容,可视为将其

位顺序反转。源地址和目的地址仍然是正常的顺序。于

是,惟一需要反转的操作数就是地址修改量。

4.3.1 位反转寻址的实现

当发生以下情况时,使能位反转寻址:

1. MODCON 寄存器中 BWM (W 寄存器选择)的

值,是除 15 以外的任何值 (不能使用位反转寻

址访问堆栈),且

2. XBREV 寄存器中的 BREN 位置 1,且

3. 使用的寻址模式是预递增或后递增的寄存器间接

寻址模式。

如果位反转缓冲区的长度是 M = 2

区起始地址的最后 “N”位必须为零。

XB<14:0> 是位反转地址修改量或 “中心点”(pivot

point),通常是一个常数。对于 FFT 计算,其值等于

FFT 数据缓冲区长度的一半。

注: 所有位反转 EA 的计算都使用字长度数据

(每个 EA 的 LSb 始终为零)。为了产生兼

容(字节)地址,要相应地调整 XB 的值。

使能位反转寻址时,仅对预递增或后递增的寄存器间接

寻址、且仅对字长度数据写入,才会进行位反转寻址。

而对于任何其他寻址模式或字节长度数据,不会进行位

反转寻址, 而是生成正常的地址。在进行位反转寻址

时, W 地址指针将始终加上地址修改量 (XB),与寄

存器间接寻址模式相关的偏移量将被忽略。此外,由于

要求是字数据, EA 的 LSb 被忽略 (且始终被清零)。

注: 不应同时使能模寻址和位反转寻址。如果

用户试图这么做的话,对于 X WAGU,位

反转寻址将优先, X WAGU 模寻址将被禁

止。然而,在 X RAGU 中,模寻址继续起

作用。

如果通过置 1 BREN (XBREV<15>)位使能了位反转

寻址,那么,在写 XBREV 寄存器之后,不应马上进行

要使用被指定为位反转指针的 W 寄存器的间接读操作。

N

字节,则数据缓冲

DS70139E_CN 第44 页 2007 Microchip Technology Inc.

Page 47

图 4-2: 位反转地址示例

b15 b14 b13 b12

dsPIC30F2011/2012/3012/3013

正常顺序的地址

b7 b6 b5 b4b11 b10 b9 b8

b3 b2 b1 0

围绕二进制值的中心

左右交换位位置

b15 b14 b13 b12

b11 b10 b9 b8

b7 b6 b5 b1

中心点

b2 b3 b4 0

位反转后的地址

对于 16 字位反转缓冲区,XB = 0x0008

表 4-2: 位反转地址序列 (16 项)

正常地址 位反转后的地址

A3 A2 A1 A0

0000 0 0000 0

0001 1 1000 8

0010 2 0100 4

0011 3 1100 12

0100 4 0010 2

0101 5 1010 10

0110 6 0110 6

0111 7 1110 14

1000 8 0001 1

1001 9 1001 9

1010 10 0101 5

1011 11 1101 13

1100 12 0011 3

1101 13 1011 11

1110 14 0111 7

1111 15 1111 15

十进制

A3 A2 A1 A0

十进制

表 4-3: XBREV 寄存器的位反转地址修改量

缓冲区大小 (字) XB<14:0> 位反转地址修改量

1024 0x0200

512 0x0100

256 0x0080

128 0x0040

64 0x0020

32 0x0010

16 0x0008

8 0x0004

4 0x0002

2 0x0001

2007 Microchip Technology Inc. DS70139E_CN 第45 页

Page 48

dsPIC30F2011/2012/3012/3013

注:

DS70139E_CN 第46 页 2007 Microchip Technology Inc.

Page 49

dsPIC30F2011/2012/3012/3013

5.0 闪存程序存储器

注: 本数据手册总结了 dsPIC30F 系列器件的功能,但是不

应把本手册当作无所不包的参考手册来使用。有关 CPU、外

设、寄存器说明和一般器件功能的更多信息,请参见

《dsPIC30F 系列参考手册》(DS70046E_CN)。有关器件

指令集和编程的更多信息,请参见 《dsPIC30F/33F 程序

员参考手册》(DS70157B_CN)。

dsPIC30F 系列器件包含用于执行用户代码的内部闪存

程序存储器。用户可以使用以下两种方法对闪存程序存

储器编程:

1. 运行时自编程 (RTSP)

2. 在线串行编程 (ICSP™)

5.1 在线串行编程 (ICSP)

可以在最终应用电路中对 dsPIC30F 器件进行串行编

程。 只需要 5 根线即可完成这一操作,其中编程时钟线

和编程数据线(名称分别为 PGC 和 PGD)各一根,其

余 3 根分别是电源线 (V

位线 (MCLR

)。 这允许用户使用未编程器件生产电路

板,而仅在产品交付前才对数字信号控制器进行编程,

从而可以将最新版本的固件或者定制固件烧写到器件

中。

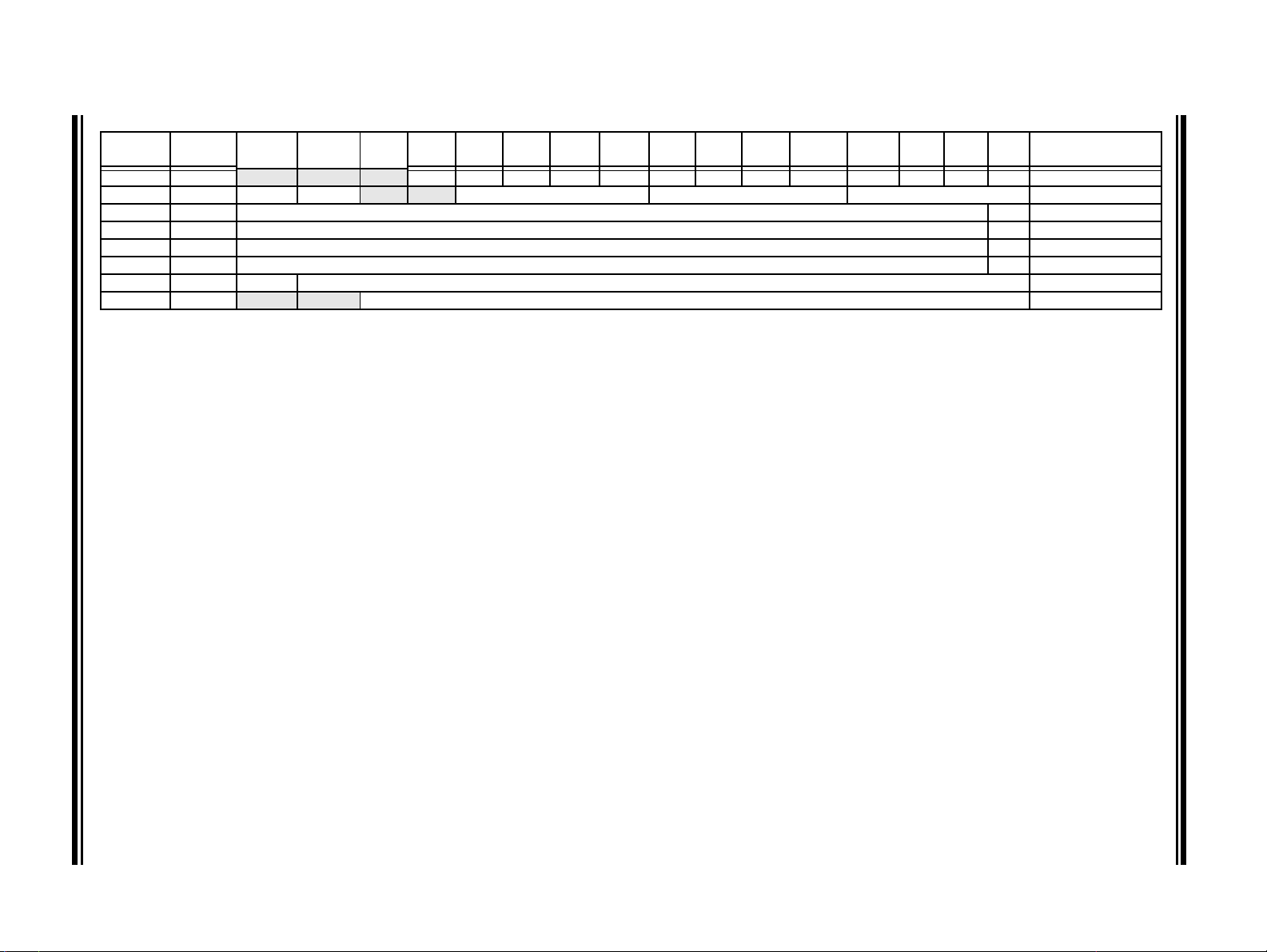

图 5-1:表和NVM 寄存器寻址

DD)、接地线 (VSS)和主复

5.2 运行时自编程 (RTSP)

运行时自编程(RTSP)使 用 TBLRD(表读)和 TBLWT

(表写)指令实现。

使用 RTSP,用户可以一次擦除 32 个指令字(96 字节)

的程序存储单元,一次可写入 32 个指令字 (96 字节)

的程序存储数据。

5.3 表指令操作综述

TBLRDL 和 TBLWTL 指令用来读或写程序存储器的

bit<15:0>。TBLRDL 和 TBLWTL 可以以字或字节模式访

问程序存储器。

TBLRDH 和 TBLWTH 指令用来读或写程序存储器的

bit<23:16>。 TBLRDH 和 TBLWTH 可以以字或字节模式

访问程序存储器。

使用 TBLPAG寄存器的 bit<7:0> 和来自表指令中指定的

W 寄存器的有效地址 (EA),形成 24 位的程序存储器

地址,如图 5-1 所示。

用户/配置

空间选择

使用

程序

计数器

使用

NVMADR

寻址

使用

表指令

0

1/0

NVMADRU 寄存器

8 位 16 位

1/0

TBLPAG 寄存器

8 位

24 位

程序计数器

NVMADR 寄存器 EA

24 位 EA

0

工作寄存器 EA

16 位

字节

选择

2007 Microchip Technology Inc. DS70139E_CN 第47 页

Page 50

dsPIC30F2011/2012/3012/3013

5.4 RTSP 操作

dsPIC30F 闪存程序存储器组织成行和板 (panel)。 每

行由 32 个指令字 (96 字节)组成。每个板由 128 行

(4K x 24 个指令字)组成。RTSP 允许用户每次擦除一

行(32 个指令字)、每次编程 4 条指令。RTSP 可以用

来对多个程序存储器板进行编程,但在每个板的边界处

必须更改表指针。

程序存储器的每个板都包含写锁存器,它能够保存32个

指令字的编程数据。在实际编程操作前,等待写入的数

据必须先装入板的写锁存器。要写入板的数据按顺序装

载到写锁存器中:指令 0,指令 1,依此类推。 装载的

指令字必须始终来自 32 个指令字的地址边界。

RTSP 编程的基本步骤是先建立一个表指针,然后执行

一系列 TBLWT 指令,装载写锁存器。通过把 NVMCON

寄存器中的特定位置 1,进行编程。 装载 32 条指令需要

32 条 TBLWTL 和 4 条 TBLWTH 指令。如果需要对多个

板进行编程,应该为下一组要写入的多个写锁存器修改

表指针。

由于只需要写表锁存器,所以所有表写操作都是单字写

入(2 个指令周期)。编程每一行需要一个编程周期。

在整个 V

可读、可写且可擦除的。

DD 范围内,正常操作期间,闪存程序存储器是

5.5 控制寄存器

四个特殊功能寄存器用来读、写闪存程序存储器,它们

是:

• NVMCON

• NVMADR

• NVMADRU

• NVMKEY

5.5.1 NVMCON 寄存器

NVMCON 寄存器控制要擦除的存储块、要编程的存储

器类型以及编程周期的启动。

5.5.2 NVMADR 寄存器

NVMADR 寄存器用来存放有效地址的两个低字节。它

捕捉已执行的上一条表指令的 EA<15:0>,选择要写的

行。

5.5.3 NVMADRU 寄存器

NVMADRU 寄存器用来存放有效地址的高字节。它捕捉

已执行的上一条表指令的 EA<23:16>。

5.5.4 NVMKEY 寄存器

NVMKEY 是只写寄存器,用于写保护。要启动编程或擦

除过程,用户必须把 0x55 和 0xAA 连续写入 NVMKEY

寄存器。更多细节,请参见第 5.6 节 “编程操作”。

注: 用户也可直接写 NVMADR 和 NVMADRU

寄存器,以指定擦除或编程的程序存储器

地址。

DS70139E_CN 第48 页 2007 Microchip Technology Inc.

Page 51

dsPIC30F2011/2012/3012/3013

5.6 编程操作

在 RTSP 模式下,对内部闪存进行编程或擦除需要完整

的编程过程。编程操作持续时间的标称值为 2 ms,编 程

操作结束之前,处理器将暂停 (等待) 。将 WR 位

(NVMCON<15>)置 1 开始编程操作,操作结束后将

自动清零 WR 位。

5.6.1 闪存程序存储器的编程算法

用户一次可擦除或编程闪存程序存储器的一行。一般过

程如下:

1. 读一行闪存程序存储器(32 个指令字),把读出

的数据作为数据 “镜像”保存到数据 RAM 中。

2. 用期望的新数据更新数据镜像。

3. 擦除闪存程序存储器行。

a) 设置 NVMCON 寄存器以允许对闪存程序存

储器进行多字擦除,并将 WREN 位置 1。

b) 把要擦除的行地址写入寄存器 NVMADRU/

NVMDR。

c) 把“55”写入 NVMKEY。

d) 把“AA”写入 NVMKEY。

e) 将 WR 位置 1。这将开始擦除周期。

f) 在擦除周期中 CPU 将暂停。

g) 当擦除周期结束时, WR 位会被清零。

4. 从数据 RAM“镜像”中把 32 个指令字的数据写

入闪存程序存储器写锁存器。

5. 将 32 个指令字写入闪存程序存储器。

a) 设置 NVMCON 寄存器以允许对闪存程序存

储器进行多字编程,并将 WREN 位置 1。

b) 把“55”写入 NVMKEY。

c) 把“AA”写入 NVMKEY。

d) 将 WR 位置 1。这将开始编程周期。

e) 在编程周期中 CPU 将暂停。

f) 当编程周期结束时, WR 位会被硬件清零。

6. 根据需要,重复步骤 1 到 5,对所需的闪存程序

存储器进行编程。

5.6.2 擦除程序存储器的一行

例 5-1 所示的代码序列可以用来擦除程序存储器的一行

(32 个指令字)。

例 5-1: 擦除程序存储器的一行

; Setup NVMCON for erase operation, multi word write

; program memory selected, and writes enabled

MOV #0x4041,W0 ;

; Init pointer to row to be ERASED

MOV W0

MOV #tblpage(PROG_ADDR),W0 ;

MOV W0

MOV #tbloffset(PROG_ADDR),W0 ; Intialize in-page EA[15:0] pointer

MOV W0, NVMADR ; Initialize NVMADR SFR

DISI #5 ; Block all interrupts with priority <7 for

MOV #0x55,W0

MOV W0

MOV #0xAA,W1 ;

MOV W1

BSET NVMCON,#WR ; Start the erase sequence

NOP ; Insert two NOPs after the erase

NOP ; command is asserted

NVMCON ; Init NVMCON SFR

,

NVMADRU ; Initialize PM Page Boundary SFR

,

; next 5 instructions

NVMKEY ; Write the 0x55 key

,

NVMKEY ; Write the 0xAA key

,

2007 Microchip Technology Inc. DS70139E_CN 第49 页

Page 52

dsPIC30F2011/2012/3012/3013

5.6.3 装载写锁存器

例 5-2 所示的指令序列可以用来装载 96 字节的写锁存

器。装载由表指针选择的写锁存器需要32 条TBLWTL指

令和 32 条 TBLWTH 指令。

5.6.4 启动编程序列

出于保护的目的,必须使用 NVMKEY 的写启动序列,

以便允许进行任何擦除或编程操作。在执行编程命令

后,用户必须等待一段时间 (编程时间),直至编程完

成。 启动编程序列后紧跟的两条指令应该为 NOP,如例

5-3 所示。

例 5-2: 装载写锁存器

; Set up a pointer to the first program memory location to be written

; program memory selected, and writes enabled

MOV #0x0000,W0 ;

MOV W0

MOV #0x6000,W0 ; An example program memory address

; Perform the TBLWT instructions to write the latches

; 0th_program_word

MOV #LOW_WORD_0,W2 ;

MOV #HIGH_BYTE_0,W3 ;

TBLWTL W2

TBLWTH W3

; 1st_program_word

MOV #LOW_WORD_1,W2 ;

MOV #HIGH_BYTE_1,W3 ;

TBLWTL W2

TBLWTH W3

; 2nd_program_word

MOV #LOW_WORD_2,W2 ;

MOV #HIGH_BYTE_2,W3 ;

TBLWTL W2

TBLWTH W3

•

•

•

; 31st_program_word

MOV #LOW_WORD_31,W2 ;

MOV #HIGH_BYTE_31,W3 ;

TBLWTL W2

TBLWTH W3

TBLPAG ; Initialize PM Page Boundary SFR

,

[W0] ; Write PM low word into program latch

,

[W0++] ; Write PM high byte into program latch

,

[W0] ; Write PM low word into program latch

,

[W0++] ; Write PM high byte into program latch

,

[W0] ; Write PM low word into program latch

,

[W0++] ; Write PM high byte into program latch

,

[W0] ; Write PM low word into program latch

,

[W0++] ; Write PM high byte into program latch

,

注:在例 5-2 中, W3 高字节的内容将不起作用。

例 5-3: 启动编程序列

DISI #5 ; Block all interrupts with priority <7 for

MOV #0x55,W0 ;

MOV W0

MOV #0xAA,W1 ;

MOV W1

BSET NVMCON,#WR ; Start the erase sequence

NOP ; Insert two NOPs after the erase

NOP ; command is asserted

DS70139E_CN 第50 页 2007 Microchip Technology Inc.

NVMKEY ; Write the 0x55 key

,

NVMKEY ; Write the 0xAA key

,

; next 5 instructions

Page 53

2007 Microchip Technology Inc. DS70139E_CN 第51 页

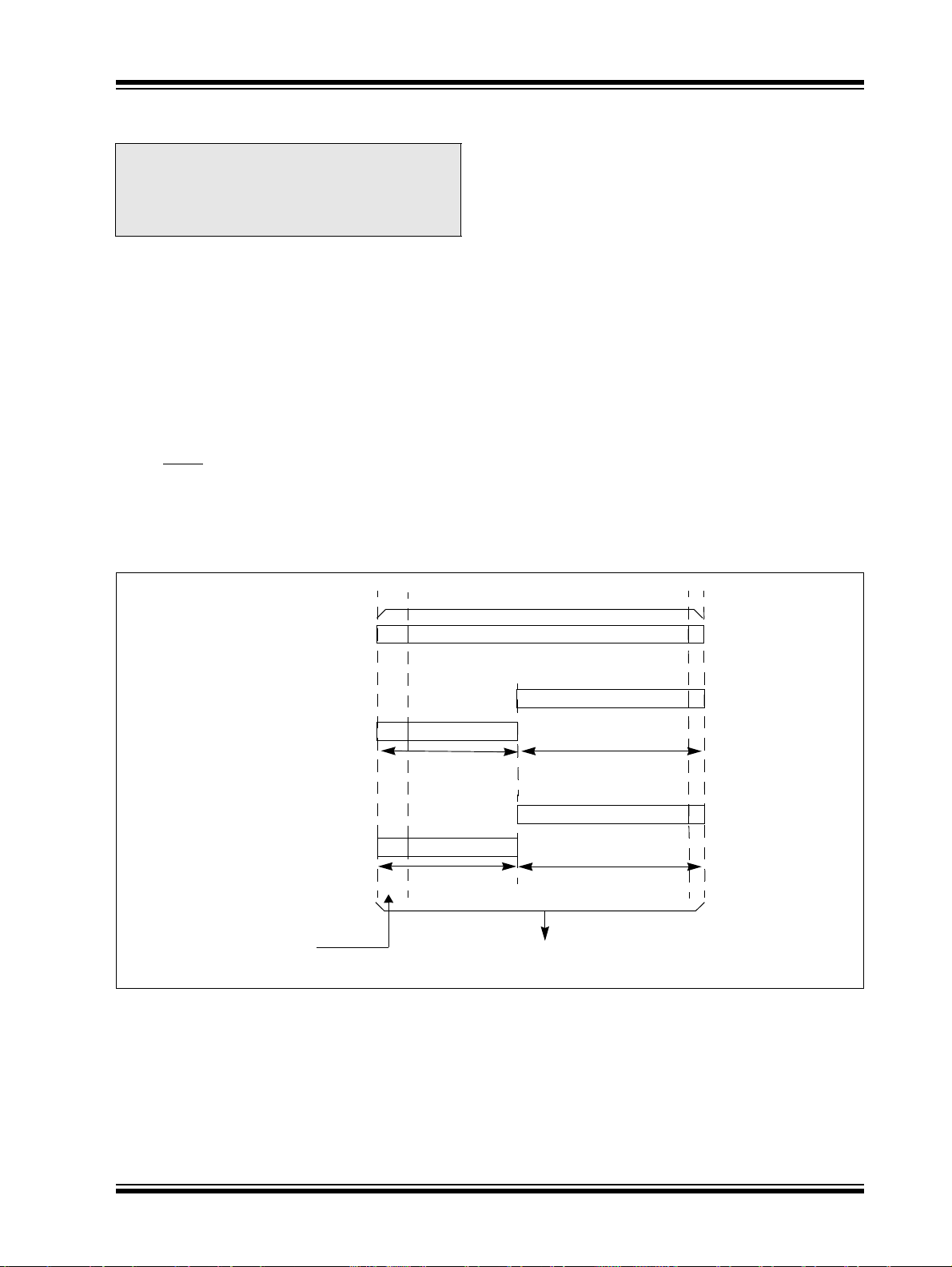

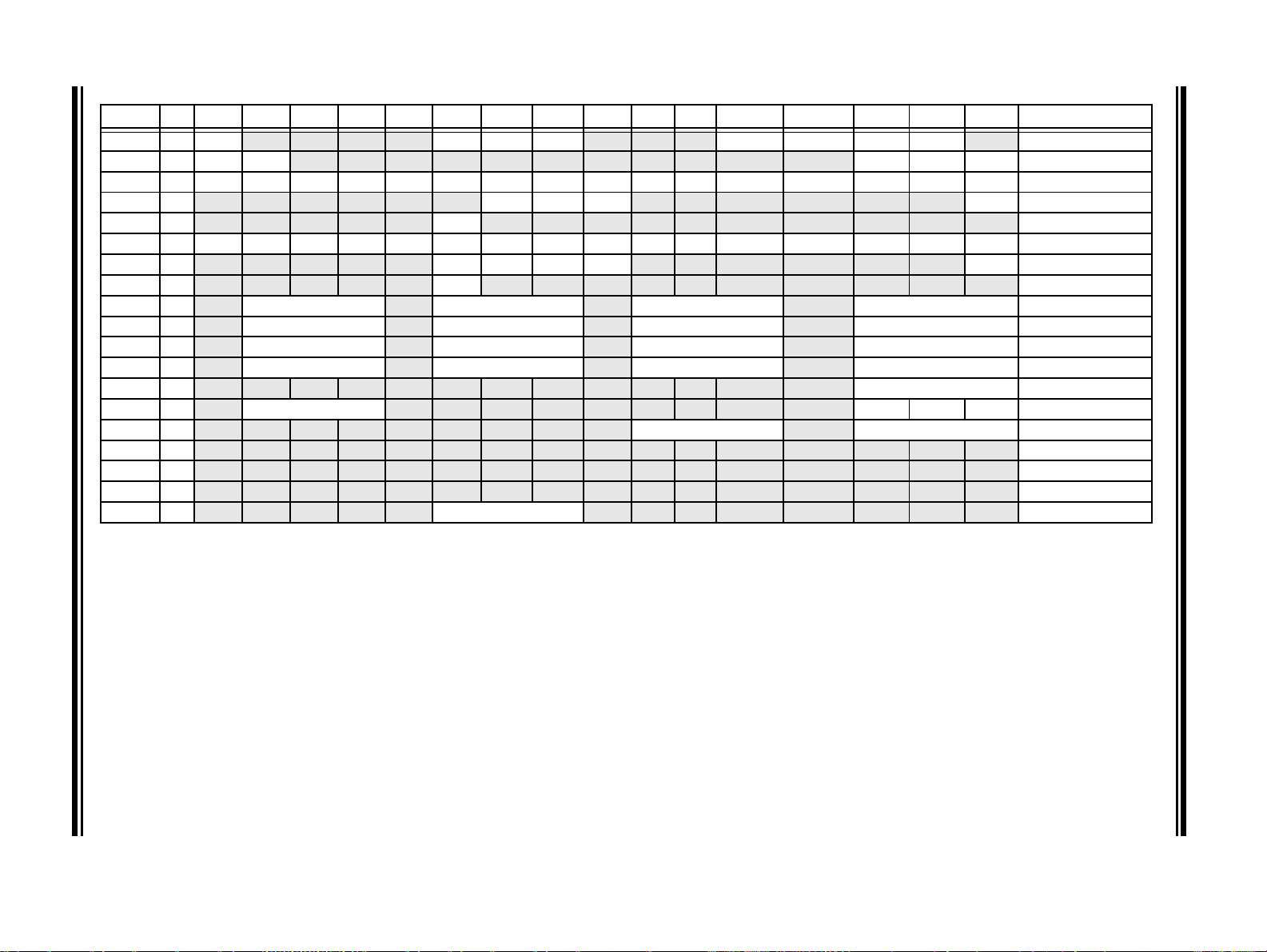

表 5-1: NVM 寄存器映射

文件寄存器

名称

NVMCON 0760 WR WREN WRERR

NVMADR 0762 NVMADR<15:0> uuuu uuuu uuuu uuuu

NVMADRU 0764

NVMKEY 0766

图注: u = 未初始化的位

注: 有关寄存器位域的描述,请参见 《dsPIC30F 系列参考手册》(DS70046E_CN)。

地址

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

- - - - TWRI - PROGOP<6:0> 0000 0000 0000 0000

- - - - - - - - NVMADR<23:16> 0000 0000 uuuu uuuu

- - - - - - - - KEY<7:0> 0000 0000 0000 0000

所有复位时的状态

dsPIC30F2011/2012/3012/3013

Page 54

dsPIC30F2011/2012/3012/3013

注:

DS70139E_CN 第52 页 2007 Microchip Technology Inc.

Page 55

dsPIC30F2011/2012/3012/3013

6.0 数据 EEPROM 存储器

注: 本数据手册总结了 dsPIC30F 系列器件的功能,但是不

应把本手册当作无所不包的参考手册来使用。有关 CPU、外

设、寄存器说明和一般器件功能的更多信息,请参见

《dsPIC30F 系列参考手册》(DS70046E_CN)。有关器件

指令集和编程的更多信息,请参见 《dsPIC30F/33F 程序员

参考手册》(DS70157B_CN)。

在整个 VDD 范围内的正常操作期间,数据 EEPROM 存

储器是可读且可写的。数据 EEPROM 存储器直接映射

到程序存储器地址空间。

用来读写闪存程序存储器的四个特殊功能寄存器,也用

来访问数据 EEPROM 存储器。如在第 5.5 节 “控制寄

存器”中所述,这些寄存器是:

•NVMCON

• NVMADR

• NVMADRU

• NVMKEY

EEPROM 数据存储器允许读写单个字和 16 字长的块。

针对数据存储器时, NVMADR 与 NVMADRU 寄存器

配合使用,用来寻址要访问的 EEPROM 存储单元。

TBLRDL 和 TBLWTL 指令用来读写数据 EEPROM。

dsPIC30F 器件有最多 8 KB (4 K 字)的数 据

EEPROM,地址范围从 0x7FF000 到 0x7FFFFE。

字写操作之前,应该先擦除相应的存储单元。写操作完

成通常需要 2 ms,不过它将随电压和温度的变化而变

化。

对数据 EEPROM 进行编程或擦除操作,不会停止指令

流。在启动另一次数据 EEPROM 写 / 擦除操作之前,用

户需要等待一段适当的时间。在编程或擦除操作进行过

程中,尝试读数据 EEPROM 将返回不确定的数据。

控制位 WR 启动写操作,这与闪存程序存储器写类似。

可通过软件置 1 WR 位,但不能对其清零。写操作完成

时,硬件将清零 WR 位。 不能用软件清零 WR 位,这样

避免了意外或提早结束写操作。

WREN 位置 1 时将允许进行写操作。上电时,WREN位

清零。当写操作被正常工作期间的 MCLR

超时复位所中断时,WRERR 位置 1。在这样的情形下,

复位后,用户可以检查 WRERR 位,重写存储单元。地

址寄存器 NVMADR 保持不变。