Page 1

dsPIC30F2010

Data Sheet

High-Performance, 16-Bit

Digital Signal Controllers

© 2006 Microchip Technology Inc. DS70118G

Page 2

Note the following details of the code protection feature on Microchip devices:

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchip’s code protection feature may be a violation of the Digit al Millennium Copyright Act. If suc h a c t s

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device

applications and t he lik e is provided only for your convenience

and may be su perseded by upda t es . It is y our responsibility to

ensure that your application meets with your specifications.

MICROCHIP MAKES NO REPRESENTATIONS OR

WARRANTIES OF ANY KIND WHETHER EXPRESS OR

IMPLIED, WRITTEN OR ORAL, STATUTORY OR

OTHERWISE, RELATED TO THE INFORMATION,

INCLUDING BUT NOT LIMITED TO ITS CONDITION,

QUALITY, PERFORMANCE, MERCHANTABILITY OR

FITNESS FOR PURPOSE. Microchip disclaims all liability

arising from this information and its use. Use of Microchip

devices in life supp ort and/or safety ap plications is entir ely at

the buyer’s risk, and the buyer agrees to defend, indemnify and

hold harmless M icrochip from any and all dama ges, claims,

suits, or expenses re sulting from such use. No licens es are

conveyed, implicitly or otherwise, under any Microchip

intellectual property rights.

Trademarks

The Microchip name and logo, the Microchip logo, Accuron,

dsPIC, K

EELOQ, microID, MPLAB, PIC, PIC, PICSTAR T,

PRO MATE, PowerSmart, rfPIC and SmartShunt are

registered trademarks of Microchip Technology Incorporated

in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB,

SEEVAL, SmartSensor and The Embedded Control Solutions

Company are registered trademarks of Microchip Technology

Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard,

dsPICDEM, dsPICDEM.net, dsPICworks, ECAN,

ECONOMONITOR, FanSense, FlexROM, fuzzyLAB,

In-Circuit Serial Programming, ICSP, ICEPIC, Linear Active

Thermistor, Mindi, MiWi, MPASM, MPLIB, MPLINK, PICkit,

PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal,

PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB,

rfPICDEM, Select Mode, Smart Serial, SmartT el, Total

Endurance, UNI/O, WiperLock and ZENA are trademarks of

Microchip Technology Incorporated in the U.S.A. and other

countries.

SQTP is a service mark of Microchip Technology Incorporated

in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2006, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received ISO/TS-16949:2002 certification for its worldwide

headquarters, design and wafer fabrication facilities in Chandler and

Tempe, Arizona, Gresham, Oregon and Mountain View, California. The

Company’s quality system processes and procedures are for its

PICmicro

EEPROMs, microperipherals, nonvolatile memory and analog

products. In addition, Microchip’s quality system for the design and

manufacture of development systems is ISO 9001:2000 certified.

®

8-bit MCUs, KEELOQ

®

code hopping devices, Serial

DS70118G-page ii © 2006 Microchip Technology Inc.

Page 3

dsPIC30F2010

28-Pin dsPIC30F2010 Enhanced Flash

16-Bit Digital Signal Controller

Note: This data sheet summarizes features of this g roup

of dsPIC30F devices and is not intended to be a complete

reference source. For more information on the CPU,

peripherals, register descriptions and general device

functionality, refer to the “dsPIC30F Family Reference

Manual” (DS70046). For more informat ion on the device

instruction set and programming, refer to the “dsPIC30F/

33F Programmer’s Reference Manual” (DS70157).

High-Performance Modified RISC CPU:

• Modified Harvard architecture

• C compiler optimized instruction set architecture

• 83 base instructions with flexible addressing

modes

• 24-bit wide instructions, 16-bit wide data path

• 12 Kbytes on-chip Fla sh program space

• 512 bytes on-chip data RAM

• 1 Kbyte nonvolatile data EEPROM

• 16 x 16-bit working register array

• Up to 30 MIPs operation:

- DC to 40 MHz external clock input

- 4 MHz-10 MHz oscillator input with

PLL active (4x, 8x, 16x)

• 27 interrupt sources

• Three external interrupt sources

• 8 user-selectable priority levels for each interrupt

• 4 processor exceptions and software traps

DSP Engine Features:

• Modulo and Bit-Reversed modes

• Two 40-bit wide accumulators with optional

saturation logic

• 17-bit x 17-bit single-cycle hardw are frac tio nal /

integer multiplier

• Single-cycle Multiply-Accumulate (MAC)

operation

• 40-stage Barrel Shifter

• Dual data fetch

Peripheral Features:

• High current sink/source I/O pins: 25 mA/25 mA

• Three 16-bit timers/counters; optionally pair up

16-bit timers into 32-bit timer modules

• Four 16-bit capture input functions

• Two 16-bit compare/PWM output functions

- Dual Compare mode available

• 3-wire SPI modules (supports 4 Frame modes)

2

•I

CTM module supports Multi-Master/Slave mode

and 7-bit/10-bit addressing

• Addressable UART modules with FIFO buffers

Motor Control PWM Module Features:

• 6 PWM output channels

- Complementary or Independent Output

modes

- Edge and Center-Aligned modes

• 4 duty cycle generators

• Dedicated time base with 4 modes

• Programmable output polarity

• Dead-time control for Complementary mode

• Manual output control

• Trigger for synchron iz ed A/D conv ersion s

Quadrature Encoder Interface Module Features:

• Phase A, Phase B and Index Pulse input

• 16-bit up/down position counter

• Count direction status

• Position Measurement (x2 and x4) mode

• Programmable digital noise filters on inputs

• Alternate 16-bit Timer/Counter mode

• Interrup t on position counter rollover/underflow

Analog Features:

• 10-bit Analog-to-Digital Converter (ADC) with:

- 1 Msps (for 10-bit A/D) conversion rate

- Six input channels

- Conversion available during Sleep and Idle

• Programmable Brown-out Reset

© 2006 Microchip Technology Inc. DS70118G-page 1

Page 4

dsPIC30F2010

Special Digital Signal Controller Features:

• Detects clock failure and switches to on-chip lowpower RC oscillator

• Programmable code protection

• Enhanced Flash program memory:

- 10,000 erase/write cycle (min.) for

industrial temperature range, 100K (typical)

• Data EEPROM memory:

- 100,000 erase/write cycle (min.) for

industrial temperature range, 1M (typical)

• Self-reprogrammable under software control

• Power-on Reset (POR), Power-up Timer (PWRT )

and Oscillator Start-up Timer (OST)

• Flexible Watchdog Timer (WDT) with on-chip lowpower RC oscillator for reliable operation

• In-Circuit Serial Programming™ (ICSP™)

programming capability

• Selectable Power Management modes

- Sleep, Idle and Alternate Clock modes

CMOS Technology:

• Low-power, high-speed Flash technology

• Wide operating voltage range (2.5V to 5.5V)

• Industrial and Extended temperature ranges

• Low power consumption

• Fail-Safe clock monitor operation

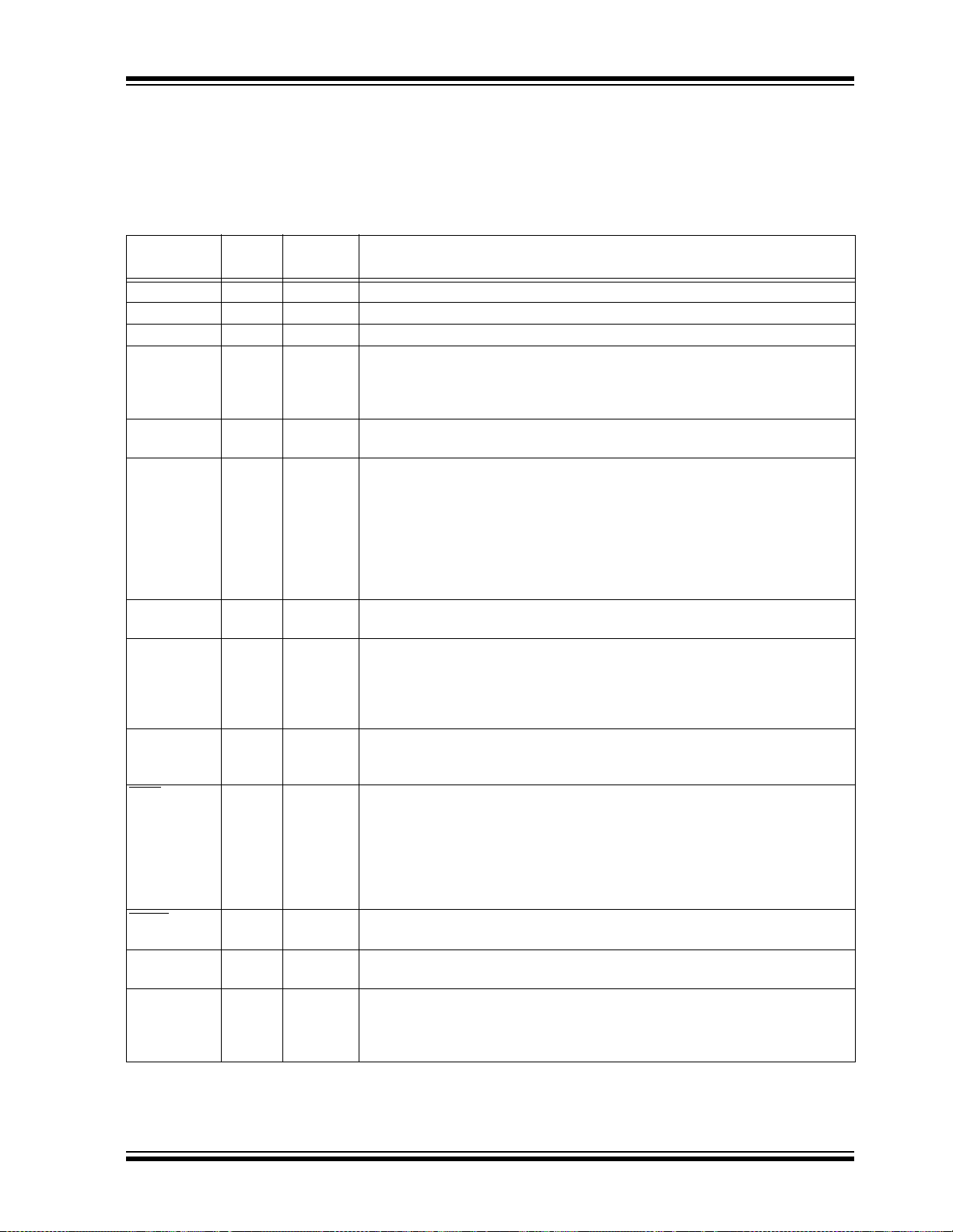

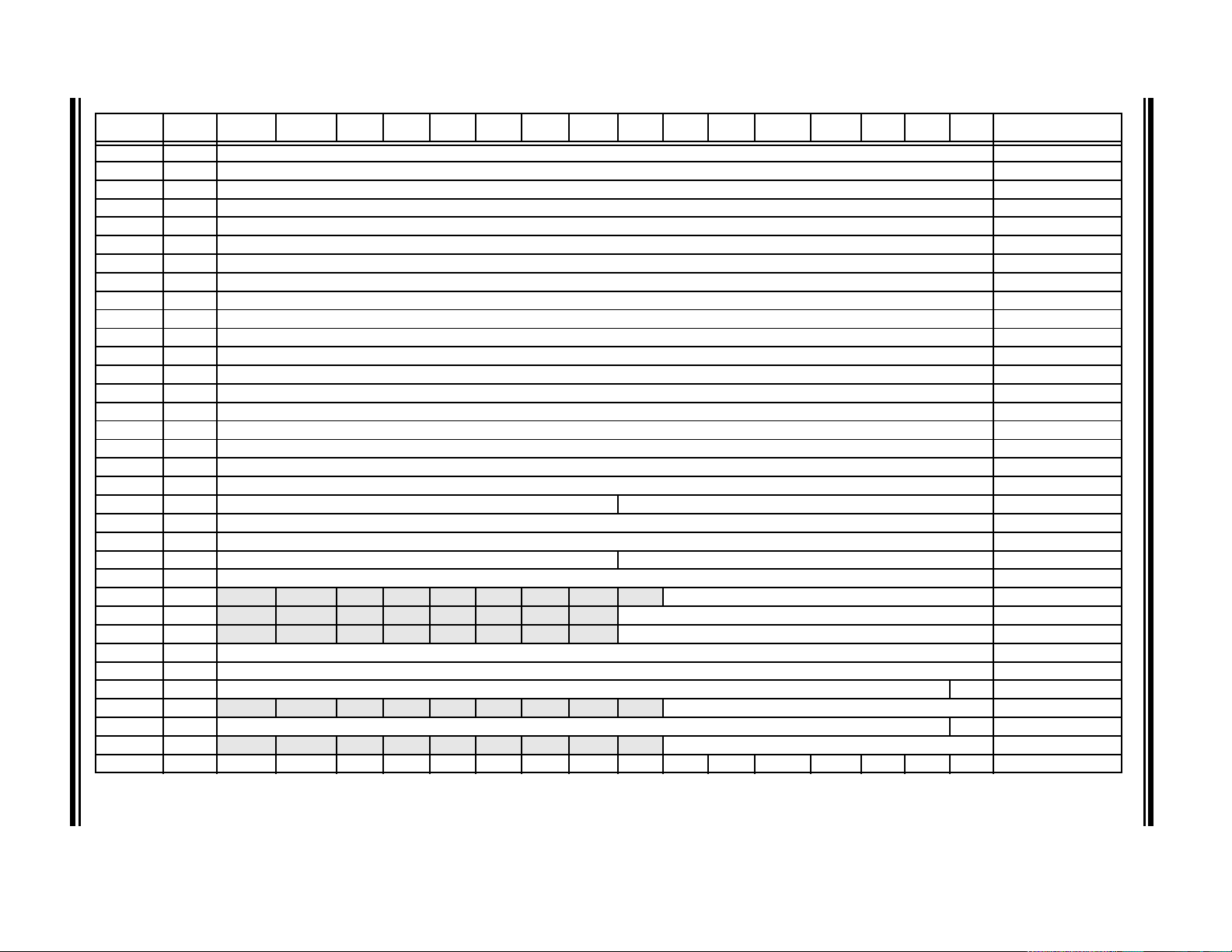

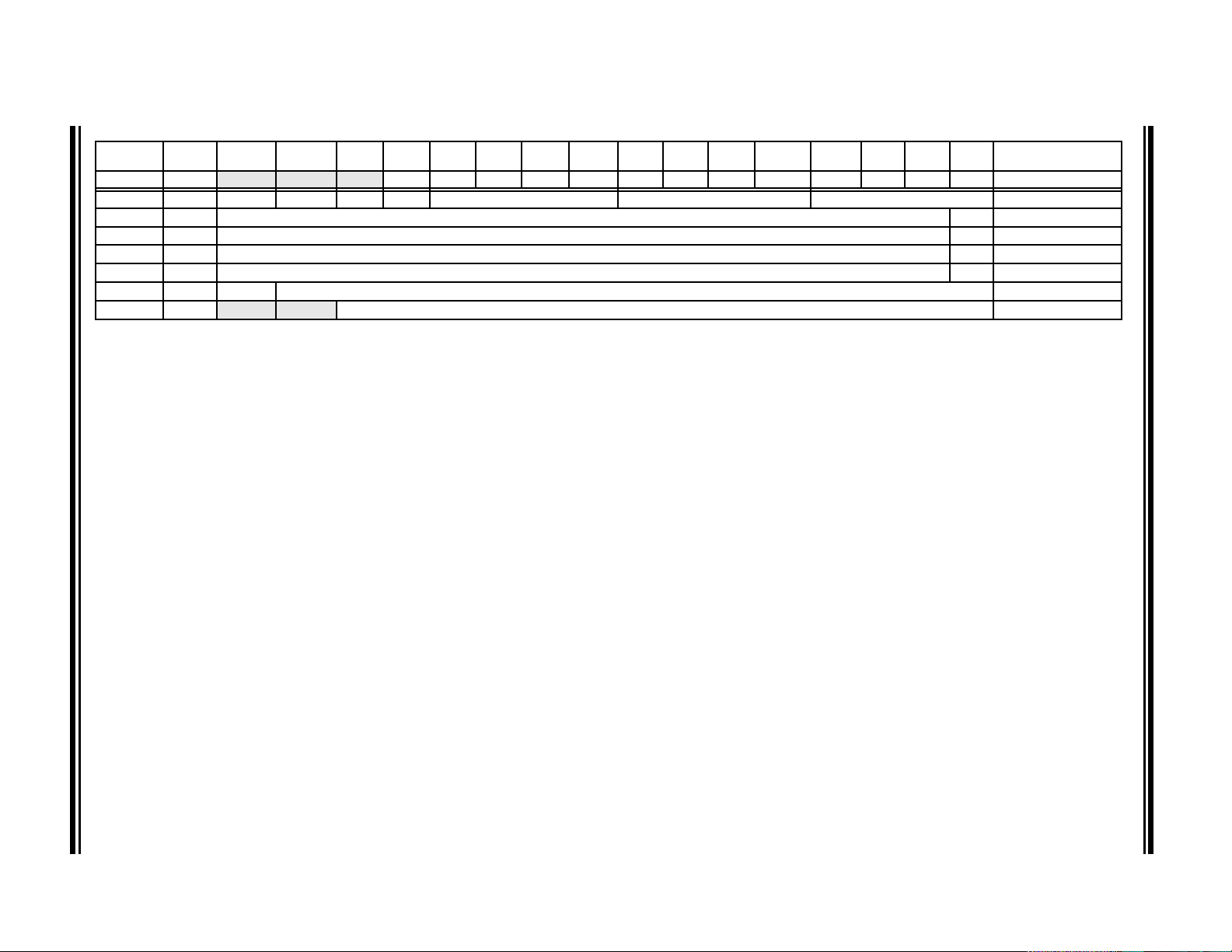

dsPIC30F Motor Control and Power Conversion Family*

Program

Device Pins

dsPIC30F2010 28 12K/4K 512 1024 3 4 2 6 ch 6 ch Yes 1 1 1 –

dsPIC30F3010 28 24K/8K 1024 1024 5 4 2 6 ch 6 ch Yes 1 1 1 –

dsPIC30F4012 28 48K/16K 2048 1024 5 4 2 6 ch 6 ch Yes 1 1 1 1

dsPIC30F3011 40/44 24K/8K 1024 1024 5 4 4 6 ch 9 ch Yes 2 1 1 –

dsPIC30F4011 40/44 48K/16K 2048 1024 5 4 4 6 ch 9 ch Yes 2 1 1 1

dsPIC30F5015 64 66K/22K 2048 1024 5 4 4 8 ch 16 ch Yes 1 2 1 1

dsPIC30F6010 80 144K/48K 8192 4096 5 8 8 8 ch 16 ch Yes 2 2 1 2

dsPIC30F6010A 80 144K/48K 8192 4096 5 8 8 8 ch 16 ch Yes 2 2 1 2

Mem. Bytes/

Instructions

SRAM

Bytes

EEPROM

Bytes

Timer

16-bit

Input

* This table provi des a summ ary of the ds PIC30F 2010 p eriphe ral feat ures. Ot her a vailable de vices in the ds PIC30 F

Motor Control and Power Conversion Family are shown for feature comparison.

Cap

Output

Comp/Std

PWM

Motor

Control

PWM

A/D 10-bit

1 Msps

Quad

Enc

TM

C

SPI

2

UART

I

CAN

DS70118G-page 2 © 2006 Microchip Technology Inc.

Page 5

Pin Diagrams

dsPIC30F2010

28-Pin SDIP and SOIC

EMUD3/AN0/VREF+/CN2/RB0

EMUC3/AN1/V

AN2/SS1/LVDIN/CN4/RB2

EMUD1/SOSCI/T2CK/U1ATX/CN1//RC13

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

EMUD2/OC2/IC2/INT2/RD1

REF-/CN3/RB1

AN3/INDX/CN5/RB3

AN4/QEA/IC7/CN6/RB4

AN5/QEB/IC8/CN7/RB5

OSC1/CLKI V

28-Pin QFN

MCLR

VDD

1

2

3

4

5

6

7

SS

8

9

10

11

12

13

14

28

AV

DD

AVSS

27

PWM1L/RE0

26

dsPIC30F2010

PWM1H/RE1

25

PWM2L/RE2

24

PWM2H/RE3

23

PWM3L/RE4

22

PWM3H/RE5V

21

DD

20

SSOSC2/CLKO/RC15

V

19

PGC/EMUC/U1RX/SDI1/SDA/RF2

18

PGD/EMUD/U1TX/SDO1/SCL/RF3

17

FLTA/INT0/SCK1/OCFA/RE8

16

15

EMUC2/OC1/IC1/INT1/RD0

AN2/SS1/LVDIN/CN4/RB2

AN3/INDX/CN5 RB3

AN4/QEA/IC7/CN6/RB4

AN5/QEB/IC8/CN7/RB5

V

OSC1/CLKI

OSC2/CLKO/RC15

SS

EMUD3/AN0/VREF+/CN2/RB0

EMUC3/AN1/VREF- /CN3/RB1

27

28

1

2

3

dsPIC30F2010

4

5

6

7

8

9

EMUD1/SOSCI/T2CK/U1ATX/CN1/RC13

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14

AVDD

AVSS

PWM1L/RE0

MCLR

23

24

25

26

1011121314

DD

V

/INT0/SCK1/OCFA/RE8

EMUD2/OC2/IC2/INT2/RD1

EMUC2/OC1/IC1/INT1/RD0

FLTA

PWM1H/RE1

22

21

PWM2L/RE2

20

PWM2H/RE3

PWM3L/RE4

19

PWM3H/RE5

18

V

DD

17

VSS

16

PGC/EMUC/U1RX/SDI1/SDA/RF2

15

PGD/EMUD/U1TX/SDO1/SCL/RF3

© 2006 Microchip Technology Inc. DS70118G-page 3

Page 6

dsPIC30F2010

Table of Contents

1.0 Device Overview..........................................................................................................................................................................5

2.0 CPU Architecture Overview..........................................................................................................................................................9

3.0 Memory Organization................................................................................................................................................................. 19

4.0 Address Generator Units............................................................................................................................................................ 31

5.0 Interrupts.................................................................................................................................................................................... 37

6.0 F la sh Program Memory..............................................................................................................................................................43

7.0 Data EEPROM Memory............................................................................................................................................................. 49

8.0 I /O Po rts.....................................................................................................................................................................................53

9.0 Timer1 Module ........................................................................................................................................................................... 57

10.0 Timer2/3 Module ...................................... .. .. .... .. ..... .... .. .. .. .. .... ..... .. .. .... .. .. .. .. ....... .. .. .. .... .............................................................61

11.0 Input Capture Module........................................................................................ .. .... .. .. .... ........................................................... 67

12.0 Output Compare Module............................................................................ ................................................................................ 71

13.0 Quadrature Encoder Interface (QEI) Module ............................................................................................................................. 75

14.0 Motor Control PWM Module....................................................................................................................................................... 81

15.0 SPI Module.................................................................................................................................................................................91

16.0 I2C Module.................................................................................................................................................................................95

17.0 Universal Asynchronous Receiver Transmitter (UART) Module .............................................................................................. 103

18.0 10-bit High-Speed Analog-to-Digital Converter (ADC) Module ................................................................................................111

19.0 System Integration.............. ................................................................. ....................................................................................123

20.0 Instruction Set Summary..........................................................................................................................................................137

21.0 Development Support. .............................................................................................................................................................. 145

22.0 Electrical Characteristics..........................................................................................................................................................149

23.0 Packaging Information...................................................................... ........................................................................................187

The Microchip Web Site..................................................................................................................................................................... 199

Customer Change Notification Service ..................................... ...... ............. ...... ............... ...... ...........................................................199

Customer Support..............................................................................................................................................................................199

Reader Response.............................................................................................................................................................................. 200

Product Identification System.............................................................................................................................................................201

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our pu blications to better s uit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or c omm ents regarding t his publication, p lease c ontact the M arket ing Co mmunications Department via

E-mail at docerrors@microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150. We

welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision

of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are

using.

Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

DS70118G-page 4 © 2006 Microchip Technology Inc.

Page 7

dsPIC30F2010

1.0 DEVICE OVERVIEW

Note: This data sheet summarizes features of this g roup

of dsPIC30F devices and is not intended to be a complete

reference source. For more information on the CPU,

peripherals, register descriptions and general device

functionality, refer to the “dsPIC30F Family Reference

Manual” (DS70046). For more informat ion on the device

instruction set and programming, refer to the “dsPIC30F/

33F Programmer’s Reference Manual” (DS70157).

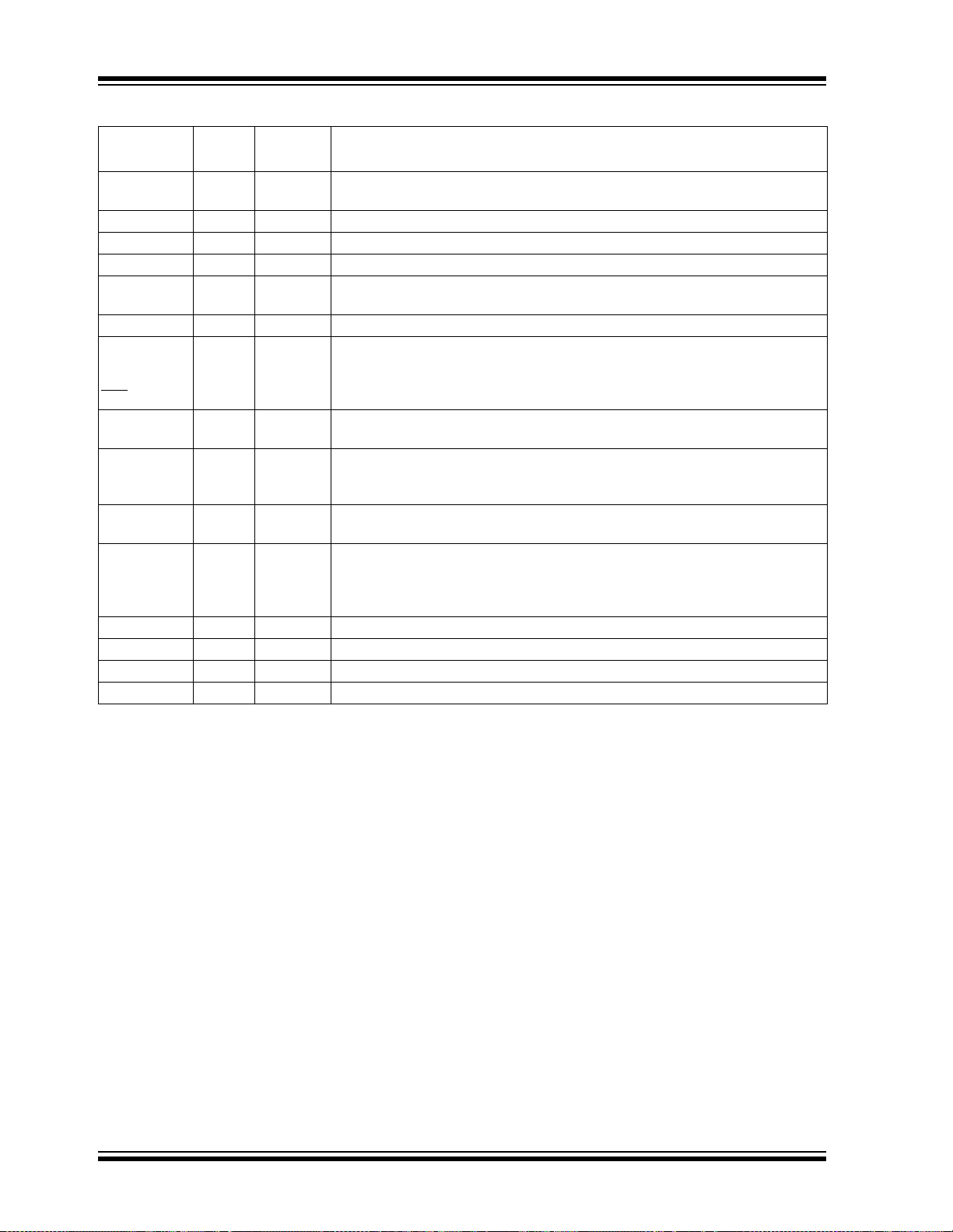

This document contains device specific information for

the dsPIC30F2010 device. The dsPIC30F devices

contain extensive Digital Signal Processor (DSP) functionality within a high-performance 16-bit mic rocontroller

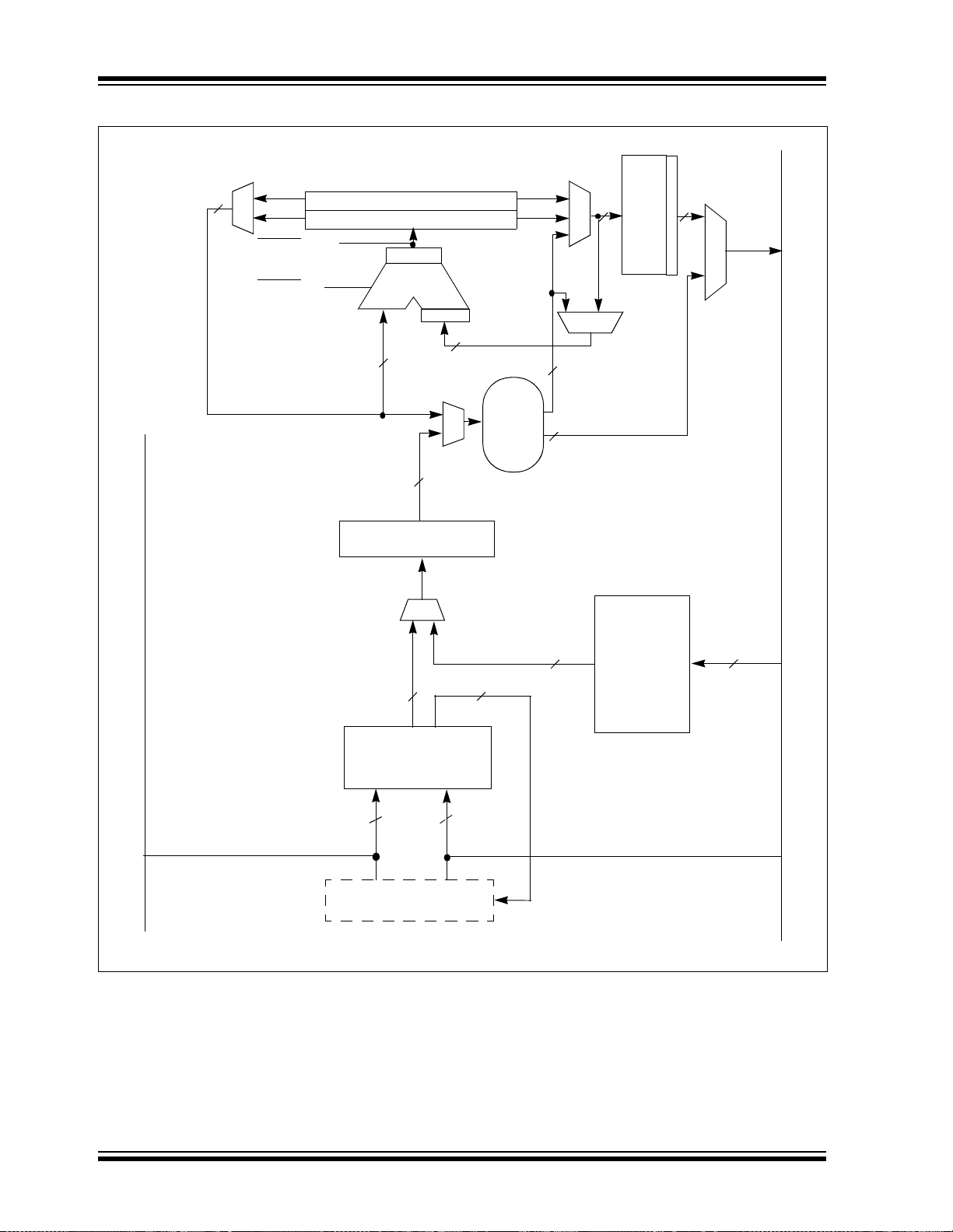

(MCU) architecture. Figure 1-1 shows a device block

diagram for the dsPIC30F2010 device.

© 2006 Microchip Technology Inc. DS70118G-page 5

Page 8

dsPIC30F2010

4

FIGURE 1-1: dsPIC30F2010 BL OC K DIAGR AM

Interrupt

Controller

24

Address Latch

Program Memory

(12 Kbytes)

Data EEPROM

(1 Kbyte)

Data Latch

Instruction

Decode &

24

24

16

Control

PSV & Table

Data Access

Control Block

Control

16

24

Y Data Bus

8

16

PCH PCL

PCU

Program Counter

Stack

Logic

Loop

Control

Logic

ROM Latch

IR

Decode

16

16

Y Data

RAM

(256 bytes)

Address

Latch

Y AGU

Effective Address

16

X Data Bus

16

Data LatchData Latch

X Data

(256 bytes)

Address

16

16

X RAGU

X WAGU

16

16 x 16

W Reg Array

16

16

RAM

Latch

16

16

EMUD3/AN0/VREF+/CN2/RB0

EMUC3/AN1/VREF-/CN3/RB1

AN2/SS1/LVDIN/CN4/RB2

AN3/INDX/CN5/RB3

AN4/QEA/IC7/CN6/RB4

AN5/QEB/IC8/CN7/RB5

PORTB

16

PORTC

EMUD1/SOSCI/T2CK/U1A T X/CN1/RC1 3

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC1

OSC2/CLKO/RC15

Control Signals

to Various Blocks

OSC1/CLKI

Generation

Timing

MCLR

10-bit ADC

Timers

Power-up

Timer

Oscillator

Start-up Timer

POR/BOR

Reset

Watchdog

Timer

Input

Capture

Module

QEI

DSP

Engine

16

Output

Compare

Module

Motor Control

PWM

Divide

Unit

ALU<16>

16

UART1SPI1

I2C™

PORTD

PORTE

PORTF

EMUC2/OC1/IC1/INT1/RD0

EMUD2/OC2/IC2/INT2/RD1

PWM1L/RE0

PWM1H/RE1

PWM2L/RE2

PWM2H/RE3

PWM3L/RE4

PWM3H/RE5

/INT0/SCK1/OCFA/RE8

FLTA

PGC/EMUC/U1RX/SDI1/SDA/RF2

PGD/EMUD/U1TX/SDO1/SCL/RF3

DS70118G-page 6 © 2006 Microchip Technology Inc.

Page 9

dsPIC30F2010

Table 1-1 provides a brief description of device I/O

pinouts and the functions that may be multiplexed to a

port pin. Multiple functions may exist on one port pin.

When multiplexing occurs, the peripheral module’s

functional requirements may force an override of the

data direction of the port pin.

TABLE 1-1: PINOUT I/O DESCRIPTIONS

Pin Name

AN0-AN5 I Analog Analog input channels.

DD P P Positive supply for analog module.

AV

AVSS P P Ground reference for analog module.

CLKI

CLKO

CN0-CN7 I ST Input change notification inputs.

EMUD

EMUC

EMUD1

EMUC1

EMUD2

EMUC2

EMUD3

EMUC3

IC1, IC2, IC7,

IC8

INDX

QEA

QEB

INT0

INT1

INT2

FLTA

PWM1L

PWM1H

PWM2L

PWM2H

PWM3L

PWM3H

MCLR

OCFA

OC1-OC2

OSC1

OSC2

Legend: CMOS = CMOS compatible input or output Analog = Analog in put

Pin

Type

I

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I ST Capture inputs. The dsPIC30F2010 has 4 capture inputs. The inputs are

I

I

I

I

I

I

I

O

O

O

O

O

O

I/P ST Master Clear (Reset) input or programming voltage input. This pin is an active-

I

O

I

I/O

ST = Schmitt Trigger input with CMOS levels O = Output

I = Input P = Power

Buffer

Type

ST/CMOS—External clock source input. Always associated with OSC1 pin function.

Oscillator crystal output. Connects to crystal or resonator in Crystal

Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always

associated with OSC2 pin function.

Can be software programmed for internal weak pull-ups on all inputs.

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

—

—

—

—

—

—

ST

—

ST/CMOS—Oscillator crystal input. ST buffer when configured in RC mode; CMOS

ICD Primary Communication Channel data input/output pin.

ICD Primary Communication Channel clock input/output pin.

ICD Secondary Communication Channel data input/output pin.

ICD Secondary Communication Channel clock input/output pin.

ICD Tertiary Communication Channel data input/output pin.

ICD Tertiary Communication Channel clock input/output pin.

ICD Quaternary Communication Channel data input/output pin.

ICD Quaternary Communication Channel clock input/output pin.

numbered for consistency with the inputs on larger device variants.

Quadrature Encoder Index Pulse inpu t.

Quadrature Encoder Phase A input in QEI mode.

Auxiliary Timer External Clock/Gate input in Timer mode.

Quadrature Encoder Phase A input in QEI mode.

Auxiliary Timer External Clock/Gate input in Timer mode.

External interrupt 0

External interrupt 1

External interrupt 2

PWM Fault A input

PWM 1 Low output

PWM 1 High output

PWM 2 Low output

PWM 2 High output

PWM 3 Low output

PWM 3 High output

low Reset to the device.

Compare Fault A input (for Compare channels 1, 2, 3 and 4).

Compare outputs.

otherwise.

Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator

mode. Optionally functions as CLKO in RC and EC modes.

Description

© 2006 Microchip Technology Inc. DS70118G-page 7

Page 10

dsPIC30F2010

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Name

PGD

PGC

RB0-RB5 I/O ST PORTB is a bidirectional I/O port.

RC13-RC14 I/O ST PORTC is a bidirectional I/O port.

RD0-RD1 I/O ST PORTD is a bidirectional I/O por t.

RE0-RE5,

RE8

RF2, RF3 I/O ST PORTF is a bidirectional I/O port.

SCK1

SDI1

SDO1

SS1

SCL

SDA

SOSCO

SOSCI

T1CK

T2CK

U1RX

U1TX

U1ARX

U1ATX

VDD P — Positive supply for logic and I/O pins.

SS P — Ground reference for logic and I/O pins.

V

VREF+ I Analog Analog Voltage Reference (High) input.

VREF- I Analog Analog Voltage Reference (Low) input.

Legend: CMOS = CMOS compatible input or output Analog = Analog in put

Pin

Type

I/O

I

I/O ST PORTE is a bidirectional I/O port.

I/O

I

O

I

I/O

I/O

O

I

I

I

I

O

I

O

ST = Schmitt Trigger input with CMOS levels O = Output

I = Input P = Power

Buffer

Type

ST

ST

ST

ST

—

ST

ST

ST

—

ST/CMOS

ST

ST

ST

—

ST

—

Description

In-Circuit Serial P rogramming™ data input/output pin .

In-Circuit Serial Programming clock input pi n.

Synchronous serial clock input/output for SPI #1.

SPI #1 Data In.

SPI #1 Data Out.

SPI #1 Slave Synchronization.

2

Synchronous serial clock input/output for I

Synchronous serial data input/output for I

32 kHz low-power oscillator crystal output.

32 kHz low-power oscillator crystal input. ST buffer when configured in RC

mode; CMOS otherwise.

Timer1 external clock input.

Timer2 external clock input.

UART1 Receive.

UART1 Transmit.

UART1 Alternate Receive.

UART1 Alternate Transmit.

2

C™.

C.

DS70118G-page 8 © 2006 Microchip Technology Inc.

Page 11

dsPIC30F2010

2.0 CPU ARCHITECTURE OVERVIEW

Note: This data sheet summarizes features of this g roup

of dsPIC30F devices and is not intended to be a complete

reference source. For more information on the CPU,

peripherals, register descriptions and general device

functionality, refer to the “dsPIC30F Family Reference

Manual” (DS70046). For more informat ion on the device

instruction set and programming, refer to the “dsPIC30F/

33F Programmer’s Reference Manual” (DS70157).

This document provides a summary of the

dsPIC30F2010 CPU and peripheral function. For a

complete description of this functionality, please refer

to the “dsPIC30F Family Reference Manual”

(DS70046).

2.1 Core Overview

The core has a 24-bit instruction word. The Program

Counter (PC) is 23 bits wide with the Least Significant

bit (LSb) always clear (see Section 3.1 “Program

Address Space ”), and the Most Significant bit (MSb)

is ignored during no rmal program exec ution, exce pt for

certain specialized instructions. Thus, the PC can

address up to 4M instruction words of user program

space. An instruction prefetch mechanism is used to

help maintain throughput. Program loop constructs,

free from loop count management overhead, are supported usin g the DO and REPEAT instructions, both of

which are interruptible at any point.

The working register array consists of 16x16-bit registers, each of which can act as data, address or offset

registers. One working register (W15) operates as a

software Stack Pointer for interrupts and calls.

The data space is 64 Kbytes (32K words) and is split

into two blocks, referred to as X and Y data memory.

Each block has its own independent Address Generation Unit (AGU). Most instructions operate solely

through the X memory AGU, which provides the

appearance of a single unified data space. The

Multiply-Accu mulate (MAC) class of dual s ource DSP

instructions operate through both the X and Y AGUs,

splitting the data address space into two parts (see

Section 3.2 “Data Address Space”). The X and Y

data space boundary is device specific and cannot be

altered by the user . Each dat a word consis ts of 2 bytes,

and most instruct ions can address data eith er as words

or bytes.

There are two methods of accessing data stored in

program memory:

• The upper 32 Kbytes of data sp ace memory can b e

mapped into the lower half (user space) of program

space at any 16K program word bound ary, defined

by the 8-bit Program Space Visibility Page

(PSVP AG) register. This le ts any instruction access

program space as if it were data space , with a lim itation that the access requires an additional cycle.

Moreover, only the lower 16 bits of eac h instruction

word can be accessed using this method.

• Linear indirect access of 32K word pages within

program space is als o possibl e using any work ing

register, via table read and write instructions.

Table read and write instructions can be used to

access all 24 bits of an instruction word.

Overhead-free circular buffers (Modulo Addressing)

are supported in both X and Y address spaces. This is

primarily intended to remove the loop overhead for

DSP algorithms.

The X AGU also supports Bit-Reversed Addressing on

destination ef fective addres ses, to greatly simplify inp ut

or output data reordering for radix-2 FFT algorithms.

Refer to Section 4.0 “Address Generator Units” for

details on Modulo and Bit-Reversed Addressing.

The core supports In here nt (n o op era nd), Relative, Literal, Memory Direct, Register Direct, Register Indirect,

Register Offset and Literal Offset Addressing modes.

Instructions are a ssociated w ith pred efined Addr essing

modes, depending upon their functional requirements.

For most i ns tru c ti o ns , the c or e i s c apa bl e of e xe c ut i ng

a data (or program data) memory read, a working register (data) read, a data memory write and a program

(instruction) memory read per instruction cycle. As a

result, 3-operand instructions are supported, allowing

C = A + B operations to be executed in a single cycle.

A DSP engine has been included to significantly

enhance the core arithmetic capability and throughput.

It features a high-speed 17-bit by 17-bit multiplier, a

40-bit ALU, two 40-bit saturating accumulators and a

40-bit bidirectional b arre l s hi fter. Data in the accumulator or any wor kin g regi ste r can be sh ifted up to 15 bi ts

right or 16 bits left in a single cycle. The DSP instructions operate seamles sly with all other in struct ion s and

have been desi gned for o ptimal re al-time p erformanc e.

The MAC class of instructions can concurrently fetch

two data operands from memory, while multiplying two

W registers. To enable this concurrent fetching of data

operands, the data space has been split for these

instructions and linear for all others. This has been

achieved in a transparent and flexible manner, by

dedicating certain working registers to each address

space for the MAC class of instructions.

The core does not support a multi-stage instruction

pipeline. However, a single stage instruction prefetch

mechanism is used, which accesses and partially

decodes instructions a cycle ahead of execution, in

order to maximize available execution time. Most

instructions execute in a single cycle, with certain

exceptions.

The core features a vectored exception processing

structure for traps and interrupts, with 62 independent

vectors. The exceptions consist of up to 8 traps (of

which 4 are reserved ) an d 54 int errup ts. Each interrupt

is prioritized based on a us er-assigned priority betwee n

1 and 7 (1 being the lowest priority and 7 being the

highest) in conjunction with a predetermined ‘natural

order’. Traps have fi xed prio rities, ranging from 8 to 15.

© 2006 Microchip Technology Inc. DS70118G-page 9

Page 12

dsPIC30F2010

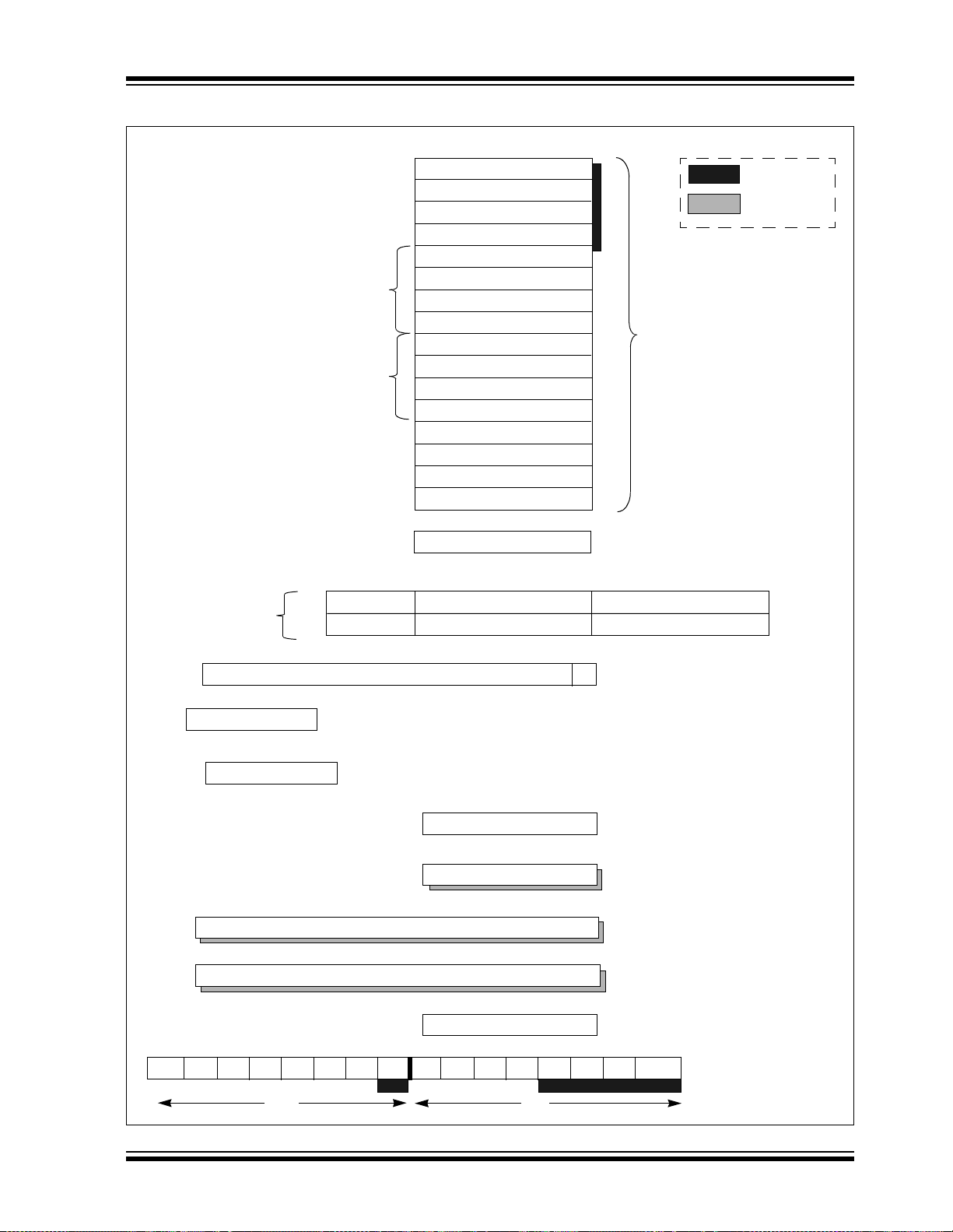

2.2 Programmer’s Model

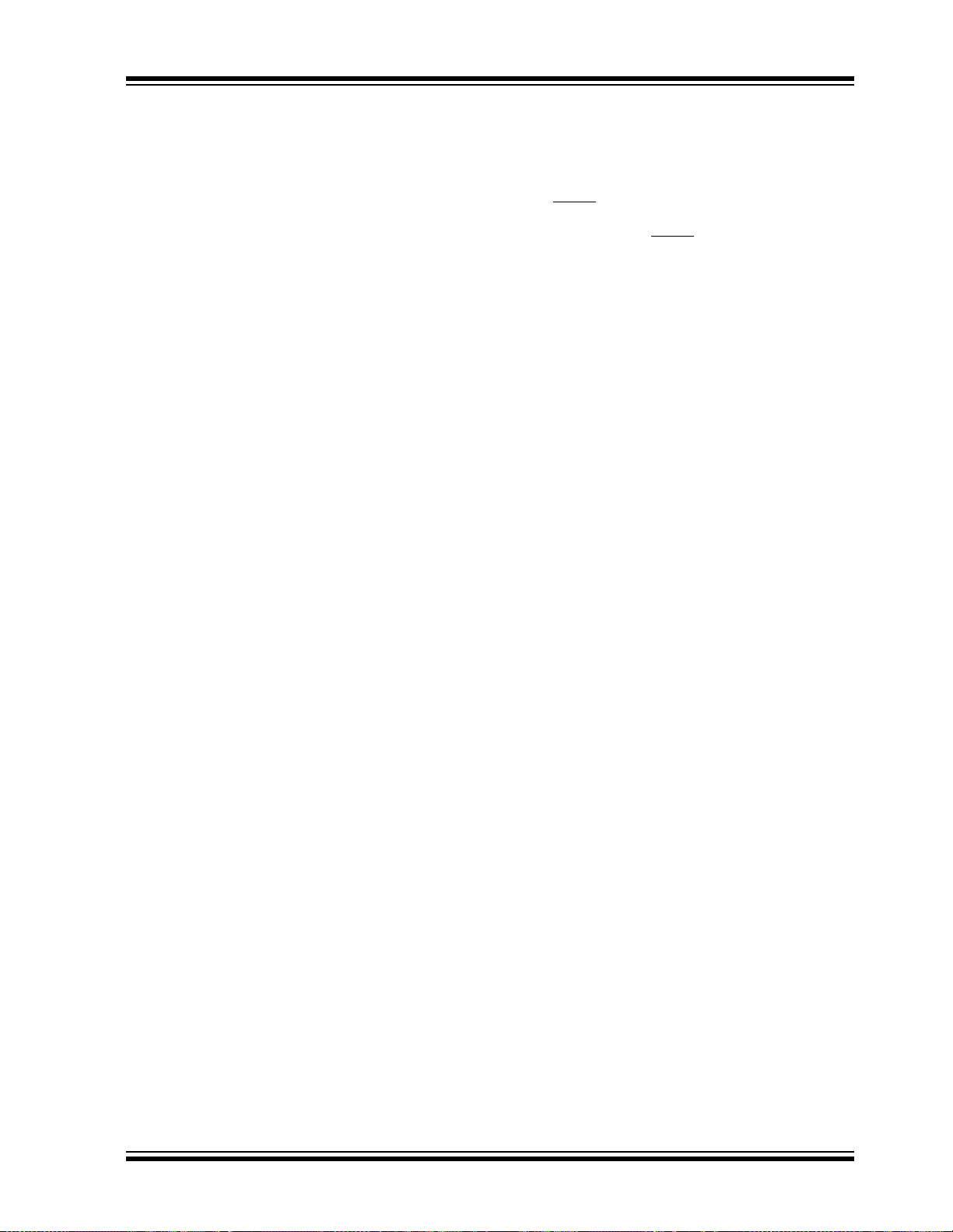

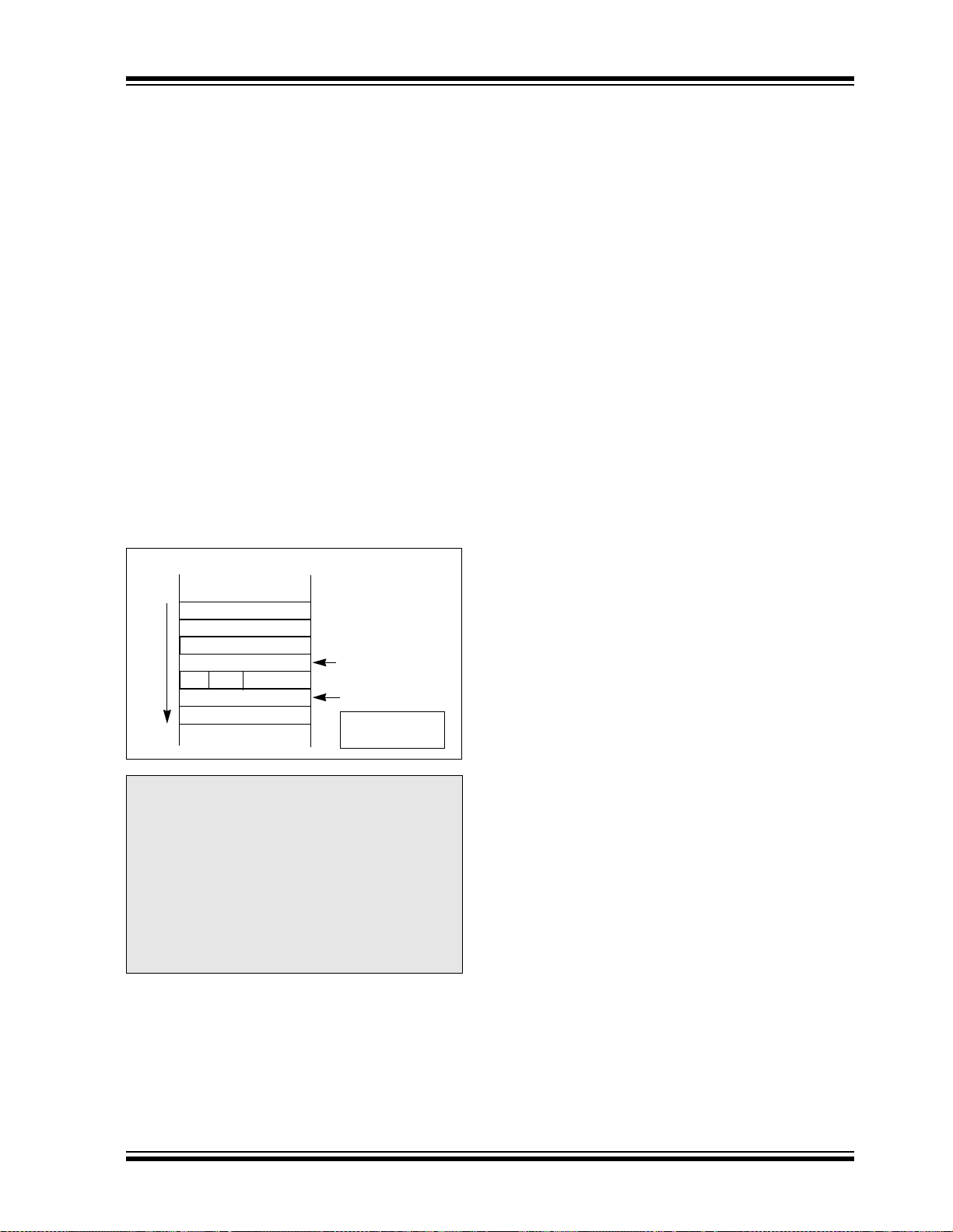

The programmer’s model is shown in Figure 2-1 and

consists of 16x16-bit working registers (W0 through

W15), 2x40-bit accumulators (ACCA and ACCB),

STATUS Register (SR), Data Table Page register

(TBLPAG), Program Space Visibility Page register

(PSVPAG), DO and REPEAT registers (DOSTART,

DOEND, DCOUNT and RCOUNT) and Program

Counter (PC). The working registers can act as data,

address or offset registers. All registers are memory

mapped. W0 acts as the W register for file register

addressing.

Some of these registers have a shadow register associated with each of them, as shown in Figure 2-1. The

shadow register is used as a temp orary holding reg ister

and can transfer it s con ten ts to or from its host reg is ter

upon the occurrence of an event. None of the shadow

registers are accessible directly. The following rules

apply for transfer of registers into and out of shadows.

• PUSH.S and POP.S

W0, W1, W2, W3, SR (DC, N, OV, Z and C bits

only) are transferred.

• DO instruction

DOSTART, DOEND, DCOUNT shadows are

pushed on loop start, and popped on loop end.

When a byte operation is performed on a working register , o nly th e L eas t S ign ifi can t By te of t he target register is affected. However, a benefit of memory mapped

working registers is that both the Least and Most Significant B ytes can be manipulate d through byte wide

data memory space accesses.

2.2.1 SOFTWARE STACK POINTER/ FRAME POINTER

The dsPIC® DSC devices contain a software stack.

W15 is the dedicated software Stack Pointer (SP), and

will be automatically modified by exception processing

and subroutine ca lls and return s. However , W15 can be

referenced by any instruction in the same manner as all

other W registers. This simplifies the reading, writing

and manipulation of the Stack Pointer (e.g., creating

stack frames).

Note: In order to protect against misaligned

stack accesses, W15<0> is always clear.

W15 is initialized to 0x0800 during a Reset. The user

may reprogram the SP during initialization to any

location within data space.

W14 has been dedicated as a Stack Frame Pointer as

defined by the LNK and ULNK instructions. However,

W14 can be referenced by any instruction in the same

manner as all other W registers.

2.2.2 STATUS REGISTER

The dsPIC DSC core has a 16-b it STATUS Register

(SR), the LSB of which is referred to as the SR Low

Byte (SRL) and the MSB as the SR High Byte (SRH).

See Figure 2-1 for SR layout.

SRL contains all the MCU ALU operation status flags

(including the Z bit), as wel l as the CPU Inter rupt Pri ority Level status bits, IPL<2:0>, and the REPEAT active

status bit, RA. During exception processing, SRL is

concatenated with the MSB of the PC to form a

complete word value which is then stacked.

The upper byte of the STATUS register contains the

DSP adder/subtracter status bits, the DO Loop Active

bit (DA) and the Digit Carry (DC) status bit.

2.2.3 PROGRAM COUNTER

The Program Counter is 23 bi ts wide. Bit 0 is a lways

clear. Therefore, the PC can address up to 4M

instruction words.

DS70118G-page 10 © 2006 Microchip Technology Inc.

Page 13

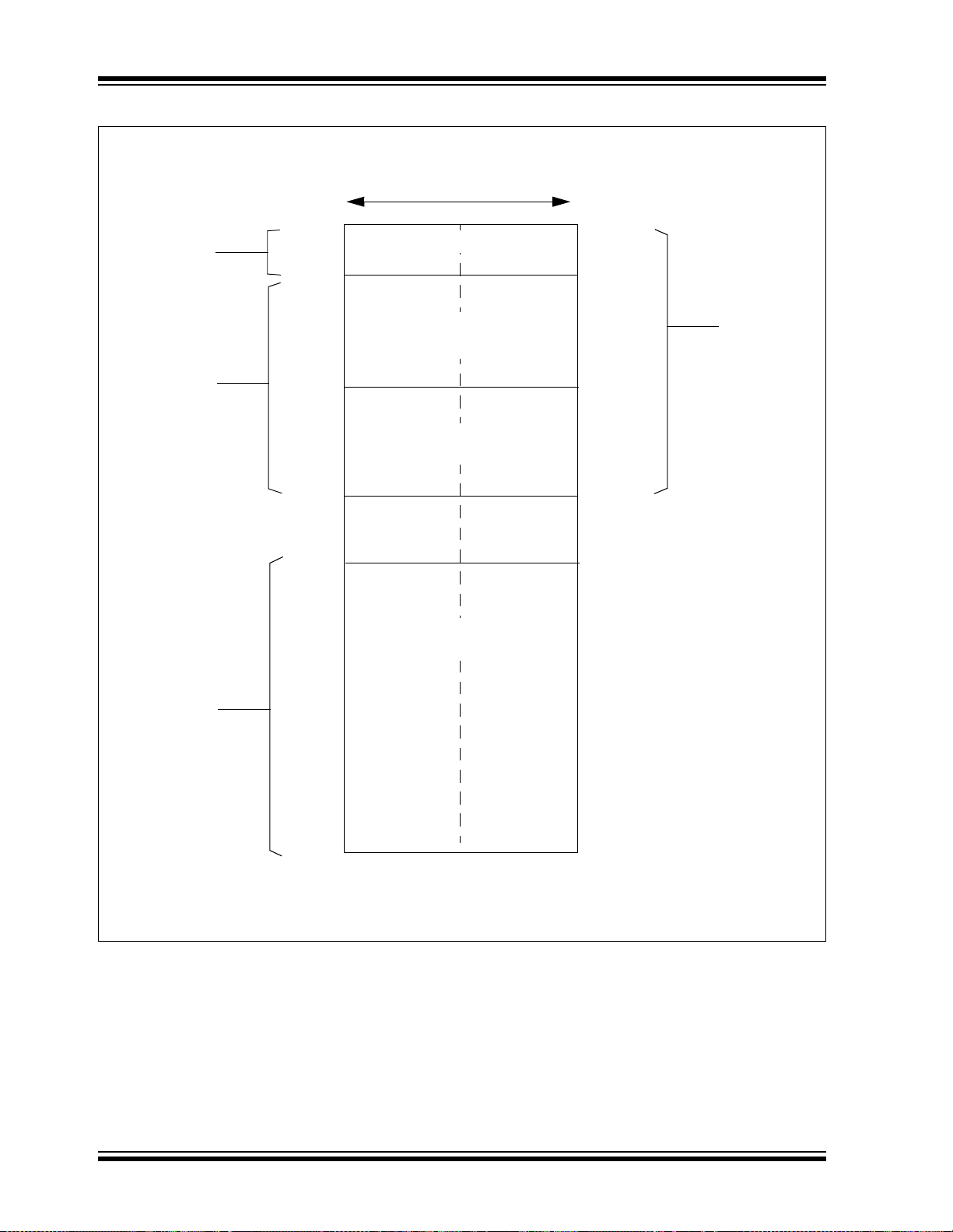

FIGURE 2-1: PROGRAMMER’S MODEL

DSP Operand

Registers

DSP Address

Registers

W0/WREG

W1

W2

W3

W4

W5

W6

W7

W8

W9

W10

W11

W12/DSP Offset

W13/DSP Write-Back

W14/Frame Pointer

W15/Stack Pointer

dsPIC30F2010

D0D15

PUSH.S Shadow

DO Shadow

Legend

Working Registers

DSP

Accumulators

PC22

7

22

22

TABPAG

TBLPAG

7

PSVPAG

PSVPAG

AD39 AD0AD31

ACCA

ACCB

0

Data Table Page Address

0

SPLIM Stack Pointer Limit Register

Program Space Visibility Page Address

15

RCOUNT

15

DCOUNT

DOSTART

DOEND

PC0

AD15

Program Counter

0

0

REPEAT Loop Counter

0

DO Loop Counter

0

DO Loop Start Address

DO Loop End Address

15

CORCON

OA OB SA SB

© 2006 Microchip Technology Inc. DS70118G-page 11

OAB SAB

SRH

DA DC

IPL2 IPL1

RA

IPL0 OV

SRL

N

0

Core Configuration Register

C

Z

STATUS Register

Page 14

dsPIC30F2010

2.3 Divide Support

The dsPIC DSC devices feature a 16/16-bit signed

fractional divide ope rati on , as w ell as 32/16-bit and 16/

16-bit signed an d unsigned intege r divide operati ons, in

the form of single instruction iterative divides. The following instructions and data sizes are supported:

1. DIVF – 16/16 signed fractional divide

2. DIV.sd – 32/16 signed divide

3. DIV.ud – 32/16 unsigned divide

4. DIV.sw – 16/16 signed divide

5. DIV.uw – 16/16 unsigned divide

The 16/16 divides are similar to the 32/16 (same number

of iterations), but the dividend is either zero-extended or

sign-extended during the first iteration.

The divide instructions must be executed within a

REPEAT loop. Any other form of exec ution (e.g. a serie s

of discrete divide instruc tions) w ill not function c orrectly

because the instruction flow depends on RCOUNT.

The divide instru ction does not automat icall y set up the

RCOUNT value, and it must, therefore, be explicitly

and correctly specified in the REPEAT instruction, as

shown in Table 2-1 (REPEAT will execute the target

instruction {operand value + 1} times). The REPEAT

loop count must be set up for 18 iterati ons of the DIV/

DIVF instruction. Thus, a complete divide operation

requires 19 cycles.

Note: The Divide flow is interruptible. However,

the user needs to save the context as

appropriate.

TABLE 2-1: DIVIDE INSTRUCTIONS

Instruction Function

DIVF Signed fractional divide: Wm/Wn → W0; Rem → W1

DIV.sd Signed divide: (Wm + 1:Wm)/Wn → W0; Rem → W1

DIV.ud Unsigned divide: (Wm + 1:Wm)/Wn → W0; Rem → W1

DIV.sw (or DIV.s) Signed divide: Wm/Wn → W0; Rem → W1

DIV.uw (or DIV.u) Unsigned divide: Wm/Wn → W0; Rem → W1

DS70118G-page 12 © 2006 Microchip Technology Inc.

Page 15

dsPIC30F2010

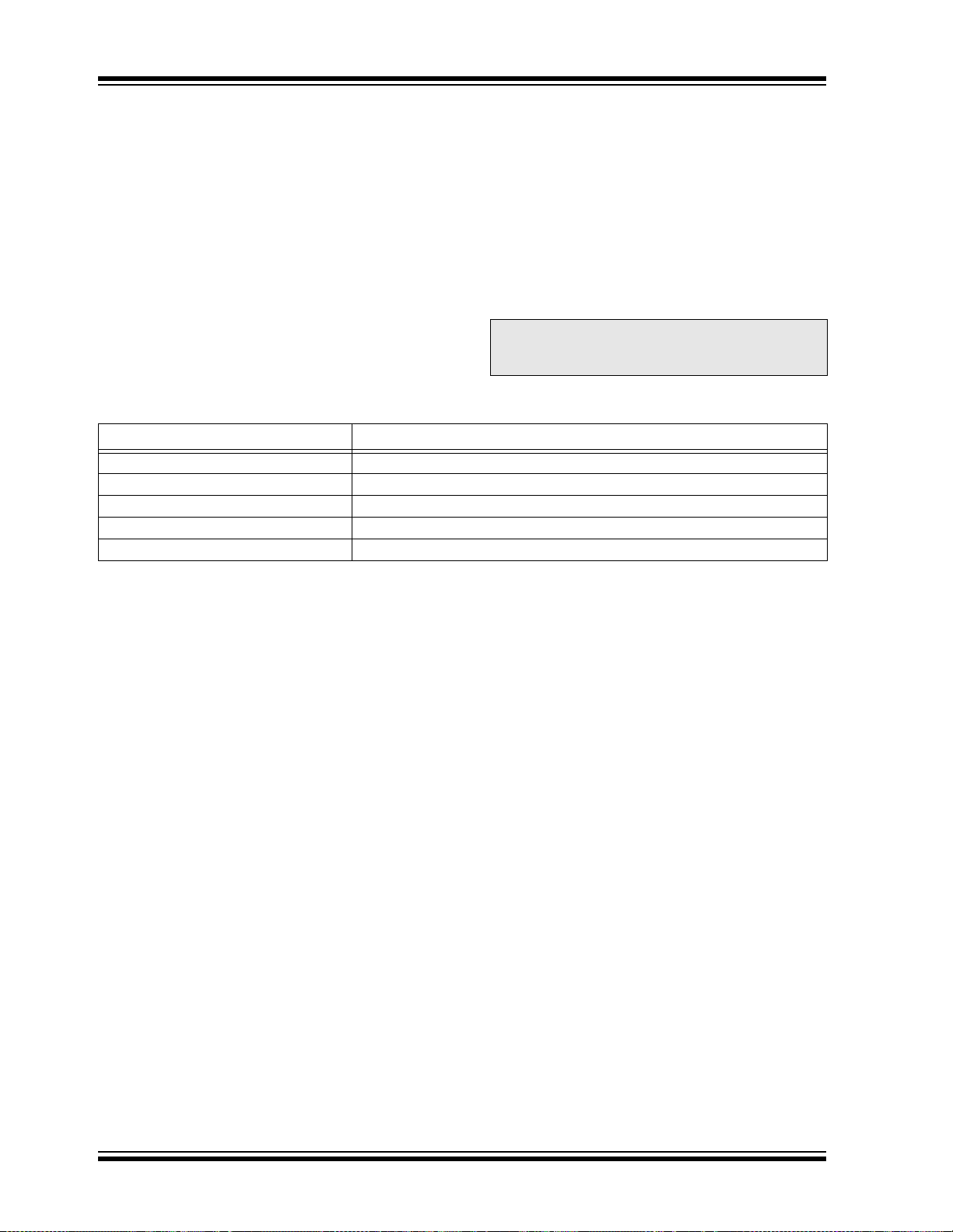

2.4 DSP Engine

The DSP engine consists of a high-speed 17-bit x

17-bit multiplier , a barrel s hifter , and a 40-bit adde r/subtracter (with two target accumulators, round and

saturation logic).

The DSP engine also has the capability to perform inherent accumulator-to-accumulator operations, which

require no additional data. These instructions are ADD,

SUB and NEG.

The DSP engine has various options selected through

various bits in the CPU Core Configuration Register

(CORCON), as listed below:

1. Fractional or integer DSP multiply (IF).

2. Signed or unsigned DSP multiply (US).

3. Conventional or convergent rounding (RND).

4. Automatic saturation on/off for ACCA (SATA).

5. Automatic saturation on/off for ACCB (SATB).

6. Automatic saturation on/off for writes to data

memory (SATDW).

7. Accumulator Saturation mode selection

(ACCSAT).

Note: For CORCON layout, see Table 3-3.

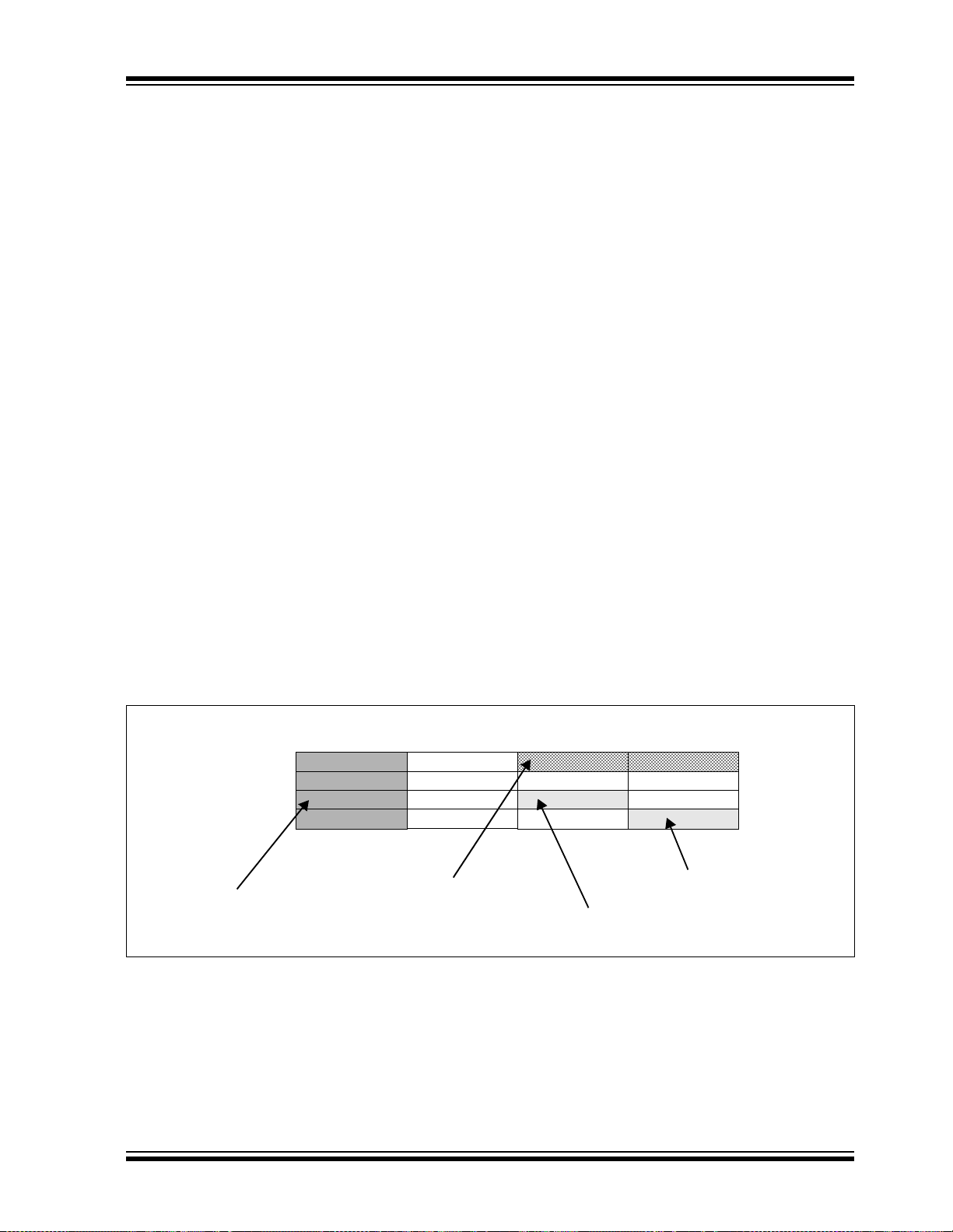

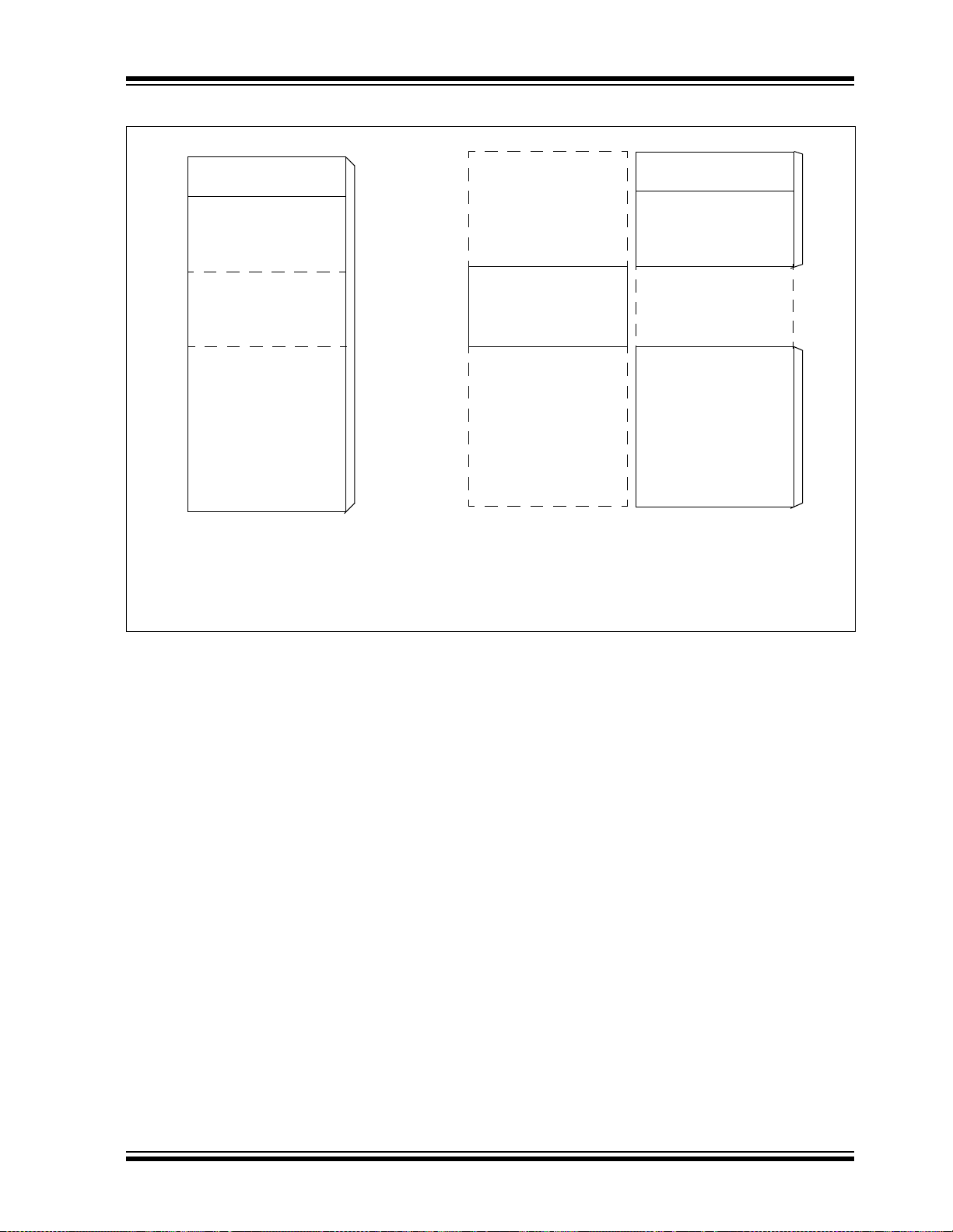

A block diagram of the DSP engine is shown in

Figure 2-2.

TABLE 2-2: DSP INSTRUCTION SUMMARY

Instruction Algebraic Operation ACC WB?

CLR A = 0 Yes

ED A = (x – y)

EDAC A = A + (x – y)

MAC A = A + (x * y) Yes

MAC A = A + x

MOVSAC No change in A Yes

MPY A = x * y No

MPY.N A = – x * y No

MSC A = A – x * y Yes

2

2

2

No

No

No

© 2006 Microchip Technology Inc. DS70118G-page 13

Page 16

dsPIC30F2010

FIGURE 2-2: DSP ENGINE BLOCK DI AGR AM

40

Carry/Borrow Out

Carry/Borrow In

40-bit Accumulator A

40-bit Accumulator B

Saturate

Adder

Negate

40

Round

Logic

S

a

16

t

u

r

a

t

e

40

40

Barrel

Shifter

32

32

40

16

X Data Bus

16

Zero Backfill

40

Sign-Extend

Y Data Bus

33

17-bit

Multiplier/Scaler

16

To/From W Array

DS70118G-page 14 © 2006 Microchip Technology Inc.

16

Page 17

dsPIC30F2010

2.4.1 MULTIPLIER

The 17x17-bit multiplier is capable of signed or

unsigned operati on and can mul tiplex i ts ou tput usi ng a

scaler to support either 1.31 fractional (Q31) or 32-bit

integer results. Unsigned operands are zero-extended

into the 17th bit of the multiplier input value. Signed

operands are sign-exten ded into the 17th bit of the mu ltiplier input value. The output of t he 17x17-bit multip lier/

scaler is a 33-bit value, which is sign-extended to 40

bits. Intege r data is inherently rep resented as a signed

two’s complement value, where the MSB is defined as

a sign bit. Generally speaking, the range of an N-bit

two’s complement integer is -2

bit integer, the data range is -32 76 8 (0x 800 0) to 3276 7

(0x7FFF), including 0. For a 32-bit integer, the data

range is -2,147,483,648 (0x8000 0000) to

2,147,483,645 (0x7FFF FFFF ).

When the multiplier is configured for fractional multiplication, the data is represented as a two’s complement

fraction, where the M SB is defined as a sign b it and the

radix point is impl ied to lie just after the sign b it (QX format). The range of an N-bit two’s complement fraction

with this implied radix point is -1.0 to (1-2

16-bit fraction, the Q15 data range is -1.0 (0x8000) to

0.999969482 (0x7FFF), including ‘0’ and has a precision of 3.01518x1 0

tiply operation generates a 1.31 product, which has a

precision of 4.65661x10

The same multiplier is used to support the MCU multiply instructions, which include integer 16-bit signed,

unsigned and mixed sign multiplies.

The MUL instruction may be directed to use byte or

word-sized operands. Byt e operands will direct a 16-bit

result, and word operands will direct a 32-bit result to

the specified register(s) in the W array.

-5

. In Fractional mode, a 16x16 mu l-

-10

N-1

N-1

to 2

– 1. For a 16-

1-N

). For a

.

2.4.2 DATA ACCUMULATORS AND ADDER/SUBTRACTER

The data accumulator consists of a 40-bit adder/subtracter with automatic si gn extension logic. It can selec t

one of two accumulators (A or B) as its preaccumulation source and post-accumulation destination. For the ADD and LAC instructions, the data to be

accumulated or load ed ca n be optio nally sca led v ia th e

barrel shifter, prior to accumulation.

2.4.2.1 Adder/Subtracter, Overflow and

Saturation

The adder/subtracter is a 40-bit adder with an optional

zero input into one side and either true or complement

data into the other input. In the case of addition, the

carry/borrow

true data (not complemented), whereas in the case of

subtraction, the carry/bo rrow

other input is complemented. The adder/subtracter

generates overflow status bits SA/SB and OA/OB,

which are latched and reflected in the STATUS

Register.

• Overflow from bit 39: this is a catastrophic

overflow in which the sign of the accumulator is

destroyed.

• Overflow into guard bits 32 through 39: this is a

recoverable overflow. This bit is set whenever all

the guard bits are not identical to each other.

The adder has an additional saturation block which

controls accumulator data saturation, if selected. It

uses the result of the adder, the overflow status bits

described above, and the SATA/B (CORCON<7:6>)

and ACCSAT (CORCON<4>) mode control bits to

determine when and to what value to saturate.

Six STATUS register bits have been provided to

support saturation and overflow; they are:

1. OA:

ACCA overflowed into guard bits

2. OB:

ACCB overflowed into guard bits

3. SA:

ACCA saturated (bit 31 overflow and sa turation)

or

ACCA overflowed into guard bits and saturated

(bit 39 overflow and s aturation)

4. SB:

ACCB saturated (bit 31 overflow and sa turation)

or

ACCB overflowed into guard bits and saturated

(bit 39 overflow and s aturation)

5. OAB:

Logical OR of OA and OB

6. SAB:

Logical OR of SA and SB

The OA and OB bits are modified each time data

passes through the adder/subtracter. When set, they

indicate that the most recent operation has overflowed

into the accumulator guard bits (bits 32 through 39).

The OA and OB bits can also optionally generate an

arithmetic warning trap when set and the corresponding overflow trap flag enable bit (OVATE, OVBTE) in

the INTCON1 register (refer to Section 5.0 “Inter-

rupts”) is set. This allows the user to take immediate

action, for example, to correct system gain.

input is active high and the other input is

input is active low and the

© 2006 Microchip Technology Inc. DS70118G-page 15

Page 18

dsPIC30F2010

The SA and SB bits are modified each ti me data pass es

through the adder/subtracter, but can only be cleared by

the user. When set, they indicate that the accumulator

has overflowed its maximum range (bit 31 for 32-bit saturation, or bit 39 for 40-bit saturation) and will be saturated (if saturation is enabled). When saturation is not

enabled, SA and SB default to bit 39 overflow and thus

indicate that a catastrophic overflow has occurred. If the

COVTE bit in the INTCON1 register is set, SA and SB

bits will generate an arithmetic warning trap when

saturation is disabled.

The overflow and saturation status bits can optionally

be viewed in the S tat us Register (SR) as the logical OR

of OA and OB (i n bit OAB) , and the lo gical OR of SA

and SB (in bit SAB). This allows programmers to check

one bit in the STATUS register to determine if either

accumulator has overflowed, or one bit to determine if

either accumulator has s aturated. T his w ould be us eful

for complex number arithmetic which typically uses

both the accumulators.

The device supports three Saturation and Overflow

modes.

1. Bit 39 Overflow and Saturation:

When bit 39 overflow and saturation occurs, the

saturation logic loads the maximally positive 9.31

(0x7FFFFFFFFF) or maximally negative 9.31

value (0x8000000000) into the target accumulator. The SA or SB bit is set and remains set until

cleared by the user. This is referred to as ‘super

saturation’ and provides protection against erroneous data or unexpected algorithm problems

(e.g., gain calculations).

2. Bit 31 Overflow and Saturation:

When bit 31 overflow and saturation occurs, the

saturation logic then loads the maximally positive

1.31 value (0x007FFFFFFF) or maximally negative 1.31 value (0x0080000000) into the target

accumulator . The SA or SB bit is set and rem ains

set until cleared by the user . When this Saturation

mode is in effect, the guard bits are not used (so

the OA, OB or OAB bits are never set).

3. Bit 39 Catastrophic Overflow

The bit 39 overflow status bit from the adder is

used to set the SA or SB bit, which remain set

until cleared by the user. No saturation operation

is performed and the accumulator is allowed to

overflow (destroying it s sign). If the C OVTE bit in

the INTCON1 register is set, a catastrophic

overflow can initiate a trap exception.

2.4.2.2 Accumulator ‘Write-Back’

The MAC class of instructions (with the exception of

MPY, MPY.N, ED and EDAC) can optionally write a

rounded version of the high word (bits 31 through 16)

of the accumulator that is not targeted by the instructio n

into data spac e memory. The write is performed across

the X bus into combined X and Y address space. The

following addressing modes are supported:

1. W13, Regi ster Direct:

The rounded contents of the non-target

accumulator are written into W13 as a 1.15

fraction.

2. [W13]+=2, Register Indirect with Post-Increment:

The rounded conten ts of the non- target accumulator are written into the address pointed to by

W13 as a 1.15 fraction. W13 is then

incremented by 2 (for a word write).

2.4.2.3 Round Logic

The round logic is a combinational block, which performs a conventional (biased) or convergent (unbiased)

round function during an accumulator write (store). The

Round mode is determined by the state of the RND bit

in the CORCON register. It generates a 16-bit, 1.15 data

value which is passed to the data space write saturation

logic. If rounding is not indicated by the instruction, a

truncated 1.15 data value is stored and the least

significant word (lsw) is simply discarded.

Conventional rounding takes bit 15 of the accumulator,

zero-extends it and ad ds it to the AC CxH w ord (bi t s 16

through 31 of the accumulato r). If the ACCxL word (bit s

0 through 15 of the accumulator) is between 0x8000

and 0xFFFF (0x8000 included), ACCxH is incremented. If ACCxL is between 0x0000 and 0x7FFF,

ACCxH is left unchanged. A consequence of this

algorithm is that over a succ ession of ran dom roundin g

operations, the value will tend to be biased slightly

positive.

Convergent (or unbiased) rounding operates in the

same manner as conventional rounding, except when

ACCxL equals 0x8000 . If this is the case, the Least Significant bit (bit 16 of the accumulator) of ACCxH is

examined. If it is ‘1’, ACCxH is incremented. If it is ‘0’,

ACCxH is not modified. Assuming that bit 16 is effectively random in nature, this scheme will remove any

rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC) or rounded (SAC.R) version of the c ontents

of the target accumul ator to data mem ory , via the X bu s

(subject to data saturation, see Section 2.4.2.4 “Data

Space Write Saturation”). Note that for the MAC cl as s

of instructions, the accumulator write-back operation

will function in the s ame mann er , a ddressing co mbine d

MCU (X and Y) data space though the X bus. For this

class of instructions, the data is always subject to

rounding.

DS70118G-page 16 © 2006 Microchip Technology Inc.

Page 19

dsPIC30F2010

2.4.2.4 Data Space Write Saturation

In addition to adder/subtrac ter saturation, writes to dat a

space may also be saturated, but without affecting the

contents of the source accumulator. The data space

write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input,

together with overflow status from the original source

(accumulator) and the 16-bit round adder. These are

combined and used t o sele ct the a ppr opriate 1.15 fra ctional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data

(after rounding or truncation) is tes te d for ove rflo w and

adjusted accordingly. For input data greater than

0x007FFF, data written to memory is fo rced to the ma ximum positi ve 1. 15 val ue, 0x 7FFF. For input data less

than 0xFF8000, da ta wr itten to me mory i s forced to th e

maximum negative 1.15 value, 0x8000. The Most Significant bit of the source (bit 39) is used to determine

the sign of the operand being tested.

If the SA TDW bi t in the CORCON regis ter is not set , the

input data is always passed through unmodified under

all conditions.

2.4.3 BARREL SHIFTER

The barrel shifter is capable of performing up to 15-bit

arithmetic or logic right shifts, or up to 16-bit left shifts

in a single c ycle. The sou rce can be ei ther of th e two

DSP accumulators or the X bus (to support multi-bit

shifts of register or memory data).

The shifter requi res a signed binary val ue to de term in e

both the magnitude (num ber of bits) and direction of the

shift operation. A positive value will shift the operand

right. A negative value will shift the operand left. A

value of 0 will not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a

40-bit result for DSP shift operati ons and a 16- bit result

for MCU shift operations. Data from the X bus is presented to the barrel shifter between bit positions 16 to

31 for right shifts, and bit positio ns 0 to 15 for left shift s.

© 2006 Microchip Technology Inc. DS70118G-page 17

Page 20

dsPIC30F2010

NOTES:

DS70118G-page 18 © 2006 Microchip Technology Inc.

Page 21

dsPIC30F2010

3.0 MEMORY ORGANIZATION

Note: This data sheet summa rizes features o f this

group of dsPIC30 F devi ces and is not inte nded to be

a complete reference source. For more information

on the CPU, peripherals, register descriptions and

general device functionality, refer to the “dsPIC30F

Family Reference Manual” (DS70046). For more

information on the device instruction set and programming, refer to the “dsPIC30F/33F

Programmer’s Reference Manual” (DS70157).

3.1 Program Address Space

The program address space is 4M instruction words. It

is addressable by a 24-bit value from either the 23-bit

PC, table instruction Effective Address (EA), or data

space EA, when program space is mapped into data

space, as defined by Table 3-1. Note that the program

space address i s incr ement ed by two betw een suc cessive program words, in order to provide compatibility

with data space addressing.

User program space access is restricted to the lower

4M instruction word address range (0x000000 to

0x7FFFFE), for all acce sses other than TBLRD/TBLWT,

which use TBLPAG<7> to determine user or configuration space access. In Table 3-1, Read/Write instructions, bit 23 allows a ccess to the De vice ID, the User ID

and the Configuration bits. Otherwise, bit 23 is always

clear.

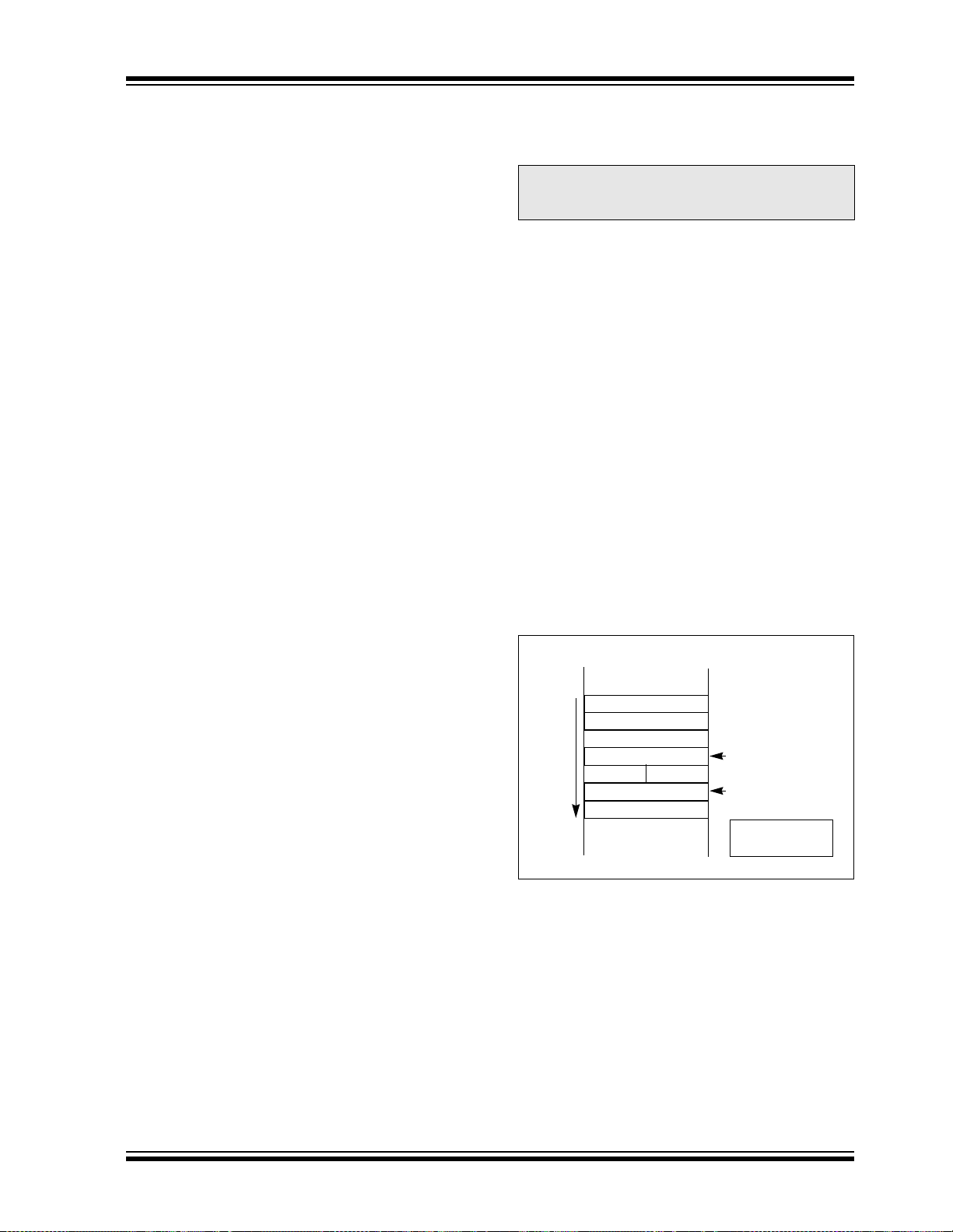

FIGURE 3-1:

Space

User Memory

PROGRAM SPACE MEMORY

MAP FOR dsPIC3 0F2010

Reset - GOTO Instruction

Reset - Target Address

Reserved

Ext. Osc. Fail Trap

Address Error Trap

Stack Error Trap

Arithmetic Warn. Trap

Reserved

Reserved

Reserved

Vector 0

Vector 1

Vector 52

Vector 53

Alternate Vector Table

User Flash

Program Memory

(4K instructions)

Reserved

(Read 0’s)

Data EEPROM

(1 Kbyte)

000000

000002

000004

000014

00007E

000080

0000FE

000100

001FFE

002000

7FFBFE

7FFC00

7FFFFE

800000

Vector Tables

Note: The address map shown in Figure 3-1 is

conceptual, and the actual memory configuration may vary across individual

devices depending on available memory.

Reserved

8005BE

Space

Configuration Memory

UNITID (32 instr.)

Reserved

Device Configuration

Registers

Reserved

DEVID (2)

8005C0

8005FE

800600

F7FFFE

F80000

F8000E

F80010

FEFFFE

FF0000

FFFFFE

© 2006 Microchip Technology Inc. DS70118G-page 19

Page 22

dsPIC30F2010

TABLE 3-1: PROGRAM SPACE ADDRESS CONSTRUCTION

Access Type

Access

Space

<23> <22:16> <15> <14:1> <0>

Instruction Access User 0 PC<22:1> 0

TBLRD/TBLWT User

TBLPAG<7:0> Data EA <15:0>

(TBLPAG<7> = 0)

TBLRD/TBLWT Configuration

TBLPAG<7:0> Data EA <15:0>

(TBLPAG<7> = 1)

Program Space Visibility User 0 PSVPAG<7:0> Data EA <14:0>

FIGURE 3-2: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

23 bits

Using

Program

Counter

0

Program Space Address

0Program Counter

Select

Using

Program

Space

Visibility

Using

Table

Instruction

Note: Program Space Visibility cannot be used to access bits <23:16> of a word in program memory.

0

1/0

User/

Configuration

Space

Select

PSVPAG Reg

8 bits

TBLPA G Reg

8 bits

1

24-bit EA

EA

15 bits

EA

16 bits

Byte

Select

DS70118G-page 20 © 2006 Microchip Technology Inc.

Page 23

dsPIC30F2010

3.1.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

This architecture fetc hes 24 -bi t w ide prog ram me mo ry.

Consequently, instructions are always aligned. However, as the architecture is modified Harvard, data can

also be present in program space.

There are two methods by which program space can

be accessed: via special table instructions, or through

the remapping of a 16 K word program space p age in to

the upper half o f da ta space (see Section 3.1.2 “Data

Access from Program Memory Using Program

Space Visibility”). The TBLRDL and TBLWTL instruc-

tions offer a direct method of reading or writing the lsw

of any address within program space, without going

through data sp ac e. The TBLRDH and TBLWTH instruc-

tions are the only method wh ereby the upp er 8 bits of a

program space word can be accessed as data.

The PC is incremented by two for each successive

24-bit program word. This allows program memory

addresses to directly map to data space addresses.

Program memory can thus be regarded as two 16-bit

word wide address sp ac es , res id ing sid e by si de, each

with the same address range. TBLRDL and TBLWTL

access the space which contains the least significant

data word, and TBLRDH a nd TBLWTH ac cess the sp ace

which contains the Most Significant data Byte.

Figure 3-2 shows h ow th e EA is created for table op erations and data space accesses (PSV = 1). Here,

P<23:0> refers to a program space word, whereas

D<15:0> refers to a data space word.

A set of T able Instruction s are provided to move byte or

word-sized data to and from program space.

1. TBLRDL: Table Re ad Low

Word: Read the least significant word of the

program address;

P<15:0> maps to D<15:0>.

Byte: Read one of the LSBs of the program

address;

P<7:0> maps to the destination byte when byte

select = 0;

P<15:8> maps to the d estination b yte when byte

select = 1.

2. TBLWTL: Table Write Lo w (ref er t o Section 6.0

“Flash Program Memory” for details on Flash

Programming).

3. TBLRDH: Table Re ad High

Word: Read the most significant word of the

program address;

P<23:16> maps to D<7:0>; D<15:8> always

be = 0.

Byte: Read one of the MSBs of the program

address;

P<23:16> maps to the destination byte when

byte select = 0;

The destination byte will always be = 0 when

byte select = 1.

4. TBLWTH: Table Write High (ref er to Section 6.0

“Flash Program Memory” for details on Flash

Programming).

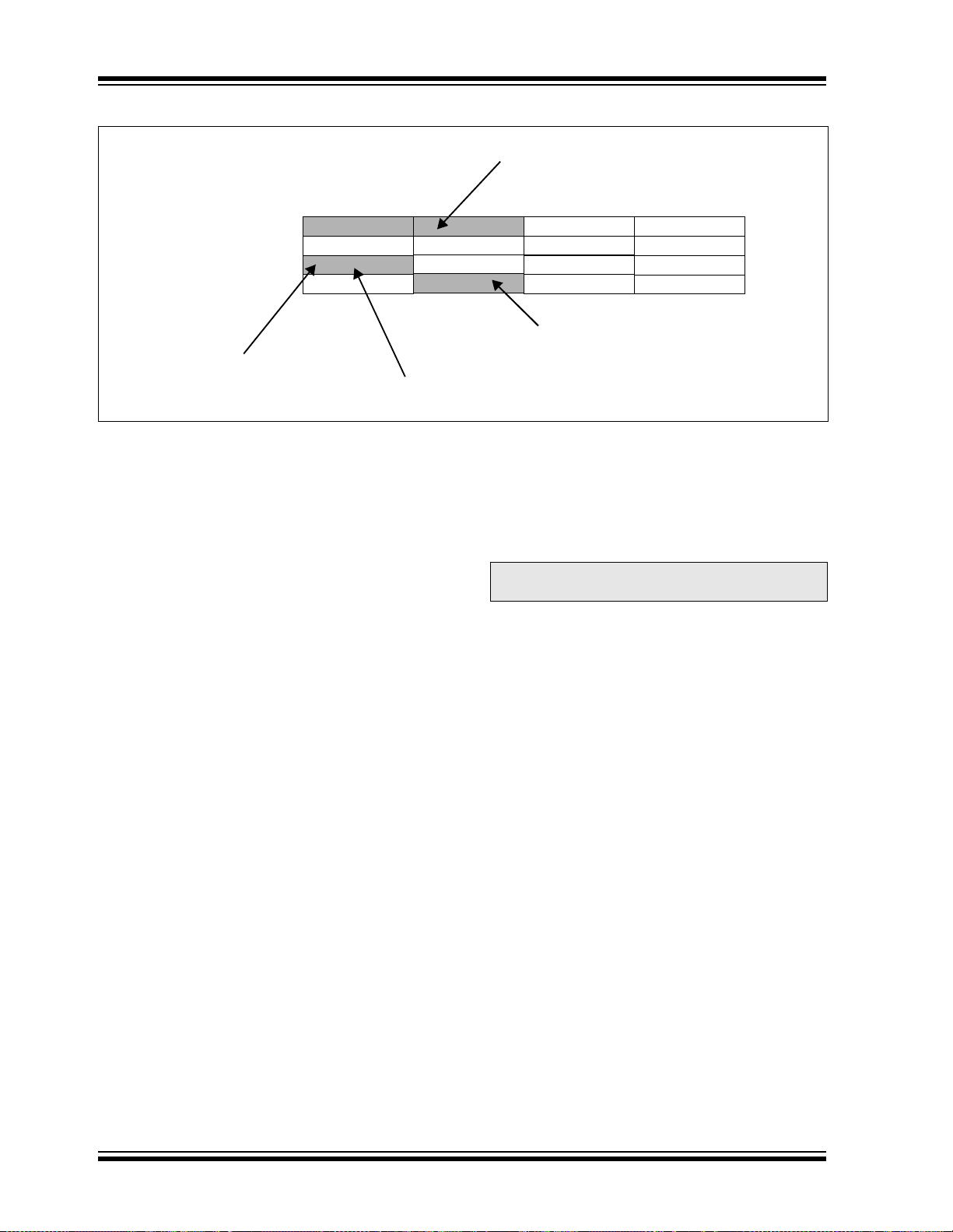

FIGURE 3-3: PROGRAM DATA T ABLE A CCESS (LEAST SI GNIFICANT WO RD)

PC Address

0x000000

0x000002

0x000004

0x000006

Program Memory

‘Phantom’ Byte

(Read as ‘0’).

00000000

00000000

00000000

00000000

23

TBLRDL.W

16

8

TBLRDL.B (Wn<0> = 0)

TBLRDL.B (Wn<0> = 1)

0

© 2006 Microchip Technology Inc. DS70118G-page 21

Page 24

dsPIC30F2010

FIGURE 3-4: PROGRAM DATA T ABLE ACCESS (M OST SI GNIFICANT BYTE)

TBLRDH.W

PC Address

0x000000

0x000002

0x000004

0x000006

Program Memory

‘Phantom’ Byte

(Read as ‘0’)

00000000

00000000

00000000

00000000

23

TBLRDH.B (Wn<0> = 1)

3.1.2 DATA ACCESS FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be

mapped into any 16K word program space page. This

provides transparent access of stored constant data

from X data space, without the need to use special

instructions (i.e., TBLRDL/H, TBLWTL/H instructions).

Program space access through the data space occurs

if the MSb of the data space EA is set and program

space visibility is enabled, by setting the PSV bit in the

Core Control register (CORCON). The functions of

CORCON are discussed in Section 2.4 “DSP

Engine”, DSP Engine.

Data accesses to this area add an additional cycle to

the instruction being executed, since two program

memory fetches are required.

Note that the upper half of addressable data space is

always part of the X data space. Therefore, when a

DSP operation uses program sp ace mapp ing to acc ess

this memory region , Y d at a space should ty pic al ly contain state (variable) data for DSP operations, whereas

X data space should typically contain coefficient

(constant) data.

Although each da ta sp ace addres s, 0x8000 and higher ,

maps directly into a corresponding program memory

address (see Figure 3-5), only the lower 16-bits of the

24-bit program word are used to contain the data. The

upper 8 bits shoul d be progra mmed to forc e an illeg al

instruction to maintain machine robustness. Refer to

the “dsPIC30F/33F Programmer’s Reference Manual”

(DS70157) for details on instruction encoding.

16

TBLRDH.B (Wn<0> = 0)

Note that by incrementing the PC by 2 for each program memory word, the Least Significant 15 bits of

data space addresses directly map to the Least Significant 15 bits in the corresponding program space

addresses. The rem aining b its a re provid ed by th e Program Space Vis ibilit y Page regi ster, PSVPAG<7:0>, as

shown in Figure 3-5.

Note: PSV access is tempor arily dis abled d uring

table reads/writes.

For instructions that use PSV which are executed

outside a REPEAT loop:

• The following instructions will require one instruction cycle in addition to the specified execution

time:

- MAC class of instructions with data operand

prefetch

- MOV instructions

- MOV.D instructions

• All other instructions will require two instruction

cycles in addition to the specified execution time

of the instruction.

For instructions that use PSV which are executed

inside a REPEAT loop:

• The following inst ances wi ll require two ins truction

cycles in addition to the specified execution time

of the instruction:

- Execution in the first iteration

- Execution in the last iteration

- Execution prior to exiting the loop due to an

interrupt

- Execution upon re-entering the loop after an

interrupt is serviced

• Any other iteration of the REPEAT loop will allow

the instruction, accessing data using PSV, to

execute in a single cycle.

8

0

DS70118G-page 22 © 2006 Microchip Technology Inc.

Page 25

dsPIC30F2010

FIGURE 3-5 : DATA S PACE WIND O W I NT O P ROG R AM SPACE OPER AT ION

Data Space Program Space

0x0000

EA<15> =

Data

Space

EA

BSET CORCON,#2 ; PSV bit set

MOV #0x00, W0 ; Set PSVPAG register

MOV W0, PSVPAG

MOV 0x9200, W0 ; Access program memory location

16

EA<15> = 1

Upper half of Data

Space is mapped

into Program Space

15

0

15

; using a data space access

0x8000

15

0xFFFF

PSVPAG

0x00

8

Address

Concatenat i on

(1)

23 15 0

23

Data Read

0x100100

0x001200

0x001FFE

Note: PSVPAG is an 8-bit register, containing bits <22:15> of the program space address

(i.e., it defines the page in program space to which the upper half of data space is being mapped).

3.2 Data Address Space

The core has two data spaces. The data spaces can be

considered either separate (for some DSP instructions), or as one unified linear address range (fo r MCU

instructions). The dat a spaces are accessed using tw o

Address Generation Units (AGUs) and separate data

paths.

3.2.1 DATA SPACE MEMORY MAP

The data space memory is split into two blocks, X and

Y data space. A key element of this architectur e is th at

Y space is a subset of X space, and is fully contained

within X space. In order to provide an apparent linear

addressing space, X and Y spaces have contiguous

addresses.

When executing any instruction other than one of the

MAC class of instructions, the X block consists of the

256 byte data address space (including all Y

addresses). When executing one of the MAC class of

instructions, the X block consists of the 256 bytes data

address space excluding the Y address block (for data

reads only). In other word s, all other i nstructions rega rd

the entire data memory as one composite address

space. The MAC class instructions extract the Y

address space from data space and address it using

EAs sourced from W10 and W11. The remaining X data

space is addressed using W8 and W9. Both address

spaces are concurrently accessed only with the MAC

class instructions.

A data space memory map is shown in Figure 3-6.

© 2006 Microchip Technology Inc. DS70118G-page 23

Page 26

dsPIC30F2010

FIGURE 3-6: DA TA SPA CE MEM OR Y MA P

SFR Space

(Note)

512 bytes

SRAM Space

MSB

Address

0x0001

0x07FF

0x0801

0x08FF

0x0901

0x09FF 0x0A00

(Note)

0x8001

16 bits

LSBMSB

SFR Space

X Data RAM (X)

256 bytes

Y Data RAM (Y)

256 bytes

LSB

Address

0x0000

0x07FE

0x0800

2560 bytes

Near

Data

Space

0x08FE

0x0900

0x8000

X Data

Unimplemented (X)

Optionally

Mapped

into Program

Memory

0xFFFF

Note: Unimplemented SFR or SRAM locations read as ‘0’.

0xFFFE

DS70118G-page 24 © 2006 Microchip Technology Inc.

Page 27

dsPIC30F2010

FIGURE 3-7: DATA SPACE FOR MCU AND DSP (MAC CLASS) INSTRUCTIONS

SFR SPACE

UNUSED

(Y SPACE)

X SPACE

Non-MAC Class Ops (Read/Write) MAC Class Ops Read-Only

MAC Class Ops (Wr i te)

Indirect EA using any W Indirect EA using W8, W9 Indirect EA using W10, W11

Y SPACE

UNUSED

SFR SPACE

UNUSED

X SPACE

X SPACE

© 2006 Microchip Technology Inc. DS70118G-page 25

Page 28

dsPIC30F2010

3.2.2 DATA SPACES

The X data space is used by all instructions and supports all addressing modes. There are separate read

and write data buses. The X read data bus is the return

data path for all inst ructions that view data spac e as

combined X and Y address space. It is also the X

address space data path for the dual operand read

instructions (MAC class). The X write data bus is the

only write path to data space for all instructions.

The X data space also supp orts Mod ulo Addressin g for

all instructions, subject to addressing mode restrictions. Bit-Reversed addressing is only supported for

writes to X data space.

The Y data space is used in concert with the X data

space by the MAC class of instructions (CLR, ED,

EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths. No writes occur

across the Y bus. This class of instructions dedicates

two W register pointers, W10 and W11, to always

address Y data space, independent of X data space,

whereas W8 and W9 always address X data space.

Note that during accumulator write-back, the data

address space is con si dere d a c om bin ati on of X and Y

data spaces, so the write occurs across the X bus.

Consequently, the write can be to any address in the

entire data space.

The Y data space can only be used for the data

prefetch operation associated with the MAC class of

instructions. It also supports Modulo Addressing for

automated circular bu f fe rs. O f c ours e, all othe r ins tru ctions can access the Y dat a address sp ace through the

X data path, as part of the composite linear space.

The boundary between the X and Y data spaces is

defined as shown in Figure 3-6 and is not user programmable. Shoul d an EA poin t to d ata out side it s own

assigned address space, or to a location outside physical memory, an all-zero word/byte will be returned. For

example, although Y address space is visible by all

non-MAC instructions using any Addressing mode, an

attempt by a MAC instruction to fetch data from that

space, usin g W8 or W9 (X spac e point ers), wi ll ret urn

0x0000.

3.2.3 DATA SPACE WIDTH

The core data width is 16 bits. All internal registers are

organized as 16-bit wide words. Data space memory is

organized in byte addressable, 16-bit wide blocks.

3.2.4 DATA ALIGNMENT

To help maintain backward compatibility with PIC

MCU devices and improve data space memory usage

efficiency, the dsPIC30F instruction set supports both

word and byte operation s. Data i s aligned in dat a memory and registers as words, but all data space EAs

resolve to bytes. Data byte reads will rea d the comp lete

word, which contain s the byte, usi ng the LSb of an y EA

to determine which byte to select. The selected byte is

placed onto the LSB of the X data path (no byte

accesses are possible fro m the Y data pa th as the MAC

class of instruction can only fetch words). That is, data

memory and registers are organized as two parallel

byte wide entities with shared (word) address decode,

but separate write lines. Data byte writes only write to

the corresponding side of the array or register which

matches the byte address.

As a consequence of th is byte acce ssibility, all effective

address calculatio ns (in cl udi ng tho se ge nera ted by th e

DSP operations, which are restricted to word-sized

data) are internal ly scaled to ste p through word-ali gned

memory. For example, the core would recognize that

Post-Modified Register Indirect Addressing mode,

[Ws ++], will result in a value of Ws + 1 for byte

operations and Ws + 2 for word operations.

All word accesses m ust be al igned to an even addre ss.

Misaligned word data fetches are not supported, so

care must be taken when mixing byte and word operations, or translatin g from 8-bit MCU cod e. Should a misaligned read or write be attempted, an address error

trap will be generated. If the error occurred on a read,

the instruction underway is completed, whereas if it

occurred on a write, the ins truction wil l be execu ted but

the write will not occur. In either case, a trap will then

be executed, allow ing the syste m and /or user to exam ine the machine state prior to execution of the address

fault.

®

TABLE 3-2: EFFECT OF INVALID

MEMORY ACCESSES

Attempted Operation Data Returned

EA = an unimplemented address 0x0000

W8 or W9 used to access Y data

space in a MAC instruction

W10 or W11 used to access X

data space in a MAC instruction

All effective addresses are 16 bits wide and point to

bytes within the data space. Therefore, the data space

address range is 64 Kbytes or 32K words.

DS70118G-page 26 © 2006 Microchip Technology Inc.

0x0000

0x0000

FIGURE 3-8: DATA ALIGNMENT

15 8 7 0

0001

0003

0005

Byte 1 Byte 0

Byte 3 Byte 2

Byte 5 Byte 4

LSBMSB

0000

0002

0004

Page 29

dsPIC30F2010

All byte loads into any W register are loaded into the

LSB. The MSB is not modified.

A sign-extend (SE) instruction is provided to allow

users to translate 8-bit signed data to 16-bit signed

values. Alternatively, for 16-bit unsigned data, users

can clear the MSB of any W register by executing a

zero-extend (ZE) instruction on the appropriate

address.

Although most ins truc tio ns a r e ca p ab le of operating on

word or byte data sizes, it should be noted that some

instructions, including the DSP instructions, operate

only on words.

3.2.5 NEAR DATA SPACE

An 8 Kbyte ‘near’ data space is reserved in X address

memory space between 0x0000 and 0x1FFF, which is

directly addressable via a 13- bit absolute address fiel d

within all memory direct instructions. The remaining X

address space and all of the Y address space is

addressable indirec tly. Additionally, the w hole of X da ta

space is addressable using MOV instructions, which

support memory direct addressing with a 16-bit

address field.

3.2.6 SOFTWARE STACK

The dsPIC DSC de vice cont ain s a softwa re sta ck. W15

is used as the Stack Pointer.

The Stack Pointer always points to the first available

free word, and grows from lower addresses towards

higher addresses. It pre-decrements for stack pops,

and post-increments for stack pushes, as shown in

Figure 3-9. Note that for a PC push during any CALL

instruction, the MSB of the PC is zero-ex tende d before

the push, ensuring that the MSB is always clear.

Note: A PC push during exception processing

will concatenate the SRL register to the

MSB of the PC prior to the push.

There is a Stack Pointer Limit register (SPLIM) associated with the Stack Pointer. SPLIM is uninitialized at

Reset. As is t he case f or t h e Stack Point er, SPLIM<0>

is forced to ‘0’, because all stack operations must be

word-aligned. Whenever an EA is generated using

W15 as a sour ce or destination poi nter, the address

thus generated is compa red with the value in SPLIM. If

the contents o f the Stack Pointer (W15) and the SPLIM

register are equal and a push operation is perf ormed, a