Micro Bridge SPP2341 Schematic [ru]

SPP2341

P-Channel Enhancement Mode MOSFET

DESCRIPTION APPLICATIONS

z Power Management in Note book

The SPP2341 is the P-Channel logic enhancement mode

power field effect transistors are produced using high cell

density , DMOS trench technology.

This high density process is especially tailored to

minimize on-state resistance.

These devices are particularly suited for low voltage

application such as cellular phone and notebook

computer power management and other battery powered

circuits, and low in-line power loss are needed in a very

small outline surface mount package.

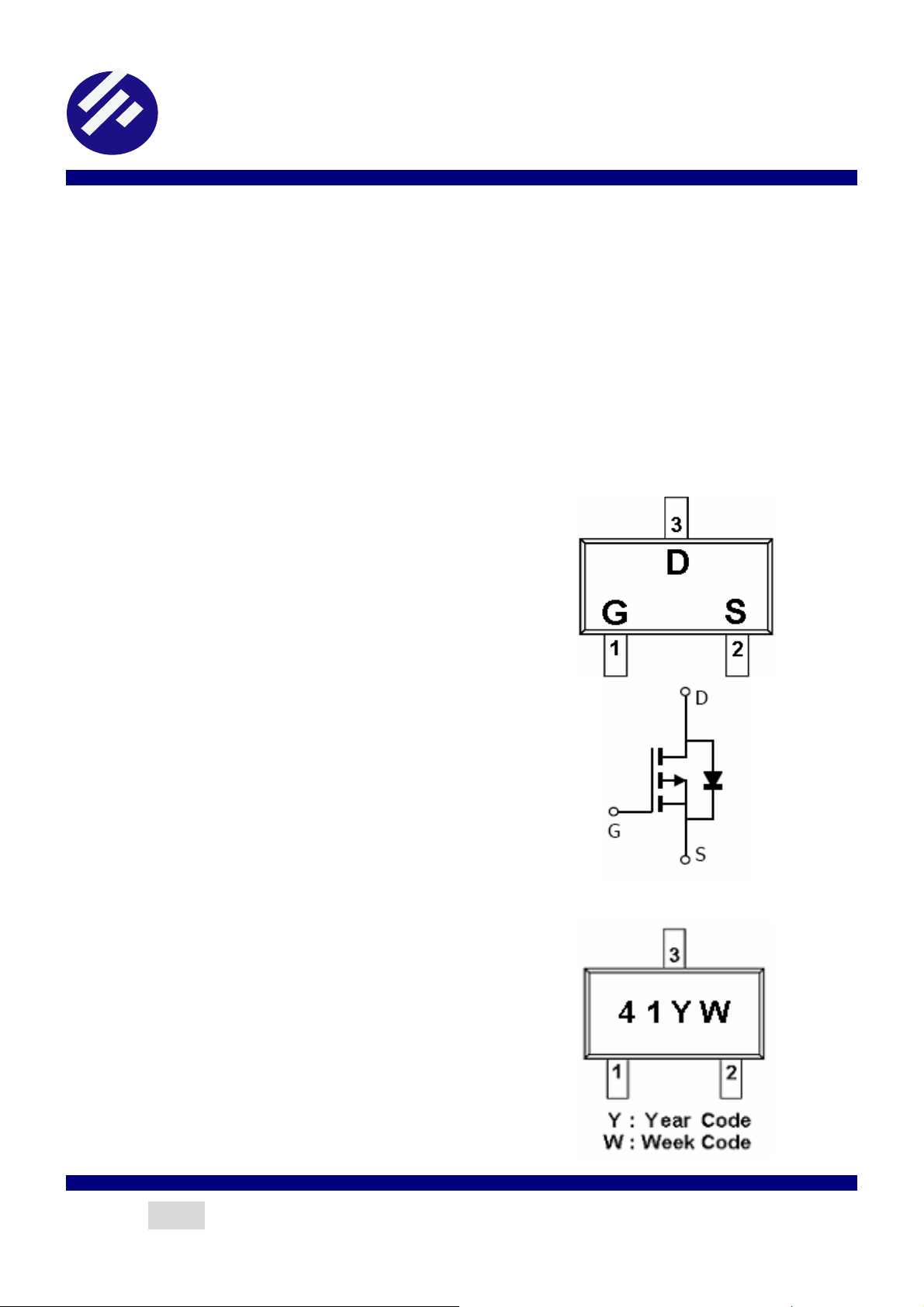

FEATURES PIN CONFIGURATION(SOT-23-3L)

-20V/-3.3 A,RDS(ON)= 45mΩ@VGS=-4.5V

-20V/-2.8 A,RDS(ON)= 55mΩ@VGS=-2.5V

-20V/-2.3 A,RDS(ON)= 65mΩ@VGS=-1.8V

Super high density cell design for extremely low

DS (ON)

R

Exceptional on-resistance and maximum DC

current capability

SOT-23-3L package design

z Portable Equipment

z Battery Powered System

z DC/DC Converter

z Load Switch

z DSC

z LCD Display inverter

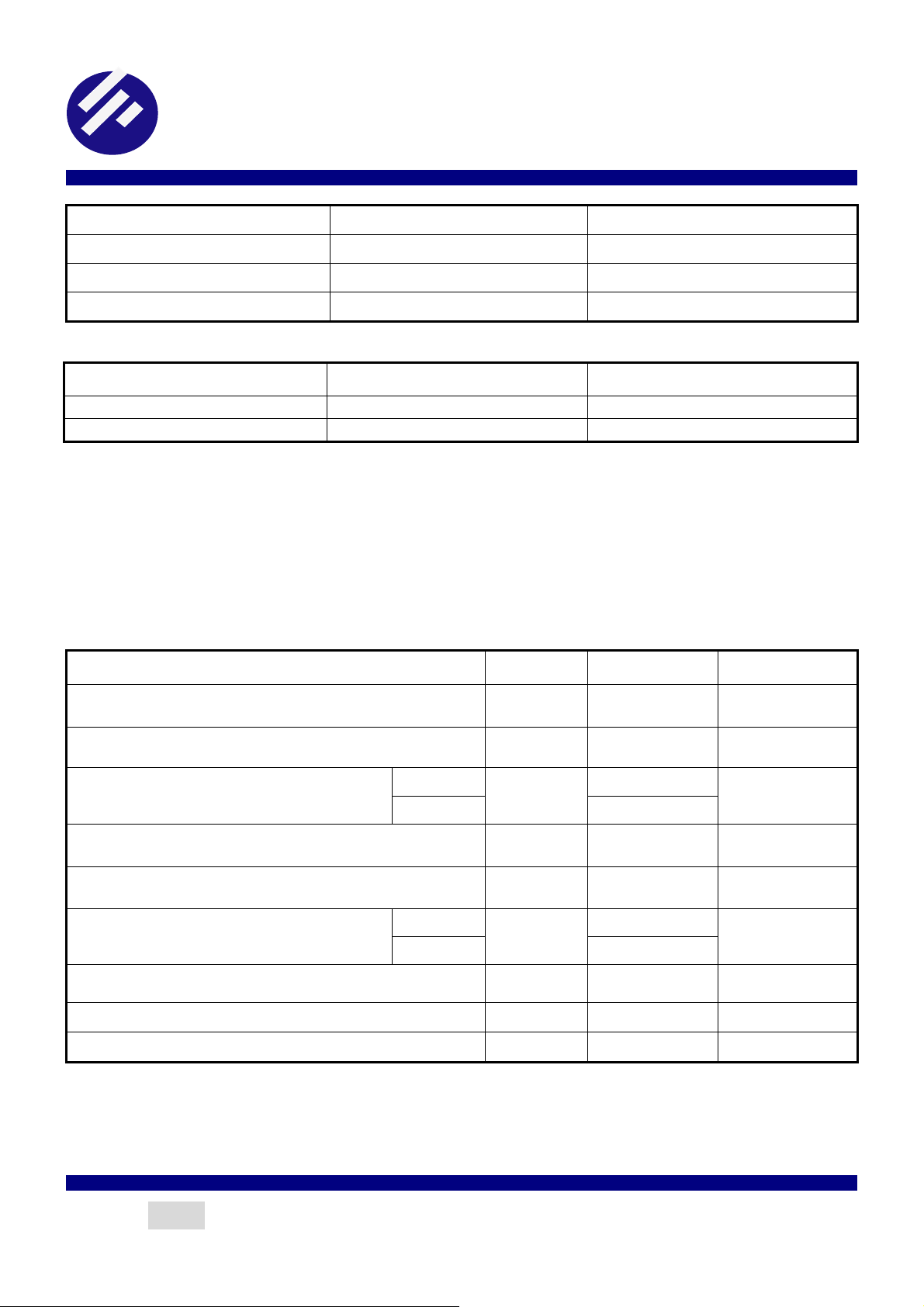

PART MARKING

2008/05/05 Ver.3 Page 1

SPP2341

P-Channel Enhancement Mode MOSFET

PIN DESCRIPTION

Pin Symbol Description

1 G Gate

2 S Source

3 D Drain

ORDERING INFORMATION

Part Number Package Part Marking

SPP2341S23RG SOT-23-3L 41YW

SPP2341S23RGB SOT-23-3L 41YW

※ Week Code : A ~ Z( 1 ~ 26 ) ; a ~ z( 27 ~ 52 )

※ SPP2341S23RG : Tape Reel ; Pb – Free

※ SPP2341S23RGB : Tape Reel ; Pb – Free ; Halogen – Free

※

ABSOULTE MAXIMUM RATINGS

(T

A=25 Unless otherwise℃ noted)

Parameter Symbol Typical Unit

Drain-Source Voltage VDSS -20 V

Gate –Source Voltage VGSS ±12 V

Continuous Drain Current(TJ=150 )℃

Pulsed Drain Current IDM -12 A

Continuous Source Current(Diode Conduction) IS -1.0 A

Power Dissipation

Operating Junction Temperature TJ -55/150 ℃

Storage Temperature Range TSTG -55/150 ℃

Thermal Resistance-Junction to Ambient RθJA 140 /W℃

TA=25℃ -4.0

T

A=70℃

TA=25℃ 1.25

T

A=70℃

D

I

D

P

-2.8

0.8

A

W

2008/05/05 Ver.3 Page 2

SPP2341

P-Channel Enhancement Mode MOSFET

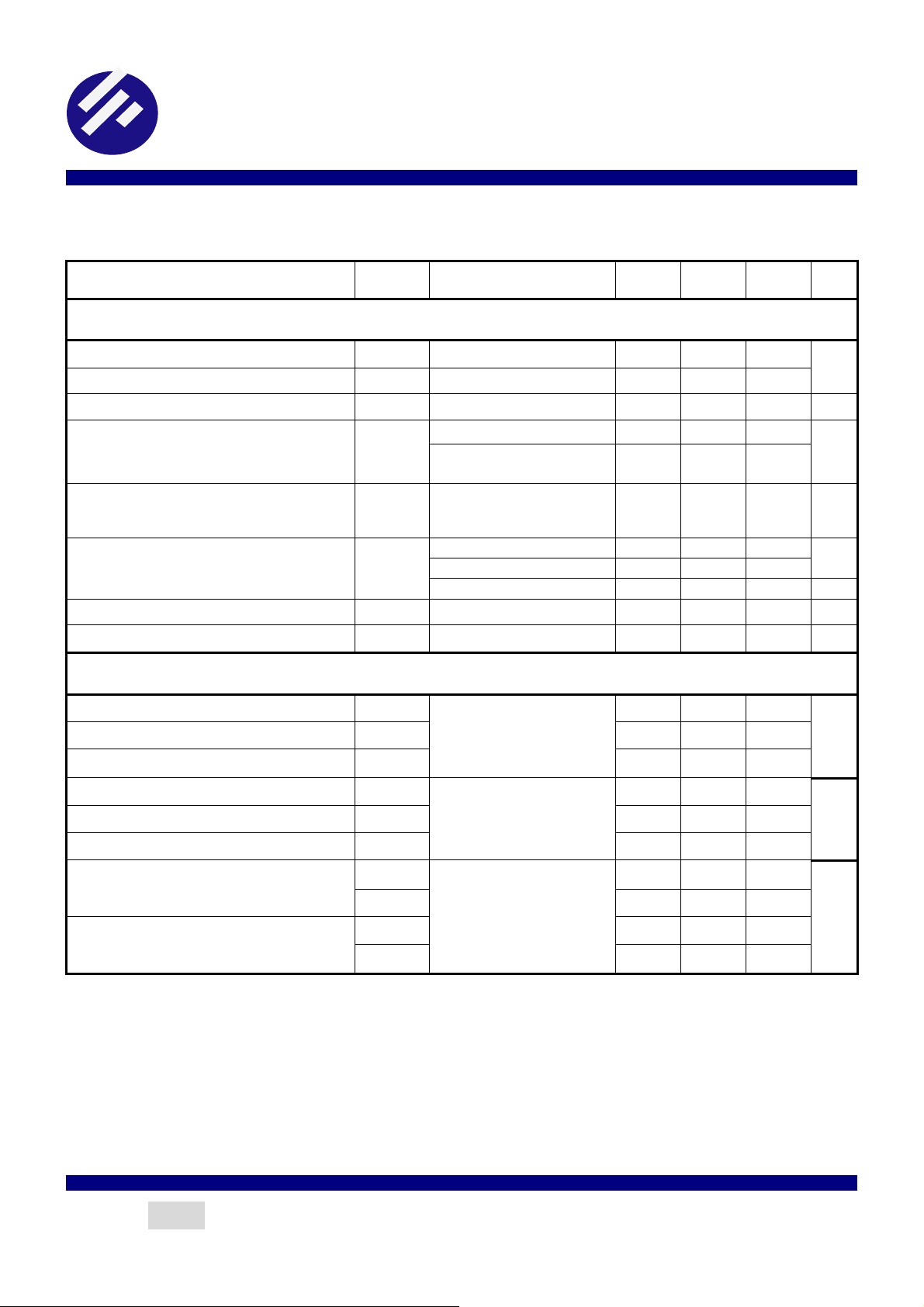

ELECTRICAL CHARACTERISTICS

(T

A=25 U℃ nless otherwise noted)

Parameter Symbol Conditions Min. Typ Max. Unit

Static

Drain-Source Breakdown Voltage V(BR)DSS VGS=0V,ID=-250uA -20

Gate Threshold Voltage VGS(th) VDS=VGS,ID=-250uA -0.35 -0.9

Gate Leakage Current IGSS VDS=0V,VGS=±12V ±100 nA

VDS=-20V,VGS=0V -1

Zero Gate Voltage Drain Current IDSS

On-State Drain Current ID(on)

Drain-Source On-Resistance RDS(on)

Forward Transconductance gfs VDS=-5.0V,ID=-3.3A 3 S

Diode Forward Voltage VSD IS=-1.6A,VGS=0V -0.8 -1.2 V

Dynamic

Total Gate Charge Qg 8 13

Gate-Source Charge Qgs 1.2

Gate-Drain Charge Qgd

Input Capacitance Ciss 700

Output Capacitance Coss 160

Reverse Transfer Capacitance Crss

V

DS=-20V,VGS=0V

T

J=55℃

DS≦-5V,VGS=-4.5V

V

VGS=- 4.5V,ID=-3.3A 0.036 0.045

VGS=- 2.5V,ID=-2.8A 0.045 0.055

VGS=- 1.8V,ID=-2.3A 0.055 0.065

DS=-6V,VGS=-4.5V

V

I

D≡-3.3A

V

DS=-6V,VGS=0V

f=1MHz

-10

-6 A

2.2

120

V

uA

Ω

nC

pF

Turn-On Time

Turn-Off Time

2008/05/05 Ver.3 Page 3

td(on) 15 25

V

r 35 55

t

td(off) 60 90

f

t

DD=-6V,RL=6Ω

I

D≡-1.0A,VGEN=-4.5V

R

G=6Ω

ns

40 60

Loading...

Loading...