MICREL SY89801A Datasheet

HP PA-8000

CLOCK SOURCE

ClockWorks™

PRELIMINARY

SY89801A

FEATURES

■ 3.3V, –1.9V power suppies

■ Differential LVPECL clock input

■ Differential HSTL/LVPECL outputs

■ Compatible with HP PA-8000 microprocessors

■ Low-jitter source for all PA-8000 required timing

signals

■ Available in 44-pin MQUAD package

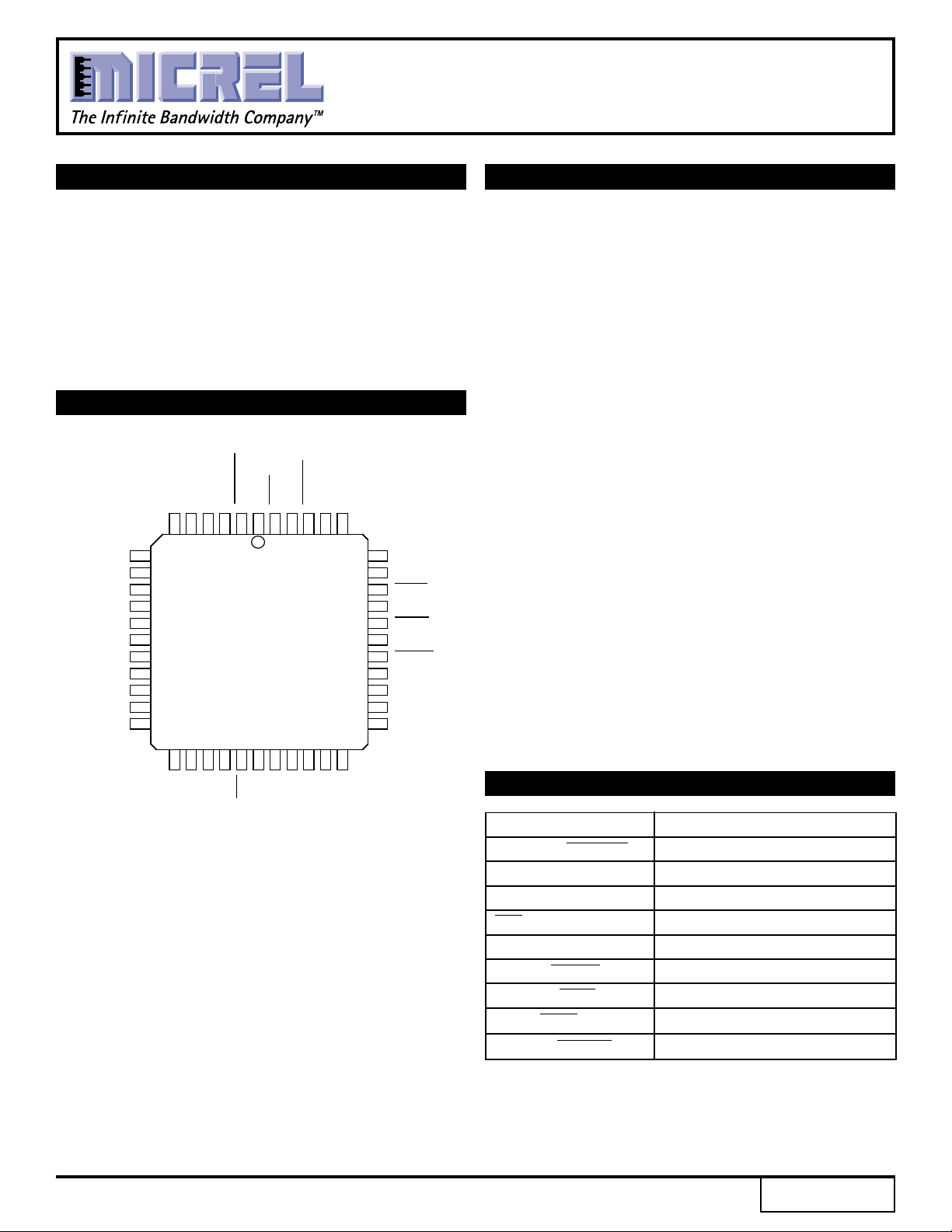

PIN CONFIGURATION

RCLK

RCLKLV

RCLKLV

VEE

39

38

37

36

35

34

33

32

31

30

29

VEE

PCLK1

PCLK1

PCLK2

PCLK2

VCC

USYNC

USYNC

NC

NC

VCC

VEEA

NC

NC

FILP

FILN

VCCA

NC

NC

NC

NC

NC

7

8

9

10

11

12

13

14

15

16

17

VEENCNC

REF_CLK

RCLK

REF_CLK

VCC

1

23456 4443424140

TOP VIEW

MQUAD

M44-1

232221201918 24 25 26 27 28

DESCRIPTION

Micrel-Synergy's SY89801A PLL based clock generator

provides, in a single chip, all the necessary clocks for HewlettPackard's PA-8000 Microprocessor.

Utilizing Micrel-Synergy's advanced PLL technology, the

SY89801A accepts a Positive-ECL (PECL) reference clock

input at 100MHz-132MHz, and provides precisely aligned,

ultra-low-jitter ratios of frequencies necessary for the operation

of the processor. In addition, the SY89801A provides the

"USYNC" synchronizing signals as required by the PA-8000.

The frequency ratios are 1:1, 4:3, 3:2, 5:3 and 2:1.

To facilitate direct interfacing to the PA-8000, the SY89801A

operates across +3.3 volt and -1.9 volt supplies. The processor

clock (PCLK), runway clock (RCLK) , and USYNC outputs are

HSTL-compatible. Additionally, there is a PECL-compatible

runway clock output (RCLKLV). The SY89801A requires only

a simple external series-RC loop filter.

Coupling Micrel-Synergy's advanced PLL technology with

our proprietary ASSET bipolar process has produced a

Timing Generator IC which meets the stringent requirements

of the PA-8000 µP, while setting a new standard for

performance and flexibility.

NCNCNC

VCC

RST

VEE

NC

FSEL1

FSEL0

VCC

FSEL2

PIN NAMES

Pin Function

REF_CLK, REF_CLK Differential Input Ref. Clock

FILP, FILN Filter Pins (Positive & Negative)

VCCA, VEEA Analog VCC, VEE

RST Master Reset

FSEL2-0 LVPECL Frequency Select Pins

USYNC, USYNC Diff. HSTL Sync Signal for PA-8000

PCLK1-2, PCLK1-2 Diff. HSTL Processor Clock Signal

RCLK, RCLK Diff. HSTL Runway Clock Signal

RCLKLV, RCLKLV Diff. LVPECL Clock Signal

Rev.: E Amendment: /0

1

Issue Date: November 1998

Micrel

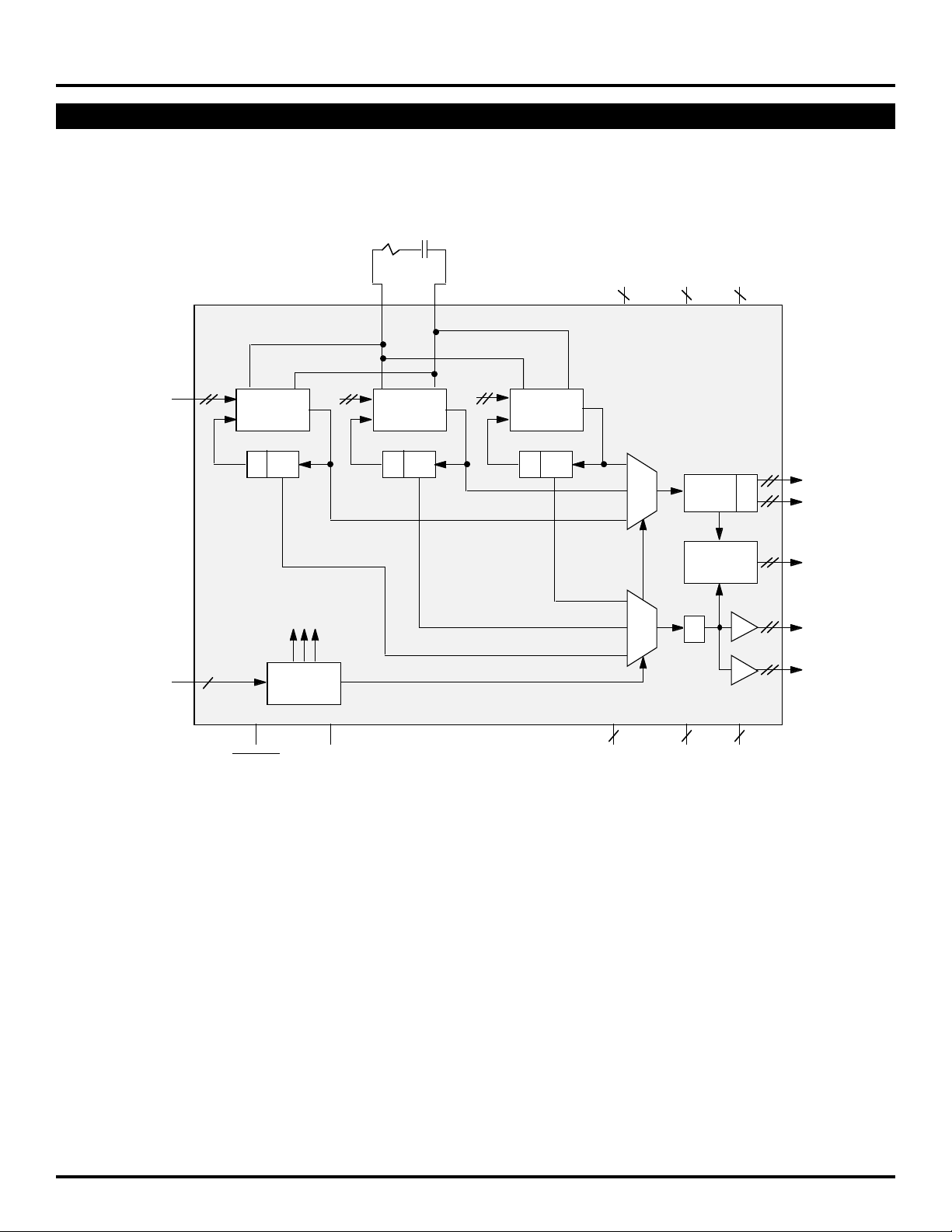

BLOCK DIAGRAM

ClockWorks™

PRELIMINARY

SY89801A

LOOP FILTER

AVCC VCCOVCC

232

REFCLK

(100-132MHz)

(PECL)

FSEL

(PECL)

3

LF VCO

(600-800)

f/2÷ 3

RESET

(PECL)

VCO

ENAB

DECODE

TEST

(PECL)

MF VCO

(800-1060)

f/2÷ 4 f/2÷ 5

HF VCO

(1000-1320)

÷

2/ 3/ 4/ 5

f/2

f/2

SYNC

LOGIC

223

GND DVEE AVEE

PCLK1

(HSTL)

PCLK2

(HSTL)

USYNC

(HSTL)

RCLK

(HSTL)

RCLKLV

(PECL)

2

Loading...

Loading...