MICREL SY89420V Datasheet

5V/3.3V DUAL

A

A

PHASE LOCKED LOOP

ClockWorks™

SY89420V

FEATURES

■ 3.3V and 5V power supply options

■ 1.12GHz maximum VCO frequency

■ 30MHz to 560MHz reference input operating

frequency

■ Frequency doubler mode

■ Low jitter design

■ PECL differential outputs

■ PECL and TTL reference voltages available

■ External loop filter optimizes performance/cost

■ Available in 28-pin PLCC package

APPLICATIONS

■ Workstations

■ Advanced communications

■ High-end consumer

■ High-performance computing

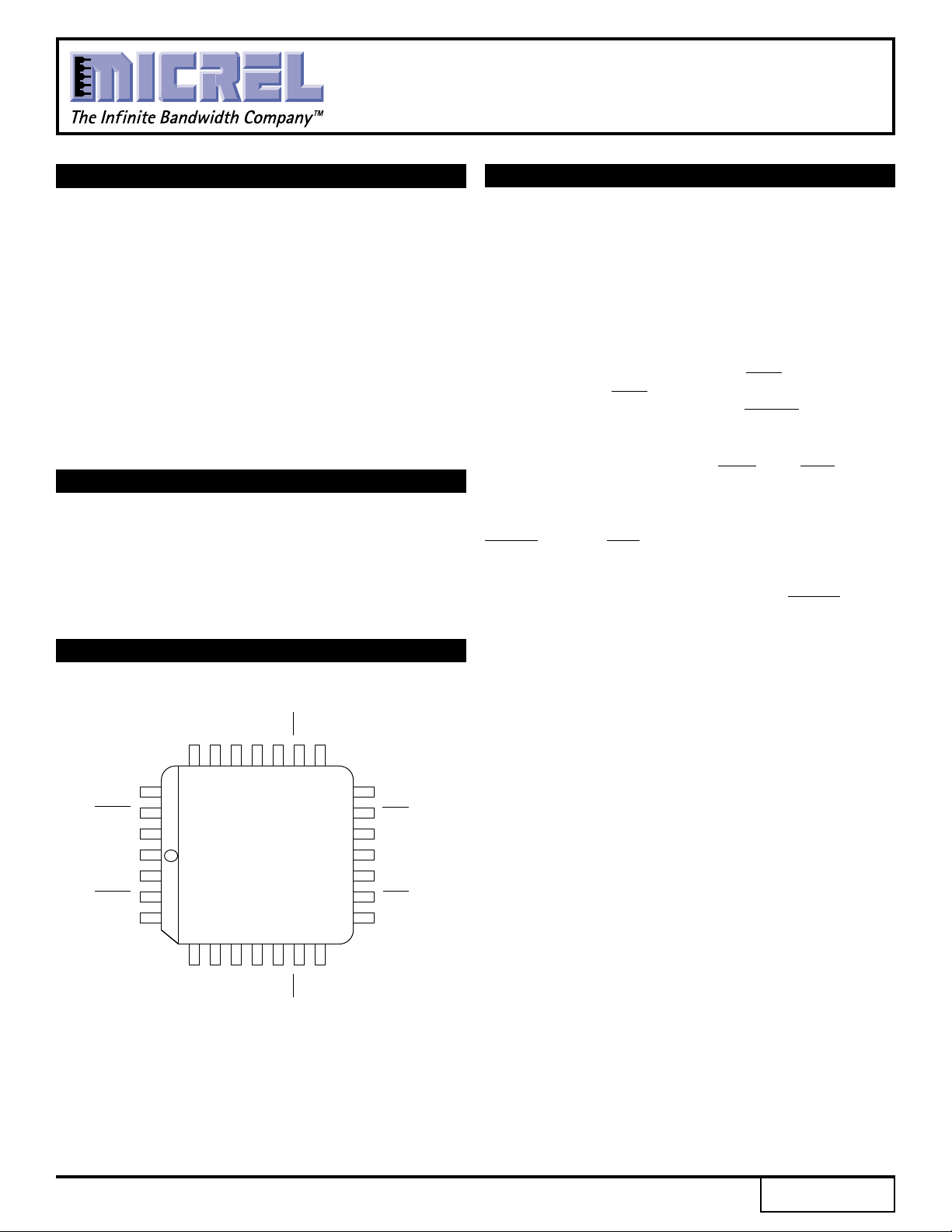

PIN CONFIGURATION

S3B

FINB

FINB

18

17

16

15

14

13

12

S4B

RINB

RINB

V

EE

RINA

RINA

V

BB

V

CCOB

FOUTB

FOUTB

V

CC

FOUT

FOUT

V

CCOA

S1B

F1B

F2B

S2B

24 23 22 21 20 19

25

26

27

28

1

2

3

4

TOP VIEW

PLCC

J28-1

567891011

DESCRIPTION

The SY89420V device consists of two identical, low

jitter, digital Phase Locked Loops based on Micrel-Synergy's

differential PLL technology. Each of the PLLs (PLLA and

PLLB) is capable of operating in the 30MHz to 560MHz

input reference frequency range independently of the other

and is configurable separately. The PLLs can be configured

to be matched in all regards, or can be configured so that

PLLB is used as a frequency doubler, while PLLA is used

to regenerate the undoubled frequency.

Two reference inputs (RINX and RINX), two feedback

inputs (FINX and FINX), two filter pins (F1X and F2X) and

two differential outputs (FOUTX and FOUTX) are provided

for each of the two PLLs. The reference and feedback

inputs can be used as either differential or single-ended

inputs. In single-ended mode RINX and FINX can be

connected to either V

VTH for normal TTL levels.

Feedback for the loops is realized by connecting FOUTX,

FOUTX to FINX, FINX by means of external circuitry. This

allows the user the flexibility of inserting additional circuitry

off-chip in the feedback paths, such as a divider. Pulldown

resistors are required for the FOUTX and FOUTX pins.

Use of a phase-frequency detector results in excellent

PLL locking and tracking characteristics. Error correction

voltages are generated by the detector if either phase or

frequency deviations occur. The VCO has a frequency

range covering more than a 2:1 ratio from 480MHz to

1120MHz.

Select pins S1X and S2X are used to program the N

dividers for optimum VCO operation, in other words with

the VCO in the center of its range. Additional select pins,

S3B and S4B, are provided for PLLB. When both S3B and

S4B are low, PLLB is identical to PLLA. When S3B is high,

NB can be set to 1, 10, 18, or 20. When S4B is high, the

frequency doubler option is enabled (P = 2). All Select pins

are TTL compatible.

BB for normal 100K PECL levels or

TH

F1A

F2A

V

FINA

FINA

Rev.: K Amendment: /0

1

Issue Date: May 2000

S1A

S2A

Micrel

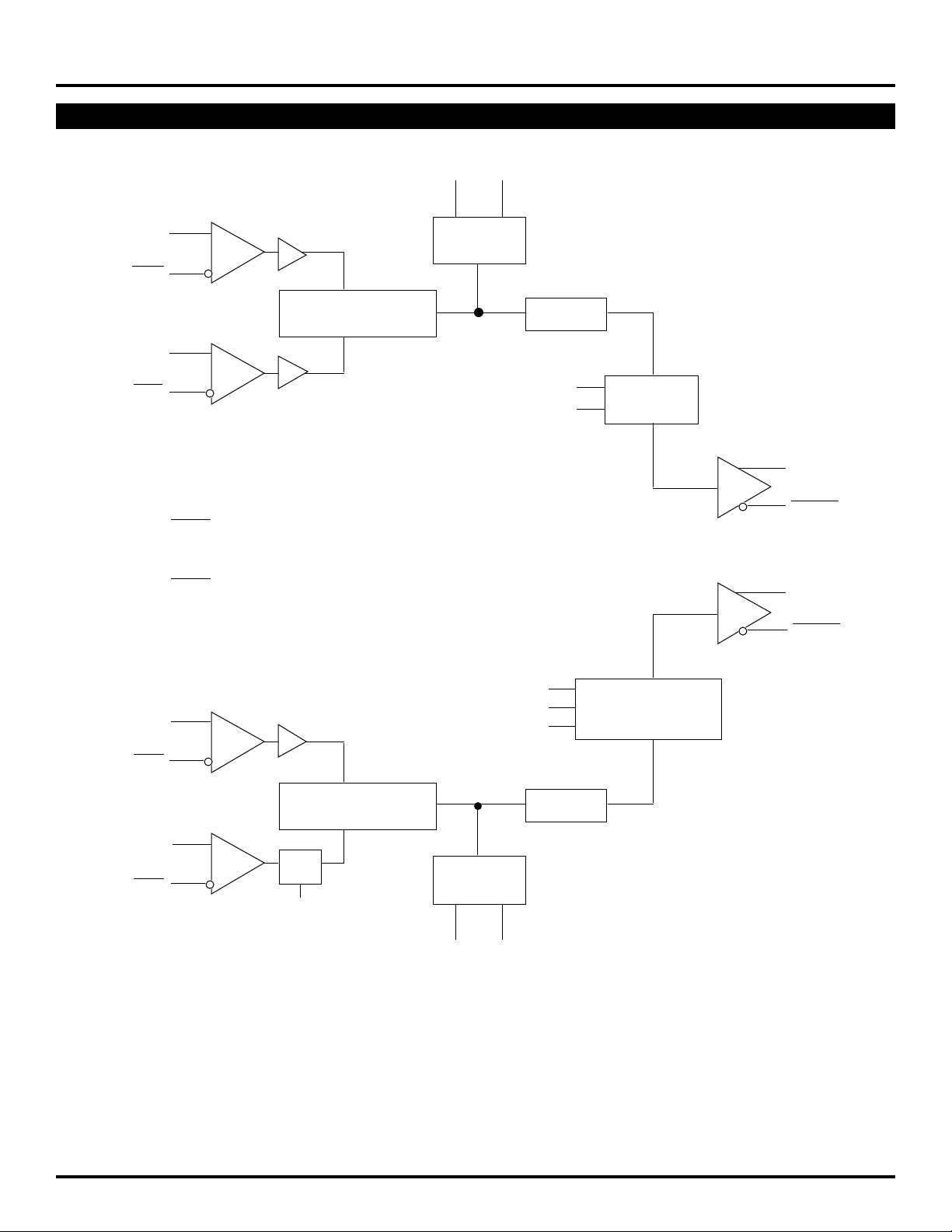

BLOCK DIAGRAM

ClockWorks™

SY89420V

F1A F2A

RINA

RINA

FINA

FINA

V

BB

V

TH

D

PHASE-FREQUENCY

DETECTOR

D

LOOP

FILTER

VCO

S1A

S2A

÷ N

A

(2, 4, 8, 16)

FOUTA

FOUTA

FOUTB

FOUTB

RINB

RINB

FINB

FINB

D

PHASE-FREQUENCY

DETECTOR

÷

P

(1, 2)

S4B

LOOP

FILTER

F1B F2B

S1B

S2B

S3B

÷ N

(1,2,4,8,10,12,16,20)

VCO

B

2

Micrel

ClockWorks™

SY89420V

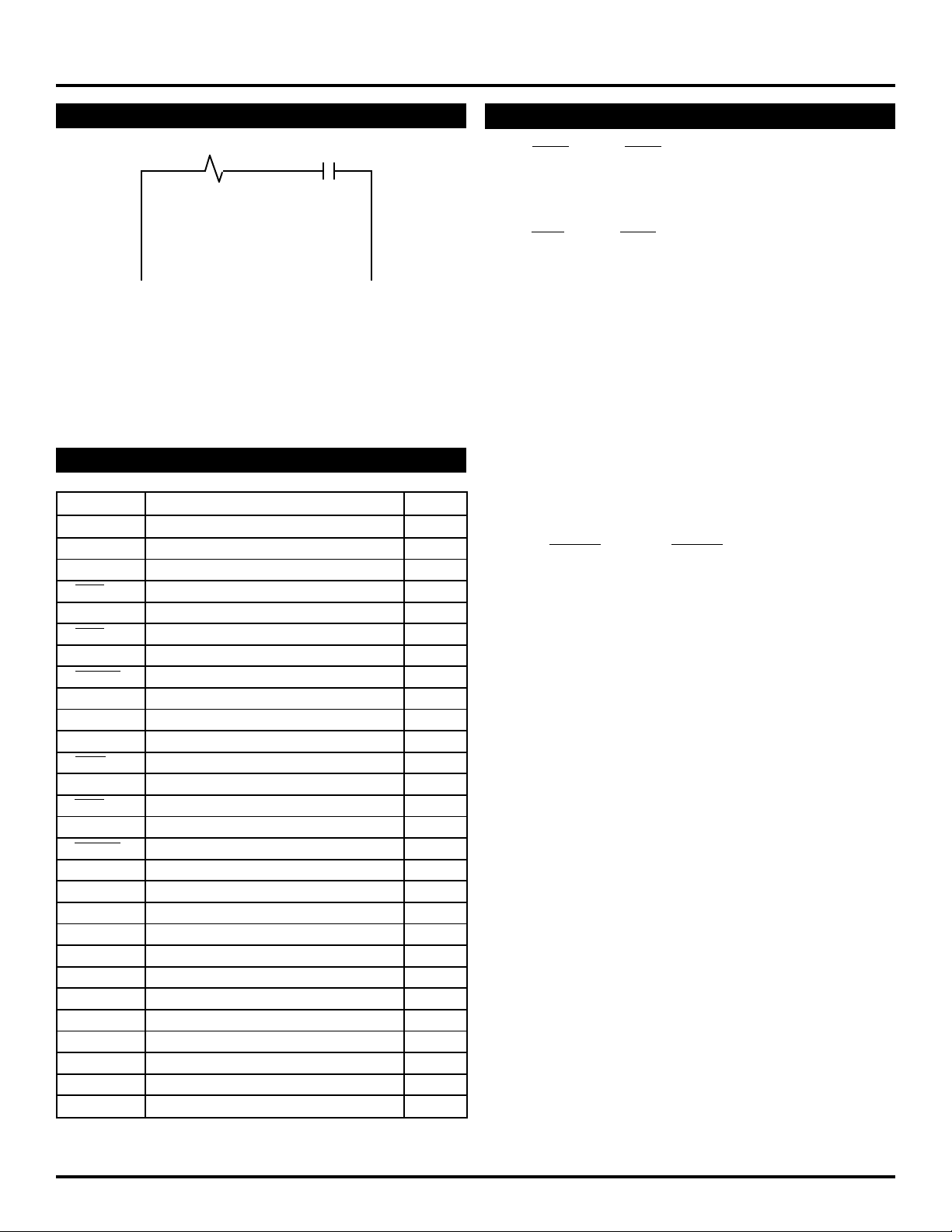

LOOP FILTER COMPONENT SELECTION

R

F1X

C = 1.0µF ±10% (X7R dielectric)

R = 560Ω ±10%

C

F2X

PIN NAMES

Pin Function I/O

F1A Filter Pin 1A I/O

F2A Filter Pin 2A I/O

RINA Reference Input A I

RINA Inverted Reference Input A I

FINA Feedback Input A I

FINA Inverted Feedback Input A I

FOUTA Frequency Output A O

FOUTA Inverted Frequency Output A O

F1B Filter Pin 1B I/O

F2B Filter Pin 2B I/O

RINB Reference Input B I

RINB Inverted Reference Input B I

FINB Feedback Input B I

FINB Inverted Feedback Input B I

FOUTB Frequency Output B O

FOUTB Inverted Frequency Output B O

VCC VCC —

VCCOA Output A VCC —

VCCOB Output B VCC —

VEE VEE (0V) —

VBB PECL Threshold Voltage O

VTH TTL Threshold Voltage O

S1A Select Input 1A (TTL) I

S2A Select Input 2A (TTL) I

S1B Select Input 1B (TTL) I

S2B Select Input 2B (TTL) I

S3B Select Input 3B (TTL) I

S4B Select Input 4B (TTL) I

PIN DESCRIPTION

RINA, RINA, RINB, RINB

Reference frequency inputs for loop A and B. These are

differential signal pairs and may be driven differentially or

single-ended.

FINA, FINA, FINB, FINB

Feedback frequency inputs for loop A and B. These are

differential signal pairs and may be driven differentially or

single-ended.

V

BB, VTH

These are the reference voltages for use as bias for the

frequency inputs. The references are generated on-chip. VBB

is PECL compatible, while VTH is TTL compatible.

F1A, F2A, F1B, F2B

These pins are connection points for the loop filters, which are

to be provided off-chip. F1X is the high impedance side, F2X

is the reference side. The loop filter should be a first order, low

pass with a DC block. The difference voltage on these pins will

be a DC level, which is controlled by the loop feedback and

determined by the required VCO frequency.

FOUTA, FOUTA, FOUTB, FOUTB

Frequency outputs for the loops. These are differential,

positive referenced, emitter-follower signals and must be

terminated off-chip. Termination in 50 ohms is recommended.

S1A, S2A, S1B, S2B, S3B, S4B

These inputs are used to select the configuration for PLLA and

PLLB. They are compatible with standard TTL signal levels.

See the Frequency Selection Table for details of the logic.

VCC

This is the positive supply for the entire chip excluding output

buffers. It should be decoupled and present a very low

impedance in order to assure low-jitter operation.

VCCOA, VCCOB

These are the positive supplies for the output buffers. They

are constrained to be equal to the value of VCC. They should

be decoupled and present a very low impedance in order to

assure low-jitter operation.

VEE

This pin is the negative supply for the chip and is normally

connected to ground (0V).

3

Loading...

Loading...