MICREL SY10H842L, SY100H842L Datasheet

3.3V SINGLE SUPPLY

QUAD PECL-TO-TTL

OUTPUT ENABLE

ClockWorks™

PRELIMINARY

SY10H842L

SY100H842L

FEATURES

■ 3.3V power supply

■ Translates positive ECL-to-TTL (PECL-to-TTL)

■ 300ps pin-to-pin skew

■ 500ps part-to-part skew

■ Differential internal design for increased noise

immunity and stable threshold inputs

■ VBB reference output

■ Single supply

■ Enable input

■ Extra TTL and ECL power/ground pins to reduce

cross-talk/noise

■ High drive capability: 24mA each output

■ Fully compatible with industry standard 10K, 100K

I/O levels

■ Available in 16-pin SOIC package

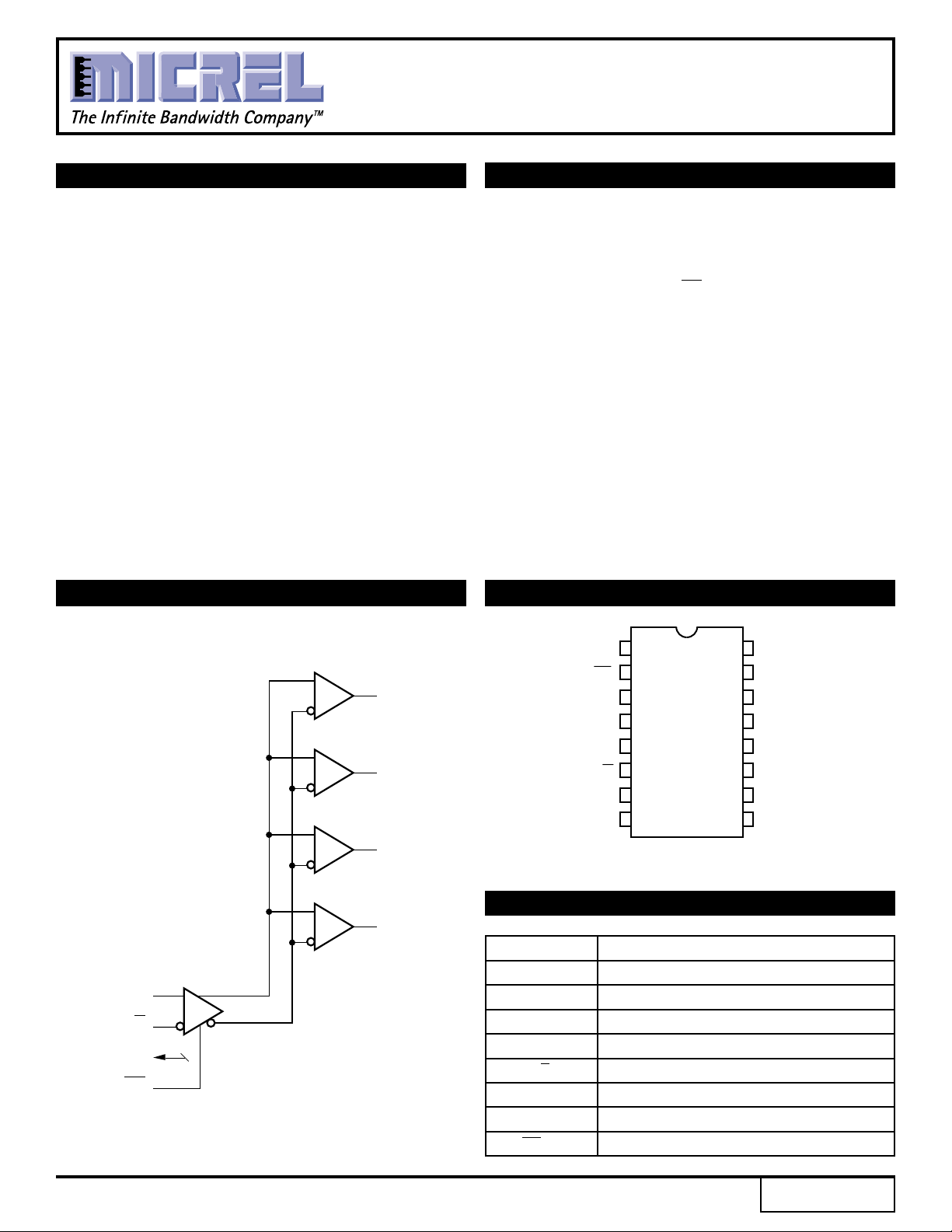

BLOCK DIAGRAM

DESCRIPTION

The SY10/100H842L are single supply, low skew

translating 1:4 clock drivers.

The devices feature a 24mA TTL output stage, with

AC performance specified into a 20pF load capacitance.

A HIGH on the enable pin (EN) forces all outputs LOW.

As frequencies increase to 40MHz and above, precise

timing and shaping of clock signals becomes extremely

important. The H842 solves several clock distribution

problems such as minimizing skew 300ps), maximizing

clock fanout (24mA drive), and precise duty cycle control

through a proprietary differential internal design.

The 10K version is compatible with 10KH ECL logic

levels. The 100K version is compatible with 100K levels.

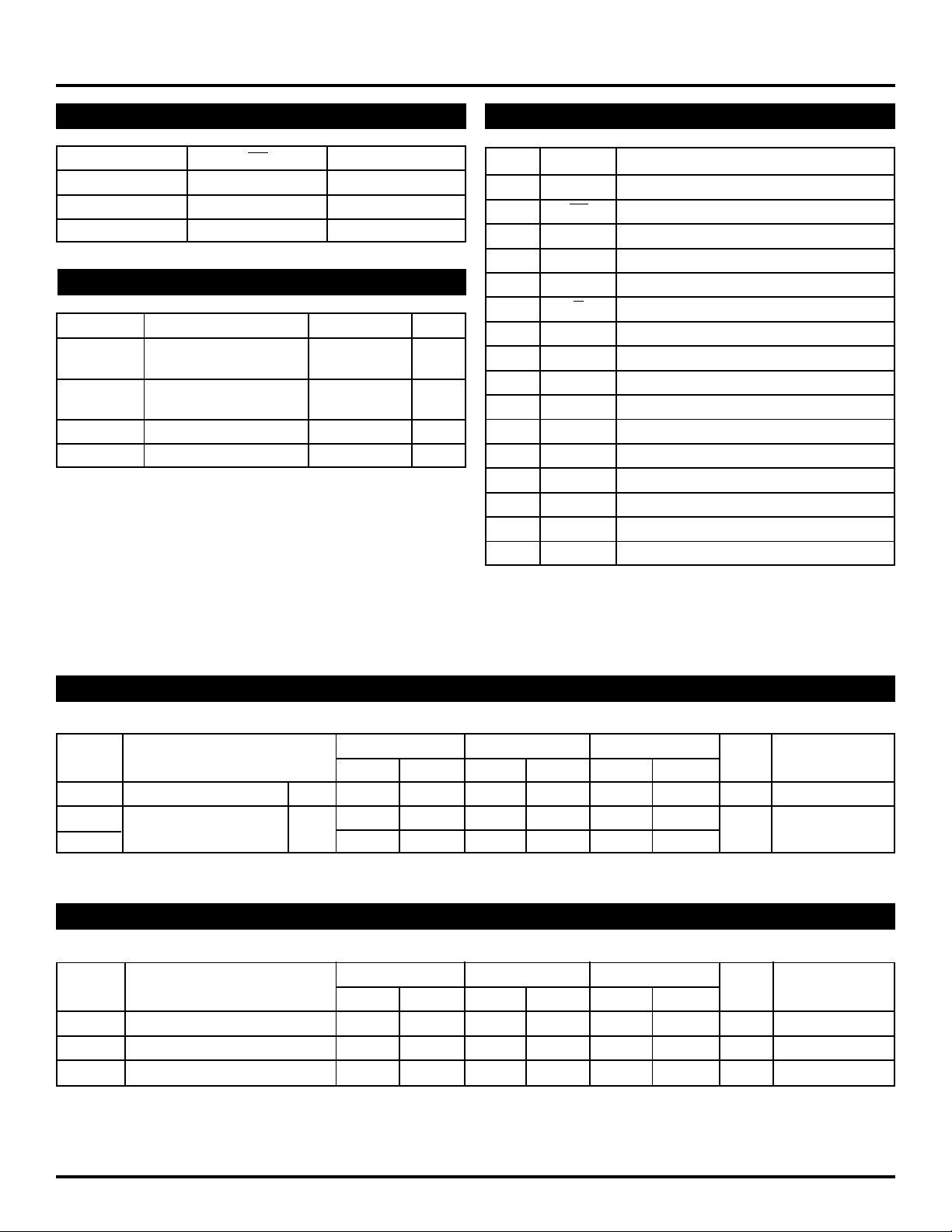

PIN CONFIGURATION

V

D

D

BB

EN

ECL Input

TTL Outputs

116

G

T

2

EN

Q

0

Q

1

V

Q

2

314

E

G

4

E

V

D

D

BB

T

G

SOIC

Z16-1

512

6

710

8

15

13

11

Q

3

T

G

Q

2

V

T

T

V

1

Q

G

T

9

Q

0

PIN NAMES

Q

3

Pin Function

GT TTL Ground (0V)

VT TTL VCC (+3.3V)

VE ECL VCC (+3.3V)

GE ECL Ground (0V)

D, D Signal Input (PECL)

VBB VBB Reference Output (PECL)

Q0 - Q3 Signal Outputs (TTL)

EN Enable Input (PECL)

Rev.: C Amendment: /1

1

Issue Date: August, 1999

Micrel

ClockWorks™

PRELIMINARY

SY10H842L

SY100H842L

TRUTH TABLE

DEN Q

LL L

HL H

XH L

ABSOLUTE MAXIMUM RATINGS

Symbol Rating Value Unit

V

E (ECL) Power Supply –0.5 to +7.0 V

VT (TTL) Voltage –0.5 to +7.0

V

I (ECL) Input Voltage 0.0 to VEE V

VOUT (TTL) 0.0 to VT

Tstore Storage Temperature –65 to +150 ˚C

T

A Operating Temperature 0 to +85 ˚C

NOTE:

1. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS

are exceeded. This is a stress rating only and functional operation is not

implied at conditions other than those detailed in the operational sections

of this data sheet. Exposure to ABSOLUTE MAXIMUM RATlNG conditions

for extended periods may affect device reliability.

(1)

PIN DESCRIPTION

Pin Symbol Description

1GT TTL Ground (0V)

2 EN Enable Input (PECL)

3GE ECL Ground (0V)

4VE ECL VCC (+3.3V)

5 D ECL Signal Input (Non-inverting)

6 D ECL Signal Input (Inverting)

7VBB VBB Reference Output (PECL)

8GT TTL Ground (0V)

9Q0 Signal Output (TTL)

10 GT TTL Ground (0V)

11 Q1 Signal Output (TTL)

12 VT TTL VCC (+3.3V)

13 VT TTL VCC (+3.3V)

14 Q2 Signal Output (TTL)

15 GT TTL Ground (0V)

16 Q

3 Signal Output (TTL)

DC CHARACTERISTICS

VT = VE = +3.0V to +3.6V

TA = 0°CTA = +25°CTA = +85°C

Symbol Parameter Min. Max. Min. Max. Min. Max. Unit Condition

IEE Power Supply Current ECL — 35 — 35 — 35 mA VE Pin

CCH Power Supply Current TTL — 20 — 20 — 20 mA Total all VT pins

I

CCL —25 — 25— 25

I

TTL DC ELECTRICAL CHARACTERISTICS

VT = VE = +3.0V to +3.6V

TA = 0°CTA = +25°CTA = +85°C

Symbol Parameter Min. Max. Min. Max. Min. Max. Unit Condition

VOH Output HIGH Voltage 2.0 — 2.0 — 2.0 — V IOH = –3.0mA

VOL Output LOW Voltage — 0.5 — 0.5 — 0.5 V IOL = 24mA

I

OS Output Short Circuit Current –80 — –80 — –80 — mA VOUT = 0V

2

Loading...

Loading...