MICREL SY10H600, SY100H600 Datasheet

9-BIT TTL-TO-ECL WITH

TTL, ECL ENABLE

SY10H600

SY100H600

FEATURES

■ 9-bit ideal for byte-parity applications

■ Flow-through configuration

■ Extra TTL and ECL power/ground pins to minimize

switching noise

■ ECL and TTL enable inputs

■ Dual supply

■ 3.5ns max. D to Q

■ PNP TTL inputs for low loading

■ Choice of ECL compatibility: MECL 10KH (10Hxxx)

or 100K (100Hxxx)

■ Fully compatible with Motorola MC10H/100H600

■ Available in 28-pin PLCC package

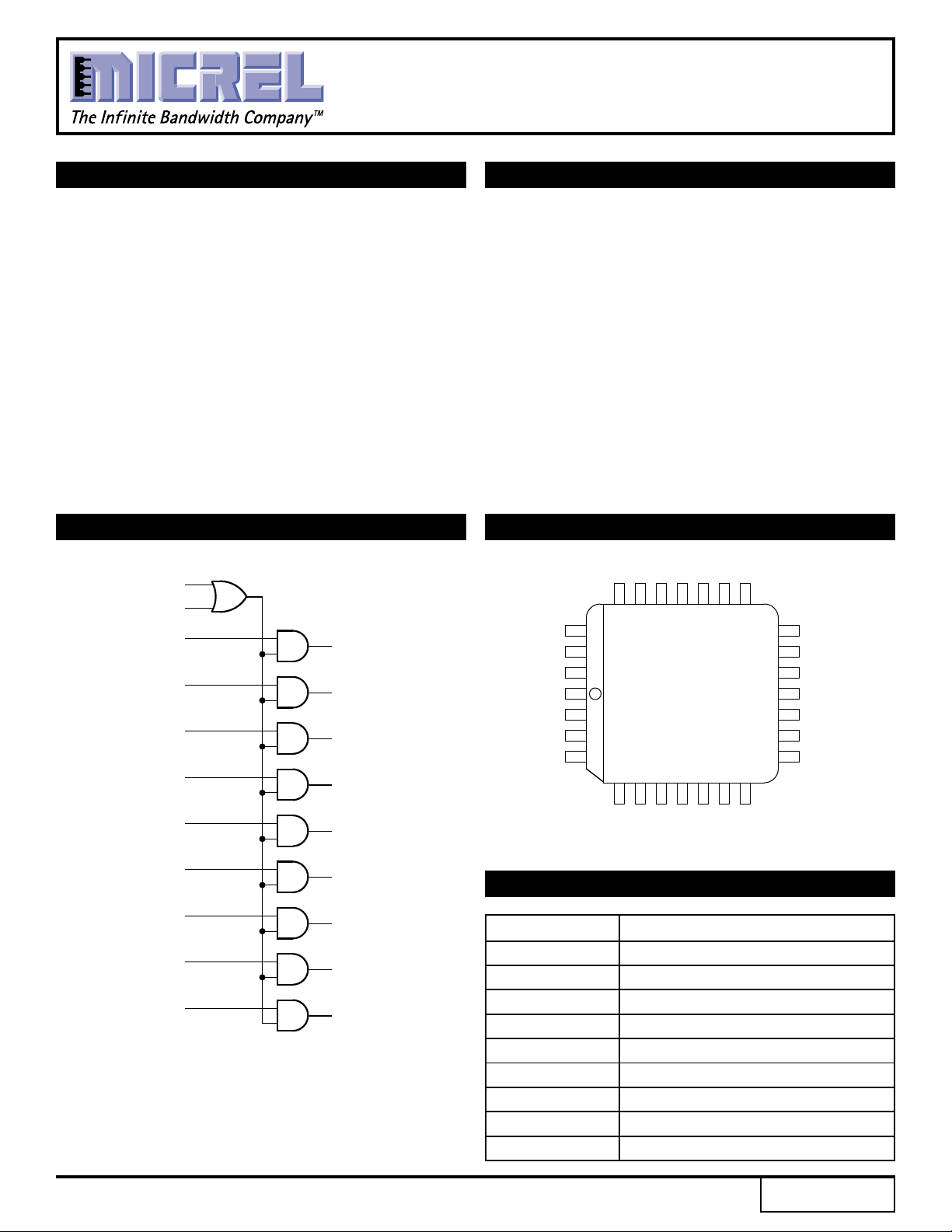

BLOCK DIAGRAM

ENECL

ENTTL

D

0

D

1

D

2

D

3

Q

0

Q

1

Q

2

Q

3

DESCRIPTION

The SY10/100H600 are 9-bit, dual supply TTL-to-ECL

translators. Devices in the Micrel-Synergy 9-bit translator

series utilize the 28-lead PLCC for optimal power pinning,

signal flow-through and electrical performance.

The H600 features both ECL and TTL logic enable

controls for maximum flexibility.

The 10H version is compatible with MECL 10KH ECL

logic levels. The 100H version is compatible with 100K

levels.

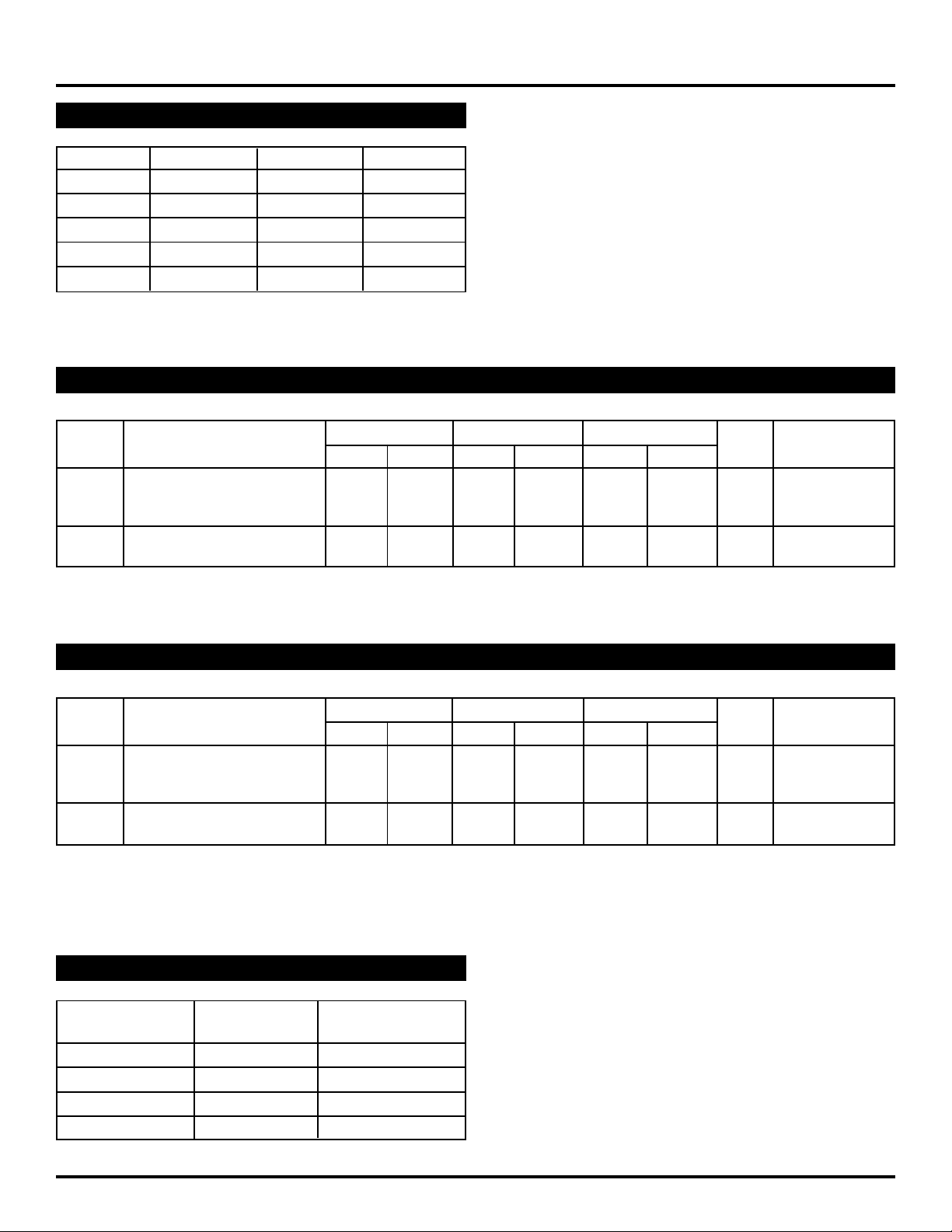

PIN CONFIGURATION

D1

D0

18

17

16

15

14

13

12

0

Q

Q1

VCCE

VCCO

Q2

VCCO

Q3

D6

D7

D8

GND

ENTTL

NC

ENECL

D4

VCCTD3D2

D5

25

24 23 22 21 20 19

26

27

28

1

2

3

4

TOP VIEW

PLCC

567891011

TTL

Q8

Q7

Q6

Q5

D

4

D

5

D

6

D

7

D

8

Q

4

Q

5

Q

6

Q

7

Q

8

ECL

VCCO

PIN NAMES

Pin Function

GND TTL Ground (0V)

VCCE ECL VCC (0V)

VCCO ECL VCC (0V) — Outputs

VCCT TTL Supply (+5.0V)

VEE ECL Supply (–5.2/–4.5V)

D0–D8 Data Inputs (TTL)

Q0–Q8 Data Outputs (ECL)

ENECL Enable Control (ECL)

ENTTL Enable Control (TTL)

1

VEE

Q4

Rev.: D Amendment: /0

Issue Date: February, 1998

SY10H600

Micrel

SY100H600

LOGIC DIAGRAMTRUTH TABLE

ENECL ENTTL D Q

HXH H

HXL L

XHH H

XHL L

LLX L

LOGIC DIAGRAMDC ELECTRICAL CHARACTERISTICS

VCCT = 5.0V ± 10%; VEE = –4.75V to –5.5V (10H Version); VEE = –4.2V to –5.5V (100H Version)

TA = 0°CTA = +25°CTA = +85°C

Symbol Parameter Min. Max. Min. Max. Min. Max. Unit Condition

EE Power Supply Current, mA —

I

ECL 10H — 125 — 125 — 125

100H — 122 — 123 — 132

CCH Power Supply Current, — 48 — 48 — 48 mA —

I

ICCL TTL — 50 — 50 — 50

LOGIC DIAGRAMAC ELECTRICAL CHARACTERISTICS

VCCT = 5.0V ± 10%; VEE = –4.75V to –5.5V (10H Version); VEE = –4.2V to –5.5V (100H Version)

TA = 0°CTA = +25°CTA = +85°C

Symbol Parameter Min. Max. Min. Max. Min. Max. Unit Condition

PLH Propagation Delay to Output ns 50Ω to –2.0V

t

tPHL D 1.4 3.0 1.5 3.2 1.7 3.5

ENECL/ENTTL 1.8 3.7 1.9 3.9 2.0 4.1

r Output Rise/Fall Time 0.5 1.5 0.5 1.5 0.5 1.5 ns 50Ω to –2.0V

t

tf 20% to 80%, 80% to 20%

LOGIC DIAGRAMPRODUCT ORDERING CODE

Ordering Package Operating

Code Type Range

SY10H600JC J28-1 Commercial

SY10H600JCTR J28-1 Commercial

SY100H600JC J28-1 Commercial

SY100H600JCTR J28-1 Commercial

2

Loading...

Loading...