MICREL SY10E195, SY100E195 Datasheet

PROGRAMMABLE

DELAY CHIP

ClockWorks™

SY10E195

SY100E195

FEATURES

■ Up to 2ns delay range

■ Extended 100E V

EE range of –4.2V to –5.5V

■ ≈20ps/digital step resolution

■ >1GHz bandwidth

■ On-chip cascade circuitry

■ 75KkΩ input pulldown resistor

■ Fully compatible with Motorola MC10E/100E195

■ Available in 28-pin PLCC package

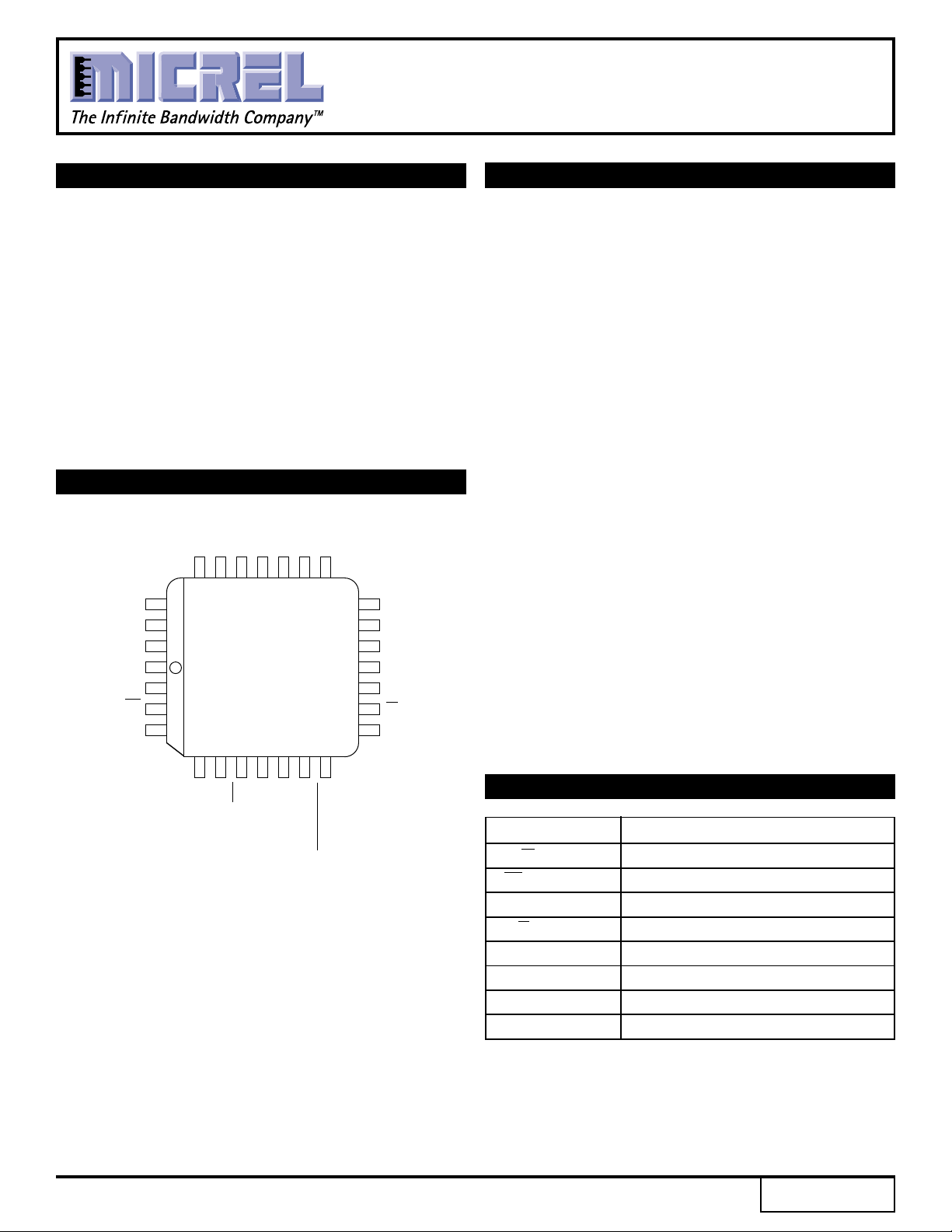

PIN CONFIGURATION

D4

D5

PLCC

J28-1

D6

D7

NC

18

NC

17

NC

16

VCC

15

VCCO

14

Q

13

Q

12

VCCO

D1

D0

LEN

VEE

IN

IN

VBB

D2

D3

25

24 23 22 21 20 19

26

27

28

1

2

3

4

TOP VIEW

567891011

DESCRIPTION

The SY10/100E195 are programmable delay chips

(PDCs) designed primarily for clock de-skewing and timing

adjustment. They provide variable delay of a differential

ECL input transition.

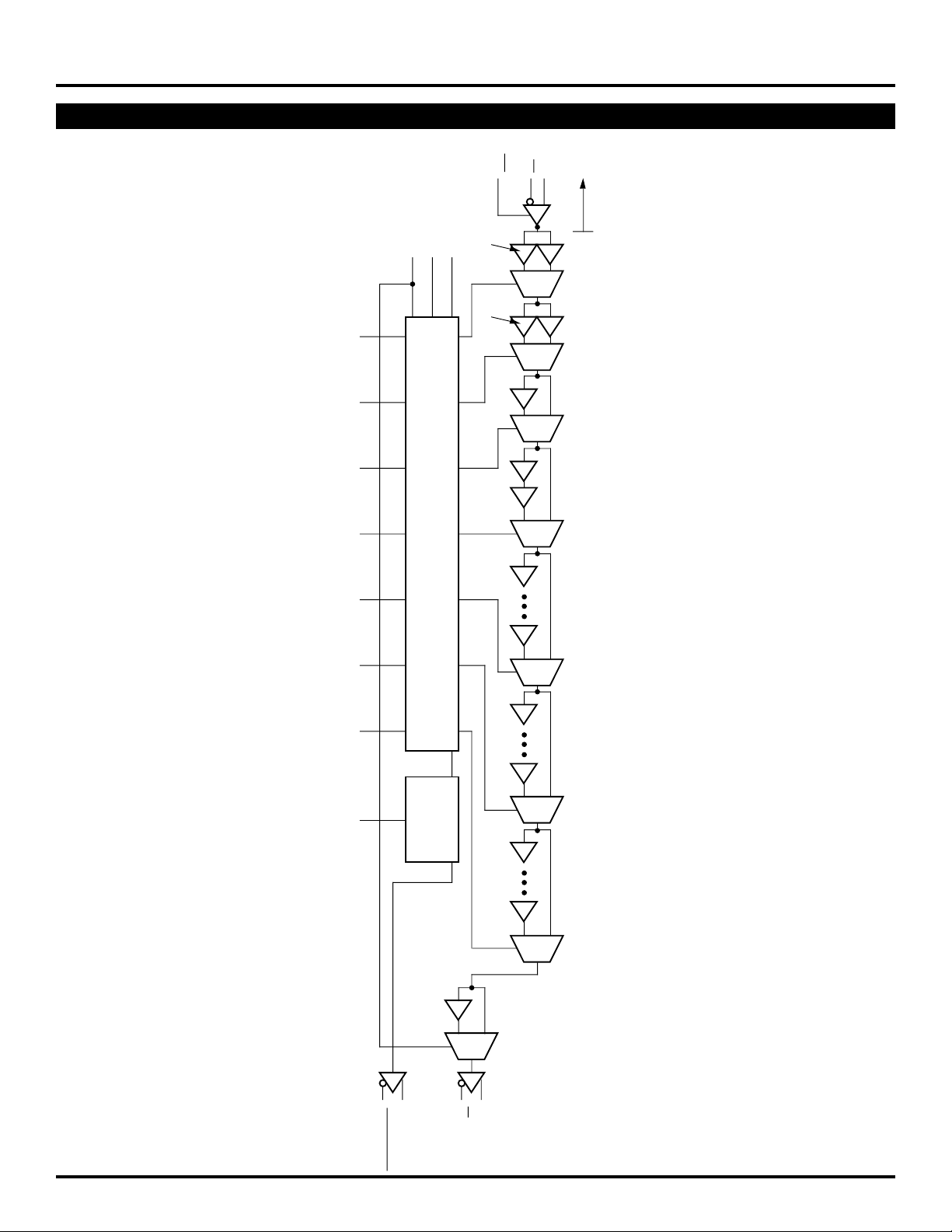

The delay section consists of a chain of gates

organized as shown in the logic diagram. The first two

delay elements feature gates that have been modified to

have delays 1.25 and 1.5 times the basic gate delay of

approximately 80ps. These two elements provide the

E195 with a digitally-selectable resolution of

approximately 20ps. The required device delay is selected

by the seven address inputs D[0:6], which are latched

on-chip by a high signal on the latch enable (LEN) control.

If the LEN signal is either LOW or left floating, then the

latch is transparent.

Because the delay programmability of the E195 is

achieved by purely differential ECL gate delays, the

device will operate at frequencies of >1GHz, while

maintaining over 600mV of output swing.

The E195 thus offers very fine resolution, at very high

frequencies, selectable entirely from a digital input,

allowing for very accurate system clock timing.

An eighth latched input, D7, is provided for cascading

multiple PDCs for increased programmable range. The

cascade logic allows full control of multiple PDCs, at the

expense of only a single added line to the data bus for

each additional PDC, without the need for any external

gating.

NC

NC

EN

SET MIN

SET MAX

CASCADE

CASCADE

PIN NAMES

Pin Function

IN/IN Signal Input

EN Input Enable

D[0:7] Mux Select Inputs

Q/Q Signal Output

LEN Latch Enable

SET MIN Minimum Delay Set

SET MAX Maximum Delay Set

CASCADE Cascade Signal

1

Rev.: E Amendment: /0

Issue Date: October, 1998

Micrel

BLOCK DIAGRAM

ClockWorks™

SY10E195

SY100E195

IN

V

BB

SET MAX

SET MIN

EN

IN

LEN

*1.25

*1.5

D

0

D

1

D

2

1

1

0

1

1

0

1

1

0

1

1

7-Bit Latch

1

D

3

0

4 gates

D

4

*Delays are 25% or 50% longer than

standard (standard = 80ps).

D

5

D

6

D

7

D

CASCADE

CASCADE

LEN

Latch

Q

Cascade

1

1

Q

1

0

8 gates

1

0

16 gates

1

0

0

Q

2

ClockWorks™

SY10E195

Micrel

SY100E195

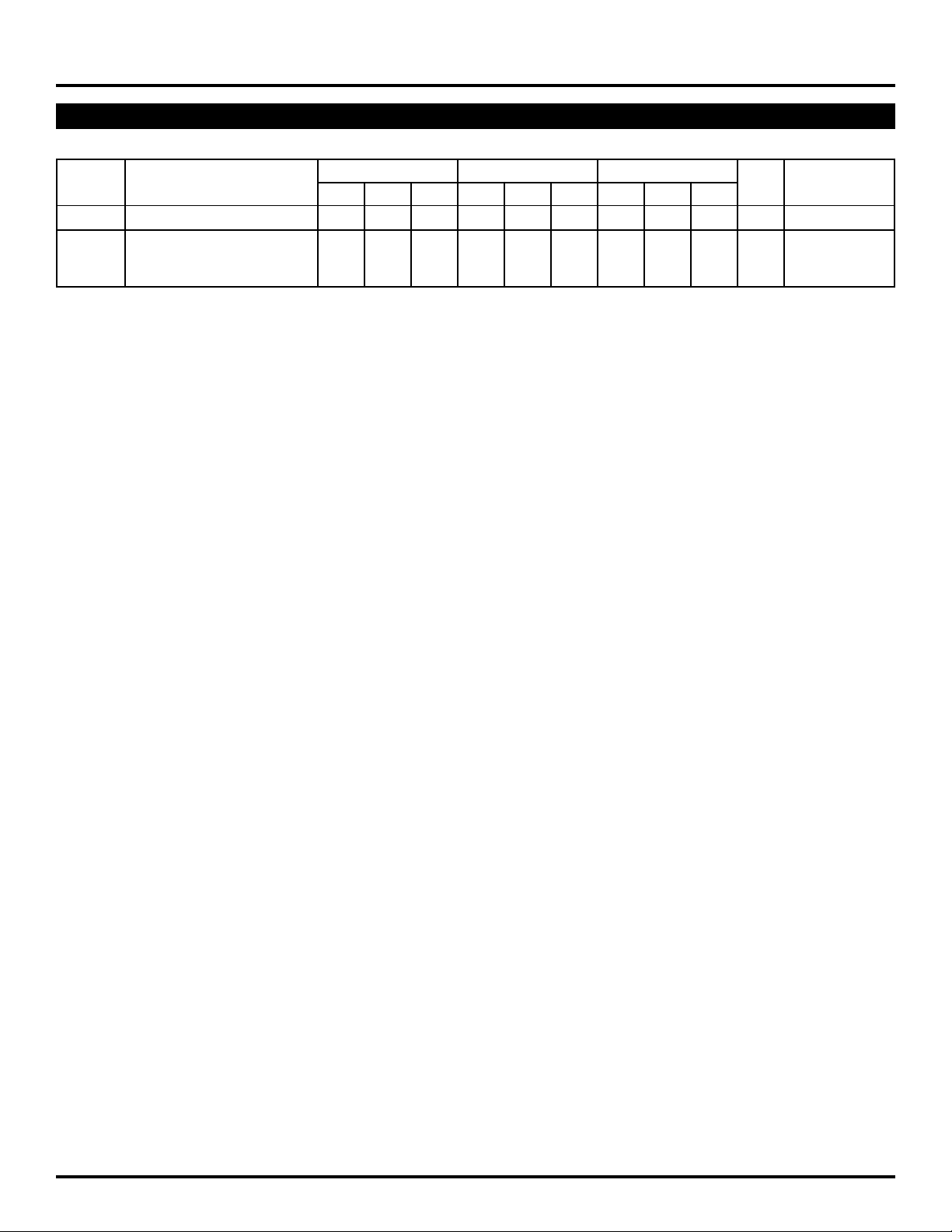

DC ELECTRICAL CHARACTERISTICS

VEE = VEE (Min.) to VEE (Max.); VCC = GND

T

A = 0°CTA = +25°CTA = +85°C

Symbol Parameter Min. Typ. Max. Min. Typ. Max. Min. Typ. Max. Unit Condition

IIH Input HIGH Current — — 150 — — 150 — — 150 µA—

EE Power Supply Current mA —

I

10E — 130 156 — 130 156 — 130 156

100E — 130 156 — 130 156 — 150 179

3

Loading...

Loading...