MICREL SY10E175, SY100E175 Datasheet

9-BIT LATCH

WITH PARITY

SY10E175

SY100E175

FEATURES

■ 9-bit latch

■ Extended 100E VEE range of –4.2V to –5.5V

■ Parity detection/generation

■ 800ps max. D to Output

■ Reset

■ Internal 75KΩ input pull-down resistors

■ Fully compatible with Motorola MC10E/100E175

■ Available in 28-pin PLCC package

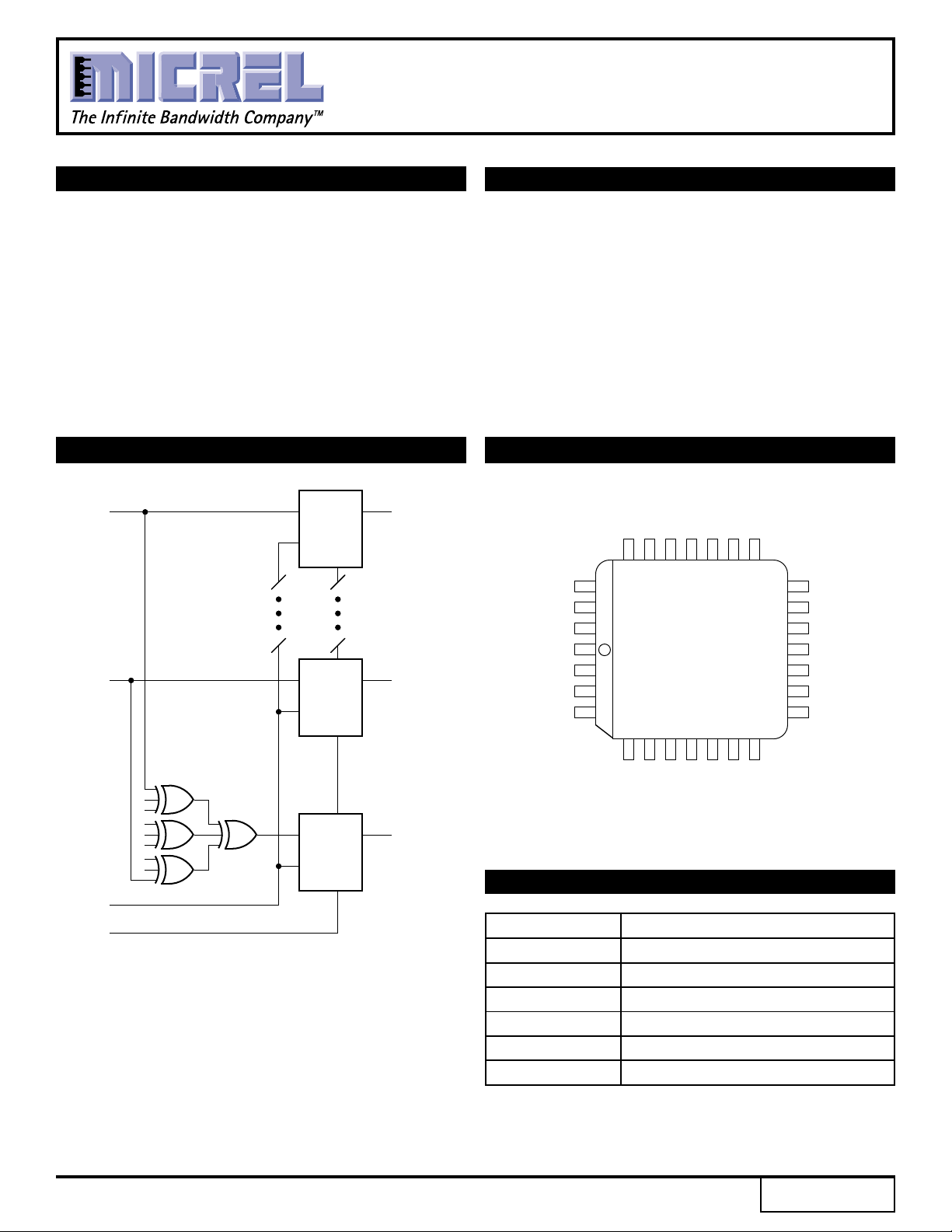

BLOCK DIAGRAM

0

D

DENQ

R

bits

1 – 7

D

8

DENQ

R

Q

0

Q

8

DESCRIPTION

The SY10/100E175 are 9-bit latches. They also feature

a tenth latched output (ODDPAR) which is formed as the

odd parity of the nine data inputs (ODDPAR is HIGH if

an odd number of the inputs are HIGH).

The E175 can also be used to generate byte parity by

using D8 as the parity-type select (L = even parity, H =

odd parity) and using ODDPAR as the byte parity output.

The LEN pin latches the data when asserted with a

logical high and makes the latch transparent when placed

at a logic low level.

PIN CONFIGURATION

D

D

D

V

EE

LEN

MR

D

7

8

6

D

D

D

25

24 23 22 21 20 19

5

26

4

27

3

28

1

2

3

2

4

TOP VIEW

PLCC

J28-1

567891011

CCO

V

Q8Q

7

CCO

V

Q

Q

V

Q

Q

V

Q

6

5

CC

4

3

CCO

2

18

17

16

15

14

13

12

LEN

MR

DENQ

R

ODDPAR

1

D

PIN NAMES

Pin Function

D0 – D8 Data Inputs

LEN Latch Enable

MR Master Reset

Q0 – Q8 Data Outputs

ODDPAR Parity Output

CCO VCC to Output

V

1

0

D

CCO

V

ODDPAR

0

1

Q

Q

CCO

V

Rev.: C Amendment: /1

Issue Date: February, 1998

SY10E175

Micrel

SY100E175

TRUTH TABLE

D LEN MR Q ODDPAR

H L L H H if odd no. of Dn HIGH

LLLLH if odd no. of Dn HIGH

XHLQ0 Q0

XXHLL

DC ELECTRICAL CHARACTERISTICS

VEE = VEE (Min.) to VEE (Max.); VCC = VCCO = GND

TA = 0°CTA = +25°CTA = +85°C

Symbol Parameter Min. Typ. Max. Min. Typ. Max. Min. Typ. Max. Unit Condition

IIH Input HIGH Current ——150 ——150 ——150 µA —

EE Power Supply Current mA —

I

10E — 110 132 — 110 132 — 110 132

100E — 110 132 — 110 132 — 127 152

AC ELECTRICAL CHARACTERISTICS

VEE = VEE (Min.) to VEE (Max.); VCC = VCCO = GND

TA = 0°CTA = +25°CTA = +85°C

Symbol Parameter Min. Typ. Max. Min. Typ. Max. Min. Typ. Max. Unit Condition

PLH Propagation Delay to Output ps —

t

tPHL D to Q 450 600 800 450 600 800 450 600 800

D to ODDPAR 850 1150 1450 850 1150 1450 850 1150 1450

LEN to Q 525 700 900 525 700 900 525 700 900

LEN to ODDPAR 525 700 900 525 700 900 525 700 900

MR to Q (tPHL) 525 700 900 525 700 900 525 700 900

MR to ODDPAR (tPHL) 525 700 900 525 700 900 525 700 900

t

S Set-up Time ps —

D (Q) 275 100 — 275 ——275 ——

D (ODDPAR) 900 700 — 900 ——900 ——

H Hold Time ps —

t

D (Q) 175 –100 — 175 ——175 ——

D (ODDPAR) –300 –700 —–300 ——–300 ——

tRR Reset Recovery Time 850 600 — 850 600 — 850 600 — ps —

skew Within-Device Skew ps 1

t

LEN, MR — 75 ——75 ——75 —

D to Q — 75 ——75 ——75 —

D to ODDPAR — 200 ——200 ——200 —

r Rise/Fall Times 300 500 800 300 500 800 300 500 800 ps —

t

tf 20–80%

NOTE:

1. Within-device skew is defined as identical transitions on similar paths

through a device.

PRODUCT ORDERING CODE

Ordering Package Operating

Code Type Range

SY10E175JC J28-1 Commercial

SY10E175JCTR J28-1 Commercial

SY100E175JC J28-1 Commercial

SY100E175JCTR J28-1 Commercial

2

Loading...

Loading...