MICREL SY100S891 Datasheet

5-BIT REGISTERED

TRANSCEIVER

SY100S891

FEATURES

■ 25Ω cut-off bus outputs

■ 50Ω receiver outputs

■ Transmit and receive registers with separate clocks

■ 1500ps max. delay from CLK1 to Bus Outputs (BUS)

■ 1500ps max. delay from CLK2 to Receiver

■ Individual bus enable pins

■ Internal 75KΩ input pull-down resistors

■ Voltage and temperature compensation for improved

noise immunity

■ Industry standard 100K ECL levels

■ Extended supply voltage option:

VEE = –4.2V to –5.5V

■ Available in 28-pin PLCC package

Outputs (Q)

DESCRIPTION

The SY100S891 is a 5-bit registered transceiver

containing five bus transceivers with both transmit and

receive registers. The bus outputs (BUS

specified for driving a 25 ohm bus and the receive outputs

(Q0 – Q4) are specified for driving a 50 ohm line. The

bus outputs have a normal high level output voltage and

a normal low level output voltage when the bus enable

(BUSEN0 – BUSEN4) is high. However, the output is

switched to a cut-off level when a bus-enable is low.

This cut-off level is sufficiently low that a relatively high

impedance is presented to the bus in order to minimize

reflections. There is one bus-enable for each bus driver;

a clock (CLK

registers; and a separate clock (CLK2) which is common

to all five receive registers. Data at the D inputs is clocked

to the Bus register by a positive transition of CLK1 and

data on the bus is clocked into the Receiver register by

a positive transition of CLK2. A high on the Master Reset

clears all registers.

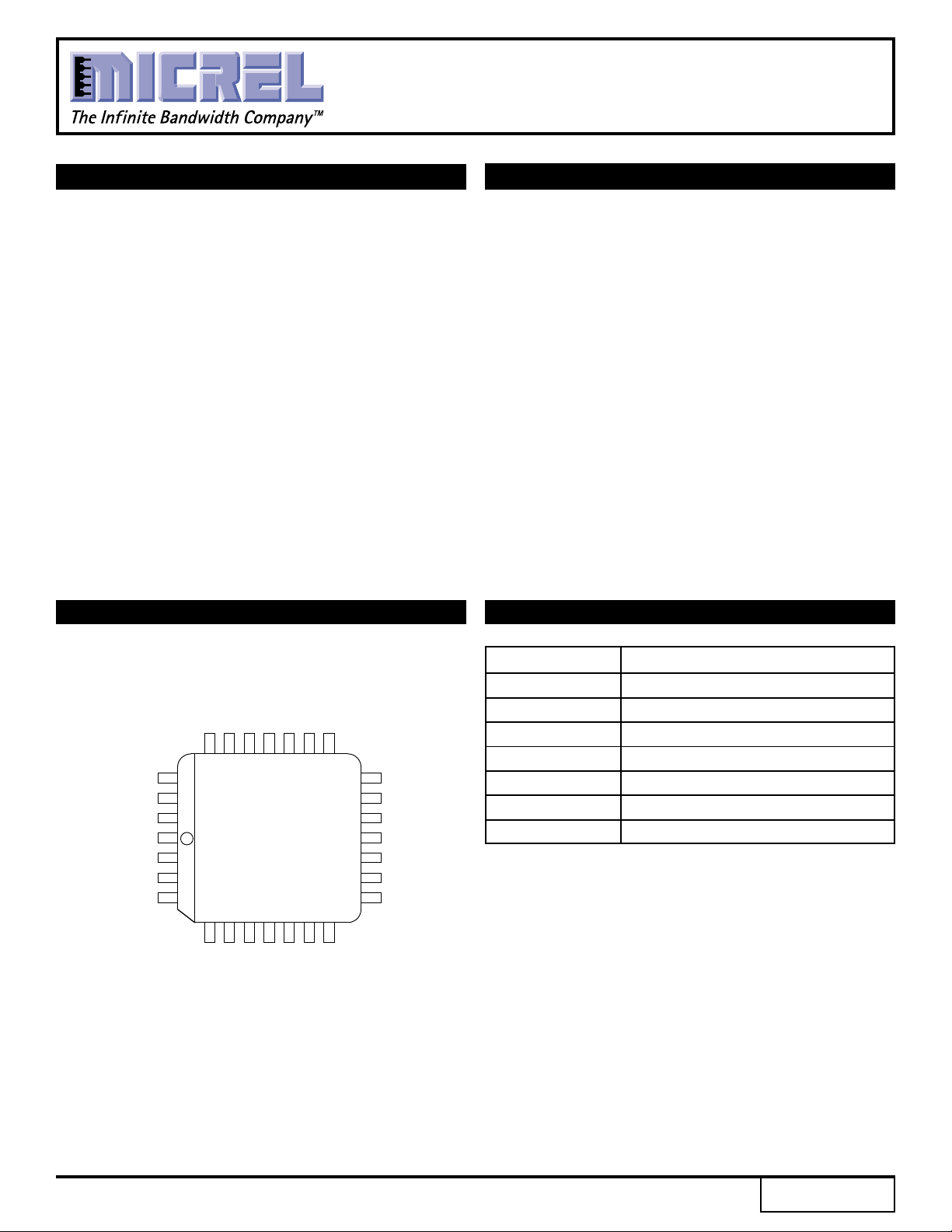

PIN CONFIGURATION PIN NAMES

0 – BUS4) are

1) which is common to all five bus driver

MR

CLK

CLK

V

BUSEN

D

D

EE

Pin Function

3

4

CCA

4

4

3

D

D

BUSEN

BUSEN

25 24 23 22 21 20 19

26

27

2

28

1

1

2

2

3

2

4

1

TOP VIEW

PLCC

J28-1

567891011

0

0

0

1

BUSEN

D

Q

BUSEN

Q

0

BUS

BUS

CCA

V

4

V

18

17

16

15

14

13

12

1

BUS

Q

3

BUS

V

CC

Q

2

BUS

V

CCA

Q

1

3

2

BUSEN0–4 Bus Enable Inputs

D0 – D4 Data Inputs

CLK1 Bus Driver Clock Input

CLK2 Receive Register Clock

MR Master Reset

Q0 – Q4 Bus Receive Outputs

BUS

0–4 Bus Outputs

Rev.: E Amendment: /0

1

Issue Date: August, 1998

Micrel

0

2

3

4

2

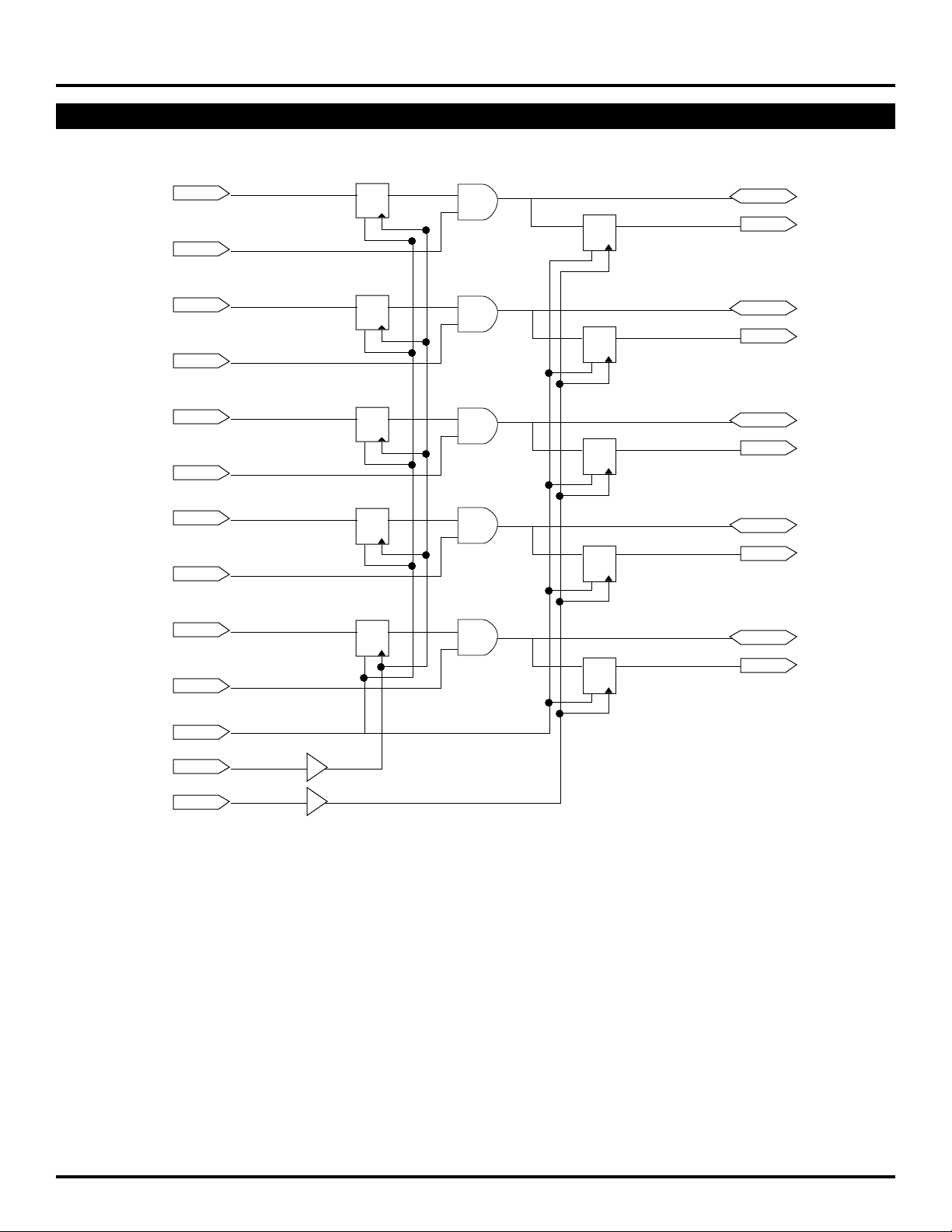

BLOCK DIAGRAM

SY100S891

BUSEN

BUSEN

BUSEN

BUSEN

BUSEN

D

0

D

1

1

D

2

D

3

D

4

DRQ

C

DRQ

C

DRQ

C

DRQ

C

DRQ

C

25Ω CUTOFF

DRQ

C

25Ω CUTOFF

DRQ

C

25Ω CUTOFF

DRQ

C

25Ω CUTOFF

DRQ

C

25Ω CUTOFF

DRQ

C

50Ω

50Ω

50Ω

50Ω

50Ω

BUS

Q

0

BUS

Q

1

BUS

Q

2

BUS

Q

3

BUS

Q

4

0

1

2

3

4

MR

CLK

CLK

1

2

Loading...

Loading...