MICREL SY100S815 Datasheet

SINGLE SUPPLY QUAD

PECL/TTL-TO-PECL

ClockWorks™

SY100S815

FEATURES

■ Quad PECL version of popular ECLinPS E111

■ Low skew

■ Guaranteed skew spec

■ TTL enable input

■ Selectable TTL or PECL clock input

■ Single +5V supply

■ Differential internal design

■ PECL I/O fully compatible with industry standard

■ Internal 75k

Ω PECL input pull-down resistors

■ Available in 16-pin SOIC package

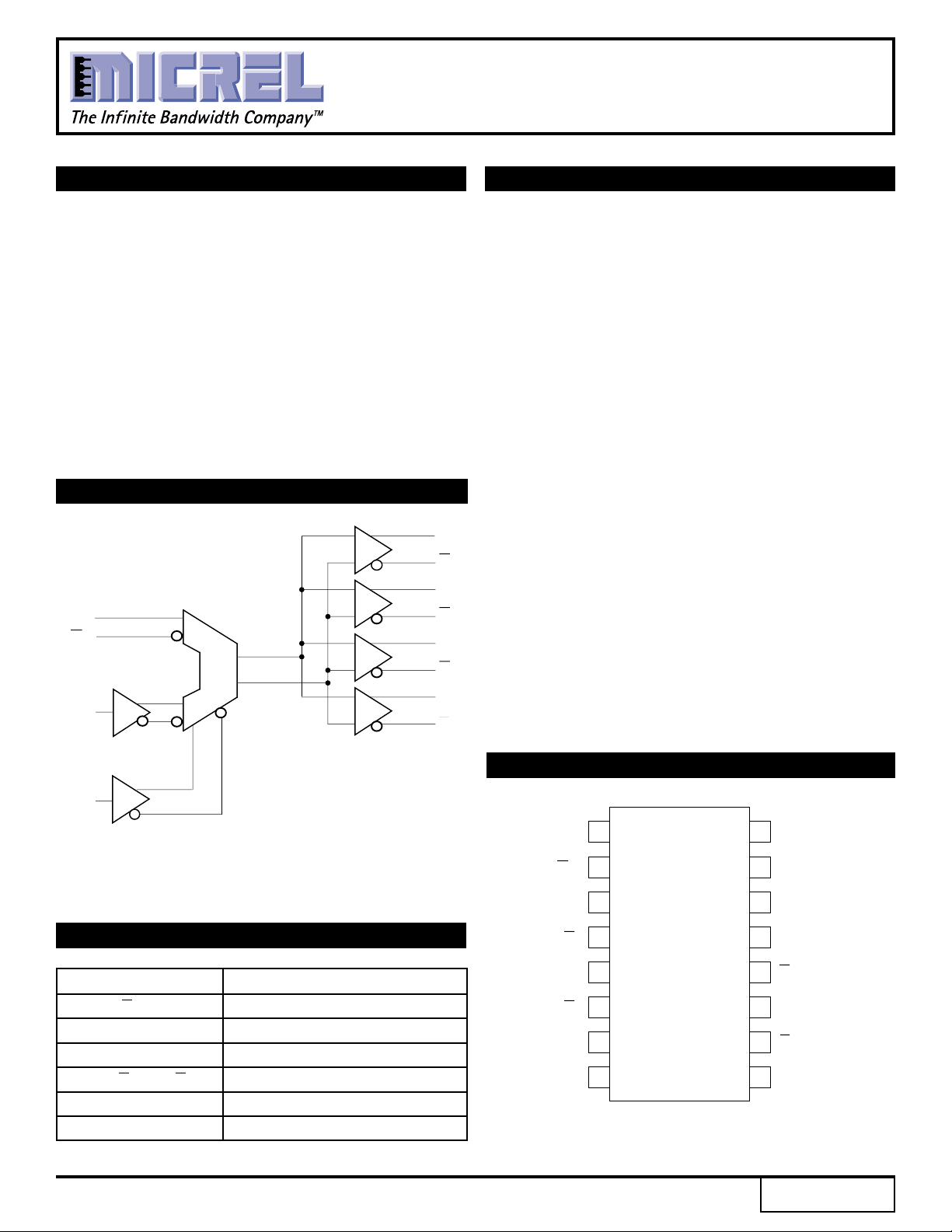

BLOCK DIAGRAM

EIN

EIN

TIN

0

1

DESCRIPTION

The SY100S815 is a low skew 1-to-4 PECL differential

driver designed for clock distribution in new, highperformance PECL systems. It accepts either a PECL

clock input or a TTL input by using the TTL enable pin TEN.

When the TTL enable pin is HIGH, the TTL input is enabled

and the PECL input is disabled. When the enable pin is set

LOW, the TTL input is disabled and the PECL input is

enabled.

The device is specifically designed and produced for low

skew. The interconnect scheme and metal layout are

carefully optimized for minimal gate-to-gate skew within

the device. Wafer characterization and process control

ensure consistent distribution of propagation delay from lot

to lot. Since the S815 shares a common set of “basic”

processing with the other members of the ECLinPS family,

wafer characterization at the point of device personalization

allows for tighter control of parameters, including

propagation delay.

Q0

Q0

Q1

Q1

Q2

Q2

Q3

Q3

To ensure that the skew specification is met, it is

necessary that both sides of the differential output are

terminated into 50Ω, even if only one side is being used. In

most applications, all nine differential pairs will be used

and, therefore, terminated. In the case where fewer than

nine pairs are used, it is necessary to terminate at least the

output pairs on the same package side (i.e. sharing the

same VCCO as the pair(s) being used on that side) in order

to maintain minimum skew.

TEN

PIN NAMES

Pin Function

EIN, EIN Differential PECL Input Pair

TIN TTL Input

TEN TTL Input Enable

Q0, Q0 – Q3, Q3 Differential PECL Outputs

VCC PECL VCC (+5.0V)

EE PECL Ground (0V)

V

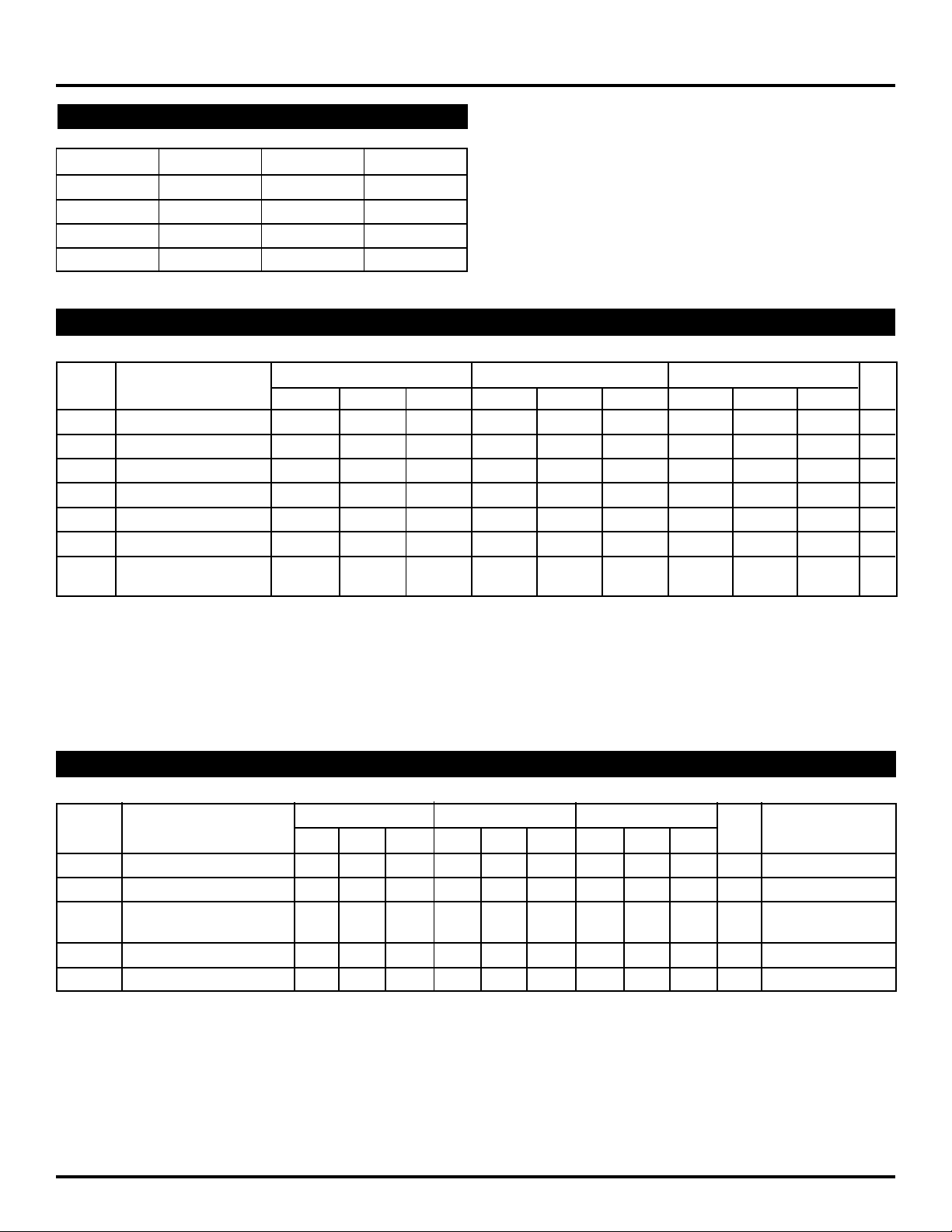

PIN CONFIGURATION

VCC

1

2

EIN

3

TIN

4

Q3

5

Q3

6

Q2

7

Q2

VCCO

1

8

TOP VIEW

SOIC

Z16-1

16

EIN

15

TEN

14

VEE

13

Q0

12

Q0

11

Q1

10

Q1

9

VCCO

Rev.: F Amendment: /0

Issue Date: October, 1998

ClockWorks™

Micrel

SY100S815

TRUTH TABLE

TEN EIN TIN Q

LLXL

LHXH

HXLL

HXHH

PECL DC ELECTRICAL CHARACTERISTICS

VCC = VCCO = +5.0V ± 5%

TA = 0°CTA = +25°CTA = +85°C

Symbol Parameter Min. Typ. Max. Min. Typ. Max. Min. Typ. Max. Unit

IIH Input HIGH Current ——150 ——150 ——150 µA

IIL Input LOW Current 0.5 ——0.5 ——0.5 ——µA

(3)

(1)

3.835 — 4.120 3.835 — 4.120 3.835 — 4.120 V

(1)

3.190 — 3.525 3.190 — 3.525 3.190 — 3.525 V

(2)

VCC –1025 VCC –955 VCC –870 VCC –1025 VCC –955 VCC –870 VCC –1025 VCC –955 VCC –870 mV

(2)

VCC –1890 VCC –1705 VCC –1620 VCC –1890 VCC –1705 VCC –1620 VCC –1890 VCC –1705VCC –1620 mV

— 53 65 — 53 65 — 60 74 mA

VIH Input HIGH Voltage

VIL Input LOW Voltage

VOH Output HIGH Voltage

VOL Output LOW Voltage

ICC Power Supply

Current

NOTES:

1. VCC = VCCO = 5.0V

2. VIN = VIH (Max.) or VIL (Min.) Loading with 50Ω to VCC –2V.

3. All inputs and outputs open.

TTL DC ELECTRICAL CHARACTERISTICS

VCC = VCCO = +5.0V ± 5%

TA = 0°CTA = +25°CTA = +85°C

Symbol Parameter Min. Typ. Max. Min. Typ. Max. Min. Typ. Max. Unit Condition

VIH Input HIGH Voltage 2.0 ——2.0 ——2.0 ——V

VIL Input LOW Voltage —— 0.8 ——0.8 ——0.8 V

IH Input HIGH Current

I

IIL Input LOW Current

V

IK Input Clamp Voltage

NOTES:

1. VIN=2.7V

2. VIN=5.0V

3. VIN=0.5V

4. IIN=-18mA

(1),(2)

(3)

(4)

—— 20 ——20 ——20 µA

——100 ——100 ——100

——–0.6 ——–0.6 ——–0.6 mA

——–1.2 ——–1.2 ——–1.2 V

2

Loading...

Loading...