MICREL SY100S370 Datasheet

UNIVERSAL

a

b

DEMULTIPLEXER/

DECODER

FEATURES

■ Max. propagation delay of 1200ps

■ I

EE min. of –92mA

■ Industry standard 100K ECL levels

■ Extended supply voltage option:

VEE = –4.2V to –5.5V

■ Voltage and temperature compensation for improved

noise immunity

■ Internal 75KΩ input pull-down resistors

■ 60% faster than National or Signetics

■ Approximately 40% lower power than Fairchild

■ Function and pinout compatible with Fairchild F100K

■ Available in 24-pin CERPACK and 28-pin PLCC

packages

PIN NAMES

Pin Function

Ana, Anb Address Inputs (n = 0,1,2)

Ena, Enb Enable Inputs (n = 1,2)

M Mode Control Input

Ha Z0 – Z3 (Z0a – Z3a) Polarity Select Input

Hb Z4 – Z7 (Z0b – Z3b) Polarity Select Input

Hc Common Polarity Select Input

Z0 – Z7 Single 1-of-8 Data Outputs

Zna, Znb Dual 1-of-4 Data Outputs (n = 1...4)

VEES VEE Substrate

CCA VCCO for ECL Outputs

V

SY100S370

DESCRIPTION

The SY100S370 is a universal demultiplexer/decoder

that can be used as either a dual 1-of-4 decoder or as a

single 1-of-8 decoder and is designed for use in highperformance ECL systems. The Mode control (M) input

determines the function. In the dual 1-of-4 mode, each 4input group has a pair of active-LOW Enable (E) inputs.

The Enable pins are assigned such that in the single 1-of8 mode they can be tied together in pairs to result in two

active-LOW Enable inputs. E

1a will be tied to E1b and E2a

to E2b.

The auxiliary inputs (Hn) are used to determine whether

the outputs are active-HIGH or active-LOW. The address

inputs for the dual 1-of-4 mode are A0a, A1a, A0b. A2a is

unused. In the 1-of-8 mode, the address inputs are A0a,

A1a, A2a. The inputs on the device have 75KΩ pull-down

resistors.

PIN CONFIGURATIONS

)

)

1

2

(Z

1a

A

Top View

PLCC

J28-1

b

0b

H

A

Z

3b (Z7

Z

0b (Z4

EES

V

EES

V

A2aM

E

1a

12

E

1b

13

V

EE

14

V

EES

15

E

2b

16

17

E

2a

H

a

1911201021922823724

c

H

(Z

0a

1a

2a

Z

Z

A

6

5

Z

0a (Z0

3a (Z3

Z

V

CCA

V

CC

V

CC

Z

1b (Z5

Z

2b (Z6

2

E

)

)

)

)

2

E

EE

V

E1bE

1a

4

3

2

1

28

27

2618

25

)

)

7

4

1b

A

(Z

(Z

3b

0b

Z

Z

a

H

19

1

H

c

H

b

2

3

A

0b

A

1b

)

)

Top View

Flatpack

4

F24-1

5

6

18

17

16

15

14

13

A

2a

M

A

1a

A

0a

Z

1a (Z1

Z

2a (Z2

)

)

7248239221021112012

)

)

5

6

(Z

(Z

1b

2b

Z

Z

1

)

)

3

CC

V

0

CCA

(Z

(Z

V

3a

0a

Z

Z

Rev.: G Amendment: /0

Issue Date: July, 1999

Micrel

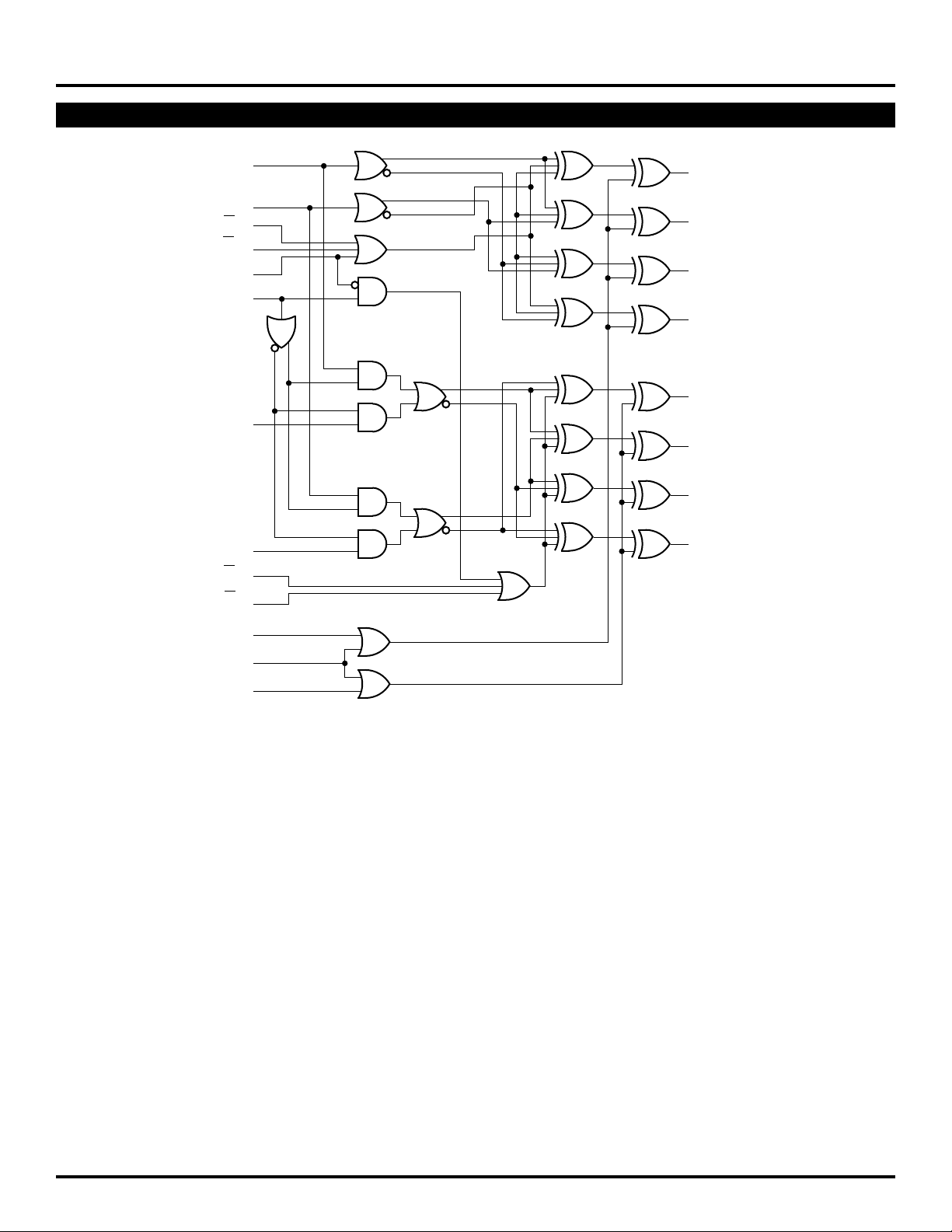

BLOCK DIAGRAM

SY100S370

A0a

A1a

E1a

E2a

A2a

A0b

A1b

E1b

E2b

Z2a (Z2)

Z0a (Z0)

Z1a (Z1)

M

Z3a (Z3)

Z2b (Z6)

Z0b (Z4)

Z1b (Z5)

Z3b (Z7)

Ha

Hc

Hb

2

Micrel

SY100S370

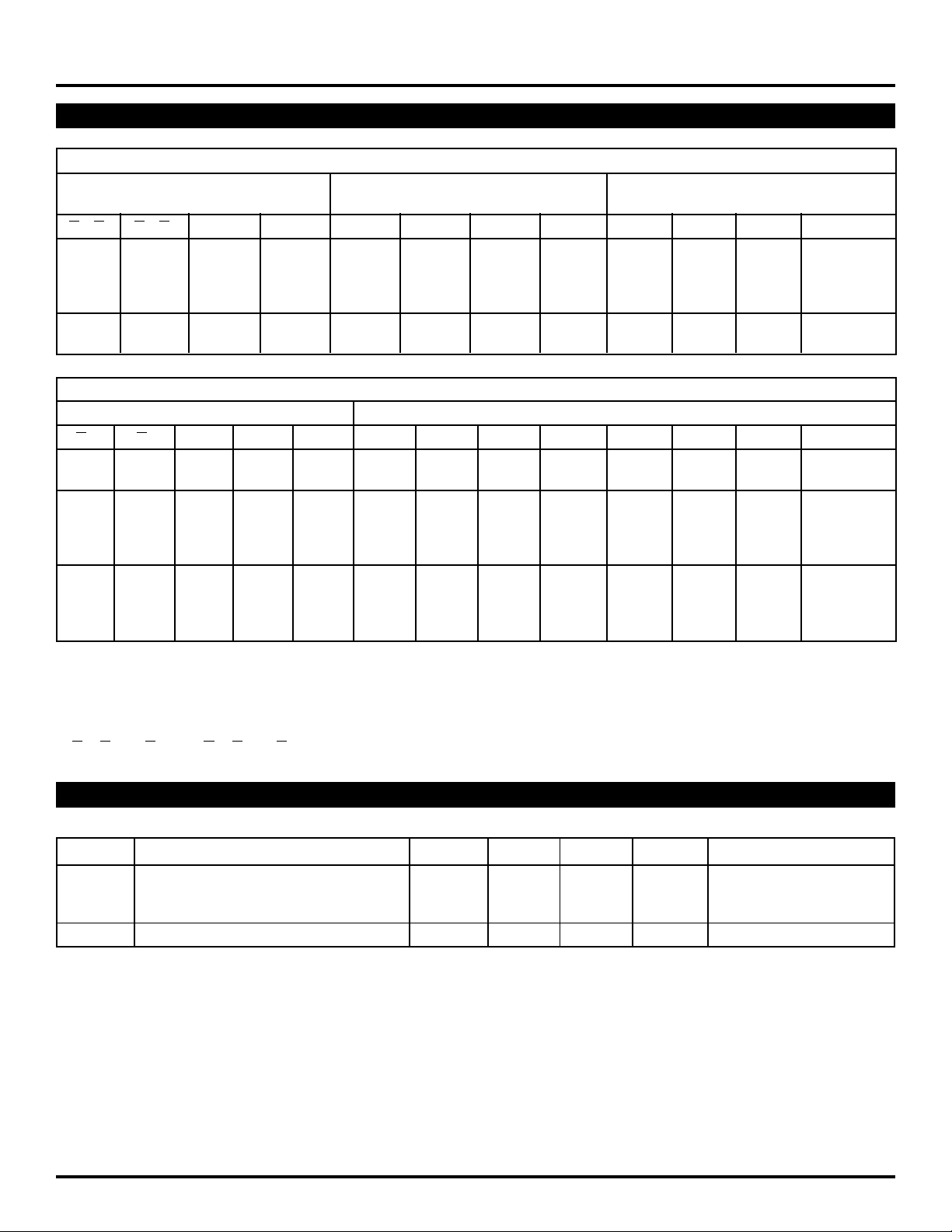

TRUTH TABLES

(1)

Dual 1-of-4 Mode (M = A2a = Hc = LOW)

Active HIGH Outputs Active LOW Outputs

Inputs (Ha and Hb Inputs HIGH) (Ha and Hb Inputs LOW)

E1a,E1b E2a,E2b A1a,A1b A0a,A0b Z0a,Z0b Z1a,Z1b Z2a,Z2b Z3a,Z3b Z0a,Z0b Z1a,Z1b Z2a,Z2b Z3a,Z3b

HXXX LLLLHHHH

XHXX LLLLHHHH

LLL L HL L LLHHH

LLL H L H L LHLHH

LLHL LLHLHHLH

LLH H L L L HHHHL

Single 1-of-8 Mode (M = HIGH; A0b = A1b = Ha = Hb = LOW)

Inputs Active HIGH Outputs* (Hc Input HIGH)

E1 E2 A2a A1a A0a Z0 Z1 Z2 Z3 Z4 Z5 Z6 Z7

HXXXXLLLLLLLL

XHXXXLLLLLLLL

LLLLLHLLLLLLL

LLLLHLHLLLLLL

LLLHLLLHLLLLL

LLLHHLLLHLLLL

LL HLL LLL L H L L L

LL HLH LLL L L H L L

LLHHLLLLLLLHL

LLHHHLLLLLLLH

NOTE:

1. H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

* for Hc = LOW, output states are complemented

E1 = E1a and E1b wired; E2 = E2a and E2b wired

DC ELECTRICAL CHARACTERISTICS

VEE = –4.2V to –5.5V unless otherwise specified; VCC = VCCA = GND

Symbol Parameter Min. Typ. Max. Unit Condition

I

IH Input HIGH Current µAVIN = VIH (Max.)

Hc, A0a, A1a, A2a ——310

All Others ——250

EE Power Supply Current –92 –73 –46 mA Inputs Open

I

3

Loading...

Loading...