MICREL SY100S351 Datasheet

HEX D FLIP-FLOP

a

SY100S351

FEATURES

■ Max. toggle frequency of 700MHz

■ Clock to Q max. of 1200ps

■ IEE min. of –98mA

■ Industry standard 100K ECL levels

■ Extended supply voltage option:

VEE = –4.2V to –5.5V

■ Voltage and temperature compensation for improved

noise immunity

■ Internal 75KΩ input pull-down resistors

■ 50% faster than Fairchild 300K

■ Better than 20% lower power than Fairchild

■ Function and pinout compatible with Fairchild F100K

■ Available in 24-pin CERPACK and 28-pin PLCC

packages

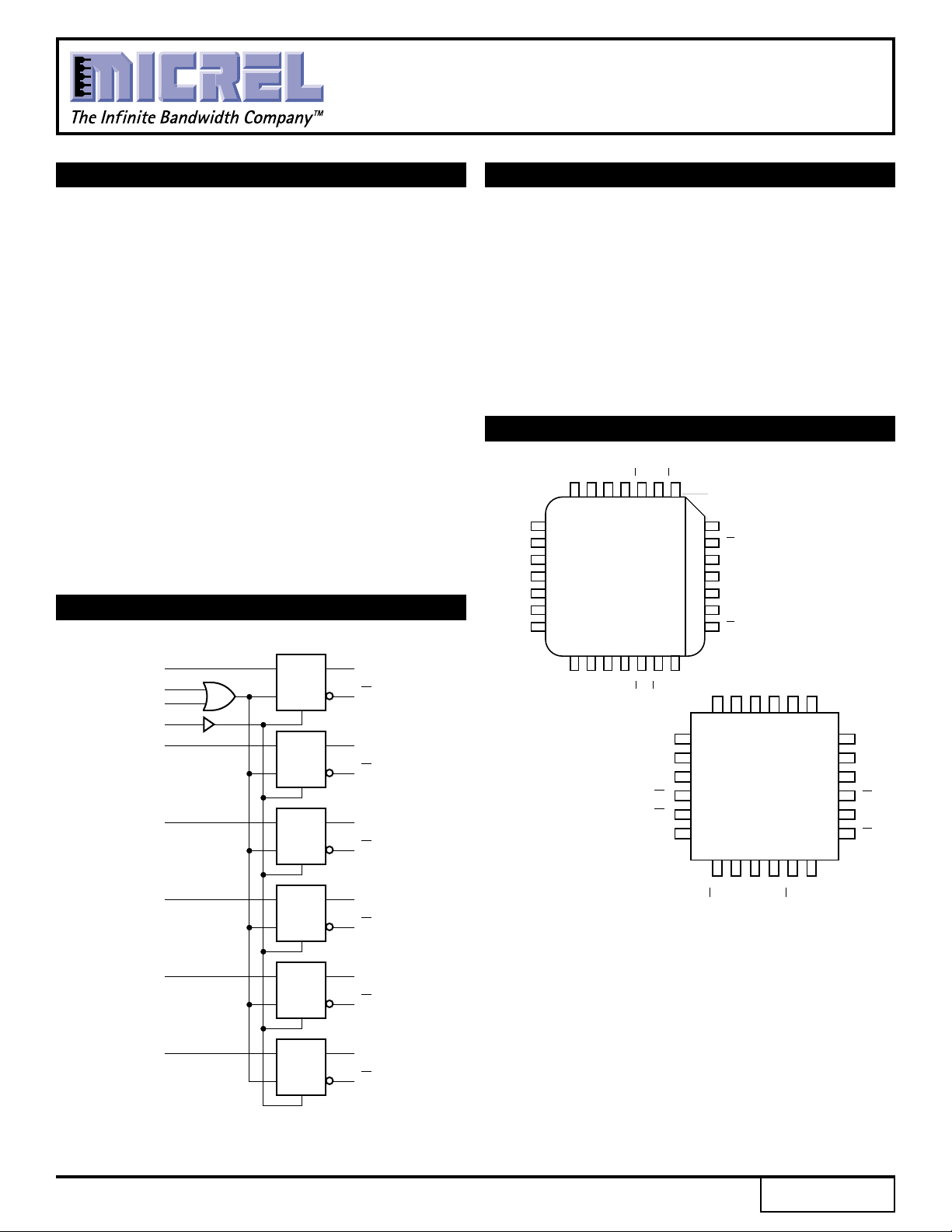

BLOCK DIAGRAM

D

Q

E Q

Q

R

D

Q

E Q

Q

R

D

Q

E Q

Q

R

D

Q

E Q

Q

R

Q

5

5

Q

4

4

Q

3

3

Q

2

2

CP

CP

MR

D

5

b

a

D

4

D

3

D

2

DESCRIPTION

The SY100S351 offers six D-type, edge-triggered,

master/slave flip-flops with differential outputs, and is

designed for use in high-performance ECL systems. The

flip-flops are controlled by the signal from the logical OR

operation on a pair of common clock signals (CPa, CPb).

Data enters the master when both CPa and CPb are LOW

and transfers to the slave when either CPa or CPb (or both)

go to a logic HIGH. The Master Reset (MR) input overrides

all other inputs and takes the Q outputs to a logic LOW. The

inputs on this device have 75KΩ pull-down resistors.

PIN CONFIGURATIONS

D1

D0

Q0

Q0Q1Q1

VEES

6

5

D2

D

VEE

VEES

MR

CPa

12

13

3

14

Top View

15

16

17

PLCC

J28-1

1911201021922823724

D5

Q5

D4

Q5

VEES

25

Q4

D

4

D

5

Q

5

Q

5

Q

4

Q

4

Q2

4

3

Q2

2

VCCA

1

VCC

28

VCC

27

Q3

2618

Q

3CPb

CPbCP

Q4

1

2

3

4

5

6

7248239221021112012

3

Q

EE

MR

V

Top View

Flatpack

F24-1

3

CC

Q

CCA

V

V

D3D

19

2

Q

2

18

17

16

15

14

13

2

Q

D

1

D

0

Q

0

Q

0

Q

1

Q

1

D

1

0

D

D

Q

E Q

Q

R

D

Q

E Q

Q

R

Q

1

1

Q

0

0

Rev.: G Amendment: /0

1

Issue Date: July, 1999

Micrel

PIN NAMES

Pin Function

D0 — D5 Data Inputs

CPa, CPb Common Clock Inputs

MR Asynchronous Master Reset Input

Q0 — Q5 Data Outputs

Q0 — Q5 Complementary Data Outputs

VEES VEE Substrate

CCA VCCO for ECL Outputs

V

TRUTH TABLES

SY100S351

Asynchronous Operation

(1)

Inputs Outputs

Dn CPa CPb MR Qn (t+1)

XXXH L

NOTE:

1. H = High Voltage Level

L = Low Voltage Level

X = Don't Care

t = Time before CP Positive Transition

t+1 = Time after CP Positive Transition

u = LOW-to-HIGH Transition

Synchronous Operation

Inputs Outputs

Dn CPa CPb MR Qn (t+1)

LuLL L

HuLL H

LLuL L

HLuL H

XHuLQn(t)

XuHLQn(t)

(1)

XLLLQ

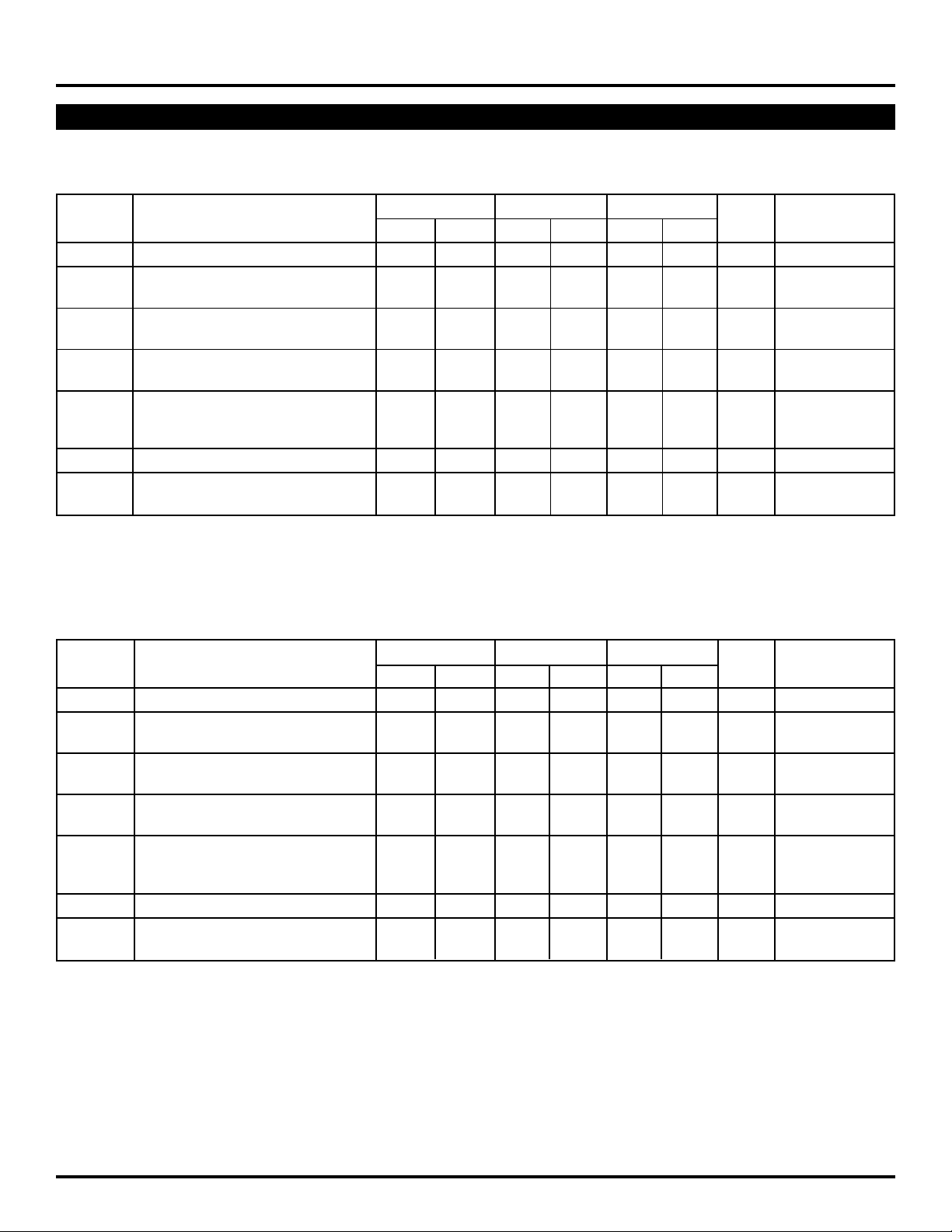

DC ELECTRICAL CHARACTERISTICS

VEE = –4.2V to –5.5V unless otherwise specified; VCC = VCCA = GND

Symbol Parameter Min. Typ. Max. Unit Condition

IH Input HIGH Current µAVIN = VIH (Max.)

I

MR — — 270

D0 – D5 ——200

CPa, CPb ——300

I

EE Power Supply Current –98 –71 –49 mA Inputs Open

n(t)

2

Micrel

SY100S351

AC ELECTRICAL CHARACTERISTICS

CERPACK

VEE = –4.2V to –5.5V unless otherwise specified; VCC = VCCA = GND

A = 0°CTA = +25°CTA = +85°C

T

Symbol Parameter Min. Max. Min. Max. Min. Max. Unit Condition

fMAX Toggle Frequency 700 — 700 — 700 — MHz

PLH Propagation Delay — 1200 — 1200 — 1200 ps

t

tPHL CPa, CPb to Output

t

PLH Propagation Delay — 1200 — 1200 — 1200 ps

tPHL MR to Output

TLH Transition Time 300 900 300 900 300 900 ps

t

tTHL 20% to 80%, 80% to 20%

S Set-up Time ps

t

D

0–D5 500 — 500 — 500 —

MR (Release Time) 1000 — 1000 — 1000 —

tH Hold Time, D0–D5 550 — 550 — 550 — ps

PW (H) Pulse Width HIGH 1000 — 1000 — 1000 — ps

t

CPa, CPb, MR

PLCC

VEE = –4.2V to –5.5V unless otherwise specified; VCC = VCCA = GND

TA = 0°CTA = +25°CTA = +85°C

Symbol Parameter Min. Max. Min. Max. Min. Max. Unit Condition

fMAX Toggle Frequency 700 — 700 — 700 — MHz

t

PLH Propagation Delay — 1200 — 1200 — 1200 ps

tPHL CPa, CPb to Output

PLH Propagation Delay — 1200 — 1200 — 1200 ps

t

tPHL MR to Output

TLH Transition Time 300 900 300 900 300 900 ps

t

tTHL 20% to 80%, 80% to 20%

S Set-up Time ps

t

D0–D5 500 — 500 — 500 —

MR (Release Time) 1000 — 1000 — 1000 —

tH Hold Time, D0–D5 550 — 550 — 550 — ps

PW (H) Pulse Width HIGH 1000 — 1000 — 1000 — ps

t

CPa, CPb, MR

3

Loading...

Loading...