MICREL SY100S321 Datasheet

D9D

8

V

CCA

V

EE

D7D

6

17

16

15

14

13

1

2

3

4

5

6

7248239221021112012

19

Top View

Flatpack

F24-1

D

1

D

3

D

2

V

CCA

O

3

V

CC

V

CCA

O1O

9

O8O

7

D

4

V

CCA

Q

6

LOW-POWER 9-BIT

INVERTER

SY100S321

FEATURES

■ Max. propagation delay of 700ps

■ IEE min. of –55mA

■ Extended supply voltage option:

VEE = –4.2V to –5.5V

■ Voltage and temperature compensation for

improved noise immunity

■ 70% faster than Fairchild 300K at lower power

■ Internal 75KΩ input pull-down resistors

■ Function and pinout compatible with Fairchild F100K

■ Available in 24-pin CERPACK and 28-pin PLCC

packages

BLOCK DIAGRAM

D

1

O

1

DESCRIPTION

The SY100S321 is a monolithic 9-bit inverter. The device

contains nine inverting buffer gates with single input and

output.

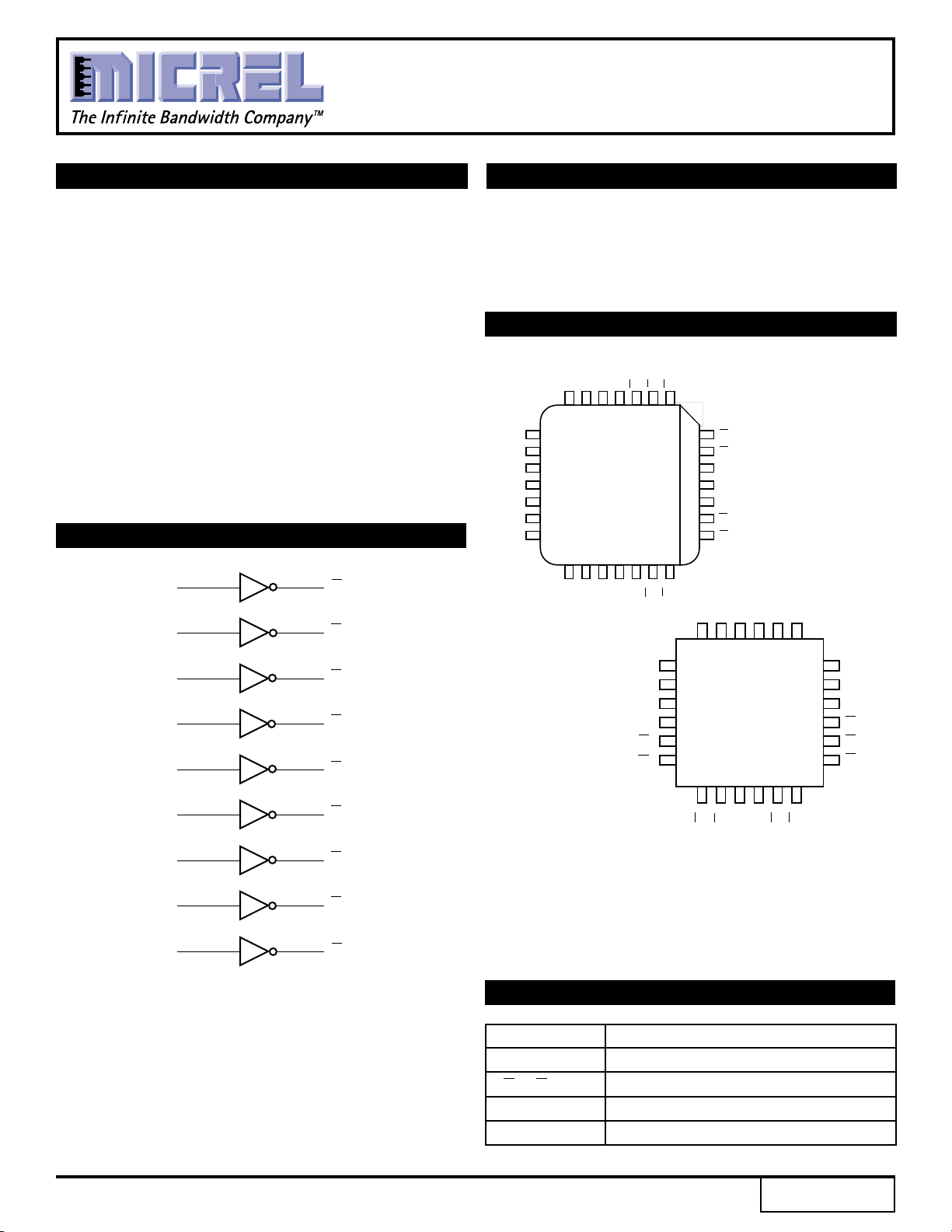

PIN CONFIGURATIONS

D5

D6

D7

VEE

VEES

VCCA

D8

D9 2618

D4

VCCAVEESO4O5

12

13

Top View

14

15

16

17

PLCC

J28-1

1911201021922823724

D3

D2

D1

VEES

VCCA

O6

6

5

4

O7

3

O8

2

VCCA

1

VCC

28

VCC

27

O9

O1

25

O2

O3

O

D

2

D

3

D

4

D

5

D

6

D

7

D

8

D

9

2

18

D

O

3

O

4

O

O

5

O

6

O

7

O

8

O

9

2

5

Q

4

Q

5

PIN NAMES

Pin Function

D1 – D9 Data Inputs

Q1 – Q9 Data Outputs

VEES VEE Substrate

CCA VCCO for ECL Outputs

V

Rev.: G Amendment: /0

1

Issue Date: July, 1999

Micrel

SY100S321

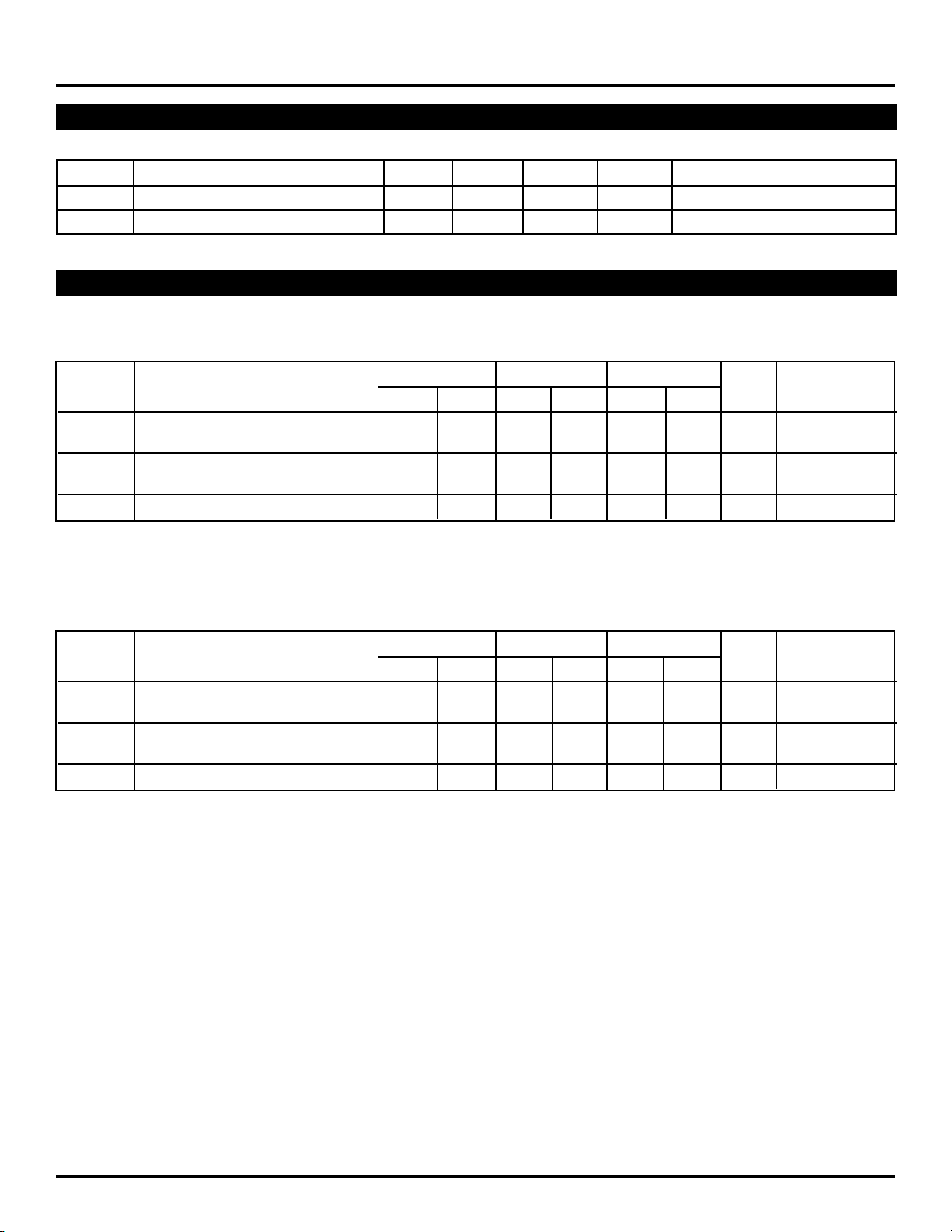

DC ELECTRICAL CHARACTERISTICS

VEE = –4.2V to –5.5V unless otherwise specified, VCC = VCCA = GND

Symbol Parameter Min. Typ. Max. Unit Condition

IIH Input HIGH Current — — 200 µAVIN = VIH (Max.)

I

EE Power Supply Current –55 –41 –25 mA Inputs Open

AC ELECTRICAL CHARACTERISTICS

CERPACK

VEE = –4.2V to –5.5V unless otherwise specified, VCC = VCCA = GND

TA = 0°CTA = +25°CTA = +85°C

Symbol Parameter Min. Max. Min. Max. Min. Max. Unit Condition

t

PLH Propagation Delay

tPHL Data to Output

TLH Transition Time

t

tTHL 20% to 80%, 80% to 20%

S, G–G Skew, Gate-to-Gate — 200 — 200 — 200 ps

t

(1)

(1)

300 800 300 800 300 800 ps

300 900 300 900 300 900 ps

NOTE:

1. Reference figures 1 and 2

PLCC

VEE = –4.2V to –5.5V unless otherwise specified, VCC = VCCA = GND

TA = 0°CTA = +25°CTA = +85°C

Symbol Parameter Min. Max. Min. Max. Min. Max. Unit Condition

PLH Propagation Delay

t

tPHL Data to Output

TLH Transition Time

t

tTHL 20% to 80%, 80% to 20%

S, G–G Skew, Gate-to-Gate — 200 — 200 — 200 ps

t

NOTE:

1. Reference figures 1 and 2

(1)

(1)

300 700 300 700 300 700 ps

300 900 300 900 300 900 ps

2

Loading...

Loading...