MICREL SY100S318 Datasheet

5-WIDE 5, 4, 4, 4, 2

D2cD1cD

4b

V

EE

D3bD

2b

D

5a

D

4a

D

3a

D

1a

D

2a

D

4c

D

4d

D

2d

17

16

15

14

13

1

2

3

4

5

6

7248239221021112012

19

Top View

Flatpack

F24-1

V

CC

V

CCA

D

2e

O

D

1e

O

OA/OAI GATE

SY100S318

FEATURES

■ Max. propagation delay of 800ps

■ IEE min. of –55mA

■ Extended supply voltage option:

VEE = –4.2V to –5.5V

■ Voltage and temperature compensation for

improved noise immunity

■ Internal 75K

Ω input pull-down resistors

■ 70% faster than Fairchild

■ 40% lower power than Fairchild

■ Function and pinout compatible with Fairchild F100K

■ Available in 24-pin CERPACK and 28-pin PLCC

packages

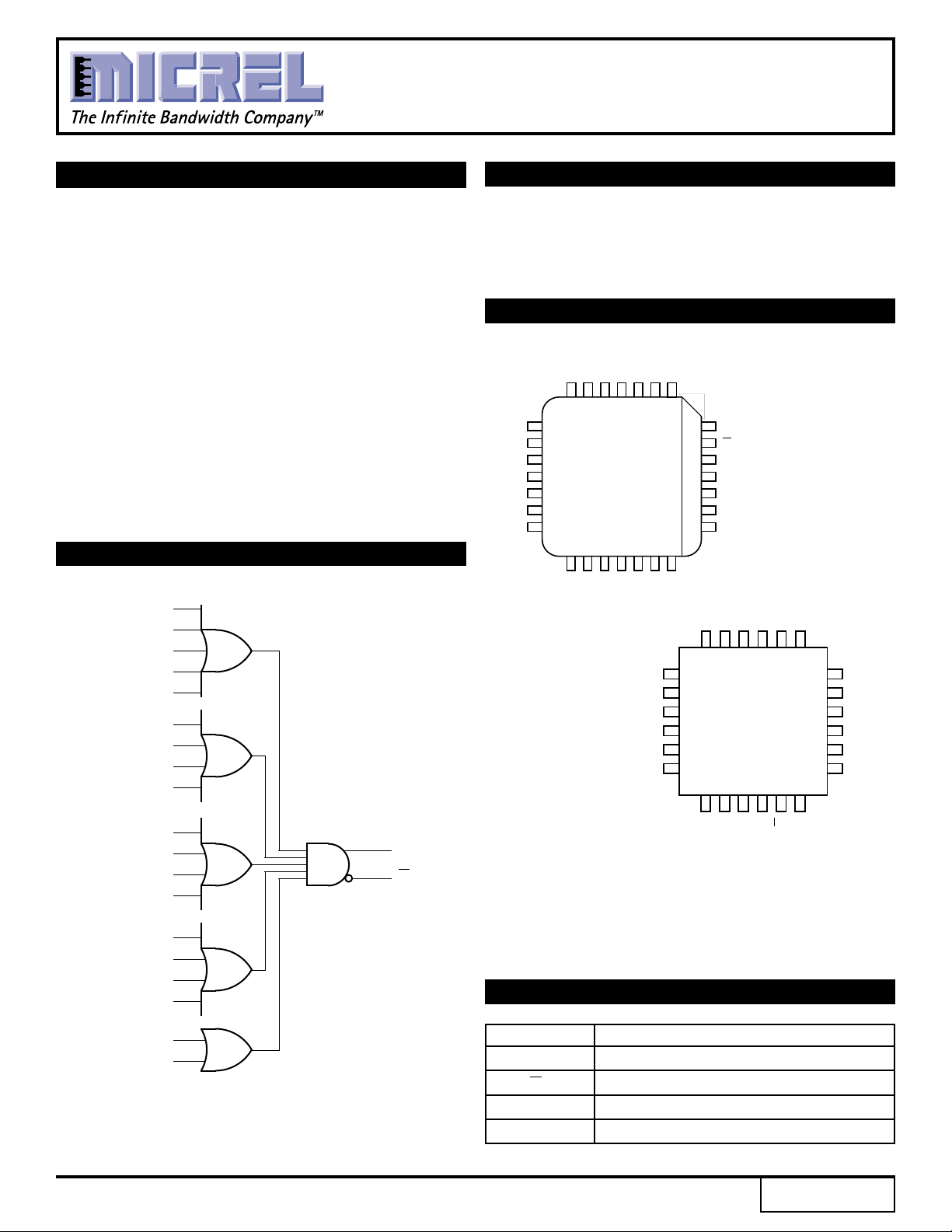

BLOCK DIAGRAM

D

1a

D

2a

D

3a

D

4a

D

5a

D

1b

D

2b

D

3b

D

4b

DESCRIPTION

The SY100S318 is an ultra-fast 5-wide 5, 4, 4, 4, 2 OR/

AND gate with both true and complementary outputs,

designed for use in high-performance ECL systems. The

inputs on this device have 75KΩ pull-down resistors.

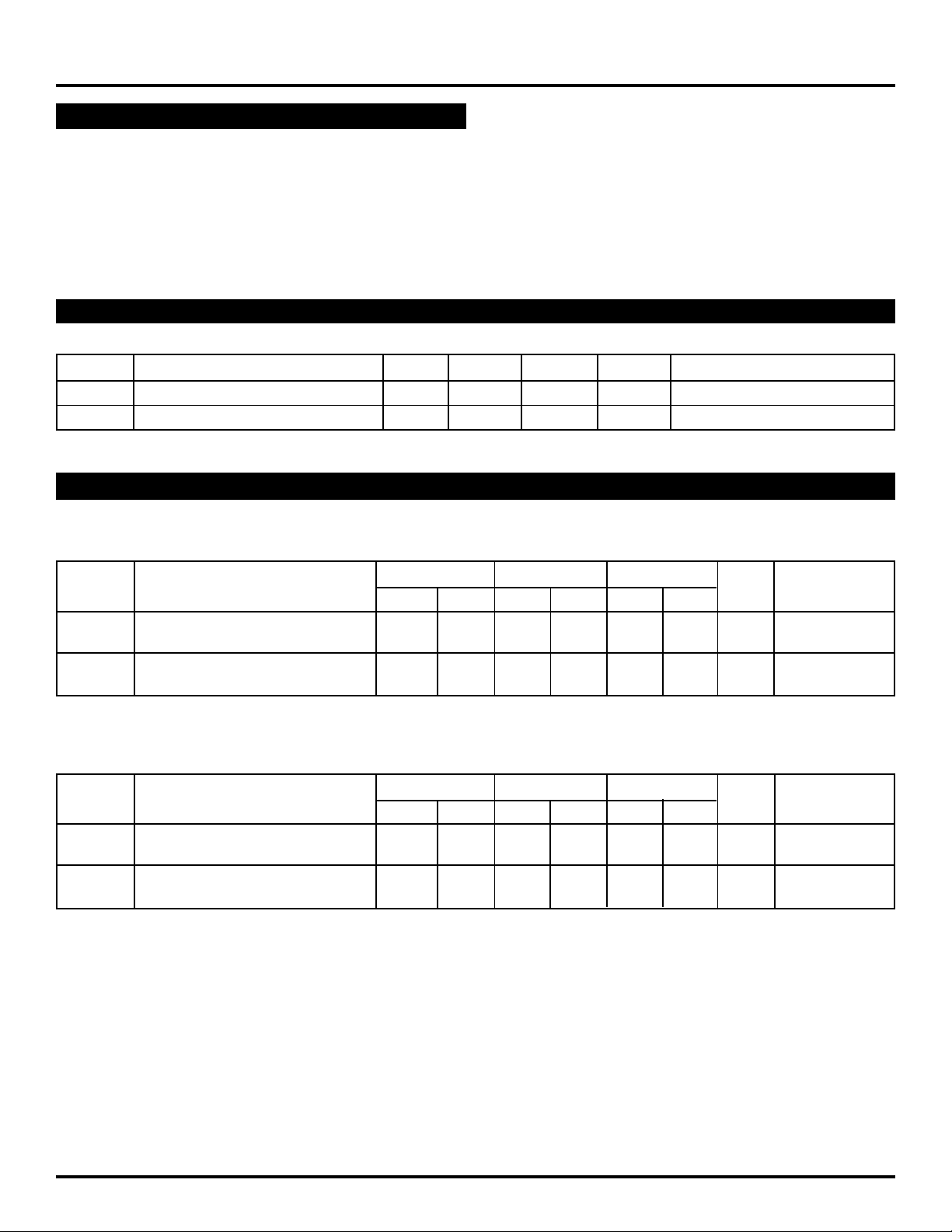

PIN CONFIGURATIONS

D5a

VEESD3a

VEES

D2a

D1a

5

6

O

4

3

O

V

CCA

2

1

VCC

VCC

28

27

D2e

2618

1eD2c

D

25

D4d

D2d

D3d

18

D

D

3c

D

1d

D

3d

1b

D2b

D3b

VEE

VEES

D4b

D1c

D1b

D4a

12

13

14

Top View

15

16

17

PLCC

J28-1

1911201021922823724

D1d

D4c

D3c

1c

D

D

2c

D

3c

D

4c

D

1d

D

2d

D

3d

D

4d

D

1e

D

2e

O

O

PIN NAMES

Pin Function

Dna – Dne Data Inputs (n = 1...5)

O – O Data Outputs

VEES VEE Substrate

CCA VCCO for ECL Outputs

V

Rev.: G Amendment: /0

1

Issue Date: July, 1999

Micrel

LOGIC EQUATION

O = (D1a + D2a + D3a + D4a + D5a)

(D1b + D2b + D3b + D4b)

(D1c + D2c + D3c + D4c)

(D1d + D2d + D3d + D4d)

(D1e + D2e)

DC ELECTRICAL CHARACTERISTICS

VEE = –4.2V to –5.5V unless otherwise specified, VCC = VCCA = GND

Symbol Parameter Min. Typ. Max. Unit Condition

IIH Input HIGH Current, All Inputs ——200 µAVIN = VIH (Max.)

EE Power Supply Current –55 –41 –25 mA Inputs Open

I

AC ELECTRICAL CHARACTERISTICS

SY100S318

CERPACK

VEE = –4.2V to –5.5V unless otherwise specified, VCC = VCCA = GND

TA = 0°CTA = +25°CTA = +85°C

Symbol Parameter Min. Max. Min. Max. Min. Max. Unit Condition

PLH Propagation Delay 300 900 300 900 300 900 ps

t

tPHL Data to Output

t

TLH Transition Time 200 900 200 900 200 900 ps

tTHL 20% to 80%, 80% to 20%

PLCC

VEE = –4.2V to –5.5V unless otherwise specified, VCC = VCCA = GND

TA = 0°CTA = +25°CTA = +85°C

Symbol Parameter Min. Max. Min. Max. Min. Max. Unit Condition

PLH Propagation Delay 300 800 300 800 300 800 ps

t

tPHL Data to Output

TLH Transition Time 200 900 200 900 200 900 ps

t

tTHL 20% to 80%, 80% to 20%

2

Loading...

Loading...