Micrel sy100E222L User Manual

Micrel, Inc.

3.3V, 1.5GHz ÷1/÷2 DIFFERENTIAL

LVECL/LVPECL PROGRAMMABLE CLOCK

GENERATOR AND 1:15 FANOUT BUFFER

FEATURES

■ Four programmable output banks and 15 total

LVPECL-compatible differential outputs

■ Pin-compatible, plug-in replacement to

MC100LVE222FA

■ f

clock = 1.5GHz

MAX

■ 50ps output-to-output skew

■ Four output banks with independent ÷1, ÷2

frequency control

■ 100k compatible I/O

■ Power supply 3.3V ±10%

■ –40°C to +85°C temperature range

■ Available in 52-pin LQFP package

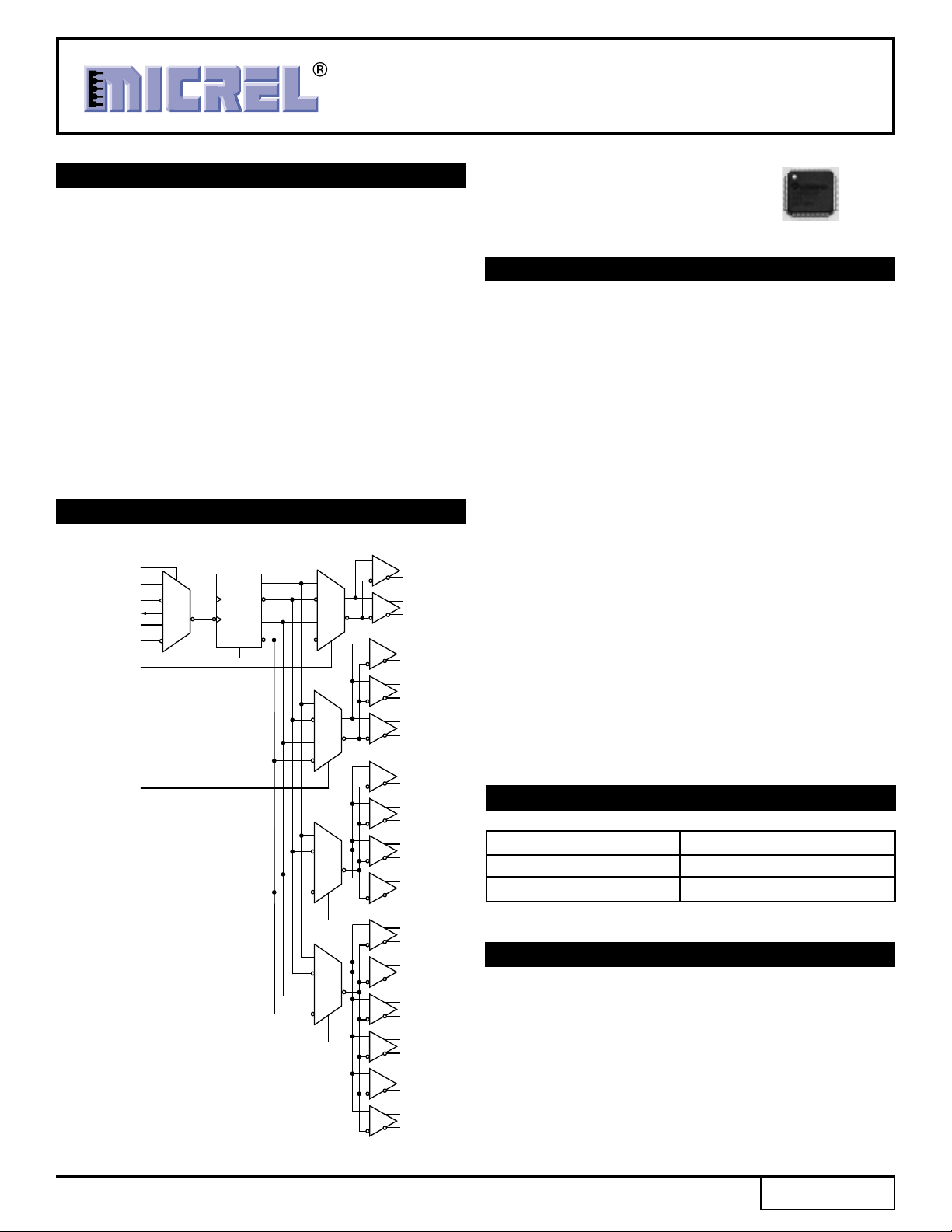

FUNCTIONAL BLOCK DIAGRAM

1:2 FOB

CLK_SEL

CLK0

/CLK0

V

CLK1

/CLK1

MR

FSELA

FSELB

FSELC

FSELD

2:1

BB

MUX

CLK

÷1

÷2

2:1

MUX

2:1

MUX

2:1

MUX

2:1

MUX

1:3 FOB

1:4 FOB

1:6 FOB

QA0

/QA0

QA1

/QA1

QB0

/QB0

QB1

/QB1

QB2

/QB2

QC0

/QC0

QC1

/QC1

QC2

/QC2

QC3

/QC3

QD0

/QD0

QD1

/QD1

QD2

/QD2

QD3

/QD3

QD4

/QD4

QD5

/QD5

Precision Edge

Precision Edge

SY100E222L

®

SY100E222L

Precision Edge

®

DESCRIPTION

The SY100E222L is a low-skew, low-jitter device capable

of receiving a high-speed LVECL/LVPECL input in either a

single-ended or differential configuration. For single-ended

configurations, a VBB output reference is supplied by the

SY100E222L. A 2:1 input multiplexer selects from two

differential input pairs by means of the CLK_SEL input select.

The internal programmable divider for each of the four

banks generates a ÷1 or ÷2 frequency of the selected input.

The ÷1/÷2 divider outputs can be asynchronously

synchronized with the master reset (MR) input so that the

outputs will start out in a known state.

The 15 total outputs are partitioned into four independently

selected output banks in a 2/3/4/6 fanout configuration. Each

of the four banks can independently select the ÷1 or ÷2

output frequency by means of the four separate frequency

select pins (FSELA-FSELD) inputs.

The SY100E222L is pin-for-pin compatible with the

MC100LVE222FA device.

The SY100E222L is part of a Micrel’s Precision Edge

product family. For other integrated clock divider plus fanout

buffer options, consider Micrel’s SY89200 family.

All support documentation can be found on Micrel’s web

site at: www.micrel.com.

CROSS REFERENCE TABLE

Micrel Part Number ON Semiconductor

SY100E222LTI MC100LVE222FA

SY100E222LTI TR MC100LVE222FAR2

APPLICATIONS

■ SONET/SDH channel applications

■ Fibre Channel multi-channel applications

■ Gigabit Ethernet multi-channel applications

®

®

Precision Edge is a registered trademark of Micrel, Inc.

M9999-111605

hbwhelp@micrel.com or (408) 955-1690

1

Rev.: B Amendment: /0

Issue Date: November 2005

Micrel, Inc.

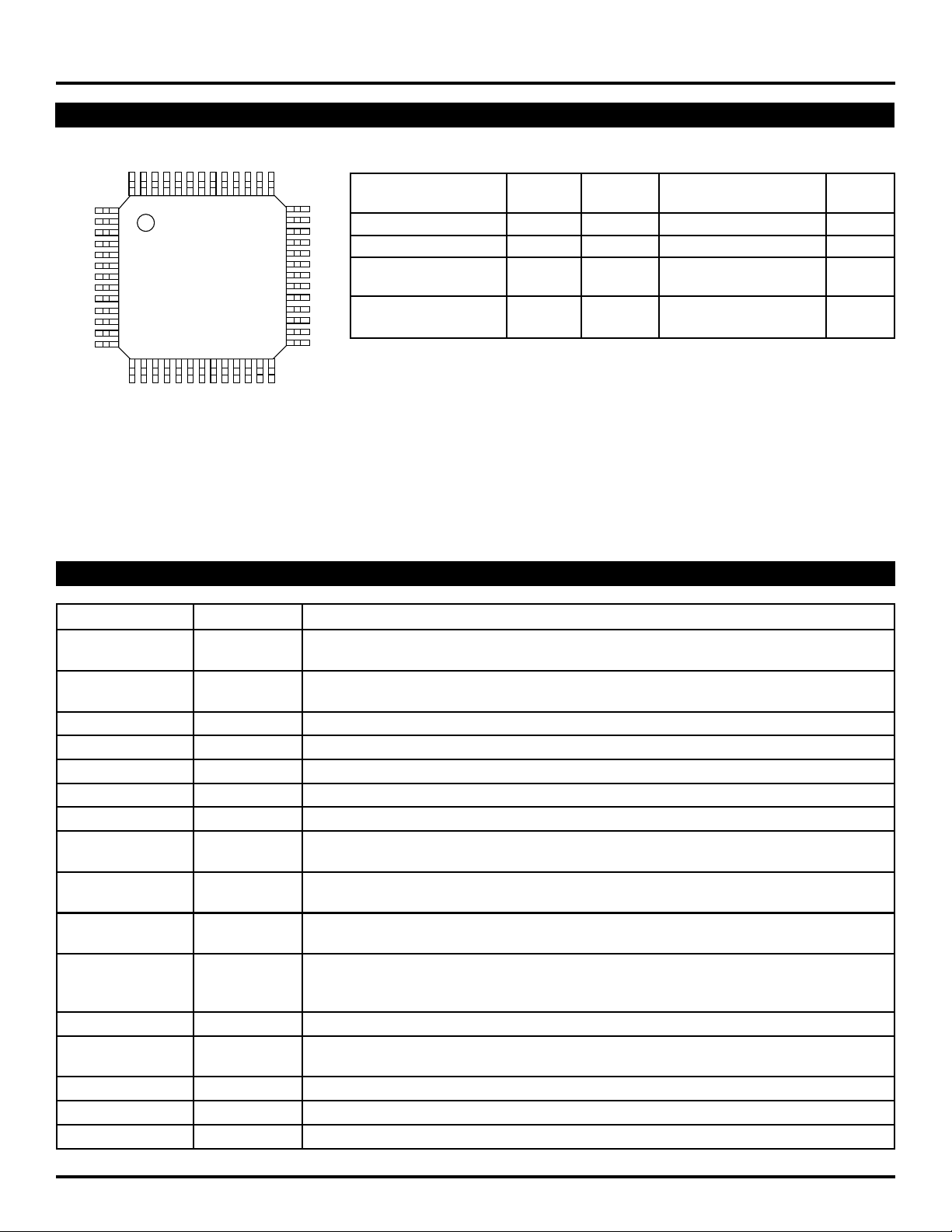

PACKAGE/ORDERING INFORMATION

Precision Edge

SY100E222L

®

VCCO

QA0

/QA0

QA1

/QA1

VCC

FSELA

FSELB

CLK0

/CLK0

CLK_SEL

CLK1

/CLK1

VBB

FSELC

FSELD

VEE

MR

52 51 50 49 48 47 46 45 44 43 42 41 40

1

2

3

4

5

6

7

8

9

10

11

12

13

14 15 16 17 18 19 20 21 22 23 24 25 26

QD5

QD4

/QD5

/QD4

VCCO

52-Pin LQFP (LQFP-52)

PIN DESCRIPTION

VCCO

/QD3

QB0

QD3

/QB0

/QD2

QB1

QD2

/QB1

/QD1

QB2

QD1

/QB2

/QD0

VCCO

39

38

37

36

35

34

33

32

31

30

29

28

27

QD0

Ordering Information

(1)

Package Operating Package Lead

Part Number Type Range Marking Finish

VCCO

QC0

SY100E222LTI LQFP-52 Industrial SY100E222L Sn-Pb

/QC0

QC1

SY100E222LTITR

/QC1

QC2

SY100E222LTY

/QC2

QC3

/QC3

VCCO

SY100E222LTYTR

NC

NC

VCCO

Notes:

1. Contact factory for die availability. Dice are guaranteed at TA = 25°C, DC Electricals only.

2. Tape and Reel.

3. Pb-Free package is recommended for new designs.

(3)

(2)

LQFP-52 Industrial SY100E222L Sn-Pb

LQFP-52 Industrial SY100E222L with Matte-Sn

Pb-Free bar-line indicator Pb-Free

(2, 3)

LQFP-52 Industrial SY100E222L with Matte-Sn

Pb-Free bar-line indicator Pb-Free

Pin Number Pin Name Pin Function

2 MR 100k ECL compatible: Master reset function resets all outputs to a differential LOW when

MR pin goes HIGH.

5, 6, CLK0, /CLK0, Differential inputs: These input pairs are the differential signal inputs to the device. Inputs

8, 9 CLK1, /CLK1 accept 100k LVPECL/LVECL levels.

7 CLK_SEL 100k ECL compatible input select. LOW = CLK0, HIGH= CLK1.

3 FSELA 100k ECL compatible bank A output select. LOW: QA0-QA1 = ÷1, HIGH: QA0-QA1 = ÷2.

4 FSELB 100k ECL compatible bank B output select. LOW: QB0-QB2 = ÷1, HIGH: QB0-QB2 = ÷2.

11 FSELC 100k ECL compatible bank C output select. LOW: QC0-QC3 = ÷1, HIGH: QC0-QC3 = ÷2.

12 FSELD 100k ECL compatible bank D output select. LOW: QD0-QD5 = ÷1, HIGH: QD0-QD5 = ÷2.

51, 49, QA0 – QA1, Bank A 100k differential output pairs controlled by FSELA.

50, 48 /QA0 – /QA1 FSELA: LOW, QA = ÷1, HIGH, QA = ÷2.

46, 44, 42, QB0 – QB2, Bank B 100k differential output pairs controlled by FSELB.

45, 43, 41 /QB0 – /QB2 FSELB: LOW, QB = ÷1, HIGH, QB = ÷2.

38, 36, 34, 32, QC0 – QC3, Bank C 100k differential output pairs controlled by FSELC.

37, 35, 33, 31 /QC0 – /QC3 FSELC: LOW, QC = ÷1, HIGH, QC = ÷2.

26, 24, 22, 20, QD0 – QD5, Bank D 100k differential output pairs controlled by FSELD.

18, 16, 25, 23, /QD0 – /QD5 FSELD: LOW, QD = ÷1, HIGH, QD = ÷2.

21, 19, 17, 15

1 VCC Positive power supply: Bypass with 0.1µF0.01µF low ESR capacitors.

14, 27, 30, 39, VCCO Positive power supply for output buffers. Bypass with 0.1µF0.01µF low ESR capacitors.

40, 47, 52

13 VEE Negative power supply. For LVPECL systems, VEE is GND.

10 VBB Reference voltage.

28, 29 NC No connect: Not internally connected (unused pins).

M9999-111605

hbwhelp@micrel.com or (408) 955-1690

2

Loading...

Loading...