MICREL SY10E131, SY100E131 Datasheet

4-BIT D

FLIP-FLOP

SY10E131

SY100E131

FEATURES

■ 1100MHz min. toggle frequency

■ Extended 100E VEE range of –4.2V to –5.5V

■ Differential output

■ Individual and common clocks

■ Indivldual asynchronous reset

■ Paired asynchronous sets

■ Fully compatible with Industry standard 10KH,

100K ECL levels

■ Internal 75KΩ input pulldown resistors

■ Fully compatible with Motorola MC10E/100E131

■ Available in 28-pin PLCC package

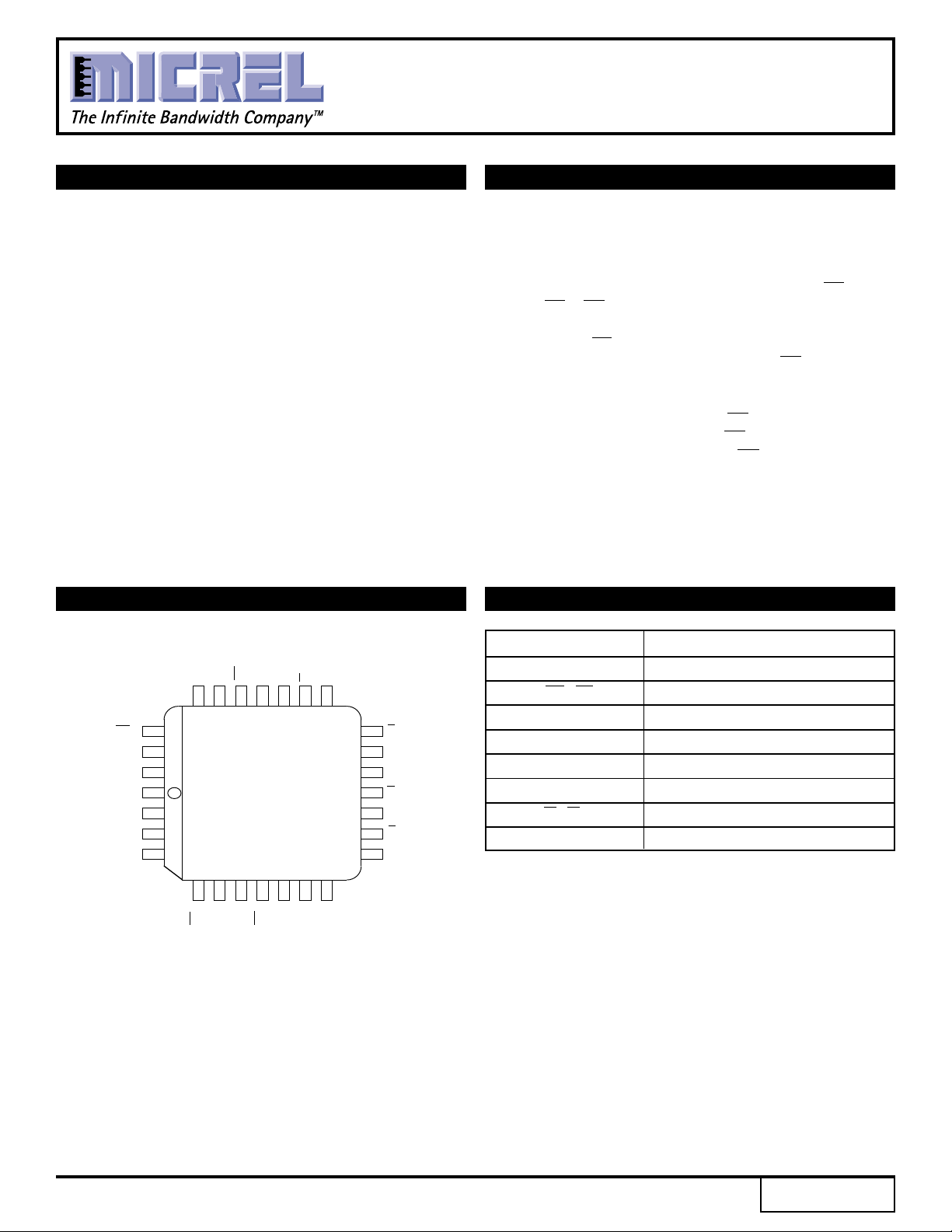

PIN CONFIGURATION

DESCRIPTION

The SY10/100E131 are high-speed quad master slave

D-type flip-flops with differential outputs designed for use

in new, high-performance ECL systems. The flip-flops may

be individually clocked by holding CC (Common Clock) at

a logic LOW and then using the four individual CE (Clock

Enable CE0–CE3) inputs to accomplish such clocking.

Alternatively, all four flip-flops can be clocked in common

by holding the CE inputs LOW and then using CC to clock

the data. In the common clock mode, the CE input acts as

a control that passes the CC signal to the flip-flop. Data is

clocked into the flip-flop on the rising edge of the output of

the logical OR operation between CE and CC (data enters

the master when both CC and CE are LOW and data

transfers to the slave when either CE or CC, or both, go

HIGH).

Asynchronous set and reset controls are provided. The

reset controls are individual and the set controls are

pairwise.

PIN NAMES

CE

S

V

C

S

2

3

2

R

CE

D

3

3

CCO

2

V

Q

R

Q

D0-D3 Data Inputs

CE0-CE3 Clock Enables (Individual)

Pin Function

25 24 23 22 21 20 19

NC

CCO

V

18

Q

2

17

Q

2

16

V

CC

15

Q

1

14

Q

1

Q

13

12

0

Q

0

26

3

D

3

27

12

28

EE

1

C

2

03

3

4

D

0

567891011

0

CE

PLCC

TOP VIEW

J28-1

1

0

D

R

1

CE

1

R

R0-R3 Resets

CC Common Clock

S03, S12 Sets (paired)

Q0-Q3 True Outputs

Q0-Q3 Inverting Outputs

CCO VCC to Output

V

Rev.: E Amendment: /0

1

Issue Date: November, 1998

Micrel

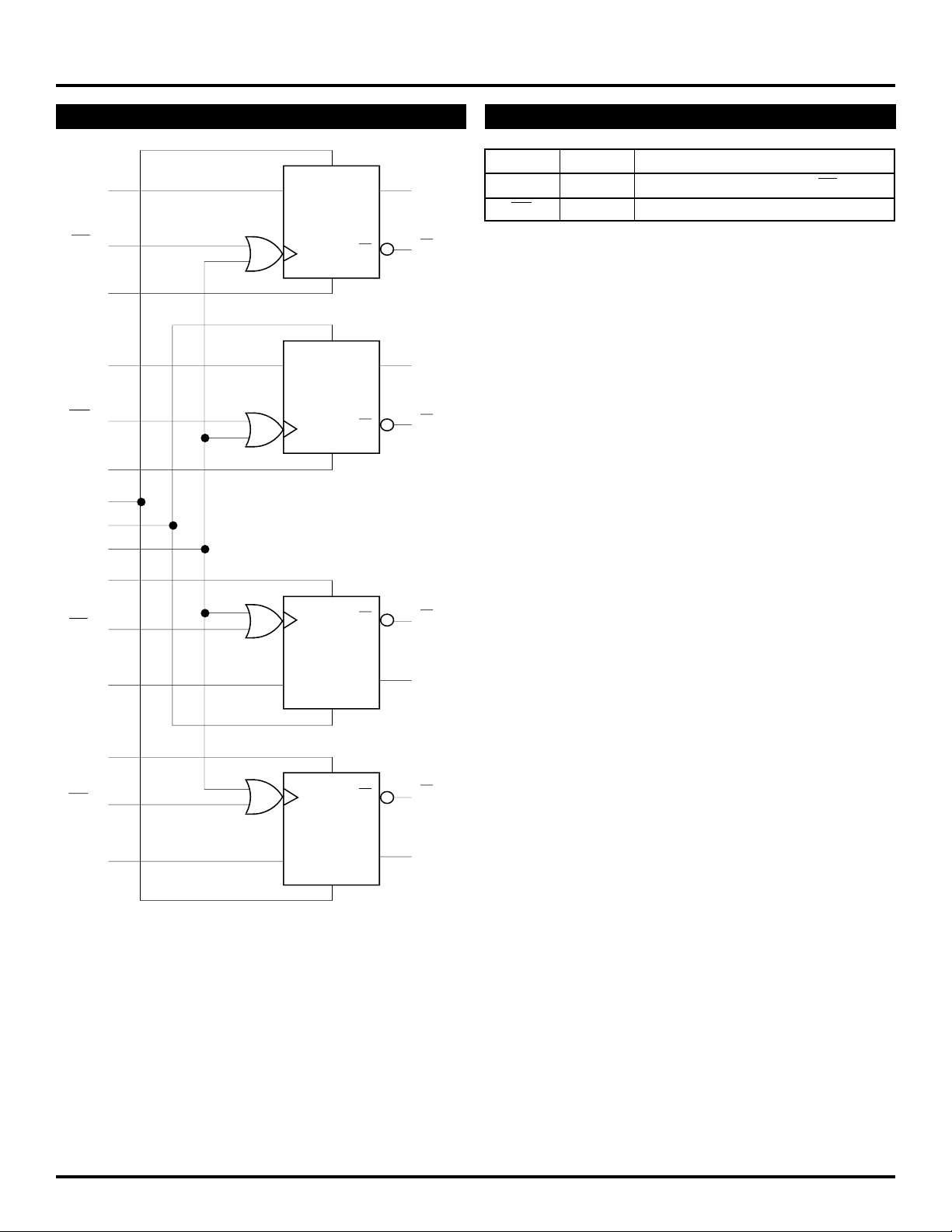

BLOCK DIAGRAM TRUTH TABLE

Pin State Mode

CE

D

CE

S

S

S

D

3

3

D

Q

Q

Q3

Q3

R

R

3

S

2

2

D

Q

Q

Q2

Q2

R

R

2

03

12

CC L Individual clocking with CEn

CE L Common clocking with CC

SY10E131

SY100E131

C

CE

CE

C

R

1

R

1

D

1

D

Q

Q

Q1

Q1

S

R

0

R

0

0

D

D

Q

Q

Q0

Q0

S

2

Loading...

Loading...