MICREL MIC8030-01CV Datasheet

MIC8030 Micrel

MIC8030

High-Voltage Display Driver

General Description

The MIC8030 is a CMOS high voltage liquid crystal display

driver. Up to 38 segments can be driven from four CMOS level

inputs (CLOCK, DATA IN, LOAD and CHIP SELECT). The

MIC8030 is rated at 50V. Data is loaded serially into a shift

register, and transferred to latches which hold the data until

new data is received.

The backplane can be driven from external source, or the

internal oscillator can be used. If the internal oscillator is

used, the frequency of the backplane will be determined by an

external resistor and capacitor. The oscillator need not be

used if a DC output is desired.

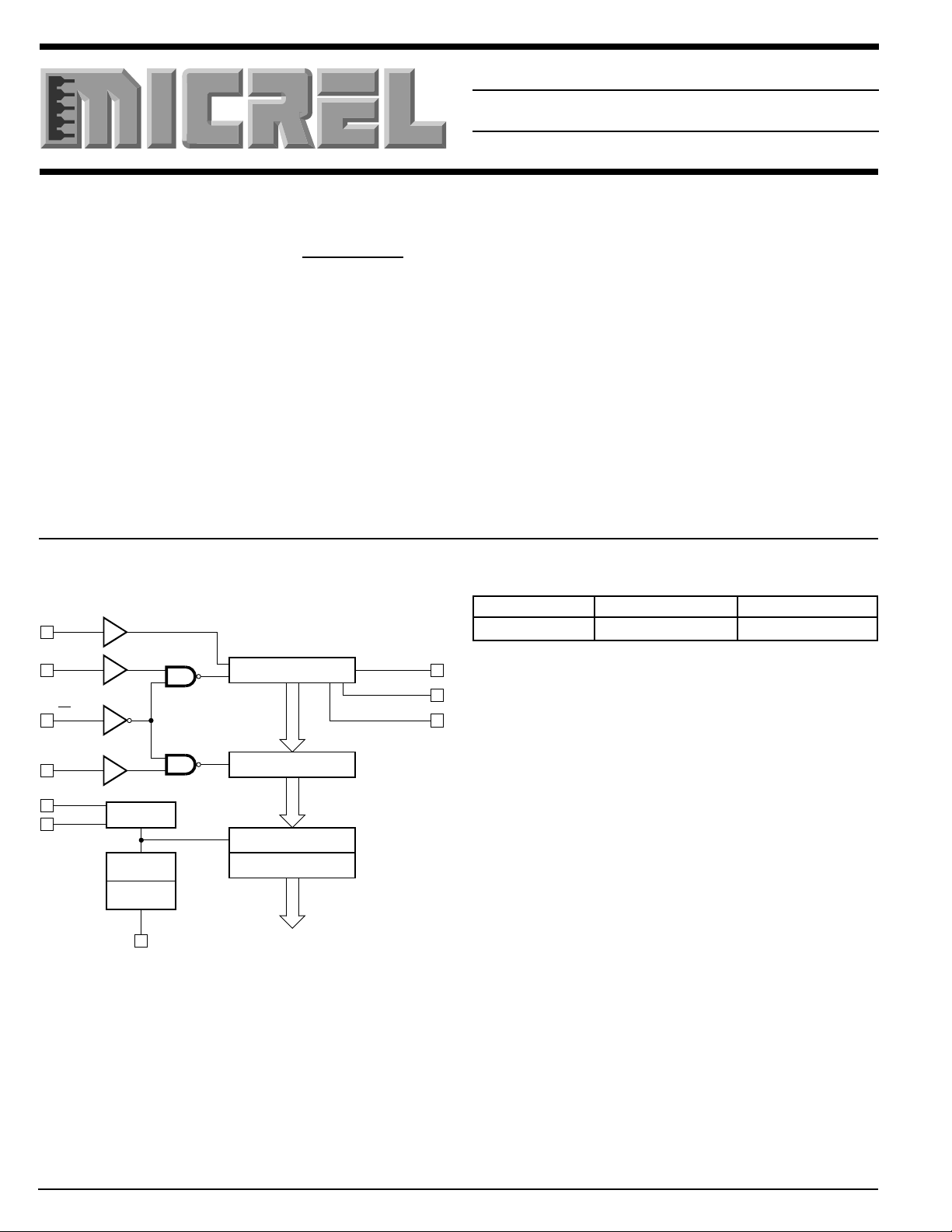

Functional Diagram

Data

S

Features

• High Voltage Outputs capable of a driving up to 100 volt

outputs from 5 to 15 volt logic

• Drives 30, 32, or 38 segments

• Cascadable

• On chip Oscillator or External Backplane Input

• CMOS construction for wide supply range and low

power consumption

• Schmitt Triggers on all inputs

• CMOS, PMOS, and NMOS compatible

Applications

• Dichroic and Standard Liquid Crystal Displays

• Flat Panel Displays

• Print Head Drives

• Vacuum Fluorescent Displays

Ordering Information

Part Number Temperature Range Package

MIC8030-01CV 0°C to +70°C 44-pin PLCC

Clock

CS

Load

LCD0

LCD0 Opt

S

S

S

Oscillator

Voltage

Translator

HV Output

Driver

Back Plane

38 Bit Static Shift Register

38 Bit Latch

Voltage Translators

HV Output Drivers

Segments

Data Out 38

Data Out 32

Data Out 30

MIC8030 8-16 October 1998

MIC8030 Micrel

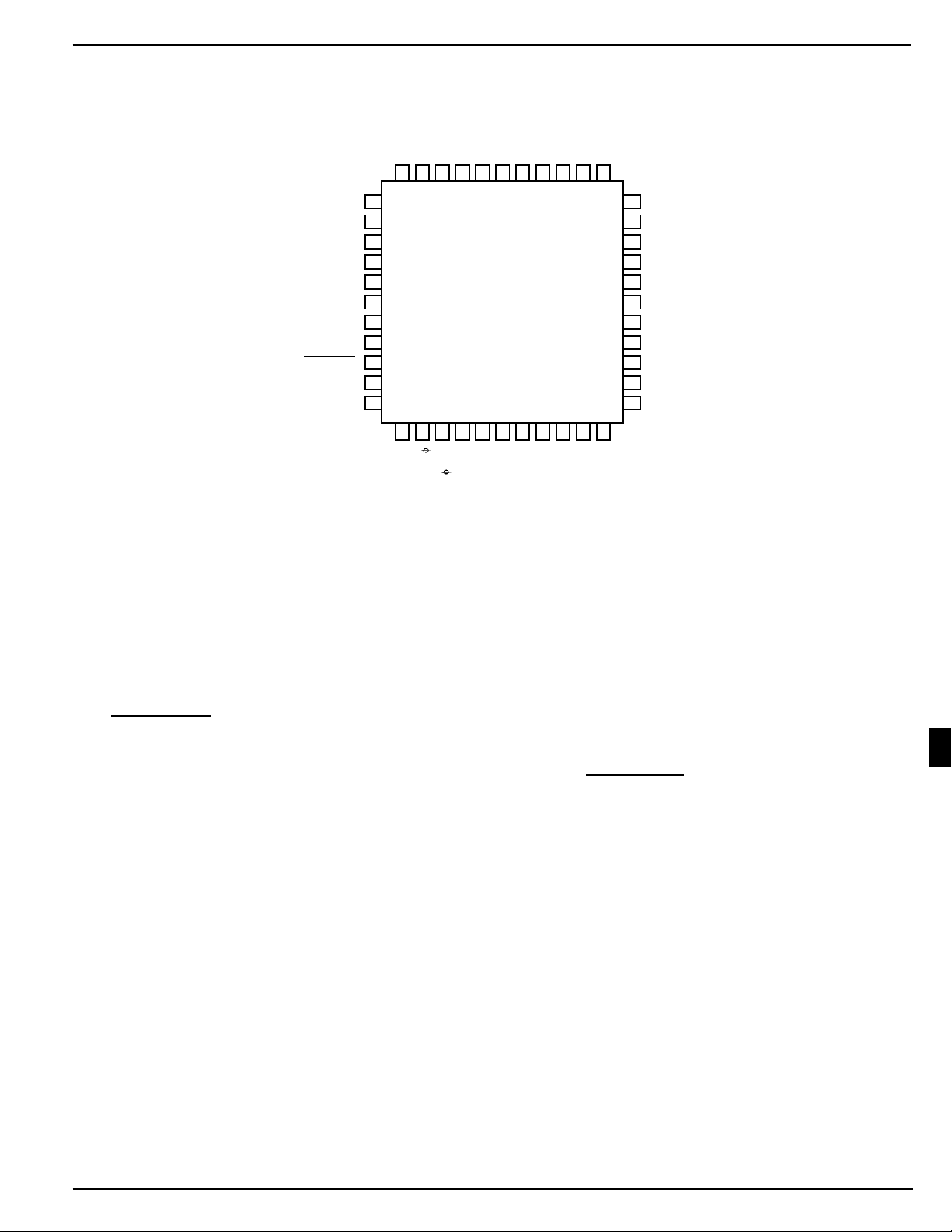

1

2

3

4

5

6

7

444342

41

8

Seg 20

MIC8030-01

9

10

11

12

13

14

15

16

17

18192021222324

4028

27

26

25

Chip Select

Data In

LCD

LCD Opt.

Seg 2

Seg 3

Seg 21

Seg 22

Seg 23

Seg 24

Seg 25

Seg 28

Seg 29

Seg 30

Seg 31

Seg 32

SS

V

CC

V

Data Out 32

Back Plate

Seg 17

Seg 16

Seg 15

Seg 14

Seg 13

Seg 12

Seg 11

Seg 10

Seg 9

Seg 8

Seg 7

Seg 6

Seg 5

Seg 4

BB

V

Seg 19

N/C

Seg 18

39

38

37

36

35

34

33

32

31

30

29

Seg 1

Clock

Load

Seg 27

Seg 26

Pin Configuration

44-Pin PLCC (-V)

Functional Description

With CHIP SELECT tied low, serial data is clocked into the

shift register at each falling edge of the CLOCK input. Pulling

LOAD high will cause a parallel loading of the shift register

contents into the latches. If load is left high, the latches are

transparent.

A logic “1” clocked into the shift register corresponds to that

segment being on, and that segment is out of phase with the

backplane.

The backplane may be externally driven or the internal

oscillator can be used. If LCDφ is externally driven, the

backplane will be in phase with the input; LCDφ OPT is not

connected. The internal oscillator is used by shorting LCDφ

OPT to LCDφ, connecting a capacitor to ground, and a

resistor to VCC. The frequency of the backplane will be 1/256

of the input frequency, and is given as: f = 10/[R(C + .0002)]

at VDD = 5V, R in kΩ, C in µF.

Example: R = 150 kΩ, C = 420 pF: f = 108 Hz

For displays with more than 38 segments, two or more

MIC8030 may be cascaded by connecting DATA OUT of the

previous stage with DATA IN of the next stage; CLOCK,

LOAD and CHIP SELECT of all following stages should be

tied to the control lines of the first MIC8030. The backplane

output of the first stage should be tied to LCDφ of all following

stages, the LCDφ OPT must be left unconnected on those

stages. If the internal oscillator is used, and VBB > 50V then

an external 330 kΩ resistor must be used between the

BACKPLANE of the first stage and LCDφ of all following

stages.

Packaging options available include DATA OUT 30, 32 or 38

with the corresponding number of segments, and the availability of LCDφ OPT. Types of packages include plastic and

ceramic DIPs, surface mount packages, plastic and ceramic

Leadless Chip Carriers and custom packaging.

8

October 1998 8-17 MIC8030

Loading...

Loading...