MICREL MIC74BQS Datasheet

MIC74 Micrel

MIC74

2-Wire Serial I/O Expander and Fan Controller

Advance Information

General Description

The MIC74 is a fully programmable serial-to-parallel I/O

expander compatible with the SMBus™ (system management bus) protocol. It acts as a “slave” on the bus, providing

eight independent I/O lines.

Each I/O bit can be individually programmed as an input or

output. If programmed as an output, each I/O bit can be

programmed as an open-drain or complementary push-pull

output. If desired, the four most significant I/O bits can be

programmed to implement fan speed control. An internal

clock generator and state machine eliminate the overhead

generally associated with “bit-banging” fan speed control.

Programming the device and reading/writing the I/O bits is

accomplished using seven internal registers. All registers can

be read by the host. Output bits are capable of directly driving

high-current loads such as LEDs. A separate interrupt output

can notify the host of state changes on the input bits without

requiring the MIC74 to perform a transaction on the serial bus

or be polled by the host. Three address selection inputs are

provided, allowing up to eight devices to share the same bus

and provide a total of 64 bits of I/O.

The MIC74 is available in an ultra-small-footprint 16-lead

QSOP. Low quiescent current, small footprint, and low package height make the MIC74 ideal for portable and desktop

applications.

Features

• Provides eight bits of general purpose I/O

• Built in fan speed control logic (optional)

• 2-wire SMBus™/I2C™ compatible serial interface

plus interrupt output

• 2.7V to 3.6V operating voltage range

• 5V-tolerant I/O

• Low quiescent current: 2µA (typical)

• Bit-programmable I/O options:

input or output

push-pull or open-drain output

interrupt on input changes

• Outputs can directly drive LEDs (10mA IOL)

• Up to 8 devices per bus

Applications

• General purpose I/O expansion via serial bus

• Personal computer system management

• Distributed sensing and control

• Microcontroller I/O expansion

• Fan Control

Ordering Information

Part Number Temperature Range Package

MIC74BQS –40°C to +85°C 16-lead QSOP

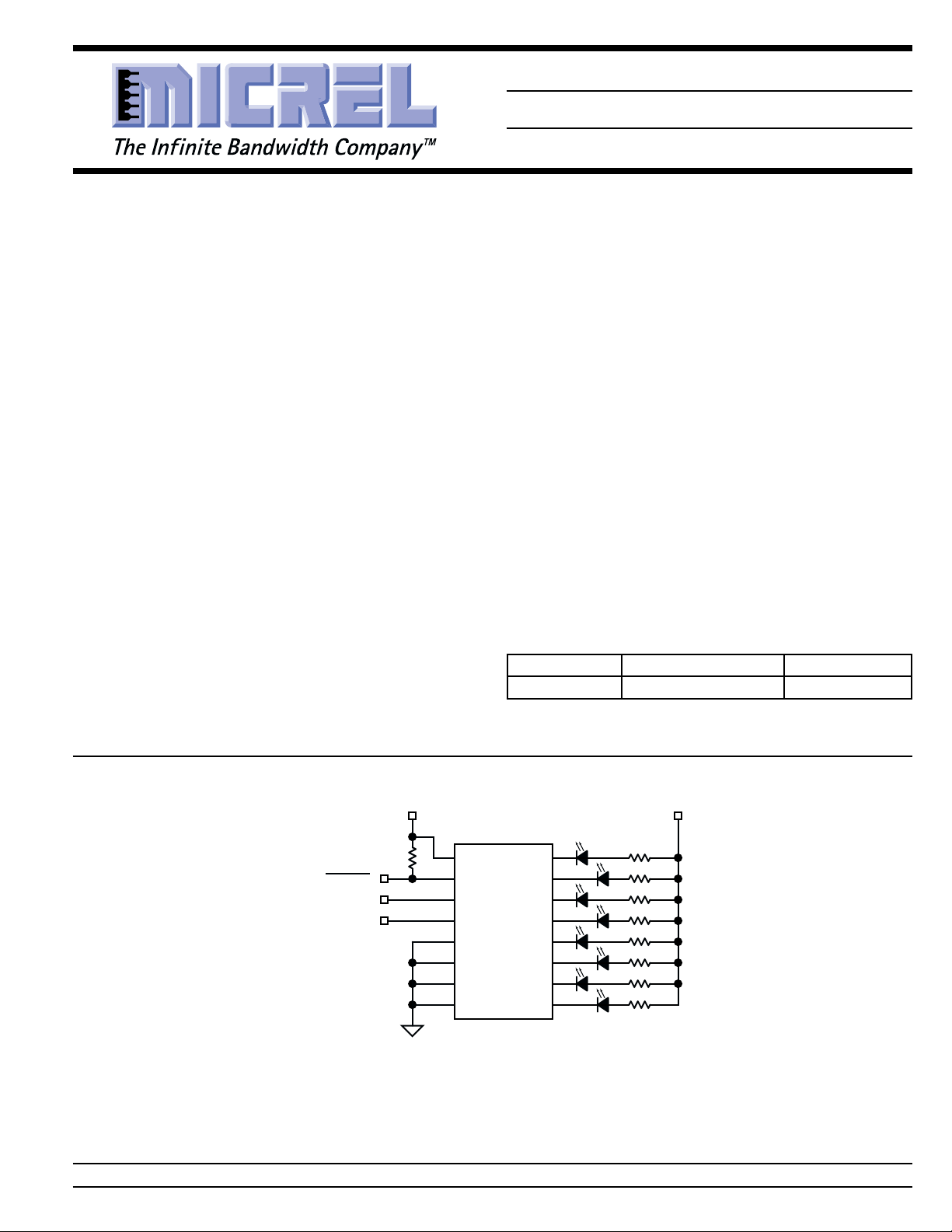

Typical Application

3.0V3.0V

MIC74

R9

ALERT

DATA

CLK

VDD

/ALERT

DATA

CLK

A0

A1

A2

GND

P0

P1

P2

P3

P4

P5

P6

P7

LED8

Serial-Bus-Controlled LED Annunciator

SMBus™ is a trademark of Intel Corporation. I2C™ is a trademark of Phillips Electronics N.V.

Micrel, Inc. • 1849 Fortune Drive • San Jose, CA 95131 • USA • tel + 1 (408) 944-0800 • fax + 1 (408) 944-0970 • http://www.micrel.com

August 1, 2000 1 MIC74

R1LED1

R2

R3

R4

R5

R6

R7

R8

MIC74 Micrel

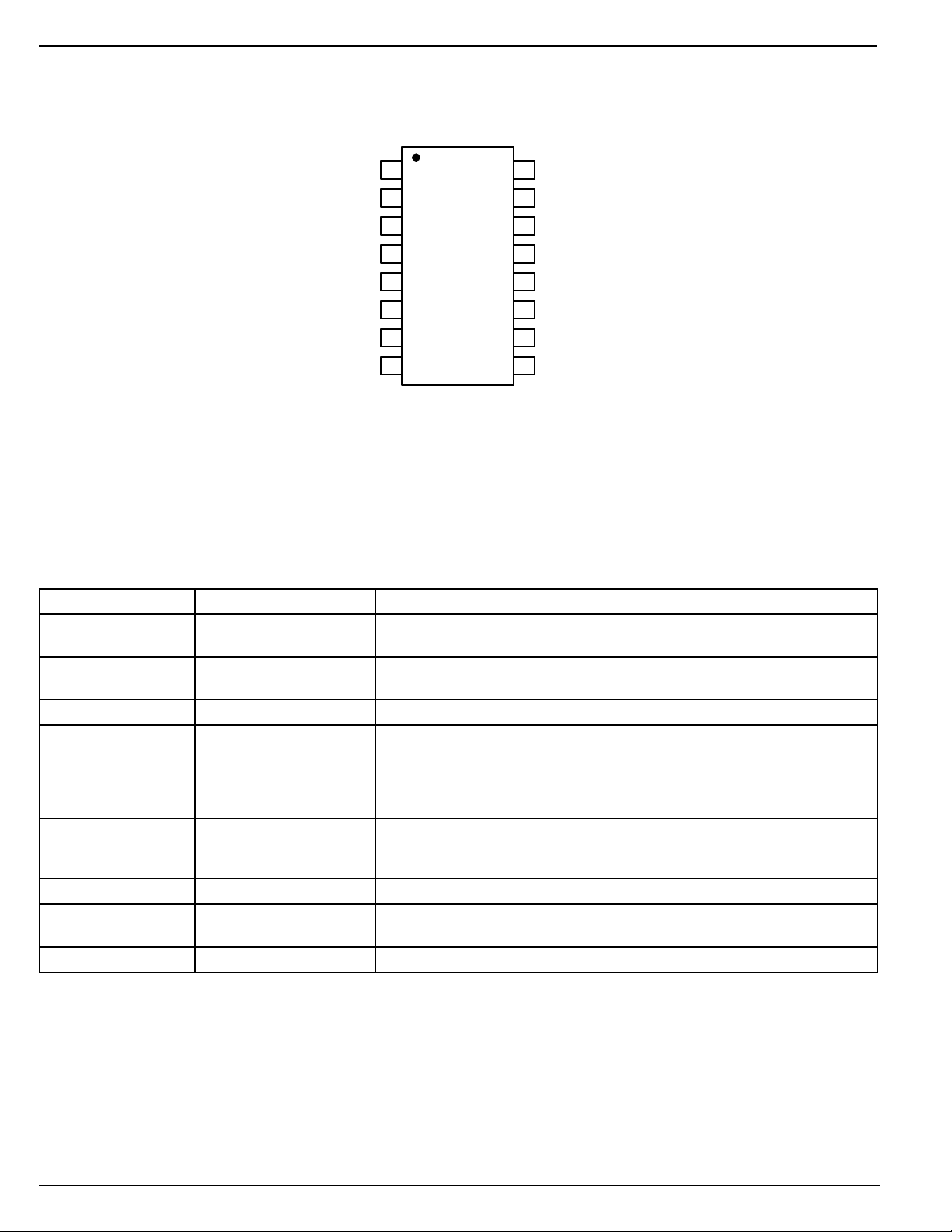

Pin Configuration

A1

A2

P0

P1

P2

P3

GND

Pin Description

Pin Number Pin Name Pin Function

1–3A0–A2 Address (Input): Slave address selection inputs; sets the three least signifi-

4–7P0–P3 Parallel I/O (Input/Output): General-purpose I/O pin. Direction and output

8 GND Ground

9–12

13 /ALERT Interrupt (Output): Active-low, open-drain output signals input-change-

14 CLK Serial Bus Clock (Input): The host provides the serial bit clock in this input.

15 DATA Serial Data (Input/Output): Serial data input and open-drain serial data

16 VDD Power Supply (Input.)

P4–P7 (/SHDN, /FS0–/FS2)

1A0

2

3

4

5

6

7

8

16 VDD

DATA

15

CLK

14

/ALERT

13

P7 (/FS2)

12

P6 (/FS1)

11

P5 (/FS0)

10

P4 (/SHDN0)

9

16-Lead QSOP

cant bits of the MIC74’s slave address.

type are user programmable.

Parallel I/O (Input/output): P4–P7 are general-purpose I/O pins. Direction

and output type are user programmable.

Shutdown (Output): When the FAN bit is set, pin 9 becomes SHDN.

Fan Speed (Output): When the FAN bit is set, pins 10 through 12 become /

FS0–/FS2 respectively, controlled by the FAN_SPEED register.

interrupts to the host on this pin. Signal is cleared when the bus master

(host) polls the ARA (alert response address = 0001 100) or reads status.

output.

MIC74 2 August 1, 2000

MIC74 Micrel

Absolute Maximum Ratings (Note 1)

Supply Voltage (V

Input Voltage

VDD and GND]

Junction Temperature (T

) .................................................+4.6V

DD

[all pins except

(VIN) ........................ GND – 0.3V to 5.5V

) ...................................... +150°C

J

Operating Ratings (Note 2)

Supply Voltage (V

Ambient Temperature (T

Package Thermal Resistance ............................... 163°C/W

) .................................. +2.7V to +3.6V

DD

) ......................... –40°C to +85°C

A

Lead Temperature (10 sec.).................................... +260°C

ESD Rating, Note 3

V

...........................................................................................

DD

1.5kV

A0,A1,A2 .................................................................500V

Others ..................................................................... 200V

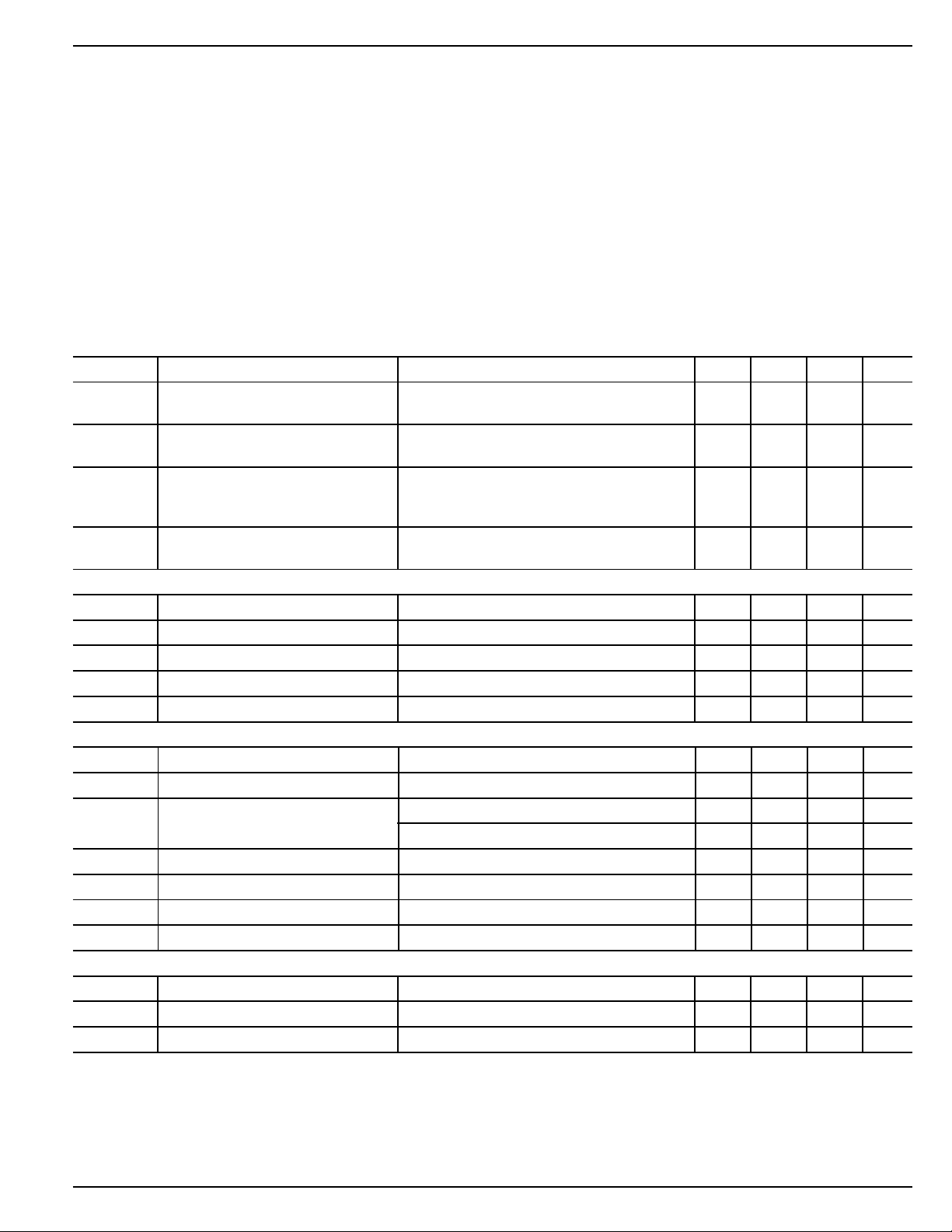

Electrical Characteristics

2.7V ≤ VDD ≤ 3.6V; TA = 25°C, bold values indicate –40°C ≤ TA ≤ +85°C; unless noted.

Symbol Parameter Condition Min Typ Max Units

V

IN

I

DD

I

START

I

STBY

Serial I/O (DATA, CLK)

V

IL

V

IH

V

OL

I

LEAK

C

IN

Parallel I/O [P0–P3, P4(/SHDN), P5(/FS0)–P7(/FS2)]

V

IL

V

IH

I

OL

I

OH

I

LEAK

C

IN

C

OUT

Address Input (A0–A2)

V

IL

V

IH

I

LEAK

Input Voltage, any pin except

GND–0.3

5.5 V

VDD and GND

Operating Supply Current P[7:0] inputs; P[7:0] = VDD or GND 2 6 µA

/ALERT open; f

Fan Startup Supply Current during t

(Fan Mode Only) /FS2[2:0] = open; V

START;

= 100kHz

CLK

/ALERT, /SHDN, 1.75 mA

SMBCLK

= V

SMBDATA

= VDD;

P[3:0] = inputs

Standby Supply Current /ALERT = open, V

SMBCLK

= V

SMBDATA

= VDD;13µA

P[3:0] = inputs

Input Low Voltage –0.3 0.8 V

Input High Voltage 2.0 5.5 V

Output Low Voltage IOL = 3mA 0.4 V

Leakage Current VIN = 5.5V or GND –1+1µA

Input Capacitance 10 pF

Input Low Voltage –0.5 0.8 V

Input High Voltage 2 5.5 V

Output Low Current VOL = 0.4V, VDD = 2.7V 7 mA

VOL = 1V, VDD = 3.3V 10 mA

Output High Current VOH = 2.4V 7 mA

Leakage Current VIN = 5.5V or GND –1+1µA

Input Capacitance 10 pF

Output Capacitance 10 pF

Input Low Voltage –0.3 0.3V

Input High Voltage 0.7V

Leakage Current VIN = V

or GND –250 +250 nA

DD

DD

VDD+0.3

DD

V

V

August 1, 2000 3 MIC74

MIC74 Micrel

Symbol Parameter Condition Min Typ Max Units

/ALERT

V

OL

I

LEAK

AC Characteristics

t

START

t

PULSE

t

/INT

t

/IR

t

HD:STA

t

SU:STA

t

SU:STO

t

HD:DAT

t

SU:DAT

t

TIMEOUT

t

LOW

t

HIGH

t

F

t

R

t

BUF

Output Low Voltage IOL = 1mA 0.4 V

Leakage Current VIN = V

DD

or V

SS

–1 ±250 +1 µA

Fan Startup Interval normal operation 0.5 1 3.3 sec

Minimum Pulse-Width minimum pulse-width on Pn to 10 ns

generate an interrupt, Note 7

Interrupt Delay interrupt delay from state change 4 µs

on Pn to /ALERT ≤ VOL, Note 7

Delay from Status Read or ARA 4 µs

Response to /ALERT ≥ V

OH

Hold Time, Note 7 hold time after repeated start condition. 4.0 µs

after this period, the first clock is generated.

Setup Time, Note 7 repeated start condition setup time 4.7 µs

Stop Condition Setup Time Note 7 4.0 µs

Data Hold Time Note 7 500 ns

Data Setup Time Note 7 0ns

Clock Low Time-Out Notes 4, 7 25 35 ms

Clock Low Period Notes 5, 7 4.7 µs

Clock High Period Notes 5, 7 4.0 50 µs

Clock/Data Fall Time Notes 6, 7 300 ns

Clock/Data Rise Time Notes 6, 7 1000 ns

Bus free time between stop and Note 7 4.7 µs

Start condition

Note 1. Exceeding the absolute maximum rating may damage the device.

Note 2. The device is not guaranteed to function outside its operating rating.

Note 3. Devices are ESD sensitive. Handling precautions recommended. Human body model, 1.5k in series with 100pF.

Note 4. Devices participating in a transfer will timeout when any clock low exceeds the value of t

Note 5. t

Note 6. Rise and fall time is defined as follows: tR = V

Note 7. Guaranteed by design.

timeout condition must reset the communication no later than t

both a master and a slave as it incorporates the cumulative stretch limit for both a master (10ms) and a slave (25ms).

HIGH(max)

provides a simple guaranteed method for devices to detect bus idle conditions.

– 0.15V to V

IL(max)

TIMEOUT(max)

IH(min)

of 35ms. The maximum value specified must be adhered to by

+ 0.15V; tF = 0.9VDD to V

TIMEOUT(min)

of 25ms. Devices that have detected a

– 0.15V.

IL(max)

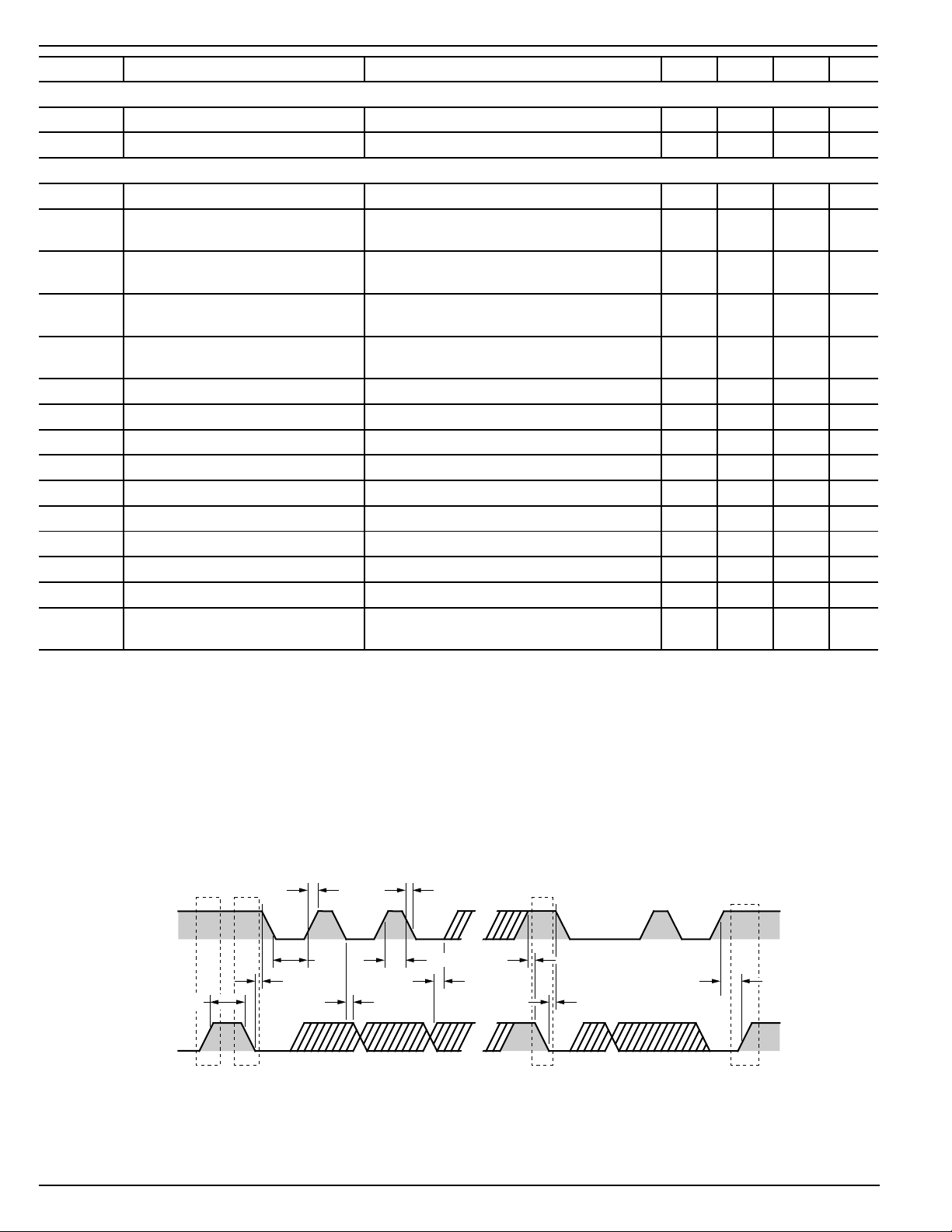

Timing Definitions

CLK

DATA

t

R

t

LOW

t

HD:STA

t

BUF

t

HD:DAT

StoP StoPStart Start

t

F

t

SU:DAT

t

HIGH

t

SU:STA

t

HD:STA

t

SU:STO

MIC74 4 August 1, 2000

MIC74 Micrel

Register Descriptions

Device Configuration Register

GFC_VED

]7[D]6[D]5[D]4[D]3[D]2[D]1[D]0[D

.orezsaetirwsyawlANAFEI

Power-On Default Value: 0000 0000b, 00

h

Interrupts disabled

Not in Fan Mode

Command_byte addess: 0000 0000b, 00

h

Type: 8-bits, read/write

Bit Name: IE

Function: Global interrupt enable.

Operation: 1 = enabled

0 = disabled

Bit Name: FAN

Function: Selects Fan Mode

(P[7:4] vs. /FS[2:0], /SHDN)

Operation: 1 = Fan Mode

0 = I/O Mode

Output Configuration Register

GFC_TUO

]7[D]6[D]5[D]4[D]3[D]2[D]1[D]0[D

7TUO6TUO5TUO4TUO3TUO2TUO1TUO0TUO

Power-On Default Value: 0000 0000b, 00

h

all outputs open-drain

Command_byte addess: 0000 0010b, 02

h

Type: 8-bits, read/write

Bit Name: OUT

n

Function: Selects output driver configuration of Pn when

Pn is configured as an output.

Operation: 1 = push-pull

0 = open-drain

Notes: If Fan Mode is selected, that is, the FAN bit of

the DEV_CFG register is set to one, P[7:4] are

automatically configured as open-drain

outputs. They are then referred to as /FS[2:0]

and /SHDN. The OUT_CFG register has no

effect on these I/O bits while in Fan Mode.

Bit Name: D[2] through D[6]

Function: Reserved

Operation: Reserved—always write as zero

Data Direction Register

RID

]7[D]6[D]5[D]4[D]3[D]2[D]1[D]0[D

7RID6RID5RID4RID3RID2RID1RID0RID

Power-On Default Value: 0000 0000b, 00

h

all Pn’s configured as inputs

Command_byte addess: 0000 0001b, 01

h

Type: 8-bits, read/write

Bit Name: DIR

Function: Selects data direction, input or output, of P

n

n

Operation: 1 = output

0 = input

Notes: If Fan Mode is selected, that is, the FAN bit of

the DEV_CFG register is set to one, P[7:4] are

automatically configured as open-drain

outputs. They are then referred to as /FS[2:0]

and /SHDN. The DIR register has no effect on

these I/O bits while in Fan Mode.

Status Register

SUTATS

]7[D]6[D]5[D]4[D]3[D]2[D]1[D]0[D

7S6S5S4S3S2S1S0S

Power-On Default Value: 0000 0000b, 00

h

no interrupts pending

Command_byte addess: 0000 0011b, 03

h

Type: 8-bits, read only

Bit Name: S

n

Function: Flag for Pn input-change event when Pn is

configured as an input; Sn is set when the

corresponding input changes state.

Operation: 1 = change occured

0 = no change occured

Notes: If Fan Mode is selected, that is, the FAN bit of

the DEV_CFG register is set to one, P[7:4] are

automatically configured as open-drain

outputs. They are then referred to as /FS[2:0]

and /SHDN. No interrupts of any kind are

generated by these pins while in Fan Mode.

All status bits are cleared after any read

operation is performed on STATUS.

August 1, 2000 5 MIC74

MIC74 Micrel

Interrupt Mask Register

KSAM_TNI

]7[D]6[D]5[D]4[D]3[D]2[D]1[D]0[D

7MI6MI5MI4MI3MI2MI1MI0MI

Power-On Default Value: 0000 0000b, 00

Command_byte addess: 0000 0100b, 04

h

h

Type: 8-bits, read/write

Bit Name: IM

n

Function: Interrupt enable bit for Pn when Pn is config-

ured as an input

Operation: 1 = enabled

0 = disabled

Notes: If Fan Mode is selected, that is, the FAN bit of

the DEV_CFG register is set to one, P[7:4] are

automatically configured as open-drain

outputs. They are then referred to as /FS[2:0]

and /SHDN. No interrupts of any kind are

generated by these pins while in Fan Mode.

Data Register

ATAD

]7[D]6[D]5[D]4[D]3[D]2[D]1[D]0[D

7P6P5P4P3P2P1P0P

Power-On Default Value: 1111 1111b, FF

Command_byte addess: 0000 0101b, 05

h

h

Type: 8-bits, read/write

Bit Name: P

n

Function: Returns the current state of any Pn configured

as an input and the last value written to Pn’s

configured as outputs; Writing the DATA

register sets the output state of any Pn’s

configured as outputs; writes to I/O bits

configured as inputs are ignored.

Read Operation: 1 = Pn is high

0 = Pn is low

Write Operation: 1 = Pn is set to one

0 = Pn is cleared

Notes: If Fan Mode is selected, that is, the FAN bit of

the DEV_CFG register is set to one, P[7:4] are

automatically configured as open-drain

outputs. They are then referred to as /FS[2:0]

and /SHDN. The state of these pins is determined by the FAN_SPEED register. While in

Fan Mode, D[7:4] of the DATA registers have

no effect.

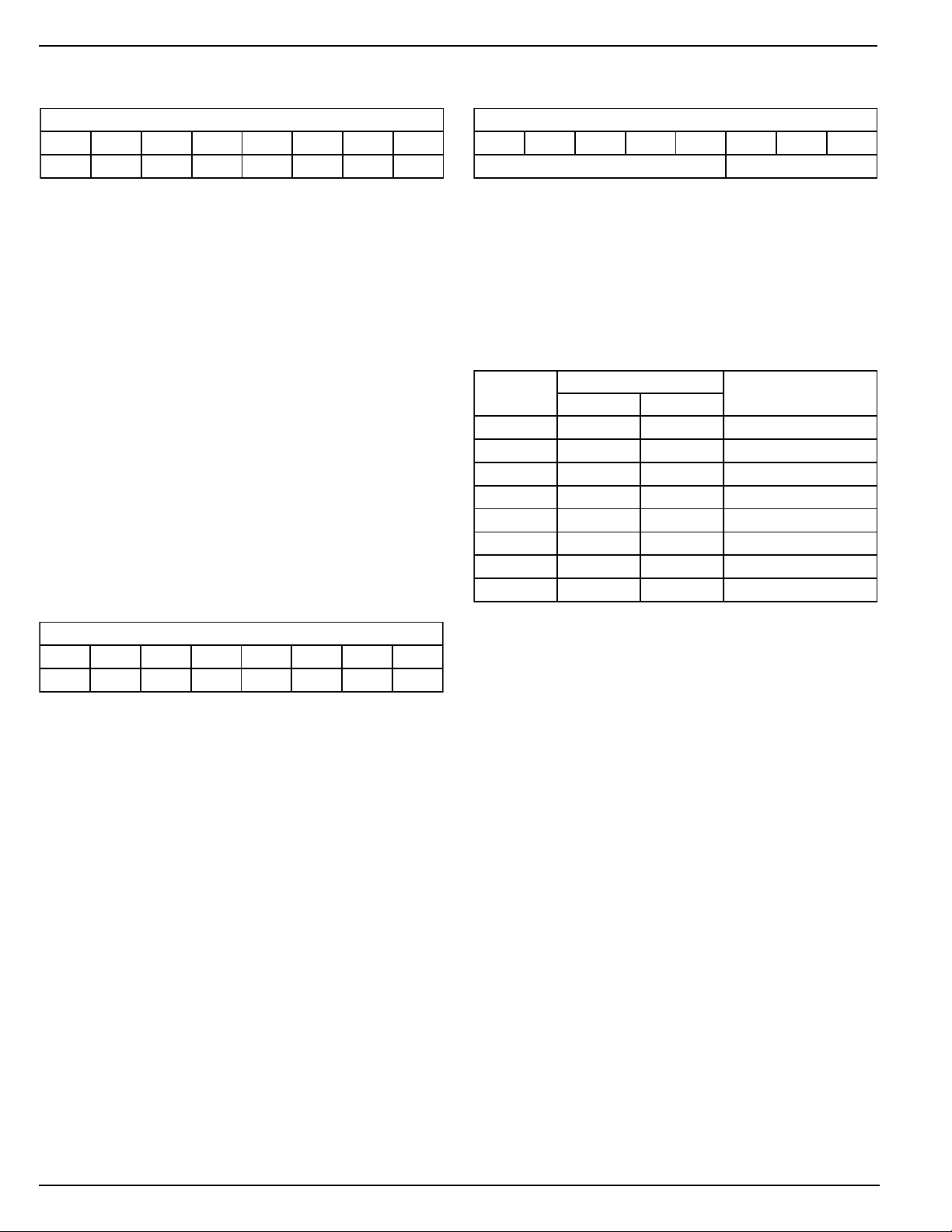

Fan Speed Register

DEEPS_NAF

]7[D]6[D]5[D]4[D]3[D]2[D]1[D]0[D

.orezsaetirwsyawlAdeepSnaF

Power-On Default Value: 0000 0000b, 00

h

fan off

Command_byte addess: 0000 0110b, 06

h

Type: 8-bits, read/write

Bit Name: D[0] through D[2]

Function: Determines bit-pattern on FS[2:0]

Operation:

]0:2[D

eulaV

0001110 ffo

1000111 )tsewols(1deeps

0101011 2deeps

1100011 3deeps

0011101 4deeps

1010101 5deeps

0111001 6deeps

1110001 )tsetsaf(7deeps

]0:2[SF/NDHS/

etatStuptuO

deepSnaF

Fan Speed Settings

Notes: Any time the fan speed register contains zero,

that is, the fan is shut down, and a non-zero

value is written into the fan speed register, the

/FS[2:0] and /SHDN outputs will assume the

highest fan speed state for approximately one

second (t

). Following this interval, the

START

state of the fan speed control outputs will

assume the value indicated by the contents of

FAN_SPEED. This insures that the fan will

start reliably when low speed operation is

desired.

Bit Name: D[3] through D[7]

Function: Reserved

Operation: Always write as zero.

MIC74 6 August 1, 2000

Loading...

Loading...