MICREL MIC68220, MIC68220YML Datasheet

General Description

MIC68220

Dual 2A LDO Regulator

Features

The MIC68220 is a dual high peak current LDO regulator

designed specifically for powering applications such as

FPGA core voltages that require high start up current with

lower nominal operating current. Capable of sourcing 2A of

current per channel for start-up, the MIC68220 provides

high power from a small MLF™ leadless package. The

MIC68220 can also implement a variety of power-up and

power-down protocols such as sequencing, tracking, and

ratiometric tracking.

The MIC68220 operates from a wide input range of 1.65V

to 5.5V, which includes all of the main supply voltages

commonly available today. It is designed to drive digital

circuits requiring low voltage at high currents (i.e. PLDs,

DSP, microcontroller, etc.). The MIC68220 incorporates a

delay pin (Delay) for control of power on reset output

(POR) at turn-on and power-down delay at turn-off. In

addition there is a ramp control pin (RC) for either tracking

applications or output voltage slew rate adjustment at turnon. This is important in applications where the load is

highly capacitive and in-rush currents can cause supply

voltages to fail and microprocessors or other complex logic

chips to hang up.

The MIC68220’s can be configured in two modes. In

tracking mode, the output voltage of Vout1 drives the RC2

pin so that the Vout2 tracks Vout1 during turn-on and turnoff. In sequencing mode, POR1 of Vout1 drives the enable

pin (EN2) of Vout2 so that it turns on after the Vout1 and

turns off before (or after) Vout1. This behavior is critical

for power-up and power-down control in multi-output

power supplies. The MIC68220 is fully protected offering

both thermal and current limit protection, and reverse

current protection.

The MIC68220 has a junction temperature range of

-40°C to +125°C and is available in an adjustable Vout1 &

Vout2 version. The MIC68220 is offered in a low profile

4mm x 5mm 20ld MLF

___________________________________________________________________________________________________________

®

package.

• Stable with 4.7uF ceramic output capacitor

• Input voltage range: 1.65V to 5.5V

• 0.5V reference

1.0% initial output tolerance

• +

• 2A maximum output current – peak start up

• 1A Continuous Operating Current

• Tracking on turn-on and turn-off with pin strapping

• Timing Controlled Sequencing On/Off

• Programmable Ramp Control™ for in-rush current

limiting and slew rate control of the output voltage on

Turn-On

• Power-on Reset (POR) supervisor with programmable

delay time

• Single Master can control multiple Slave regulators

with tracking output voltages

• Tiny 4mm x 5mm MLF

• Maximum dropout (V

temperature at 1A output current

• Adjustable Output Voltages

• Excellent line and load regulation specifications

• Logic controlled shutdown

• Thermal shutdown and current limit protection

®

package

– V

IN

) of 400mV over

OUT

Applications

• FPGA/PLD Power Supply

• Networking/Telecom Equipment

• Microprocessor Core Voltage

• High Efficiency Linear Post Regulator

• Sequenced or Tracked Power Supply

MLF and MicroLead Frame is a registered trademark of Amkor Technologies

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (

December 2006

408

) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

M9999-121406

(408) 944-0800

Micrel MIC68220

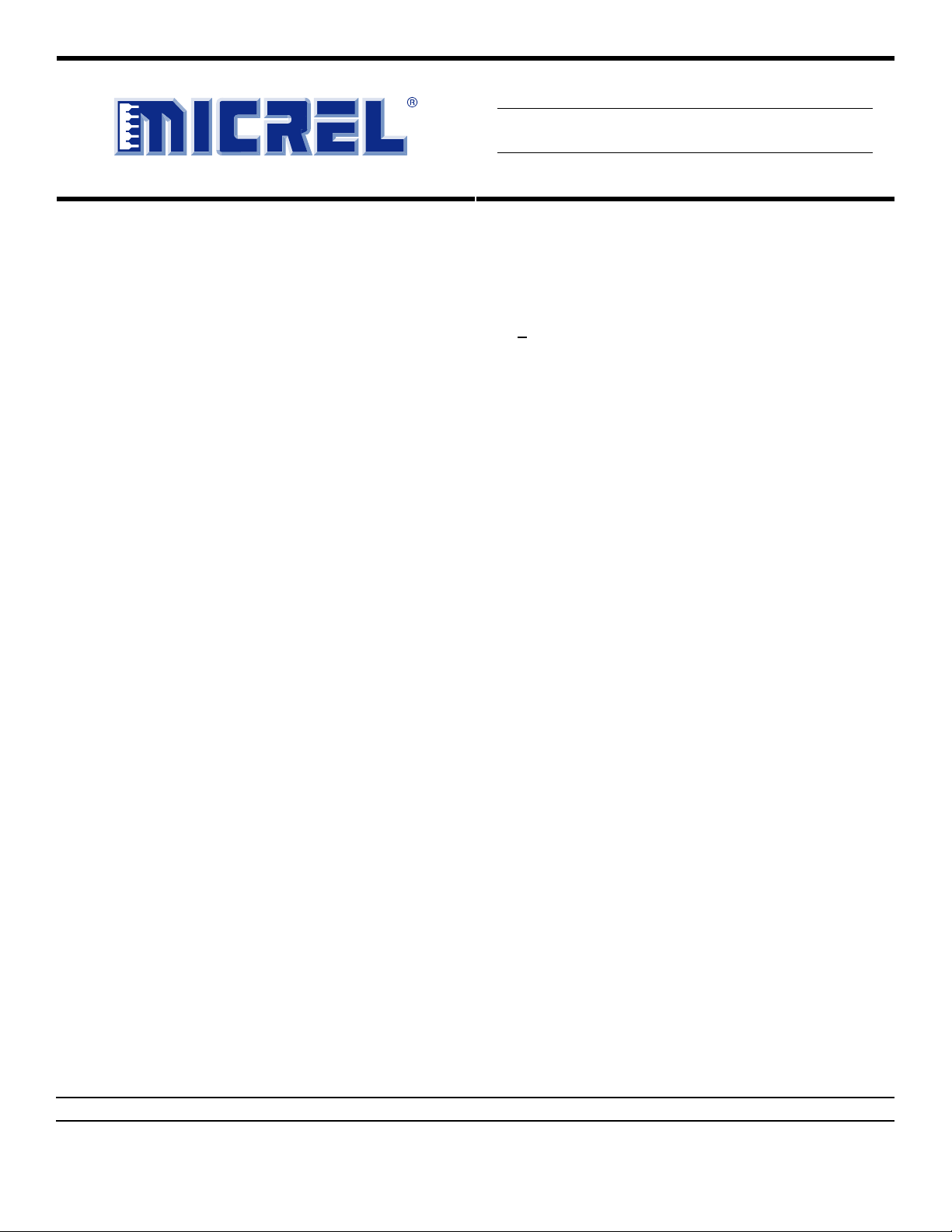

Typical Application

Sequenced Dual Power Supply for I/O and Core Voltage of µProcessor

December 2006

2

M9999-121406

(408) 955-1690

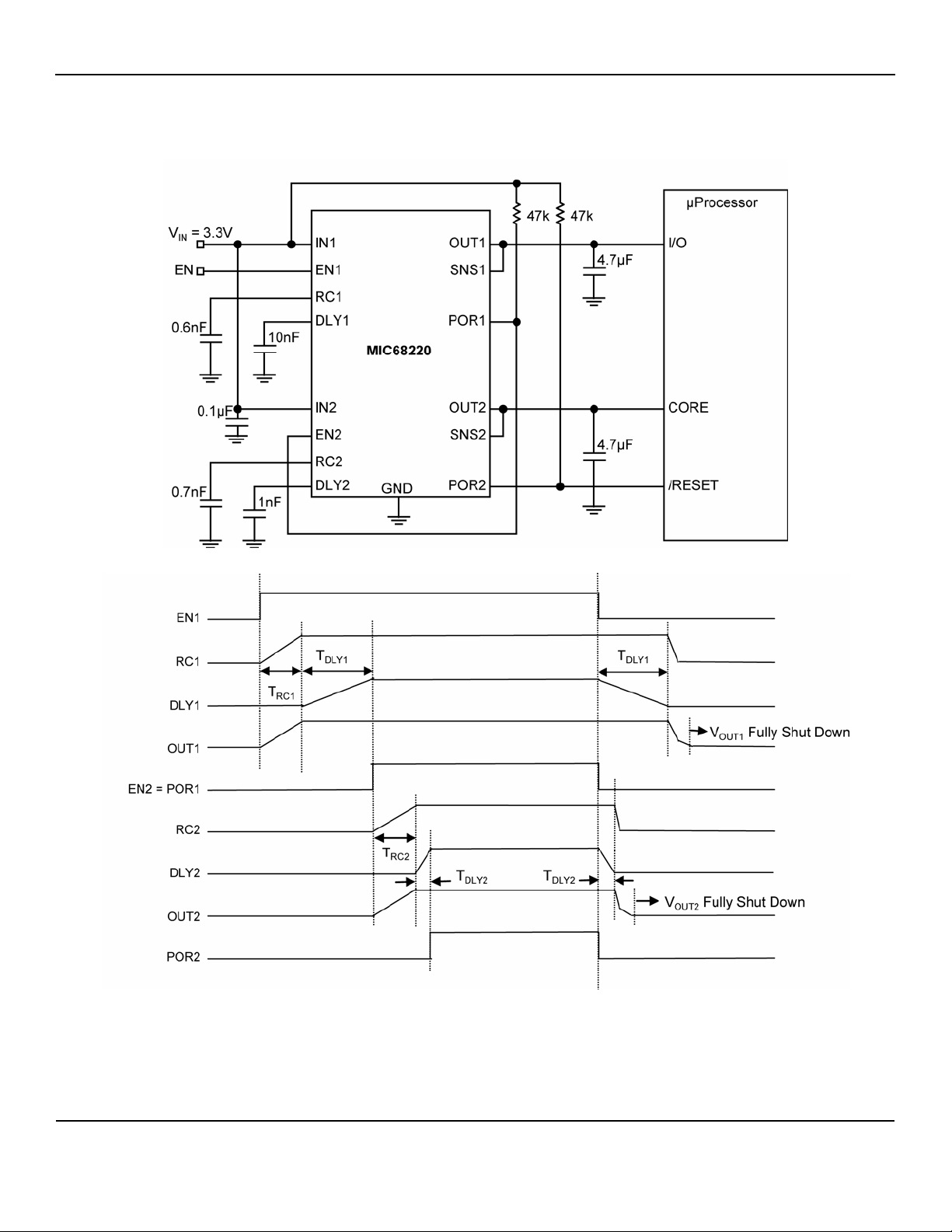

Micrel MIC68220

Tracking Dual Power Supply for I/O and Core Voltage of µProcessor

December 2006

3

M9999-121406

(408) 955-1690

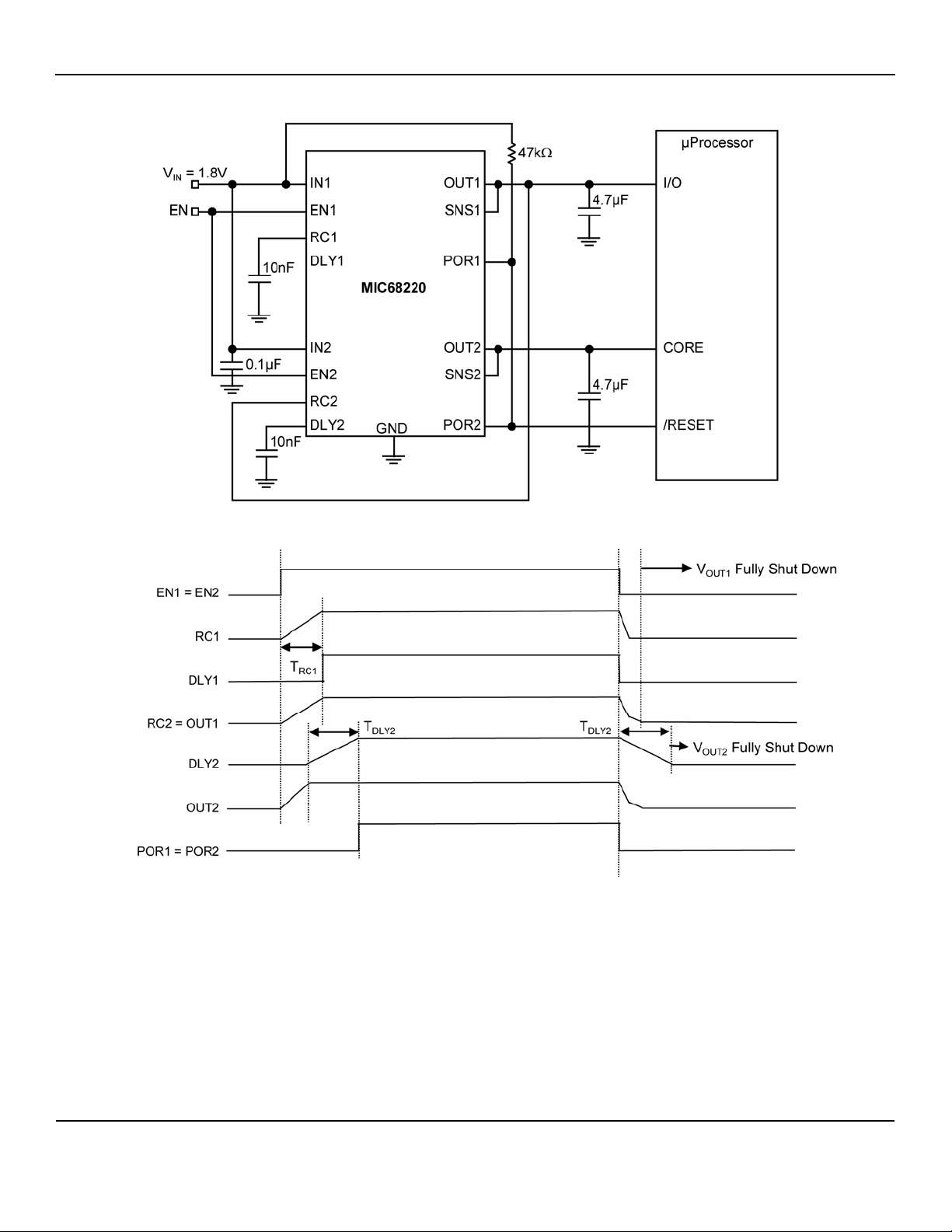

Micrel MIC68220

Block Diagram

December 2006

4

M9999-121406

(408) 955-1690

Micrel MIC68220

Ordering Information

Part Number

MIC68220YML 2.0A ADJ –40°C to +125°C PB-Free 20-Pin 4x5 MLF®

NOTE: For additional voltage options, contact Micrel Marketing.

Output

Current

Voltage

Junction

Temperature Range

Package

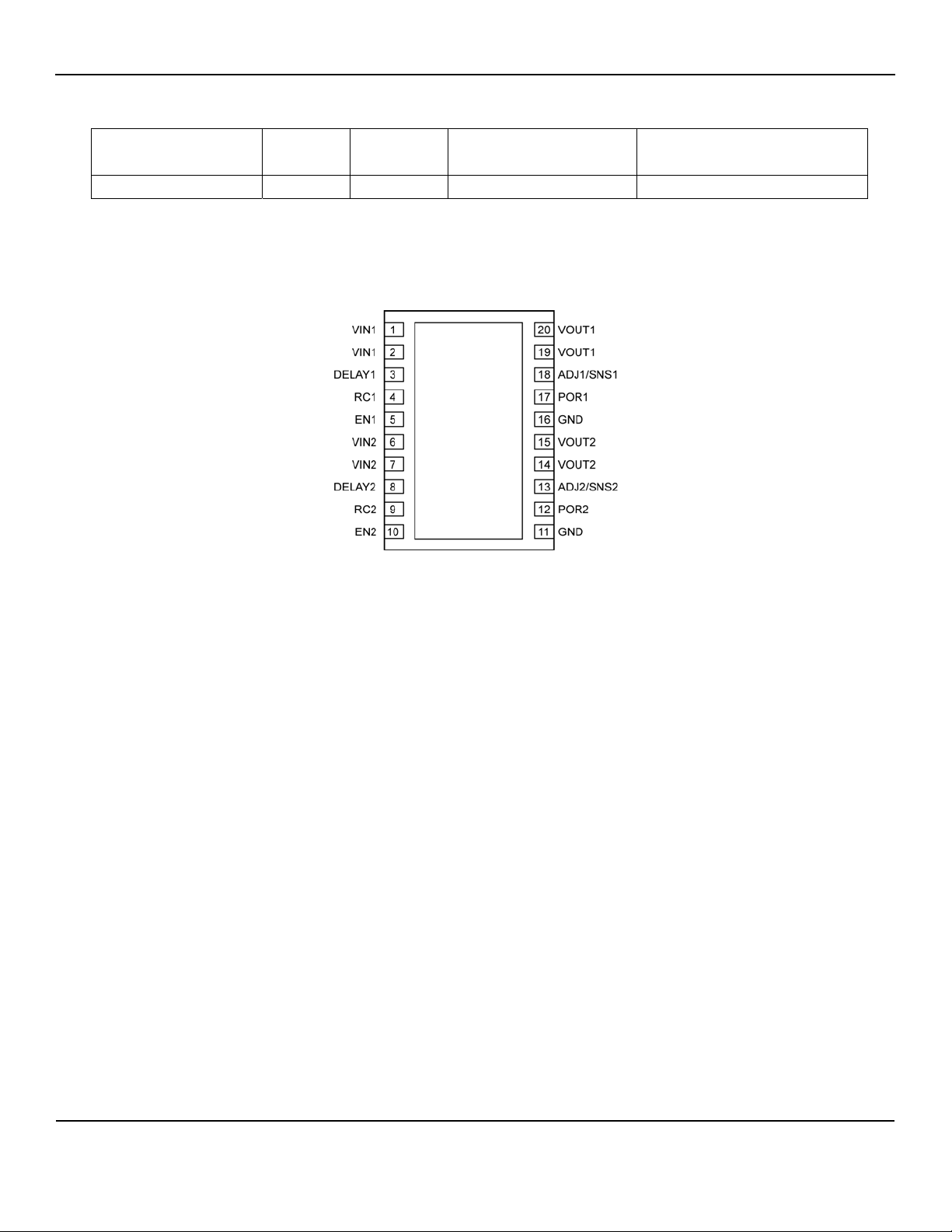

Pin Configuration

December 2006

5

M9999-121406

(408) 955-1690

Micrel MIC68220

Pin Description

(Pin Numbering may change depending on layout considerations)

1,2 VIN1

3 Delay1

4 RC1

5 EN1 Enable (Input): CMOS compatible input. Logic high = enable, logic low = shutdown

6,7 VIN2

8 Delay2

9 RC2

10 EN2 Enable (Input): CMOS compatible input. Logic high = enable, logic low = shutdown

11 GND Ground

12 POR2

13 ADJ2 Adjustable regulators: Feedback input. Connect to external resistor voltage divider.

13 SNS2 Fixed Output Voltage Regulators: Sense pin. Connect directly to VOUT2

14,15 VOUT2

16 GND Ground

17 POR1

18 ADJ1 Adjustable regulators: Feedback input. Connect to external resistor voltage divider.

18 SNS1 Fixed Output Voltage Regulators: Sense pin. Connect directly to VOUT1

19,20 VOUT1

Input: Input voltage supply pin. Place a capacitor to ground to bypass the input

supply

Delay. Capacitor to ground sets internal delay timer. Timer delays power-on reset

(POR) output at turn-on, and ramp down at turn-off.

Ramp Control. May be voltage driven for tracking applications, or a capacitor to

ground will set the slew rate of output voltage during start-up.

Input: Input voltage supply pin. Place a capacitor to ground to bypass the input

supply

Delay. Capacitor to ground sets internal delay timer. Timer delays power-on reset

(POR) output at turn-on, and ramp down at turn-off.

Ramp Control. May be voltage driven for tracking applications, or a capacitor to

ground will set the slew rate of output voltage during start-up.

Power-on Reset: Open-drain output device indicates when the output is in regulation.

High (open) means device is regulating within 10%. POR onset can be delayed using

a single capacitor from Delay to ground.

Output Voltage: Output of voltage regulator. Place capacitor to ground to bypass the

output voltage. Minimum load current is 100uA. Nominal bypass capacitor is 4.7uf.

Power-on Reset: Open-drain output device indicates when the output is in regulation.

High (open) means device is regulating within 10%. POR onset can be delayed using

a single capacitor from Delay-to-ground.

Output Voltage: Output of voltage regulator. Place capacitor to ground to bypass the

output voltage. Minimum load current is 100uA. Nominal bypass capacitor is 4.7uf.

December 2006

6

M9999-121406

(408) 955-1690

Loading...

Loading...