Micrel KSZ8841-16, KSZ8841-32 User Manual

KSZ8841-16/32

MQL/MVL/MVLI

Single-Port Ethernet MAC Controller

with Non-PCI Interface

General Description

The KSZ8841-series single-port chip includes PCI and

non-PCI CPU interfaces, and are available in 8/16-bit and

32-bit bus designs (see

datasheet describes the KSZ8841M-series of non-PCI

CPU interface chips. For information on the KSZ8841 PCI

CPU interface chips, refer to the KSZ8841P datasheet.

The KSZ8841M is a single chip, mixed analog/digital

device offering Wake-on-LAN technology for effectively

addressing Fast Ethernet applications. It consists of a Fast

Ethernet MAC controller, an 8-bit, 16-bit, and 32-bit

generic host processor interface and incorporates a unique

dynamic memory pointer with 4-byte buffer boundary and

a fully utilizable 8KB for both TX and RX directions in host

buffer interface.

The KSZ8841M is designed to be fully compliant with the

appropriate IEEE 802.3 standards. An industrial

temperature-grade version of the KSZ8841M, the

KSZ8841MQLI, also can be ordered (see

Information).

Ordering Information). This

Ordering

Data Sheet Rev 1.3

Physical signal transmission and reception are enhanced

through the use of analog circuitry, making the design

more efficient and allowing for lower-power consumption.

The KSZ8841M is designed using a low-power CMOS

process that features a single 3.3V power supply with 5V

tolerant I/O. It has an extensive feature set that offers

management information base (MIB) counters and CPU

control/data interfaces.

The KSZ8841M includes a unique cable diagnostics

feature called LinkMD™. This feature determines the

length of the cabling plant and also ascertains if there is an

open or short condition in the cable. Accompanying

software enables the cable length and cable conditions to

be conveniently displayed. In addition, the KSZ8841M

supports Hewlett Packard (HP) Auto-MDIX thereby

eliminating the need to differentiate between straight or

crossover cables in applications.

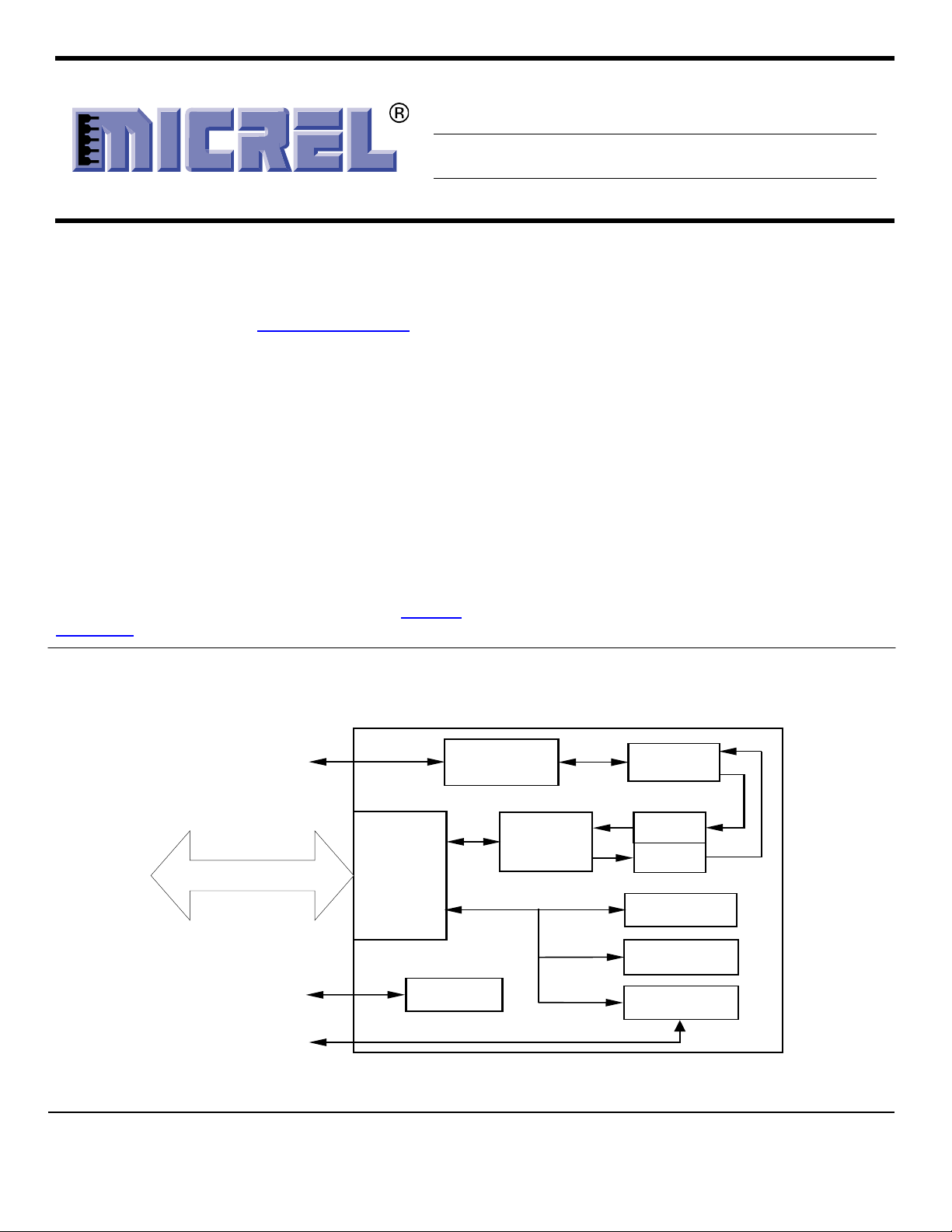

Functional Diagram

P1 HP Auto

MDI/MDI-X

Non-PCI

Em bedded Processor

In te rfa c e

8,16, or 32-bit G eneric

H o s t In te rfa c e

P1 LED[3:0]

EEPROM I/F

November 2005 1

CPU

Bus

In te rfa c e

Unit

Figure 1. KSZ8841M Functional Diagram

Base-T/TX

LED

Driver

10/100

PHY

Channel

QMU

DMA

Host MAC

RXQ

4KB

TXQ

4KB

Control

Registers

MIB

Counters

EEPROM

In te rfa c e

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

Features

• Single chip Ethernet controller with IEEE802.3u

support

• Supports 10BASE-T/100BASE-TX

• Supports IEEE 802.3x full-duplex flow control and

half-duplex backpressure collision flow control

• Supports burst data transfers

• 8KB internal memory for RX/TX FIFO buffers

• Early TX/RX functions to minimize latency through the

device

• Optional to use external serial EEPROM configuration

for both KSZ8841-16MQL and KSZ8841-32MQL

• Single 25MHz reference clock for both PHY and MAC

Network Features

• Fully integrated to comply with IEEE802.3u standards

• 10BASE-T and 100BASE-TX physical layer support

• Auto-negotiation: 10/100Mbps full and half duplex

• Adaptive equalizer

• Baseline wander correction

Power Modes, Power Supplies, and Packaging

• Single power supply (3.3V) with 5V tolerant I/O

buffers

• Enhanced power management feature with powerdown feature to ensure low-power dissipation during

device idle periods

• Comprehensive LED indicator support for link,

activity, full/half duplex, and 10/100 speed (4 LEDs)

– User programmable

• Low-power CMOS design

• Commercial Temperature Range: 0

• Industrial Temperature Range: –40

Ordering Information)

• Available in 128-pin PQFP (128-pin LQFP optional).

Ordering Information.

See

o

C to +70oC

o

C to +85oC (see

Additional Features

In addition to offering all of the features of a Layer 2

controller, the KSZ8841M offers:

• Dynamic buffer memory scheme

– Essential for applications such as Video over IP

where image jitter is unacceptable

• Flexible 8-bit, 16-bit, and 32-bit generic host

processor interfaces

• Micrel LinkMD™ cable diagnostic capabilities to

determine cable length, diagnose faulty cables, and

determine distance to fault

• Wake-on-LAN functionality

– Incorporates Magic Packet™, network link state,

and wake-up frame technology

• HP Auto MDI-X™ crossover with disable/enable

option

• Ability to transmit and receive frames up to 1916

bytes

Applications

• Video Distribution Systems

• High-end Cable, Satellite, and IP set-top boxes

• Video over IP

• Voice over IP (VoIP) and Analog Telephone Adapters

(ATA)

• Industrial Control in Latency Critical Applications

• Motion Control

• Industrial Control Sensor Devices (Temperature,

Pressure, Levels, and Valves)

• Security and Surveillance Cameras

Markets

• Fast Ethernet

• Embedded Ethernet

• Industrial Ethernet

LinkMD is a trademark of Micrel, Inc.

Magic Packet is a trademark of Advanced Micro Devices, Inc.

Product names used in this datasheet are for identification purposes

only and may be trademarks of their respective companies.

November 2005 2

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

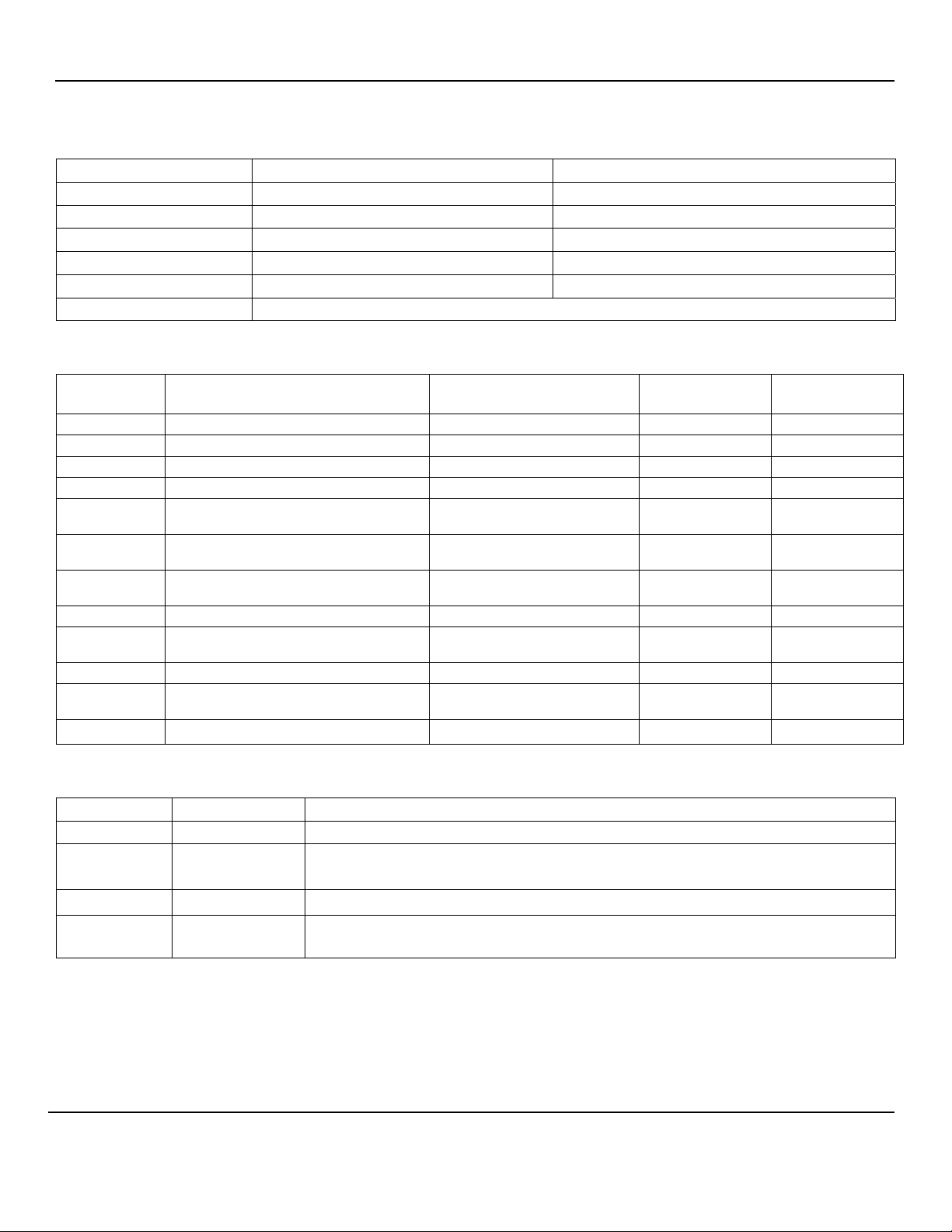

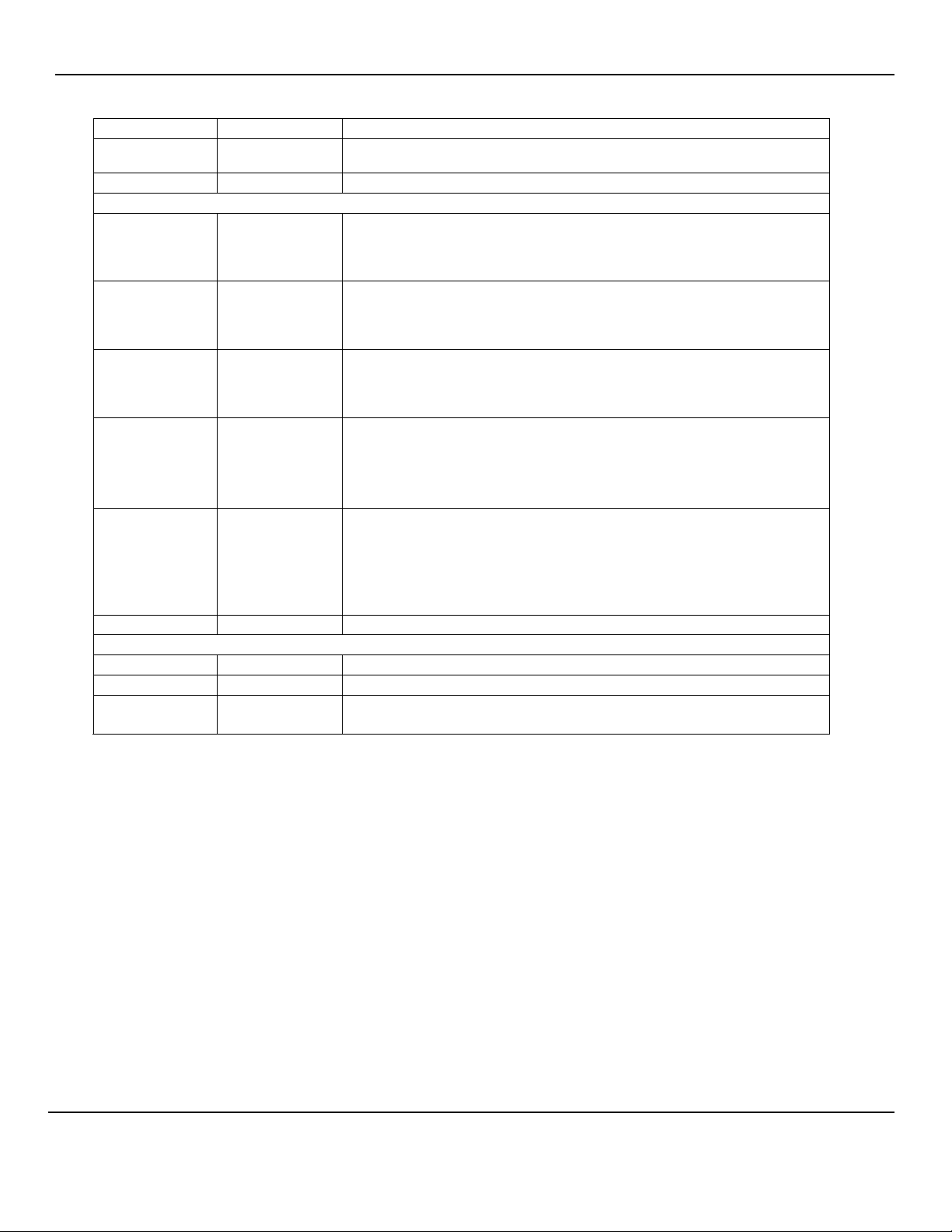

Ordering Information

Part Number Junction Temp. Range

KSZ8841-16MQL 0oC to 70oC 128-Pin PQFP

KSZ8841-32MQL 0oC to 70oC 128-Pin PQFP

KSZ8841-16MVL 0oC to 70oC 128-Pin LQFP (Available Q1, 2006 Samples)

KSZ8841-32MVL 0oC to 70oC 128-Pin LQFP (Available Q1, 2006 Samples)

KSZ8841-16MVLI –40oC to +85oC 128-Pin LQFP- (Available Q1, 2006 Samples)

KSZ8841-16MQL-Eval Evaluation Board for the KSZ8841-16MQL

(1)

Package

Contacts

Location Address

City, State/Province,

Country

Corporate HQ 2180 Fortune Drive San Jose, CA 95131 USA +1 (408) 944-0800 +1 (408) 474-1000

Eastern USA 93 Branch Street Medford, NJ 08055 USA +1 (609) 654-0078 +1 (609) 546-0989

Central USA 2425 N.Central Expressway, Suite 351 Richardson, TX 75080 USA +1 (972) 393-2533 +1 (972) 393-2370

Western USA 2180 Fortune Drive San Jose, CA 95131 USA +1 (408) 944-0800 +1 (408) 914-7878

China Room 712, Block B, Intl. Chamber of

Korea 8F AnnJay Tower Bldg

Taiwan 4F, No. 18, Lane 321, Yang-Guang Street,

Singapore 300 Beach Road, #10-07 The Concourse Singapore 199555 +65-6291-1318 +65-6291-1332

Japan 2-3-1 Minato Mirai, Queen’s Tower A 14F,

Uk/EMEIA 1st Floor, 3 Lockside Place, Mill Lane Newbury, Berks RG14 5QS UK +44 1635 524455 +44 1635 524466

France/Southern

Europe

New Zealand Office 2, CML Building 2 Perry Street Masterton New Zealand + 64-6-378-9799 + 64-6-378-9599

Commerce Bldg., Fuhua Rd 1, Futian

718-2 Yeoksam-dong, Kangnam-ku

Nei-Hu Chu

Nishi-ku

10, avenue du Quebec, Villebon BP116 Courtaboeuf Cedex 91944 France +33 (0) 1-6092-4190 +33 (0) 1-6092-4189

Shenzhen, PR China 518026 +86 (755) 8302-

Seoul 135-080 Korea +82 (2) 538-2380 +82 (2) 538-2381

Taipei, 11468 Taiwan, R.O.C. +886 (2) 8751-0600 +886 (2) 8751-0746

Yokohama, Kanagawa 220-8543

Japan

Telephone Fax

7618

+81-45-224-6616 +81-45-224-6716

+86 (755) 83027637

Revision History

Revision Date Summary of Changes

1.0 06/30/05 First released Preliminary Information.

1.1 08/08/05 Updated General Description, Functional Diagram, Pin Description and Features.

Added this Revision History Table and Loopback support sections.

1.2 10/04/05 Update Power Saving bit description in P1PHYCTRL and P1SCSLMD registers.

1.3 11/01/05 Updated Figure 12/13/14 Asynchronous Timing and Table 16/17/18 parameters, PQFP

package information.

November 2005 3

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

Contents

General Description............................................................................................................................................1

Functional Diagram............................................................................................................................................1

Features...............................................................................................................................................................2

Network Features .........................................................................................................................................................2

Power Modes, Power Supplies, and Packaging........................................................................................................2

Additional Features............................................................................................................................................2

Applications........................................................................................................................................................2

Markets................................................................................................................................................................2

Ordering Information..........................................................................................................................................3

Contacts ..............................................................................................................................................................3

Revision History .................................................................................................................................................3

Contents..............................................................................................................................................................4

List of Figures.....................................................................................................................................................7

List of Tables.......................................................................................................................................................8

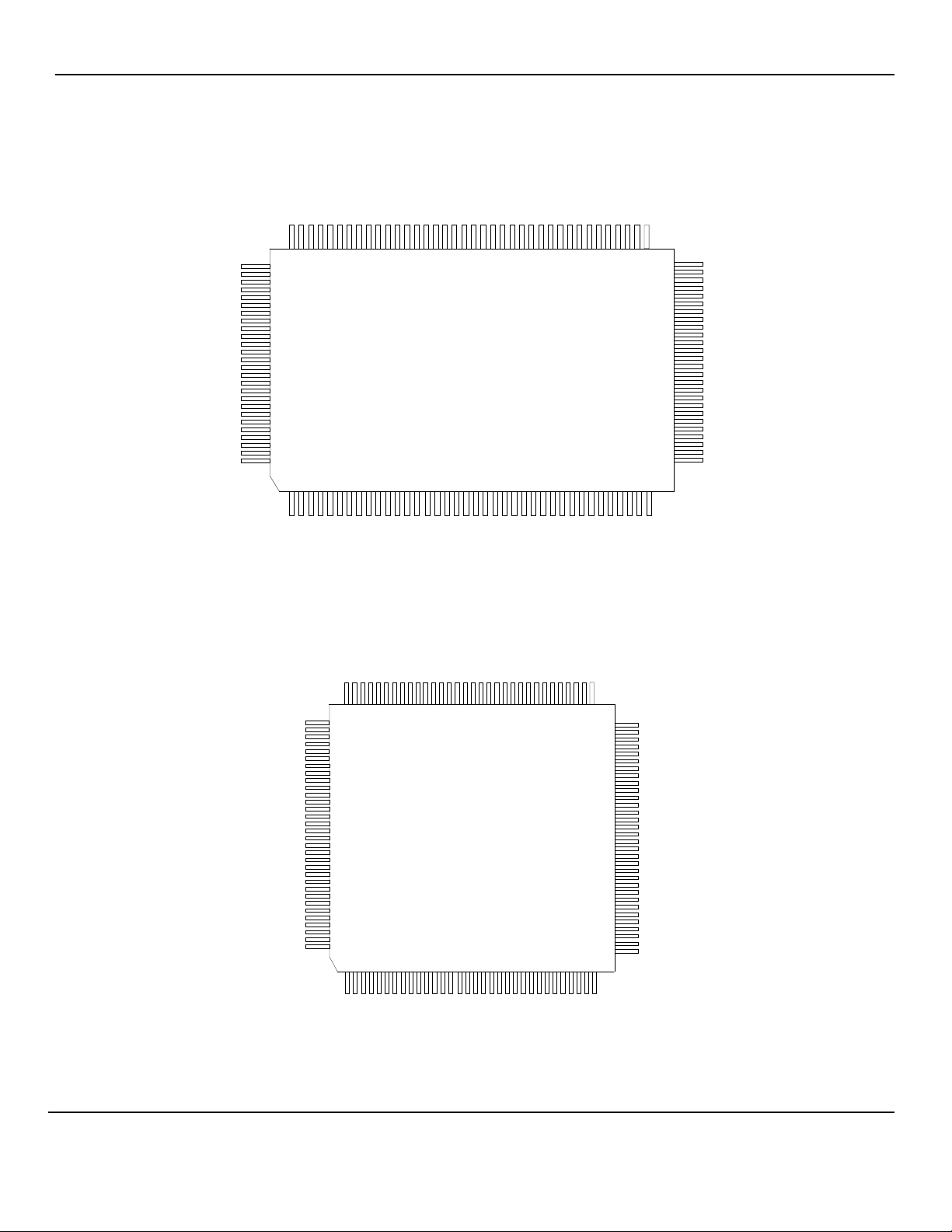

Pin Configuration for KSZ8841-16 Chip (8/16-Bit)...........................................................................................9

Pin Description for KSZ8841-16 Chip (8/16-Bit).............................................................................................10

Pin Configuration for KSZ8841-32 Chip (32-Bit)............................................................................................15

Pin Description for KSZ8841-32 Chip (32-Bit)................................................................................................16

Functional Description.....................................................................................................................................21

Functional Overview.........................................................................................................................................21

Power Management....................................................................................................................................................21

Power down....................................................................................................................................................................................21

Wake-on-LAN .................................................................................................................................................................................21

Link Change....................................................................................................................................................................................21

Wake-up Packet..............................................................................................................................................................................21

Magic Packet ..................................................................................................................................................................................22

Physical Layer Transceiver (PHY) ............................................................................................................................22

100BASE-TX Transmit....................................................................................................................................................................22

100BASE-TX Receive.....................................................................................................................................................................22

PLL Clock Synthesizer (Recovery) .................................................................................................................................................23

Scrambler/De-scrambler (100BASE-TX Only)................................................................................................................................23

10BASE-T Transmit........................................................................................................................................................................23

10BASE-T Receive.........................................................................................................................................................................23

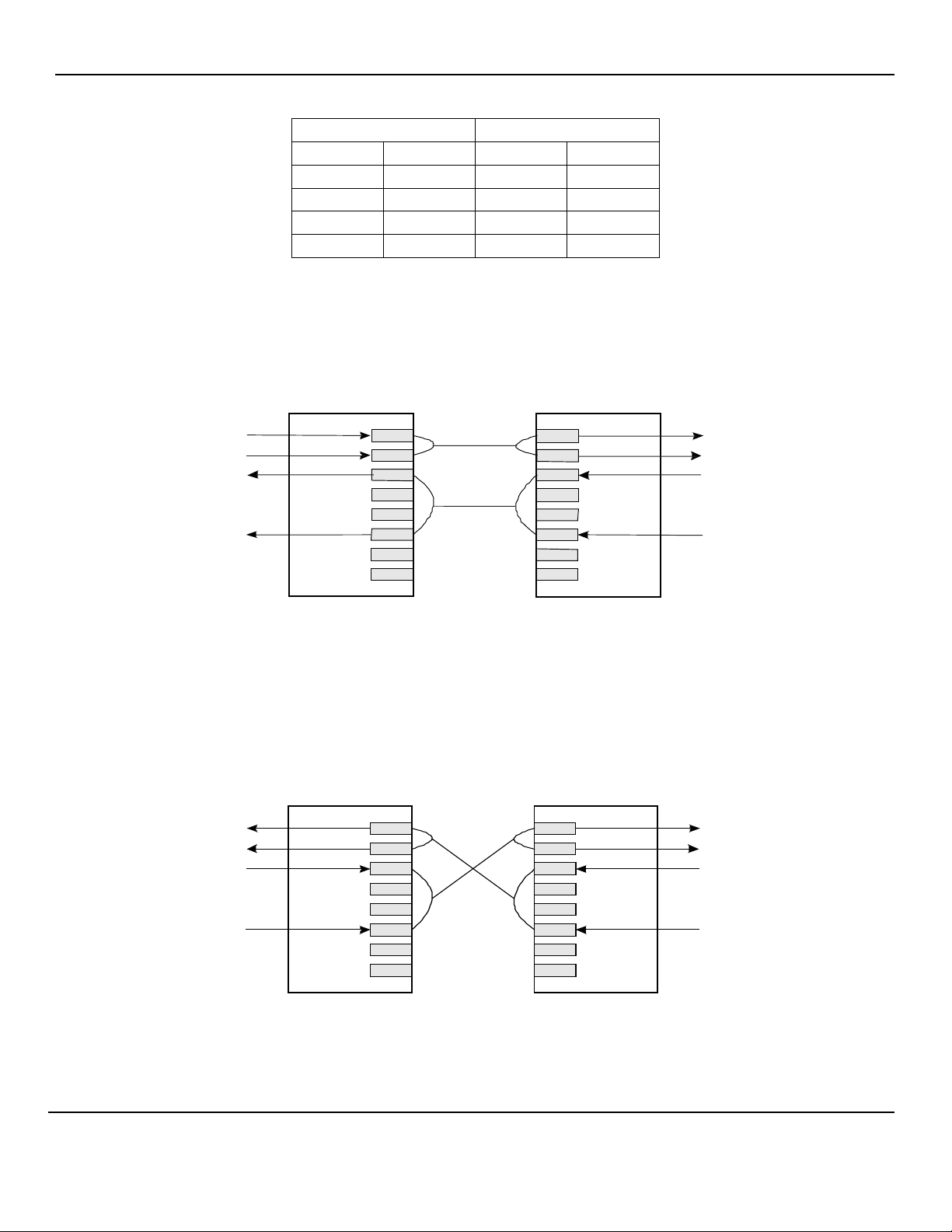

MDI/MDI-X Auto Crossover.............................................................................................................................................................23

Straight Cable......................................................................................................................................................................................................24

Crossover Cable .................................................................................................................................................................................................24

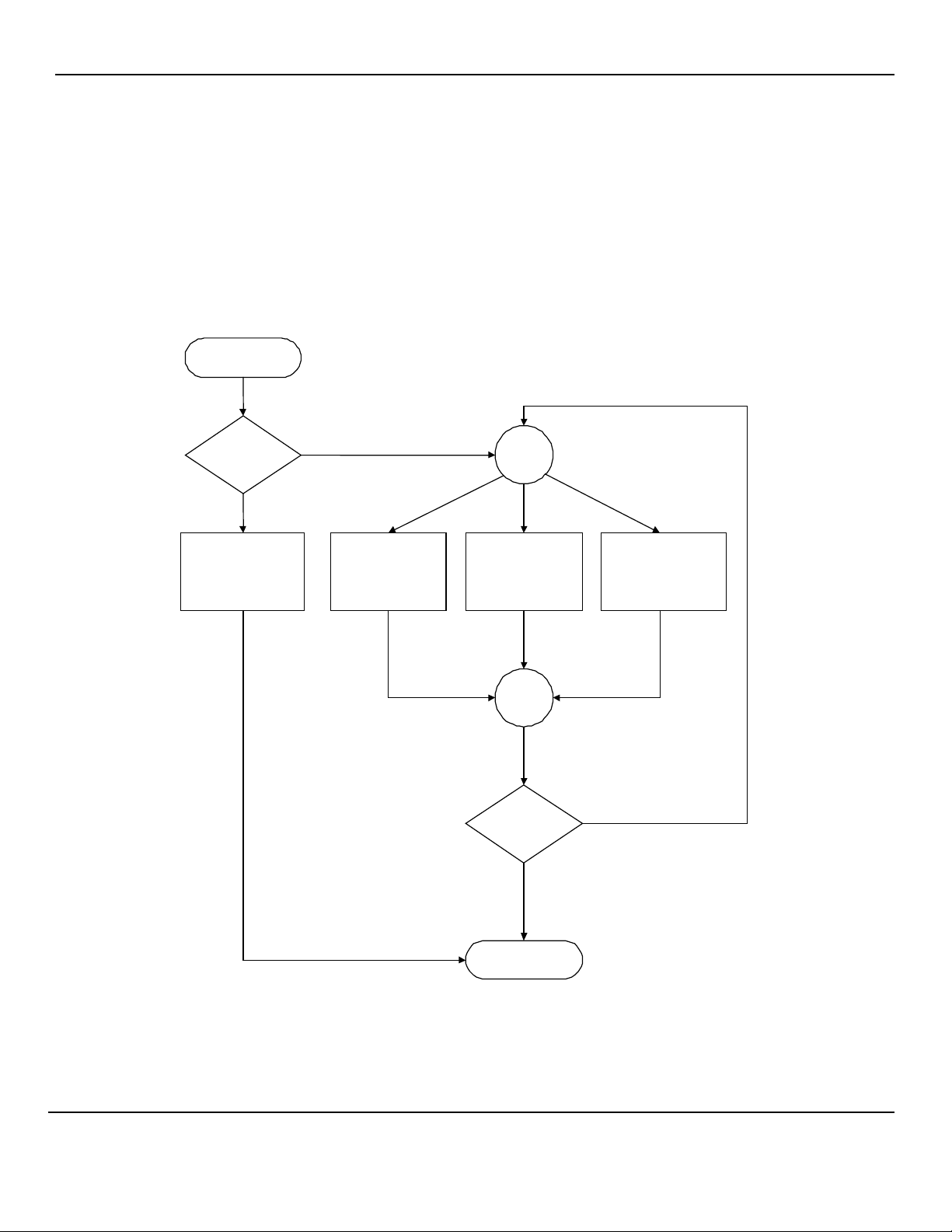

Auto Negotiation .............................................................................................................................................................................25

LinkMD Cable Diagnostics..............................................................................................................................................................26

Access .................................................................................................................................................................................................................26

Usage ...................................................................................................................................................................................................................26

Media Access Control (MAC) Operation..................................................................................................................26

Inter Packet Gap (IPG) ...................................................................................................................................................................26

Back-Off Algorithm.......................................................................................................................................................................... 26

Late Collision ..................................................................................................................................................................................26

Flow Control....................................................................................................................................................................................27

Half-Duplex Backpressure ..............................................................................................................................................................27

Clock Generator..............................................................................................................................................................................27

Bus Interface Unit (BIU).............................................................................................................................................27

Supported Transfers .......................................................................................................................................................................27

Physical Data Bus Size...................................................................................................................................................................28

November 2005 4

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

Asynchronous Interface ..................................................................................................................................................................29

Synchronous Interface....................................................................................................................................................................30

BIU Summation...............................................................................................................................................................................30

BIU Implementation Principles........................................................................................................................................................31

Queue Management Unit (QMU)................................................................................................................................32

Transmit Queue (TXQ) Frame Format............................................................................................................................................32

Receive Queue (RXQ) Frame Format ............................................................................................................................................33

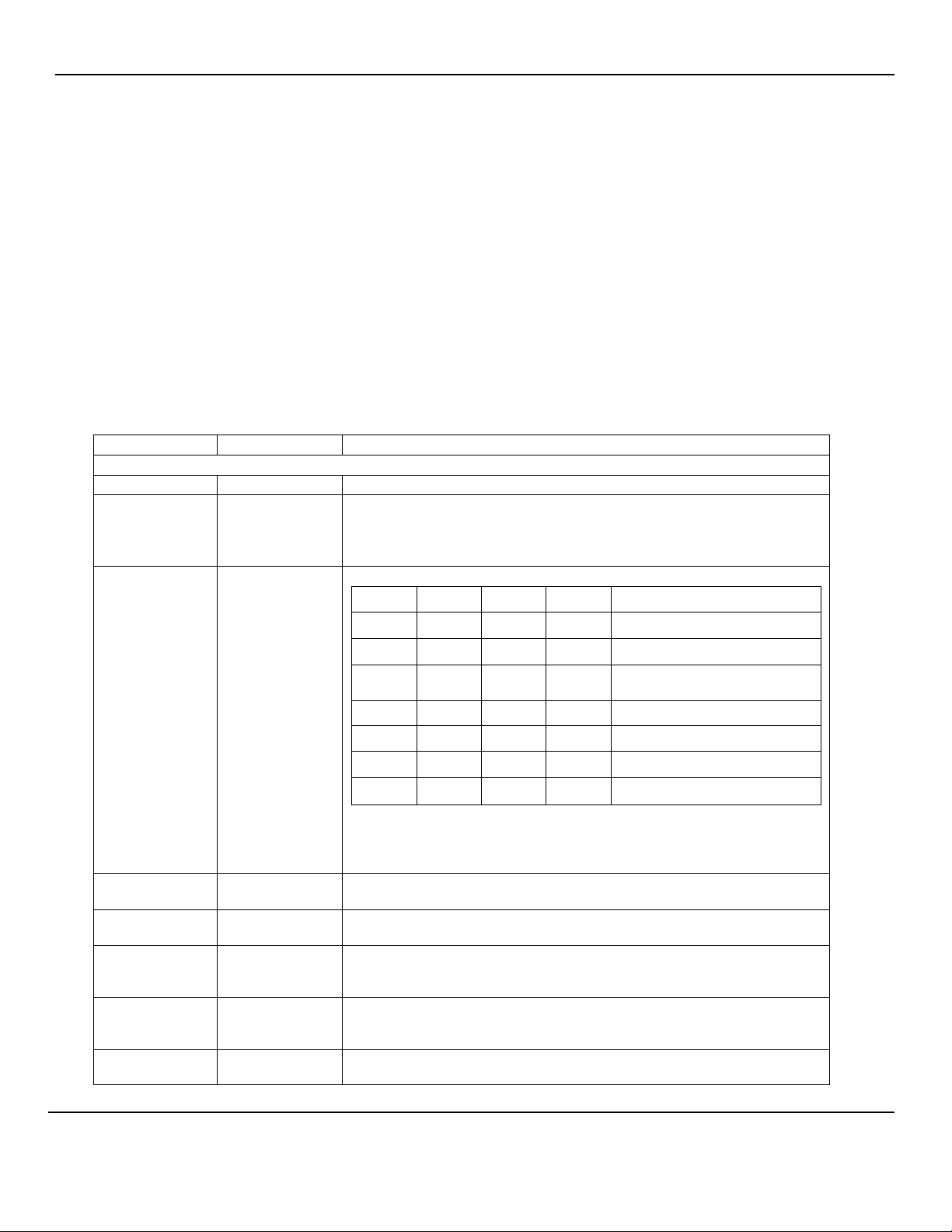

EEPROM Interface......................................................................................................................................................34

Loopback Support......................................................................................................................................................36

Near-end (Remote) Loopback.........................................................................................................................................................36

CPU Interface I/O Registers............................................................................................................................. 37

I/O Registers...................................................................................................................................................................................37

Internal I/O Space Mapping ............................................................................................................................................................38

Register Map: MAC and PHY...........................................................................................................................46

Bit Type Definition...........................................................................................................................................................................46

Bank 0-63 Bank Select Register (0x0E): BSR (same location in all Banks)....................................................................................46

Bank 0 Base Address Register (0x00): BAR...................................................................................................................................46

Bank 0 Bus Error Status Register (0x06): BESR ............................................................................................................................47

Bank 0 Bus Burst Length Register (0x08): BBLR............................................................................................................................47

Bank 1: Reserved ...........................................................................................................................................................................47

Bank 2 Host MAC Address Register Low (0x00): MARL ................................................................................................................48

Bank 2 Host MAC Address Register Middle (0x02): MARM............................................................................................................48

Bank 2 Host MAC Address Register High (0x04): MARH...............................................................................................................48

Bank 3 On-Chip Bus Control Register (0x00): OBCR.....................................................................................................................49

Bank 3 EEPROM Control Register (0x02): EEPCR........................................................................................................................49

Bank 3 Memory BIST Info Register (0x04): MBIR...........................................................................................................................50

Bank 3 Global Reset Register (0x06): GRR....................................................................................................................................50

Bank 3 Power Management Capabilities Register (0x08): PMCR ..................................................................................................50

Bank 3 Wakeup Frame Control Register (0x0A): WFCR................................................................................................................ 52

Bank 4 Wakeup Frame 0 CRC0 Register (0x00): WF0CRC0.........................................................................................................52

Bank 4 Wakeup Frame 0 CRC1 Register (0x02): WF0CRC1.........................................................................................................53

Bank 4 Wakeup Frame 0 Byte Mask 0 Register (0x04): WF0BM0 .................................................................................................53

Bank 4 Wakeup Frame 0 Byte Mask 1 Register (0x06): WF0BM1 .................................................................................................53

Bank 4 Wakeup Frame 0 Byte Mask 2 Register (0x08): WF0BM2 .................................................................................................53

Bank 4 Wakeup Frame 0 Byte Mask 3 Register (0x0A): WF0BM3.................................................................................................53

Bank 5 Wakeup Frame 1 CRC0 Register (0x00): WF1CRC0.........................................................................................................54

Bank 5 Wakeup Frame 1 CRC1 Register (0x02): WF1CRC1.........................................................................................................54

Bank 5 Wakeup Frame 1 Byte Mask 0 Register (0x04): WF1BM0 .................................................................................................54

Bank 5 Wakeup Frame 1 Byte Mask 1 Register (0x06): WF1BM1 .................................................................................................54

Bank 5 Wakeup Frame 1 Byte Mask 2 Register (0x08): WF1BM2 .................................................................................................54

Bank 5 Wakeup Frame 1 Byte Mask 3 Register (0x0A): WF1BM3.................................................................................................55

Bank 6 Wakeup Frame 2 CRC0 Register (0x00): WF2CRC0.........................................................................................................55

Bank 6 Wakeup Frame 2 CRC1 Register (0x02): WF2CRC1.........................................................................................................55

Bank 6 Wakeup Frame 2 Byte Mask 0 Register (0x04): WF2BM0 .................................................................................................55

Bank 6 Wakeup Frame 2 Byte Mask 1 Register (0x06): WF2BM1 .................................................................................................55

Bank 6 Wakeup Frame 2 Byte Mask 2 Register (0x08): WF2BM2 .................................................................................................56

Bank 6 Wakeup Frame 2 Byte Mask 3 Register (0x0A): WF2BM3.................................................................................................56

Bank 7 Wakeup Frame 3 CRC0 Register (0x00): WF3CRC0.........................................................................................................56

Bank 7 Wakeup Frame 3 CRC1 Register (0x02): WF3CRC1.........................................................................................................56

Bank 7 Wakeup Frame 3 Byte Mask 0 Register (0x04): WF3BM0 .................................................................................................56

Bank 7 Wakeup Frame 3 Byte Mask 1 Register (0x06): WF3BM1 .................................................................................................57

Bank 7 Wakeup Frame 3 Byte Mask 2 Register (0x08): WF3BM2 .................................................................................................57

Bank 7 Wakeup Frame 3 Byte Mask 3 Register (0x0A): WF3BM3.................................................................................................57

Bank 8 – 15: Reserved ...................................................................................................................................................................57

November 2005 5

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

Bank 16 Transmit Control Register (0x00): TXCR..........................................................................................................................57

Bank 16 Transmit Status Register (0x02): TXSR............................................................................................................................58

Bank 16 Receive Control Register (0x04): RXCR...........................................................................................................................58

Bank 16 TXQ Memory Information Register (0x08): TXMIR...........................................................................................................59

Bank 16 RXQ Memory Information Register (0x0A): RXMIR..........................................................................................................59

Bank 17 TXQ Command Register (0x00): TXQCR.........................................................................................................................60

Bank 17 RXQ Command Register (0x02): RXQCR........................................................................................................................60

Bank 17 TX Frame Data Pointer Register (0x04): TXFDPR...........................................................................................................60

Bank 17 RX Frame Data Pointer Register (0x06): RXFDPR...........................................................................................................61

Bank 17 QMU Data Register Low (0x08): QDRL............................................................................................................................61

Bank 17 QMU Data Register High (0x0A): QDRH..........................................................................................................................61

Bank 18 Interrupt Enable Register (0x00): IER...............................................................................................................................62

Bank 18 Interrupt Status Register (0x02): ISR................................................................................................................................62

Bank 18 Receive Status Register (0x04): RXSR ............................................................................................................................63

Bank 18 Receive Byte Count Register (0x06): RXBC.....................................................................................................................64

Bank 18 Early Transmit Register (0x08): ETXR..............................................................................................................................64

Bank 18 Early Receive Register (0x0A): ERXR..............................................................................................................................65

Bank 19 Multicast Table Register 0 (0x00): MTR0..........................................................................................................................65

Bank 19 Multicast Table Register 1 (0x02): MTR1..........................................................................................................................65

Bank 19 Multicast Table Register 2 (0x04): MTR2..........................................................................................................................65

Bank 19 Multicast Table Register 3 (0x06): MTR3..........................................................................................................................66

Bank 19 Power Management Control and Status Register (0x08): PMCS .....................................................................................66

Banks 20 – 31: Reserved................................................................................................................................................................67

Bank 32 Chip ID and Enable Register (0x00): CIDER....................................................................................................................67

Bank 32 Chip Global Control Register (0x0A): CGCR ....................................................................................................................67

Banks 33 – 41: Reserved................................................................................................................................................................67

Bank 42 Indirect Access Control Register (0x00): IACR.................................................................................................................68

Bank 42 Indirect Access Data Register 1 (0x02): IADR1................................................................................................................68

Bank 42 Indirect Access Data Register 2 (0x04): IADR2................................................................................................................68

Bank 42 Indirect Access Data Register 3 (0x06): IADR3................................................................................................................68

Bank 42 Indirect Access Data Register 4 (0x08): IADR4................................................................................................................68

Bank 42 Indirect Access Data Register 5 (0x0A): IADR5................................................................................................................68

Bank 43 – 44: Reserved .................................................................................................................................................................69

Bank 45 PHY 1 MII-Register Basic Control Register (0x00): P1MBCR ..........................................................................................69

Bank 45 PHY 1 MII-Register Basic Status Register (0x02): P1MBSR............................................................................................70

Bank 45 PHY 1 PHYID Low Register (0x04): PHY1ILR..................................................................................................................71

Bank 45 PHY 1 PHYID High Register (0x06): PHY1IHR ................................................................................................................71

Bank 45 PHY 1 Auto-Negotiation Advertisement Register (0x08): P1ANAR ..................................................................................71

Bank 45 PHY 1 Auto-Negotiation Link Partner Ability Register (0x0A): P1ANLPR.........................................................................72

Bank 46: Reserved .........................................................................................................................................................................72

Bank 47 PHY1 LinkMD Control/Status (0x00): P1VCT...................................................................................................................72

Bank 47 PHY1 Special Control/Status Register (0x02): P1PHYCTRL............................................................................................73

Bank 48: Reserved .........................................................................................................................................................................73

Bank 49 Port 1 PHY Special Control/Status, LinkMD (0x00): P1SCSLMD.....................................................................................74

Bank 49 Port 1 Control Register 4 (0x02): P1CR4..........................................................................................................................75

Bank 49 Port 1 Status Register (0x04): P1SR ................................................................................................................................76

Banks 50 – 63: Reserved................................................................................................................................................................77

MIB (Management Information Base) Counters.............................................................................................78

Additional MIB Information..............................................................................................................................................................79

Absolute Maximum Ratings

Operating Ratings

(1)

..........................................................................................................................................80

Electrical Characteristics

(1)

..........................................................................................................................80

(1)

..............................................................................................................................81

Timing Specifications.......................................................................................................................................82

Asynchronous Timing without using Address Strobe (ADSN = 0)...................................................................................................82

November 2005 6

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

Asynchronous Timing using Address Strobe (ADSN).....................................................................................................................83

Asynchronous Timing using DATACSN..........................................................................................................................................84

Address Latching Timing for All Modes...........................................................................................................................................85

Synchronous Timing in Burst Write (VLBUSN = 1).........................................................................................................................86

Synchronous Timing in Burst Read (VLBUSN = 1).........................................................................................................................87

Synchronous Write Timing (VLBUSN = 0)......................................................................................................................................88

Synchronous Read Timing (VLBUSN = 0)......................................................................................................................................89

Auto Negotiation Timing..................................................................................................................................................................90

Reset Timing...................................................................................................................................................................................91

EEPROM Timing.............................................................................................................................................................................92

Selection of Isolation Transformers ...............................................................................................................93

Selection of Reference Crystal........................................................................................................................93

Package Information ........................................................................................................................................94

Acronyms and Glossary ..................................................................................................................................96

List of Figures

Figure 1. KSZ8841M Functional Diagram ..................................................................................................................................................1

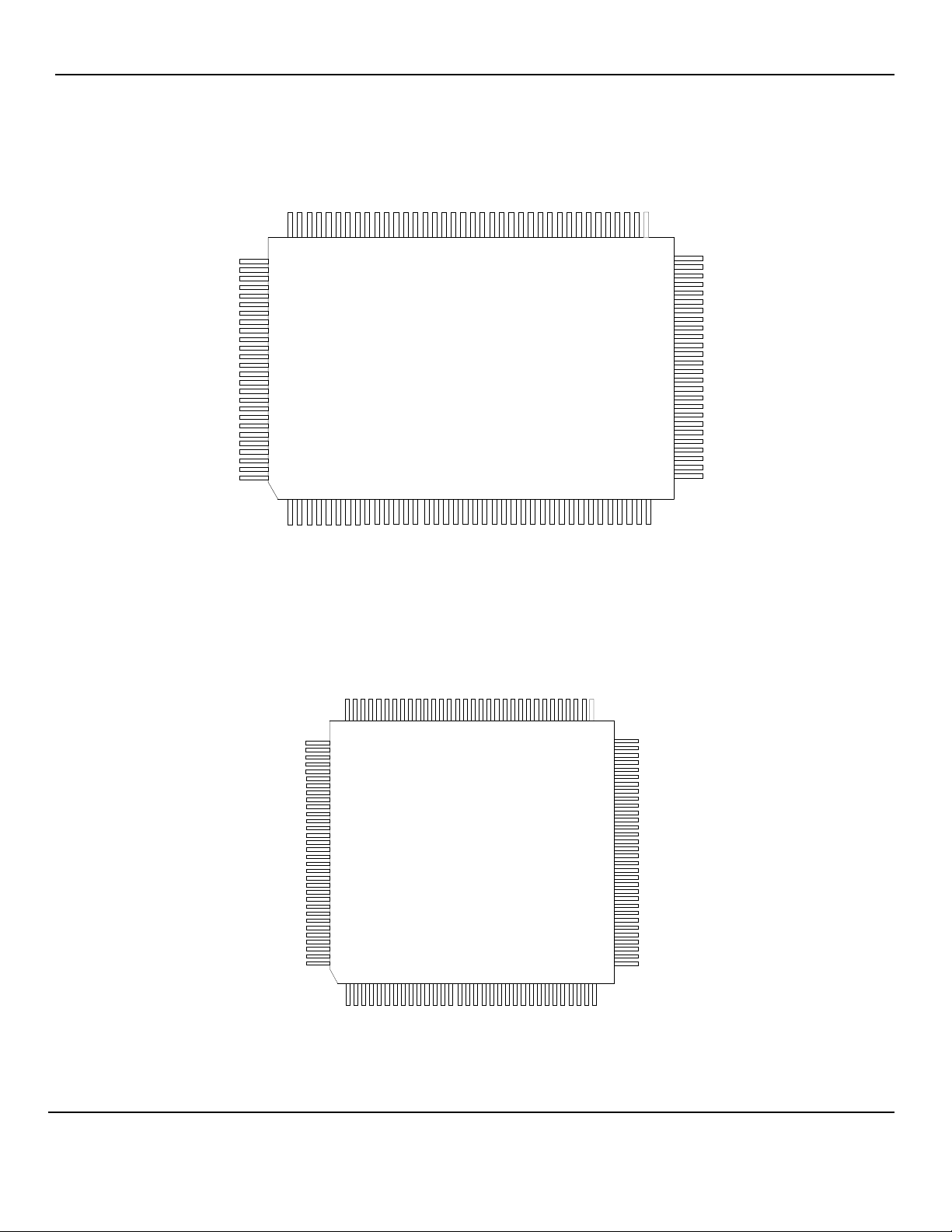

Figure 2. Standard – KSZ8841-16 MQL 128-Pin PQFP (Top View)...........................................................................................................9

Figure 3. Option – KSZ8841-16 MVL 128-Pin PQFP (Top View)...............................................................................................................9

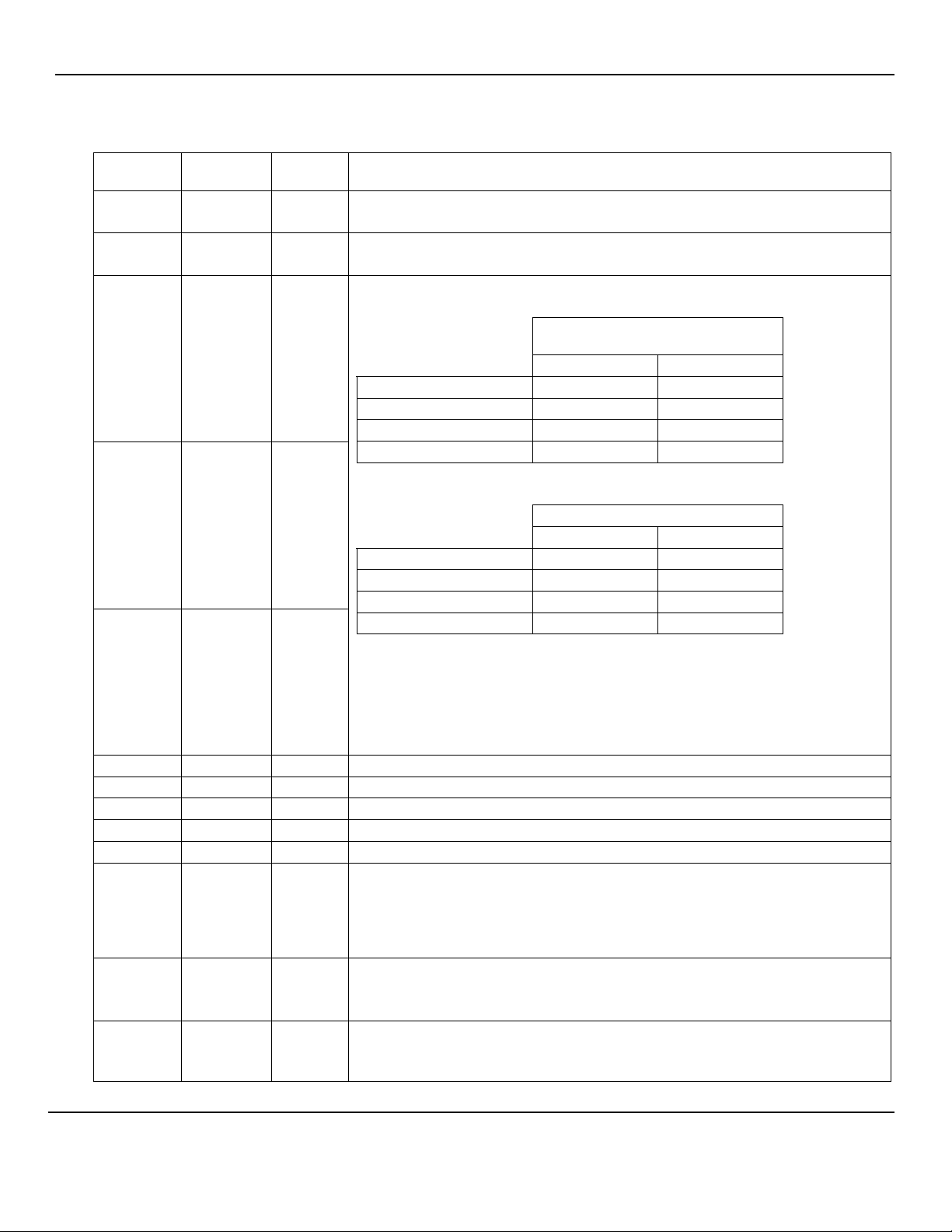

Figure 4. Standard – KSZ8841-32 MQL 128-Pin PQFP (Top View).........................................................................................................15

Figure 5. Option – KSZ8841-32 MVL 128-Pin PQFP (Top View).............................................................................................................15

Figure 6. Typical Straight Cable Connection............................................................................................................................................24

Figure 7. Typical Crossover Cable Connection........................................................................................................................................24

Figure 8. Auto Negotiation and Parallel Operation ...................................................................................................................................25

Figure 9. Mapping from the ISA, EISA, and VLBus to the KSZ8841M Bus Interface...............................................................................31

Figure 10. KSZ8841M 8-Bit, 16-Bit, and 32-Bit Data Bus Connections....................................................................................................31

Figure 11. PHY Port 1 Near-end (Remote) Loopback Path......................................................................................................................36

Figure 12. Asynchronous Cycle – ADSN = 0............................................................................................................................................82

Figure 13. Asynchronous Cycle – Using ADSN........................................................................................................................................83

Figure 14. Asynchronous Cycle – Using DATACSN ................................................................................................................................84

Figure 15. Address Latching Cycle for All Modes.....................................................................................................................................85

Figure 16. Synchronous Burst Write Cycles – VLBUSN = 1.....................................................................................................................86

Figure 17. Synchronous Burst Read Cycles – VLBUSN = 1 ....................................................................................................................87

Figure 18. Synchronous Write Cycle – VLBUSN = 0................................................................................................................................88

Figure 19. Synchronous Read Cycle – VLBUSN = 0................................................................................................................................89

Figure 20. Auto Negotiation Timing..........................................................................................................................................................90

Figure 21. Reset Timing...........................................................................................................................................................................91

Figure 22. EEPROM Read Cycle Timing Diagram..................................................................................................................................92

Figure 23. 128-Pin PQFP Package ..........................................................................................................................................................94

Figure 24. Optional 128-Pin LQFP Package ............................................................................................................................................95

November 2005 7

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

List of Tables

Table 1. MDI/MDI-X Pin Definitions……………………………………........................................................................................................24

Table 2. Bus Interface Unit Signal Grouping ............................................................................................................................................29

Table 3. Frame Format in Transmit Queue ..............................................................................................................................................32

Table 4. Transmit Control Word Bit Fields................................................................................................................................................32

Table 5. Transmit Byte Count Format ......................................................................................................................................................33

Table 6. Frame Format in Receive Queue ...............................................................................................................................................33

Table 7. RXQ Receive Packet Status Word.............................................................................................................................................34

Table 8. RXQ Receive Packet Byte Count Word......................................................................................................................................34

Table 9. KSZ8841M EEPROM Format.....................................................................................................................................................34

Table 10. ConfigParam Word in EEPROM Format ..................................................................................................................................35

Table 11. Format of MIB Counters ...........................................................................................................................................................78

Table 12. Port 1 MIB Counters Indirect Memory Offsets..........................................................................................................................79

Table 13. Maximum Ratings.....................................................................................................................................................................80

Table 14. Operating Ratings.....................................................................................................................................................................80

Table 15. Electrical Characteristics ..........................................................................................................................................................81

Table 16. Asynchronous Cycle (ADSN = 0) Timing Parameters ..............................................................................................................82

Table 17. Asynchronous Cycle using ADSN Timing Parameters.............................................................................................................83

Table 18. Asynchronous Cycle using DATACSN Timing Parameters......................................................................................................84

Table 19. Address Latching Timing Parameters.......................................................................................................................................85

Table 20. Synchronous Burst Write Timing Parameters...........................................................................................................................86

Table 21. Synchronous Burst Read Timing Parameters...........................................................................................................................87

Table 22. Synchronous Write (VLBUSN = 0) Timing Parameters ............................................................................................................88

Table 23. Synchronous Read (VLBUSN = 0) Timing Parameters............................................................................................................89

Table 24. Auto Negotiation Timing Parameters........................................................................................................................................ 90

Table 25. Reset Timing Parameters.........................................................................................................................................................91

Table 26. EEPROM Timing Parameters ...................................................................................................................................................92

Table 27. Transformer Selection Criteria..................................................................................................................................................93

Table 28. Qualified Single Port Magnetics................................................................................................................................................93

Table 29. Typical Reference Crystal Characteristics................................................................................................................................93

November 2005 8

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

Pin Configuration for KSZ8841-16 Chip (8/16-Bit)

NC

NC

A1

A4

A6

DGND

VDDIO

D15

D14

D13

D12

D11

D10

DGND

DGND

VDDIO

VDDC

DGND

BE0N

BE1N

VDDIO

NC

9998979695949392919089888786858483828180797877767574737271706968676665

101

102

100

NC

NC

NC

NC

NC

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

123456789

NCNCNCNCNCNCNCNCNC

KSZ8841-16

MQL

1011121314151617181920212223242526272829303132333435363738

NCA2A3

(To p Vie w )

A5

VDDIO

DGNDA7A9

A8

A10

A15

RSTN

A11

A12

X2

A13

X1

A14

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

AGND

VDDAP

AGND

ISE T

NC

NC

AGND

VDDA

NC

NC

AGND

NC

NC

VDDARX

VDDATX

TXM1

TXP1

AGND

RXM1

RXP1

NC

VDDA

AGND

NC

NC

AGND

DGND

NC

BCLK

PMEN

VDDIO

RDYRTNN

SRDYN

INTRN

LDEVN

RDN

EECS

NC

DGND

VDDCO

VLBUSN

EEEN

P1LED3

ARDY

CYCLEN

AEN

EEDI

SWR

WRN

EESK

EEDO

DGND

ADSN

PWRDN

AGND

VDDA

NCNCNC

P1LED1

P1LED2

P1LED0

TESTEN

SCANEN

Figure 2. Standard – KSZ8841-16 MQL 128-Pin PQFP (Top View)

DGND

VDDIO

D15

D14

D13

D12

D11

D10

DGND

DGND

VDDIO

NCA1A4

VDDC

DGNDNCBE0N

VDDIO

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

96959493929190898887868584838281807978777675747372717069686766

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

123456789

BE1NNCA2

KSZ8841-16

MVL

(Top V ie w )

1011121314151617181920212223242526272829303132

A6

A8

A5

VDDIO

DGNDA7A9

A3

A15

RSTN

A11

A10

X2

A13

A12

X1

A14

65

64

AGND

63

VDDAP

62

AGND

61

ISET

60

NC

59

NC

58

AGND

57

VDDA

56

NC

55

NC

54

AGND

53

NC

52

NC

51

VDDARX

50

VDDATX

49

TXM1

48

TXP1

47

AGND

46

RXM1

45

RXP1

44

NC

43

VDDA

42

AGND

41

NC

40

NC

AGND

39

VDDA

38

AGND

37

36

PWRDN

35

ADSN

DGND

34

33

WRN

NCNCNC

DGND

P1LED1

P1LED2

TESTEN

SCANEN

VDDIO

P1LED0

RDYRTNN

Figure 3. Option – KSZ8841-16 MVL 128-Pin PQFP (Top View)

November 2005 9

NC

BCLK

PMEN

INTRN

SRDYN

NC

RDN

EECS

ARDY

LDEVN

EEEN

DGND

VDDCO

VLBUSN

CYCLEN

AEN

SWR

EEDI

EESK

EEDO

P1LED3

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

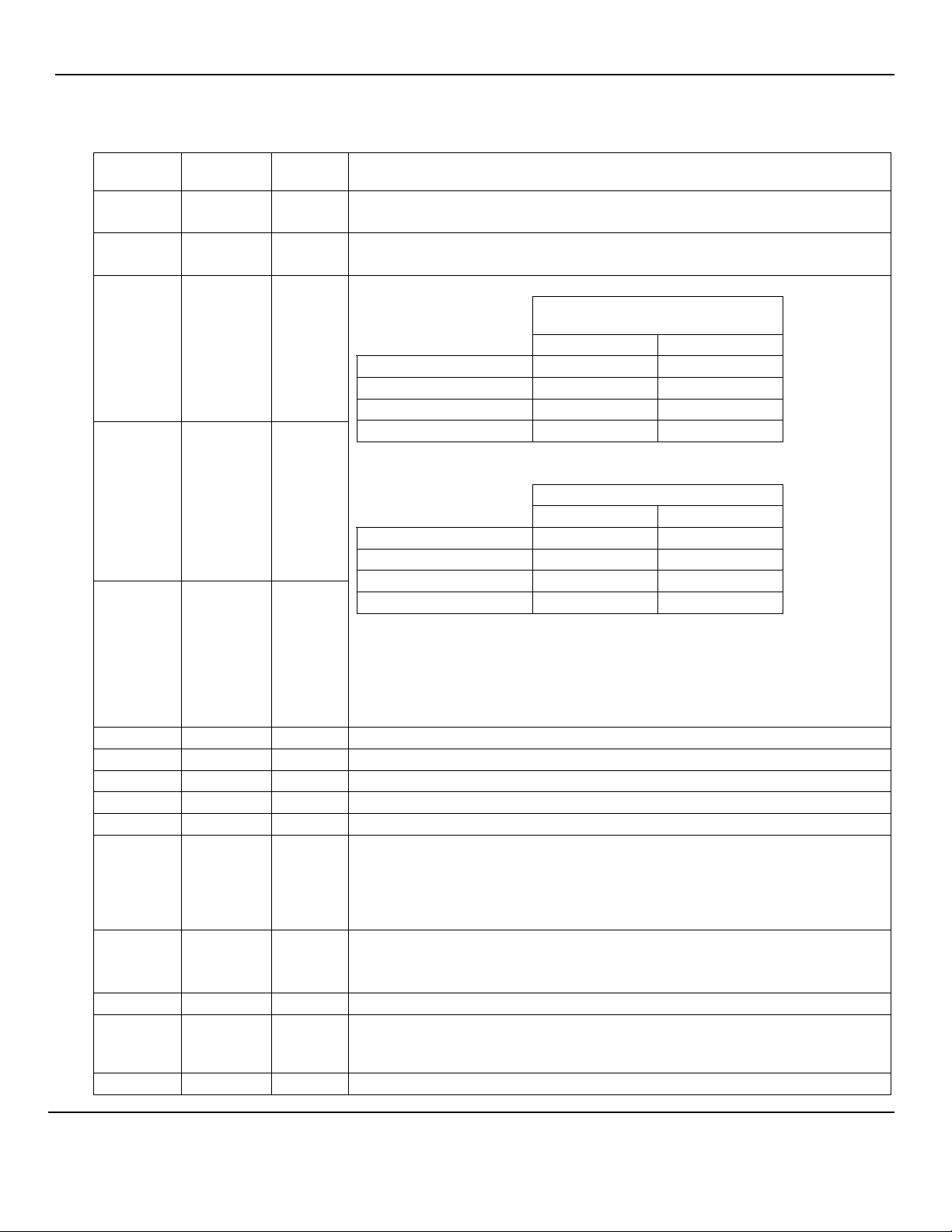

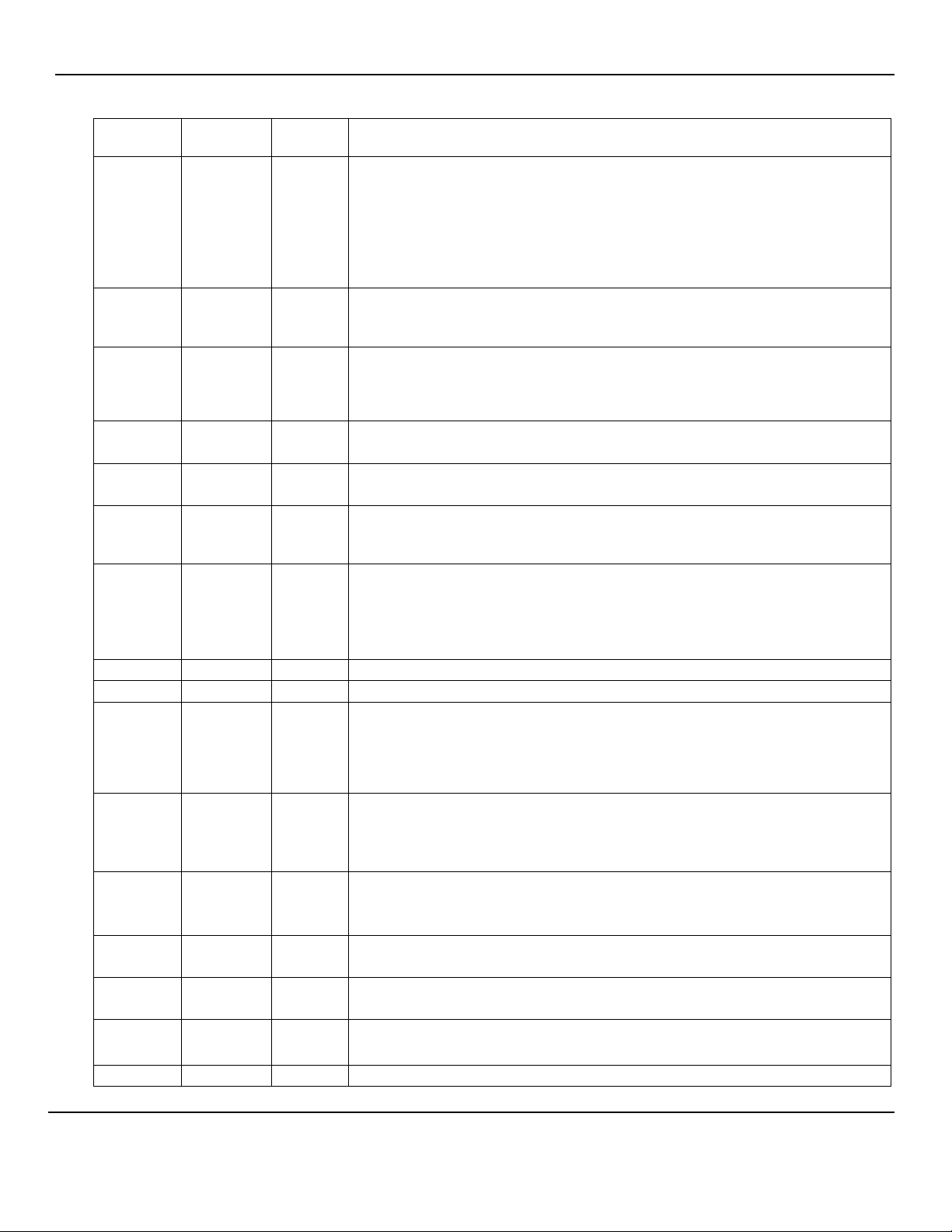

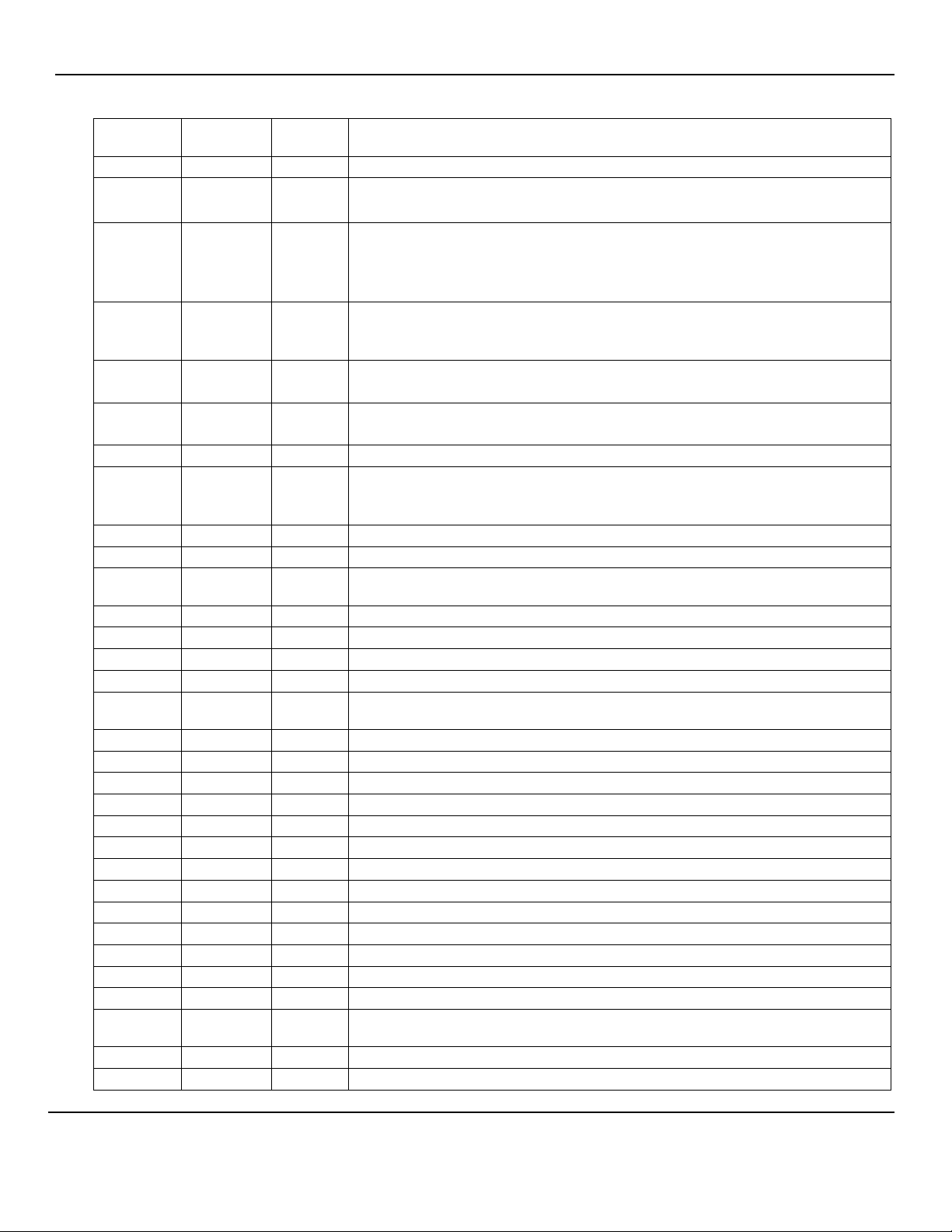

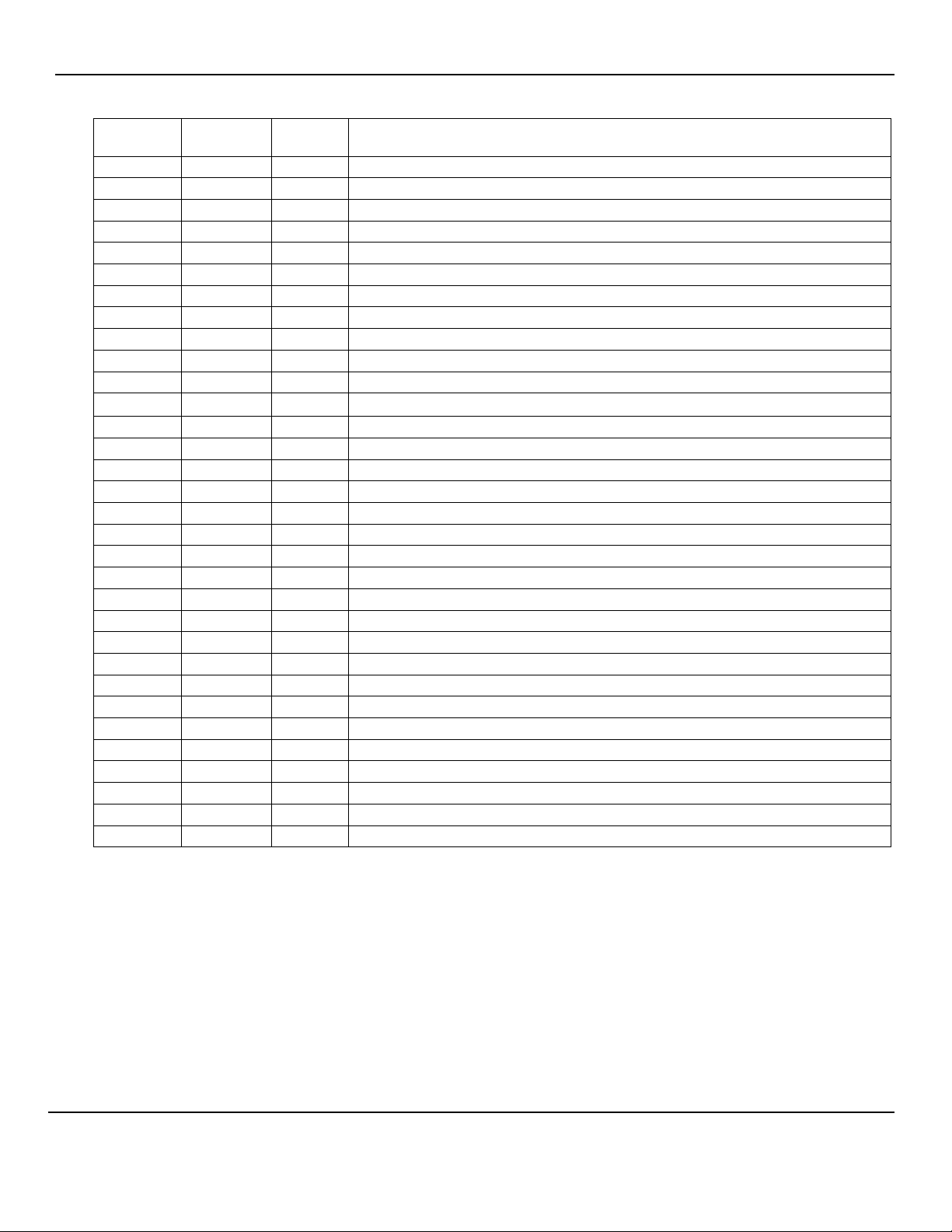

Pin Description for KSZ8841-16 Chip (8/16-Bit)

Pin

Number

1 TEST_EN I Test Enable

2 SCAN_EN I Scan Test Scan Mux Enable

3 P1LED2 Opu

4 P1LED1 Opu

5 P1LED0 Opu

Pin Name Type Pin Function

For normal operation, pull-down this pin to ground.

For normal operation, pull-down this pin to ground.

Port 1 LED indicators

[0,0] Default [0,1]

P1LED32 — —

P1LED2 Link/Act 100Link/Act

P1LED1 Full duplex/Col 10Link/Act

P1LED0 Speed Full duplex

Reg. CGCR bit [15,9]

[1,0] [1,1]

P1LED32 Act —

P1LED2 Link —

P1LED1 Full duplex/Col —

P1LED0 Speed —

Notes:

1. Link = On; Activity = Blink; Link/Act = On/Blink; Full Dup/Col = On/Blink;

Full Duplex = On (Full duplex); Off (Half duplex)

Speed = On (100BASE-T); Off (10BASE-T)

2. P1LED3 is pin 27.

1

defined as follows:

Chip Global Control Register: CGCR

bit [15,9]

6 NC Opu No Connect.

7 NC Opu No Connect.

8 NC Opu No Connect.

9 DGND Gnd Digital ground

10 VDDIO P 3.3V digital V

11 RDYRTNN Ipd Ready Return Not:

For VLBus-like mode: Asserted by the host to complete synchronous read cycles. If

the host doesn’t connect to this pin, assert this pin.

For burst mode (32-bit interface only): Host drives this pin low to signal waiting

states.

12 BCLK Ipd Bus Interface Clock

Local bus clock for synchronous bus systems. Maximum frequency is 50MHz.

This pin should be tied Low or unconnected if it is in asynchronous mode.

13 NC Ipu No Connect.

14 PMEN Opu Power Management Event Not

When asserted (Low), this signal indicates that a power management event has

occurred in the system when a wake-up signal is detected by KSZ8841M.

15 SRDYN Opu Synchronous Ready Not

DDIO

November 2005 10

input power supply for IO with well decoupling capacitors.

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

Pin

Number

16 INTRN Opd Interrupt

17 LDEVN Opd Local Device Not

18 RDN Ipd Read Strobe Not

19 EECS Opu EEPROM Chip Select

20 ARDY Opd Asynchronous Ready

21 CYCLEN Ipd Cycle Not

22 NC Opd No Connect

23 DGND Gnd Digital IO ground

24 VDDCO P 1.2V digital core voltage output (internal 1.2V LDO power supply output), this 1.2V

25 VLBUSN Ipd VLBus-like Mode

26 EEEN Ipd EEPROM Enable

27 P1LED3 Opd Port 1 LED indicator

28 EEDO Opd EEPROM Data Out

29 EESK Opd EEPROM Serial Clock

30 EEDI Ipd EEPROM Data In

Pin Name Type Pin Function

Ready signal to interface with synchronous bus for both EISA-like and VLBus-like

extend accesses.

For VLBus-like mode, the falling edge of this signal indicates ready. This signal is

synchronous to the bus clock signal BCLK.

For burst mode (32-bit interface only), the KSZ8841M drives this pin low to signal

wait states.

Active Low signal to host CPU to indicate an interrupt status bit is set, this pin need

an external 4.7K pull-up resistor.

Active Low output signal, asserted when AEN is Low and A15-A4 decode to the

KSZ8841M address programmed into the high byte of the base address register.

LDEVN is a combinational decode of the Address and AEN signal.

Asynchronous read strobe, active Low.

This signal is used to select an external EEPROM device.

ARDY may be used when interfacing asynchronous buses to extend bus access

cycles. It is asynchronous to the host CPU or bus clock.

For VLBus-like mode cycle signal; this pin follows the addressing cycle to signal the

command cycle.

For burst mode (32-bit interface only), this pin stays High for read cycles and Low for

write cycles.

output pin provides power to VDDC, VDDA and VDDAP pins.

Note: Internally generated power voltage. Do not connect an external power supply

to this pin. This pin is used for connecting external filter (Ferrite bead and

capacitors).

Pull-down or float: Bus interface is configured for synchronous mode.

Pull-up: Bus interface is configured for 8-bit or 16-bit asynchronous mode or EISA-

like burst mode.

EEPROM is enabled and connected when this pin is pull-up.

EEPROM is disabled when this pin is pull-down or no connect.

See the description in pins 3, 4, and 5.

This pin is connected to DI input of the serial EEPROM.

A 4

µs serial output clock to load configuration data from the serial EEPROM.

November 2005 11

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

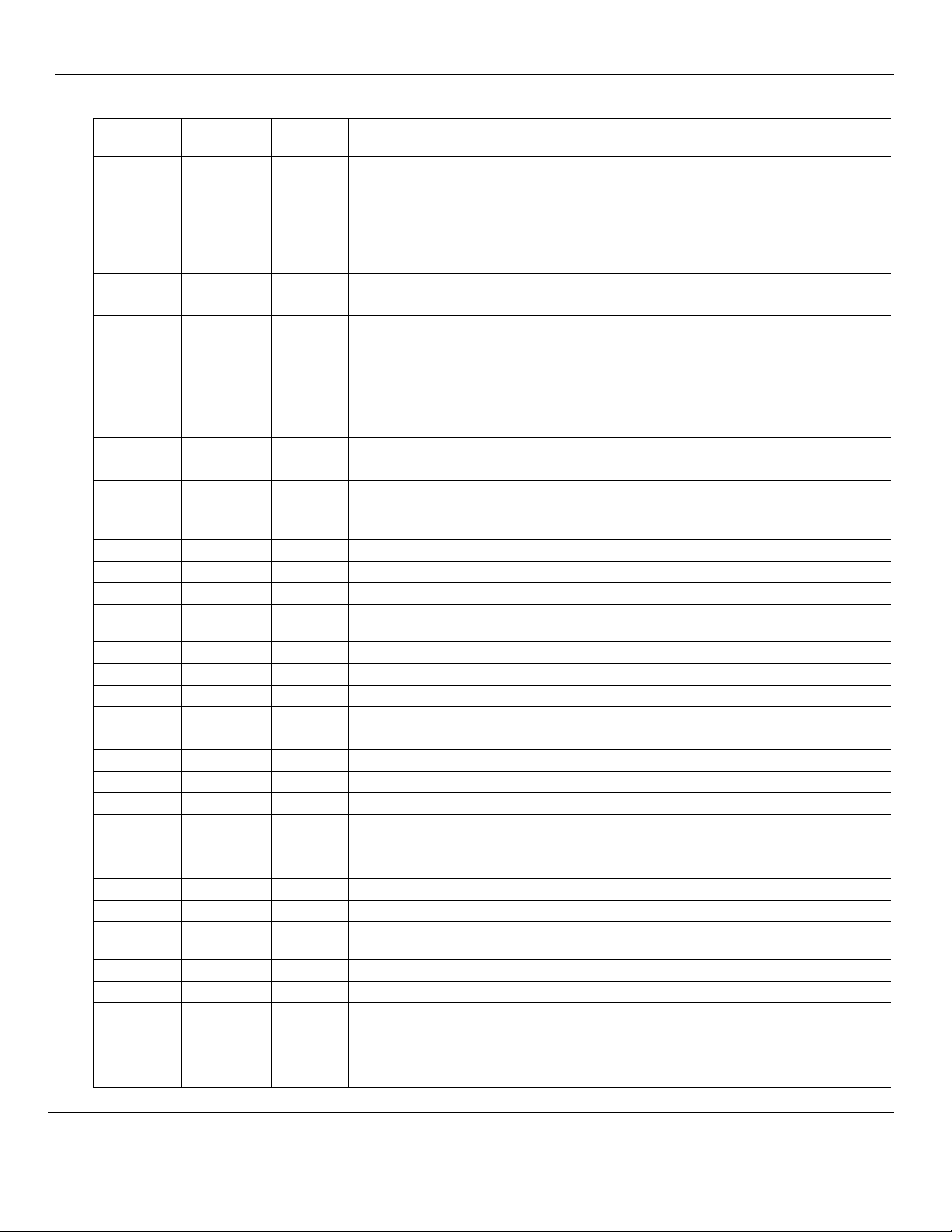

Pin

Number

31 SWR Ipd Synchronous Write/Read

32 AEN Ipd Address Enable

33 WRN Ipd Write Strobe Not

34 DGND Gnd Digital IO ground

35 ADSN Ipd Address Strobe Not

36 PWRDN I Full-chip power-down. Active Low (Low = Power down; High = Normal operation).

37 AGND Gnd Analog ground

38 VDDA P 1.2V analog V

39 AGND Gnd Analog ground

40 NC — No Connect

41 NC — No Connect

42 AGND Gnd Analog ground

43 VDDA P 1.2V analog V

44 NC — No Connect

45 RXP1 I/O Port 1 physical receive (MDI) or transmit (MDIX) signal (+ differential)

46 RXM1 I/O Port 1 physical receive (MDI) or transmit (MDIX) signal (– differential)

47 AGND Gnd Analog ground

48 TXP1 I/O Port 1 physical transmit (MDI) or receive (MDIX) signal (+ differential)

49 TXM1 I/O Port 1 physical transmit (MDI) or receive (MDIX) signal (– differential)

50 VDDATX P 3.3V analog V

51 VDDARX P 3.3V analog V

52 NC — No Connect

53 NC — No Connect

54 AGND Gnd Analog ground

55 NC — No Connect

56 NC — No Connect

57 VDDA P 1.2 analog V

58 AGND Gnd Analog ground

59 NC Ipu No connect

60 NC Ipu No connect

61 ISET O Set physical transmits output current.

62 AGND Gnd Analog ground

Pin Name Type Pin Function

This pin is connected to DO output of the serial EEPROM when EEEN is pull-up.

This pin can be pull-down for 8-bit bus mode, pull-up for 16-bus mode or don’t care

for 32-bus mode when EEEN is pull-down (without EEPROM).

Write/Read signal for synchronous bus accesses. Write cycles when high and Read

cycles when low.

Address qualifier for the address decoding, active Low.

Asynchronous write strobe, active Low.

For systems that require address latching, the rising edge of ADSN indicates the

latching moment of A15-A1 and AEN.

bead and capacitor.

bead and capacitor.

bead and capacitor.

Pull-down this pin with a 3.01K 1% resistor to ground.

input power supply from VDDCO (pin24) through external Ferrite

DD

input power supply from VDDCO (pin24) through external Ferrite

DD

input power supply with well decoupling capacitors.

DD

input power supply with well decoupling capacitors.

DD

input power supply from VDDCO (pin24) through external Ferrite

DD

November 2005 12

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

Pin

Number

63 VDDAP P 1.2V analog VDD for PLL input power supply from VDDCO (pin24) through external

64 AGND Gnd Analog ground

65 X1 I

66 X2 O

67 RSTN Ipu Reset Not

68 A15 I Address 15

69 A14 I Address 14

70 A13 I Address 13

71 A12 I Address 12

72 A11 I Address 11

73 A10 I Address 10

74 A9 I Address 9

75 A8 I Address 8

76 A7 I Address 7

77 A6 I Address 6

78 DGND Gnd Digital IO ground

79 VDDIO P 3.3V digital V

80 A5 I Address 5

81 A4 I Address 4

82 A3 I Address 3

83 A2 I Address 2

84 A1 I Address 1

85 NC I No Connect

86 NC I No Connect

87 BE1N I Byte Enable 1 Not, Active low for Data byte 1 enable (don’t care in 8-bit bus mode).

88 BE0N I Byte Enable 0 Not, Active low for Data byte 0 enable (there is an internal inverter

89 NC I No Connect

90 DGND Gnd Digital core ground

91 VDDC P

92 VDDIO P 3.3V digital V

93 NC I No Connect

94 NC I No Connect

95 NC I No Connect

96 NC I No Connect

97 NC I No Connect

98 NC I No Connect

99 NC I No Connect

Pin Name Type Pin Function

Ferrite bead and capacitor.

25MHz crystal or oscillator clock connection.

Pins (X1, X2) connect to a crystal. If an oscillator is used, X1 connects to a 3.3V

tolerant oscillator and X2 is a no connect.

Note: Clock requirement is ± 50ppm for either crystal or oscillator.

Hardware reset pin (active Low). This reset input is required minimum of 10ms low

after stable supply voltage 3.3V.

enabled and connected to the BE1N for 8-bit bus mode).

1.2V digital core V

Ferrite bead and capacitor.

input power supply for IO with well decoupling capacitors.

DDIO

input power supply from VDDCO (pin24) through external

DD

input power supply for IO with well decoupling capacitors.

DDIO

November 2005 13

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

Pin

Number

100 NC I No Connect

101 NC I No Connect

102 NC I No Connect

103 NC I No Connect

104 NC I No Connect

105 NC I No Connect

106 NC I No Connect

107 DGND Gnd Digital IO ground

108 VDDIO P

109 NC I No Connect

110 D15 I/O Data 15

111 D14 I/O Data 14

112 D13 I/O Data 13

113 D12 I/O Data 12

114 D11 I/O Data 11

115 D10 I/O Data 10

116 D9 I/O Data 9

117 D8 I/O Data 8

118 D7 I/O Data 7

119 D6 I/O Data 6

120 D5 I/O Data 5

121 D4 I/O Data 4

122 D3 I/O Data 3

123 DGND Gnd Digital IO ground

124 DGND Gnd Digital core ground

125 VDDIO P 3.3V digital V

126 D2 I/O Data 2

127 D1 I/O Data 1

128 D0 I/O Data 0

Pin Name Type Pin Function

3.3V digital V

input power supply for IO with well decoupling capacitors.

DDIO

input power supply for IO with well decoupling capacitors.

DDIO

Legend:

P = Power supply Gnd = Ground

I/O = Bi-directional I = Input O = Output.

Ipd = Input with internal pull-down.

Ipu = Input with internal pull-up.

Opd = Output with internal pull-down.

Opu = Output with internal pull-up.

November 2005 14

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

Pin Configuration for KSZ8841-32 Chip (32-Bit)

D21

D22

D24

D25

D26

D28

D20

D19

D18

D17

DGND

VDDIO

D16

D15

D14

D13

D12

D11

D10

D6

D5

D4

D3

DGND

DGND

VDDIO

D2

D0

D27

D29

D30

VDDC

D23

9998979695949392919089888786858483828180797877767574737271706968676665

101

102

100

103

104

105

106

107

108

109

110

111

112

113

114

115

D9

D8

D7

D1

116

117

118

119

120

121

122

123

124

125

126

127

128

123456789

VDDIO

KSZ8841-32

MQL

1011121314151617181920212223242526272829303132333435363738

BE2N

DGND

D31

A1

BE0N

BE1N

BE3NA2A3

(Top View)

A4

A5

VDDIO

A6

A8

DGNDA7A9

A10

A11

A12

A13

A14

A15

RSTN

X2

X1

AGND

64

VDDAP

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

AGND

ISET

NC

NC

AGND

VDDA

NC

NC

AGND

NC

NC

VDDARX

VDDATX

TXM1

TXP1

AGND

RXM1

RXP1

NC

VDDA

AGND

NC

NC

AGND

NCNCNC

P1LED1

P1LED2

P1LED0

TESTEN

SCANEN

BCLK

VDDIO

RDYRTNN

PMEN

INTRN

LDEVN

SRDYN

DATACSN

DGND

RDN

NC

EECS

ARDY

CYCLEN

EEEN

DGND

VDDCO

P1LED3

VLBUSN

AEN

SWR

EEDI

WRN

EESK

EEDO

ADSN

AGND

DGND

VDDA

PWRDN

Figure 4. Standard – KSZ8841-32 MQL 128-Pin PQFP (Top View)

BE2N

A1

A4

A6

DGND

VDDIO

D10

DGND

DGND

VDDIO

D26

D25

D24

D23

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

D11

VDDC

DGND

D31

BE0N

VDDIO

BE1N

D28

D27

D29

D30

96959493929190898887868584838281807978777675747372717069686766

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

D9

D8

117

D7

118

D6

119

D5

120

D4

121

D3

122

123

124

125

D2

126

D1

127

D0

128

123456789

BE3NA2A3

KSZ8841-32

MVL

(Top View )

1011121314151617181920212223242526272829303132

A5

VDDIO

A8

DGNDA7A9

A15

RSTN

A11

A10

X2

A13

A12

X1

A14

65

64

AGND

63

VDDAP

62

AGND

61

ISET

60

NC

59

NC

58

AGND

57

VDDA

56

NC

55

NC

54

AGND

53

NC

52

NC

51

VDDARX

50

VDDATX

49

TXM1

48

TXP1

47

AGND

46

RXM1

45

RXP1

44

NC

43

VDDA

42

AGND

41

NC

40

NC

AGND

39

VDDA

38

AGND

37

36

PWRDN

35

ADSN

DGND

34

33

WRN

NCNCNC

BCLK

DGND

TESTEN

P1LED1

P1LED2

SCANEN

VDDIO

P1LED0

RDYRTNN

Figure 5. Option – KSZ8841-32 MVL 128-Pin PQFP (Top View)

November 2005 15

NC

RDN

EECS

PMEN

DATACSN

ARDY

INTRN

LDEVN

SRDYN

EEEN

DGND

VDDCO

VLBUSN

CYCLEN

AEN

SWR

EEDI

EESK

EEDO

P1LED3

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

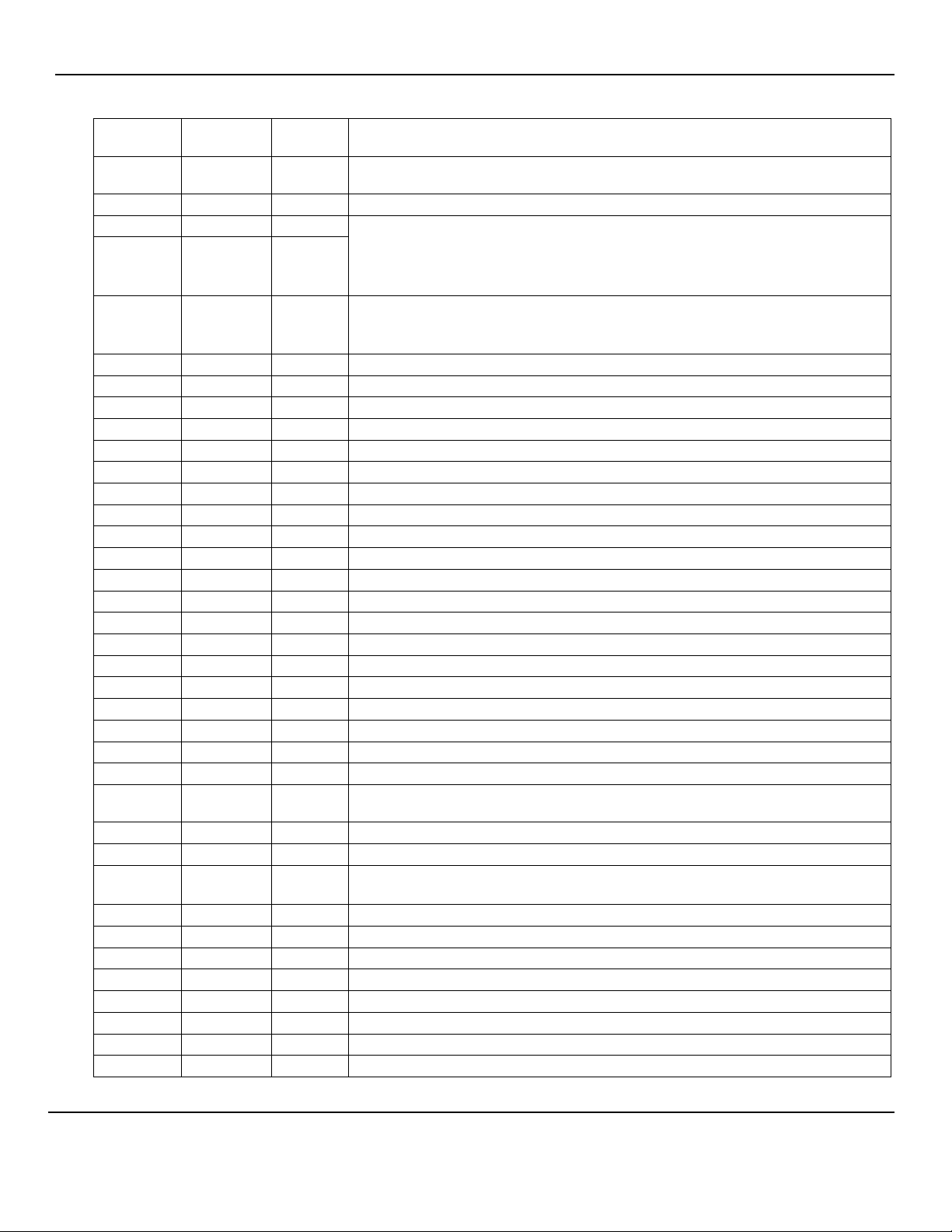

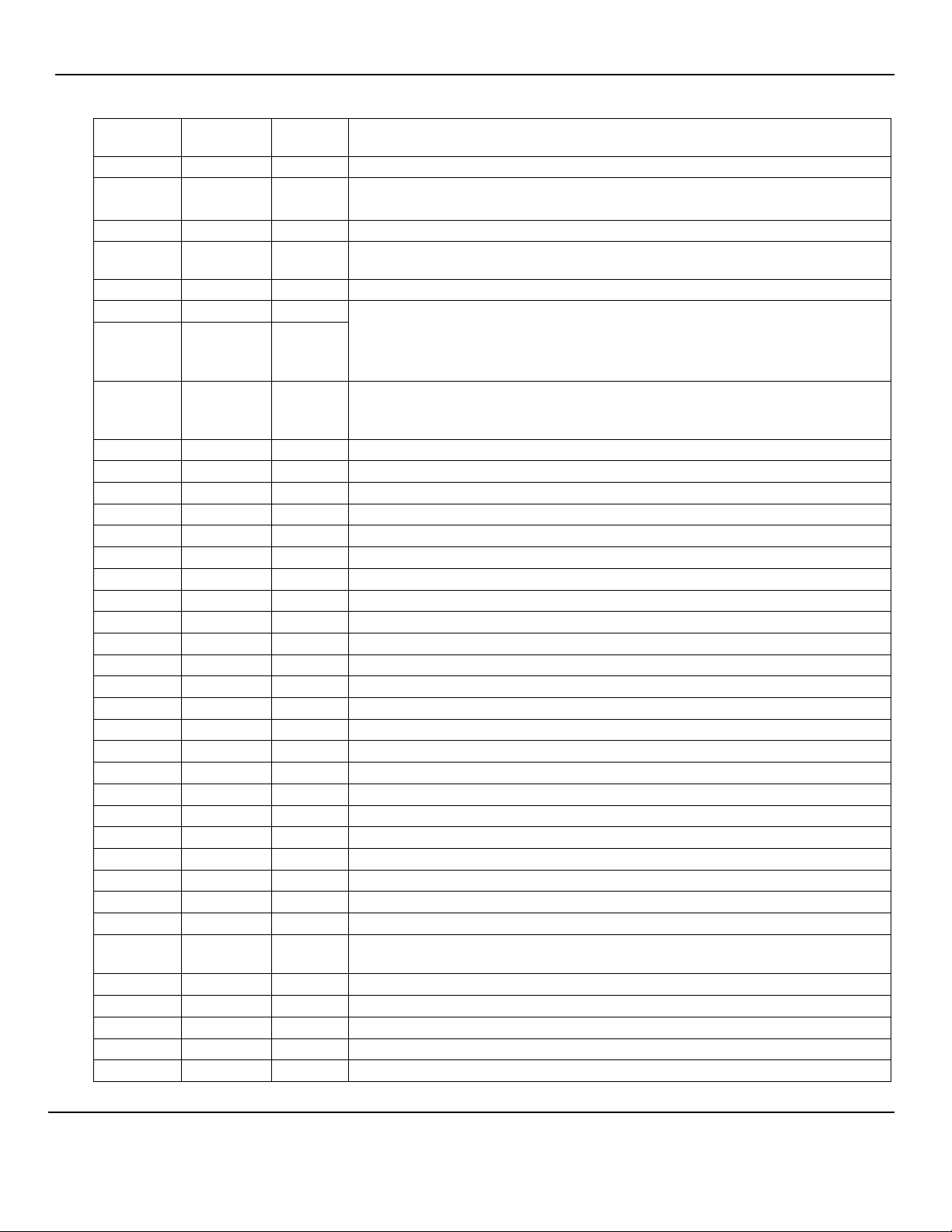

p

Pin Description for K

SZ8841-32 Chip (32-Bit)

Pin

Number

1 TEST_EN I Test Enable

2 SCAN_EN I Scan Test Scan Mux Enable

3 P1LED2 Opu

4 P1LED1 Opu

5 P1LED0 Opu

Pin Name Type Pin Function

For normal operation, pull-down this pin to ground.

For normal operation, pull-down this pin to ground.

Port 1 LED indicators

[0,0] Default [0,1]

P1LED32 — —

P1LED2 Link/Act 100Link/Act

P1LED1 Full duplex/Col 10Link/Act

P1LED0 Speed Full duplex

Reg. CGCR bit [15,9]

[1,0] [1,1]

P1LED32 Act —

P1LED2 Link —

P1LED1 Full duplex/Col —

P1LED0 Speed —

Notes:

1. Link = On; Activity = Blink; Link/Act = On/Blink; Full Dup/Col = On/Blink;

Full Duplex = On (Full duplex); Off (Half duplex)

Speed = On (100BASE-T); Off (10BASE-T)

2. P1LED3 is pin 27.

1

defined as follows:

Chip Global Control Register: CGCR

bit [15,9]

6 NC Opu No Connect.

7 NC Opu No Connect.

8 NC Opu No Connect.

9 DGND Gnd Digital ground

10 VDDIO P 3.3V digital V

11 RDYRTNN Ipd Ready Return Not:

For VLBus-like mode: Asserted by the host to complete synchronous read cycles. If

the host doesn’t connect to this pin, assert this pin.

For burst mode (32-bit interface only): Host drives this pin low to signal waiting

states.

12 BCLK Ipd Bus Interface Clock

Local bus clock for synchronous bus systems. Maximum frequency is 50MHz.

This pin should be tied Low or unconnected if it is in asynchronous mode.

13 DATACSN Ipu DATA Chip Select Not (For KSZ8841-32 Mode only)

Chip select signal for QMU data register (QDRH, QDRL), active Low.

When DATACSN is Low, the data

input power supply for IO with well decoupling capacitors.

DDIO

ath can be accessed regardless of the value of

November 2005 16

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

Pin

Number

14 PMEN Opu Power Management Event Not

15 pu

16 INTRN Opd Interrupt

17 LDEVN Opd Local Device Not

18 RDN Ipd Read Strobe Not

19 EECS Opu EEPROM Chip Select

20 ARDY Opd A us Ready

21 CYCLEN Ipd ot

22 NC Opd No Connect

23 D nd DGN Gnd Digital IO grou

24 CO re voltage output (internal 1.2V LDO power supply output), this 1.2V

25 VLBUSN Ipd VLBus-like Mode

26 EEEN Ipd EEPROM Enable

27 P1LED3 Opd Port 1 LED indicator

28 EEDO Opd EEPROM Data Out

Pin Name Type Pin Function

AEN, A15-A1, and the content of the BANK select register.

When asserte

occurred in the system when a wake-up signal is de

SRDYN O Synchronous Ready Not

Ready signal to interface with synchronous bus for b

extend accesses.

F

or VLBus-like mode, the falling edge of this signal indicates ready. This signal is

sy

nchronous to the bus clock signal BCLK.

o ce only), the KSZ8841M drives this pin low

F r burst mode (32-bit interfa to signal

a

w it states.

Active Low ignal to host CPU te an interrupt status bit is set, this pin need

n external

a 4.7K pull-up resis

ctive Low erted wh ow and A15-

A output signal, ass en AEN is L A4 decode to the

K

SZ8841M address programmed into the high byte of the base address register.

L

DEVN is a combinational decode of the Address and AEN signal.

Asynchronous read strobe, active Low.

T is used to select a rnal EEPROM ice.

his signal n exte dev

synchrono

ARDY may be used when interfacing asy

ycles. It is

c asynchronous to the host CPU or bus clock.

Cycle N

For VLBus-like mode cycle signal; this pin follows the addressing cycle to si

command cycle.

For burst mode (32-bit interface only), this pin

write cycles.

VDD P 1.2V digital co

output pin pro

Note: Internally

to this pin. Thi in is used for connecting external filter (Ferrite bead and

capacitors).

Pull-down or float: Bus interface is configured for synchronous mode.

Pull-up: Bus interface is configured for 32-bit asynchronous mode or EISA-like b

mode.

EEPROM is enabled and connected when this pin is pull-up.

EEPROM is disabled when this pin is pull-down or no connect.

See the description in pins 3, 4, and 5.

d (Low), this signal indicates that a power management event has

s to indica

vides power to VDDC, VDDA and VDDAP pins.

generated power voltage. Do not connect an external power supply

p

s

tected by KSZ8841M.

oth EISA-like and VLBus-like

tor

nchronous buses to extend bus access

gnal the

stays High for read cycles and Low for

urst

November 2005 17

Rev 1.3

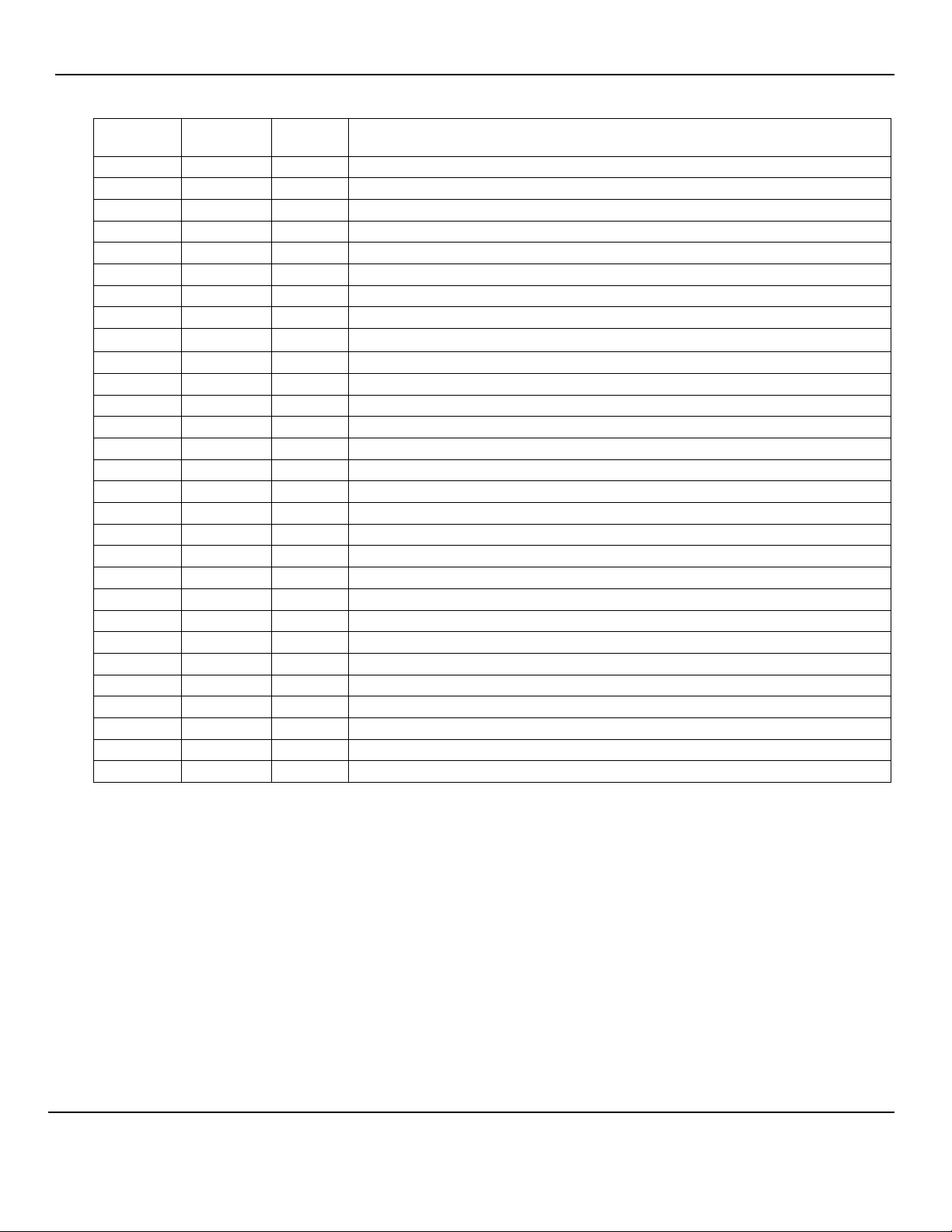

Micrel Confidential KSZ8841-16/32 MQL/MVL

Pin

Number

29 EESK Opd EEPROM Serial Clock

30 EEDI Ipd EEPROM Data In

31 SWR Ipd d Synchronous Write/Read

32 AEN Ipd Address Enable

33 WRN Ipd

34 DGND Gnd Digital IO ground

35 ADSN Ipd

36 PWRDN I Power down; High = Normal operation). Full-chip power-down. Active Low (Low =

37 AGND Gnd Analog ground

38 VDDA P rough external Ferrite 1.2V analog V

39 AGND Gnd Analog ground

40 NC — No Connect

41 NC — No Connect

42 AGND Gnd Analog ground

43 VDDA P 1.2V analog V

44 NC — No Connect

45 RXP1 I/O Port 1 physical receive (MDI) or transmit (MDIX) signal (+ differential)

46 RXM1 I/O Port 1 physical receive (MDI) or transmit (MDIX) signal (– differential)

47 AGND Gnd Analog ground

48 TXP1 I/O Port 1 physical transmit (MDI) or receive (MDIX) signal (+ differential)

49 TXM1 I/O Port 1 physical transmit (MDI) or receive (MDIX) signal (– differential)

50 VDDATX P 3.3V analog V

51 VDDARX P 3.3V analog V

52 NC — No Connect

53 NC — No Connect

54 AGND Gnd Analog ground

55 NC — No Connect

56 NC — No Connect

57 VDDA P 1.2 analog V

58 AGND Gnd Analog ground

59 NC Ipu No connect

November 2005 18

Pin Name Type Pin Function

This pin is connected to DI input of the serial EEPROM.

A 4

µs serial output clock to load configuration data from the serial EEPROM.

This pin is connected to D

This pin can be pull-down for 8-bit bus mode, pull-up for 16-bus mode or don’t care

for 32-bus mode w

Write/Read signal for synchronous bus accesses. Write cycles when high and Rea

cycles when low.

Address qualifier for the address decoding, active Low.

Write Strobe Not

Asynchronous writ

Address Strobe Not

For systems that require address latching,

latching moment o

bead and capacitor.

bead and capacitor.

bead and capacitor.

O output of the serial EEPROM when EEEN is pull-up.

hen EEEN is pull-down (without EEPROM).

e strobe, active Low.

the rising edge of ADSN indicates the

f A15-A1 and AEN.

input power supply from VDDCO (pin24) th

DD

input power supply from VDDCO (pin24) through external Ferrite

DD

input power supply with well decoupling capacitors.

DD

input power supply with well decoupling capacitors.

DD

input power supply from VDDCO (pin24) through external Ferrite

DD

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

Pin

Number

60 NC Ipu No connect

61 ISET O Set physical transmits output current.

62 AGND Gnd Analog ground

63 VDDAP P 1.2V analog VDD for PLL input power supply from VDDCO (pin24) through external

64 AGND Gnd Analog ground

65 X1 I

66 X2 O

67 RSTN Ipu

68 A15 I Address 15

69 A14 I Address 14

70 A13 I Address 13

71 A12 I Address 12

72 A11 I Address 11

73 A10 I Address 10

74 A9 I Address 9

75 A8 I Address 8

76 A7 I Address 7

77 A6 I Address 6

78 DGND und Gnd Digital IO gro

79 VDDIO P 3.3V digital V

80 A5 I Address 5

81 A4 I Address 4

82 A3 I Address 3

83 A2 I Address 2

84 A1 I Address 1

85 BE3N I Byte Enable 3 Not, Active low for Data byte 3 enable

86 BE2N I Byte Enable 2 Not, Active low for Data byte 2 enable

87 BE1N I Byte Enable 1 Not, Active low for Data byte 1 enable

88 BE0N I Byte Enable 0 Not, Active low for Data byte 0 enable

89 D31 I/O Data 31

90 DGND round Gnd Digital core g

91 VDDC P

92 VDDIO

93 D30 I/O Data 30

94 D29 I/O Data 29

95 D28 I/O Data 28

96 D27 I/O Data 27

Pin Name Type Pin Function

Pull-down this pin with a 3.01K 1% resistor to ground.

Ferrite bead and capacitor.

25MHz crystal or oscillator

Pins (X1, X2) connect to a crystal. If an oscillator is used, X1 connects to a 3.3V

tolerant oscillator a

Note: Clock requi

Reset Not

Hardware reset pi

after stable supply voltage 3.3V.

1.2V digital core

Ferrite bead and

clock connection.

nd X2 is a no connect.

rement is ± 50ppm for either crystal or oscillator.

n (active Low). This reset input is required minimum of 10ms low

input power supply for IO with well decoupling capacitors.

DDIO

input power supply from VDDCO (pin24) through external

V

DD

capacitor.

input power supply for IO with well decoupling capacitors. P 3.3V digital V

DDIO

November 2005 19

Rev 1.3

Micrel Confidential KSZ8841-16/32 MQL/MVL

Pin

Number

97 D26 I/O Data 26

98 D25 I/O Data 25

99 D24 I/O Data 24

100 D23 I/O Data 23

101 D22 I/O Data 22

102 D21 I/O Data 21

103 D20 I/O Data 20

104 D19 I/O Data 19

105 D18 I/O Data 18

106 D17 I/O Data 17

107 DGND Gnd Digital IO ground

108 VDDIO P

109 D16 I/O Data 16

110 D15 I/O Data 15

111 D14 I/O Data 14

112 D13 I/O Data 13

113 D12 I/O Data 12

114 D11 I/O Data 11

115 D10 I/O Data 10

116 D9 I/O Data 9

117 D8 I/O Data 8

118 D7 I/O Data 7

119 D6 I/O Data 6

120 D5 I/O Data 5

121 D4 I/O Data 4

122 D3 I/O Data 3

123 D nd round DGN G Digital IO g

124 D nd ground DGN G Digital core