Micrel KSZ8041NL User Manual

KSZ8041NL

10Base-T/100Base-TX

Physical Layer Transceiver

General Description

The KSZ8041NL is a single s upply 10Bas e-T/100Bas e-TX

Physical Layer Transceiver, which provides MII/RMII

interfaces to transm it and receive data. An unique mixed

signal design extends signaling distance while reducing

power consumption.

HP Auto MDI/MDI-X provid es the most robust solution f or

eliminating the need to differentiate between crossover

and straight-through cables.

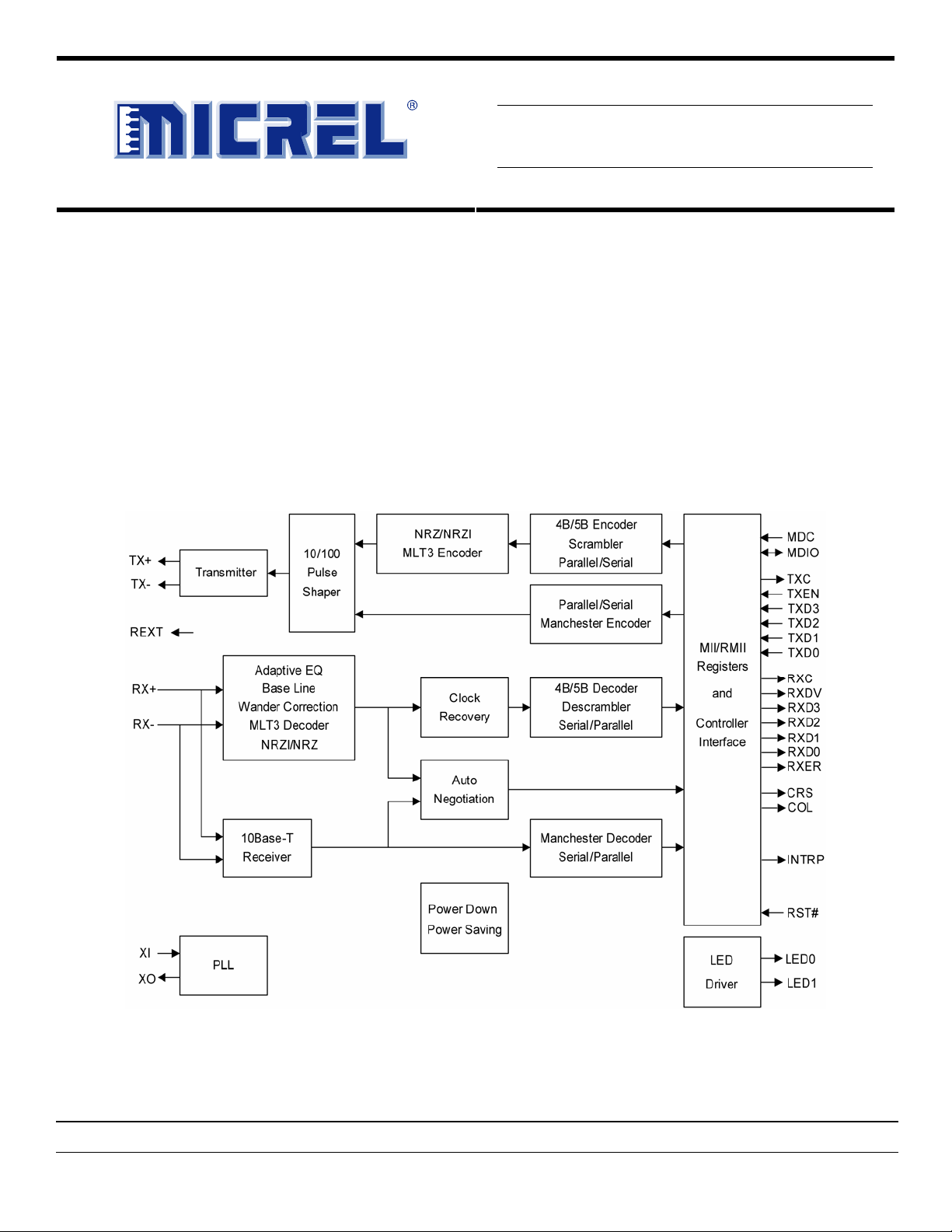

Functional Diagram

Data Sheet Rev. 1.2

The KSZ8041NL represents a new level of features and

performance and is an ideal choice of physical layer

transceiver for 10Base-T/100Base-TX applications.

The KSZ8041NL com es in a 32-pin , lead-free MLF

per JDEC) package (See Ordering Information).

Data sheets and support doc umentation can be found on

Micrel’s web site at: www.micrel.com.

®

(QFN

MicroLeadFrame and MLF are registered trademarks of Amkor Technology, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

July 2008

M9999-071808-1.2

Micrel, Inc. KSZ8041NL

Features

Applications

• Single-chip 10Base-T/100Base-TX physical layer

solution

• Fully compliant to IEEE 802.3u Standard

• Low power CMOS design, power consumption of

<180mW

• HP auto MDI/MDI-X for reliable detection and

correction for straight-through and crossover cables

with disable and enable option

• Robust operation over standard cables

• Power down and power saving modes

• MII interface support

• RMII interface support with external 50MHz s ystem

clock

• MIIM (MDC/MDIO) management bus to 6.25MHz for

rapid PHY register configuration

• Interrupt pin option

• Programmable LED outputs for link, activity and

speed

• ESD rating (6kV)

• Single power supply (3.3V)

• Built-in 1.8V regulator for core

®

• Available in 32-pin (5mm x 5mm) MLF

package

• Printer

• LOM

• Game Console

• IPTV

• IP Phone

• IP Set-top Box

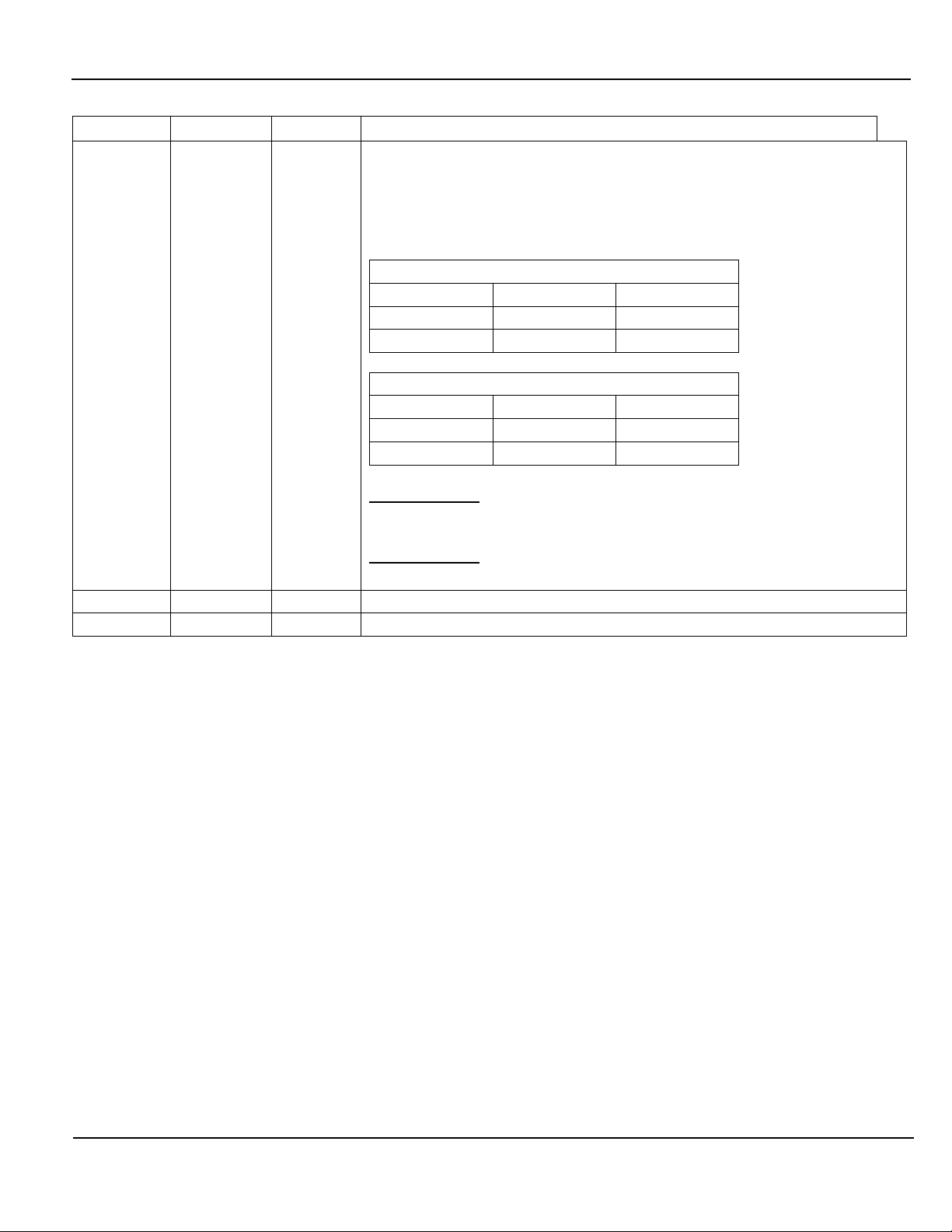

Ordering Information

Part Number Temp. Range Package Lead Finish Description

KSZ8041NL 0°C to 70°C 32-Pin MLF® Pb-Free Commercial Temperature Device

KSZ8041NLI

KSZ8041NL AM

Note:

1. Contact factory for lead time.

(1)

-40°C to 85°C 32-Pin MLF® Pb-Free Industrial Temperature Device

(1)

-40°C to 85°C 32-Pin MLF® Pb-Free Automotive Qualified Device

July 2008 2 M9999-071808-1.2

Micrel, Inc. KSZ8041NL

Revision History

Revision Date Summary of Changes

1.0 10/13/06 Data sheet created.

1.1 4/27/07 Added maximum MDC clock speed.

Added 40K +/-30% to note 1 of Pin Description and Strapping Options tables for internal pull-ups/pull-

downs.

Changed Model Number in Register 3h – PHY Identifier 2.

Changed polarity (swapped definition) of DUPLEX strapping pin.

Removed DUPLEX strapping pin update to Register 4h – Auto-Negotiation Advertisement bits [8, 6].

Set “Disable power saving” as the default for Register 1Fh bit [10].

Corrected LED1 (pin 31) definition for Activity in LED mode 01.

Added Symbol Error to MII/RMII Receive Error description and Register 15h – RXER Counter.

Added a 100pF capacitor on REXT (pin 10) in Pin Description table.

1.2 7/18/08 Added Automotive Qualified part number to Ordering Information.

Added maximum case temperature.

Added thermal resistance (θ

Added chip maximum current consumpti on.

).

JC

July 2008 3 M9999-071808-1.2

Micrel, Inc. KSZ8041NL

Contents

Pin Configuration..................................................................................................................................................................8

Pin Description......................................................................................................................................................................9

Strapping Options...............................................................................................................................................................12

Functional Description .......................................................................................................................................................13

100Base-TX Transmit.......................................................................................................................................................13

100Base-TX Receive........................................................................................................................................................13

PLL Clock Synthesizer......................................................................................................................................................13

Scrambler/De-scrambler (100Base-TX only)....................................................................................................................13

10Base-T Transmit...........................................................................................................................................................13

10Base-T Receive ............................................................................................................................................................13

SQE and Jabber Function (10Base-T only)......................................................................................................................14

Auto-Negotiation...............................................................................................................................................................14

MII Management (MIIM) Interface ....................................................................................................................................16

Interrupt (INTRP) ..............................................................................................................................................................16

MII Data Interface .............................................................................................................................................................16

MII Signal Definition..........................................................................................................................................................17

Transmit Clock (TXC)...................................................................................................................................................17

Transmit Enable (TXEN) ..............................................................................................................................................17

Transmit Data [3:0] (TXD[3:0]) .....................................................................................................................................17

Receive Clock (RXC)....................................................................................................................................................17

Receive Data Valid (RXDV)..........................................................................................................................................18

Receive Data [3:0] (RXD[3:0])......................................................................................................................................18

Receive Error (RXER) ..................................................................................................................................................18

Carrier Sense (CRS) ....................................................................................................................................................18

Collision (COL) .............................................................................................................................................................18

Reduced MII (RMII) Data Interface...................................................................................................................................18

RMII Signal Definition .......................................................................................................................................................19

Reference Clock (REF_CLK) .......................................................................................................................................19

Transmit Enable (TX_EN) ............................................................................................................................................19

Transmit Data [1:0] (TXD[1:0]) .....................................................................................................................................19

Carrier Sense/Receive Data Valid (CRS_DV)..............................................................................................................19

Receive Data [1:0] (RXD[1:0])......................................................................................................................................19

Receive Error (RX_ER) ................................................................................................................................................19

Collision Detection........................................................................................................................................................20

HP Auto MDI/MDI-X..........................................................................................................................................................20

Straight Cable...............................................................................................................................................................20

Crossover Cable...........................................................................................................................................................21

Power Management ..........................................................................................................................................................22

Power Saving Mode .....................................................................................................................................................22

Power Down Mode .......................................................................................................................................................22

Reference Clock Connection Options ..............................................................................................................................22

July 2008 4 M9999-071808-1.2

Micrel, Inc. KSZ8041NL

Reference Circuit for Power and Ground Connections ....................................................................................................23

Register Map........................................................................................................................................................................24

Register Description...........................................................................................................................................................24

Absolute Maximum Ratings

Operating Ratings

(2)

............................................................................................................................................................31

Electrical Characteristics

Electrical Characteristics

(1)

............................................................................................................................................31

(4)

................................................................................................................................................31

(6)

................................................................................................................................................32

Timing Diagrams.................................................................................................................................................................33

MII SQE Timing (10Base-T) .............................................................................................................................................33

MII Transmit Timing (10Base-T).......................................................................................................................................34

MII Receive Timing (10Base-T)........................................................................................................................................35

MII Transmit Timing (100Base-TX) ..................................................................................................................................36

MII Receive Timing (100Base-TX) ...................................................................................................................................37

RMII Timing.......................................................................................................................................................................38

Auto-Negotiation Timing...................................................................................................................................................39

MDC/MDIO Timing ...........................................................................................................................................................40

Reset Timing.....................................................................................................................................................................41

Reset Circuit ........................................................................................................................................................................42

Reference Circuits for LED Strapping Pins......................................................................................................................43

Selection of Isolation Transformer....................................................................................................................................44

Selection of Reference Crystal ..........................................................................................................................................44

Package Information...........................................................................................................................................................45

July 2008 5 M9999-071808-1.2

Micrel, Inc. KSZ8041NL

List of Figures

Figure 1. Auto-Negotiation Flow Chart .................................................................................................................................15

Figure 2. Typical Straight Cable Connection .......................................................................................................................20

Figure 3. Typical Crossover Cable Connection ...................................................................................................................21

Figure 4. 25MHz Crystal / Oscillator Reference Clock for MII Mode...................................................................................22

Figure 5. 50MHz Oscillator Reference Clock for RMII Mode...............................................................................................22

Figure 6. KSZ8041NL Power and Ground Connections......................................................................................................23

Figure 7. MII SQE Timing (10Base-T) .................................................................................................................................33

Figure 8. MII Transmit Timing (10Base-T)...........................................................................................................................34

Figure 9. MII Receive Timing (10Base-T)............................................................................................................................35

Figure 10. MII Transmit Timing (100Base-TX).....................................................................................................................36

Figure 11. MII Receive Timing (100Base-TX)......................................................................................................................37

Figure 12. RMII Timing – Data Received from RMII............................................................................................................38

Figure 13. RMII Timing – Data Input to RMII .......................................................................................................................38

Figure 14. Auto-Negotiation Fast Link Pulse (FLP) Timing .................................................................................................39

Figure 15. MDC/MDIO Timing..............................................................................................................................................40

Figure 16. Reset Timing.......................................................................................................................................................41

Figure 17. Recommended Reset Circuit..............................................................................................................................42

Figure 18. Recommended Reset Circuit for interfacing with CPU/FPGA Reset Output......................................................42

Figure 19. Reference Circuits for LED Strapping Pins.........................................................................................................43

July 2008 6 M9999-071808-1.2

Micrel, Inc. KSZ8041NL

List of Tables

Table 1. MII Management Frame Format ............................................................................................................................16

Table 2. MII Signal Definition...............................................................................................................................................17

Table 3. RMII Signal Description..........................................................................................................................................19

Table 4. MDI/MDI-X Pin Definition.......................................................................................................................................20

Table 5. KSZ8041NL Power Pin Description.......................................................................................................................23

Table 6. MII SQE Timing (10Base-T) Parameters...............................................................................................................33

Table 7. MII Transmit Timing (10Base-T) Parameters.........................................................................................................34

Table 8. MII Receive Timing (10Base-T) Parameters..........................................................................................................35

Table 9. MII Transmit Timing (100Base-TX) Parameters....................................................................................................36

Table 10. MII Receive Timing (100Base-TX) Parameters...................................................................................................37

Table 11. RMII Timing Parameters......................................................................................................................................38

Table 12. Auto-Negotiation Fast Link Pulse (FLP) Timing Parameters...............................................................................39

Table 13. MDC/MDIO Timing Parameters...........................................................................................................................40

Table 14. Reset Timing Parameters ....................................................................................................................................41

Table 15. Transformer Selection Criteria .............................................................................................................................44

Table 16. Qualified Single Port Magnetics...........................................................................................................................44

Table 17. Typical Reference Crystal Characteristics...........................................................................................................44

July 2008 7 M9999-071808-1.2

Micrel, Inc. KSZ8041NL

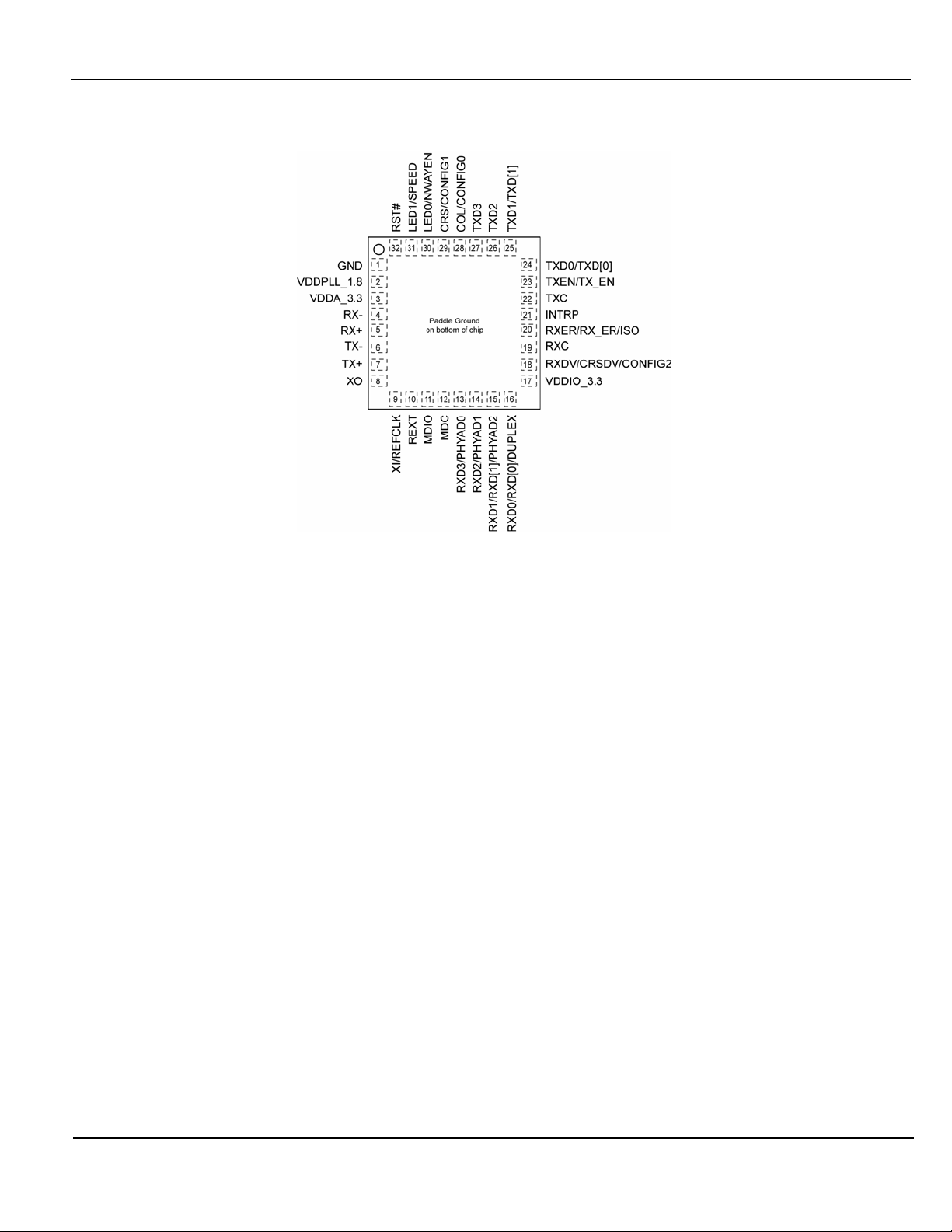

Pin Configuration

32-Pin (5mm x 5mm) MLF®

July 2008 8 M9999-071808-1.2

Micrel, Inc. KSZ8041NL

Pin Description

Pin Number Pin Name

1 GND Gnd Ground

2 VDDPLL_1.8 P 1.8V analog VDD

3 VDDA_3.3 P 3.3V analog VDD

4 RX- I/O Physical receive or transmit signal (- differential)

5 RX+ I/O Physical receive or transmit signal (+ differential)

6 TX- I/O Physical transmit or receive signal (- differential)

7 TX+ I/O Physical transmit or receive signal (+ differential)

8 XO O Crystal feedback

9 XI /

REFCLK

10 REXT I/O Set physical transmit output current

11 MDIO I/O Management Interface (MII) Data I/O

12 MDC I Management Interface (MII) Clock Input

13 RXD3 /

PHYAD0

14 RXD2 /

PHYAD1

15 RXD1 /

RXD[1] /

PHYAD2

16 RXD0 /

RXD[0] /

DUPLEX

17 VDDIO_3.3 P 3.3V digital VDD

18 RXDV /

CRSDV /

CONFIG2

19 RXC O MII Mode: Receive Clock Output

(1)

Type

Pin Function

This pin is used only in MII mode when a 25 MHz crystal is used.

This pin is a no connect if oscillator or external clo ck sou r ce i s used, or if RMII

mode is selected.

I Crystal / Oscillator / External Clock Input

MII Mode: 25MHz +/-50ppm (crystal, oscillator, or external clock)

RMII Mode: 50MHz +/-50ppm (oscillator, or external clock only)

Connect a 6.49KΩ resistor in parallel with a 100pF capacitor to ground on this

pin. See KSZ8041NL reference schematics.

This pin requires an external 4.7KΩ pull-up resistor.

This pin is synchronous to the MDIO data interface.

Ipu/O

MII Mode: Receive Data Output[3]

(2)

/

Config Mode: The pull-up/pull-down value is latched as PHYADDR[0] during

power-up / reset. See “Strapping Options” section for details.

Ipd/O

MII Mode: Receive Data Output[2]

(2)

/

Config Mode: The pull-up/pull-down value is latched as PHYADDR[1] during

power-up / reset. See “Strapping Options” section for details.

Ipd/O

MII Mode: Receive Data Output[1]

RMII Mode: Receive Data Output[1]

(2)

(3)

/

/

Config Mode: The pull-up/pull-down value is latched as PHYADDR[2] during

power-up / reset. See “Strapping Options” section for details.

Ipu/O

MII Mode: Receive Data Output[0]

RMII Mode: Receive Data Output[0]

(2)

(3)

/

/

Config Mode: Latched as DUPLEX (register 0h, bit 8) during power-up /

reset. See “Strapping Options” section for details.

Ipd/O MII Mode: Receive Data Valid Output /

RMII Mode: Carrier Sense/Receive Data Valid Output /

Config Mode: The pull-up/pull-down value is latched as CONFIG2 during

power-up / reset. See “Strapping Options” section for details.

July 2008 9 M9999-071808-1.2

Micrel, Inc. KSZ8041NL

Pin Number Pin Name

20 RXER /

RX_ER /

ISO

21 INTRP Opu Interrupt Output: Programmable Interrupt Output

22 TXC O MII Mode: Transmit Clock Output

23 TXEN /

TX_EN

24 TXD0 /

TXD[0]

25 TXD1 /

TXD[1]

26 TXD2 I

27 TXD3 I

28 COL /

CONFIG0

29 CRS /

CONFIG1

30 LED0 /

NWAYEN

(1)

Type

Pin Function

Ipd/O MII Mode: Receive Error Output /

RMII Mode: Receive Error Output /

Config Mode: The pull-up/pull-down value is latched as ISOLATE during

power-up / reset. See “Strapping Options” section for details.

Register 1Bh is the Interrupt Control/Status Register for programming the interrupt

conditions and reading the interrupt status. Register 1Fh bit 9 sets the interrupt

output to active low (default) or active high.

I MII Mode: Transmit Enable Input /

RMII Mode: Transmit Enable Input

I

MII Mode: Transmit Data Input[0]

RMII Mode: Transmit Data Input[0]

I

MII Mode: Transmit Data Input[1]

RMII Mode: Transmit Data Input[1]

MII Mode: Transmit Data Input[2]

MII Mode: Transmit Data Input[3]

(4)

(5)

(4)

(5)

(4)

(4)

/

/

/

/

Ipd/O MII Mode: Collision Detect Output /

Config Mode: The pull-up/pull-down value is latched as CONFIG0 during

power-up / reset. See “Strapping Options” section for details.

Ipd/O MII Mode: Carrier Sense Output /

Config Mode: The pull-up/pull-down value is latched as CONFIG1 during

power-up / reset. See “Strapping Options” section for details.

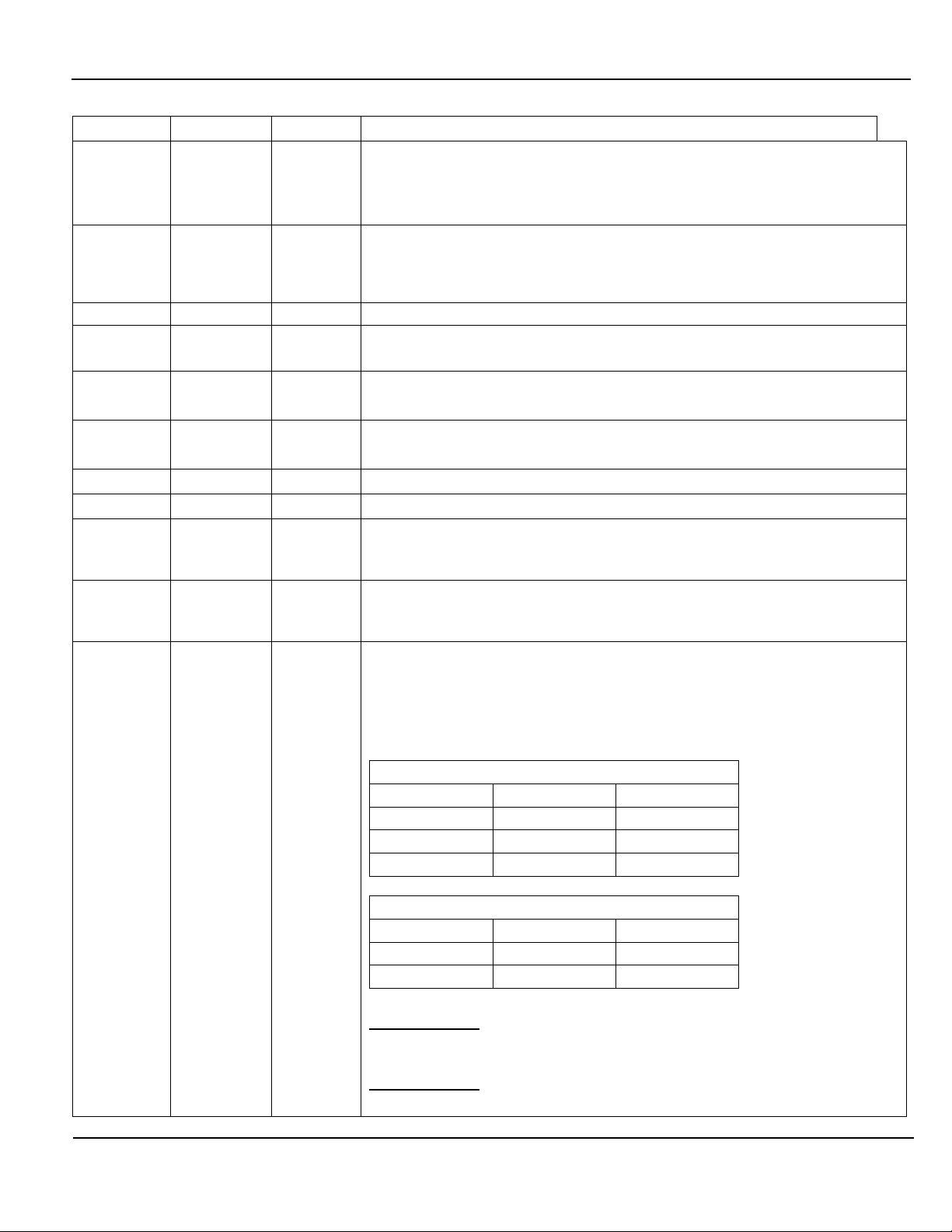

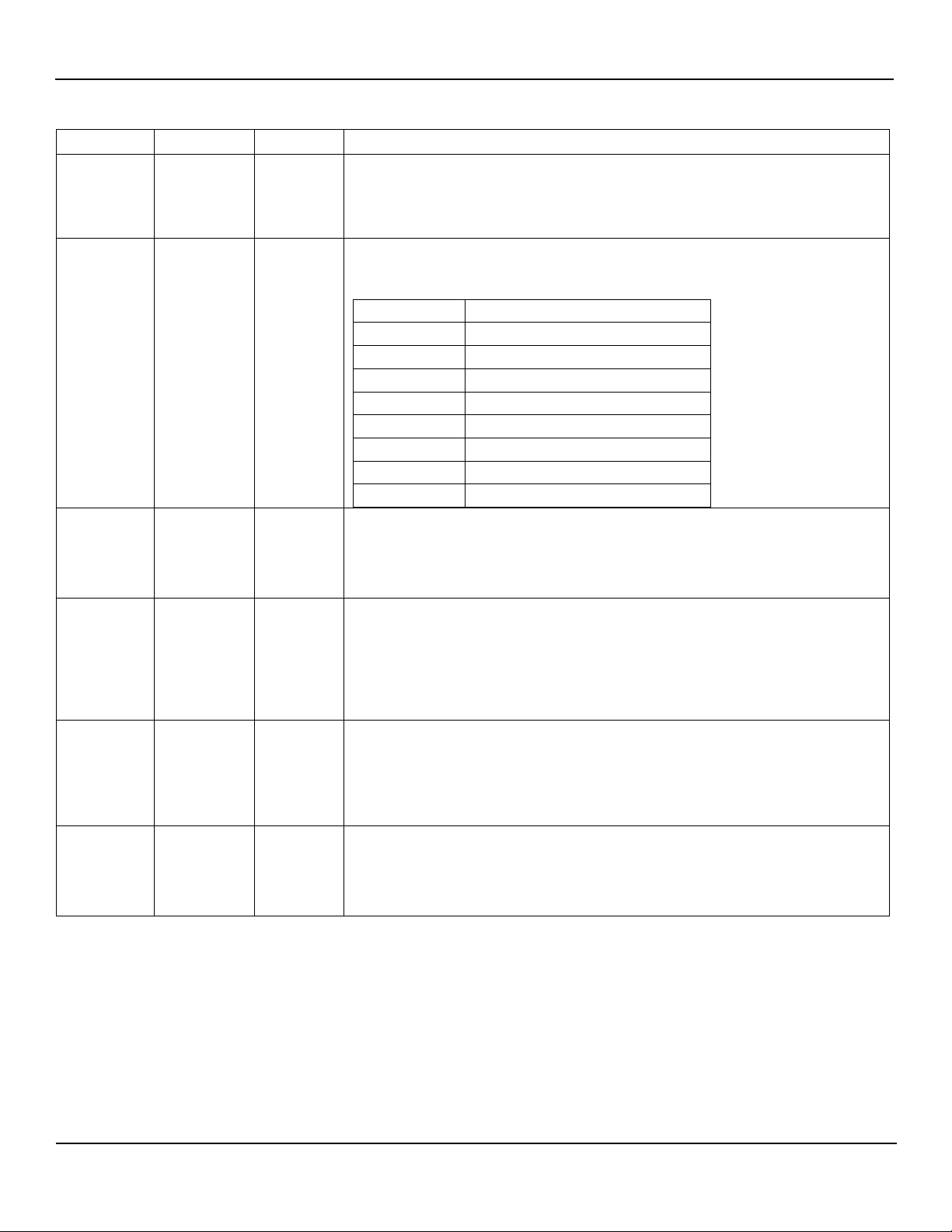

Ipu/O LED Output: Programmable LED0 Output /

Config Mode: Latched as Auto-Negotiation Enable (register 0h, bit 12) during

power-up / reset. See “Strapping Options” section for details.

The LED0 pin is programmable via register 1Eh bits [15:14], and is defined as

follows.

LED mode = [00]

Link/Activity Pin State LED Definition

No Link H OFF

Link L ON

Activity Toggle Blinking

LED mode = [01]

Link Pin State LED Definition

No Link H OFF

Link L ON

LED mode = [10]

Reserved

LED mode = [11]

Reserved

July 2008 10 M9999-071808-1.2

Micrel, Inc. KSZ8041NL

Pin Number Pin Name

31 LED1 /

SPEED

32 RST# I Chip Reset (active low)

PADDLE GND Gnd Ground

Notes:

1. P = Power supply.

Gnd = Ground.

I = Input.

O = Output.

I/O = Bi-directional.

Ipd = Input with internal pull-down (40K +/-30%).

Ipu = Input with internal pull-up (40K +/-30%).

Opu = Output with internal pull-up (40K +/-30%).

Ipu/O = Input with internal pull-up (40K +/-30%) during power-up/reset; output pin otherwise.

Ipd/O = Input with internal pull-down (40K +/-30%) during power-up/reset; output pin otherwise.

2. MII Rx Mode: The RXD[3..0] bits are synchronous with RXCLK. When RXDV is asserted, RXD[3..0] presents valid data to MAC through the MII.

RXD[3..0] is invalid when RXDV is de-asserted.

3. RMII Rx Mode: The RXD[1:0] bits are synchronous with REF_CLK. For each clock period in which CRS_DV is asserted, two bits of recovered

data are sent from the PHY.

4. MII Tx Mode: The TXD[3..0] bits are synchronous with TXCLK. When TXEN is asserted, TXD[3..0] presents valid data from the MAC through

the MII. TXD[3..0] has no effect when TXEN is de-asserted.

5. RMII Tx Mode: The TXD[1:0] bits are synchronous with REF_CLK. For each clock period in which TX_EN is asserted, two bits of data are

received by the PHY from the MAC.

(1)

Type

Pin Function

Ipu/O LED Output: Programmable LED1 Output /

Config Mode: Latched as SPEED (register 0h, bit 13) during power-up / reset.

See “Strapping Options” section for details.

The LED1 pin is programmable via register 1Eh bits [15:14], and is defined as

follows.

LED mode = [00]

Speed Pin State LED Definition

10BT H OFF

100BT L ON

LED mode = [01]

Activity Pin State LED Definition

No Activity H OFF

Activity Toggle Blinking

LED mode = [10]

Reserved

LED mode = [11]

Reserved

July 2008 11 M9999-071808-1.2

Micrel, Inc. KSZ8041NL

Strapping Options

Pin Number Pin Name

15

14

13

18

29

28

20 ISO Ipd/O ISOLATE mode

31 SPEED Ipu/O SPEED mode

16 DUPLEX Ipu/O DUPLEX mode

30 NWAYEN Ipu/O Nway Auto-Negotiation Enable

Note:

1. Ipu/O = Input with internal pull-up (40K +/-30%) during power-up/reset; output pin otherwise.

Ipd/O = Input with internal pull-down (40K +/-30%) during power-up/reset; output pin otherwise.

PHYAD2

PHYAD1

PHYAD0

CONFIG2

CONFIG1

CONFIG0

Pin strap-ins are latc hed during power-u p or reset. In some s ystems, the MAC receive in put pins may drive high during

power-up or reset, and c on s equen tl y cause the PHY strap-in pi ns on t he MII/RMII signals to be latch ed h ig h. In th is c ase ,

it is recomm ended to add 1K pull-do wns on these PHY strap- in pins to ensure the P HY does no t strap-in to ISOLAT E or

PCS Loopback mode, or is not configured with an incorrect PHY Address.

Type

Ipd/O

Ipd/O

Ipu/O

Ipd/O

Ipd/O

Ipd/O

(1)

Pin Function

The PHY Address is latched at power-up / reset and is configurable to any value from

1 to 7.

The default PHY Address is 00001.

PHY Address bits [4:3] are always set to ‘00’.

The CONFIG[2:0] strap-in pins are latched at power-up / reset and are defined as

follows:

CONFIG[2:0] Mode

000 MII (default)

001 RMII

010 Reserved – not used

011 Reserved – not used

100 PCS Loopback

101 Reserved – not used

110 Reserved – not used

111 Reserved – not used

Pull-up = Enable

Pull-down (default) = Disable

During power-up / reset, this pin value is latched into register 0h bit 10.

Pull-up (default) = 100Mbps

Pull-down = 10Mbps

During power-up / reset, this pin value is latched into register 0h bit 13 as the Speed

Select, and also is latched into register 4h (Auto-Negotiation Advertisement) as the

Speed capability support.

Pull-up (default) = Half Duplex

Pull-down = Full Duplex

During power-up / reset, this pin value is latched into register 0h bit 8 as the Duplex

Mode.

Pull-up (default) = Enable Auto-Negotiation

Pull-down = Disable Auto-Negotiation

During power-up / reset, this pin value is latched into register 0h bit 12.

July 2008 12 M9999-071808-1.2

Micrel, Inc. KSZ8041NL

Functional Description

The KSZ8041NL is a single 3.3V supply Fast Ethernet transceiver. It is fully compliant with the IEEE 802.3u Specification.

On the media side, the KS Z8041NL supports 10Base- T and 100Base-TX with HP auto MD I/MD I -X f or reliabl e detec t ion of

and correction for straight-through and crossover cables.

The KSZ8041NL off ers a choice of MII or RMII data interfac e connection with th e MAC processor. T he MII managem ent

bus option gives the M AC processor complete access to the K SZ8041NL control and status registers. Additionally, an

interrupt pin eliminates the need for the processor to poll for PHY status change.

Physical signal trans mission and reception are enha nced through the use of patented a nalog circuitries that make the

design more efficient and allow for lower power consumption and smaller chip die size.

100Base-TX Transmit

The 100Base-TX transmit function performs parallel-to-serial conversion, 4B/5B coding, scrambling, NRZ-to-NRZI

conversion, and MLT3 encoding and transmission.

The circuitry starts with a p arallel-t o-seria l conversion, which conver ts the MII dat a from the MAC into a 125 MHz serial bit

stream. The data and contr ol stream is then converted into 4B/5B coding, f ollowed by a scr ambler. The s erialized data is

further converted from NRZ-to-NRZI format, and then transmitted in MLT3 current output.

The output current is set by an extern al 6.49kΩ 1% res istor for the 1:1 tra nsform er ratio. It has typical r ise/fall tim es of 4

ns and complies with the ANSI TP-PMD standard regarding am plitude balance, overshoot an d timing jitter. The waveshaped 10Base-T output drivers are also incorporated into the 100Base-TX drivers.

100Base-TX Receive

The 100Base-TX receiver function performs adaptive equalization, DC restoration, MLT 3-to-NRZI conversion, data and

clock recovery, NRZI-to-NRZ conversion, de-scrambling, 4B/5B decoding, and serial-to-parallel conversion.

The receiving side star ts with the equali zation filter to c ompensate for inter-symbol inter ference (ISI) over the twisted pair

cable. Since the amplitude loss and phase distortion is a function of the cable length, the equalizer must adjust its

characteristics to optimize performance. In this design, the variable equalizer makes an initial estimation based on

comparisons of i ncom ing signal s trength against some k nown cable c haracter istics , and then t unes its elf f or optim ization.

This is an ongoing process and self-adjusts against environmental changes such as temperature variations.

Next, the equalized signal goes t hroug h a DC restor ation and data c onvers ion bl ock . The DC res tor ation c ircuit is use d to

compensate for the ef fect of baseline wander and to im prove the dynam ic range. The differ ential data conversion c ircuit

converts the MLT3 format back to NRZI. The slicing threshold is also adaptive.

The clock recovery circ uit e xtr ac ts the 125MHz clock from the edges of the NRZI sign al. T his r ecover ed c lock is then used

to convert the NRZI signal into the NRZ format. This signal is sent through the de-scrambler followed by the 4B/5B

decoder. Finally, the NRZ serial data is converted to the MII format and provided as the input data to the MAC.

PLL Clock Synthesizer

The KSZ8041NL generates 125MΗz, 25 MΗz and 20MΗz clocks for system timing. Internal clocks are generated from an

external 25MHz cr ystal or osc illator . In RMII m ode, thes e internal c lock s are gener ated fr om an exter nal 50MH z oscillat or

or system clock.

Scrambler/De-scrambler (100Base-TX only)

The purpose of the scrambler is to spread the power spectrum of the signal in order to reduce EMI and baseline wander.

10Base-T Transmit

The 10Base-T driver s are incorporated with th e 100Base-TX drivers to allow for transmiss ion using the same magnetic .

The drivers also perf orm internal wave-s hapi ng an d pr e-em phasi ze, and output 10Bas e-T sign als wit h a t ypical am plit ude

of 2.5V peak. The 10Base-T signals have harm onic contents that are at least 27dB below the fundamental frequency

when driven by an all-ones Manchester-encoded signal.

10Base-T Receive

On the receive side, input buf fer and leve l detectin g squelc h circuits ar e emplo yed. A differ ential input r eceiver circuit and

a PLL performs the decoding function. The Manchester-encoded data stream is separated into clock signal and NRZ data.

A squelch circuit r ejects signals with levels less than 400 m V or with short pu lse widths to prevent noise at the RX+ and

RX- inputs from falsely trigger the decoder. W hen the input exceeds the sq uelch limit, the PLL l ocks onto the incoming

July 2008 13 M9999-071808-1.2

Micrel, Inc. KSZ8041NL

signal and the KSZ8041NL decodes a data frame. The receive clock is kept active during idle periods in b etween data

reception.

SQE and Jabber Function (10Base-T only)

In 10Base-T operation, a s hort puls e is put out on t he COL pin af ter each fr ame is transm itted. This SQE Tes t is required

as a test of the 10Base-T transm it/receive path. If transmit enable (T XEN) is high for more than 20 ms (jabbering), th e

10Base-T transm itter is disabled and COL is as ser te d hig h. If TXEN is then dri ven low for more than 250 ms, the 10BaseT transmitter is re-enabled and COL is de-asserted (returns to low).

Auto-Negotiation

The KSZ8041NL c onforms to the a uto-negotiatio n protocol, def ined in Claus e 28 of the IEEE 802.3u specification . Autonegotiation is enabled by either hardware pin strapping (pin 30) or software (register 0h bit 12).

Auto-negotiation allo ws unshiel ded twiste d pair (UT P) link partners to sel ect the hig hest comm on m ode of operation. Link

partners advertise th eir capabiliti es to each other, an d then compare their own capabilities with those the y received from

their link partners . The highest s peed and duplex setting that is comm on to the two link partners is selec ted as the m ode

of operation.

The following list shows the speed and duplex operation mode from highest to lowest.

• Priority 1: 100Base-T X , full- dupl ex

• Priority 2: 100Base-TX , half -dupl ex

• Priority 3: 10Base-T, f ull-dupl ex

• Priority 4: 10Base-T, half- dupl ex

If auto-negotiation is not s upported or the KSZ8 041NL link partner is f orced to bypass auto-negot iation, the KSZ8041 NL

sets its operating mode by observing the signal at its receiver. This is known as parallel detection, and allows the

KSZ8041NL to establish link by listening for a fixed signal protocol in the absence of auto-negotiation advertisement

protocol.

The auto-negotiation link up process is shown in the following flow chart.

July 2008 14 M9999-071808-1.2

Loading...

Loading...