Micrel KS8995XA User Manual

KS8995XA Micrel, Inc.

查询KS8995XA供应商

KS8995XA

Integrated 5-Port 10/100 QoS Switch

Rev. 2.3

General Description

The KS8995XA is a highly integrated Layer-2 quality of

service (QoS) switch with optimized bill of materials (BOM)

cost for low port count, cost-sensitive 10/100Mbps switch

systems. It also provides an extensive feature set including

three different QoS priority schemes, a dual MII interface for

BOM cost reduction, rate limiting to offload CPU tasks,

software and hardware power-down, a MDC/MDIO control

interface and port mirroring/monitoring to effectively address

both current and emerging Fast Ethernet applications.

The KS8995XA contains five 10/100 transceivers with patented mixed-signal low-power technology, five media access

control (MAC) units, a high-speed non-blocking switch fabric,

a dedicated address lookup engine, and an on-chip frame

buffer memory.

All PHY units support 10BASE-T and 100BASE-TX. In addition, two of the PHY units support 100BaseFX (Ports 4 and 5).

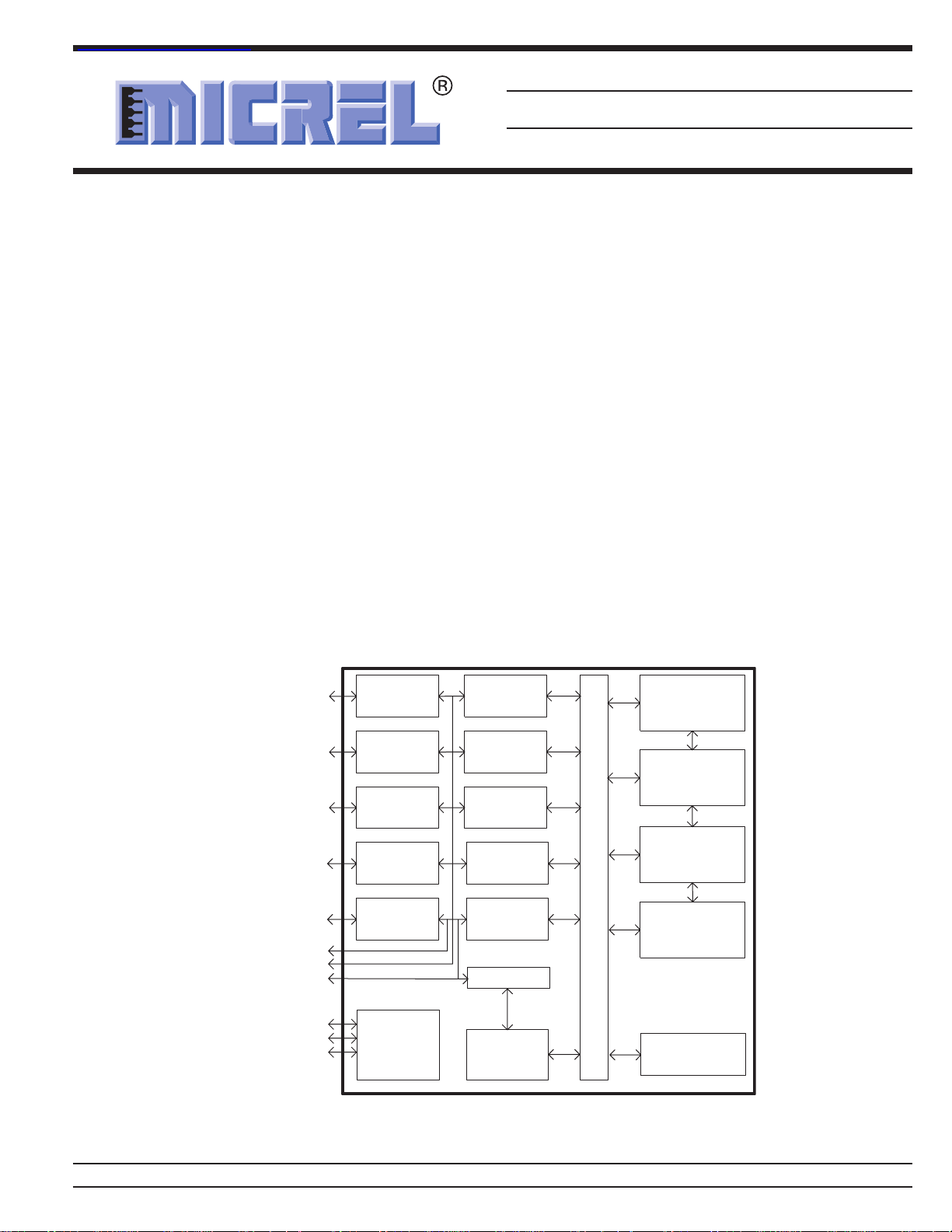

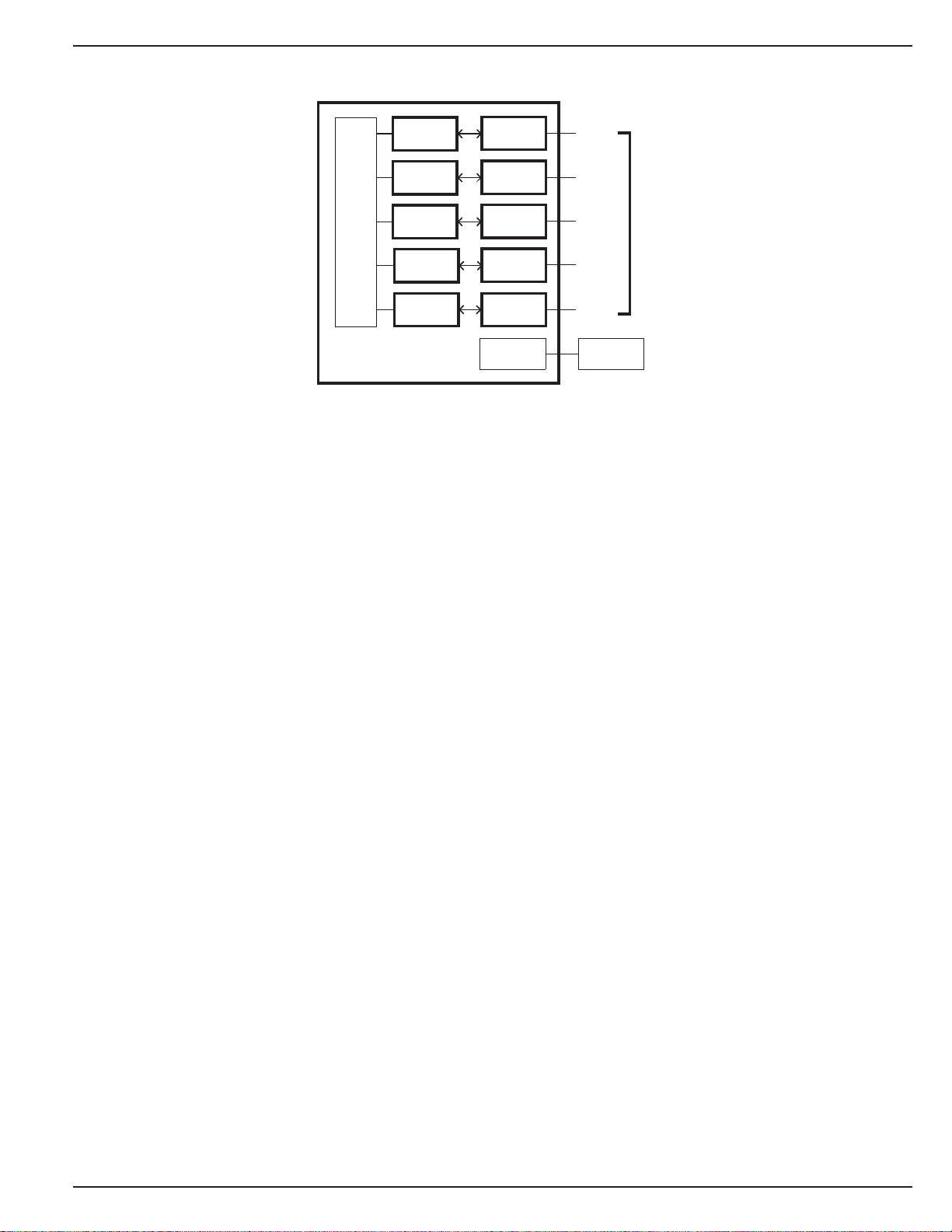

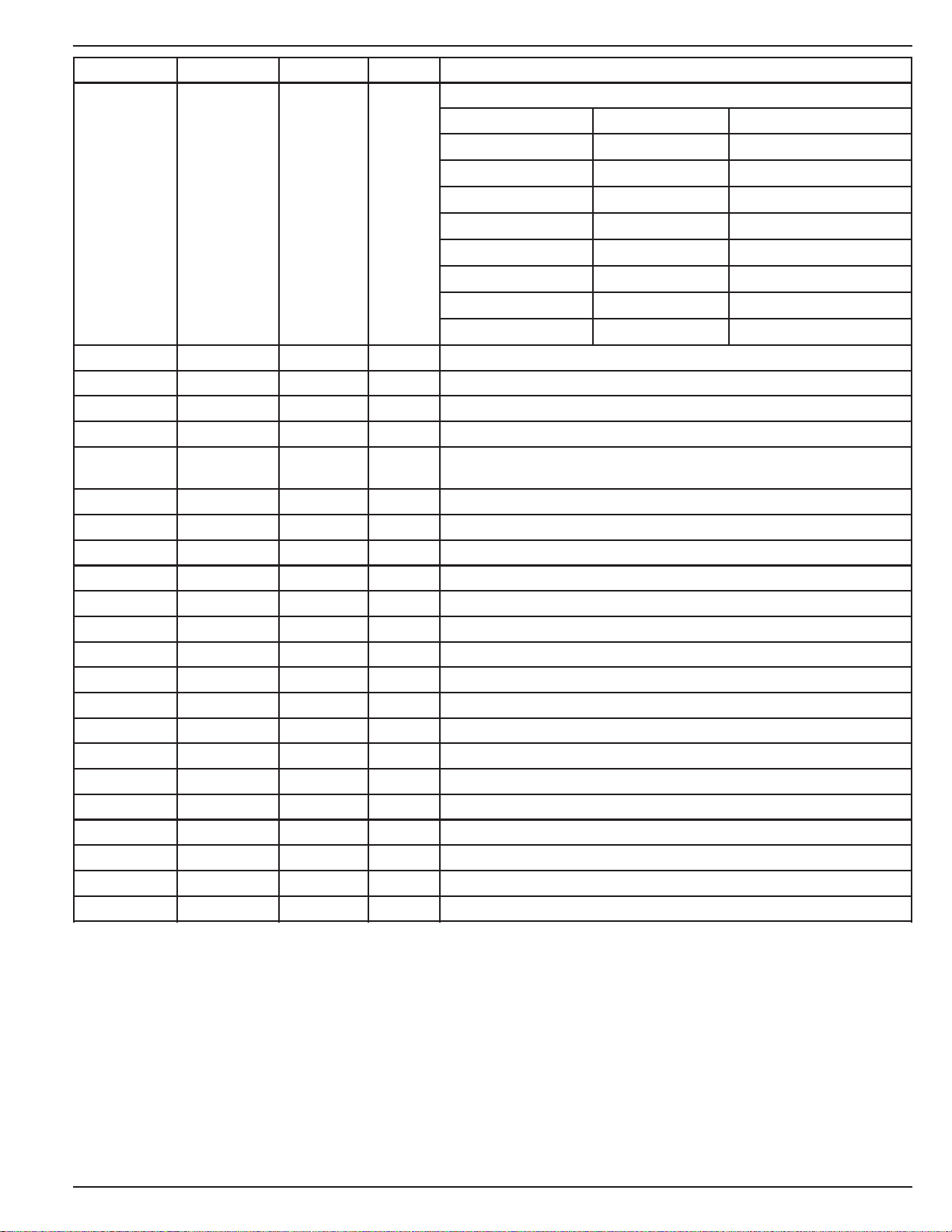

Functional Diagram

Features

•Integrated switch with five MACs and five Fast Ethernet

transceivers fully compliant to IEEE 802.3u standard

• Shared memory based switch fabric with fully nonblocking configuration

• 10BASE-T, 100BASE-TX and 100BASE-FX modes

(FX in Ports 4 and 5)

• Dual MII configuration: MII-Switch (MAC or PHY

mode MII) and MII-P5 (PHY mode MII)

• VLAN ID tag/untag options, per-port basis

• Enable/disable option for huge frame size up to

1916 bytes per frame

•Broadcast storm protection with percent control –

global and per-port basis

• Optimization for fiber-to-copper media conversion

• Full-chip hardware power-down support (register

configuration not saved)

• Per-port-based software power-save on PHY

(idle link detection, register configuration preserved)

• QoS/CoS packets prioritization supports: per port,

802.1p and DiffServ-based

Auto

MDI/MDI-X

Auto

MDI/MDI-X

Auto

MDI/MDI-X

Auto

MDI/MDI-X

Auto

MDI/MDI-X

MII-P5

MDC, MDI/O

MII-SW or SNI

LED0[5:1]

LED1[5:1]

LED2[5:1]

10/100

T/Tx 1

10/100

T/Tx 2

10/100

T/Tx 3

10/100

T/Tx/Fx 4

10/100

T/Tx/Fx 5

LED I/F

10/100

MAC 1

10/100

MAC 2

10/100

MAC 3

10/100

MAC 4

10/100

MAC 5

SNI

Control

Registers

FIFO

, Flo

w Control, VLAN

T

agging, P

r

iority

1K Look-Up

Engine

Queue

Mgmnt

Buffer

Mgmnt

Frame

Buffers

EEPROM

I/F

KS8995XA

Micrel, Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel + 1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

May 2005 1 M9999-051305

KS8995XA Micrel, Inc.

Features (continued)

• 802.1p/q tag insertion or removal on a per-port basis

(egress)

• Port-based VLAN support

• MDC and MDI/O interface support to access the MII

PHY control registers (not all control registers)

•MII local loopback support

• On-chip 64Kbyte memory for frame buffering (not

shared with 1K unicast address table)

•1.4Gbps high performance memory bandwidth

•Wire-speed reception and transmission

•Integrated look-up engine with dedicated 1K unicast

MAC addresses

• Automatic address learning, address aging and address

migration

• Full-duplex IEEE 802.3x and half-duplex back pressure

flow control

• Comprehensive LED support

•7-wire SNI support for legacy MAC interface

• Automatic MDI/MDI-X crossover for plug-and-play

•Disable automatic MDI/MDI-X option

• Low power

Core: 1.8V

I/O: 2.5 or 3.3V

•0.18µm CMOS technology

• Commercial temperature range: 0°C to +70°C

• Available in 128-pin PQFP package

Applications

•Broadband gateway/firewall/VPN

•Integrated DSL or cable modem multi-port router

•Wireless LAN access point plus gateway

• Home networking expansion

•Standalone 10/100 switch

• Hotel/campus/MxU gateway

• Enterprise VoIP gateway/phone

• FTTx customer premise equipment

• Media converter

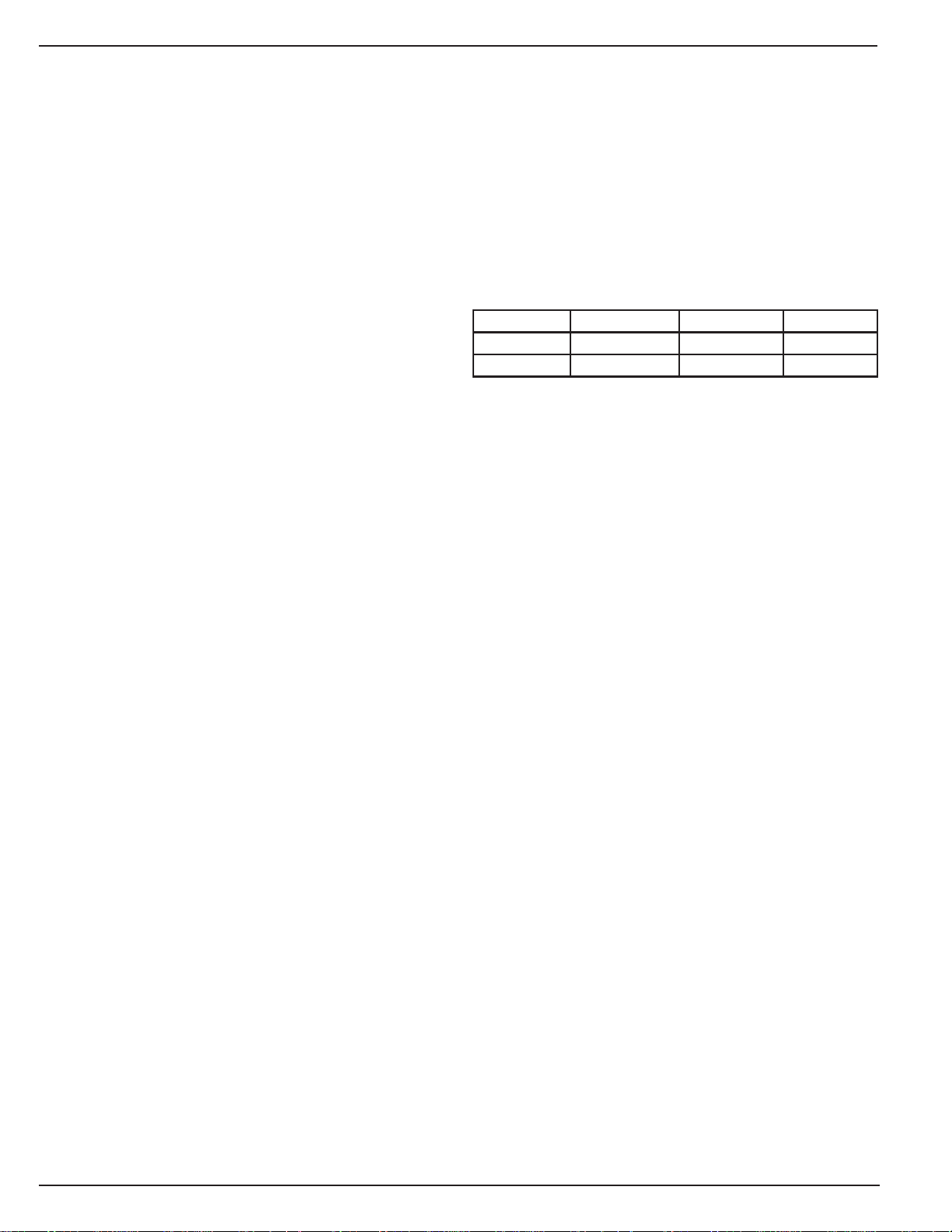

Ordering Information

Part Number Temp. Range Package Lead Finish

KS8995XA 0°C to +70°C 128-Pin PQFP Standard

KSZ8995XA 0°C to +70°C 128-Pin PQFP Pb-Free

M9999-051305 2 May 2005

KS8995XA Micrel, Inc.

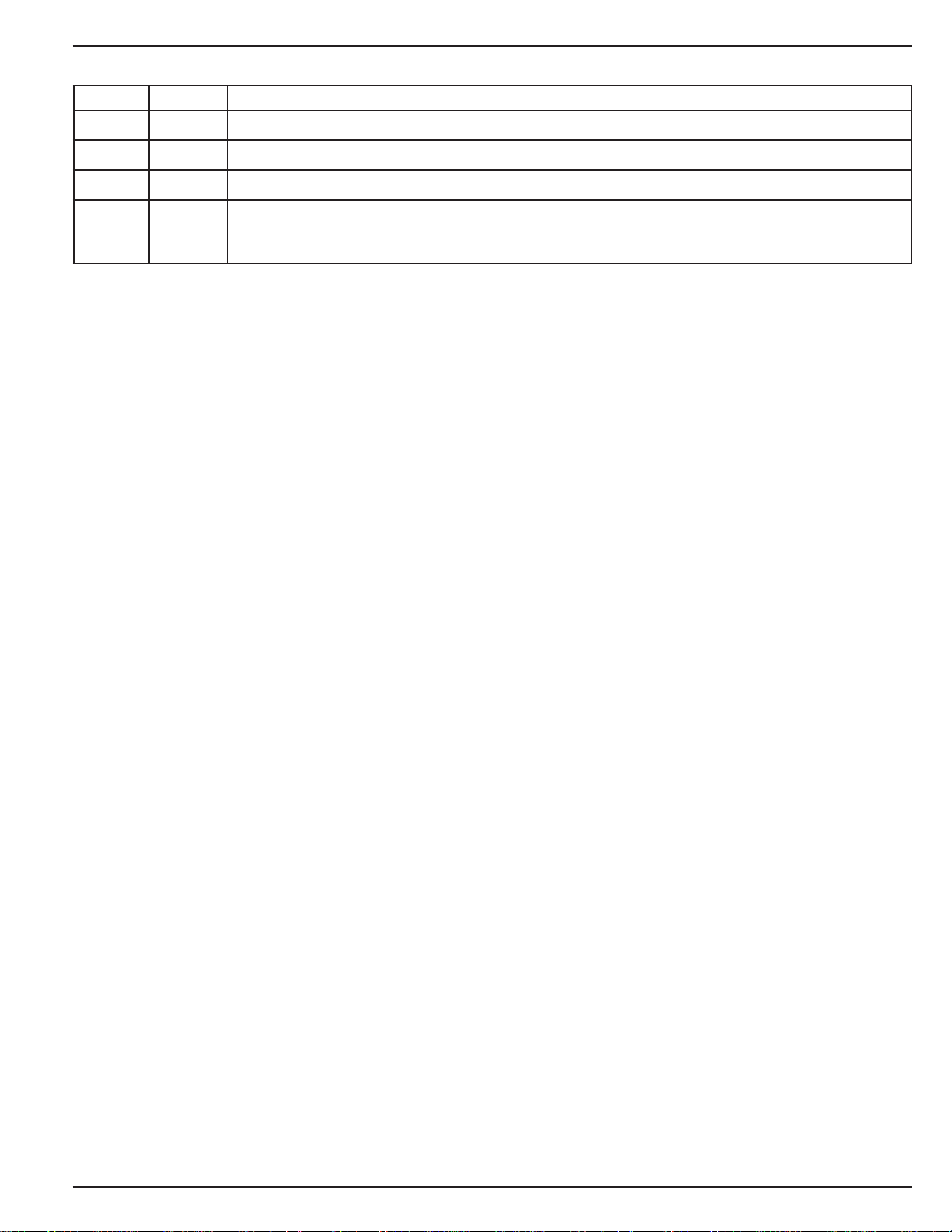

Revision History

Revision Date Summary of Changes

2.0 10/15/03 Created.

2.1 4/1/04 Editorial changes on TTL input and output electrical characteristics.

2.2 1/19/05 Insert recommeneded reset circuit.

2.3 4/13/05 Switched pins names for pins 7 & 8 on page 16.

Changed VDDIO to 3.3V.

Changed Jitter to 16 ns Max.

May 2005 3 M9999-051305

KS8995XA Micrel, Inc.

Table of Contents

System Level Applications .............................................................................................................................................................. 6

Pin Description (by Number) ........................................................................................................................................................... 8

Pin Description (by Name) ............................................................................................................................................................ 13

Pin Configuration ........................................................................................................................................................................... 18

Introduction ............................................................................................................................................................................ 19

Functional Overview: Physical Layer Transceiver..................................................................................................................... 19

100BASE-TX Transmit ............................................................................................................................................................ 19

100BASE-TX Receive ............................................................................................................................................................. 19

PLL Clock Synthesizer ............................................................................................................................................................ 19

Scrambler/De-scrambler (100BASE-TX only) ......................................................................................................................... 19

100BaseFX Operation ............................................................................................................................................................. 19

100BaseFX Signal Detection ................................................................................................................................................... 20

100BaseFX Far End Fault ....................................................................................................................................................... 20

10BASE-T Transmit ................................................................................................................................................................. 20

10BASE-T Receive .................................................................................................................................................................. 20

Power Management ................................................................................................................................................................ 20

MDI/MDI-X Auto Crossover ..................................................................................................................................................... 20

Auto-Negotiation ...................................................................................................................................................................... 20

Functional Overview: Switch Core ............................................................................................................................................... 21

Address Look Up ..................................................................................................................................................................... 21

Learning ............................................................................................................................................................................ 21

Migration ............................................................................................................................................................................ 21

Aging ............................................................................................................................................................................ 21

Switching Engine ..................................................................................................................................................................... 21

MAC (Media Access Controller) Operation ............................................................................................................................. 22

Inter-Packet Gap ............................................................................................................................................................. 22

Backoff Algorithm ............................................................................................................................................................ 22

Late Collision .................................................................................................................................................................. 22

Illegal Frame ................................................................................................................................................................... 22

Flow Control .................................................................................................................................................................... 22

Half-Duplex Back Pressure ............................................................................................................................................. 22

Broadcast Storm Protection ............................................................................................................................................ 23

MII Interface Operation .................................................................................................................................................................. 23

SNI Interface Operation ................................................................................................................................................................. 25

Advanced Functionality ................................................................................................................................................................. 25

QoS Support ............................................................................................................................................................................ 25

Rate Limit Support ................................................................................................................................................................... 27

Configuration Interface ............................................................................................................................................................ 28

2

I

C Master Serial Bus Configuration ............................................................................................................................... 28

MII Management Interface (MIIM) .................................................................................................................................................. 28

Register Map ............................................................................................................................................................................ 29

Global Registers ...................................................................................................................................................................... 29

Register 0 (0x00): Chip ID0............................................................................................................................................ 29

Register 1 (0x01): Chip ID1/Start Switch ....................................................................................................................... 29

Register 2 (0x02): Global Control 0................................................................................................................................ 29

Register 3 (0x03): Global Control 1................................................................................................................................ 30

Register 4 (0x04): Global Control 2................................................................................................................................ 31

Register 5 (0x05): Global Control 3................................................................................................................................ 31

Register 6 (0x06): Global Control 4................................................................................................................................ 32

Register 7 (0x07): Global Control 5................................................................................................................................ 32

M9999-051305 4 May 2005

KS8995XA Micrel, Inc.

Register 8 (0x08): Global Control 6................................................................................................................................ 32

Register 9 (0x09): Global Control 7................................................................................................................................ 32

Register 10 (0x0A): Global Control 8 ............................................................................................................................. 32

Register 11 (0x0B): Global Control 9 ............................................................................................................................. 33

Port Registers .......................................................................................................................................................................... 33

Register 16 (0x10): Port 1 Control 0 .............................................................................................................................. 33

Register 17 (0x11): Port 1 Control 1 .............................................................................................................................. 34

Register 18 (0x12): Port 1 Control 2 .............................................................................................................................. 34

Register 19 (0x13): Port 1 Control 3 .............................................................................................................................. 35

Register 20 (0x14): Port 1 Control 4 .............................................................................................................................. 35

Register 21 (0x15): Port 1 Control 5 .............................................................................................................................. 35

Register 22 (0x16): Port 1 Control 6 .............................................................................................................................. 35

Register 23 (0x17): Port 1 Control 7 .............................................................................................................................. 36

Register 24 (0x18): Port 1 Control 8 .............................................................................................................................. 36

Register 25 (0x19): Port 1 Control 9 .............................................................................................................................. 36

Register 26 (0x1A): Port 1 Control 10 ............................................................................................................................ 36

Register 27 (0x1B): Port 1 Control 11 ............................................................................................................................ 37

Register 28 (0x1C): Port 1 Control 12 ............................................................................................................................ 37

Register 29 (0x1D): Port 1 Control 13 ............................................................................................................................ 38

Register 30 (0x1E): Port 1 Status 0 ............................................................................................................................... 39

Register 31 (0x1F): Port 1 Control 14 ............................................................................................................................ 39

Advanced Control Registers .................................................................................................................................................... 39

Register 96 (0x60): TOS Priority Control Register 0 ...................................................................................................... 39

Register 97 (0x61): TOS Priority Control Register 1 ...................................................................................................... 40

Register 98 (0x62): TOS Priority Control Register 2 ...................................................................................................... 40

Register 99 (0x63): TOS Priority Control Register 3 ...................................................................................................... 40

Register 100 (0x64): TOS Priority Control Register 4 .................................................................................................... 40

Register 101 (0x65): TOS Priority Control Register 5 .................................................................................................... 40

Register 102 (0x66): TOS Priority Control Register 6 .................................................................................................... 40

Register 103 (0x67): TOS Priority Control Register 7 .................................................................................................... 40

Register 104 (0x68): MAC Address Register 0 .............................................................................................................. 40

Register 105 (0x69): MAC Address Register 1 .............................................................................................................. 40

Register 106 (0x6A): MAC Address Register 2.............................................................................................................. 40

Register 107 (0x6B): MAC Address Register 3.............................................................................................................. 40

Register 108 (0x6C): MAC Address Register 4 ............................................................................................................. 40

Register 109 (0X6D): MAC Address Register 5 ............................................................................................................. 40

MIIM Registers ........................................................................................................................................................................ 40

Register 0: MII Control ................................................................................................................................................... 40

Register 1: MII Status .................................................................................................................................................... 41

Register 2: PHYID HIGH ................................................................................................................................................ 41

Register 3: PHYID LOW ................................................................................................................................................ 41

Register 4: Advertisement Ability ................................................................................................................................... 41

Register 5: Link Partner Ability ....................................................................................................................................... 42

Absolute Maximum Ratings .......................................................................................................................................................... 43

Operating Ratings .......................................................................................................................................................................... 43

Electrical Characteristics .............................................................................................................................................................. 43

Timing Diagrams ............................................................................................................................................................................ 45

Selection of Isolation Transformers ............................................................................................................................................. 50

Package Information ...................................................................................................................................................................... 51

May 2005 5 M9999-051305

KS8995XA Micrel, Inc.

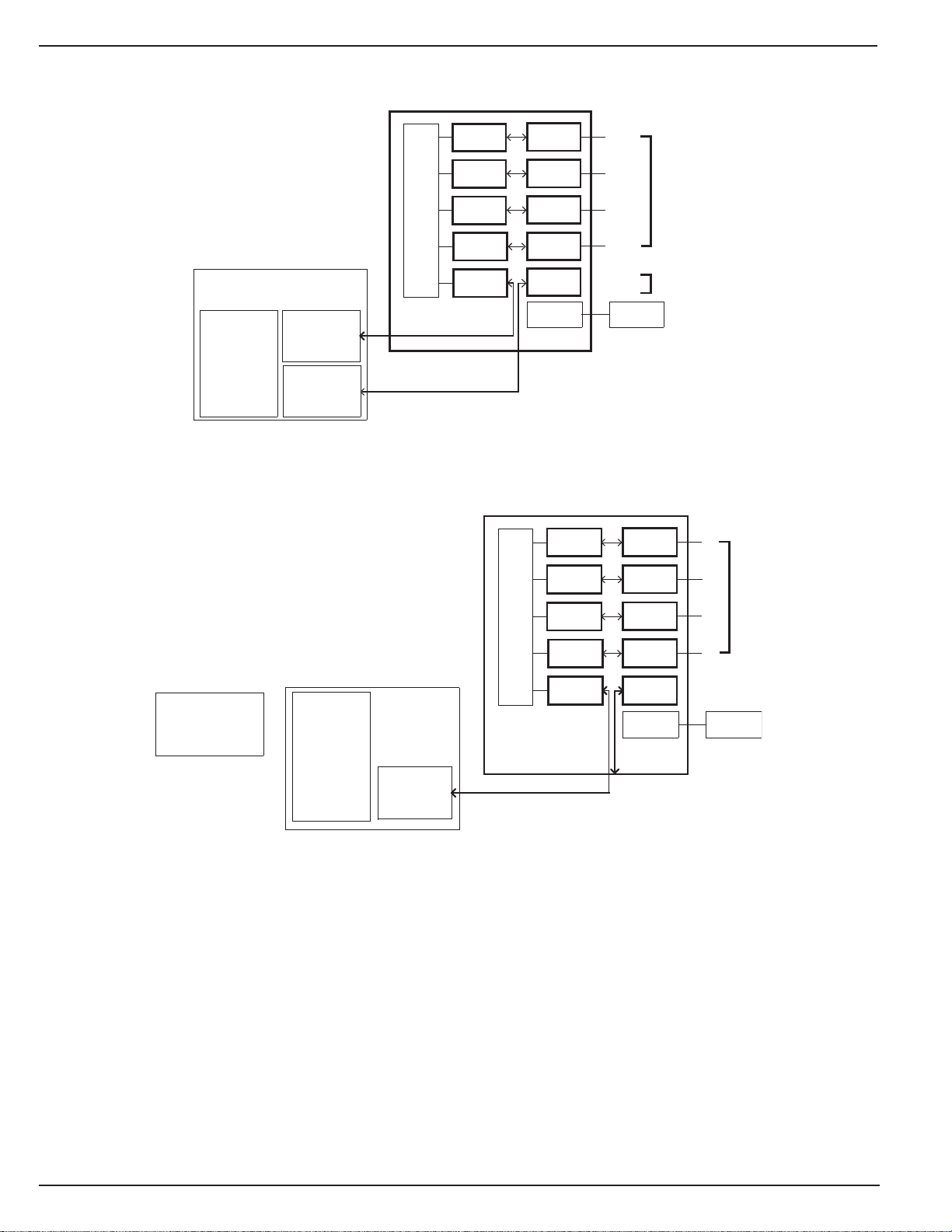

System Level Applications

CPU

WAN PHY & AFE

(XDSL, CM...)

10/100

MAC 1

10/100

MAC 2

10/100

MAC 3

10/100

Switch Controller

MAC 4

On-Chip Frame Buffers

10/100

MAC 5

Ethernet

MAC

MII-SW

KS8995XA

Ethernet

MAC

Figure 1. Broadband Gateway

CPU

Ethernet

MAC

10/100

PHY 1

10/100

PHY 2

10/100

PHY 3

10/100

PHY 4

10/100

PHY 5

EEPROM

I/F

MII-P5

rnal W

Exte AN port PHY not required.

10/100

MAC 1

10/100

MAC 2

10/100

MAC 3

Switch Controller

10/100

On-Chip Frame Buffers

MAC 4

10/100

MAC 5

MII-SW

EEPROM

10/100

PHY 1

10/100

PHY 2

10/100

PHY 3

10/100

PHY 4

10/100

PHY 5

EEPROM

MII-P5

KS8995XA

I/F

4-port

LAN

1-port

WAN I/F

4-port

LAN

EEPROM

Figure 2. Integrated Broadband Router

M9999-051305 6 May 2005

KS8995XA Micrel, Inc.

Switch Controller

On-Chip Frame Buffers

KS8995XA

Figure 3. Standalone Switch

10/100

MAC 1

10/100

MAC 2

10/100

MAC 3

10/100

MAC 4

10/100

MAC 5

10/100

PHY 1

10/100

PHY 2

10/100

PHY 3

10/100

PHY 4

10/100

PHY 5

EEPROM

I/F

5-port

LAN

EEPROM

May 2005 7 M9999-051305

KS8995XA Micrel, Inc.

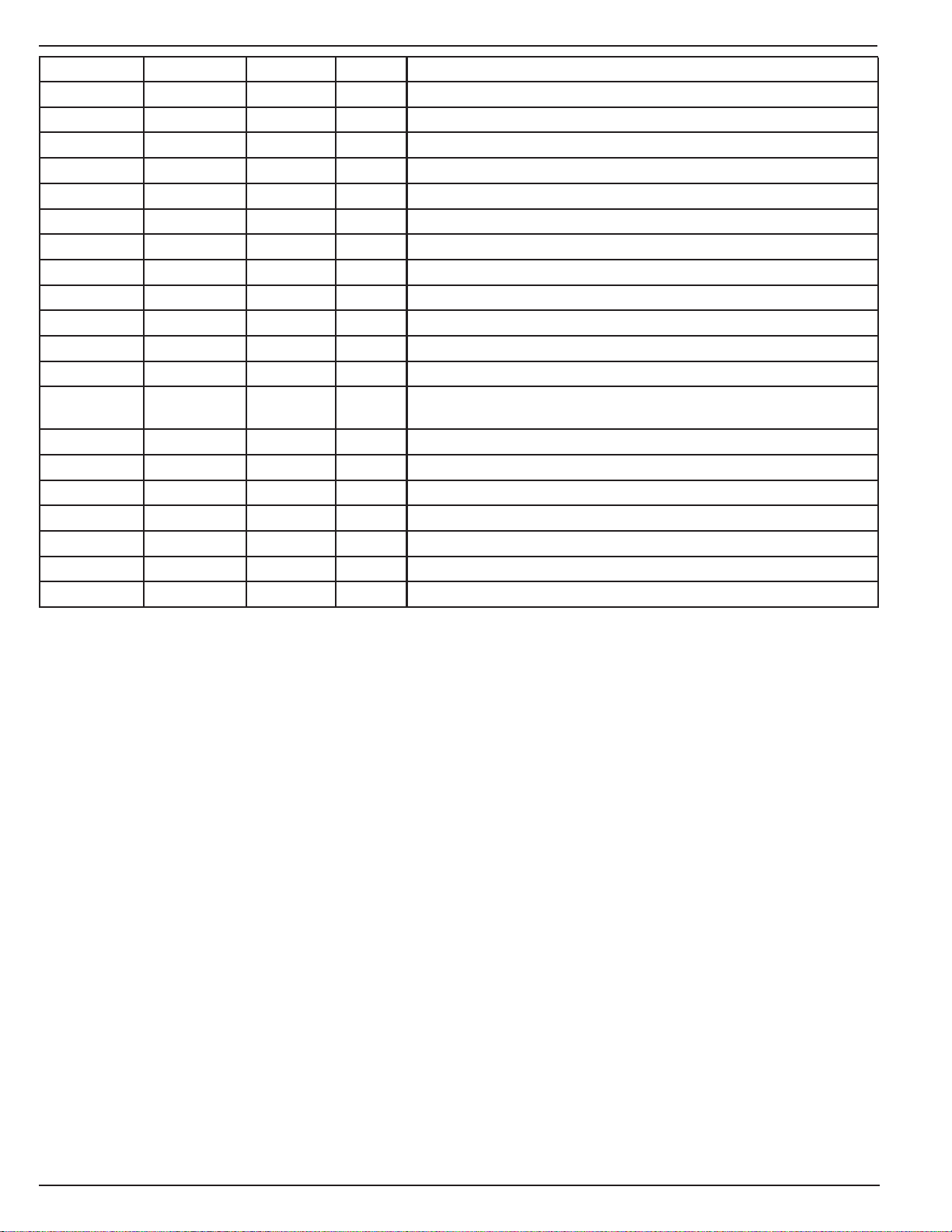

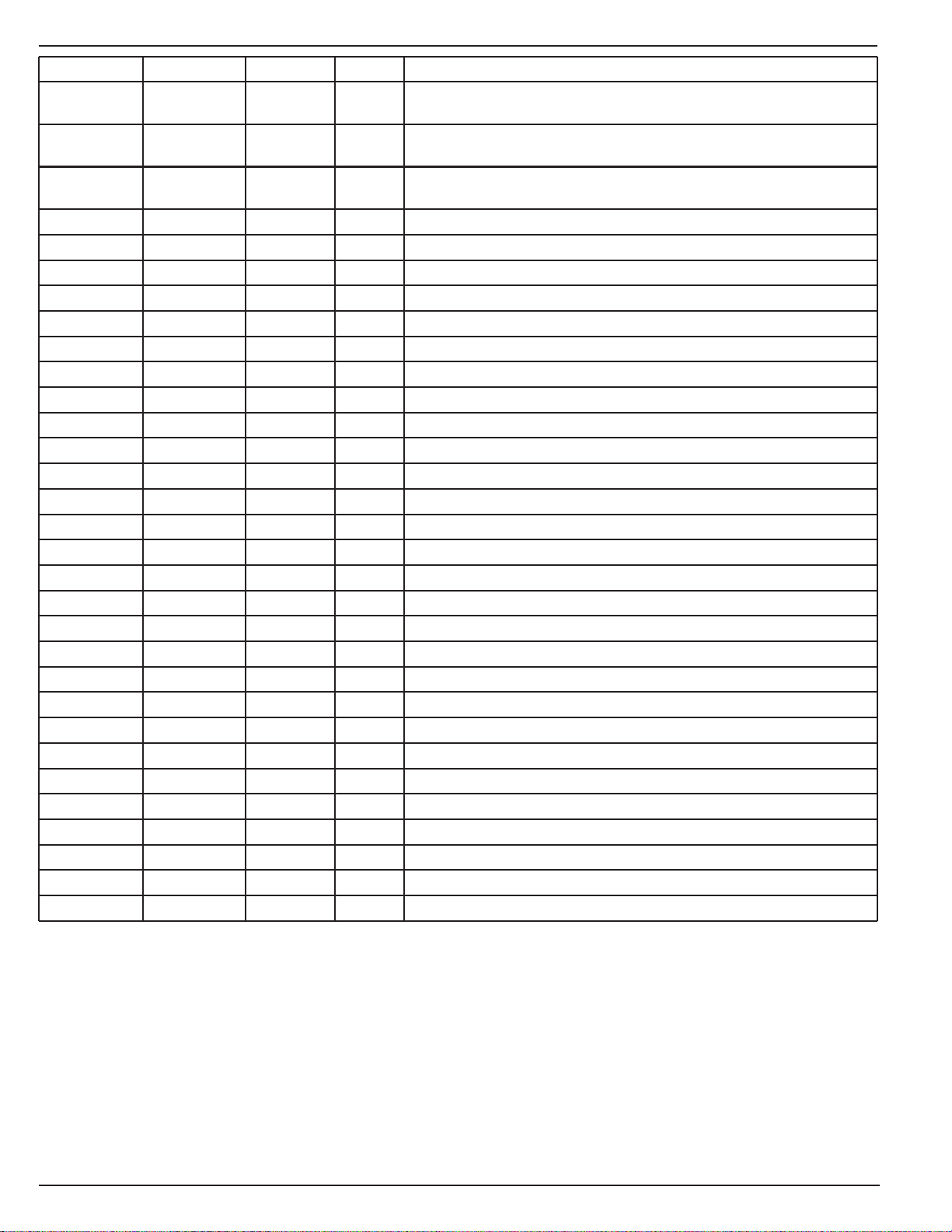

Pin Description (by Number)

Pin Number Pin Name Type

(1)

Port Pin Function

1 MDI-XDIS I 1-5 Disable auto MDI/MDI-X.

PD (default) = normal operation.

PU = disable auto MDI/MDI-X on all ports.

2 GNDA Gnd Analog ground.

3 VDDAR P 1.8V analog VDD.

4 RXP1 I 1 Physical receive signal + (differential).

5 RXM1 I 1 Physical receive signal – (differential).

6 GNDA Gnd Analog ground.

7 TXP1 O 1 Physical transmit signal + (differential).

8 TXM1 O 1 Physical transmit signal – (differential).

9 VDDAT P 2.5V or 3.3V analog VDD.

10 RXP2 I 2 Physical receive signal + (differential).

11 RXM2 I 2 Physical receive signal – (differential).

12 GNDA Gnd Analog ground.

13 TXP2 O 2 Physical transmit signal + (differential).

14 TXM2 O 2 Physical transmit signal – (differential).

15 VDDAR P 1.8V analog VDD.

16 GNDA Gnd Analog ground.

17 ISET Set physical transmit output current. Pull-down with a 3.01kΩ 1%

resistor.

18 VDDAT P 2.5V or 3.3V analog VDD.

19 RXP3 I 3 Physical receive signal + (differential).

20 RXM3 I 3 Physical receive signal - (differential).

21 GNDA Gnd Analog ground.

22 TXP3 O 3 Physical transmit signal + (differential).

23 TXM3 O 3 Physical transmit signal – (differential).

24 VDDAT P 2.5V or 3.3V analog VDD.

25 RXP4 I 4 Physical receive signal + (differential).

26 RXM4 I 4 Physical receive signal - (differential).

27 GNDA Gnd Analog ground.

28 TXP4 O 4 Physical transmit signal + (differential).

29 TXM4 O 4 Physical transmit signal – (differential).

30 GNDA Gnd Analog ground.

(2)

Notes:

1. P = Power supply.

I = Input.

O = Output.

I/O = Bidirectional.

Gnd = Ground.

Ipu = Input w/internal pull-up.

Ipd = Input w/internal pull-down.

Ipd/O = Input w/internal pull-down during reset, output pin otherwise.

Ipu/O = Input w/internal pull-up during reset, output pin otherwise.

2. PU = Strap pin pull-up.

PD = Strap pull-down.

Otri = Output tristated.

M9999-051305 8 May 2005

KS8995XA Micrel, Inc.

Pin Number Pin Name Type

(1)

Port Pin Function

(2)

31 VDDAR P 1.8V analog VDD.

32 RXP5 I 5 Physical receive signal + (differential).

33 RXM5 I 5 Physical receive signal – (differential).

34 GNDA Gnd Analog ground.

35 TXP5 O 5 Physical transmit signal + (differential).

36 TXM5 O 5 Physical transmit signal – (differential).

37 VDDAT P 2.5V or 3.3V analog V

DD.

38 FXSD5 I 5 Fiber signal detect/factory test pin.

39 FXSD4 I 4 Fiber signal detect/factory test pin.

40 GNDA Gnd Analog ground.

41 VDDAR P 1.8V analog VDD.

42 GNDA Gnd Analog ground.

43 VDDAR P 1.8V analog VDD.

44 GNDA Gnd Analog ground.

45 NC / MUX1 I No connect. Factory test pin.

46 NC / MUX2 I No connect. Factory test pin.

47 PWRDN_N Ipu Full-chip power down. Active low.

48 RESERVE/NC Reserved pin. No connect.

49 GNDD Gnd Digital ground.

50 VDDC P 1.8V digital core VDD.

51 PMTXEN Ipd 5 PHY[5] MII transmit enable.

52 PMTXD3 Ipd 5 PHY[5] MII transmit bit 3.

53 PMTXD2 Ipd 5 PHY[5] MII transmit bit 2.

54 PMTXD1 Ipd 5 PHY[5] MII transmit bit 1.

55 PMTXD0 Ipd 5 PHY[5] MII transmit bit 0.

56 PMTXER Ipd 5 PHY[5] MII transmit error.

57 PMTXC O 5 PHY[5] MII transmit clock. PHY mode MII.

58 GNDD Gnd Digital ground.

59 VDDIO P 3.3V digital VDD for digital I/O circuitry.

60 PMRXC O 5 PHY[5] MII receive clock. PHY mode MII.

61 PMRXDV Ipd/O 5 PHY[5] MII receive data valid.

62 PMRXD3 Ipd/O 5 PHY[5] MII receive bit 3. Strap option: PD (default) = enable flow

control; PU = disable flow control.

Notes:

1. P = Power supply.

I = Input.

O = Output.

I/O = Bidirectional.

Gnd = Ground.

Ipu = Input w/internal pull-up.

Ipd = Input w/internal pull-down.

Ipd/O = Input w/internal pull-down during reset, output pin otherwise.

Ipu/O = Input w/internal pull-up during reset, output pin otherwise.

2. PU = Strap pin pull-up.

PD = Strap pull-down.

Otri = Output tristated.

May 2005 9 M9999-051305

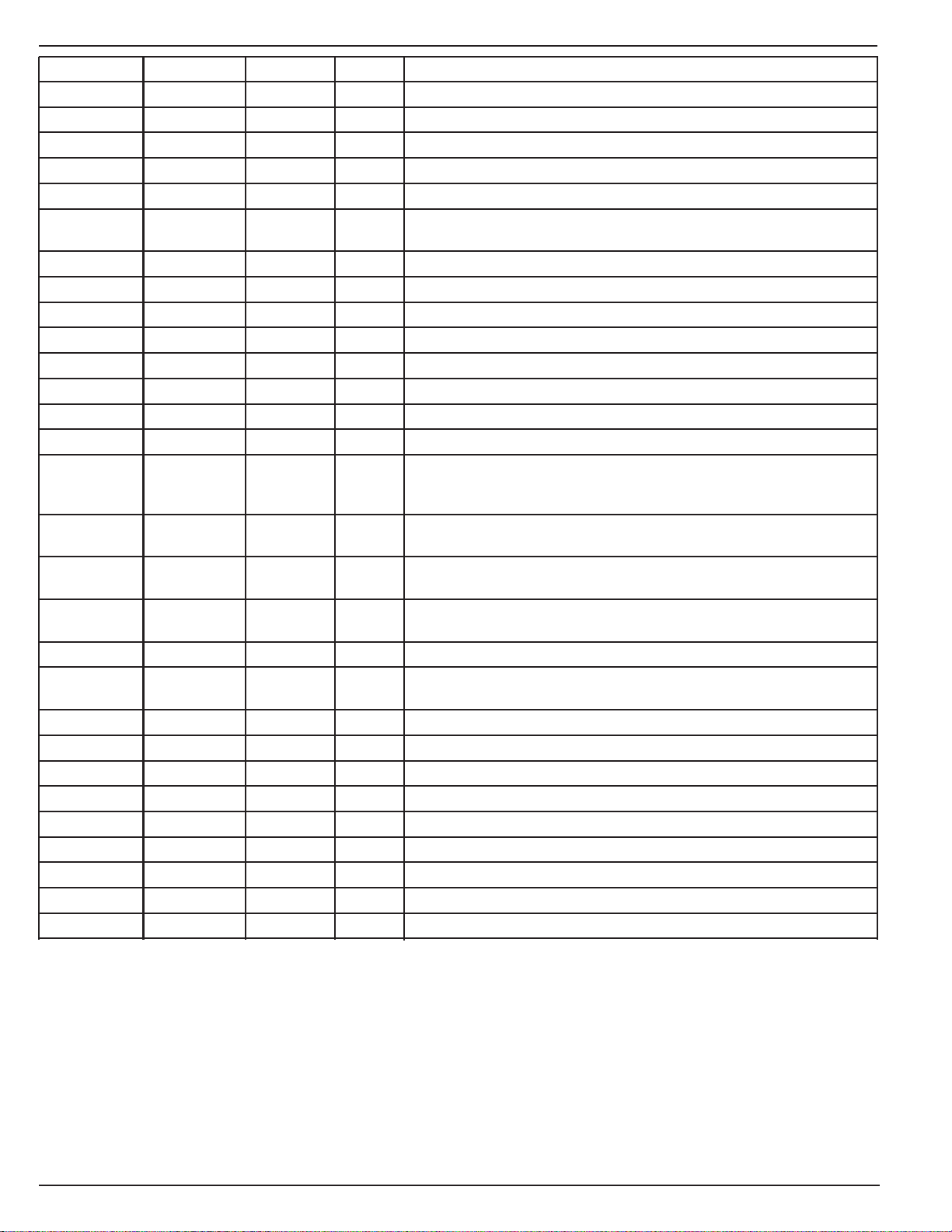

KS8995XA Micrel, Inc.

Pin Number Pin Name Type

(1)

Port Pin Function

(2)

63 PMRXD2 Ipd/O 5 PHY[5] MII receive bit 2. Strap option: PD (default) = disable back

pressure; PU = enable back pressure.

64 PMRXD1 Ipd/O 5 PHY[5] MII receive bit 1. Strap option: PD (default) = drop excessive

collision packets; PU = does not drop excessive collision packets.

65 PMRXD0 Ipd/O 5 PHY[5] MII receive bit 0. Strap option: PD (default) = disable

aggressive back-off algorithm in half-duplex mode; PU = enable for

performance enhancement.

66 PMRXER Ipd/O 5 PHY[5] MII receive error. Strap option: PD (default) = packet size

1518/1522 bytes; PU = 1536 bytes.

67 PCRS Ipd/O 5 PHY[5] MII carrier sense/force duplex mode. See “Register 28.”

68 PCOL Ipd/O 5 PHY[5] MII collision detect/force flow control. See “Register 18.”

69 SMTXEN Ipd Switch MII transmit enable.

70 SMTXD3 Ipd Switch MII transmit bit 3.

71 SMTXD2 Ipd Switch MII transmit bit 2.

72 SMTXD1 Ipd Switch MII transmit bit 1.

73 SMTXD0 Ipd Switch MII transmit bit 0.

74 SMTXER Ipd Switch MII transmit error.

75 SMTXC I/O Switch MII transmit clock. PHY or MAC mode MII.

76 GNDD Gnd Digital ground.

77 VDDIO P 3.3V digital VDD for digital I/O circuitry.

78 SMRXC I/O Switch MII receive clock. PHY or MAC mode MII.

79 SMRXDV Ipd/O Switch MII receive data valid.

80 SMRXD3 Ipd/O Switch MII receive bit 3. Strap option: PD (default) = Disable Switch MII

full-duplex flow control; PU = Enable Switch MII full-duplex flow control.

81 SMRXD2 Ipd/O Switch MII receive bit 2. Strap option: PD (default) = Switch MII in

full-duplex mode; PU = Switch MII in half-duplex mode.

82 SMRXD1 Ipd/O Switch MII receive bit 1. Strap option: PD (default) = Switch MII in

100Mbps mode; PU = Switch MII in 10Mbps mode.

83 SMRXD0 Ipd/O Switch MII receive bit 0; Strap option: see “Register 11[1].”

84 SCOL Ipd/O Switch MII collision detect.

85 SCRS Ipd/O Switch mode carrier sense.

Notes:

1. P = Power supply.

I = Input.

O = Output.

I/O = Bidirectional.

Gnd = Ground.

Ipu = Input w/internal pull-up.

Ipd = Input w/internal pull-down.

Ipd/O = Input w/internal pull-down during reset, output pin otherwise.

Ipu/O = Input w/internal pull-up during reset, output pin otherwise.

2. PU = Strap pin pull-up.

PD = Strap pull-down.

Otri = Output tristated.

M9999-051305 10 May 2005

KS8995XA Micrel, Inc.

Pin Number Pin Name Type

(1)

Port Pin Function

(2)

86 SCONF1 Ipd Dual MII configuration pin.

Pin# (91, 86, 87): Switch MII PHY [5] MII

000 Disable, Otri Disable, Otri

001 PHY Mode MII Disable, Otri

010 MAC Mode MII Disable, Otri

011 PHY Mode SNI Disable, Otri

100 Disable Disable

101 PHY Mode MII PHY Mode MII

110 MAC Mode MII PHY Mode MII

111 PHY Mode SNI PHY Mode MII

87 SCONF0 Ipd Dual MII configuration pin.

88 GNDD Gnd Digital ground.

89 VDDC P 1.8V digital core VDD.

90 LED5-2 Ipu/O 5 LED indicator 2. Aging setup. See “Aging” section.

91 LED5-1 Ipu/O 5 LED indicator 1. Strap option: PU (default): enable PHY MII I/F.

PD: tristate all PHY MII output. See “Pin# 86 SCONF1.”

92 LED5-0 Ipu/O 5 LED indicator 0.

93 LED4-2 Ipu/O 4 LED indicator 2.

94 LED4-1 Ipu/O 4 LED indicator 1.

95 LED4-0 Ipu/O 4 LED indicator 0.

96 LED3-2 Ipu/O 3 LED indicator 2.

97 LED3-1 Ipu/O 3 LED indicator 1.

98 LED3-0 Ipu/O 3 LED indicator 0.

99 GNDD Gnd Digital ground.

100 VDDIO P 3.3V digital VDD for digital I/O.

101 LED2-2 Ipu/O 2 LED indicator 2.

102 LED2-1 Ipu/O 2 LED indicator 1.

103 LED2-0 Ipu/O 2 LED indicator 0.

104 LED1-2 Ipu/O 1 LED indicator 2.

105 LED1-1 Ipu/O 1 LED indicator 1.

106 LED1-0 Ipu/O 1 LED indicator 0.

107 MDC Ipu All Switch or PHY[5] MII management data clock.

108 MDIO Ipu/O All Switch or PHY[5] MII management data I/O.

Notes:

1. P = Power supply.

I = Input.

O = Output.

I/O = Bidirectional.

Gnd = Ground.

Ipu = Input w/internal pull-up.

Ipd = Input w/internal pull-down.

Ipd/O = Input w/internal pull-down during reset, output pin otherwise.

Ipu/O = Input w/internal pull-up during reset, output pin otherwise.

2. PU = Strap pin pull-up.

PD = Strap pull-down.

Otri = Output tristated.

May 2005 11 M9999-051305

KS8995XA Micrel, Inc.

Pin Number Pin Name Type

(1)

Port Pin Function

109 Reserved All No connect.

110 SCL I/O All Output clock at 81kHz in I2C master mode.

111 SDA I/O All Serial data input/output in I2C master mode.

112 Reserved All No connect

113 PS1 Ipd No connect or pull-down.

114 PS0 Ipd No connect or pull-down.

115 RST_N Ipu Reset the KS8995XA. Active low.

116 GNDD Gnd Digital ground.

117 VDDC P 1.8V digital core VDD.

118 TESTEN Ipd Factory test pin.

119 SCANEN Ipd Factory test pin.

120 NC NC No connection.

121 X1 I 25MHz crystal clock connection/or 3.3V tolerant oscillator input.

Oscillator should be ±100ppm.

122 X2 O 25MHz crystal clock connection.

123 VDDAP P 1.8V analog VDD for PLL.

124 GNDA Gnd Analog ground.

125 VDDAR P 1.8V analog VDD.

126 GNDA Gnd Analog ground.

127 GNDA Gnd Analog ground.

128 TEST2 Factory test pin.

Note:

1. P = Power supply.

I = Input.

O = Output.

I/O = Bidirectional.

Gnd = Ground.

Ipu = Input w/internal pull-up.

Ipd = Input w/internal pull-down.

Ipd/O = Input w/internal pull-down during reset, output pin otherwise.

Ipu/O = Input w/internal pull-up during reset, output pin otherwise.

NC = No connect.

M9999-051305 12 May 2005

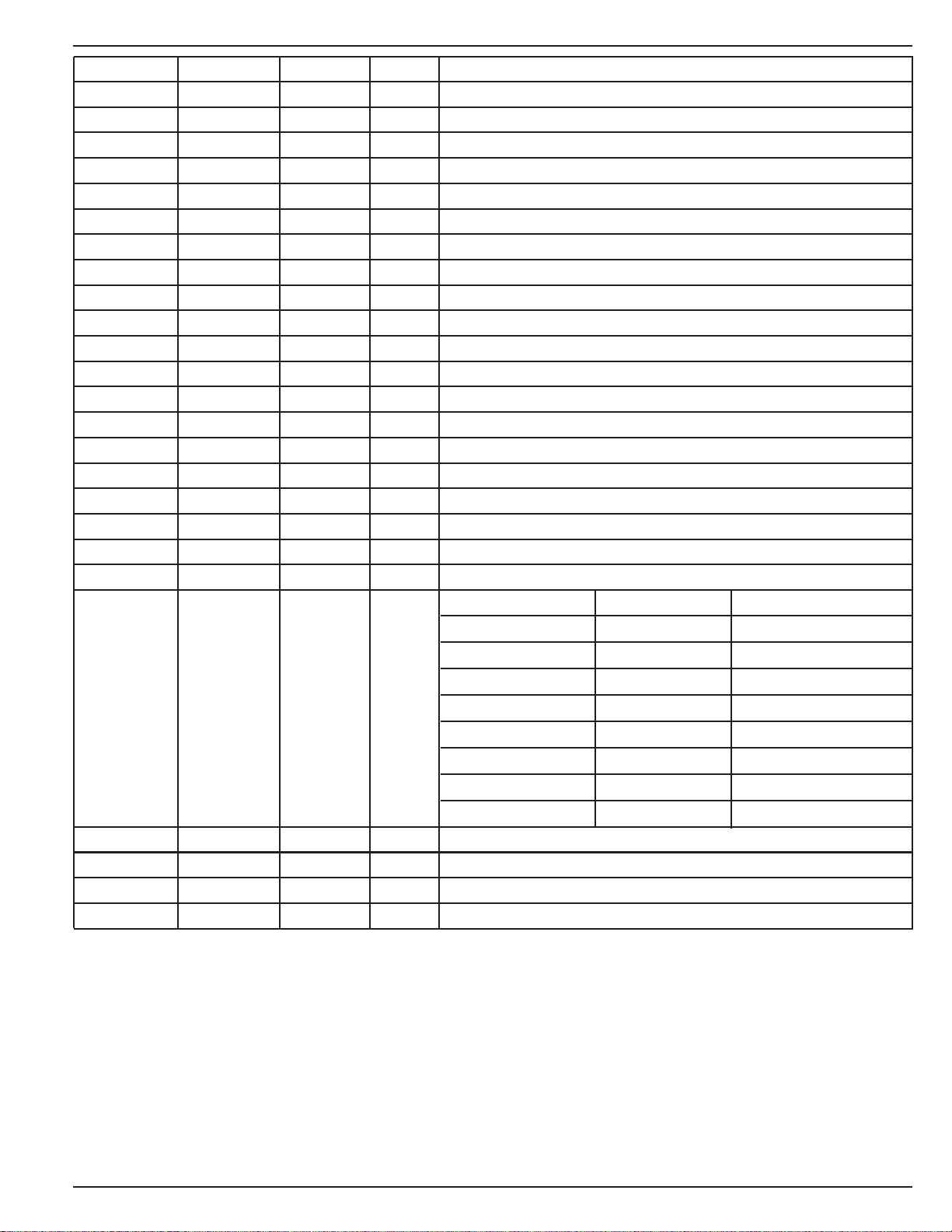

KS8995XA Micrel, Inc.

Pin Description (by Name)

Pin Number Pin Name Type

39 FXSD4 I 4 Fiber signal detect/factory test pin.

38 FXSD5 I 5 Fiber signal detect/factory test pin.

2 GNDA Gnd Analog ground.

6 GNDA Gnd Analog ground.

12 GNDA Gnd Analog ground.

16 GNDA Gnd Analog ground.

21 GNDA Gnd Analog ground.

27 GNDA Gnd Analog ground.

30 GNDA Gnd Analog ground.

34 GNDA Gnd Analog ground.

40 GNDA Gnd Analog ground.

42 GNDA Gnd Analog ground.

44 GNDA Gnd Analog ground.

120 NC NC No connection.

124 GNDA Gnd Analog ground.

126 GNDA Gnd Analog ground.

127 GNDA Gnd Analog ground.

49 GNDD Gnd Digital ground.

58 GNDD Gnd Digital ground.

76 GNDD Gnd Digital ground.

88 GNDD Gnd Digital ground.

99 GNDD Gnd Digital ground.

116 GNDD Gnd Digital ground.

17 ISET Set physical transmit output current. Pull down with a 3.01kΩ 1%

106 LED1-0 Ipu/O 1 LED indicator 0.

105 LED1-1 Ipu/O 1 LED indicator 1.

104 LED1-2 Ipu/O 1 LED indicator 2.

103 LED2-0 Ipu/O 2 LED indicator 0.

102 LED2-1 Ipu/O 2 LED indicator 1.

101 LED2-2 Ipu/O 2 LED indicator 2.

98 LED3-0 Ipu/O 3 LED indicator 0.

97 LED3-1 Ipu/O 3 LED indicator 1.

(1)

Port Pin Function

resistor.

Note:

1. P = Power supply.

I = Input.

O = Output.

I/O = Bidirectional.

Gnd = Ground.

Ipu = Input w/internal pull-up.

Ipd = Input w/internal pull-down.

Ipd/O = Input w/internal pull-down during reset, output pin otherwise.

Ipu/O = Input w/internal pull-up during reset, output pin otherwise.

NC = No connect.

May 2005 13 M9999-051305

KS8995XA Micrel, Inc.

Pin Number Pin Name Type

(1)

Port Pin Function

(2)

96 LED3-2 Ipu/O 3 LED indicator 2.

95 LED4-0 Ipu/O 4 LED indicator 0.

94 LED4-1 Ipu/O 4 LED indicator 1.

93 LED4-2 Ipu/O 4 LED indicator 2.

92 LED5-0 Ipu/O 5 LED indicator 0.

91 LED5-1 Ipu/O 5 LED indicator 1. Strap option: PU (default): enable PHY MII I/F

Pd: tristate all PHY MII output. See “Pin# 86 SCONF1.”

90 LED5-2 Ipu/O 5 LED indicator 2. Aging setup. See “Aging” section.

107 MDC Ipu All Switch or PHY[5] MII management data clock.

108 MDIO Ipu/O All Switch or PHY[5] MII management data I/O.

45 NC / MUX1 I No connect. Factory test pin.

46 NC / MUX2 I No connect. Factory test pin.

68 PCOL Ipd/O 5 PHY[5] MII collision detect/ Force flow control. See “Register 18.”

67 PCRS Ipd/O 5 PHY[5] MII carrier sense/Force duplex mode. See “Register 28.”

60 PMRXC O 5 PHY[5] MII receive clock. PHY mode MII.

65 PMRXD0 Ipd/O 5 PHY[5] MII receive bit 0. Strap option: PD (default) = disable

aggressive back-off algorithm in half-duplex mode; PU = enable for

performance enhancement.

64 PMRXD1 Ipd/O 5 PHY[5] MII receive bit 1. Strap option: PD (default) = drop excessive

collision packets; PU = does not drop excessive collision packets.

63 PMRXD2 Ipd/O 5 PHY[5] MII receive bit 2. Strap option: PD (default) = disable back

pressure; PU = enable back pressure.

62 PMRXD3 Ipd/O 5 PHY[5] MII receive bit 3. Strap option: PD (default) = enable flow

control; PU = disable flow control.

61 PMRXDV Ipd/O 5 PHY[5] MII receive data valid.

66 PMRXER Ipd/O 5 PHY[5] MII receive error. Strap option: PD (default) = packet size 1518/

1522 bytes; PU = 1536 bytes.

57 PMTXC O 5 PHY[5] MII transmit clock. PHY mode MII.

55 PMTXD0 Ipd 5 PHY[5] MII transmit bit 0.

54 PMTXD1 Ipd 5 PHY[5] MII transmit bit 1.

53 PMTXD2 Ipd 5 PHY[5] MII transmit bit 2.

52 PMTXD3 Ipd 5 PHY[5] MII transmit bit 3.

51 PMTXEN Ipd 5 PHY[5] MII transmit enable.

56 PMTXER Ipd 5 PHY[5] MII transmit error.

114 PS0 Ipd No connect or pull down.

113 PS1 Ipd No connect or pull down.

Notes:

1. P = Power supply.

I = Input.

O = Output.

I/O = Bidirectional.

Gnd = Ground.

Ipu = Input w/internal pull-up.

Ipd = Input w/internal pull-down.

Ipd/O = Input w/internal pull-down during reset, output pin otherwise.

Ipu/O = Input w/internal pull-up during reset, output pin otherwise.

2. PU = Strap pin pull-up.

PD = Strap pull-down.

M9999-051305 14 May 2005

KS8995XA Micrel, Inc.

Pin Number Pin Name Type

(1)

Port Pin Function

(2)

47 PWRDN_N Ipu Full-chip power down. Active low.

48 RESERVE/NC Reserved pin. No connect.

109 Reserved All No connect.

112 Reserved All No connect.

115 RST_N Ipu Reset the KS8995X. Active low.

5 RXM1 I 1 Physical receive signal - (differential).

11 RXM2 I 2 Physical receive signal - (differential).

20 RXM3 I 3 Physical receive signal - (differential).

26 RXM4 I 4 Physical receive signal - (differential).

33 RXM5 I 5 Physical receive signal - (differential).

4 RXP1 I 1 Physical receive signal + (differential).

10 RXP2 I 2 Physical receive signal + (differential).

19 RXP3 I 3 Physical receive signal + (differential).

25 RXP4 I 4 Physical receive signal + (differential).

32 RXP5 I 5 Physical receive signal + (differential).

119 SCANEN Ipd Factory test pin.

110 SCL I/O All Output clock at 81kHz in I2C master mode. See “Pin# 113.”

84 SCOL Ipd/O Switch MII collision detect.

87 SCONF0 Ipd Dual MII configuration pin.

86 SCONF1 Ipd Dual MII configuration pin.

Pin# (91, 86, 87): Switch MII PHY [5] MII

000 Disable, Otri Disable, Otri

001 PHY Mode MII Disable, Otri

010 MAC Mode MII Disable, Otri

011 PHY Mode SNI Disable, Otri

100 Disable Disable

101 PHY Mode MII PHY Mode MII

110 MAC Mode MII PHY Mode MII

111 PHY Mode SNI PHY Mode MII

85 SCRS Ipd/O Switch MII carrier sense.

111 SDA I /O All Serial data input/output in I2C master mode. See “Pin# 113.”

78 SMRXC I/O Switch MII receive clock. PHY or MAC mode MII.

83 SMRXD0 Ipd/O Switch MII receive bit 0; strap option: see “Register 11[1].”

Notes:

1. P = Power supply.

I = Input.

O = Output.

I/O = Bidirectional.

Gnd = Ground.

Ipu = Input w/internal pull-up.

Ipd = Input w/internal pull-down.

Ipd/O = Input w/internal pull-down during reset, output pin otherwise.

Ipu/O = Input w/internal pull-up during reset, output pin otherwise.

2. Otri = Output tristated.

May 2005 15 M9999-051305

KS8995XA Micrel, Inc.

Pin Number Pin Name Type

(1)

Port Pin Function

(2)

82 SMRXD1 Ipd/O Switch MII receive bit 1. Strap option: PD (default) = Switch MII in

100Mbps mode; PU = Switch MII in 10Mbps mode.

81 SMRXD2 Ipd/O Switch MII receive bit 2. Strap option: PD (default) = Switch MII in full-

duplex mode; PU = Switch MII in half-duplex mode.

80 SMRXD3 Ipd/O Switch MII receive bit 3. Strap option: PD (default) = Disable Switch MII

full-duplex flow control; PU = Enable Switch MII full-duplex flow control.

79 SMRXDV Ipd/O Switch MII receive data valid.

75 SMTXC I/O Switch MII transmit clock. PHY or MAC mode MII.

73 SMTXD0 Ipd Switch MII transmit bit 0.

72 SMTXD1 Ipd Switch MII transmit bit 1.

71 SMTXD2 Ipd Switch MII transmit bit 2.

70 SMTXD3 Ipd Switch MII transmit bit 3.

69 SMTXEN Ipd Switch MII transmit enable.

74 SMTXER Ipd Switch MII transmit error.

1 MDIXDIS I 1-5 Disable auto MDI/MDI-X.

128 TEST2 Factory test pin.

118 TESTEN Ipd Factory test pin.

7 TXP1 O 1 Physical transmit signal + (differential).

13 TXP2 O 2 Physical transmit signal + (differential).

22 TXP3 O 3 Physical transmit signal + (differential).

28 TXP4 O 4 Physical transmit signal + (differential).

35 TXP5 O 5 Physical transmit signal + (differential).

8 TXM1 O 1 Physical transmit signal – (differential).

14 TXM2 O 2 Physical transmit signal – (differential).

23 TXM3 O 3 Physical transmit signal – (differential).

29 TXM4 O 4 Physical transmit signal – (differential).

36 TXM5 O 5 Physical transmit signal – (differential).

123 VDDAP P 1.8V analog VDD for PLL.

3 VDDAR P 1.8V analog VDD.

15 VDDAR P 1.8V analog VDD.

31 VDDAR P 1.8V analog VDD.

41 VDDAR P 1.8V analog VDD.

43 VDDAR P 1.8V analog VDD.

125 VDDAR P 1.8V analog VDD.

Notes:

1. P = Power supply.

I = Input.

O = Output.

I/O = Bidirectional.

Gnd = Ground.

Ipu = Input w/internal pull-up.

Ipd = Input w/internal pull-down.

Ipd/O = Input w/internal pull-down during reset, output pin otherwise.

Ipu/O = Input w/internal pull-up during reset, output pin otherwise.

2. PU = Strap pin pull-up.

PD = Strap pull-down.

M9999-051305 16 May 2005

Loading...

Loading...