Page 1

Preliminary, v 0.06

MA816

MA816

数据手册

版本 0.06

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 1/79

Page 2

Preliminary, v 0.06

MA816

目 录

1. 概述 ..............................................................................................................5

2. 功能 ..............................................................................................................6

3. 方框图...........................................................................................................7

4. 特殊功能寄存器SFR .....................................................................................8

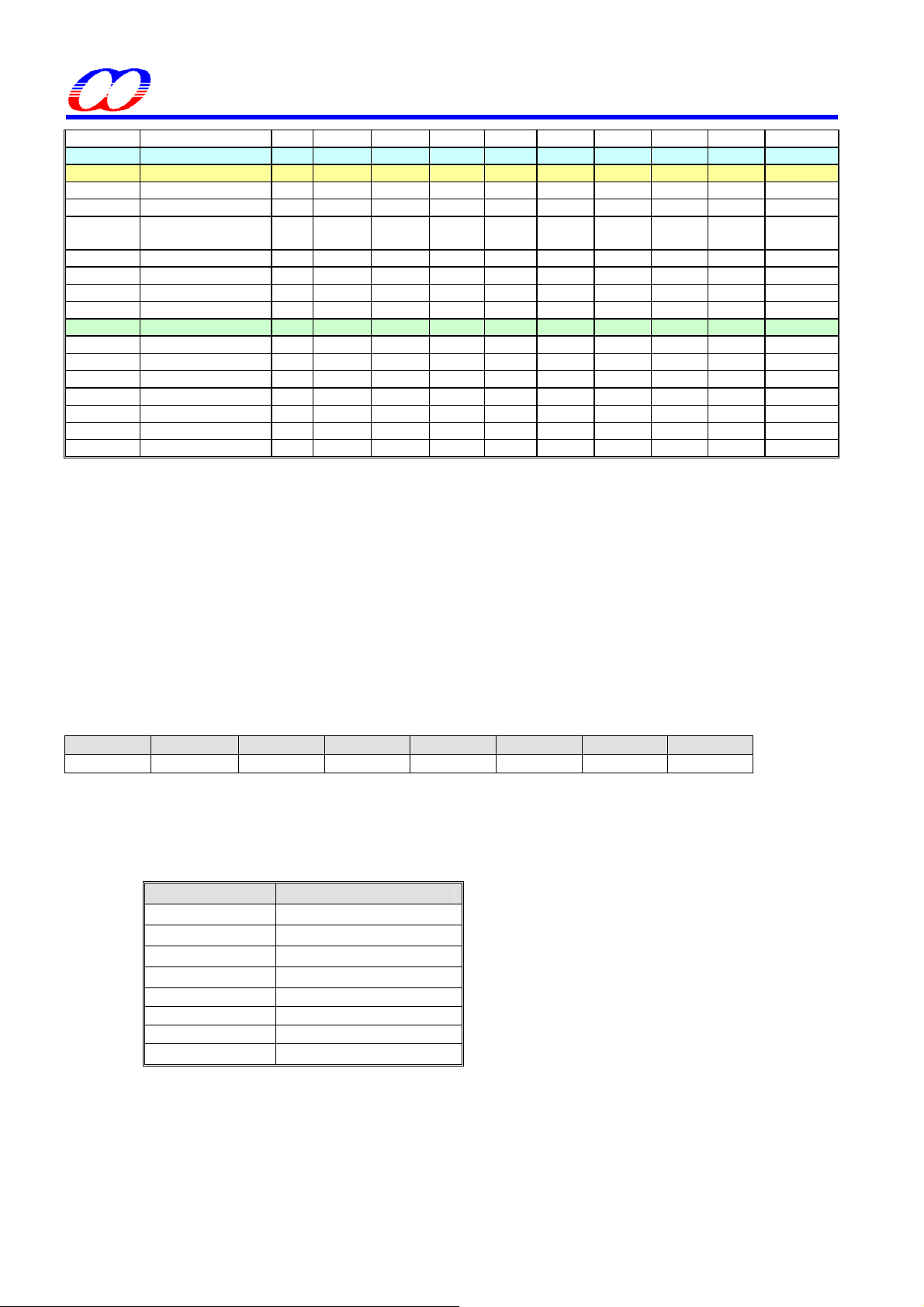

4.1. SFR 映射表...........................................................................................................................8

4.2. SFR 位分配...........................................................................................................................9

4.3. SFR 内存分页 .....................................................................................................................10

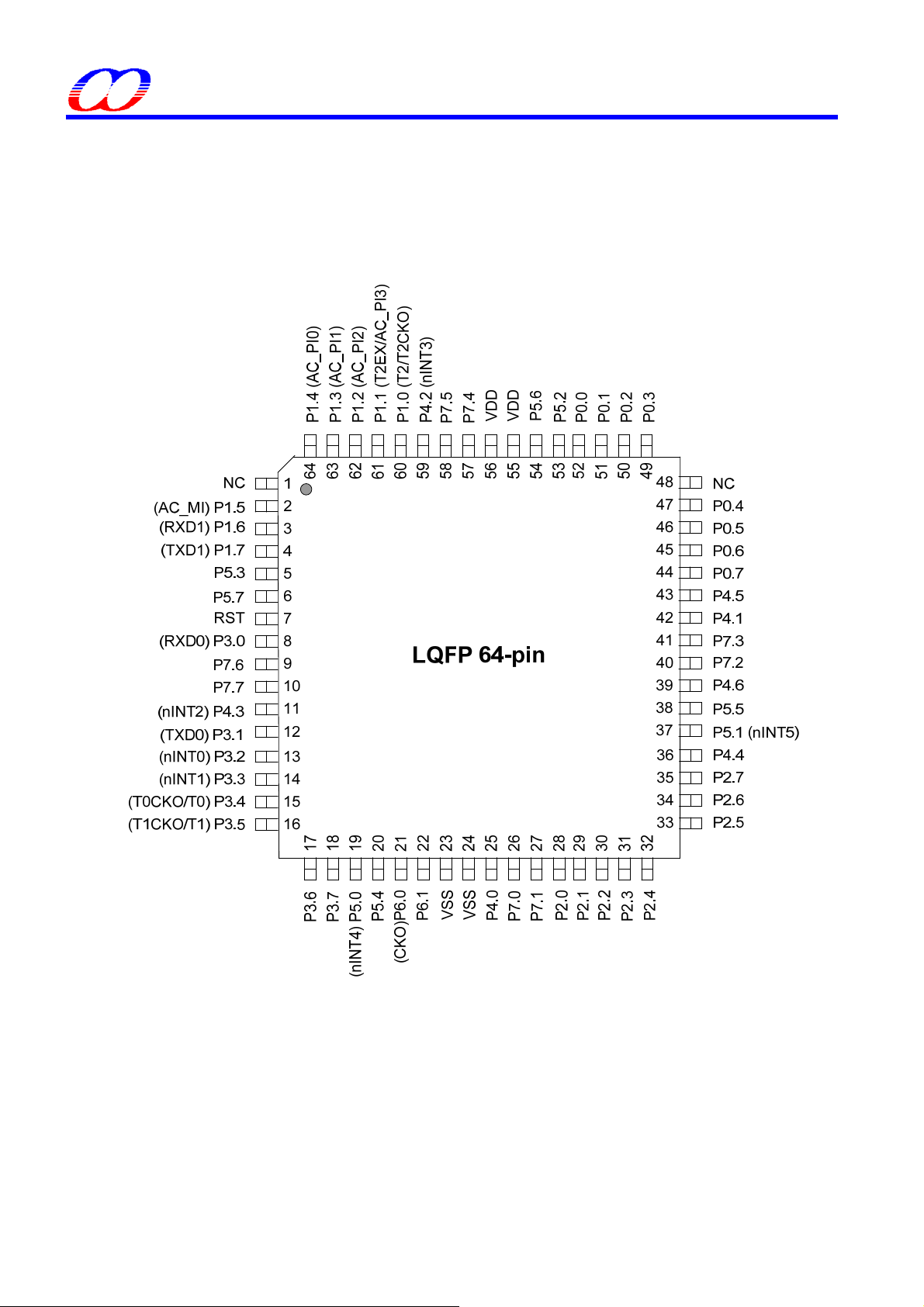

5. 引脚 ............................................................................................................11

5.1. 封装 .....................................................................................................................................11

5.2. 引脚定义 ..............................................................................................................................12

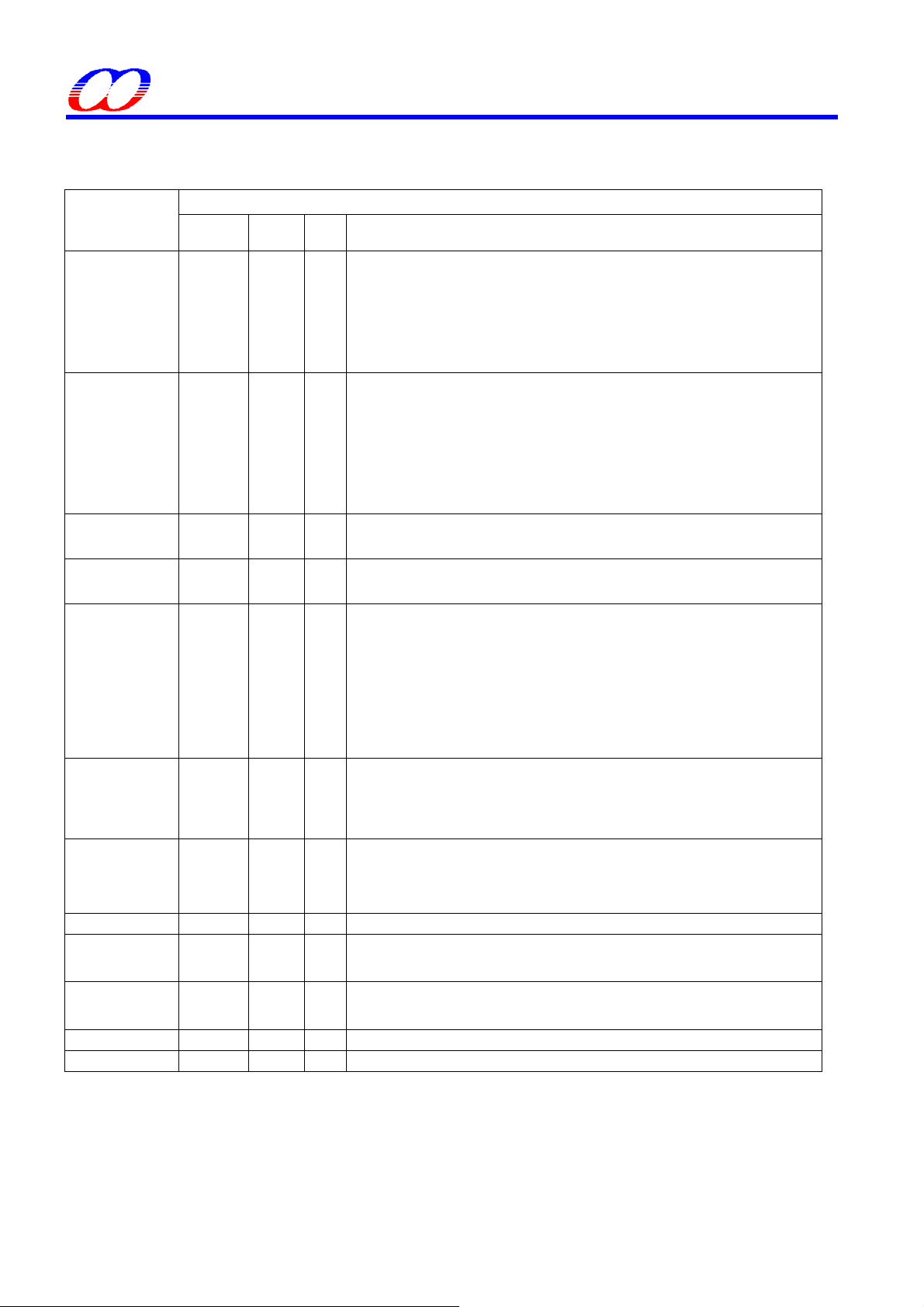

6. 系统时钟 .....................................................................................................13

6.1. 时钟结构图 ..........................................................................................................................13

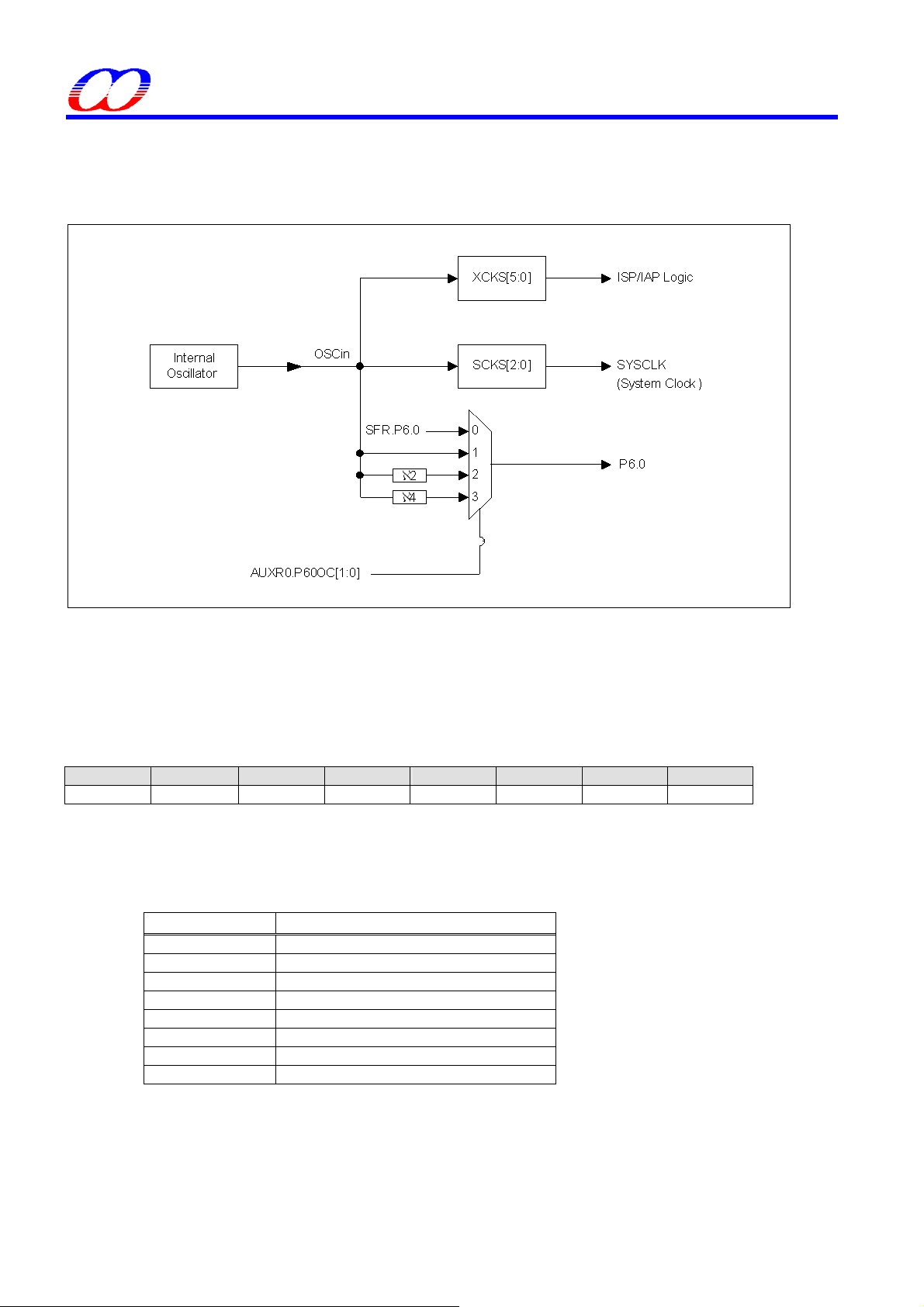

6.2. 时钟寄存器 ..........................................................................................................................13

7. 8051 CPU 功能描述...................................................................................15

7.1. CPU 寄存器 ........................................................................................................................15

7.2. CPU 时序............................................................................................................................16

7.3. CPU 寻址方式.....................................................................................................................16

8. 存储器结构..................................................................................................17

8.1. 片上程序存储器 ...................................................................................................................17

8.2. 片上数据存储器 RAM .........................................................................................................18

8.3. 片上扩展RAM (XRAM) ........................................................................................................18

8.4. 关于C51 编译器的声明识别符 .............................................................................................19

9. 双数据指针寄存器 (DPTR).........................................................................20

10. I/O 结构......................................................................................................21

10.1. IO 配置................................................................................................................................21

10.1.1. 准双向口........................................................................................................................21

10.1.2. 推挽输出........................................................................................................................21

10.1.3. 仅输入(高阻输入) ..........................................................................................................22

10.1.4. 开漏集输出....................................................................................................................22

10.2. I/O 端口寄存器....................................................................................................................23

10.2.1. 端口 0...........................................................................................................................24

10.2.2. 端口 1...........................................................................................................................24

10.2.3. 端口 2...........................................................................................................................24

10.2.4. 端口 3...........................................................................................................................25

10.2.5. 端口 4...........................................................................................................................25

10.2.6. 端口 5...........................................................................................................................26

10.2.7. 端口 6...........................................................................................................................26

10.2.8. 端口 7...........................................................................................................................27

11. 中断 ............................................................................................................28

11.1. 中断结构..............................................................................................................................28

11.2. 中断寄存器 ..........................................................................................................................29

12. 定时器/计数器 .............................................................................................35

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 2/79

Page 3

12.1. 定时器 0 和定时器 1............................................................................................................35

12.1.1. 模式 0...........................................................................................................................35

12.1.2. 模式 1 ............................................................................................................................36

12.1.3. 模式 2 ............................................................................................................................36

12.1.4. 模式 3 ............................................................................................................................37

12.1.5. 定时器时钟输出.............................................................................................................37

12.1.6. 定时器 0/1 寄存器..........................................................................................................38

12.2. 定时器 2...............................................................................................................................40

12.2.1. 捕获模式 (CP) ..............................................................................................................40

12.2.2. 自动加载模式(AR).........................................................................................................40

12.2.3. 波特率发生器模式 (BRG) .............................................................................................42

12.2.4. 定时器 2 的可编程时钟输出模式 ...................................................................................43

12.2.5. 定时器 2 寄存器.............................................................................................................43

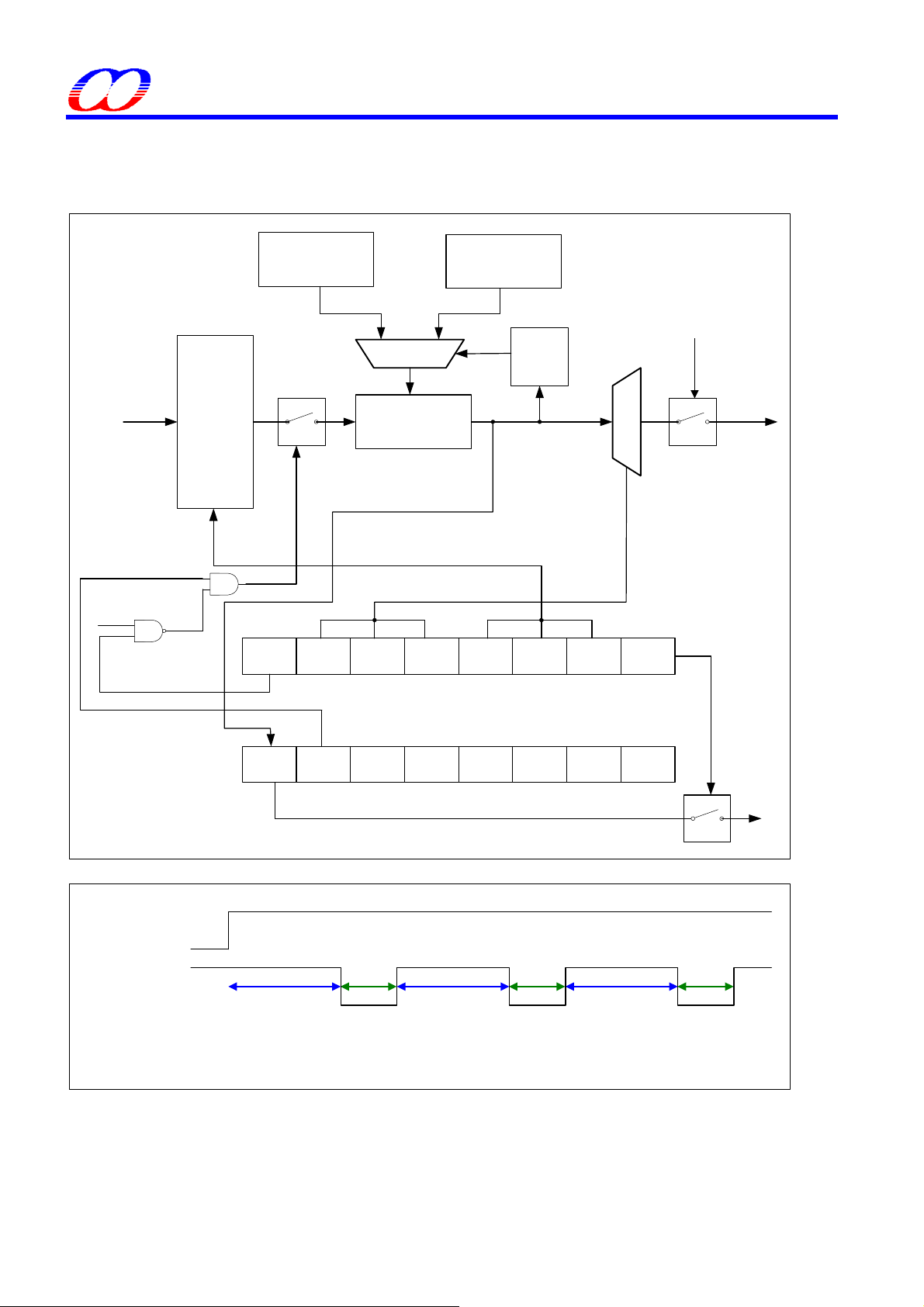

12.3. PWM 定时器 .......................................................................................................................45

12.3.1. PWM 定时器结构 .........................................................................................................45

12.3.2. PWM 定时器寄存器......................................................................................................46

Preliminary, v 0.06

MA816

13. 串行口 (UART)...........................................................................................48

13.1. 模式 0 详述 ..........................................................................................................................48

13.2. 模式 1 详述 ..........................................................................................................................51

13.3. 模式 2、3 详述.....................................................................................................................52

13.4. 帧错误检测 ..........................................................................................................................52

13.5. 多处理器通讯.......................................................................................................................53

13.6. 自动地址识别.......................................................................................................................53

13.7. 波特率设置 ..........................................................................................................................55

13.7.1. 模式 0 波特率 ................................................................................................................55

13.7.2. 模式 2 波特率 ................................................................................................................55

13.7.3. 模式 1 & 3 波特率..........................................................................................................55

13.8. 串口寄存器 ..........................................................................................................................55

14. 模拟比较器..................................................................................................58

14.1. 模拟比较器结构 ...................................................................................................................58

14.2. 模拟比较器寄存器................................................................................................................58

15. 看门狗 (WDT) ............................................................................................61

15.1. 看门狗结构 ..........................................................................................................................61

15.2. 看门狗寄存器.......................................................................................................................61

15.3. WDT 硬件选项 ....................................................................................................................62

16. Power Management ...................................................................................63

16.1. 节能模式..............................................................................................................................63

16.1.1. 空闲模式(Idle)...........................................................................................................63

16.1.2. 掉电模式(Power-down) .................................................................................................63

16.1.3. 中断唤醒........................................................................................................................63

16.1.4. 复位唤醒........................................................................................................................63

16.1.5. 普通I/O (GPIO) 唤醒.....................................................................................................63

16.2. Brown-Out侦察器 ................................................................................................................64

16.3. 电源控制寄存器 ...................................................................................................................64

17. 在系统编程 (ISP)........................................................................................66

18. 在应用程序编程 (IAP) ................................................................................69

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 3/79

Page 4

Preliminary, v 0.06

MA816

19. 辅助特殊功能寄存器SFR ............................................................................70

20. 指令集.........................................................................................................72

21. 最大绝对额定参数.......................................................................................76

22. 电气特性 .....................................................................................................77

22.1. 直流特性..............................................................................................................................77

23. 封装尺寸 .....................................................................................................78

24. 修订历史 .....................................................................................................79

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 4/79

Page 5

Preliminary, v 0.06

MA816

1. 概述

MA816 是基于80C51的高效1-T结构的单芯片微处理器,每条指令需要1~7个时钟信号 (比标准8051快6~7倍),与8051

指令集兼容。因此在与标准8051有同样的处理能力的情况下,MA816只需要非常低的运行速度,同时由此能很大程度

的减少耗电量。

MA816拥有14.5K字节的内置Flash存储器用于保存代码AP和数据IAP。Flash存储器可以通过在系统编程(ISP), ISP

让使用者无需从产品中取下微控制器就可以下载新的代码;IAP意味着应用程序正在运行时,微控制器能够在Flash中

写入非易失数据。这些功能都由内建的电荷泵提供编程用的高压。

MA816 保留了标准80C52的基本特色:256 字节的随机存储器、四个8位I/O口、两个外部中断、一个多源4级中断控

制器、及三个定时/计数器。增加的有:MA816 有四个额外的I/O口(P4[6:0]、P5、 P6[1:0]、 P7),一个256字节的 XRAM,

四个额外的能选择高电平或低电平触发的外部中断,一个PWM定时器,一个一次性使能的看门狗WDT,一个精确的多

路输入和片上VDD参考电压的模拟比较器,一个Brown-out侦察器,一个片上晶体振荡器(共享P6.0、P6.1),一个高

精度内部振荡器,一个为方便多处理器通讯和改进了速度(额外X2/X4模式)的增强型通用串行口(EUART)。

MA816有两种节能模式和8位的系统时钟分频器,以减少耗电量。在空闲模式下,CPU被冻结而外围模块和中断系统

依然活动。在掉电模式下,随机存储器RAM和特殊功能寄存器SFR的内容被保存,而其他所有功能被终止。最重要的

是,在掉电模式下的微控制器可以被外部中断唤醒。同时使用者可以通过8位的系统时钟分频器减慢系统速度以减少耗

电量。

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 5/79

Page 6

Preliminary, v 0.06

MA816

2. 功能

z 1-T 80C51 中央处理单元

z MA816 有 14.5K 字节 Flash ROM

━ 13.5KB 为 AP 空间(0x0000 ~ 0x35FF)

━ 1KB 为 IAP 空间(0x3600 ~ 0x39FF)

━ 为 Flash 存储器存取提供代码保护

z 片上 256 字节数据 RAM 和片上 256 字节扩展 RAM

z 双数据指针 DPTR

z 三个 16 位定时/计数器:Timer 0、 Timer 1 和 Timer 2.

━ T0CKO - P34,T1CKO - P35, T2CKO - P10

━ T0/T1/T2 可选择使能 X12 模式

z PWM-定时间器可以作 PWM 发生器或作普通 16 位定时器

━ 最大 16 路 PWM 输出 在 P2、P5 端口选择

z 增强型 UART

━ 支持帧错误检测,硬件地址识别

━ 在 P16/P17 上功能交换

z 六个外部中断输入: nINT0/nINT1/nINT2/nINT3/nINT4/nINT5

━ nINT0/nINT1 触发类型:低电平或下降沿

━ nINT2/nINT3/nINT4/nINT5 触发类型:低电平、下降沿、高电平、或上升沿

z 13 个中断源,四级优先级中断能力

z 内建模拟比较器和片上 VDD 参考输入

━ 比较器正输入有 4 路 I/O 选择

━ I/O 口可编程比较器负输入或 15 级片上 VDD 参考

z 15 位看门狗定时器 Watch-Dog-Timer.

━ 8 位分频

━ 通过 CPU 或上电一次性使能

z 最大有 57 个通用输入输出

━ P0, P1, P2, P3, P4, P5 能被配置为准双向口(quasi-bidirectional)、推挽式输出(push-pull)、开漏集输出

(open-drain)及仅输入(input only)四种模式

━ P6 和 P7 只能作准双向口模式

━ P4.0 和 P4.1 能被配置为仅输入或准双向口模式(缺省)

z 电源控制:空闲模式(idle mode)和掉电模式(power-down mode)

━ 所有的中断和 16 个 GPIO 能唤醒空闲模式

━ 6 个外部中断和 16 个 GPIO 能唤醒掉电模式

z Brown-Out 侦察器 4.0V

━ 选择复位 CPU 或产生 CPU 中断

z 工作电压:4.5V~5.5V

z 工作频率:

━ 12 MHz 内部 RC 振荡器,温度在-40 ~ 85℃范围内误差 +/- 4%的频漂

━ 内部 RC 振荡器通过 P6.0 输出

z 工作温度:

━ 工业级别 (-40℃ 至 +85℃)*

z 封装类型:

━ LQFP64:MA816

*:样品测试

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 6/79

Page 7

Preliminary, v 0.06

MA816

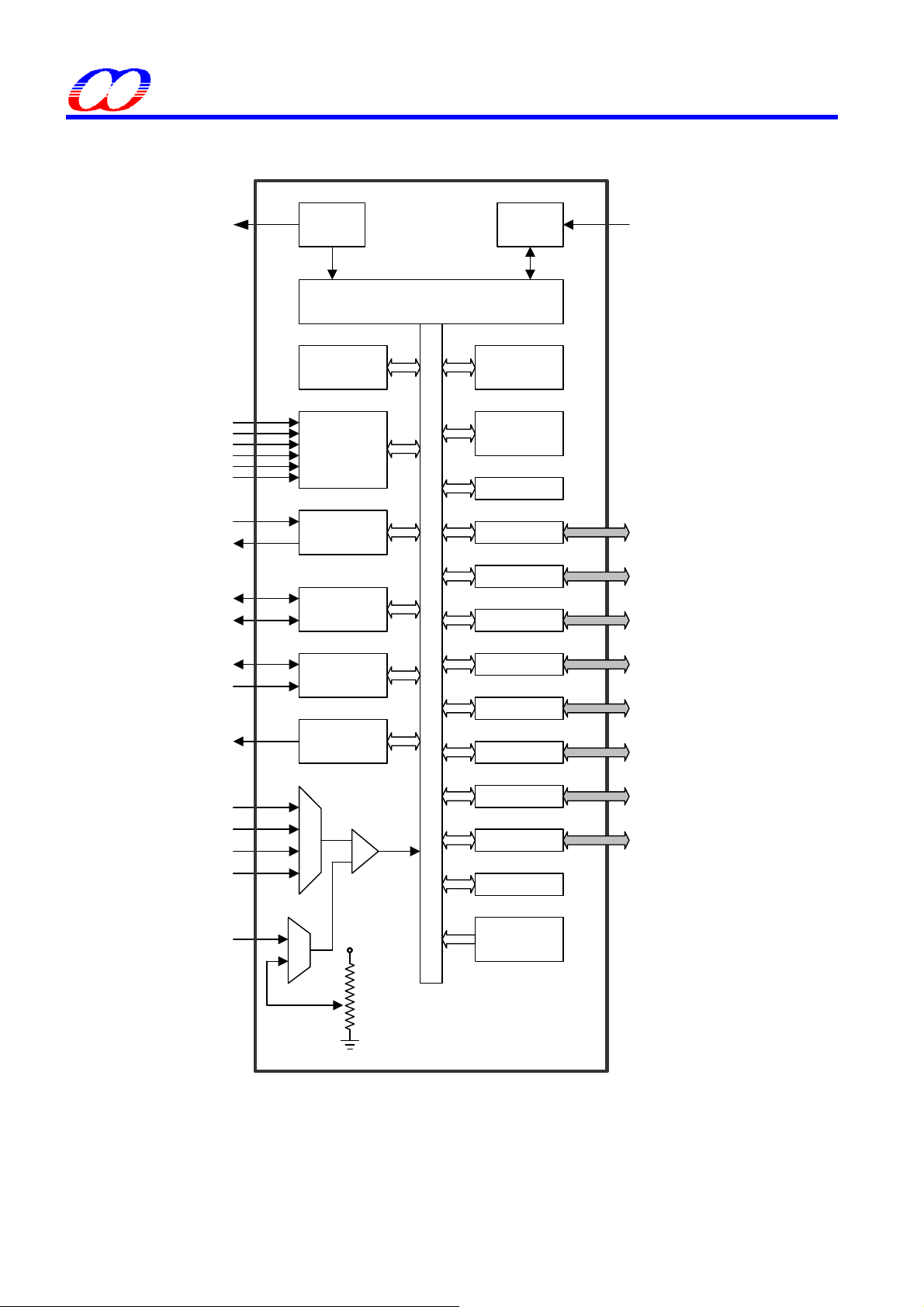

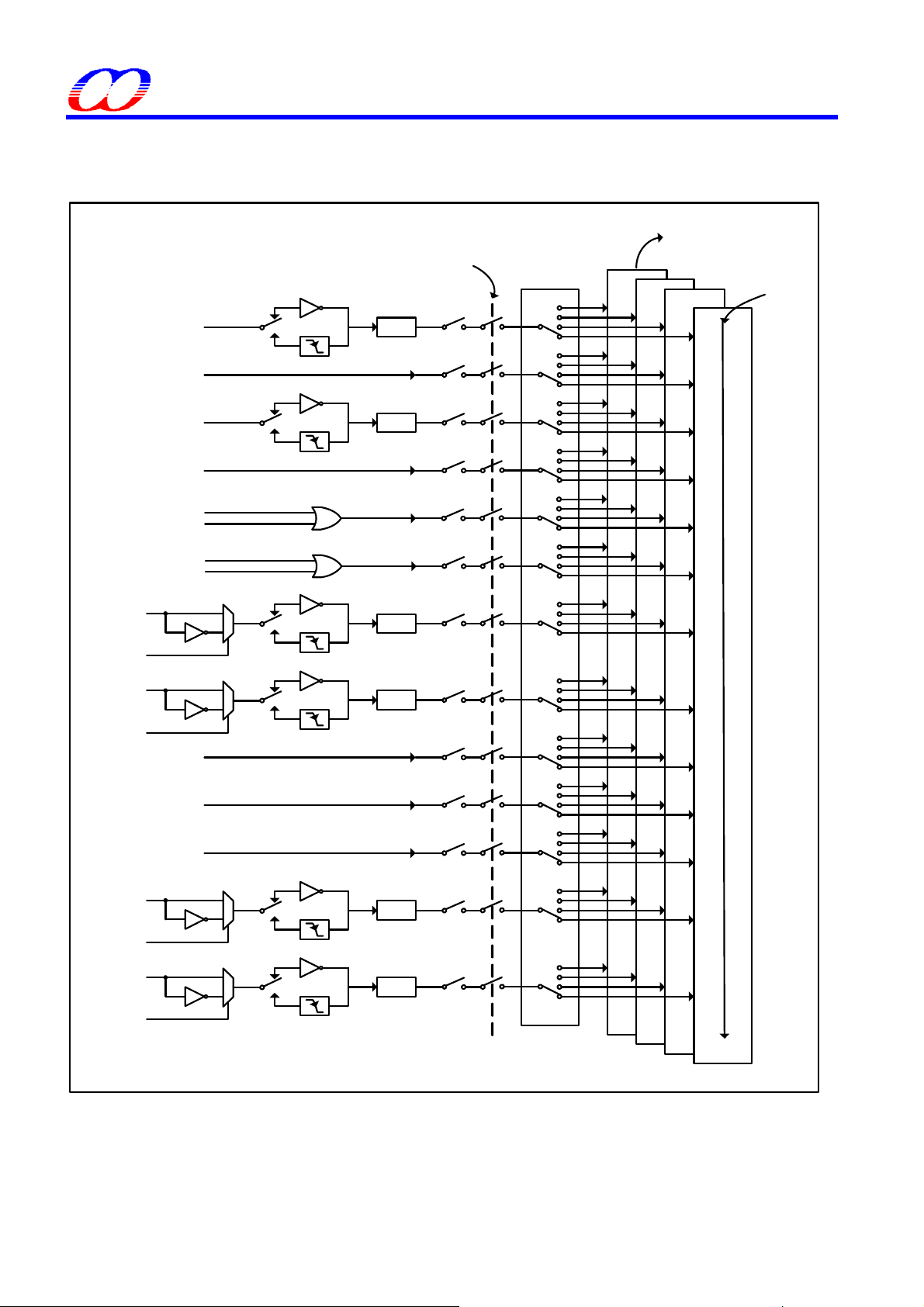

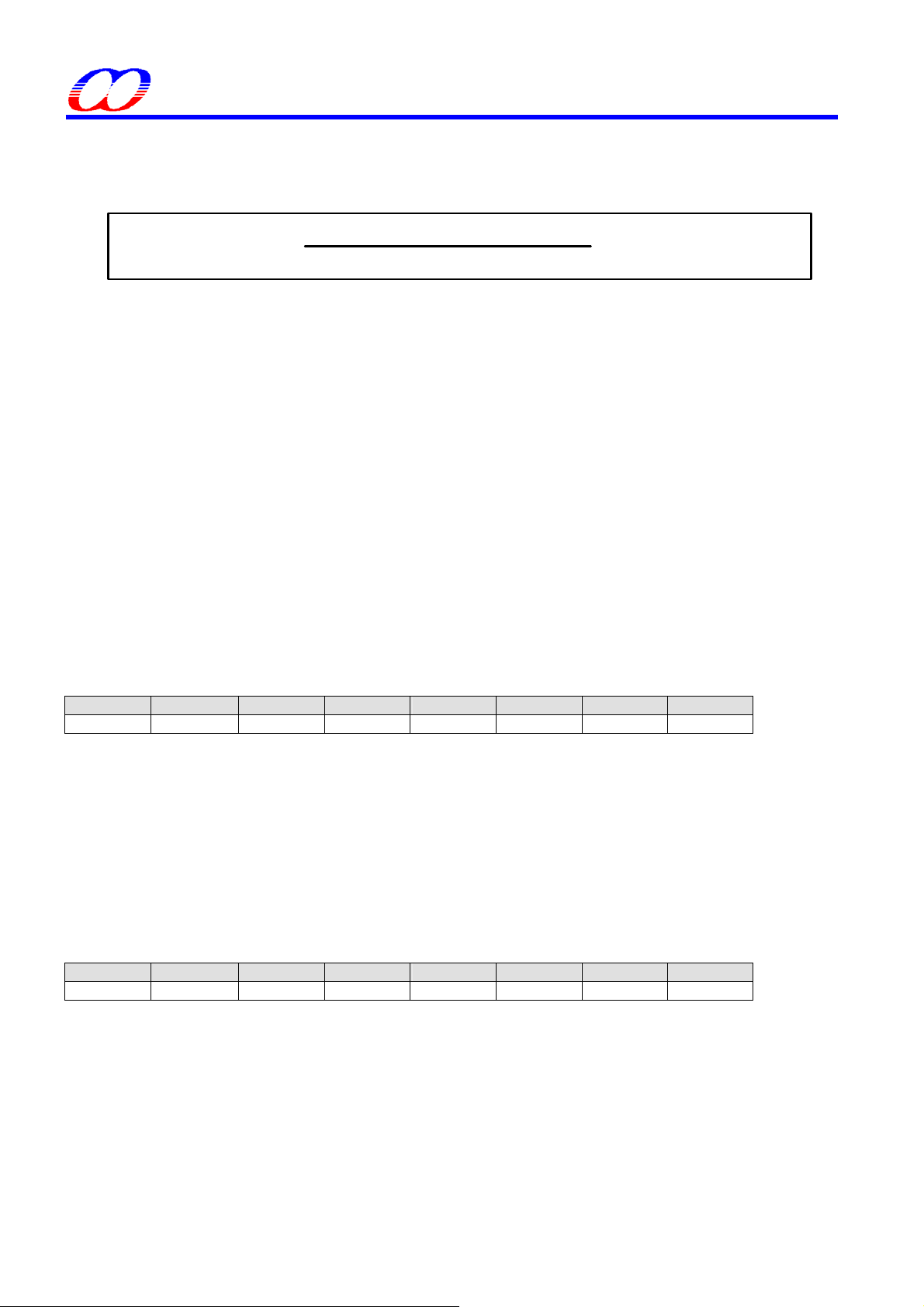

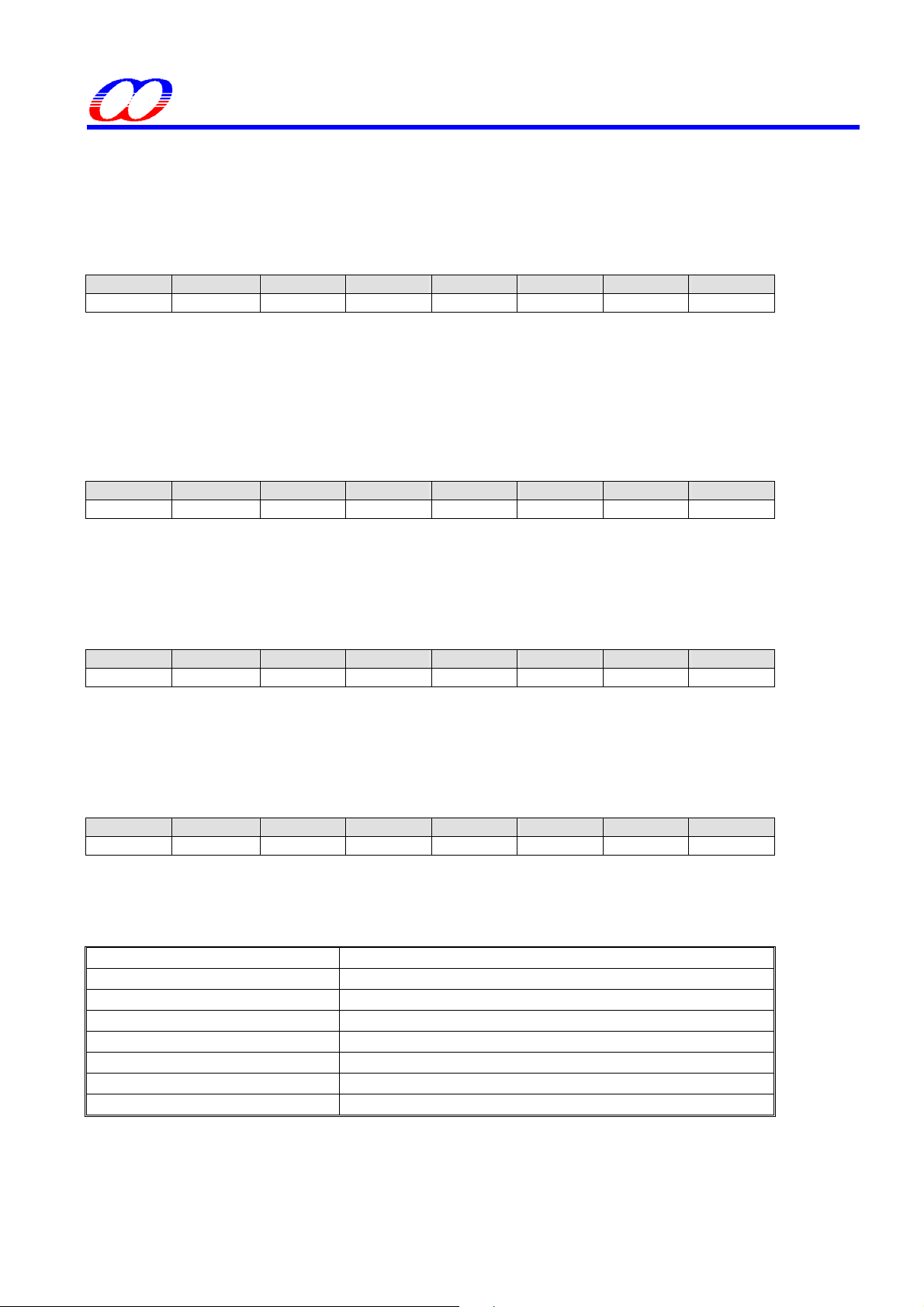

3. 方框图

CKO(P6.0)

nINT0(P3.2)

nINT1(P3.3)

nINT2(P4.3)

nINT3(P4.2)

nINT4(P5.0)

nINT5(P5.1)

RXD(P3.0/P1.6)

TXD(P3.1/P1.7)

T0/T0CKO(P3.4)

T1/T1CKO(P3.5)

T2/T2CKO(P1.0)

T2EX(P1.1)

PWM(P2/P5)

Internal

OSC

Flash

14.5K X 8

Ext. INT

UART

Timer0

Timer1

Timer2

PWM

Timer

8051 CPU (1T)

Ctrl

Block

RAM

256 X 8

XRAM

256 X 8

ISP

Port0

Port1

Port2

Port3

Port4

Port5

RST

P0.0~P0.7

P1.0~P1.7

P2.0~P2.7

P3.0~P3.7

P4.0~P4.6

P5.0~P5.7

AC_PI0(P1.4)

AC_PI1(P1.3)

AC_PI2(P1.2)

AC_PI3(P1.1)

AC_MI(P1.5)

0

1

2

3

0

1

Analog

Comparator

+

-

VDD

On-Chip

Voltage

Reference

Port6

Port7 P7.0~P7.7

WDT

BOD

4.0V

P6.0~P6.1

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 7/79

Page 8

Preliminary, v 0.06

MA816

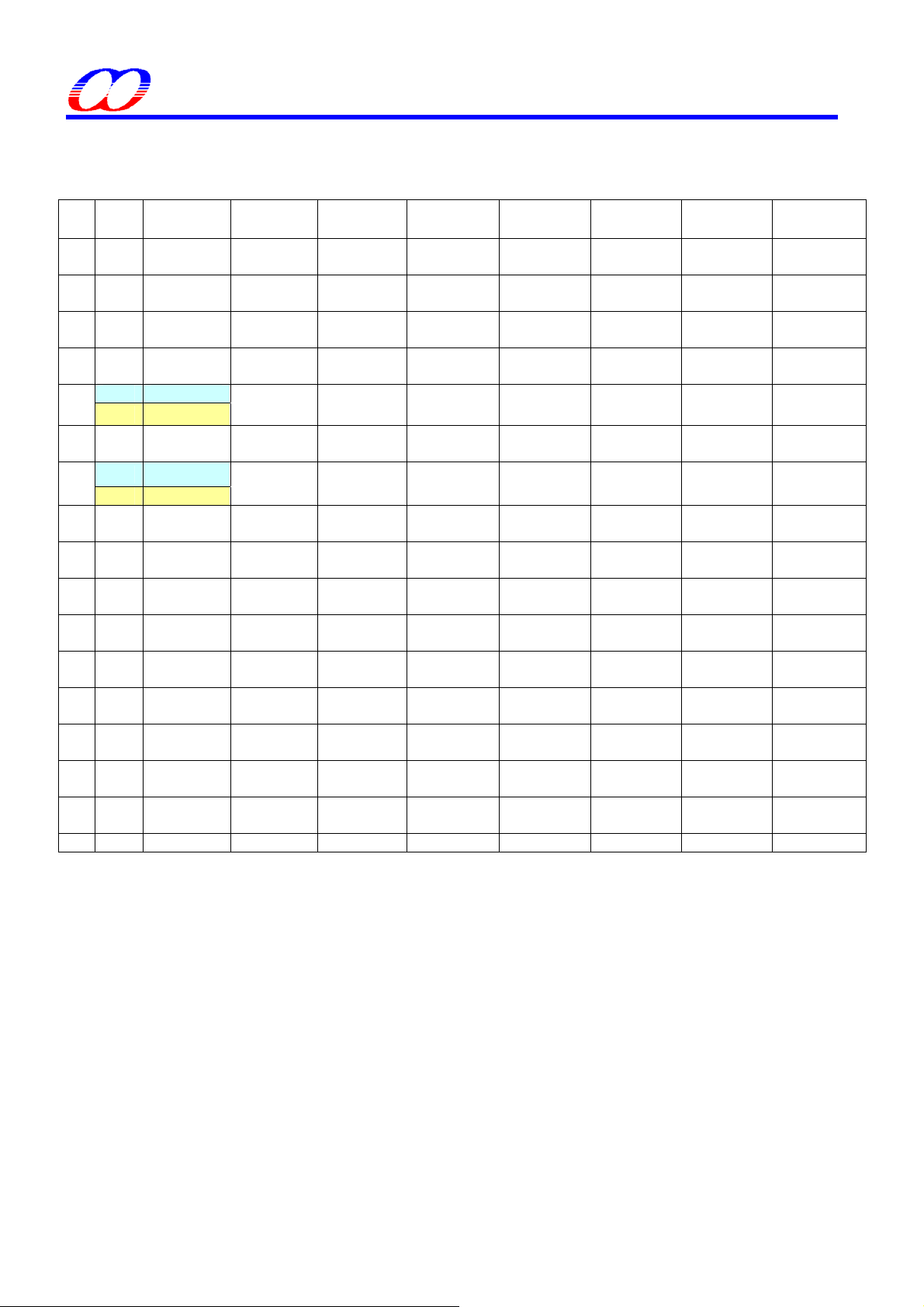

4. 特殊功能寄存器SFR

4.1. SFR 映射表

SFR

页

F8

F0

E8

E0

D8

D0

C8

C0

B8

B0

A8

A0

98

90

88

80

0

F

0

F

0

F

0

F

0 CCON

F P7

0

F

0 T2CON

F P6

0

F

0

F

0

F

0

F

0

F

0

F

0

F

0

F

0

F

0/8 1/9 2/A 3/B 4/C 5/D 6/E 7/F

P5 -- CCAP0H -- -- -- -- --

B -- -- -- -- -- -- --

P4 -- CCAP0L -- -- -- -- --

ACC WDTCR IFD IFADRH IFADRL IFMT SCMD ISPCR

CMOD -- -- -- -- -- --

PSW -- -- -- -- -- GPWKPE P1WKPE

T2MOD RCAP2L RCAP2H TL2 TH2 -- --

XIFLG XICON0 XICON1 -- -- -- -- CKCON0

IP0L SADEN -- -- -- -- -- CKCON1

P3 P3M0 P3M1 P4M0 P4M1 P5M0 P5M1 IP0H

IE SADDR -- -- SFRPI EIE1 EIP1L EIP1H

P2 -- AUXR1 AUXR2 -- -- -- --

SCON SBUF -- -- -- -- ACCON ACMOD

P1 P1M0 P1M1 P0M0 P0M1 P2M0 P2M1 PCON1

TCON TMOD TL0 TL1 TH0 TH1 AUXR0 STRETCH

P0 SP DPL DPH -- -- -- PCON0

0/8 1/9 2/A 3/B 4/C 5/D 6/E 7/F

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 8/79

Page 9

Preliminary, v 0.06

MA816

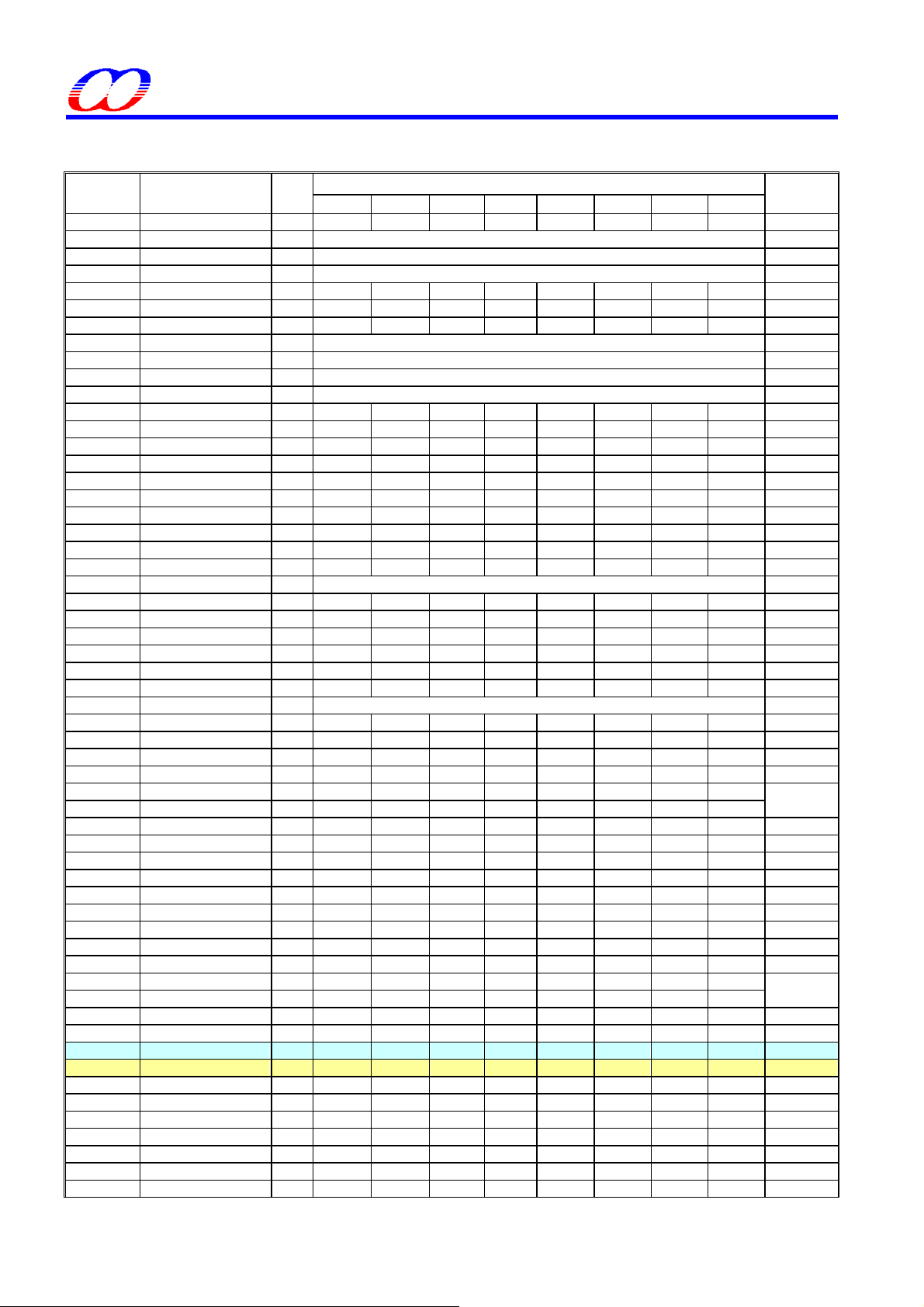

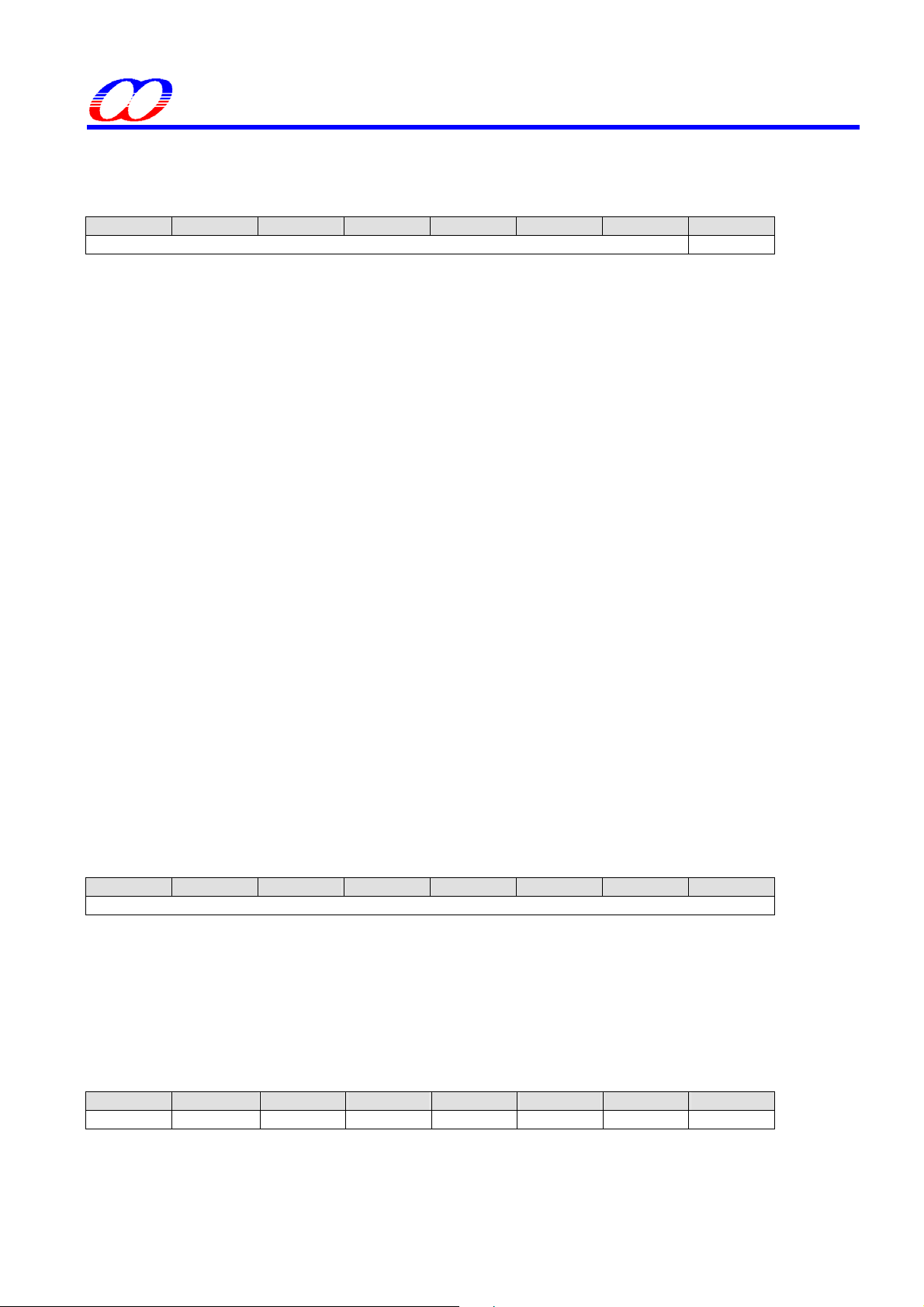

4.2. SFR 位分配

符号 描述 地址

P0

SP

DPL

DPH

PCON0

TCON

TMOD

TL0

TL1

TH0

TH1

AUXR0

P1

P1M0

P1M1

P0M0

P0M1

P2M0

P2M1

PCON1

SCON

SBUF

ACCON

ACMOD

P2

AUXR1

AUXR2

IE

SADDR

SFRPI

EIE1

EIP1L

EIP1H

P3

P3M0

P3M1

P4M0

P4M1

P5M0

P5M1

IP0H

IP0L

SADEN

CKCON1

XIFLG

XICON0

XICON1

CKCON0

T2CON

P6

T2MOD

RCAP2L

RCAP2H

TL2

TH2

PSW

GPWKPE

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 9/79

端口 0

堆栈指针

数据指针低

数据指针高

电源控制 0

定时器控制

定时器模式

定时器 0 低字节

定时器 1 低字节

定时器 0 高字节

定时器 1 高字节

辅助寄存器 0

端口 1

端口 1 模式寄存器 0

端口 1 模式寄存器 1

端口 0 模式寄存器 0

端口 0 模式寄存器 1

端口 2 模式寄存器 0

端口 2 模式寄存器 1

电源控制 1

串口控制

串口数据缓冲器

模拟比较器控制

模式比较器模式

端口 2

辅助寄存器 1

辅助寄存器 2

中断使能

从机地址

SFR 页索引

外部中断使能 1

外部中断优先级 1 低

外部中断优先级 1 高

端口 3

端口 3 模式寄存器 0

端口 3 模式寄存器 1

端口 4 模式寄存器 0

端口 4 模式寄存器 1

端口 5 模式寄存器 0

端口 5 模式寄存器 1

中断优先级 0 高

中断优先级 0 低

从机地址屏蔽

时钟控制 1

外部中断标志

外部中断控制 0

外部中断控制 1

时钟控制 0

定时器 2 控制

端口 6

定时器 2 模式

定时器 2 捕获 低

定时器 2 捕获 高

定时器 2 低字节

定时器 2 高字节

程序状态字

普通端口唤醒使能

80H P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1 P0.0 11111111B

81H

82H

83H

87H SMOD1 SMOD0 GF POF GF1 GF0 PD IDL

88H TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 00000000B

89H GATE C/T M1 M0 GATE C/T M1 M0

8AH

8BH

8CH

8DH

8EH P60OC1 P60OC0 P60FD P34FD -- -- EXTRAM -90H P1.7 P1.6 P1.5 P1.4 P1.3 P1.2 P1.1 P1.0

91H P1M0.7 P1M0.6 P1M0.5 P1M0.4 P1M0.3 P1M0.2 P1M0.1 P1M0.0

92H P1M1.7 P1M1.6 P1M1.5 P1M1.4 P1M1.3 P1M1.2 P1M1.1 P1M1.0

93H P0M0.7 P0M0.6 P0M0.5 P0M0.4 P0M0.3 P0M0.2 P0M0.1 P0M0.0

94H P0M1.7 P0M1.6 P0M1.5 P0M1.4 P0M1.3 P0M1.2 P0M1.1 P0M1.0

95H P2M0.7 P2M0.6 P2M0.5 P2M0.4 P2M0.3 P2M0.2 P2M0.1 P2M0.0

96H P2M1.7 P2M1.6 P2M1.5 P2M1.4 P2M1.3 P2M1.2 P2M1.1 P2M1.0

97H -- -- BORF -- -- -- -- BOD

98H SM0/FE SM1 SM2 REN TB8 RB8 Ti RI

99H

9EH ACIDX ACPDX ACOUT ACF ACEN ACM2 ACM1 ACM0

9FH MVRS3 MVRS2 MVRS1 MVRS0 -- -- PIS1 PIS0

A0H P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0

A2H GPWKS1 GPWKS0 P5PWM P1S0 GF2 -- -- DPS

A3H T0X12 T1X12 URM0X6 -- -- -- T1CKOE T0CKOE

A8H EA GF4 ET2 ES ET1 EX1 ET0 EX0

A9H

ACH -- -- -- -- IDX3 IDX2 IDX1 IDX0

ADH -- -- -- -- -- -- EACI EBOI

AEH -- -- -- PX5L PX4L PPTL PACL PBOL

AFH -- -- -- PX5H PX4H PPTH PACH PBOH

B0H P3.7 P3.6 P3.5 P3.4 P3.3 P3.2 P3.1 P3.0

B1H P3M0.7 P3M0.6 P3M0.5 P3M0.4 P3M0.3 P3M0.2 P3M0.1 P3M0.0

B2H P3M1.7 P3M1.6 P3M1.5 P3M1.4 P3M1.3 P3M1.2 P3M1.1 P3M1.0

B3H -- P4M0.6 P4M0.5 P4M0.4 P4M0.3 P4M0.2 P4M0.1 P4M0.0

B4H -- P4M1.6 P4M1.5 P4M1.4 P4M1.3 P4M1.2 P4M1.1 P4M1.0

B5H P5M0.7 P5M0.6 P5M0.5 P5M0.4 P5M0.3 P5M0.2 P5M0.1 P5M0.0

B6H P5M1.7 P5M1.6 P5M1.5 P5M1.4 P5M1.3 P5M1.2 P5M1.1 P5M1.0

B7H PX3H PX2H PT2H PSH PT1H PX1H PT0H PX0H

B8H PX3L PX2L PT2L PSL PT1L PX1L PT0L PX0L

B9H

BFH OSCDR -- -- XCKS4 XCKS3 XCKS2 XCKS1 XCKS0

C0H -- -- -- -- IE5 IE4 IE3 IE2

C1H -- INT3H IT3 EX3 -- INT2H IT2 EX2

C2H -- INT5H IT5 EX5 -- INT4H IT4 EX4

C7H -- -- -- -- -- SCKS2 SCKS1 SCKS0

C8H TF2 EXF2 RCLK TCLK EXEN2 TR2 C/T2 CP/RL

C8H -- -- -- -- -- -- P6.1 P6.0

C9H -- -- -- T2X12 -- -- T2OE DCEN

CAH

CBH

CCH

CDH

D0H CY AC F0 RS1 RS0 OV F1 P

D6H GP7WE GP6WE GP5WE GP4WE GP3WE GP2WE GP1WE GP0WE

Bit-7 Bit-6 Bit-5 Bit-4 Bit-3 Bit-2 Bit-1 Bit-0

位地址和符号

复位值

00000111B

00000000B

00000000B

00010000B

00000000B

00000000B

00000000B

00000000B

00000000B

0000xx0xB

11111111B

00000000B

00000000B

00000000B

00000000B

00000000B

00000000B

xxxxxxx0B

00000000B

xxxxxxxxB

00x00000B

0000xx00B

11111111B

00000xx0B

0000xx00B

00000000B

00000000B

xxxx0000B

xxxxxx00B

xxx00000B

xxx00000B

11111111B

00000000B

00000000B

x00000xxB

x0000000B

00000000B

00000000B

00000000B

00000000B

00000000B

xxx01010B

xxxx0000B

x000x000B

x000x000B

xxxxx000B

00000000B

xxxxxx11B

xxx0xx00B

00000000B

00000000B

00000000B

00000000B

00000000B

00000000B

Page 10

Preliminary, v 0.06

MA816

P1WKPE

CCON

P7

CMOD

ACC

WDTCR

IFD

IFADRH

IFADRL

IFMT

IAPLB

SCMD

ISPCR

P4

CCAP0L

B

P5

CCAP0H

端口 1 唤醒使能

计数器控制寄存器.

端口 7

计数器模式寄存器

累加器

看门狗定时器控制寄存

器

ISP Flash 数据

ISP Flash 地址 高

ISP Flash 地址 低

ISP 模式选择

IAP 低边界 注 1

ISP 指令

ISP 控制寄存器

端口 4

PWM 占空比 低

B 寄存器

端口 5

PWM 占空比 高

D7H P17WE P16WE P15WE P14WE P13WE P12WE P11WE P10WE

D8H CF CR - - PWMEN - - -

D8H P7.7 P7.6 P7.5 P7.4 P7.3 P7.2 P7.1 P7.0

D9H CIDL POS2 POS1 POS0 CPS2 CPS1 CPS0 ECF 00000000B

E0H ACC.7 ACC.6 ACC.5 ACC.4 ACC.3 ACC.2 ACC.1 ACC.0 00000000B

E1H WRF -- ENW CLW WIDL PS2 PS1 PS0

E2H

E3H

E4H

E5H -- -- -- -- MS3 MS2 MS1 MS0

E6H

E7H ISPEN BS SRST CFAIL -- -- -- -E8H -- P4.6 P4.5 P4.4 P4.3 P4.2 P4.1 P4.0

EAH

F0H F7H F6H F5H F4H F3H F2H F1H F0H

F8H P5.7 P5.6 P5.5 P5.4 P5.3 P5.2 P5.1 P5.0

FAH

IAPLB6 IAPLB5 IAPLB4 IAPLB3 IAPLB2 IAPLB1 IAPLB0 --

00000000B

00xx0xxxB

11111111B

0x000000B

11111111B

00000000B

00000000B

xxxx0000B

00110110B

xxxxxxxxB

0000xxxxB

11111111B

00000000B

00000000B

11111111B

00000000B

注 1: 这个寄存器地址通过 IFMT 和 SCMD 来决定。详情请见 IFMT 寄存器描述。

4.3. SFR 内存分页

MA816 SFR 内存分页允许设备在 0x80 至 0xFF 存储器地址区域映射更多的 SFR 。SFR 存储器区域有 16 页。因

此,从 0x80 至 0xFF 的每一页存储器能存取最大到 128 个 SFR。 MA816 利用两个 SFR 页:0 和 F。利用 SFR 页

索引寄存器(SFRPI)去选择 SFR 页。读写 SFR 的流程如下:

1. 利用 SFRPI 寄存器选择 SFR 页号。

2. 用直接寻址方式读或写特殊功能寄存器 SFR((MOV 指令)。

SFRPI: SFR

SFR 地址 = 0xAC

SFR 页 = 全部 复位值 = XXXX-0000

7 6 5 4 3 2 1 0

-- -- -- -- PIDX3 PIDX2 PIDX1 PIDX0

R R R R R/W R/W R/W R/W

Bit 7~4: 保留给测试。这些位必须写 “0” 。

Bit 3~0: SFR 页索引。可用到的页只有页 “0” 和 “F”。

有两个寄存只在页 0中:T2CON(C8H) 和 CCON(D8H),及两个寄存只在页 F 中:P6(C8H) 和 P7(D8H)。其它的

寄存能在页 0 和页 F 两个页中存取。

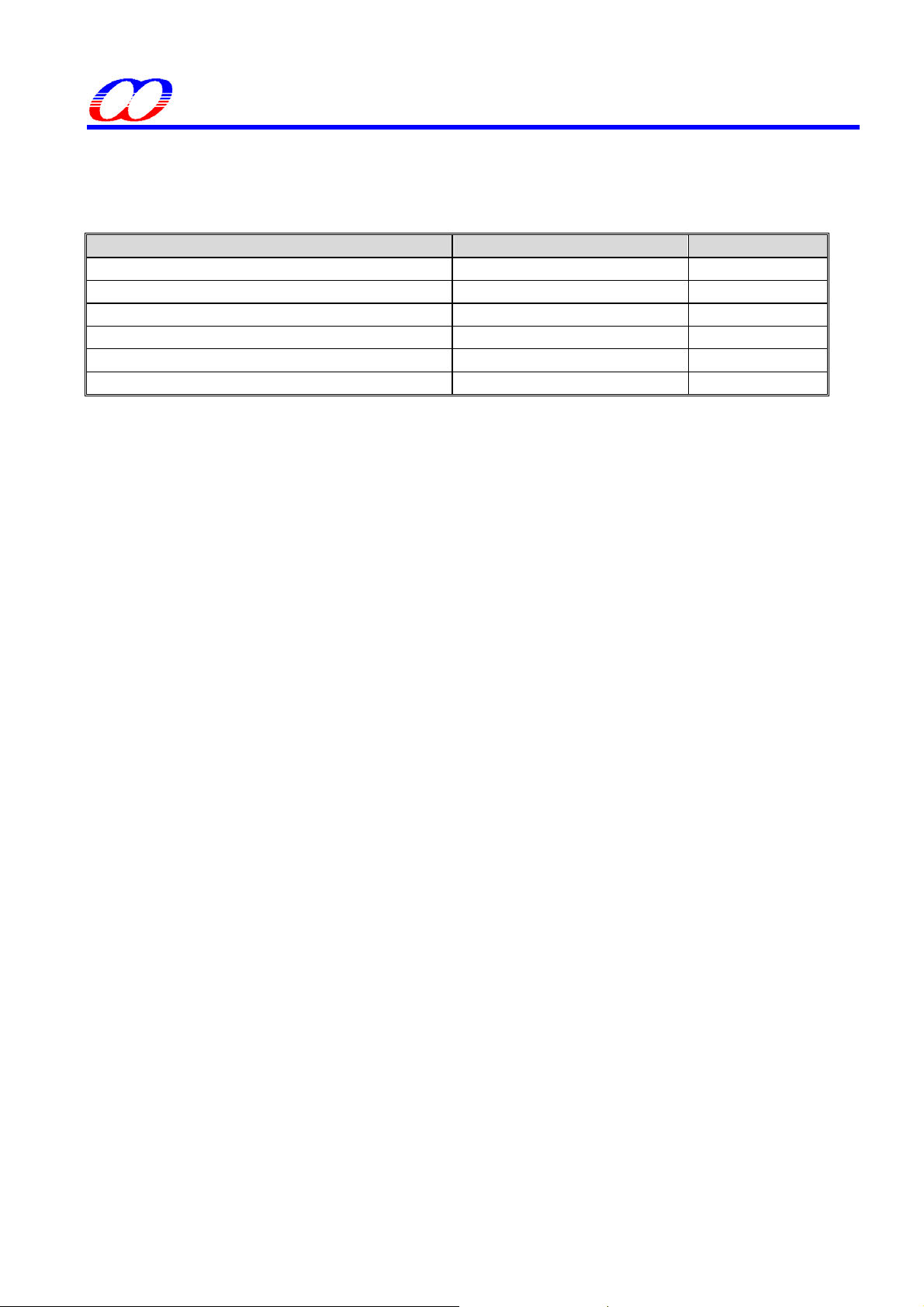

页索引寄存器

PIDX[3:0]

0000

0001

0010

0011

选择的页

页 0

页 1

页 2

页 3

…… ……

…… ……

…… ……

1111

页 F

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 10/79

Page 11

Preliminary, v 0.06

MA816

5. 引脚

5.1. 封装

MA816

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 11/79

Page 12

Preliminary, v 0.06

MA816

5.2. 引脚定义

助记符

P1.0 ~ P1.4 60~64 I/O

P1.5 ~ P1.7 2~4 I/O

P3.0 8 I/O

P3.1 ~ P3.3 12~14 I/O

P3.4 15 I/O

P3.5 16 I/O

P3.6 ~ P3.7 17,18 I/O

P0.7 ~ P0.0 44~47,

64-Pin

LQFP

49~52

类型

I/O

端口 1: 普通通用 I/O 口 1.

P1.0 可作 T2 或 T2CKO.

P1.1 可作 T2EX.

P1.1 ~ P1.4 可作可编程比较器正输入.默认输入口是 P1.4.

P1.5 可作比较器负输入

P1.6/P1.7 可通过固件配置为第二功能 RXD/TXD

端口 3: 普通通用 I/O 口 3.

P3.0 可作串口 RXD.

P3.1 可作串口 TXD.

P3.2 可作 nINT0.

P3.3 可作 nINT1.

P3.4 可作 T0 或 T0CKO.

P3.5 可作 T1 或 T1CKO.

端口 0: 普通通用 I/O 口 0.

描述

P2.0 ~ P2.7 28~35 I/O

P4.0 25 I/O

P4.1 42 I/O

P4.2 59 I/O

P4.3 11 I/O

P4.4 36 I/O

P4.5 39 I/O

P4.6 43 I/O

P5.0 ~ P5.1 19,37 I/O

P5.2 ~ P5.3 53,5 I/O

P5.4 ~ P5.5 20,38 I/O

P5.6 ~ P5.7 54,6 I/O

P7.0 ~ P7.1 26,27 I/O

P7.2 ~ P7.3 40,41 I/O

P7.4 ~ P7.5 57,58 I/O

P7.6 ~ P7.7 9,10 I/O

RST 7 I

P6.1 22 I/O

P6.0 I/O

端口 2: 普通通用 I/O 口 2.

可以做 PWM 定时器的 PWM 输出

端口 4: 普通通用 I/O 口 4.

P4.0 和 P41 能被配置仅输入在默认状态

P4.2 可作 nINT3.

P4.3 可作 nINT2.

端口 5: 普通通用 I/O 口 5.

可以做 PWM 定时器的 PWM 输出

P5.0 可作 nINT4.

P5.1 可作 nINT5.

端口 7: 普通通用 I/O 口 7.

RST: 最少两个机器周期的高电平复位微控制器

端口 6: 普通通用 I/O 口 6

P6.1

P6.0 和内部时钟输出.

VDD 55,56 P

VSS 23,24 G

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 12/79

电源

地

Page 13

Preliminary, v 0.06

MA816

6. 系统时钟

6.1. 时钟结构图

6.2. 时钟寄存器

CKCON0:

SFR 地址 = 0xC7

SFR 页 = 全部 复位值 = xxxx-x000

Bit 7~3: 保留.

Bit 2~0: SCKS2 ~ SCKS0, 可编程系统时钟选择

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 13/79

时钟控制寄存器

7 6 5 4 3 2 1 0

- - - - - SCKS2 SCKS1 SCKS0

R R R R R R/W R/W R/W

SCKS[2:0]

0 0 0 CLKin

0 0 1 CLKin /2

0 1 0 CLKin /4

0 1 1 CLKin /8

1 0 0 CLKin /16

1 0 1 CLKin /32

1 1 0 CLKin /64

1 1 1 CLKin /128

0

系统时钟 (Fosc)

Page 14

Preliminary, v 0.06

MA816

CKCON1:

时钟控制寄存器

1

SFR 地址 = 0xBF

SFR 页 = 全部 复位值= xxx0-1010

7 6 5 4 3 2 1 0

OSCDR -- -- XCKS4 XCKS3 XCKS2 XCKS1 XCKS0

R/W R R R/W R/W R/W R/W R/W

Bit 7: OSCDR, OSC 驱动控制寄存器。

0: 足够驱动能力,驱动晶体振荡器。

1: 减少晶体振荡器的驱动能力。可以帮助减少 EMI。

Bit 6~5: 保留.

Bit 4~0: 设置振荡频率值去定义 ISP/IAP 操作的基本时间。根据 OSCin 填充一个适当的值,如下表:

时。

[XCKS4~XCKS0] = OSCin – 1, 当 OSCin=1~25 (MHz)

例如:

(1) 如果 OSCin=12MHz,则填充 [XCKS4~XCKS0]为 11,即:001011B.

(2) 如果 OSCin=6MHz,则填充 [XCKS4~XCKS0]为 5,即:000101B.

OSCin XCKS[4:0]

1MHz 5’b00000

2MHz 5’b00001

3MHz 5’b00010

4MHz 5’b00011

…… ……

22MHz 5’b10101

23MHz 5’b10110

24MHz 5’b10111

25MHz 5’b11000

默认值 XCKS= 5’b01010

AUXR0:

辅助寄存器

0

SFR 地址 = 0x8E

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

P60OC1 P60OC0 P60FD P34FD -- -- -- --

R/W R/W R/W R/W R/W R/W R/W R/W

Bit 7~6: P60 输出配置控制位 1 和 0。P60 支持下面的选择为 GPIO 或时钟源发生器。当 P60OC[1:0] 索引为非 P60

功能时,XTAL2 将驱动片上 RC 振荡器输出为其它设备提供时钟源。

P60OC[1:0]

00 P60

01 INTOSC

10 INTOSC/2

11 INTOSC/4

XTAL2 功能 I/O 模式

准双向口

推挽输出

推挽输出

推挽输出

Bit 5: P60FD, P6.0 快速驱动

0: P6.0 默认驱动输出

1: P6.0 快速驱动输出使能。如果 P6.0 被配置作时钟输出。

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 14/79

Page 15

Preliminary, v 0.06

MA816

7. 8051 CPU 功能描述

7.1. CPU 寄存器

PSW:

程序状态字

SFR 地址 = 0xD0

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

CY AC F0 RS1 RS0 OV F1 P

R/W R/W R/W R/W R/W R/W R/W R/W

CY:进位标志。有进位/借位时 CY=1,否则 CY=0。

AC:半进位标志。当 D3 位向 D4 位产生进位/借位时 AC=1,否则 AC=0,常用于十进制调整运算中。

F0:用户可设定的标志位 0,可置位/复位,也可供测试。

RS1、RS0:四个通用寄存器组的选择位,该两位的四种组合状态用来选择 0~3 寄存器组。见下表:

OV:溢出标志。当带符号数运算结果超出 -128~+127 范围时 OV=1,否则 OV=0。当无符号数乘法结果超过 255 时,

或当无符号数除法的除数为 0 时,OV=1,否则 OV=0。

F1:用户可设定的标志 1,可置位/复位,也可供测试。

P:奇偶校验标志。每条指令执行完,若 A 中 1 的个数为奇数时 P=1,否则 P=0,即奇偶校验方式。

堆栈指针

SP:

SFR 地址 = 0x81

SFR 页 = 全部 复位值 = 0000-0111

7 6 5 4 3 2 1 0

SP[7] SP[6] SP[5] SP[4] SP[3] SP[2] SP[1] SP[0]

R/W R/W R/W R/W R/W R/W R/W R/W

数据指针低字节

DPL:

SFR 地址 = 0x82

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

DPL[7] DPL[6] DPL[5] DPL[4] DPL[3] DPL[2] DPL[1] DPL[0]

R/W R/W R/W R/W R/W R/W R/W R/W

数据指针高字节

DPH:

SFR 地址 = 0x83

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

DPH[7] DPH[6] DPH[5] DPH[4] DPH[3] DPH[2] DPH[1] DPH[0]

R/W R/W R/W R/W R/W R/W R/W R/W

寄存器

B: B

SFR 地址 = 0xF0

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

B[7] B[6] B[5] B[4] B[3] B[2] B[1] B[0]

R/W R/W R/W R/W R/W R/W R/W R/W

RS1 RS0

0 0

0 1

1 0

1 1

工作寄存器组

0 组(00-07H)

1 组(08-0FH)

2 组(10-17H)

3 组(18-1FH)

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 15/79

Page 16

Preliminary, v 0.06

MA816

7.2. CPU 时序

MA816 是一个基于1-T结构80C51 CPU的单芯片维处理器,指令完全兼容8051,执行一条指令只要 1~7时钟周期(是

标准8051的 6~7倍)。它通过管道结构加快了指令执行速度超过标准8051结构。指令时序不同于标准8051。

多数8051执行指令的差别是基于机器周期和时钟周期的,机器周期为2到12个时钟周期。然而,1T-80C51是基于时钟

周期时序的。 所有指令时序被指定为时钟周期期间。关于1T-80C51指令的更多详情(包括每条指令的助记符、字节

数、时钟周期)请参考“指令集”。

7.3. CPU 寻址方式

直接寻址

在指令中直接给出操作数地址的就属于直接寻址。此时,指令中的操作数部分就是操作数的地址。例如指令:

MOV A,4FH ;(A)←(4FH)

可用于直接寻址的空间是,内部数据RAM的低128字节及特殊功能寄存器SFRs。

寄存器间接寻址

由指令中指出某一个寄存器的内容作为操作数的地址。内部RAM和外部RAM都能通过间接寻址方式进行访问。使用当

前工作寄存器组中的R0或R1存放操作数单元的地址指针(8位地址),在执行PUSH(压栈)和POP(出栈)指令时

采用堆栈指针SP作寄存间接寻址。而如果地址是16位时就只能使用DPTR数据指针作间接寻址了。例如指令:

MOV A,@R0 ;(A) ←((R0))

MOVX A,@R1 ;(A) ←((R1))

MOVX A,@DPTR ;(A) ←((DPTR))

寄存器寻址

寄存器寻址就是以通过寄存器的内容作为操作数。在指令的助记符号中直接以寄存器的名字来表示操作数的地址。例

如指令:

MOV A,R0 ;(A) ←(R0)

ADD A,R0 ;(A) ←(Acc)+(R0)

能用于这种寻址方式的寄存器还有ACC、B、DPTR、AB(双字节)和CY(位累加器)。

变址寻址

以某个寄存器的内容作为基本地址,然后在这个基本地址基础上加上地址偏移量才是真正的操作数地址。例如指令:

MOVC A,@A+DPTR ;(A) ←((A)+(DPTR))

不论用DPTR或是PC作为基址指针,变址寻址方式都只适用于8051的程序存储器,通常用于读取数据表。

立即寻址

指令中地址码部分给出的就是操作数。即取出指令的同时立即得到了操作数。例如指令:

MOV A,#4FH ;(A) ←6FH

相对寻址

相对寻址时,由程序计数器PC提供的基地址与指令中提供的偏移量rel相加,得到操作数的地址。这时指出的地址是操

作数与现行指令的相对位置。例如指令:

SJMP rel ;PC←(PC)+2+rel

位寻址

操作数是二进制数的某一位,其位地址出现在指令中,例如指令:

(REG)

SETB bit ;(bit) ←1

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 16/79

Page 17

Preliminary, v 0.06

MA816

8. 存储器结构

像所有的 80C51一样, MA816 的程序存储器和数据存储器的地址空间是分开的,这样8位微处理器可以通过一个8

位的地址快速而有效的访问数据存储器。

程序存储器(AP)最大13.5K字节。在MA816中,所有的程序存储器都是片上Flash存储器。因为没有设计外部程序使能

(/EA)和编程使能 (/PSEN) 信号,所以不允许外接程序存储器。

数据存储器使用与程序存储器不同的地址空间。MA816 有256字节的内部RAM和256字节片上扩展存储器 (XRAM)。

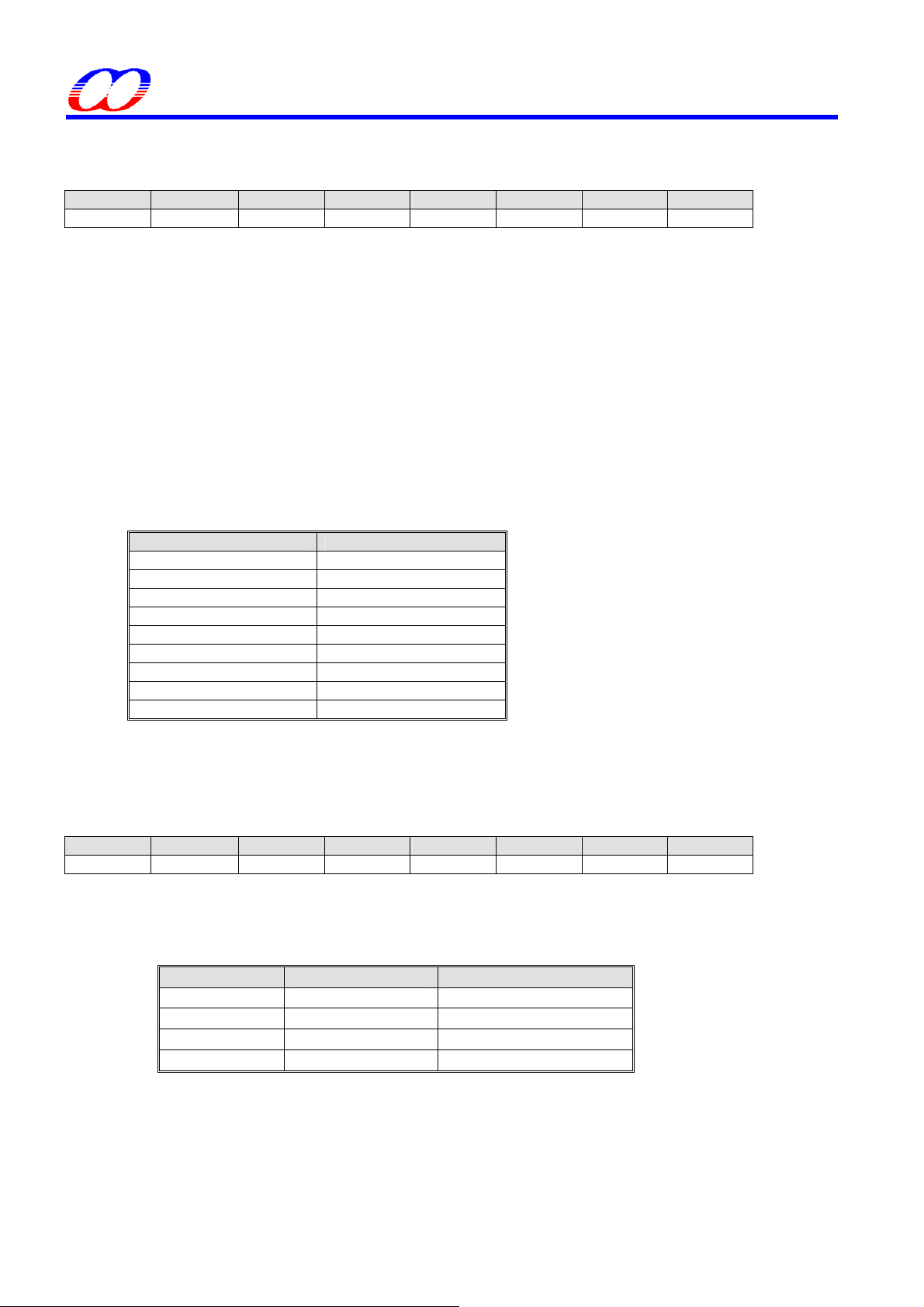

8.1. 片上程序存储器

程序存储器用来保存让CPU进行处理的程序代码,如图 8-1所示。复位后,CPU从地址为0000H的地方开始运行,用

户应用代码的起始部分应该放在这里。为了响应中断,中断服务位置(被称为中断矢量)应该位于程序存储器。每个中断

在程序存储器中有一个固定的起始地址,中断使CPU跳到这个地址运行中断服务程序。举例来说, 外部中断0被指定

到地址0003H,如果使用外部中断0,那么它的中断服务程序一定是从0003H开始的。如果中断未被使用,那么这些地

址就可以被一般的程序使用。

中断服务程序的起始地址之间有8字节的地址间隔:外部中断0,0003H;定时器0,000BH;外部中断1,0013H;定

时器1,001BH等等。如果中断服务程序足够短,它完全可以放在这8字节的空间中。如果其他的中断也被使用的话,

较长的中断服务程序可以通过一条跳转指令越过后面的中断服务起始地址。

图 8-1 程序存储器

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 17/79

Page 18

Preliminary, v 0.06

MA816

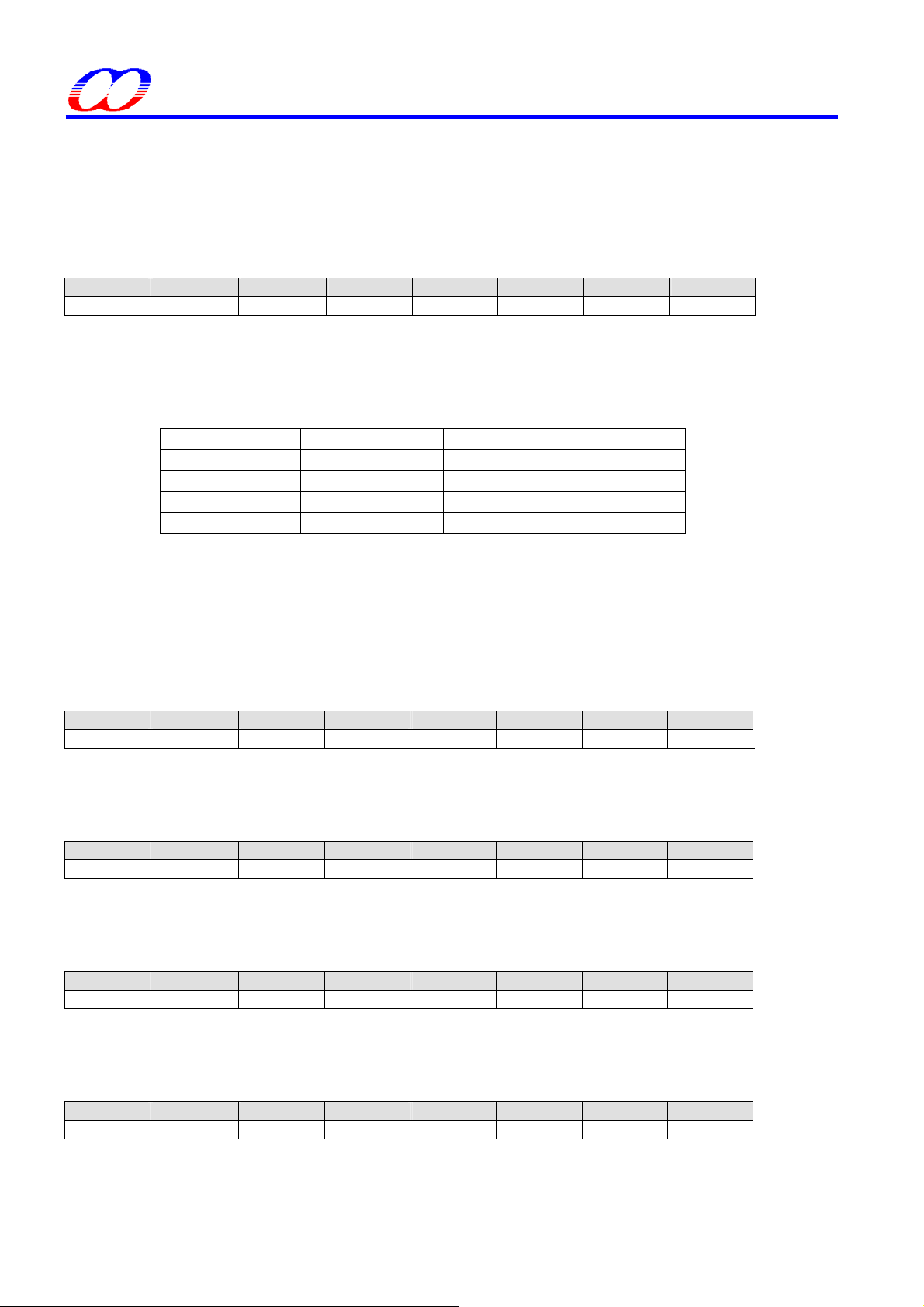

8.2. 片上数据存储器 RAM

图 8-2 向MA816使用者展示了内部和外部数据存储器的空间划分。内部数据存储器被划分为三部分,通常被称为低128

字节 RAM ,高128字节 RAM 和128字节 SFR 空间。内部数据存储器的地址线只有8位宽,因此地址空间只有256

字节。SFR 空间的地址高于7FH,用直接地址访问;而用间接访问的方法访问高128字节的RAM。这样虽然SFR和高

128字节RAM占用相同的地址空间,但他们实际上是分开的。

图 8-2 所示,低128字节RAM与所有80C51 一样。最低的32字节被划分为4组每组8字节的寄存器组。指令中称这些

寄存器为R0到R7。程序状态字 (PSW) 中的两位用于选择哪组寄存器被使用。这使得程序空间能够被更有效的使用,

因为对寄存器访问的指令比使用直接地址的指令短。 接下来的16字节是可以位寻址的存储器空间。80C51的指令集包

含一个位操作指令集,这区域中的128位可以被这些指令直接使用。位地址从00H开始到7FH结束。

所有的低128字节RAM都可以用直接或间接地址访问,而高128字节RAM只能用间接地址访问。

SFR包括端口寄存器,定时器和外围器件控制器,这些寄存器只能用直接地址访问。SFR 空间中有16个地址同时支持

位寻址和直接寻址。可以位寻址的 SFR 的地址末位是0H 或8H。

存取片上扩展 RAM (XRAM),256 字节的 XRAM (0000H ~ 00FFH) 通过指令 MOVX 间接寻址。存取 XRAM 没有任

何关于地址,地址锁存器和读/写选通信号的输出。

图 8-2 低 128 字节内部 RAM

Lower 128 Bytes of

internal SRAM

7FH

Four banks of 8

registers R0~R7

30H

20H

18H

10H

08H

00H

Bit Addressable

Bank 3

Bank 2

Bank 1

Bank 0

2FH

1FH

17H

0FH

07H

Reset value of

Stack Pointer

8.3. 片上扩展RAM (XRAM)

存取片上 RAM (XRAM), 256 字节的 XRAM (0000H ~ 00FFH) 通过指令“MOVX @Ri” 和 “MOVX @DPTR”间接寻

址。KEIL-C51 编译器中,分配变量定位 XRAM,应使用 “pdata” 或 “xdata” 去定义。编译后,这变量被分别编译为

通过“MOVX @Ri” 和 “MOVX @DPTR”寻址。从而 MA816 硬体能正确存取它们。

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 18/79

Page 19

Preliminary, v 0.06

MA816

8.4. 关于C51 编译器的声明识别符

C51编译器的声明识别符与 MA816 存储空间的对应关系。

data

128字节的内部数据存储空间 (00h~7Fh);使用除MOVX和MOVC以外的指令,可以直接或间接的访问。 全部或部分

的堆栈可能保存在此区域中。

idata

间接数据;256字节的内部数据存储空间 (00h~FFh) 使用除MOVX和 MOVC以外的指令间接访问。全部或部分的堆

栈可能保存在此区域中。此区域包括 data区 和data区以上的128字节。

sfr

特殊功能寄存器; CPU寄存器和外围部件控制/状态寄存器,只能通过直接地址访问。

xdata

外部数据或片上的扩展RAM (XRAM);通过 “MOVX @DPTR” 指令访问标准80C51的64K存储空间。MA816有 256 字

节的片上 xdata 存储空间。

pdata

分页的外部数据(256 字节) 或片上的扩展RAM;通过 “MOVX @Ri” 指令访问标准80C51的256字节存储空间。MA816

有片上256 字节 pdata 存储空间,它与xdata共享。

code

16K程序存储空间;通过“MOVC @A+DTPR”访问,作为程序的一部分被读取。MA816有16K字节的片上 code存储器.

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 19/79

Page 20

Preliminary, v 0.06

MA816

9. 双数据指针寄存器 (DPTR)

通过数据指针用来加速代码执行和减少代码尺寸,双DPTR结构是一种方法。芯片将指定外部数据存储器的定位地址。

外部存储器有两个16位DPTR寄存器,和一个控制位称作为DPS(AUXR1.0),允许在程序代码和外部存储器之间的切换。

图 9-1 双 DPTR

(83h) (82h)

DPH DPLDPTR0

AUXR1.DPS=0

DPH DPLDPTR1

AUXR1.DPS=1

External Data Memory

DPTR 指令

使用DPS位的六条指令参考DPTR的当前选择,如下:

INC DPTR ;数据指针加1

MOV DPTR,#data16 ;DPTR加载16位常量

MOVC A,@A+DPTR ;将代码字节移动到ACC

MOVX A,@DPTR ; 移动外部RAM(16位地址)到ACC

MOVX @DPTR,A ;移动ACC到外部RAM(16位地址)

JMP @A+DPTR ;直接跳转到DPTR

AUXR1:

辅助控制积存器

1

SFR 地址 = 0xA2

SFR 页 = 全部 复位值 = 0000-0xx0

7 6 5 4 3 2 1 0

GPWKS1 GPWKS0 P5PWM P1S0 GF2 GF GF DPS

R/W R/W R/W R/W R/W R/W R/W R/W

Bit 0: DPTR 选择位,用来在 DPTR0 和 DPTR1 之间切换。

0: 选择 DPTR0

1: 选择 DPTR1

DPS

选择 DPTR

0 DPTR0

1 DPTR1

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 20/79

Page 21

Preliminary, v 0.06

MA816

10. I/O 结构

MA816 有下列 I/O 端口:P0.0~P0.7, P1.0~P1.7, P2.0~P2.7, P3.0~P3.7, P4.0~P4.6, P5.0~P5.7, P6.0~P6.1 及

P7.0~P7.7。如果选择内部振荡器作系统时钟输入,XTAL2 和 XTAL1 被配置为 P6.0 和 P6.1。 确切的 I/O 口数目根

据封装而不同,见下表:

表 10-1 可用到的 I/O 口数目

I/O Pins Number of I/O ports

P0.0~P0.7, P1.0~P1.7, P2.0~P2.7, P3.0~P3.7,

P4.0~P4.6, P5.0~P5.7, P7.0~P7.7,

XTAL2(P6.0), XTAL1(P6.1)

10.1. IO 配置

除 P6.0~P6.1 和 P7.0~P7.7 外,所有 I/O 端口引脚可以配置为四种模式中的其中一种。这四种类型有:准双向口(标

准 8051 的 I/O 端口)、上拉输出、集电极开路输出和输入(高阻抗输入)。P6.0 和 P6.1 只能作准双向口模式

下面描述这四种 I/O 口模式。

10.1.1. 准双向口

端口引脚工作在准双向模式时与标准 8051 端口引脚类似。一个准双向端口用作输入和输出时不需要对端口重新

配置。这种可能是因为端口输出逻辑高时,弱上拉,允许外部器件拉低引脚。当输出低时,强的驱动能力可吸收大电

流。在准双向输出时有三个上拉晶体管用于不同的目的。

其中的一种上拉,称为微上拉,只要端口寄存器的引脚包含逻辑 1 则打开。如果引脚悬空,则这种非常弱上拉提

供一个非常小的电流将引脚拉高。第二种上拉称为“弱上拉”,端口寄存器的引脚包含逻辑 1 时且引脚自身也在逻辑电平

时打开。这种上拉对准双向引脚提供主要的电流源输出为 1。如果引脚被外部器件拉低,这个弱上拉关闭,只剩一个

微上拉。为了在这种条件下将引脚拉低,外部器件不得不吸收超过弱上拉功率的电流,且拉低引脚在输入的极限电压

之下。第三种上拉称为“强”上拉。这种上拉用于加速准双向端口的上升沿跳变,当端口寄存器从逻辑 0 到逻辑 1 时。当

这发生时,强上拉打开两个 CPU 时钟,快速将端口引脚拉高。

准双向端口配置如下图所示。

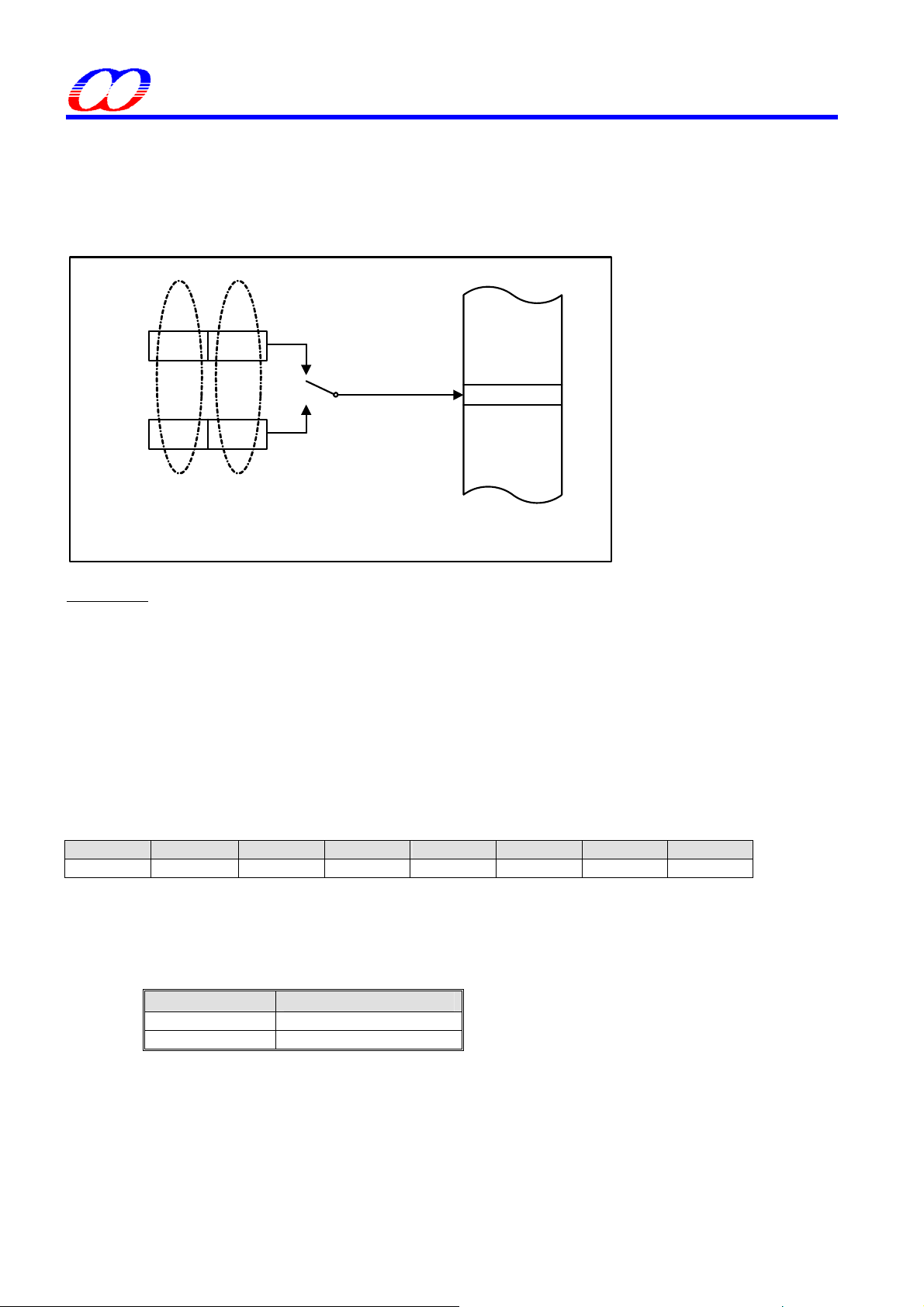

图 10-1 准双向 I/O 口

55 or

57 (INTOSC enabled)

VDD

Weak

Port

Pin

Port latch data

Input data

2 clocks

delay

Strong

VDDVDD

Very

weak

10.1.2. 推挽输出

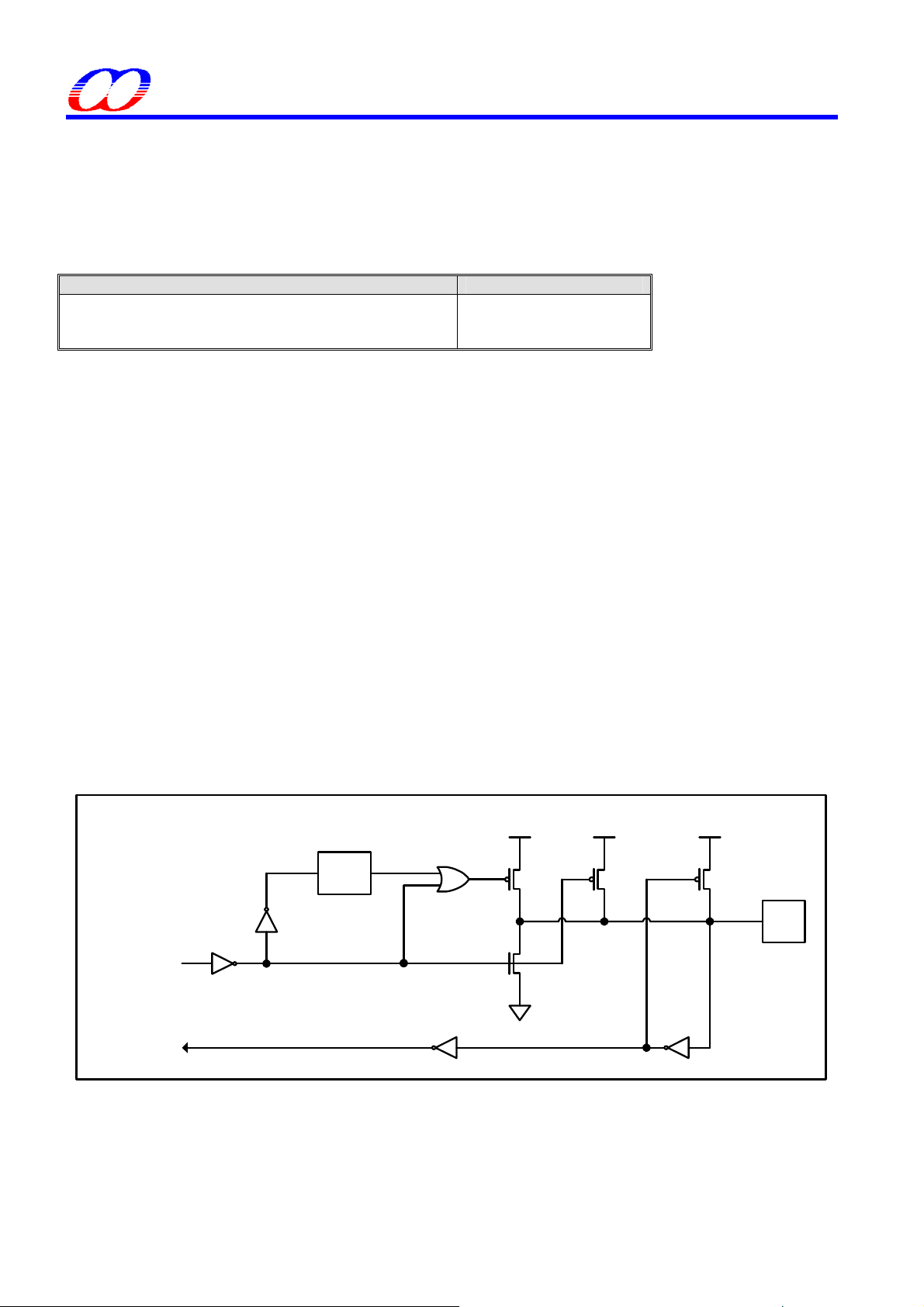

推挽输出配置有下拉,和开漏输出、准双向输出模式有着相同的结构,当端口寄存器包含逻辑 1 时提供一个连续

的强上拉。当一个端口输出需要更大的电流时可配置为推挽输出模式。另外,在这种配置下的端口输入引脚和输入路

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 21/79

Page 22

Preliminary, v 0.06

MA816

径的准双向模式的配置相同。

推挽输出配置如下图所示。

图 10-2 推挽输出

VDD

Strong

Port

Pin

Port latch data

Input data

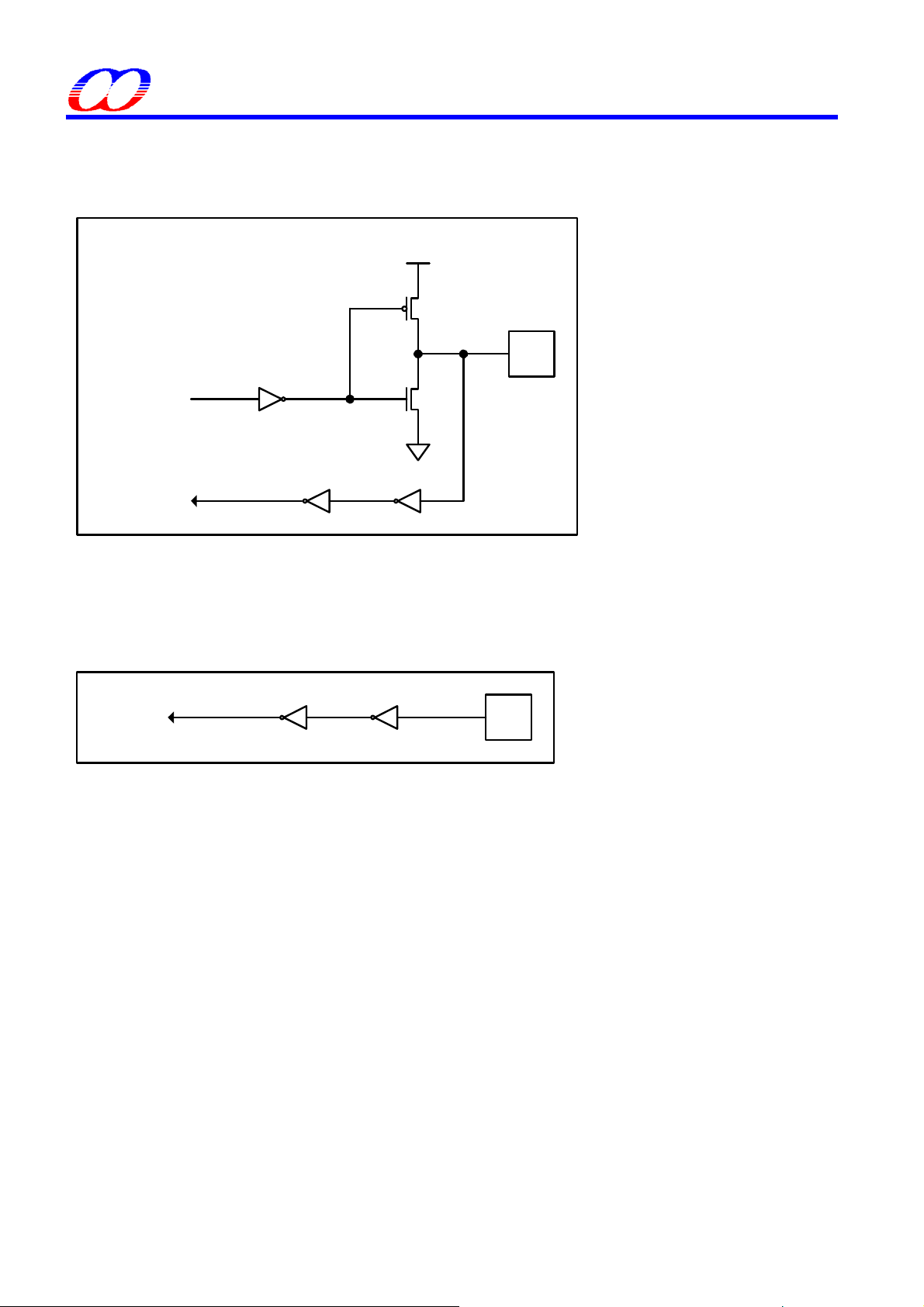

10.1.3. 仅输入(高阻输入)

仅输入模式在引脚上没有任何上拉电阻,如下图所示。

图 10-3 仅输入

Input data

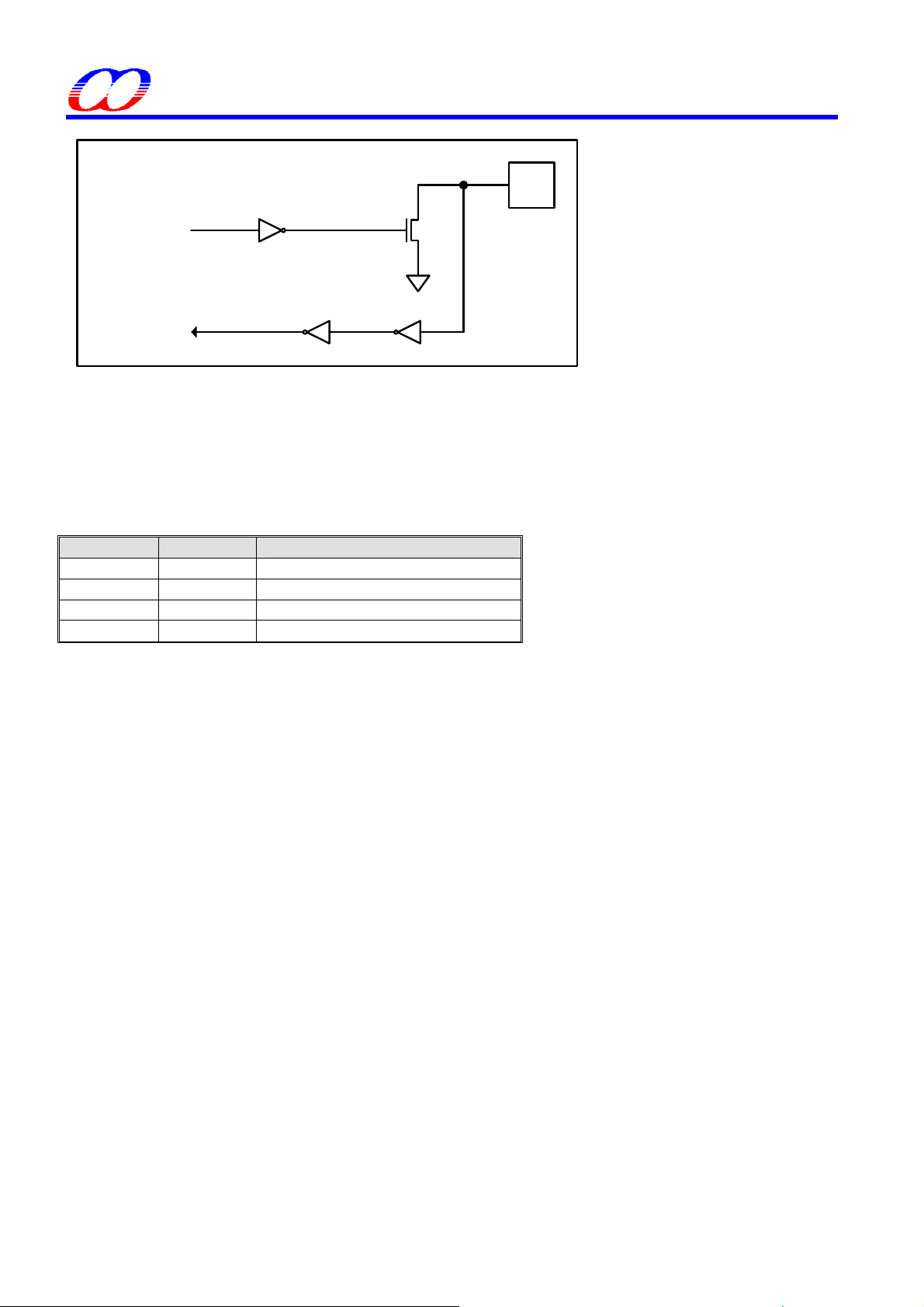

10.1.4. 开漏集输出

配置为开漏输出时,当端口寄存器包含逻辑 0 时,关闭所有上拉,只有端口引脚的下拉晶体管。使用这个功能配

置应用,端口引脚必须有外部上拉,典型的将电阻接到 VDD。这个模式的下拉和准双向端口的模式相同。另外,在这

种配置下的端口输入引脚的输入路径和准双向模式相同。

开漏输出端口配置如图 10-2 所示。

图 10-4 开漏集输出

Port

Pin

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 22/79

Page 23

Preliminary, v 0.06

MA816

Port

Pin

Port latch data

Input data

10.2. I/O 端口寄存器

MA816 所有端口可通过软件个别的、独立的配置为四种之中的一种类型,基于位位基础,如下表所示。这四种类型有:

准双向(标准 8051 的 I/O 端口)、上拉输出、集电极开路输出和输入(高阻抗输入)。每个端口有两个模式寄存器来选择

各个端口引脚的类型。

表 10-2 端口配置设定

PxM0.y PxM1.y

0 0

0 1

1 0

1 1

这里 x=0~4 (端口号),y=0~7 (端口引脚)。寄存器 PxM0 和 PxM1 列表如下。

端口模式

准双向端口

推挽式输出

仅输入(高阻抗输入)

开漏集输出

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 23/79

Page 24

Preliminary, v 0.06

MA816

10.2.1. 端口 0

端口 0寄存器

P0:

SFR 地址 = 0x80

SFR 页 = 全部 复位值 = 1111-1111

7 6 5 4 3 2 1 0

P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1 P0.0

R/W R/W R/W R/W R/W R/W R/W R/W

Bit 7~0: P0.7~P0.0 通过 CPU 置 1/清 0。

P0M0:

模式寄存器

0

端口

0

SFR 地址 = 0x93

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

P0M0.7 P0M0.6 P0M0.5 P0M0.4 P0M0.3 P0M0.2 P0M0.1 P0M0.0

R/W R/W R/W R/W R/W R/W R/W R/W

P0M1:

模式寄存器

1

端口

0

SFR 地址 = 0x94

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

P0M1.7 P0M1.6 P0M1.5 P0M1.4 P0M1.3 P0M1.2 P0M1.1 P0M1.0

R/W R/W R/W R/W R/W R/W R/W R/W

10.2.2. 端口 1

端口

1

P1:

寄存器

SFR 地址 = 0x90

SFR 页 = 全部 复位值 = 1111-1111

7 6 5 4 3 2 1 0

P1.7 P1.6 P1.5 P1.4 P1.3 P1.2 P1.1 P1.0

R/W R/W R/W R/W R/W R/W R/W R/W

Bit 7~0: P1.7~P1.0 通过 CPU 置 1/清 0

P1M0:

模式寄存器

0

端口

1

SFR 地址 = 0x91

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

P1M0.7 P1M0.6 P1M0.5 P1M0.4 P1M0.3 P1M0.2 P1M0.1 P1M0.0

R/W R/W R/W R/W R/W R/W R/W R/W

P1M1:

模式寄存器

1

端口

1

SFR 地址 = 0x92

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

P1M1.7 P1M1.6 P1M1.5 P1M1.4 P1M1.3 P1M1.2 P1M1.1 P1M1.0

R/W R/W R/W R/W R/W R/W R/W R/W

如果 P1.1 ~ P1.5 任何一个口设置为比较器模式输入,则必须配置这个 I/O 口模式为仅输入模式为比较器得到模拟信号。

10.2.3. 端口 2

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 24/79

Page 25

Preliminary, v 0.06

MA816

P2:

端口

2

寄存器

SFR 地址 = 0xA0

SFR 页 = 全部 复位值 = 1111-1111

7 6 5 4 3 2 1 0

P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0

R/W R/W R/W R/W R/W R/W R/W R/W

Bit 7~0: P2.7~P2.0 通过 CPU 置 1/清 0。 或在 PWM 模式时作 PWM 定时器下溢出事件的通道。

P2M0:

模式寄存器

0

端口

2

SFR 地址 = 0x95

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

P2M0.7 P2M0.6 P2M0.5 P2M0.4 P2M0.3 P2M0.2 P2M0.1 P2M0.0

R/W R/W R/W R/W R/W R/W R/W R/W

P2M1:

模式寄存器

1

端口

2

SFR 地址 = 0x96

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

P2M1.7 P2M1.6 P2M1.5 P2M1.4 P2M1.3 P2M1.2 P2M1.1 P2M1.0

R/W R/W R/W R/W R/W R/W R/W R/W

10.2.4. 端口 3

端口

3

P3:

寄存器

SFR 地址 = 0xB0

SFR 页 = 全部 复位值 = 1111-1111

7 6 5 4 3 2 1 0

P3.7 P3.6 P3.5 P3.4 P3.3 P3.2 P3.1 P3.0

R/W R/W R/W R/W R/W R/W R/W R/W

Bit 7~0: P3.7~P3.0 通过 CPU 置 1/清 0。

P3M0:

模式寄存器

0

端口

3

SFR 地址 = 0xB1

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

P3M0.7 P3M0.6 P3M0.5 P3M0.4 P3M0.3 P3M0.2 P3M0.1 P3M0.0

R/W R/W R/W R/W R/W R/W R/W R/W

P3M1:

模式寄存器

1

端口

3

SFR 地址 = 0xB2

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

P3M1.7 P3M1.6 P3M1.5 P3M1.4 P3M1.3 P3M1.2 P3M1.1 P3M1.0

R/W R/W R/W R/W R/W R/W R/W R/W

10.2.5. 端口 4

端口

4

P4:

寄存器

SFR 地址 = 0xE8

SFR 页 = 全部 复位值 = x111-1111

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 25/79

Page 26

Preliminary, v 0.06

MA816

7 6 5 4 3 2 1 0

-- P4.6 P4.5 P4.4 P4.3 P4.2 P4.1 P4.0

R R/W R/W R/W R/W R/W R/W R/W

Bit 6~0: P4.6~P4.0 通过 CPU 置 1/清 0。

P4M0:

模式寄存器

0

端口

4

SFR 地址 = 0xB3

SFR 页 = 全部 复位值 = x000-00xx

7 6 5 4 3 2 1 0

-- P4M0.6 P4M0.5 P4M0.4 P4M0.3 P4M0.2 P4M0.1 P4M0.0

R R/W R/W R/W R/W R/W R/W R/W

P4M0.1 和 P4M0.0 的复位值由硬件选项 P41IOE 和 P40IOE 决定。如果硬件选项 P41IOE 和 P40IOE 被打开,则

P4M0.1 和 P4M0.0 的复位值被置 “1” 配置 P4.1/P4.0 作仅输入模式。否则 P4M0.1/P4M0.0 的复位值被清 “0”配置

P4.1/P4.0 作准双向口。

P4M1:

模式寄存器

1

端口

4

SFR 地址 = 0xB4

SFR 页 = 全部 复位值 = x000-0000

7 6 5 4 3 2 1 0

-- P4M1.6 P4M1.5 P4M1.4 P4M1.3 P4M1.2 P4M1.1 P4M1.0

R R/W R/W R/W R/W R/W R/W R/W

10.2.6. 端口 5

端口

5

P5:

寄存器

SFR 地址 = 0xF8

SFR 页 = 全部 复位值 = 1111-1111

7 6 5 4 3 2 1 0

P5.7 P5.6 P5.5 P5.4 P5.3 P5.2 P5.1 P5.0

R/W R/W R/W R/W R/W R/W R/W R/W

Bit 7~0: P5.7~P5.0 通过 CPU 置 1/清 0。 当 PWM 定时器被使能和 AUXR1.P5PWM 被使能时P5 也可作PWM 输出 。

P5M0:

模式寄存器

0

端口

5

SFR 地址 = 0xB5

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

P5M0.7 P5M0.6 P5M0.5 P5M0.4 P5M0.3 P5M0.2 P5M0.1 P5M0.0

R/W R/W R/W R/W R/W R/W R/W R/W

P5M1:

模式寄存器

1

端口

5

SFR 地址 = 0xB6

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

P5M1.7 P5M1.6 P5M1.5 P5M1.4 P5M1.3 P5M1.2 P5M1.1 P5M1.0

R/W R/W R/W R/W R/W R/W R/W R/W

10.2.7. 端口 6

端口

6

P6:

寄存器

SFR 地址 = 0xC8

SFR 页 = F 复位值 = xxxx-xx11

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 26/79

Page 27

Preliminary, v 0.06

MA816

7 6 5 4 3 2 1 0

-- -- -- -- -- -- P6.1 P6.0

R R R R R R R/W R/W

Bit 7~2: 保留.

Bit 1~0: P6.1~P6.0 通过 CPU 置 1/清 0。它们只支持准双向口模式。此寄存器只能通过 SFR 页 F 存取。

10.2.8. 端口 7

端口

7

P7:

寄存器

SFR 地址 = 0xD8

SFR 页 = F 复位值 = 1111-1111

7 6 5 4 3 2 1 0

P7.7 P7.6 P7.5 P7.4 P7.3 P7.2 P7.1 P7.0

R/W R/W R/W R/W R/W R/W R/W R/W

Bit 7~0: P7.7~P7.0 通过 CPU 置 1/清 0。 端口 7 只支持准双向口模式。 o此寄存器只能通过 SFR 页 F 存取。

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 27/79

Page 28

Preliminary, v 0.06

MA816

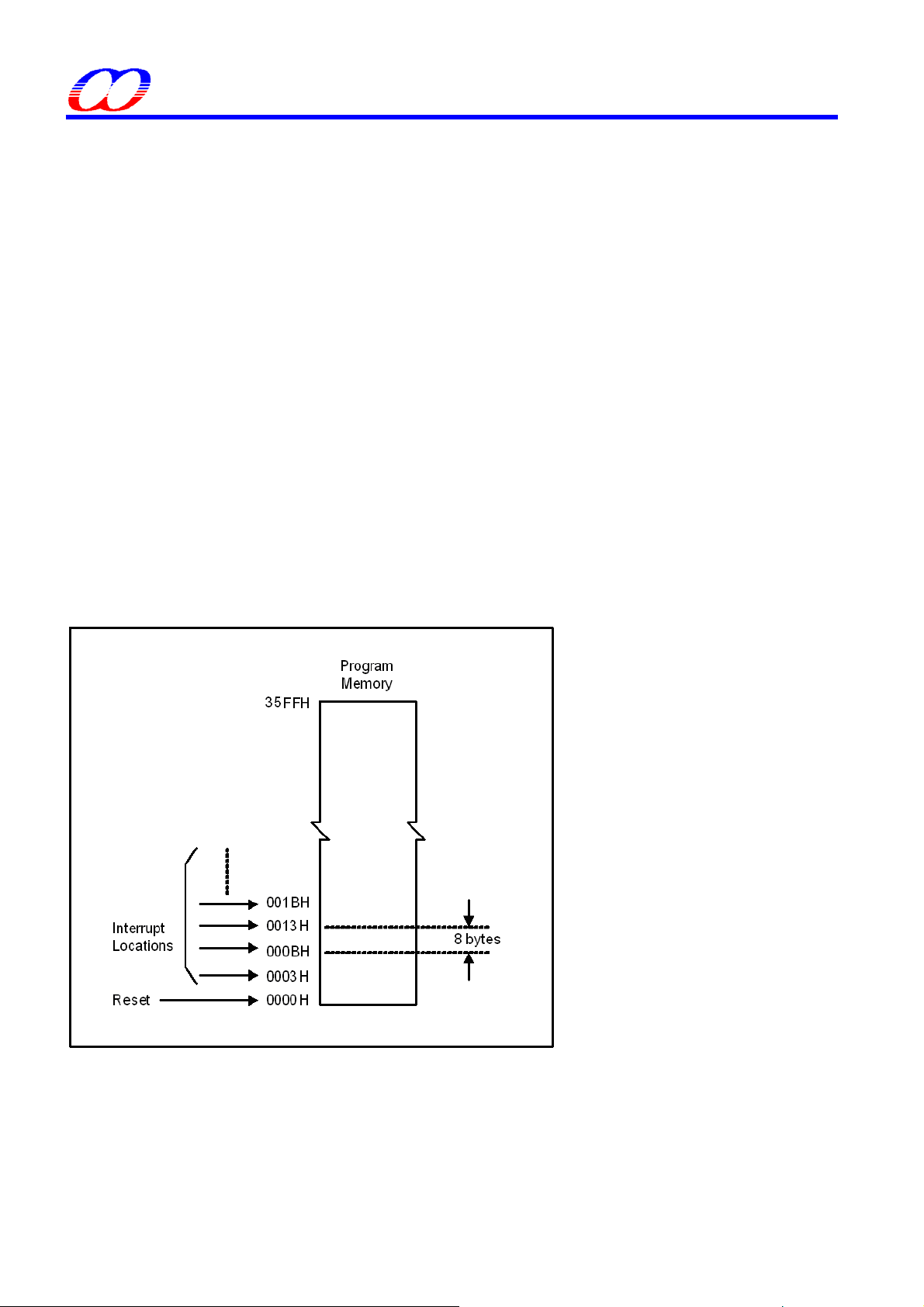

11. 中断

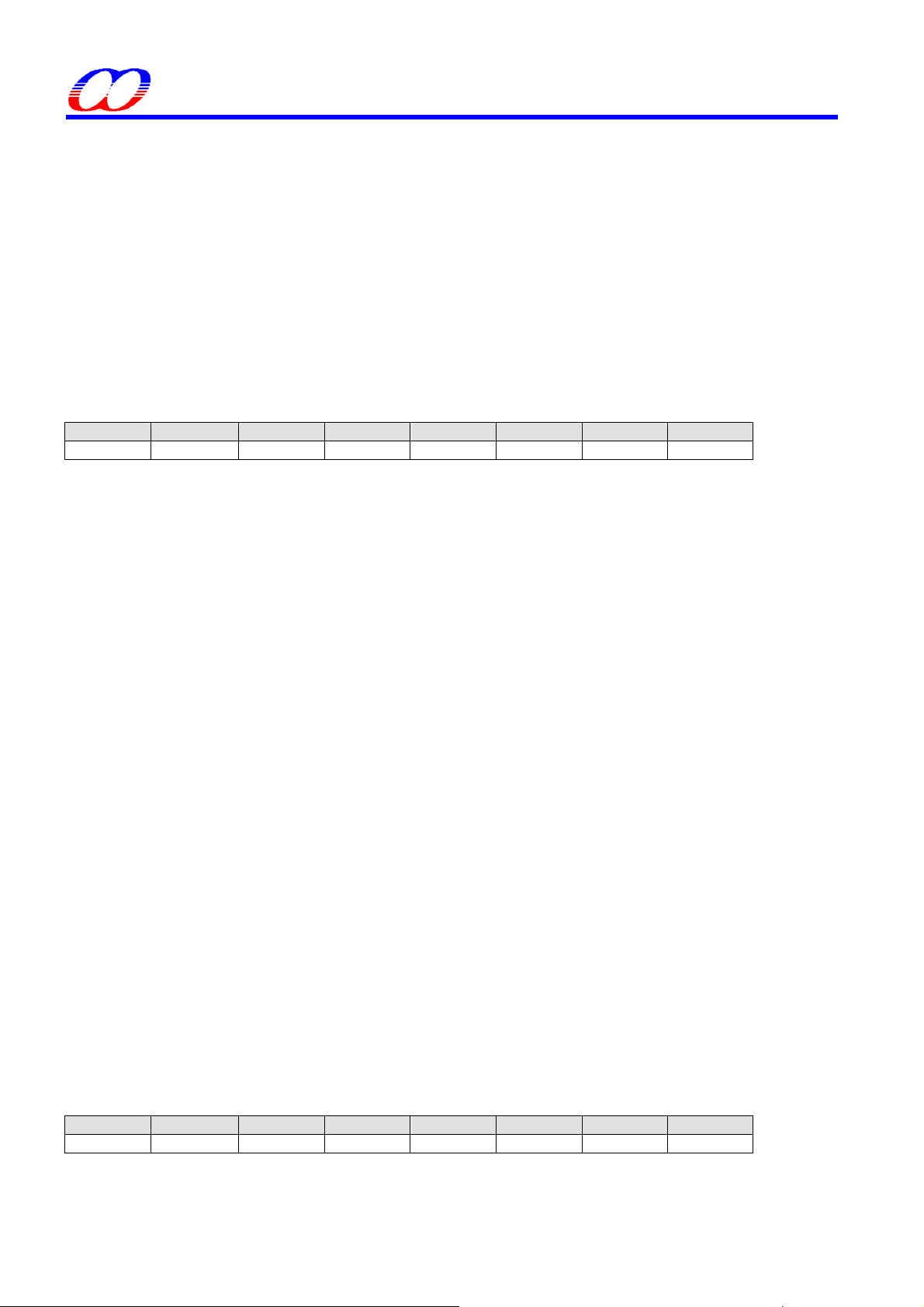

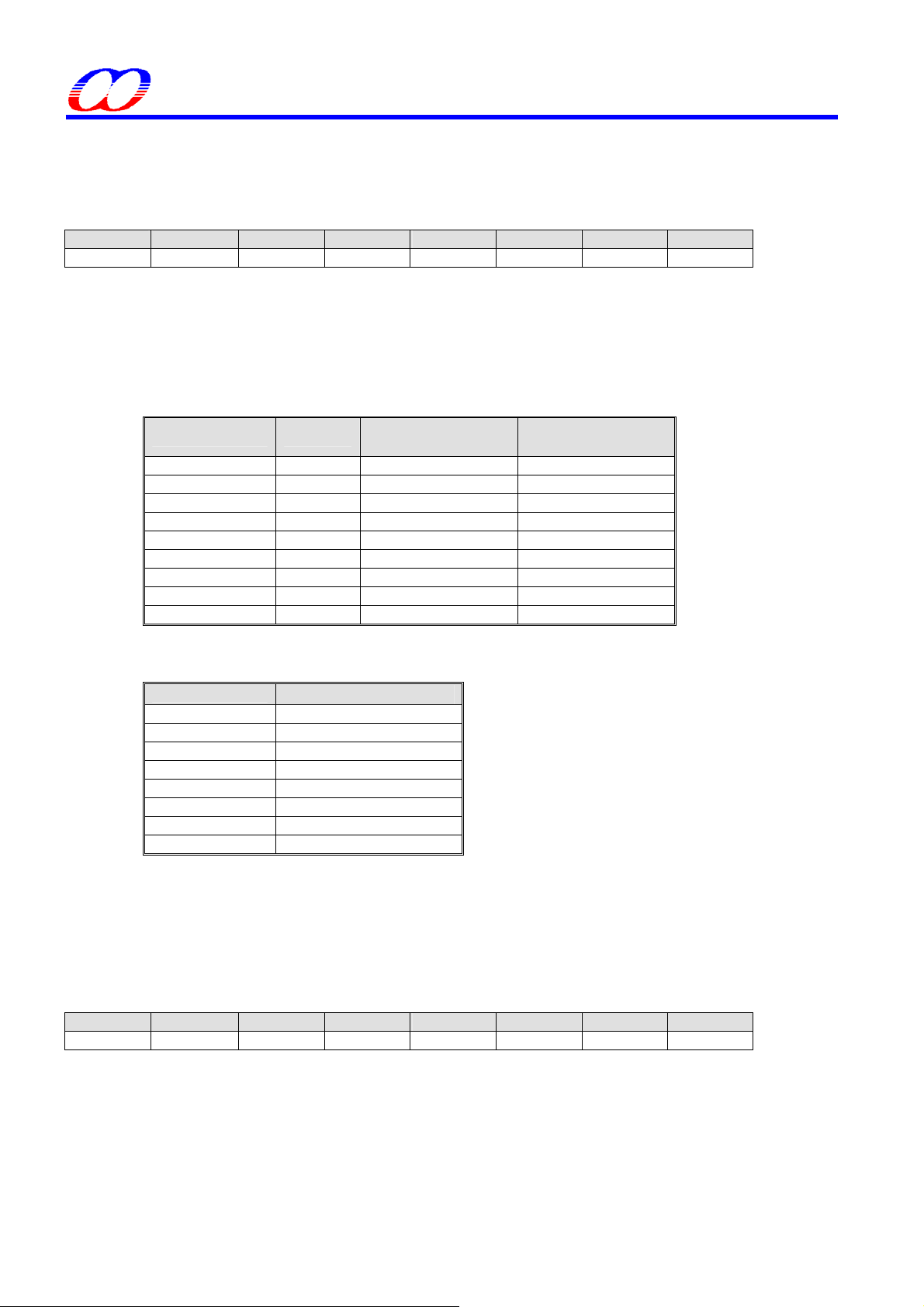

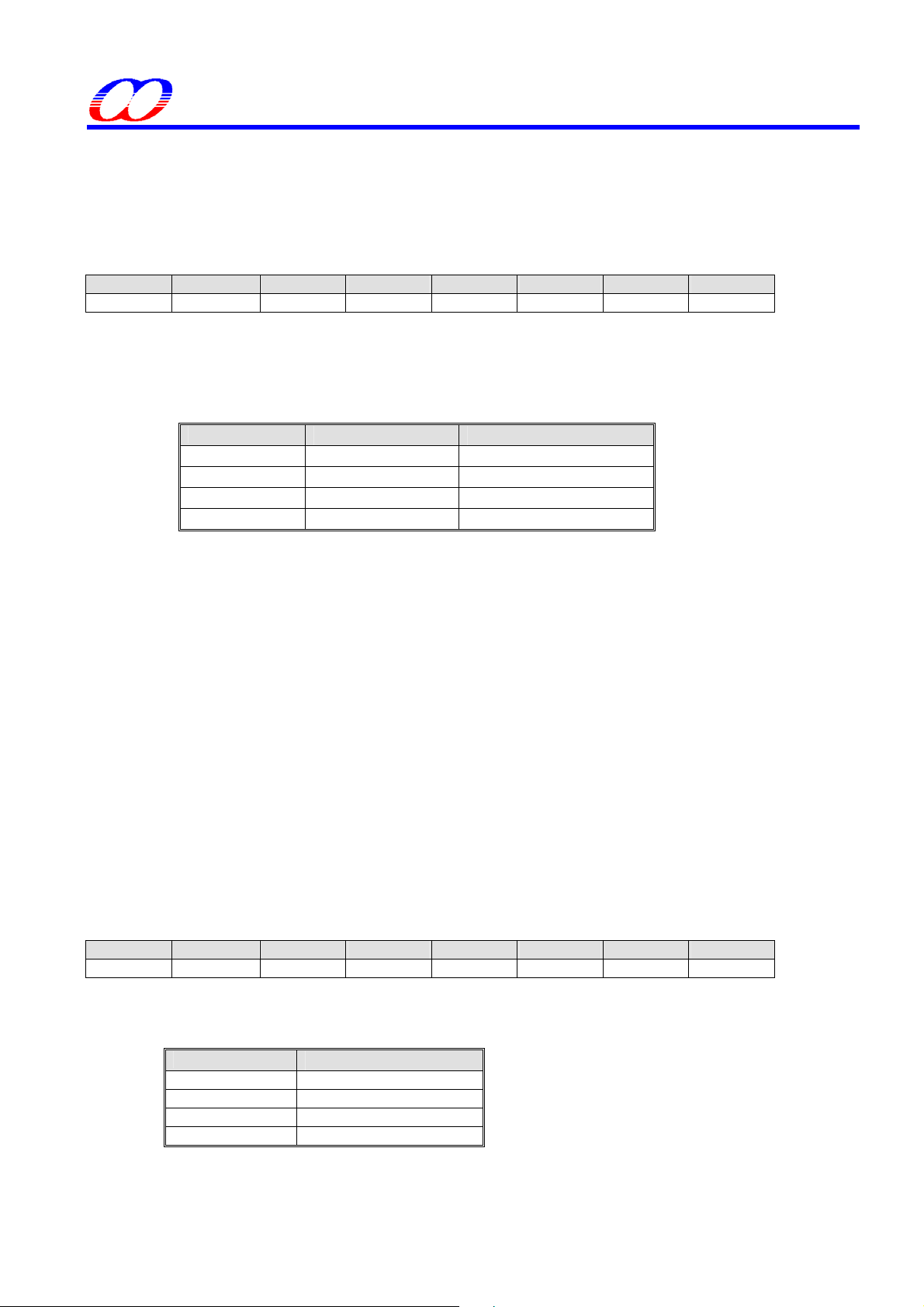

11.1. 中断结构

nINT2

nINT3

PCON1.BOD

nINT0

TCON.TF0

nINT1

TCON.TF1

SCON.RI

SCON.TI

TF2

EXF2

XICO N0.IN T2H

XICO N0.IN T3H

0

1

0

1

TCON.IT 0

TCON.IT 1

XICO N0.IT 2

XICO N0.IT 3

IE0

IE1

IE2

IE3

Global Enable

(IE.EA)

IE.EX0

IE.ET 0

IE.EX1

IE.ET 1

IE.ES

IE.ET 2

XICON 0.E X2

XICON 0.E X3

EIE 1.EBOI

IP0L,IP0H,EIP1L,EIP1H

Registers

Highest Priority Level

Interrupt

Inte rrupt Polling

Sequence

EIE 1.EAC I

ACON.AC F

CMOD_ ECF

CCON.CF

nINT4

nINT5

XICO N1.IT 4

0

1

XICO N1.IN T4H

XICO N1.IT 5

0

1

XICO N1.IN T5H

IE4

IE5

XICON 1.E X4

XICON 1.E X5

Lowest Priori ty

Level I nterrupt

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 28/79

Page 29

Preliminary, v 0.06

MA816

11.2. 中断寄存器

中断使能寄存器

IE:

SFR 地址 = 0xE8

SFR 页 = 全部 复位值 = 0X00-0000

7 6 5 4 3 2 1 0

EA -- ET2 ES ET1 EX1 ET0 EX0

R/W R R/W R/W R/W R/W R/W R/W

Bit 7: EA, 全局中断使能位

0: 禁止所有中断

1: 使能全局中断

Bit 6: 保留.

Bit 5: ET2, 定时器 2 中断使能位

0: 禁止定时器 2 中断

1: 使能定时器 2 中断

Bit 4: ES, 串口中断使能位

0: 禁止串口中断

1: 使能串口中断

Bit 3: ET1, 定时器 1 中断使能位

0: 禁止定时器 1 中断

1: 使能定时器 1 中断

Bit 2: EX1, 外部中断 1 使能位

0: 禁止外部中断 1

1: 使能外部中断 1

Bit 1: ET0, 定时器 0 中断使能位

0: 禁止定时器 0 中断

1: 使能定时器 0 中断

Bit 0: EX0, 外部中断 0 使能位

0: 禁止外部中断 0

1: 使能外部中断 0

XIFLG:

外部中断标志寄存器

SFR 地址 = 0xC0

SFR 页 = 全部 复位值 = XXXX-0000

7 6 5 4 3 2 1 0

-- -- -- -- IE5 IE4 IE3 IE2

R R R R R/W R/W R/W R/W

Bit 7~4: 保留.

Bit 3: IE5, 外部中断 5 请求标志

0: 当进入中断服务程序时硬件清零。也可以通过指令清零。

1: 当侦察到外部中断时硬件置 1。也可以通过软件置 1。

Bit 2: IE4, 外部中断 4 请求标志

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 29/79

Page 30

Preliminary, v 0.06

MA816

0: 当进入中断服务程序时硬件清零。也可以通过指令清零。

1: 当侦察到外部中断时硬件置 1。也可以通过软件置 1。

Bit 1: IE3, 外部中断 3 请求标志

0: 当进入中断服务程序时硬件清零。也可以通过指令清零。

1: 当侦察到外部中断时硬件置 1。也可以通过软件置 1。

Bit 0: IE2, 外部中断 2 请求标志

0: 当进入中断服务程序时硬件清零。也可以通过指令清零。

1: 当侦察到外部中断时硬件置 1。也可以通过软件置 1。

XICON0:

外部中断控制寄存器

0

SFR 地址 = 0xC1

SFR 页 = 全部 复位值 = X000-X000

7 6 5 4 3 2 1 0

-- INT3H IT3 EX3 -- INT2H IT2 EX2

R R/W R/W R/W R R/W R/W R/W

Bit 7: 保留.

Bit 6: INT3H, nINT3 高/低触发使能

0: nINT3 低电平或下降沿触发(P4.2)。

1: nINT3 高电平或上升沿触发(P4.2)。

Bit 5: IT3, 外部中断 3 类型控制位

0: 电平触发

1: 边沿触发

Bit 4: EX3, 外部中断 3 使能位

0: 禁止外部中断 3

1: 使能外部中断 3

Bit 3: 保留.

Bit 2: INT2H, nINT2 高/低触发使能

0: nINT2 低电平或下降沿触发(P4.3)。

1: nINT2 高电平或上升沿触发(P4.3)。

Bit 1: IT2, 外部中断 2 类型控制位

0: 电平触发

1: 边沿触发

Bit 0: EX2, 外部中断 2 使能位

0: 禁止外部中断 2

1: 使能外部中断 2

XICON1:

外部中断控制寄存器

1

SFR 地址 = 0xC2

SFR 页 = 全部 复位值 = X000-X000

7 6 5 4 3 2 1 0

-- INT5H IT5 EX5 -- INT4H IT4 EX4

R R/W R/W R/W R R/W R/W R/W

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 30/79

Page 31

Preliminary, v 0.06

MA816

Bit 7: 保留.

Bit 6: INT5H, nINT5 高/低触发使能

0: nINT5 低电平或下降沿触发(P5.1)

1: nINT5 高电平或上升沿触发(P5.1)

Bit 5: IT5, 外部中断 5 类型控制位

0: 电平触发

1: 边沿触发

Bit 4: EX5, 外部中断 5 使能位

0: 禁止外部中断 5

1: 使能外部中断 5

Bit 3: 保留.

Bit 2: INT4H, nINT4 高/低触发使能

0: nINT4 低电平或下降沿触发(P5.0)

1: nINT4 高电平或上升沿触发(P5.0)

Bit 1: IT4, 外部中断 4 类型控制位

0: 电平触发

1: 边沿触发

Bit 0: EX4, 外部中断 4 使能位

0: 禁止外部中断 4

1: 使能外部中断 4

扩展中断使能寄存器

EIE1:

SFR 地址 = 0xAD

SFR 页 = 全部 复位值 = XXXX-XX00

7 6 5 4 3 2 1 0

-- -- -- -- -- -- EACI EBOI

R R R R R R R/W R/W

Bit 7~2: 保留.

Bit 1: EACI, 模拟比较器中断使能位

0: 模拟比较器中当 ACCON.ACF =1 时使能比较器中断

1: 模拟比较器中当 ACCON.ACF =1 时禁止比较器中断

Bit 0: EBOI, BOD 中断使能

0: 电源控制模块中当 PCON1.BOD=1 时使能 BOD 中断

1: 电源控制模块中当 PCON1.BOD=1 时禁止 BOD 中断

中断优先级寄存器

IP0L:

0 低

SFR 地址 = 0xB8

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

PX3L PX2L PT2L PSL PT1L PX1L PT0L PX0L

R/W R/W R/W R/W R/W R/W R/W R/W

Bit 7: PX3L, 外部中断 3 优先级 低位

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 31/79

Page 32

Preliminary, v 0.06

MA816

Bit 6: PX2L, 外部中断 2 优先级 低位

Bit 5: PT2L, 定时器 2 中断优先级 低位

Bit 4: PSL, 串行口中断优先级 低位

Bit 3: PT1L, 定时器 1 中断优先级 低位

Bit 2: PX1L, 外部中断 1 优先级 低位

Bit 1: PT0L, 定时器 0 中断优先级 低位

Bit 0: PX0L, 定时器 0 中断优先级 低位

IP0H:

中断优先级寄存器

0 高

SFR 地址 = 0xB7

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

PX3H PX2H PT2H PSH PT1H PX1H PT0H PX0H

R/W R/W R/W R/W R/W R/W R/W R/W

Bit 7: PX3H, 外部中断 3 优先级 高位

Bit 6: PX2H, 外部中断 2 优先级 高位

Bit 5: PT2H, 定时器 2 中断优先级 高位

Bit 4: PSH, 串行口中断优先级 高位

Bit 3: PT1H, 定时器 1 中断优先级 高位

Bit 2: PX1H, 外部中断 1 优先级 高位

Bit 1: PT0H, 定时器 0 中断优先级 高位

Bit 0: PX0H, 定时器 0 中断优先级 高位

EIP1L:

扩展中断优先级寄存器

1 低

SFR 地址 = 0xAE

SFR 页 = 全部 复位值 = XXX0-0000

7 6 5 4 3 2 1 0

-- -- -- PX5L PX4L PPTL PACL PBOL

R R R R/W R/W R/W R/W R/W

Bit 7~5: 保留.

Bit 4: PX5L, 外部中断 5 优先级 低位

Bit 3: PX4L, 外部中断 4 优先级 低位

Bit 2: PPTL, PWM 定时器 中断优先级 低位

Bit 1: PACL, 模拟比较器中断优先级 低位

Bit 0: PBOL, BOD 中断优先级 低位

EIP1H:

扩展中断优先级寄存器

1 高

SFR 地址 = 0xAF

SFR 页 = 全部 复位值 = XXX0-0000

7 6 5 4 3 2 1 0

-- -- -- PX5H PX4H PPTH PACH PBOH

R R R R/W R/W R/W R/W R/W

Bit 7~5: 保留.

Bit 4: PX5H, 外部中断 5 优先级 高位

Bit 3: PX4H, 外部中断 4 优先级 高位

Bit 2: PPTH, PWM 定时器 中断优先级 高位

Bit 1: PACH, 模拟比较器中断优先级 高位

Bit 0: PBOH, BOD 中断优先级 高位

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 32/79

Page 33

Preliminary, v 0.06

MA816

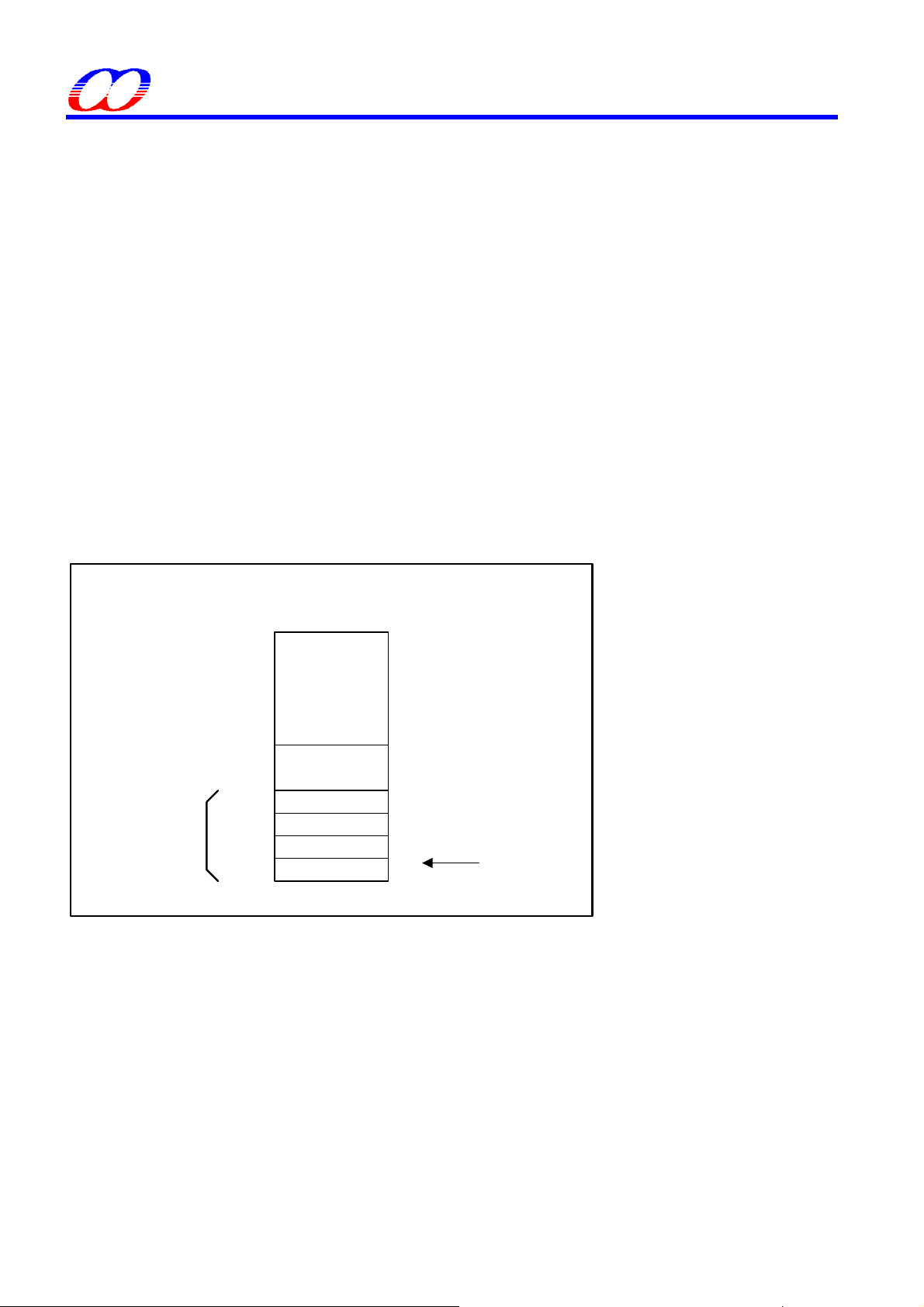

IP0L, IP0H, EIP1L 和 EIP1H 组合成 4 级优先级中断,见下表:

{IPH.x , IPL.x}

11

优先级

1 (最高)

10 2

01 3

00 4

MA816 有 13 个中断源。通过置位或清零寄存器 IE、EIE1、 XICON0、 XICON1 中对应使能位可以单独的使能或禁

止每一个中断源。也包含一个全局禁止位 EA,清零 EA 则禁止所有中断。

每个中断源有两个对应的中断优先级寄存器位去设置它的优先级。一个在 IpxH 寄存器中,另一个在案 IpxL 寄存器中。

高优先级的中断不会被低优先级的中断请求打断。两个优先不同的中断请求同时发生则高优先级的中断优先被处理,

若优先级相同的中断请求同时发生则由内部查询顺序决定处理哪个中断。两级优先级中断结构在控制这些中断事物中

是非常灵活的。下表展示了相同级别中断的内部查询顺序和中断向量。

中断源 向量地址 优先级别

外部中断 0

定时器 0

外部中断 1

定时器 1

串行口中断

定时器 2

外部中断 2

外部中断 3

0003H

1 (高)

000BH 2

0013H 3

001BH 4

0023H 5

002BH 6

0033H 7

003BH 8

BOD 0043H 9

模拟比较器

PWM 定时器

外部中断 4

外部中断 5

004BH 10

0053H 11

005BH 12

0063H 13

外部中断/INT0、/INT1、/INT2、/INT3 和 /INT4 分别通过 TCON 的 IT0、IT1,XICON0 的 IT2、IT3,XICON1 的

IT4、IT5 可以设置成电平触发或边沿触发。实际产生的中断标志位是 TCON 的 IE0、IE1,XIFLG 的 IE2、IE3、IE4、

IE5。产生外部中断时,如果是边沿触发,进入中断服务程序后由硬件清除中断标志位,如果中断是电平触发,由外部

请求源而不是由片内硬件控制请求标志。

定时器 0 和定时器 1 中断由 TF0 和 TF1(分别由各自的定时/计数寄存器控制)产生。当产生定时器中断时,进入中断服

务程序后由片内硬件清除标志位。

串口中断由 RI 和 TI 的逻辑或产生。进入中断服务程序后,这些标志均不能被硬件清除。实际上,中断服务程序通常

需要确定是由 R I 还是 TI 产生的中断,然后由软件清除中断标志。

定时器 2 中断由 TF2 和 EXF2 的逻辑或产生。进入中断服务程序后,这些标志均不能被硬件清除。实际上,中断服

务程序通常需要确定是由 TF2 还是 EXF2 产生的中断,然后由软件清除中断标志。

BOD 中断由 PCON1.BOD 产生,当片上的 Brownout-Detector 检测到对应的低电平事件时置此位中断请求标志。进

入中断服务程序后由片内硬件清除标志位。

模拟比较器中断由 ACCON .ACF 产生。进入中断服务程序后由片内硬件清除标志位。

PWM 定时器中断由 CCON.CF 产生。进入中断服务程序后由片内硬件清除标志位。i

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 33/79

Page 34

所有这些产生中断的位都可通过软件置位或清零,与通过硬件置位或清零的效果相同。简而言之,中断可由软件产生,

推迟或取消。

硬件如何响应中断

每一个机器周期的 S5P2 时间采样中断请求标志,采样被保持到下一个 S5P2 时期。如果一个中断

请求标志在第一个 S5P2 时间被置位,在第二个 S5P2 时间(采样周期)将被硬件发现,这时若没有下

面任何一个阻止条件则中断系统将产生一个硬件调用 LCALL 转去执行相应的中断服务程序。

阻止条件如下:

1. CPU 正在处理同级或更高级的中断;

2. 现行机器周期不是所执行的最后一个机器周期;

3. 正在执行的是 RETI 或是访问 IE 或 IP 的指令。

上叙任何一个条件都会阻止硬件去响应发生的中断请求。条件 2保证了在进入其它中断服务程序前

执行完当前指令。条件 3 保证了执行完 RETI 指令或是访问 IE 或 IP 的指令后在进入其它中断向量前能

执行至少一条或更多条的指令。

每个机器周期硬件都会重复查询中断请求标志,查询到的值都是前一个 S5P2 时间的状态。值得注

意的是如果一个被触发的中断标志由于上面的阻止条件发生了而没得到响应,并且此标志没有持续到阻

止条件消失,这样的中断请求将得不到响应。也就是说,中断处理本身不能锁存中断,譬如外部电平中

断若在电平出现时被屏蔽,而在中断识别之前电平消失,它被完全忽略。也就是每个查询都是新状态。

Preliminary, v 0.06

MA816

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 34/79

Page 35

Preliminary, v 0.06

MA816

12. 定时器/计数器

MA816 有四个定时/计数器:定时器 0、定时器 1、定时器 2和 PWM 定时器 。定时器 0/1/2 能被配置作为定时器或

事件计数器。PWM 定时器能配置为定时器 或 PWM 发生器。

定时器功能,TLx 寄存器每 12 个时钟周期或 1 个时钟周期加 1,通过软件设置 AUXR2.T0X12、 AUXR2.T1X12 和

T2MOD.T2X12 位来选择 。每 12 个时钟周期加一,计数速率达 1/12 的晶振频率。

计数器功能,根据对应的外部输入引脚的下降沿 T0、T1 或 T2 寄存器加 1。在这些功能中,每个时钟周期对外部输入

信号(T0、T1 和 T2 引脚)进行采样,每 12 个时钟周期对 T2 引脚采样。当采样信号出现一个高电平接着一个低电平,

计数加 1。当检测到跳变时新计数值出现在寄存器中。对定时器 0 和定时器 1 来说,需要用两个时钟周期来识别下降

沿跳变,最大的计数速率为 1/2 的晶振频率;对于定时器 2,需要用 24 个时钟周期来识别下降沿跳变,最大计数速率

为 1/24 的晶振频率。外部输入信号没有严格的周期限制,但是要确保在电平改变前至少有一次采样,对定时器 0 和定

时器 1 来说信号应该至少保持一个时钟,定时器 2 需要 12 个时钟周期。

12.1. 定时器 0 和定时器 1

12.1.1. 模式 0

在这个模式,定时器寄存器配置为一个 13 位寄存器。计数器所有位从全 1 翻转到全 0,置位定时器中断标志位 TFx。

当 TRx=1 且 GATE=0 或/INTx=1,定时器使能输入计数。(置 GATE=1 时通过外部输入/INTx 控制定时器,以便脉冲宽

度测量)。TRx 和 TFx 控制位在专用寄存器 TCON。GATE 位在TMOD。有两个不同的 GATE 位,一个是定时器 0(TMOD.7)

另一个是定时器 0(TMOD.3)。

13 位寄存器包含 THx 的所有 8 位和 TLx 的低 5 位。TLx 的高 3 位是不确定的可以忽略。置位运行标志(TRx)不会清除

寄存器。意思是说用户在开始计数前应对 THx 和 TLx 进行初始化。

SYSCLK

≅ 12

SYSCLK

Tx Pin

TRx

GATE

nINTx Pin

AUXR2.TxX12=0

AUXR2.TxX12=1

C/T =0

C/T =1

Overflow

TFx Interr uptTHx[7:0]TLx[4:0]

x = 0 or 1

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 35/79

Page 36

Preliminary, v 0.06

MA816

12.1.2. 模式 1

除了定时器的寄存器使用全部 16 位外,模式 1 和模式 0 是相同的。在这个模式,THx 和 TLx 串联,没有预分频。

SYSCLK

12

SYSCLK

Tx Pin

TRx

GATE

nINTx Pin

AUXR2.TxX12=0

AUXR2.TxX12=1

C/T =0

C/T =1

Overflow

TFx Interr uptTHx[7:0]TLx[7:0]

x = 0 or 1

12.1.3. 模式 2

模式 2 配置定时器寄存器为一个自动加载的 8 位计数器(TLx)。TLx 溢出不仅置位 TFx,而且也将 THx 的内容加

载到 TLx,THx 内容由软件预置,加载不会改变 THx 的值。

SYSCLK

Ξ 12

AUXR2.TxX12=0

SYSCLK

Tx Pin

TRx

GATE

nINTx Pin

AUXR2.TxX12=1

C/T =0

C/T =1

THx[7:0]

Reload

Overflow

TFx InterruptTLx[7:0]

x = 0 or 1

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 36/79

Page 37

Preliminary, v 0.06

MA816

12.1.4. 模式 3

定时器 1 在模式 3 保持计数值。效果和设置 TR1=0 一样。

定时器 0 在模式 3 建立 TL0 和 TH0 两个独立的计数器。TL0 使用定时器 0 控制位:C/T、GATE、TR0、/INT0

和 TF0。TH0 锁定为定时器功能(每个机器周期计数)且接替定时器 1 来使用 TR1 和 TF1,因从 TH0 控制定时器 1 中断。

模式 3 提供当有额外的需求应用时的一个 8 位时器或计数器时。当定时器 0 在模式 3 时,定时器 1 可打开或关闭

并切换到脱离,进入到自己的模式 3,或仍然可用作为串行口的波特率发生器,或者不需要中断的其它应用。

SYSCLK

SYSCLK

Ξ 12

SYSCLK

Ξ 12

SYSCLK

T0 Pin

TR0

GATE

nINT0 Pin

TR1

AUXR2.T0X12=0

AUXR2.T0X12=1

AUXR2.T0X12=0

AUXR2.T0X12=1

C/T =0

C/T =1

TH0[7:0]

Overflow

Overflow

TF0 InterruptTL0[7:0]

TF1 Interrupt

12.1.5. 定时器时钟输出

定时器的可编程时钟输出模式,则从引脚 TxCK0 输出占空比为 50%的时钟周期。输出频率根据系统时钟频率(Fosc)

和加载值到 THx 寄存器的值决定,公式如下所示。时钟输出模式编程步骤如下:

1. 在 AUXR2 寄存器置位 TxCKOE。

2. 在 TMOD 寄存器清除定时器 0/1 的 C/T 位。

SYSCLK

Ξ 12

SYSCLK

AUXR2.TxX12=0

AUXR2.TxX12=1

C/T=0

TRx

GAT E=0

nINTx Pin

TLx[7:0]

THx[7:0]

Overflow

Reload

QD

Q

CK

AUXR2.TxCKOE = 1

TxCKO

x = 0 or 1

; n=24, if TxX12=0

; n=2, if TxX12=1

; x = 0 or 1 & C/T = 0

T0/T1 Cloc k-out Frequency =

SYSCLK Frequency

n X (256 – THx)

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 37/79

Page 38

Preliminary, v 0.06

MA816

12.1.6. 定时器 0/1 寄存器

TMOD:

定时器/计数器模式寄存器

SFR 地址 = 0x89

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

GATE C/T M1 M0 GATE C/T M1 M0

R/W R/W R/W R/W R/W R/W R/W R/W

|Å----------------------- Timer1 -------------------------Æ|Å--------------------------Timer0 ------------------------Æ|

GATE: 当门控位置位时,只有在/INT0 或/INT1 引脚是高电平且 TR0 或 TR1 控制位置位时,定时器/计数器 0 或 1 使

能。当门控制位清零时,只要 TR0 或 TR1 置 1 定时器 0 或 1 使能。

C/T: 定时器或计数器选择器。清零为定时器功能(从内部系统时钟输入)。置位为计数器功能(从 T0 或 T1 引脚输入)。

M1 M0

0 0

0 1

1 0

1 1

1 1

工作模式

13 位定时器/计数器。

16 位定时器/计数器。THx 与 TLx 串联,没有分频器

8 位自动重载定时器/计数器。THx 保持一个值,并在每次溢出时加载

到 TLx

(定时器 0)TL0 是一个 8 位定时器/计数器并通过标准定时器 0 的控制

位控制。TH0 仅仅是一个 8 位定时器通过定时器 1 的控制位控制

(定时器 1)定时器/计数器停止

TCON:

定时器/计数器控制寄存器

SFR 地址 = 0x88

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

R/W R/W R/W R/W R/W R/W R/W R/W

TF1: 定时器 1 溢出标志位。定时器/计数器溢出时由硬件置位。处理器进入中断向量程序由硬件清零。

TR1: 定时器 1 运行控制位。通过软件置位/清零开启或关闭定时器/计数器 1。

TF0: 定时器 0 溢出标志位。定时器/计数器溢出时由硬件置位。处理器进入中断向量程序由硬件清零。

TR0: 定时器 0 运行控制位。通过软件置位/清零开启或关闭定时器/计数器 0。

IE1: 外部中断 1 请求标志. 外部中断 1 由边沿或电平触发(由 IT1 设置)硬件置标志.

IT1: 外部中断 1 类型控制位. 软件选择下降沿/低电平触发外部中断 1.

IE0: 外部中断 0 请求标志. 外部中断 0 由边沿或电平触发(由 IT0 设置)硬件置标志.

IT0: 外部中断 0 类型控制位. 软件选择下降沿/低电平触发外部中断 0.

TL0:

定时器0低

SFR 地址 = 0x8A

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

TL0[7] TL0[6] TL0[5] TL0[4] TL0[3] TL0[2] TL0[1] TL0[0]

R/W R/W R/W R/W R/W R/W R/W R/W

TH0:

定时器0高

SFR 地址 = 0x8C

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

TH0[7] TH0[6] TH0[5] TH0[4] TH0[3] TH0[2] TH0[1] TH0[0]

R/W R/W R/W R/W R/W R/W R/W R/W

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 38/79

Page 39

Preliminary, v 0.06

MA816

TL1:

定时器1低

SFR 地址 = 0x8B

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

TL1[7] TL1[6] TL1[5] TL1[4] TL1[3] TL1[2] TL1[1] TL1[0]

R/W R/W R/W R/W R/W R/W R/W R/W

TH1:

定时器1高

SFR 地址 = 0x8D

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

TH1[7] TH1[6] TH1[5] TH1[4] TH1[3] TH1[2] TH1[1] TH1[0]

R/W R/W R/W R/W R/W R/W R/W R/W

AUXR2:

辅助寄存器

2

SFR 地址 = 0xA3

SFR 页 = 全部 复位值 = 000X-XX00

7 6 5 4 3 2 1 0

T0X12 T1X12 URM0X6 -- -- -- T1CKOE T0CKOE

R/W R/W R/W R R R R/W R/W

T0X12: 当 C/T=0 时,定时器 0 的时钟源选择。

置位选择 Fosc 作为系统时钟源,清零选择 Fosc/12 作为时钟源。

T1X12: 当 C/T=0 时,定时器 1 的时钟源选择。

置位选择 Fosc 作为系统时钟源,清零选择 Fosc/12 作为时钟源。

T1CKOE: 置位/清零来使能/禁止从 P3.5 输出定时器 1 时钟。

T0CKOE: 置位/清零来使能/禁止从 P3.4 输出定时器 0 时钟。

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 39/79

Page 40

Preliminary, v 0.06

MA816

12.2. 定时器 2

定时器 2 是一个 16 位定时器/计数器,既可作为一个定时器也可以作为一个事件计数器,通过专用寄存器 T2CON 的

C/T2 位来选择。定时器 2 有四种工作模式:捕获、自动加载(向上或向下计数)、波特率发生器和可编程时钟输出,通

过专用寄存器 T2CON 和 T2MOD 来选择。

12.2.1. 捕获模式 (CP)

在捕获模式,有两个选项通过 T2CON 中的 EXEN2 位来选择。如果 EXEN2=0,定时器 2 做为一个 16 位的定时器或

计数器,向上溢出,定时器 2 溢出时 TF2 置位。这位可以用来产生中断(通过使能 IE 寄存器中的定时器 2 中断位)。如

果 EXEN2=1,定时器 2 仍然向上, 当外部输入信号 T2EX 由下降沿跳变时引起定时器 2 的寄存器 TH2 和 TL2 分别

对应的捕获到 RCAP2H 和 RCAP2L。另外,T2EX 的跳变引起 T2CON 的 EXF2 置位,且 EXF2 位(象 TF2)将产生一

个中断(中断向量的位置和定时器 2 溢出中断位置相同)。捕获模式图解如下图。(在这个模式 TL2 和 TH2 没有加载值。

直到从 T2EX 捕获事件发生,在 T2EX 引脚跳变或 Fosc/12 的脉冲产生时计数器仍然保持计数)。

图 12-5 定时器 2 捕获模式

SYSCLK

12

SYSCLK

T2 Pin

T2EX Pin

T2MOD.T2X12=0

T2MOD. T2X12=1

Transition

Detection

C/T2=0

C/T2=1

TR2

EXEN2

Capture

TL2

(8 Bits)

TH2

(8 Bits)

RCAP2HRCAP2L

Overflow

TF2

Timer2 Interrupt

EXF2

12.2.2. 自动加载模式(AR)

在 16 位自动加载模式,定时器既可配置成定时器也可以配置成计数器(C/T2 在 T2CON 寄存器),接着编程向上或

向下计数。计数方向由 T2MOD 寄存器的 DCEN 位来决定(向下计数使能)。在复位之后,DCEN=0 意思是默认为定时

器 2 向上计数。如果 DCEN 置位,定时器 2 向上或向下计数由 T2EX 引脚的值来决定。

图 12-6 示 DCEN=0,自动使能定时器 2 向上计数。这个模式有两个选项可以通过 T2CON 寄存器的 EXEN2 位来

选择。 如果 EXEN2=0,定时器向上计数 0XFFFF 接着计数将置位 TF2(溢出标志位)。这将引起定时器 2 的寄存器将

RCAP2L 和 RCAP2H 的值加载。RCAP2L 和 RCAP2H 的值由软件预置。如果 EXEN2=1,一个溢出或在输入 T2EX

的一个负跳变将触发加载 16 位值。跳变将置位 EXF2 位。当 TF2 或 EXF2 置 1 时,如果定时器 2 中断使能,将产生

中断。

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 40/79

Page 41

Preliminary, v 0.06

MA816

图 12-6 定时器 2自动加载模式(CEN=0)

SYSCLK

12

SYSCLK

T2MOD.T2X12=0

T2M OD.T2 X1 2= 1

T2 Pin

T2EX Pin

Transition

Detection

C/T2=0

C/T2=1

TR2

EXEN2

Reload

TL2

(8 Bits)

TH2

(8 Bits)

RCAP2HRCAP2L

Overflow

TF2

Timer2 Interrupt

EXF2

图 12-7 示 DCEN=1,使能定时器 2 向上或向下计数。这种模式下允许 T2EX 引脚控制计数方向。当 T2EX 的引脚

为逻辑 1 时定时器 2 向上计数。定时器 2 在 0FFFFH 时溢出并置位 TF2 标志位,如果中断使能将产生中断。溢出也将

引起 RCAP2L 和 RCAP2H 的 16 位值加载到定时器的寄存器 TL2 和 TH2。当 T2EX 的引脚为逻辑 0 时定时器 2 向下

计数。当 TL2 和 TH2 和存储在 RCAP2L 和 RCAP2H 的值相等时将产生下溢。下溢将置位 TF2 标志位并将 0FFFFH

加载到定时器的寄存器 TL2 和 TH2。

当定时器 2 下溢或上溢时外部标志位 EXF2 将被触发。如果需要 EXF2 可作为 17 位分辨率。EXF2 标志位在这

个模式下不会产生中断。

图 12-7 定时器 2自动加载模式(CEN=1)

SYSCLK

ℵ 12

SYSCLK

T2MOD.T2X12=0

T2MOD.T2X1 2=1

T2 Pin

C/T 2= 0

C/T 2= 1

TR2

(Down Counting Reload Value)

FFHFFH

TL2

(8 Bits)

(Up Counting Reload Value)

TH2

(8 Bits)

RCAP2HRCAP2L

Overflow

Count Direction

1 = UP

0 = DOWN

T2EX Pin

Toggle

TF2

EXF2

Timer2 Interrupt

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 41/79

Page 42

Preliminary, v 0.06

MA816

12.2.3. 波特率发生器模式 (BRG)

T2CON 寄存器的 RCLK 和或 RCLK 位允许串行口发送和接收波特率既可源自定时器 1 或定时器 2。当 TCLK=0

时,定时器 1 作为串行口传送波特率发生器。当 TCLK=1,定时器 2 作为串行口传送波特率发生器。RCLK 对串行口

接收波特率有相同的功能。有了这两位,串行口可能有不同的接收和发送波特率,一个通过定时器 1 来产生,另一个

通过定时器 2 来产生。

图 12-8 所示定时器 2 在波特率发生器模式。波特率发生器模式像自动加载模式,翻转时将把寄存器 RCAP2H 和

RCAP2L 的值加载到定时器 2 的寄存器,RCAP2H 和 RCAP2L 的值由软件预置。

模式 1 和 3 的波特率由定时器 2 的溢出速率决定

波特率和模式模式 =

2时31溢出速率器定

16

定时器既可配置为“定时器”或“计数器”工作方式。在许多应用场合,配置成“定时器”工作方式(C/T2=0)。当定时器 2

作为波特率发生器时定时器操作是不同的。

通常,作为一个定时器将在 1/12 的系统时钟频率加 1。作为一个波特率发生器,系统时钟频率的 1/2 加 1。波特

率计算公式如下:

LRCAPHRCAPx

16

]2,2[65536(2

Timer 1

Overflow

1

31 x

=的波特率和模式模式

Fosc

−

这里:Fosc 是系统时钟。RCAP2H,RCAP2L 的内容为一个 16 位的无符号数,可由如下计算出:

LRCAPHRCAP

65536]2,2[ −=

32

Fosc

波特率x

定时器 2 作为一个波特率发生器模式如图 12-8 所示,只有在 T2CON 寄存器的位 RCLK 和/或 TCLK=1 为 1 时有

效。注意 TH2 翻转不会置位 TF2,也不会产生中断。因而,当定进器 2 在波特率发生器模式时定时器中断不需要禁止。

如果 EXEN2(T2 外部中断使能位)置位,T2EX(定时器/计数器 2 触发输入)的负跳变将置位 EXF2(T2 外部标志位),但

是不会引起从(RCAP2H,RCAP2L)到(TH2,TL2 的)重载。因此,当定时器 2 作为波特率发生器时,如果需要的话,

T2EX 也可以作为传统的外部中断。

当定时器 2 在波特率发生器模式时,不能试着去读 TH2 和 TL2。作为一个波特率发生器,定时器 2 在 1/2 的系统

时钟频率或从 T2 引脚的异步时增 1;在这些条件下,读写操作将会不正确。寄存器 RCAP2 可以读,但是不可以写,

因为写和重载重叠并引起写和/或加载错误。在进入定时器 2 或 RCAP2 寄存器时定时器不可以关闭(清零 TR2)。

图 12-8 定时器 2 波特率发生器模式

ℵ 2

“0"“1"

SMOD1

SYSCLK

T2 Pin

T2EX Pin

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 42/79

ℵ 2

C/T 2 =0

C/T 2 =1

Transition

Detection

TR2

EXEN2

TL2

(8 Bits)

“1"

“1"

“0"

“0"

TH2

(8 Bits)

Reload

RCAP2HRCAP2L

EXF2 Timer2 Interrupt

RCLK

RX Clock

TCLK

TX Clock

Page 43

Preliminary, v 0.06

MA816

12.2.4. 定时器 2 的可编程时钟输出模式

使用定时器 2 的可编程时钟输出模式,则从引脚 T2CKO(P1.0)输出占空比为 50%的时钟周期。

输出频率由系统时钟频率(SYSCLK)和在 RCAP2H 和 RCAP2L 寄存器的加载值来决定,如下公式:

T2 Clock-out Frequency =

这里[RCAP2H,RCAP2L]=RCAP2H 和 RCAP2L 内容产生的一个 16 位无符号数。

定时器 2 的可编程时钟输出模式编程步骤如下:

1. 置位 T2MOD 寄存器的 T2OE 位。

2. 清除 T2CON 寄存器的 C/T2 位。

3. 从公式计算出 16 位加载值并输入到 RCAP2H 和 RCAP2L 寄存器。

4. 在 TH2 和 TL2 输入一个 16 位初始值。可以和重载值相等。

5. 设置 T2CON 的 TR2 控制位开启动定时器。

在时钟输出模式,定时器 2 翻转不会产生中断,这和用作波特率发生器时相似。可同时使用定时器 2 作为一个波

特率发生器和时钟发生器。注意,波特率和时钟输出都由定时器 2 的溢出速率来决定。

注:

(1)

此模式定时器

(2) SYSCLK=12MHz

2

溢出标志

TF2

时,定时器 2可编程输出频率范围为

4 x (65536 – (RCAP2H, RCAP2L))

从来不会被置1。

SYSCLK Frequency

45.7Hz到 3MHz。

12.2.5. 定时器 2 寄存器

T2MOD:

SFR 地址 = 0xC9

SFR 页 = 全部 复位值= XXX0-XX00

T2X12:定时器 2 时钟源选择

0:选择 SYSCLK/12 作为时钟源

1:选择 SYSCLK 作为时钟源

T2OE:定时器 2 时钟输出使能位,置位使能清零禁止。

DCEN:定时器 2 向下计数使能位,置位使能清零禁止。

T2CON:

SFR 地址 = 0xC8

SFR 页 = 0 复位值 = 0000-0000

TF2:定时器 2 溢出标志位,定时器 2 溢出置位且必须通过软件清零。当 RCLK=1 或 TCLK=1 时,TF2 不会被置位。

EXF2:定时器 2 外部标志位,在 EXEN2=1 时,且在 T2EX 上有负跳变时加载或捕获将引起置位。当定时器 2 中断使

能时,EXF2=1 时将引起 CPU 进入定时器 2 中断向量程序。EXF2 必须通过软件清零。EXF2 在向上/向下计数器模式

不会产生中断。

RCLK:接收时钟控制位。置位时,串行口使用定时器 2 溢出脉冲来接收,在模式 1 和模式 3 时。RCLK=0 使用定时

器 1 溢出脉冲来产生接收时钟。

TCLK:传送时钟控制位。置位时,串行口使用定时器 2 溢出脉冲来发送,在模式 1 和模式 3 时。TCLK=0 使用定时器

1 溢出脉冲来产生发送时钟。

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 43/79

定时器/计数器 2模式寄存器

7 6 5 4 3 2 1 0

-- -- -- T2X12 -- -- T2OE DCEN

R R R R/W R R R/W R/W

定时器/计数器 2控制寄存器

7 6 5 4 3 2 1 0

TF2 EXF2 RCLK TCLK EXEN2 TR2 C/T2 CP/RL2

R/W R/W R/W R/W R/W R/W R/W R/W

Page 44

Preliminary, v 0.06

MA816

EXEN2:定时器 2 外部使能位。置位时,如果定时器 2 没有用作串行口时钟,在 T2EX 的负跳变时捕获或加载并作为

结果。

TR2:定时器 2 的启始和停止位。逻辑 1 时启动定时器。

C/T2:定时器或计数器选择。清零时,选择内部定时器。置位时,选择外部事件计数器(下降沿触发)。

CP/RL2:捕获/加载控制位。置位时,如果 EXEN2=1,在 T2EX 的负跳变时将产生捕获。清零时,如果 EXEN2=1,

定时器 2 溢出或 T2EX 上有负跳变时将产生自动加载。当 RCLK=1 或 TCLK=1 时,这一位被忽略并强制加载在定时器

2 溢出时。

定时器 2 运行模式

RCLK + TCLK TR2 CP/-RL2 DCEN T2OE Mode

x x 0 x 0

1 x 1 0 0

0 1 1 0 0

0 0 1 0 0

0 0 1 0

1

0 0 1 0

定时器关闭

波特率发生器

16位捕获

16位自动加载 (仅向上计数)

16位自动加载(向上计数或向下计数)

1

可编程时钟输出

TL2:

定时器 2寄存器 低

SFR 地址 = 0xCC

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

TL2[7] TL2[6] TL2[5] TL2[4] TL2[3] TL2[2] TL2[1] TL2[0]

R/W R/W R/W R/W R/W R/W R/W R/W

定时器 2寄存器 高

TH2:

SFR 地址 = 0xCD

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

TH2[7] TH2[6] TH2[5] TH2[4] TH2[3] TH2[2] TH2[1] TH2[0]

R/W R/W R/W R/W R/W R/W R/W R/W

RCAP2L:

捕获寄存器 低

定时器

2

SFR 地址 = 0xCA

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

RCAP2L[7] RCAP2L[6] RCAP2L[5] RCAP2L[4] RCAP2L[3] RCAP2L[2] RCAP2L[1] RCAP2L[1]

R/W R/W R/W R/W R/W R/W R/W R/W

RCAP2H:

定时器

2

捕获寄存器 高

SFR 地址 = 0xCB

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

RCAP2H[7] RCAP2H[6] RCAP2H[5] RCAP2H[4] RCAP2H[3] RCAP2H[2] RCAP2H[1] RCAP2H[0]

R/W R/W R/W R/W R/W R/W R/W R/W

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 44/79

Page 45

Preliminary, v 0.06

MA816

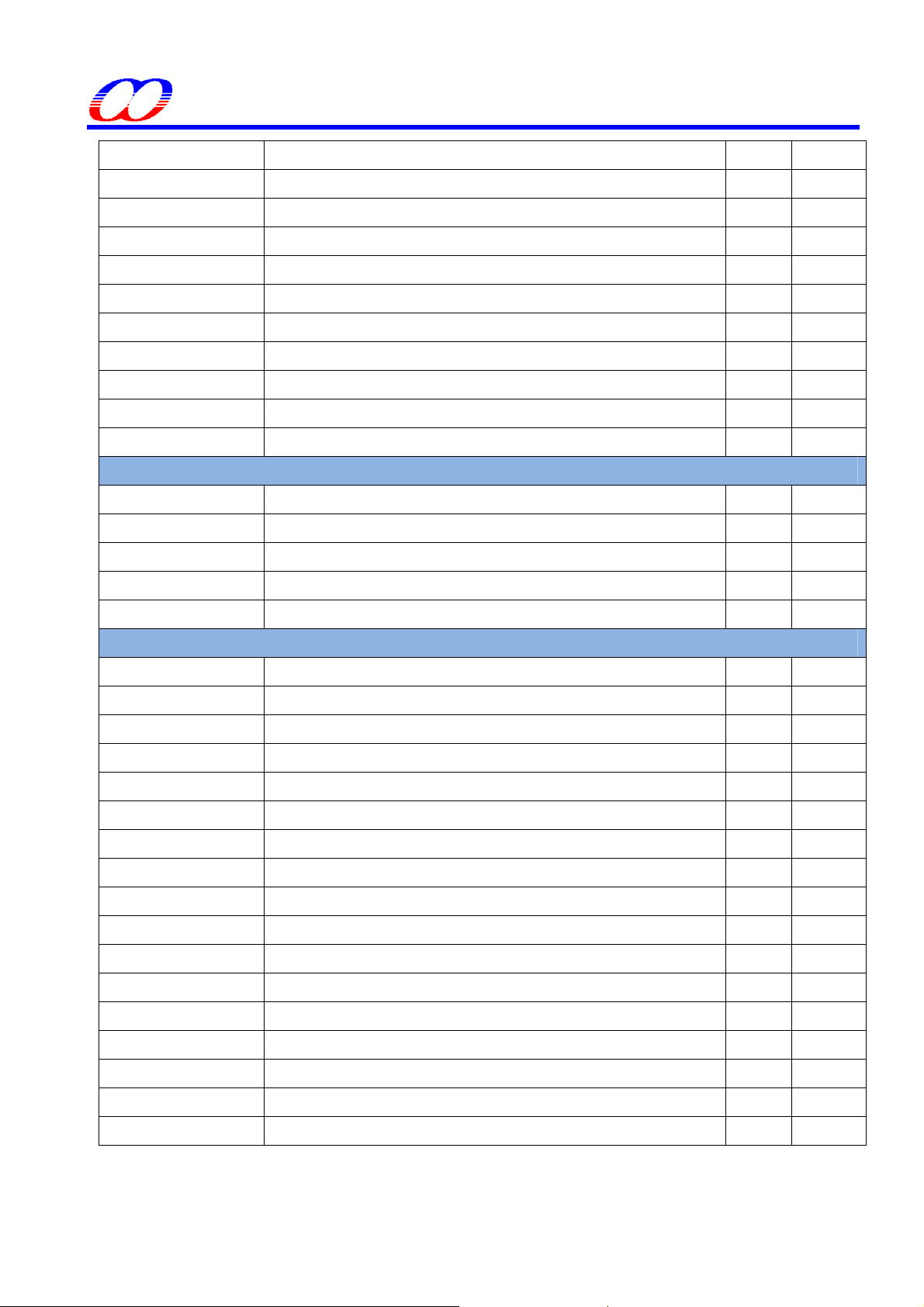

12.3. PWM 定时器

12.3.1. PWM 定时器结构

SYSCLK

IDLE

Pre-Scaler

/1

/2

/4

/8

/16

/32

/64

/128

CCAP0H

CL

8-bit

Down Counter

CIDL POS2 POS1 POS0 CPS2 CPS1 CPS0 ECF

CCAP0L

Toggle

CMOD

PWMEN

PWM out

Toggle P2.0~P2.7

or P 5.0~P5.7

CF CR

PWMEN

interrupt

vector(53H)

CCON

CR

PWM Output P1.x

T

CCAPH

T

= (CCAP0H + 1) x T

CCAPH

T

= (CCAP0L + 1) x T

CCAPL

T

CCAPL

T

CCAPH

SYSTEM_CLOCK

SYSTEM_CLOCK

x Pre-Scaler

x Pre-Scaler

T

CCAPL

T

CCAPH

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 45/79

T

CCAPL

Page 46

Preliminary, v 0.06

MA816

12.3.2. PWM 定时器寄存器

CMOD: PWM

定时器模式寄存器

SFR 地址 = 0xD9

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

CIDL POS2 POS1 POS0 CPS2 CPS1 CPS0 ECF

R/W R/W R/W R/W R/W R/W R/W R/W

Bit 7: CIDL, CPU 空闲模式(IDLE)计数控制

0: IDLE 时 PWM 定时器继续计数

1: IDLE 时 PWM 定时器停止计数

Bit 6~4: POS[2:0], PWM 输出口选择

POS[2:0] PWMEN

0 0 0 1 P2.0 P5.0

0 0 1 1 P2.1 P5.1

0 1 0 1 P2.2 P5.2

0 1 1 1 P2.3 P5.3

1 0 0 1 P2.4 P5.4

1 0 1 1 P2.5 P5.5

1 1 0 1 P2.6 P5.6

1 1 1 1 P2.7 P5.7

X X X 0 Disabled Disabled

Bit 3~1: CPS[2:0], PWM 计数器分频选择

CPS[2:0]

0 0 0 1

0 0 1 2

0 1 0 4

0 1 1 8

1 0 0 16

1 0 1 32

1 1 0 64

1 1 1 128

Bit 0: ECF, 使能 PWM 定时器向下溢出时中断

0: 禁止 CCON.CF 位产生中断

1: 使能 CCON.CF 位产生中断

CCON: PWM

定时器控制寄存器

SFR 地址 = 0xD8

SFR 页 = 0 复位值 = 00XX-0XXX

7 6 5 4 3 2 1 0

CF CR - - PWMEN - - -

R/W R/W R R R/W R R R

Bit 7: CF, PWM 定时器下溢出标志

0: 只能通过软件清 0

1: 当 PWM 计数器向下溢出时硬件置 1。若 EMOD.ECF=1 时,将产生一个中断请求。可以由硬件或软件置 1。

Bit 6: CR, PWM 定时器启动控制位

0: 停止

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 46/79

PWM 输出口

(AUXR1.P5PWM=0)

PWM 输出口

(AUXR1.P5PWM=1)

分频

Page 47

Preliminary, v 0.06

MA816

1: 启动

Bit 5~4: 保留.

Bit 3: PWMEN, PWM 输出使能

0: 禁止在选定的 I/O 口上输出 PWM

1: 使能在选定的 I/O 口上输出 PWM

Bit 2~0: 保留.

CACP0L: PWM

占空比寄存器 低

SFR 地址 = 0xEA

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

CACP0L[7] CACP0L[6] CACP0L[5] CACP0L[4] CACP0L[4] CACP0L[2] CACP0L[1] CACP0L[0]

R/W R/W R/W R/W R/W R/W R/W R/W

CACP0H: PWM

占空比寄存器 高

SFR 地址 = 0xFA

SFR 页 = 全部 复位值 = 0000-0000

7 6 5 4 3 2 1 0

CACP0H[7] CACP0H[6] CACP0H[5] CACP0H[4] CACP0H[4] CACP0H[2] CACP0H[1] CACP0H[0]

R/W R/W R/W R/W R/W R/W R/W R/W

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 47/79

Page 48

Preliminary, v 0.06

MA816

13. 串行口 (UART)

MA816 支持一个全双工的串行口,意思是可以同时发送和接收数据。它有一个接收缓冲,意味着在前一个接收到

的字节没有从寄存器读出前,就可以开始接收第二个字节。但是,如果第一个字节在第二个字节接收完成前仍然没有

被读出,则其中的一个字节将会丢失。串行口的接收和发送寄存器都通过特殊寄存器 SBUF 来访问。写到 SBUF 加

载到传送寄存器,当从 SBUF 读时是一个物理上独立分离的接收寄存器。

串行口可以工作在四种模式:模式 0 提供同步通讯同时模式 1、2 和模式 3 提供异步通讯。异步通讯作为一个

全双工的通用异步收发器(UART),可以同时发送和接收并使用不同的波特率。

模式 0:8 位数据(低位先出)通过 RXD(P3.0)传送和接收。TXD(P3.1)总是作为输出移位时钟。波特率可通过 AUXR2.

URM0X6 选择为系统时钟频率的 1/12 或 1/2。

模式 1:10 位通过 TXD 传送或通过 RXD 接收,数据帧包括一个起始位(0),8 个数据位(低位优先),和一个停止位

(1)。在接收时,停止位进入到专用寄存器(SCON)的 RB8。波特率是可变的。

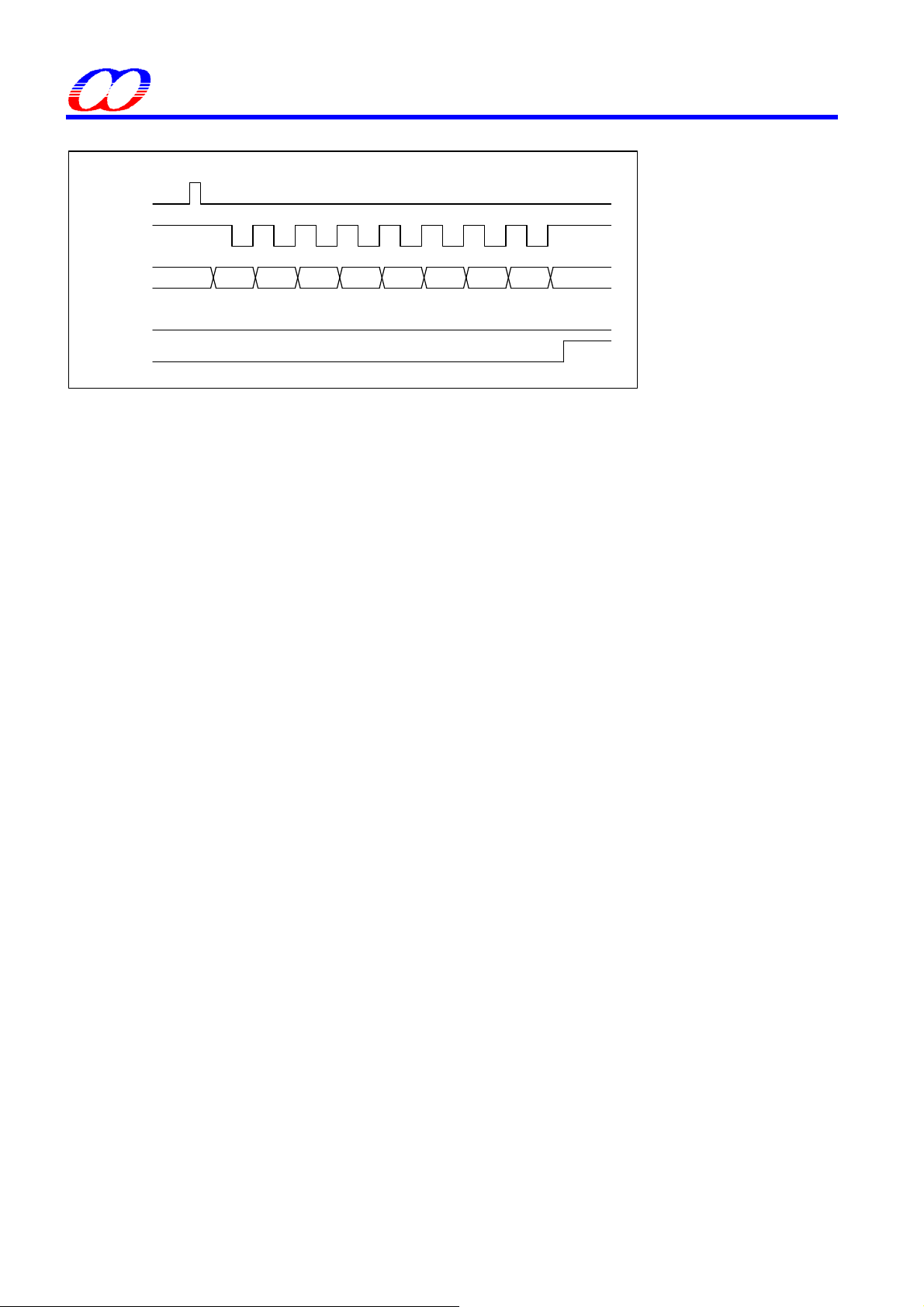

图 133-1 模式 1 数据帧

Mode 1

Start D0 Stop

D1 D2 D3 D4 D5 D6 D7

8-bit data

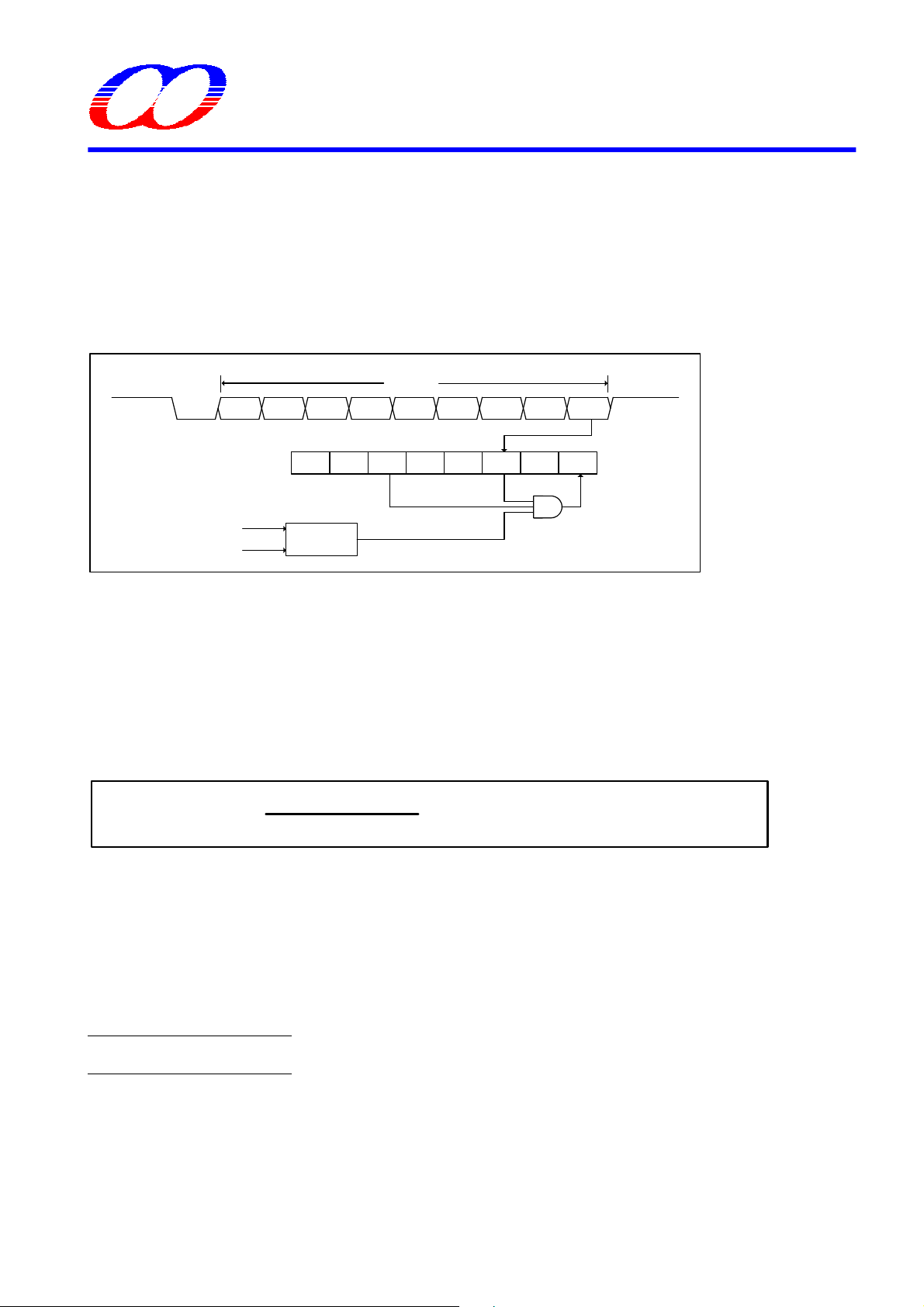

模式 2:11 位通过 TXD 传送或通过 RXD 接收,数据帧包括一个起始位(0),8 个数据位(低位优先),一个可编程的

第九个数据位和一个停止位(1)。在传送时,第 9 个数据位(TB8 在 SCON 寄存器)可以分配为 0 或者 1。例如,奇

偶检验位(P,在 PSW 寄存器)可以移到 TB8 中。在接收时,第九个数据位到 SCON 寄存器中的 RB8,同时忽略停

止位。波特率可以配置为 1/32 或 1/64 的系统时钟频率。也就是 Fosc/64 或 Fosc/32。

图 133-2 模式 2 数据帧

Mode 2, 3

Start D0

D1 D2 D3 D4 D5 D6

9-bit data

D8D7

Stop

模式 3:11 位通过 TXD 传送或通过 RXD 接收,起始位(0),8 个数据位(低位优先),一个可编程的第九个数据位和

一个停止位(1)。实际上,模式 3 和模式 2 除了波特率不相同之外其它的都相同。模式 3 的波特率是可变的。

在四种模式中,使用 SBUF 作为一个目的寄存器,可以通过任何指令发起传输。在模式 0,当 RI=0 且 REN=1

时启动接收。在其它模式,在 REN=1 时,收到起始位时启动接收。

除了标准操作外,UART 还能具有侦察丢失停止位的帧错误和自动地址识别的功能。

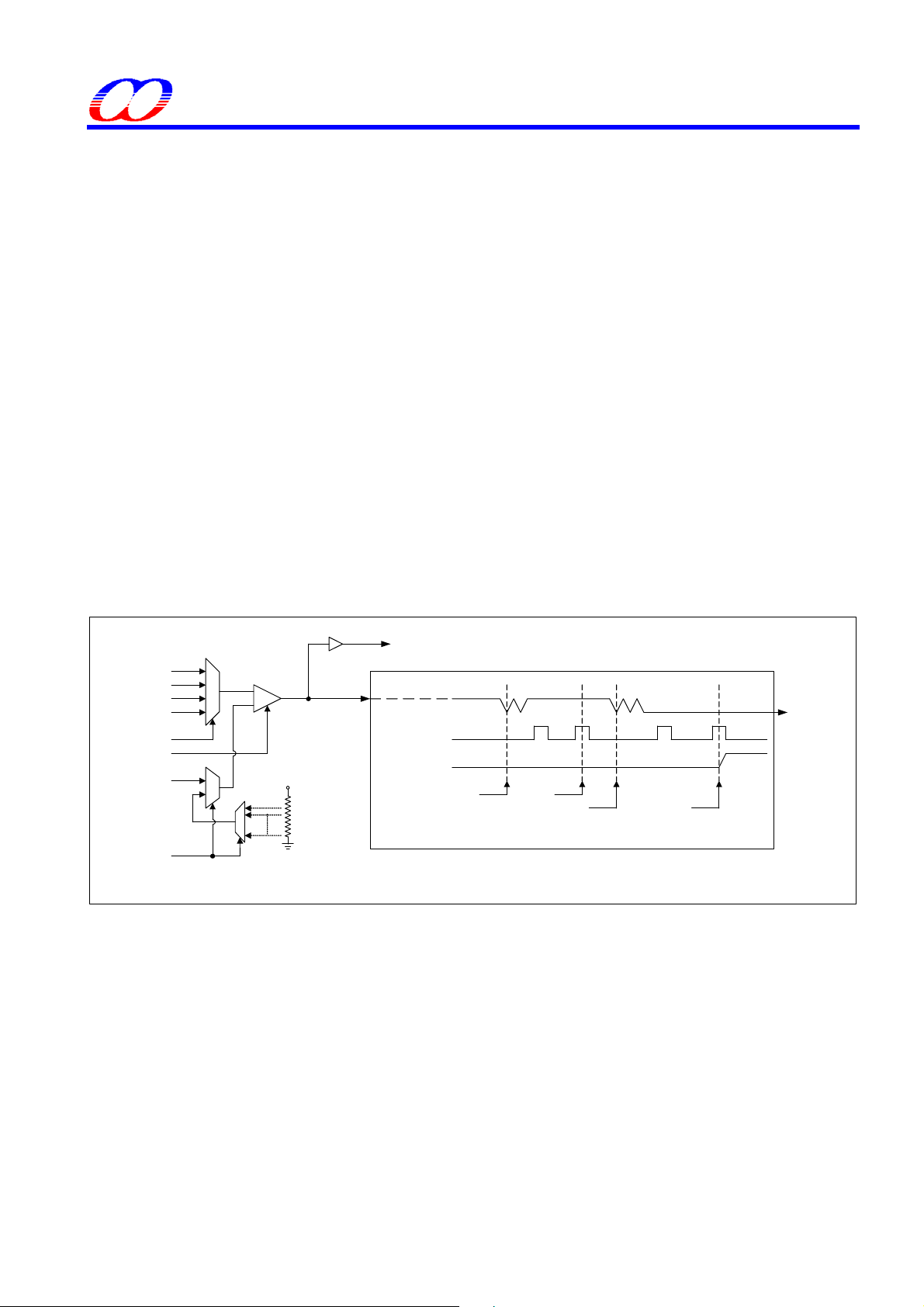

13.1. 模式 0 详述

串行数据通过 RXD 读入和输出,TXD 输出移位时钟。接收和发送 8 位数据:8 个数据位(低位优先)。波特率

可选择为系统时钟的 1/12 或 1/2。图 133-3 显示了串口模式 0 的简化功能框图。

使用 SBUF 作为一个目的寄存器可通过任何指令来启动传输。“写到 SBUF”信号触发 UART 引擎开始发送。SBUF

里面的数据在 TXD(P3.1)脚的每一个上升沿移出到 RXD(P3.0)脚。八个上升沿移位时钟过后,硬件置 TI 为 1 标

志发送完成。见图 133-4。

当 REN=1 和 RI=0 时接收启动。在下一个指令周期,RX 控制单元写 11111110 到接收移位寄存器,且在下一

个时钟相位激活接收。

This document information is the intellectual property of Megawin Technology.

© Megawin Technology Co., Ltd. 2009 All rights reserved.

QP-7300-03D 48/79

Page 49

Preliminary, v 0.06

MA816

接收使能移位时钟选择输出功能 P3.1 引脚。当接收激活时,在移位时钟的下降沿采样 RXD(P3.0)脚并移到寄

存中。八个下降沿移位时钟过后,硬件置 RI 为 1 标志接收完成。见图 133-5。

图 133-3 串口模式 0

SYSCLK

80C51 Int ernal BUS

2

12

“0"“1"

REN

__

RI

AUXR2.URM0X6

图 133-4 模式 0 发送波型

TX Clock

RX Clock

RXSTART

Write

SBUF

Read

SBUF

UART engine

80C51 Internal BUS

RXD Alternated