2kb SPI EEPROM with PIO, RTC,

DS28DG02

Reset, Battery Monitor, and Watchdog

www.maxim-ic.com

GENERAL DESCRIPTION

The DS28DG02 combines 2kb (256 x 8) EEPROM

with 12 PIO lines, a real-time clock (RTC) and

calendar with alarm function, a CPU reset monitor, a

battery monitor, and a watchdog. Communication

with the device is accomplished with an industrystandard SPI™ interface. The user EEPROM is

organized as four blocks of 64 bytes each with

single-byte and up to 16-byte page write capability.

Additional registers provide access to PIOs and to

setup functions. Individual PIO lines can be

configured as inputs or outputs. The power-on state

of PIOs programmed as outputs is stored in

nonvolatile (NV) memory. All PIOs may be

reconfigured by the user through the serial interface.

The RTC/calendar operates in the 12/24-hour format

and automatically corrects for leap years. Battery

monitor threshold and watchdog timeout are userprogrammable through NV registers. The reset

monitor generates a reset to the CPU if the voltage at

the V

output includes a debounce circuit for manual

pushbutton reset.

pin falls below the factory-set limit. The reset

CC

APPLICATIONS

Asset-Tracking Systems

Broadband Access Network Equipment

Patient-Monitoring Systems

Home Lighting Control Systems

Holter Heart Monitors

Typical Operating Circuit appears on page 32.

Pin Configuration appears on page 33.

ORDERING INFORMATION

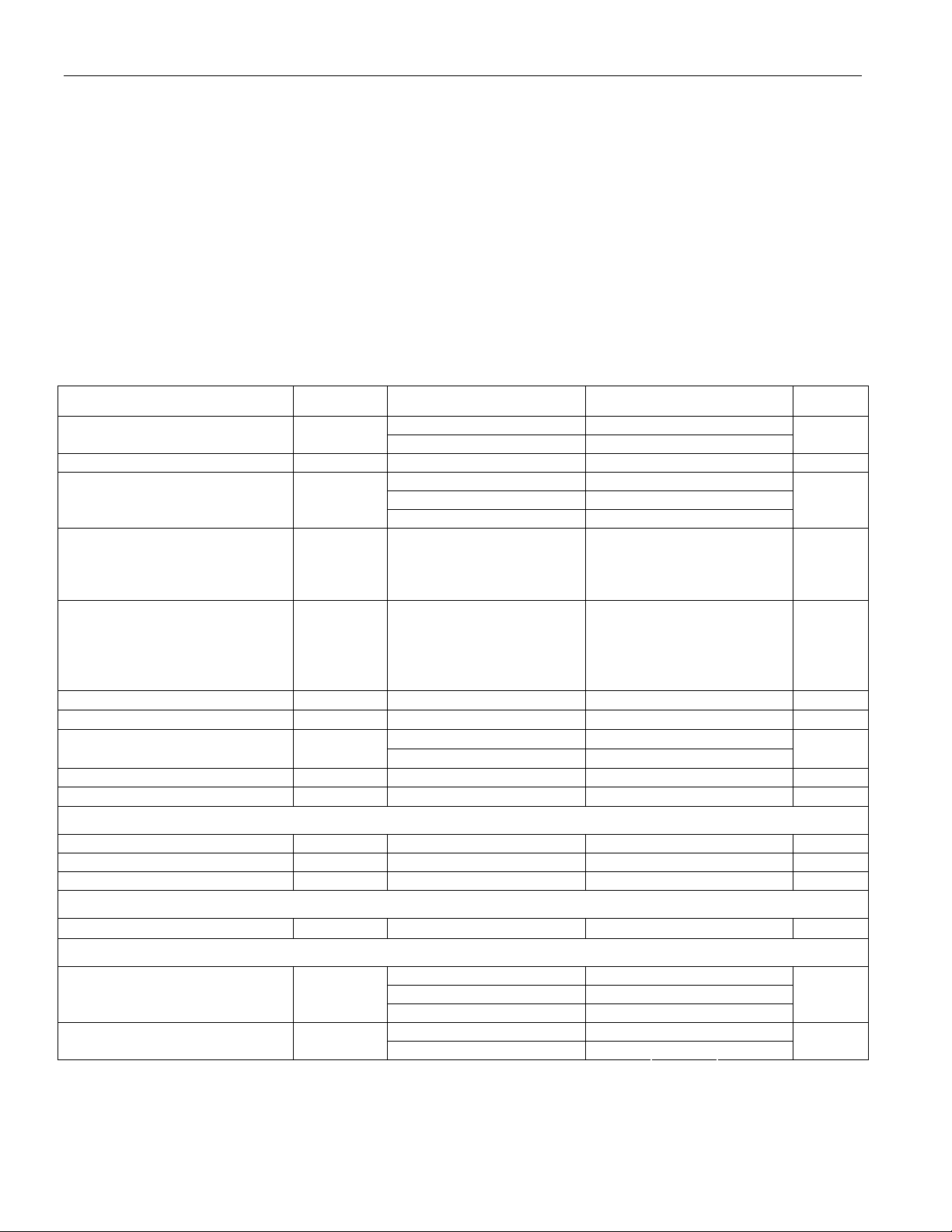

PART TEMP RANGE VCC TRIP PIN-PACKAGE PKG CODE

DS28DG02E-3C+ -40°C to +85°C 3.3V -5% 28 TSSOP-EP* (4.4mm) U28E+5

DS28DG02E-3C+T -40°C to +85°C 3.3V -5% 28 TSSOP-EP* T&R U28E+5

DS28DG02G-3C+ -40°C to +85°C 3.3V -5% 36 TQFN-EP* (6mm × 6mm) T3666+3

DS28DG02G-3C+T -40°C to +85°C 3.3V -5% 36 TQFN-EP* T&R T3666+3

*EP = Exposed Paddle.

+ Denotes lead-free/RoHS compliant device.

For additional VCC monitor trip points or other device options, contact the factory.

Note: Registers are capitalized for clarity.

SPI is a trademark of Motorola, Inc.

FEATURES

2kb (256 x 8) EEPROM Organized in Four

64-Byte Blocks

Single Byte and Up to 16-Byte EEPROM Write

Sequences

EEPROM Write-Protect Control Pin Protects

1, 2, or All 4 Blocks

Endurance 200k Cycles per Page at +25°C;

10ms (max) EEPROM Write Cycle

SPI Serial Interface Supporting Modes (0,0)

and (1,1) at Up to 2MHz Clock Frequency

12 PIO Lines with LED Drive Capability

Each PIO is Configured to Input or Output,

Open-Drain/Push-Pull on Startup by Stored

Value

All PIOs are Reconfigurable After Startup

RTC/Calendar/Alarm with BCD Format and

Leap-Year Compensation

RTC Controlled Through 32.768kHz, 12.5pF

Crystal or External TCXO

CPU Reset Through Fast-Response Precision

Monitor with Hysteresis or Pushbutton

V

CC

Battery Monitor 2.5V, 2.25V, 2.0V, 1.75V, -5%

Watchdog Timer 1.6s, 0.8s, 0.4s, 0.2s (typ)

Unique Factory-Programmed 64-Bit Device

Registration Number

Operating Range: 2.2V to 5.25V,

-40°C to +85°C

±4kV IEC 1000-4-2 ESD Protection Level

(Except Crystal Pins)

Available in 28-Lead, 4.4mm TSSOP or

36-Lead 6mm × 6mm QFN Package

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device

may be simultaneously available through various sales channels. For information about device errata, click here: www.maxim-ic.com/errata

1 of 33

REV: 061907

.

DS28DG02: 2kb SPI EEPROM with PIO, RTC, Reset, Battery Monitor, and Watchdog

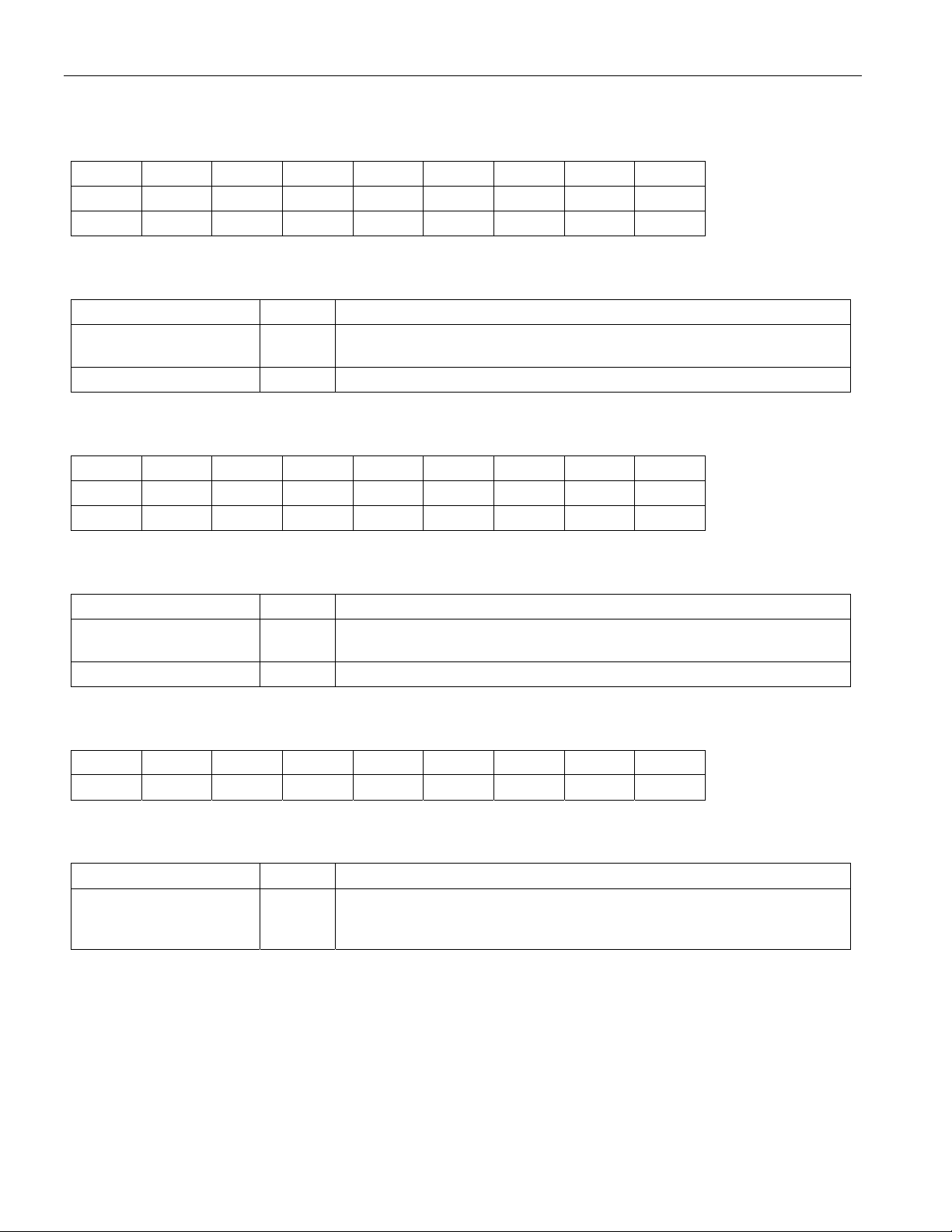

ABSOLUTE MAXIMUM RATINGS

Voltage Range on Any Pin Relative to Ground -0.5V, +6V

Maximum Current SO, ALMZ, RSTZ, WDOZ Pins

Maximum Current Each PIO Pin

Maximum GND and V

Current 270mA

CC

Operating Temperature Range

Junction Temperature

+150°C

Storage Temperature Range

Soldering Temperature

See IPC/JEDEC J-STD-020

-40°C to +85°C

-55°C to +125°C

±20mA

±50mA

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only,

and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is

not implied. Exposure to the absolute maximum rating conditions for extended periods may affect device.

ELECTRICAL CHARACTERISTICS

(TA = -40°C to +85°C.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Supply Voltage VCC

Battery Voltage V

Battery Current (V

= 3.0V,

BAT

Note 1)

Standby Current (Note 2) I

Operating Current I

Programming Current I

VCC Monitor Trip Point V

VCC Monitor Trip-Point

Tolerance

VCC Monitor Hysteresis V

Power-Up Wait Time t

I

BAT

CCS

CCA

PROG

V

TRIPTOL

HYST

POIP

BAT

TRIP

EEPROM

Programming Time t

Endurance N

Data Retention t

PROG

CYCLE

RET

REAL-TIME CLOCK

Frequency Deviation

Δ

F

PIO PINS (See Figures 21, 22, 23)

LOW-Level Output Current at

= 0.5V (Note 8)

V

OL

(Note 8)

I

OL

I

OH

Battery monitor off 2.2 5.25

Battery monitor enabled 2.7 5.25

V

(Note 1) 1.5 3.0 VCC V

RTC oscillator off 2

RTC oscillator on 0.4 10

µA

RTC oscillator on, +25°C 4.7

SPI idle, ALMZ, WDOZ,

RTSZ high, V

RTC oscillator on, all

= 5.25V,

CC

60 100 µA

PIOs grounded

Reading EEPROM at 2

Mbps, ALMZ, WDOZ,

RTSZ high, V

= 5.25V,

CC

550 800 µA

RTC oscillator on, all

PIOs grounded

VCC = 5.25V 600 1000 µA

(Note 3) 2.97 3.05 3.14 V

+25°C

-40°C to +85°C -2.5 +2.5

0.4 0.5 0.6 %V

-1.5 +1.5

%V

TRIP

TRIP

60 µs

10 ms

At +25°C (Notes 4, 5) 200k —

At +85°C (Notes 5, 6) 40 years

(Notes 5, 7) -46 +46 PPM

VCC = 2.2V 6 9.5

VCC = 3.3V 12.5 22.0

= 5.25V 19 30

V

CC

VOH = 2.4V, VCC = 3.3V 6.5 11.0 HIGH-Level Output Current

= 4.5V, VCC = 5.25V 12.5 18.0

V

OH

mA

mA

2 of 33

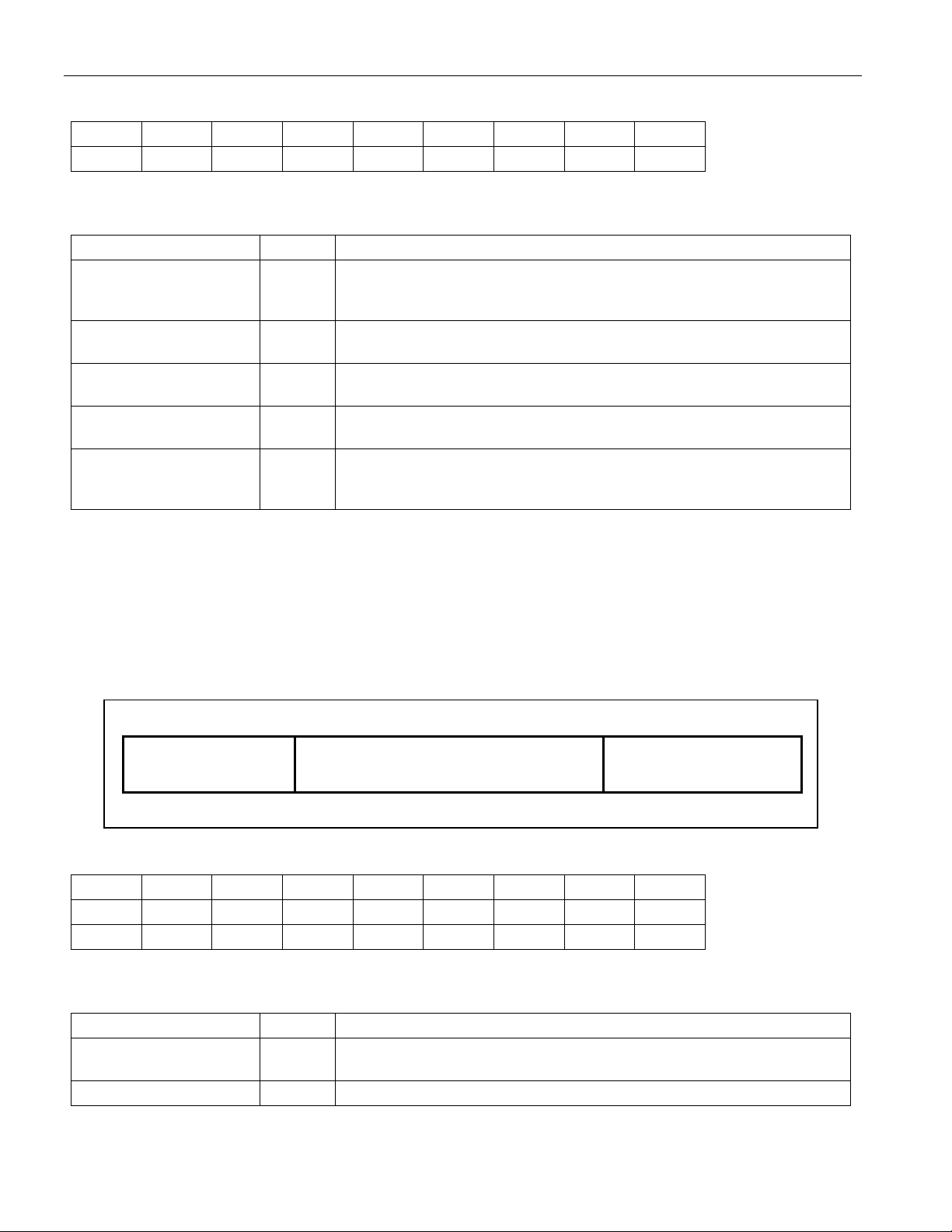

DS28DG02: 2kb SPI EEPROM with PIO, RTC, Reset, Battery Monitor, and Watchdog

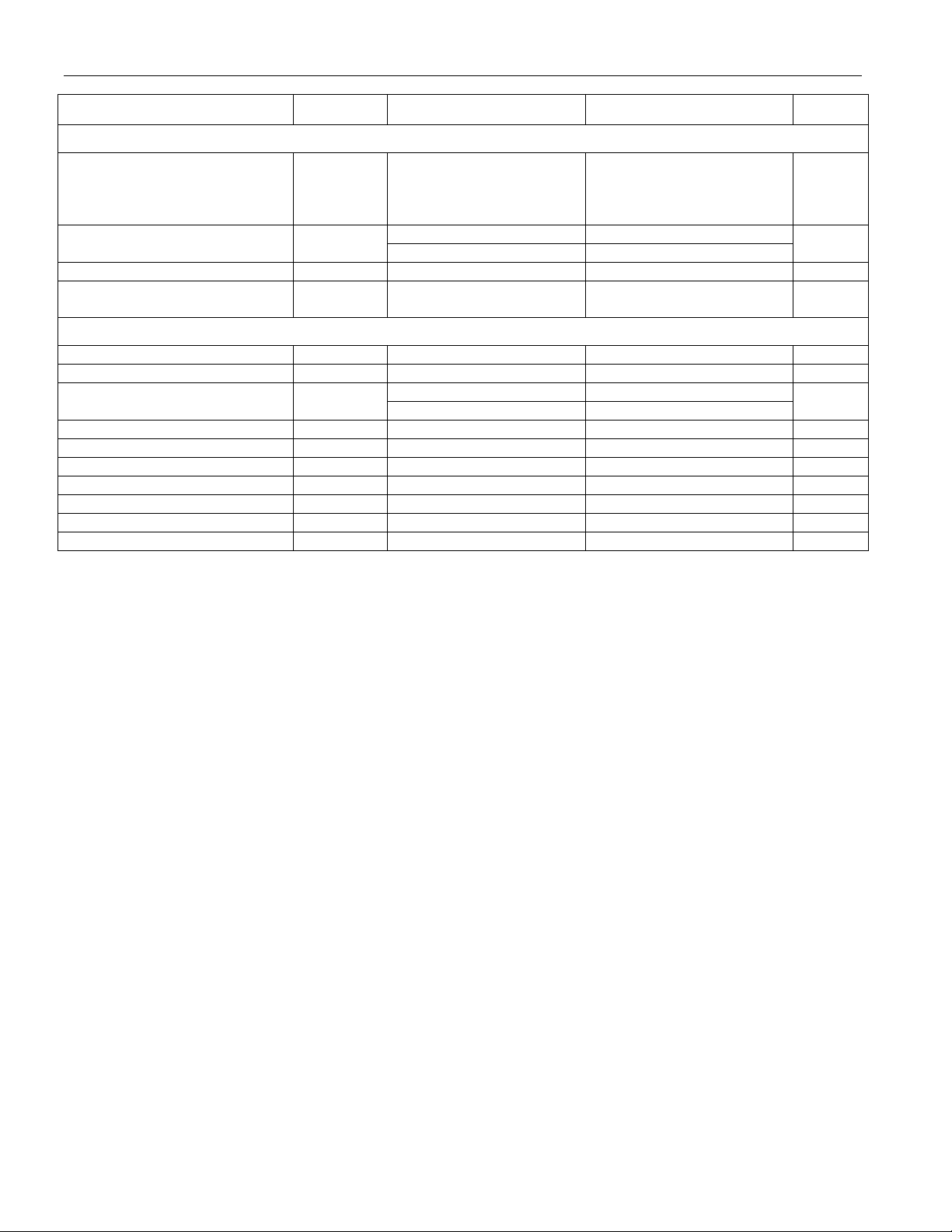

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

LOW-Level Input Voltage VIL 0.8 V

HIGH-Level Input Voltage VIH

Output Transition Time tOT

Power-On Setting Time

t

POS

Low-current mode

(Note 9)

High-current mode

(Note 10)

High-current mode

(Note 11)

0.7 ×

V

CC

1

25

25 µs

V

CC

0.5V

+

V

µs

PIO Read Setup Time tPS (Note 5) 100 ns

PIO Read Hold Time tPH (Note 5) 100 ns

Leakage Current IL

High impedance, at

CCMAX

V

-1 +1 µA

RSTZ PIN (Note 12) (See Figures 6, 7)

LOW-Level Output Voltage VOL At 4mA sink current 0.3 V

LOW-Level Input Voltage VIL

0.3 ×

V

CC

V

Input Leakage Current IL -1 +1 µA

Minimum VCC for Valid RSTZ V

RSTZ Pulse Duration t

Manual Reset Pulse Width t

Manual Reset Release

Threshold

Manual Reset Debounce Time t

RSTZ Delay t

(Notes 5, 13) 2.13 V

POR

176 328 532 ms

RST

1 µs

MPW

V

(Note 14) VIL V

TRMS

t

DEB

V

DEL

falling below V

CC

(Note 15)

TRIP

90 µs

ms

RST

ALMZ, WDOZ PINS

LOW-Level Output Voltage VOL At 4mA sink current 0.3 V

WDI PIN

LOW-Level Input Voltage VIL

HIGH-Level Input Voltage VIH

0.7 ×

V

CC

0.3 ×

V

CC

VCC +

0.5V

V

V

Input Leakage Current IL -1 +1 µA

Minimum Input Pulse Width t

Watchdog Timeout tWD User programmable

1 µs

MPW

0.88

0.44

0.22

0.11

1.64

0.82

0.41

0.20

2.66

1.33

0.67

0.33

s

WPZ, SI, SCK, CSZ PINS

LOW-Level Input Voltage VIL

HIGH-Level Input Voltage VIH

0.7 ×

V

CC

0.3 ×

V

CC

V

+

CC

0.5V

V

V

Input Leakage Current IL -1 +1 µA

SO PIN

LOW-Level Output Voltage VOL

HIGH-Level Output Voltage VOH At 1mA source current

Output Leakage Current IL

At 1mA sink current and

V

CCmin

High impedance, at

V

CCmax

0.2 V

0.7 ×

V

CC

V

-1 +1 µA

3 of 33

DS28DG02: 2kb SPI EEPROM with PIO, RTC, Reset, Battery Monitor, and Watchdog

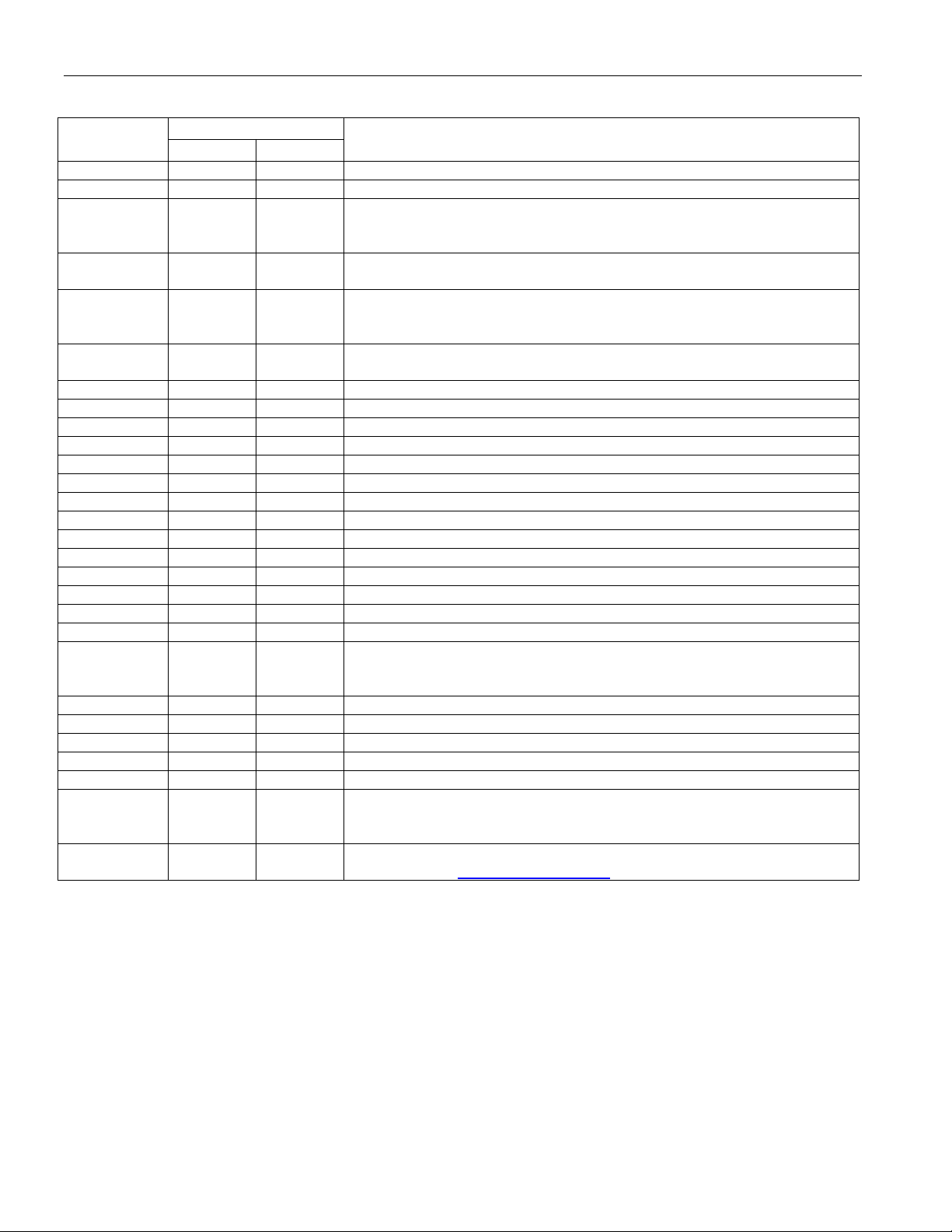

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

BATTERY MONITOR (See Figure 8)

V

Trip Point V

BAT

Monitor Trip-Point

BAT

Tolerance

V

Battery Test Load Current I

Battery Test Duration t

2.25

2.03

1.80

1.58

2 s

BTP

Measured with V

falling; trip point is user

BAT

programmable

+25°C -1.5 +1.5 V

TRIPTOL

LOAD

BTPW

-40°C to +85°C -2.5 +2.5

7.5 20 µA

Load applied to battery

(Notes 5, 16)

2.31

2.08

1.85

1.62

2.38

2.14

1.90

1.66

%V

V

BTP

SPI INTERFACE TIMING (See Figures 9, 10)

CSZ Setup Time t

CSZ Hold Time t

(Note 5)

CSZ to High-Z at SO t

SCK Clock Frequency f

(Note 5) 0.4 µs

CSS

(Note 5) 0.4 µs

CSH

t

CPH

CHZ

CLK

Normal communication 0.25 CSZ Standby Pulse Width

(Note 17) 2.0

µs

0.25 µs

2 MHz

Data Setup Time tDS (Note 5) 50 ns

Data Hold Time tDH (Note 5) 50 ns

SCK Rise Time t

SCK Fall Time t

(Note 5) 1 µs

SCKR

(Note 5) 1 µs

SCKF

Output Valid time tV (Note 5) 0 120 ns

Note 1:

Note 2:

Note 3:

Note 4:

Note 5:

Note 6:

Note 7:

Note 8:

Note 9:

Note 10:

Note 11:

Note 12:

Note 13:

Note 14:

Note 15:

Note 16:

Note 17:

If no battery is used, connect the V

To the first order, this current is independent of the supply voltage value.

Nominal values: 3.3V -5%, set at factory. Measured with V

V

TRIP

+ V

HYST

.

This specification is valid for each 16-byte memory page.

Not production tested. Either guaranteed by design (GBD) or guaranteed by a reliability study (EEPROM lifetime

parameters).

EEPROM writes can become nonfunctional after the data-retention time is exceeded. Long-time storage at

elevated temperatures is not recommended; the device can lose its write capability after 10 years at +125°C or 40

years at +85°C.

Valid with 32KHz crystal, 12.5pF, ESR ≤ 45kΩ, +25°C.

Total PIO sink and source currents through all PIO pins must be externally limited to less than the absolute

maximum rating of 270mA minus 1.5mA for EEPROM programming and SPI communication. Exceeding the

absolute maximum rating can cause damage.

Assumes the configuration of the system and the part is such that changing GOV<i> (0 ≤ i ≤ 11) between ‘b1 and

‘b0 switches between sourcing no current and sinking the absolute maximum current at the PIO<i> pin. The limit

refers to the switching time between sinking 20% of the DC current and 80% of the DC current. The same is true

for changing between 'b0 and 'b1 causing the part to switch from sinking no current to sourcing the absolute

maximum current at the PIO<i> pin.

Each output pin transitions in 1µs with a pause of 1µs before the next pin transitions.

All PIO are tri-stated at beginning of reset prior to setting to power-on values.

If the part has battery power (normal case) the active pulldown of RSTZ is supported by the battery.

is tied to VCC (no battery supply) the state of the RSTZ pulldown transistor is not guaranteed when VCC falls

If V

BAT

below V

POR

.

Threshold refers to the manual reset function obtained by forcing RSTZ low.

Transient response to a step on V

are guaranteed to be suppressed, regardless of their amplitude. Glitches on VCC that are longer than t

t

DELmin

are guaranteed not to be suppressed. This parameter is tested at high V

If enabled, this test takes place every hour on the hour. The battery voltage is compared to V

half of the t

window. The timing is controlled by the RTC.

BTPW

Extended duration applies to the following cases:

1) Aborted WREN, WRDI, RDSR, and WRSR command.

2) WRITE command aborted before transmitting the first complete data byte after command and address.

3) READ command aborted before reading the first complete data byte after command and address.

4) Read aborted before the end of a byte.

pin to VCC. The RTC is powered by V

BAT

falling; for VCC rising, the actual threshold is

CC

from above V

CC

down to (V

TRIP

TRIP

if VCC falls below V

BAT

CCmin

.

- 1mV). Glitches on VCC that are shorter than

and guaranteed by design at low.

CC

during the second

BTP

DELmax

4 of 33

DS28DG02: 2kb SPI EEPROM with PIO, RTC, Reset, Battery Monitor, and Watchdog

PIN DESCRIPTION

NAME

TSSOP28 TQFN36

X1 1 33

X2 2 34

RSTZ 3 36

WDI 4 2

WDOZ 5 3

WPZ 6 4

PIO0 7 5

PIO4 8 6

PIO8 9 7

GND 10, 19 9, 19

PIO10 11 10

PIO6 12 11

PIO2 13 12

VCC 14, 15 13, 15

PIO3 16 16

PIO7 17 17

PIO11 18 18

PIO9 20 21

PIO5 21 22

PIO1 22 23

ALMZ 23 24

SO 24 25

SI 25 26

SCK 26 28

CSZ 27 30

V

28 31 Backup Battery Supply for RTC and RSTZ support.

BAT

N.C. —

GND EP EP

PIN

1, 8, 14,

20, 27,

29, 32, 35

FUNCTION

32.768kHz Crystal Connection 1 or 32.768kHz Input from TCXO

32.768kHz Crystal Connection 2

Open-Drain Output Pin (Active Low) for V

power-fail reset,

CC

watchdog alarm, and Manual Reset Input. See Multifunction

Control/Setup Register description for more information.

Watchdog Input Pin (Active High). See Multifunction Control/Setup

Register description at address 134h for more information.

Open-Drain Output Pin (Active Low) for (user-choice) watchdog

alarm. See Multifunction Control/Setup Register description for more

information.

Hardware Write-Protect Input Pin (Active Low). See the SPI Interface

description for more information.

PIO Line #0

PIO Line #4

PIO Line #8

Ground Supply

PIO Line #10

PIO Line #6

PIO Line #2

Power Supply Input

PIO Line #3

PIO Line #7

PIO Line #11

PIO Line #9

PIO Line #5

PIO Line #1

Open-Drain Output Pin (Active Low) for RTC, battery monitor, and

(user-choice) watchdog alarms. See the Multifunction Control/Setup

Register description for more information.

SPI Serial Data Output (tristate)

SPI Serial Data Input

SPI Serial Clock Input

Chip Select Input (Active Low)

No Connection

Exposed Paddle. Solder evenly to the board’s ground plane for proper

operation. See

Application Note 3273 for additional information.

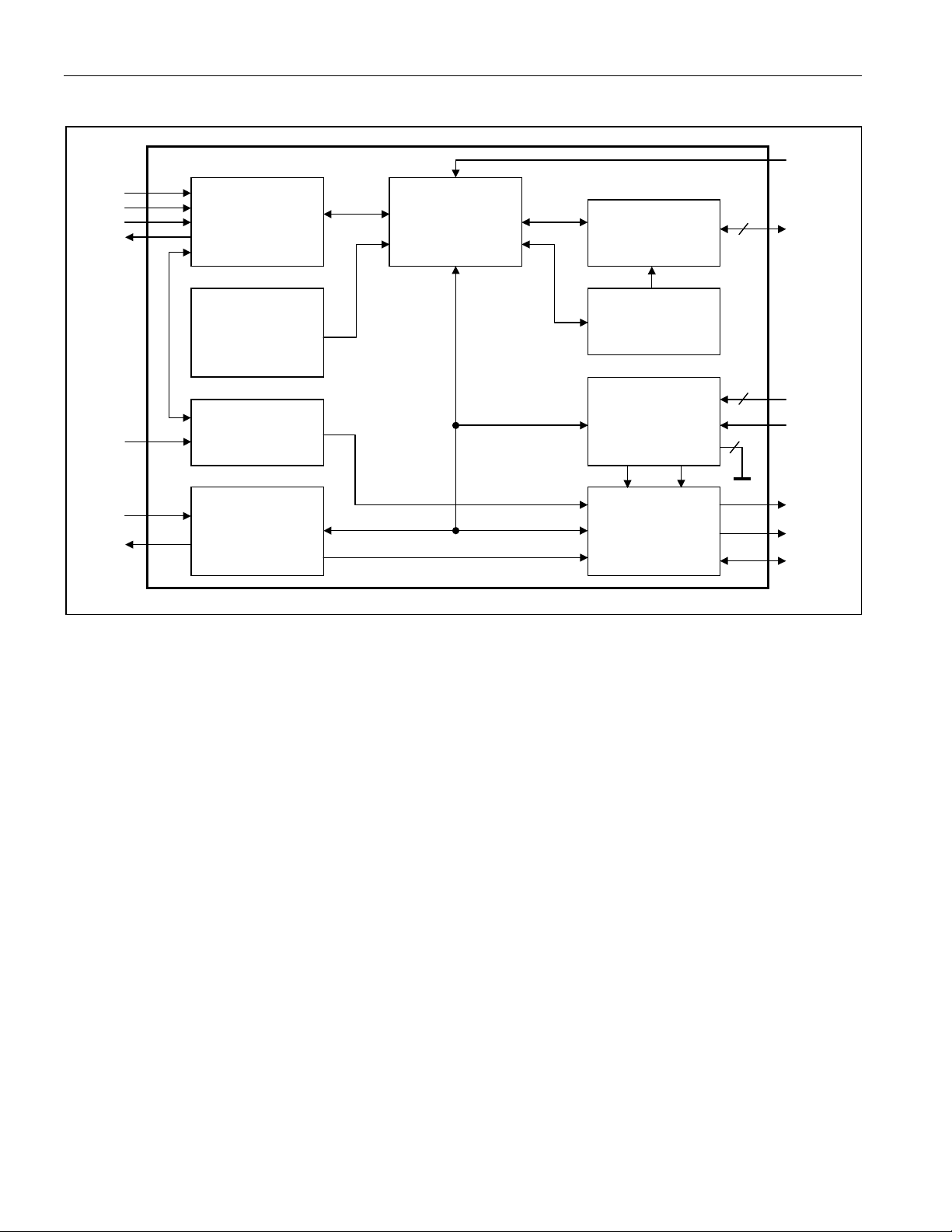

OVERVIEW

The DS28DG02 features 2kb of EEPROM, 12 bidirectional PIO channels, an RTC with calendar and alarm

function, a watchdog timer, two voltage monitors with precision trip points, and three alarm/reset outputs. Each

DS28DG02 has its own unique registration number, which serves as identification of the product the device is

embedded in. All these resources are accessed through a serial SPI interface, as shown in the block diagram in

Figure 1. The SPI interface automatically adjusts to SPI modes (0,0) and (1,1). The V

the power-fail reset output (RSTZ pin), is set at the factory. The user can set the battery monitor threshold and the

watchdog time-out through software. The RTC uses the common BCD format for time, calendar and day of the

week. The device can be programmed to generate an RTC alarm every second, minute, hour, or day and once a

week or once a month at a user-defined time. RTC, watchdog, and battery alarm can be individually enabled.

trip point, which controls

CC

5 of 33

DS28DG02: 2kb SPI EEPROM with PIO, RTC, Reset, Battery Monitor, and Watchdog

K

A

Figure 1. Block Diagram

WPZ

CSZ

SC

SI

SO

SPI

Communication

Interface

64-bit Unique

Registration

Memory

Function Buffer

and Control

PIO Function

Control

2kb

EEPROM Array

12

PIOn

Number

WDI

X1

X2

Watchdog

Timer

Real-Time

Clock, Calendar

and RTC Alarm

WDA

CLKA

2

Voltage Monitors

and Power

Distribution

BATA VCLA

2

Alarm Control

Logic, RSTZ

Debounce

V

CC

V

BAT

GND

LMZ

WDOZ

RSTZ

The PIO configuration and setup of RTC/calendar with alarm are part of the Detailed Register Description. This

section also includes specifics of the Multifunction Control/Setup register, which enables/disables several device

functions, and the Alarm/Status register. For detailed information on the operation of the V

monitor/power-fail

CC

reset and the battery monitor see the Monitoring Functions section. The SPI Interface description explains the

communication protocol for memory and register access and the use of the watchdog function. The PIO

Read/Write Access section illustrates the behavior of the PIOs, in particular the address generation and timing in

low- and high-current mode.

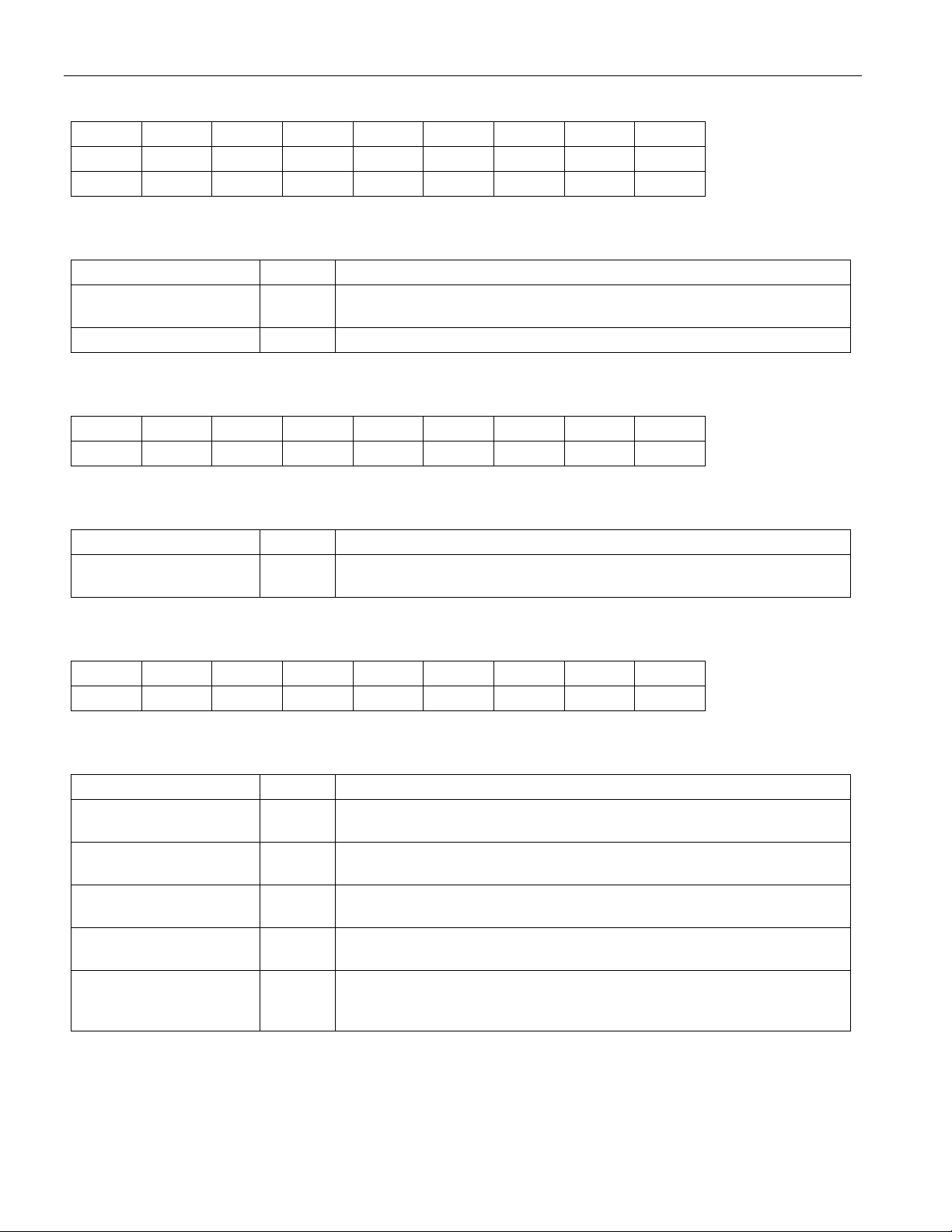

The DS28DG02 memory map (Figure 2) begins with 256 bytes of general-purpose user EEPROM, organized as

four blocks of 64 bytes. Additional EEPROM is set aside to store power-on defaults for PIO state (high, low, in

output mode), data direction (in, out), read-inversion (true, false), port output type (push-pull, open-drain), and

output mode (high current, low current). Once powered up, the PIO settings can be overwritten through SRAM

registers without affecting the power-on defaults. PIO state, direction, and read-inversion can be set for individual

ports. The output type is set for groups of four PIOs and the selected output mode applies to all PIOs in output

mode. The RTC/calendar, associated Alarm registers and the Multifunction Control/Status registers are kept

nonvolatile through battery backup. Write-protection, if enabled, is available for all four EEPROM blocks, blocks 2

and 3 only, or block 3 only and for all writeable registers from address 120h and higher.

6 of 33

DS28DG02: 2kb SPI EEPROM with PIO, RTC, Reset, Battery Monitor, and Watchdog

Figure 2. Memory Map

ADDRESS TYPE ACCESS DESCRIPTION

000h to 03Fh EEPROM R/W User memory block 0.

040h to 07Fh EEPROM R/W User memory block 1.

080h to 0BFh EEPROM R/W User memory block 2.

0C0h to 0FFh EEPROM R/W User memory block 3.

100h to 109h — — Reserved, contents undefined.

10Ah EEPROM R/W Power-on default for PIO output state (PIO0 to PIO7).

10Bh EEPROM R/W Power-on default for PIO output state (PIO8 to PIO11).

10Ch EEPROM R/W Power-on default for PIO direction (PIO0 to PIO7).

10Dh EEPROM R/W Power-on default for PIO direction (PIO8 to PIO11).

10Eh EEPROM R/W Power-on default for PIO read-inversion (PIO0 to PIO7).

Power-on default for PIO read-inversion (PIO8 to PIO11),

10Fh EEPROM R/W

110h to 117h — — Reserved, contents is undefined.

PIO output type (PIO0 to PIO11 in groups of 4 PIOs), PIO

output mode (same mode for all PIOs).

118h to 11Fh ROM R 64-bit unique registration number.

120h SRAM R/W PIO output state (PIO0 to PIO7).

121h SRAM R/W PIO output state (PIO8 to PIO11).

122h SRAM R/W PIO direction (PIO0 to PIO7).

123h SRAM R/W PIO direction (PIO8 to PIO11).

124h SRAM R/W PIO read-inversion (PIO0 to PIO7).

PIO read-inversion (PIO8 to PIO11), PIO output type (PIO0

125h SRAM R/W

126h — R PIO read access (PIO0 to PIO7).

127h — R PIO read access (PIO8 to PIO11).

128h — — Reserved, contents undefined.

129h to 12Fh NV SRAM R/W RTC and calendar.

130h to 133h NV SRAM R/W RTC alarm.

134h NV SRAM R/W Multifunction control/setup register.

135h NV SRAM R/Clear Alarm and status register.

136h and above — — Reserved, contents undefined.

to PIO11 in groups of 4 PIOs), PIO output mode (same

mode for all PIOs).

7 of 33

DS28DG02: 2kb SPI EEPROM with PIO, RTC, Reset, Battery Monitor, and Watchdog

DETAILED REGISTER DESCRIPTIONS

Power-On Default for PIO Output State

ADDR b7 b6 b5 b4 b3 b2 b1 b0

10Ah

10Bh

There is general read and write access to these addresses. Factory default: 10Ah: FFh; 10Bh: 0Fh. The contents of

this register are automatically transferred to address 120h/121h when the device powers up.

BIT DESCRIPTION BIT(S) DEFINITION

POVn: PIO Power-On

Default State

X: (Not Assigned) — Reserved for future use.

Power-On Default for PIO Direction

ADDR b7 b6 b5 b4 b3 b2 b1 b0

10Ch

10Dh

POV7 POV6 POV5 POV4 POV3 POV2 POV1 POV0

X X X X POV11 POV10 POV9 POV8

—

POD7 POD6 POD5 POD4 POD3 POD2 POD1 POD0

X X X X POD11 POD10 POD9 POD8

Power-on default output state of PIO0 to PIO11. POV0 applies to PIO0,

etc.

There is general read and write access to these addresses. Factory default: 10Ch: FFh; 10Dh: 0Fh. The contents

of this register are automatically transferred to address 122h/123h when the device powers up.

BIT DESCRIPTION BIT(S) DEFINITION

PODn: PIO Power-On

Default Direction

X: (Not Assigned) — Reserved for future use.

Power-On Default for PIO Read Inversion (PIO0 to PIO7)

ADDR b7 b6 b5 b4 b3 b2 b1 b0

10Eh

There is general read and write access to this address. Factory default: 00h. The contents of this register are

automatically transferred to address 124h when the device powers up.

BIT DESCRIPTION BIT(S) DEFINITION

PIMn: PIO Power-On

Default Read-Inversion

PIM7 PIM6 PIM5 PIM4 PIM3 PIM2 PIM1 PIM0

—

—

Power-on default direction of PIO0 to PIO11. POD0 applies to PIO0, etc.

Legend: 0 Î output; 1 Î input

Power-on default state of the read-inversion bit of PIO0 to PIO7. PIM0

applies to PIO0, etc.

Legend: 0 Î no inversion; 1 Î inversion

8 of 33

DS28DG02: 2kb SPI EEPROM with PIO, RTC, Reset, Battery Monitor, and Watchdog

Power-On Default for PIO Read Inversion (PIO8 to PIO11), PIO Output Type and Output Mode

ADDR b7 b6 b5 b4 b3 b2 b1 b0

10Fh

POTM POT3 POT2 POT1 PIM11 PIM10 PIM9 PIM8

There is general read and write access to this address. Factory default: 80h. The contents of this register are

automatically transferred to address 125h when the device powers up.

BIT DESCRIPTION BIT(S) DEFINITION

PIMn: PIO Power-On

Default Read-Inversion

POT1: Power-On

Default Output Type

POT2: Power-On

Default Output Type

POT3: Power-On

Default Output Type

POTM: Power-On

Default Output Mode

b0 to b3

b4

b5

b6

b7

Power-on default state of the read-inversion bit of PIO8 to PIO11. PIM8

applies to PIO8, etc.

Legend: 0 Î no inversion; 1 Î inversion

Power-on default output type of PIO0 to PIO3;

Legend: 0 Î push-pull; 1 Î open drain

Power-on default output type of PIO4 to PIO7;

Legend: 0 Î push-pull; 1 Î open drain

Power-on default output type of PIO8 to PIO11;

Legend: 0 Î push-pull; 1 Î open drain

Power-on default output mode of PIO0 to PIO11;

Legend: 0 Î low-current, simultaneous switching; 1 Î high-current,

sequential switching

Unique Registration Number (118h to 11Fh)

Each DS28DG02 has a unique registration number that is 64 bits long, as shown in Figure 3. The registration

number begins with the family code at address 118h followed by the 48-bit serial number (LS-byte at the lower

address) and ends at address 11Fh with the Cyclic Redundancy Check (CRC) of the first 56 bits. This CRC is

generated using the a polynomial X

8

+ X5 + X

4

+ 1. Additional information about CRCs is available in Application

Note 27.

Figure 3. 64-Bit Registration Number

MSB LSB

8-Bit CRC Code 48-Bit Serial Number

8-Bit Family Code (70h)

MSB LSB MSB LSB MSB LSB

PIO Output State

ADDR b7 b6 b5 b4 b3 b2 b1 b0

120h

121h

OV7 OV6 OV5 OV4 OV3 OV2 OV1 OV0

X X X X OV11 OV10 OV9 OV8

There is general read and write access to these addresses. These registers are automatically loaded with data

from address 10Ah/10Bh when the device powers up.

BIT DESCRIPTION BIT(S) DEFINITION

OVn: PIO Output State —

Output state of PIO0 to PIO11. OV0 applies to PIO0, etc.

Legend: 0 Î LOW; 1 Î HIGH if PIO direction is output

X: (Not Assigned) — Reserved for future use.

9 of 33

DS28DG02: 2kb SPI EEPROM with PIO, RTC, Reset, Battery Monitor, and Watchdog

PIO Direction

ADDR b7 b6 b5 b4 b3 b2 b1 b0

122h

123h

DIR7 DIR6 DIR5 DIR4 DIR3 DIR2 DIR1 DIR0

X X X X DIR11 DIR10 DIR9 DIR8

There is general read and write access to these addresses. These registers are automatically loaded with data

from address 10Ch/10Dh when the device powers up.

BIT DESCRIPTION BIT(S) DEFINITION

DIRn: PIO Direction —

Direction of PIO0 to PIO11. DIR0 applies to PIO0, etc.

Legend: 0 Î output; 1 Î input

X: (Not Assigned) — Reserved for future use.

PIO Read Inversion (PIO0 to PIO7)

ADDR b7 b6 b5 b4 b3 b2 b1 b0

124h

IMSK7 IMSK6 IMSK5 IMSK4 IMSK3 IMSK2 IMSK1 IMSK0

There is general read and write access to this address. This register is automatically loaded with data from address

10Eh when the device powers up.

BIT DESCRIPTION BIT(S) DEFINITION

IMSKn: PIO ReadInversion

—

Read-inversion bit of PIO0 to PIO7. IMSK0 applies to PIO0, etc.

Legend: 0 Î no inversion; 1 Î inversion

PIO Read Inversion (PIO8 to PIO11), PIO Output Type and Output Mode

ADDR b7 b6 b5 b4 b3 b2 b1 b0

125h

OTM OT3 OT2 OT1

IMSK11 IMSK10

IMSK9 IMSK8

There is general read and write access to this address. This register is automatically loaded with data from address

10Fh when the device powers up.

BIT DESCRIPTION BIT(S) DEFINITION

IMSKn: PIO ReadInversion

b0 to b3

OT1: Output Type b4

OT2: Output Type b5

OT3: Output Type b6

Read-inversion bit of PIO8 to PIO11. PIM8 applies to PIO8, etc.

Legend: 0 Î no inversion; 1 Î inversion

Output type of PIO0 to PIO3;

Legend: 0 Î push-pull; 1 Î open drain

Output type of PIO4 to PIO7;

Legend: 0 Î push-pull; 1 Î open drain

Output type of PIO8 to PIO11;

Legend: 0 Î push-pull; 1 Î open drain

Output mode of PIO0 to PIO11;

OTM: Output Mode b7

Legend: 0 Î low-current, simultaneous switching; 1 Î high-current,

sequential switching

10 of 33