Page 1

Rev 0; 6/09

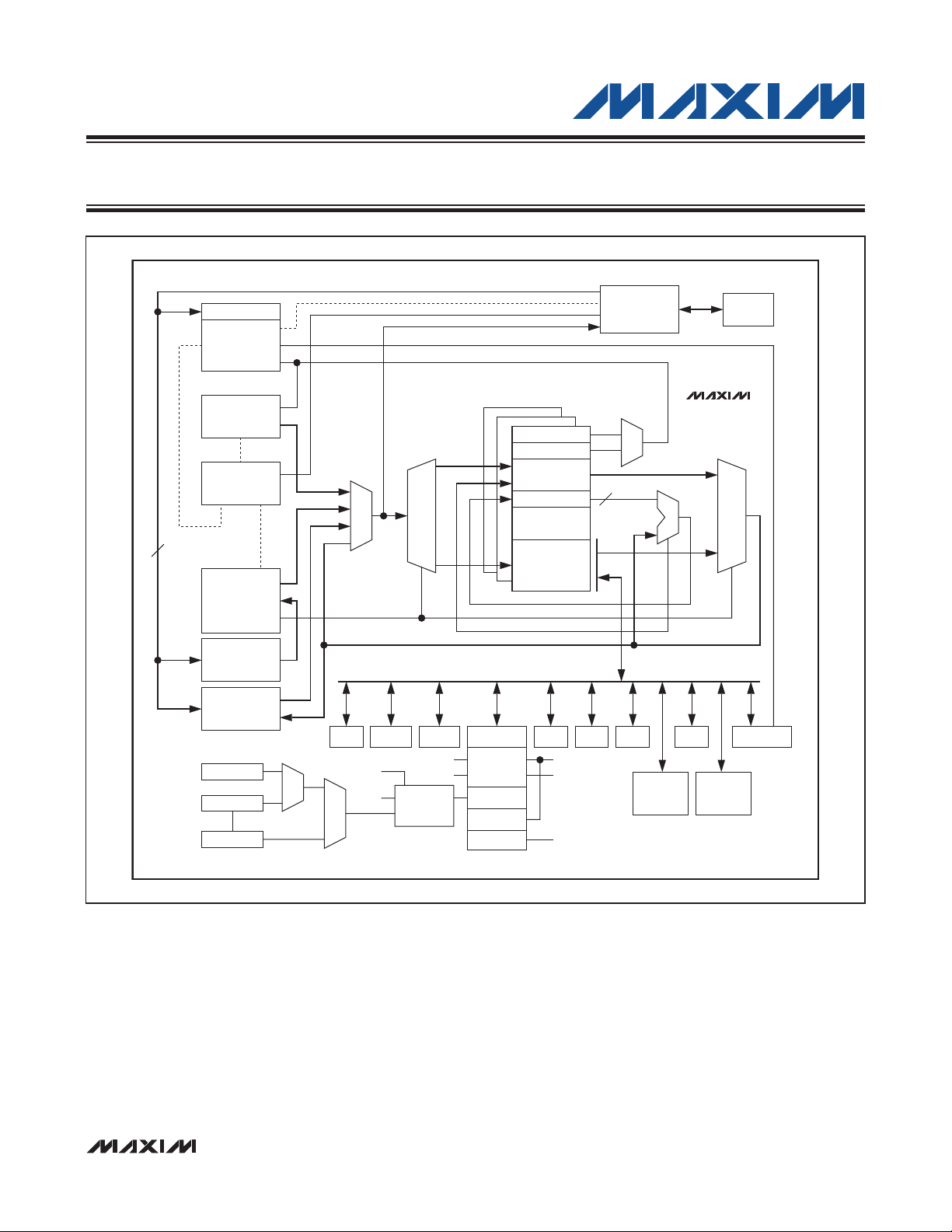

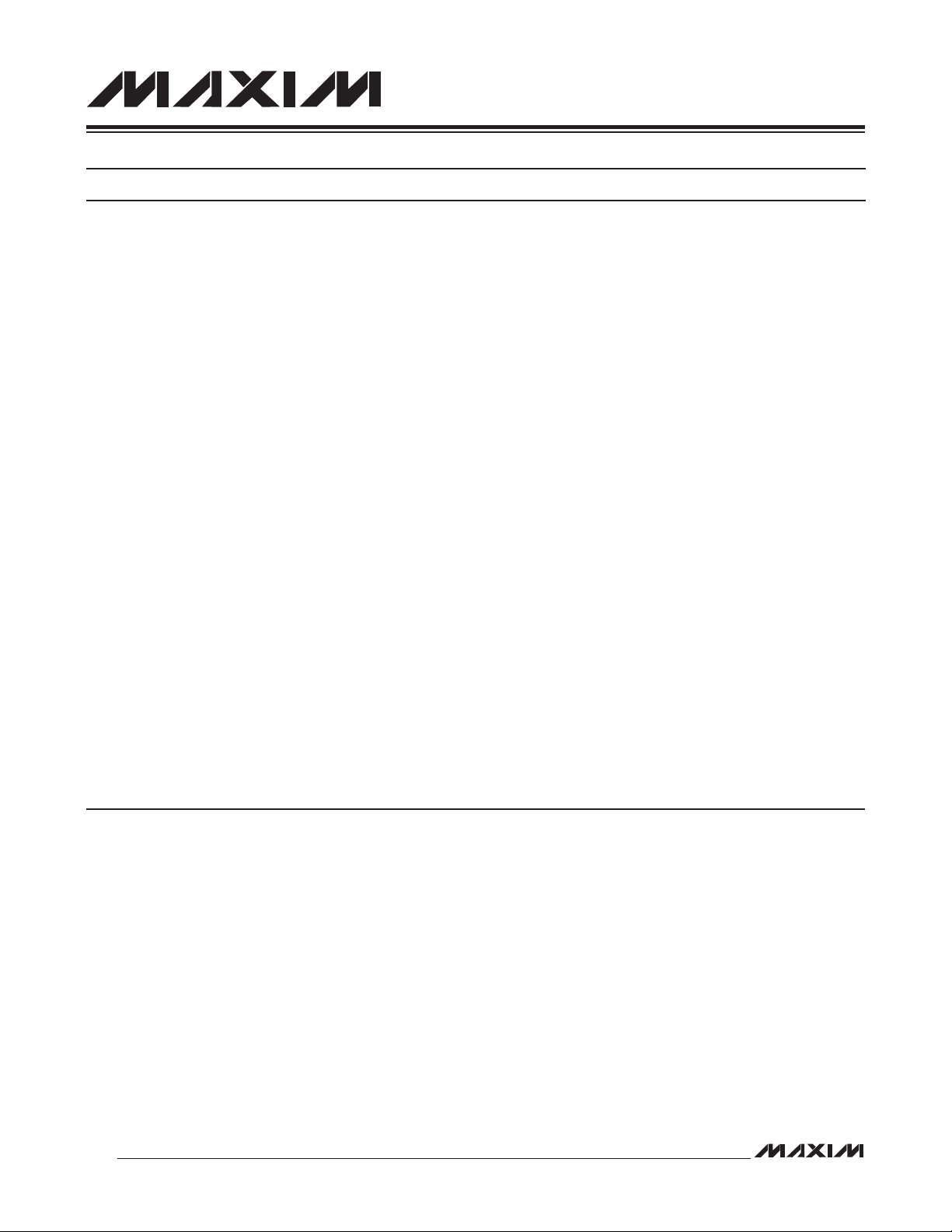

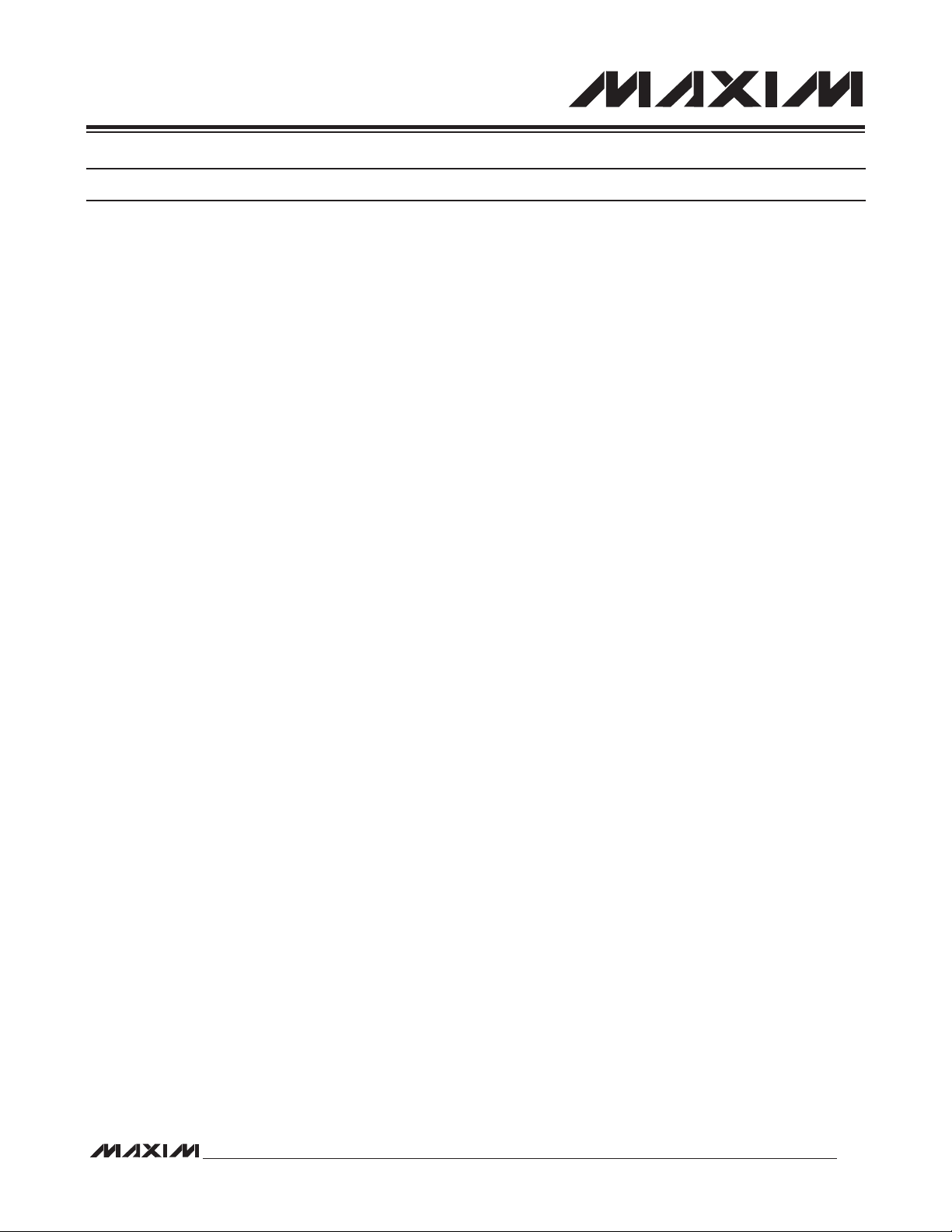

MAXQ FAMILY USER’S GUIDE:

MAXQ2010 SUPPLEMENT

16

IN-CIRCUIT

DEBUGGER

I2CRTCSPI

12-BIT

8-CHANNEL

MACWATCHDOG

ADC

ADD REG

ADDRESS

GENERATOR

STACK

IP

DP

SYSTEM

REGISTERS

Acc

PERIPHERAL

REGISTERS

LCD

DVDD

DGND

RESET

DEMUX

TIMERUSART

AVDD

AGND

SYSTEM

CLOCK

STATUS

POWER

OSC UP

BROWNOUT

RESET

CONTROL

16

INSTRUCTION

DECODER

PROGRAM

MEMORY

DATA

MEMORY

HFX

FLL

32kHz

PMM

STOP

JTAG

MAXQ2010

MUX

INTERRUPT

SUPPLY

VOLTAGE

MONITOR

_______________________________________________________________ Maxim Integrated Products i

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,

or visit Maxim’s website at www.maxim-ic.com.

Page 2

MAXQ Family User’s Guide:

MAXQ2010 Supplement

TABLE OF CONTENTS

ADDENDUM TO SECTION 1: OVERVIEW 1-1

1.1 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-1

ADDENDUM TO SECTION 2: ARCHITECTURE 2-1

2.1 Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-1

2.2 Harvard Memory Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-1

2.3 Register Space. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-1

2.4 Memory Organization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.4.1 Register Space. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.4.2 Program Stack . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.4.3 Data SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.4.4 Program Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.5 Program and Data Memory Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.6 Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.6.1 External High-Frequency Oscillator Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.6.2 External 32kHz Crystal Oscillator Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.6.3 Frequency-Locked Loop (FLL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

2.7 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

2.8 Reset Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-9

2.8.1 Power-On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

2.8.2 Watchdog Timer Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

2.8.3 External Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

2.9 Power-Management Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

2.9.1 Divide-by-256 Mode (PMM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12

2.9.2 Switchback Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12

2.9.3 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13

ADDENDUM TO SECTION 3: PROGRAMMING 3-1

ADDENDUM TO SECTION 4: SYSTEM REGISTER DESCRIPTIONS 4-1

4.1 System Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-3

4.1.1 Processor Status Flags Register (PSF, M8[04h]). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-3

4.1.2 Interrupt Mask Register (IMR, M8[06h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-3

4.1.3 System Control Register (SC, M8[08h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

4.1.4 Interrupt Identification Register (IIR, M8[0Bh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

4.1.5 System Clock Control Register (CKCN, M8[0Eh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-5

ADDENDUM TO SECTION 5: PERIPHERAL REGISTER MODULES 5-1

ADDENDUM TO SECTION 6: GENERAL-PURPOSE I/O MODULE 6-1

6.1 GPIO and External Interrupt Register Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-4

6.1.1 Port 0 Direction Register (PD0, M0[10h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-4

ii

Page 3

MAXQ Family User’s Guide:

MAXQ2010 Supplement

TABLE OF CONTENTS (continued)

6.1.2 Port 1 Direction Register (PD1, M0[11h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-4

6.1.3 Port 2 Direction Register (PD2, M0[12h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-5

6.1.4 Port 3 Direction Register (PD3, M0[13h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-5

6.1.5 Port 4 Direction Register (PD4, M1[10h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-5

6.1.6 Port 5 Direction Register (PD5, M1[11h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-6

6.1.7 Port 6 Direction Register (PD6, M1[12h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-6

6.1.8 Port 0 Output Register (PO0, M0[00h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-6

6.1.9 Port 1 Output Register (PO1, M0[01h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-6

6.1.10 Port 2 Output Register (PO2, M0[02h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-7

6.1.11 Port 3 Output Register (PO3, M0[03h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-7

6.1.12 Port 4 Output Register (PO4, M1[00h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-7

6.1.13 Port 5 Output Register (PO5, M1[01h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-7

6.1.14 Port 6 Output Register (PO6, M1[02h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-8

6.1.15 Port 0 Input Register (PI0, M0[08h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-8

6.1.16 Port 1 Input Register (PI1, M0[09h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-8

6.1.17 Port 2 Input Register (PI2, M0[0Ah]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-8

6.1.18 Port 3 Input Register (PI3, M0[0Bh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-9

6.1.19 Port 4 Input Register (PI4, M1[08h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-9

6.1.20 Port 5 Input Register (PI5, M1[09h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-9

6.1.21 Port 6 Input Register (PI6, M1[0Ah]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-9

6.1.22 External Interrupt Flag 0 Register (EIF0, M0[04h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-10

6.1.23 External Interrupt Flag 1 Register (EIF1, M1[04h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-10

6.1.24 External Interrupt Flag 2 Register (EIF2, M1[06h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-11

6.1.25 External Interrupt Enable 0 Register (EIE0, M0[05h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-11

6.1.26 External Interrupt Enable 1 Register (EIE1, M1[05h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-12

6.1.27 External Interrupt Enable 2 Register (EIE2, M1[07h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-12

6.1.28 External Interrupt Edge Select 0 Register (EIES0, M0[0Ch]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-13

6.1.29 External Interrupt Edge Select 1 Register (EIES1, M1[0Bh]). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-13

6.1.30 External Interrupt Edge Select 2 Register (EIES2, M1[0Ch]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-14

6.2 GPIO and External Interrupt Code Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-14

6.2.1 GPIO Example 1: Driving Outputs on Port 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-14

6.2.2 GPIO Example 2: Receiving Inputs on Port 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-14

6.2.3 External Interrupt Example: Handling Interrupt on INT10/P5.2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-15

ADDENDUM TO SECTION 7: TIMER/COUNTER 0 MODULE 7-1

ADDENDUM TO SECTION 8: TIMER/COUNTER 1 MODULE 8-1

ADDENDUM TO SECTION 9: TIMER/COUNTER 2 MODULE 9-1

iii

Page 4

MAXQ Family User’s Guide:

MAXQ2010 Supplement

TABLE OF CONTENTS (continued)

ADDENDUM TO SECTION 10: SERIAL I/O MODULE 10-1

10.1 Serial USART I/O Pins and Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-1

10.2 Serial USART Code Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-1

10.2.1 Serial USART Example: Echo Characters in 10-Bit Asynchronous Mode. . . . . . . . . . . . . . . . . . . . . . . .10-1

ADDENDUM TO SECTION 11: SERIAL PERIPHERAL INTERFACE (SPI) MODULE 11-1

11.1 SPI Input/Output Pins and Control Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-1

11.2 SPI Code Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-1

11.2.1 SPI Example 1: Transmitting Data in Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-1

11.2.2 SPI Example 2: Receiving Data in Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-2

ADDENDUM TO SECTION 12: HARDWARE MULTIPLIER MODULE 12-1

12.1 Hardware Multiplier Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-1

12.2 Hardware Multiplier Code Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-1

12.2.1 Hardware Multiplier Example: Multiply and Square/Accumulate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-1

ADDENDUM TO SECTION 13: 1-Wire BUS MASTER 13-1

ADDENDUM TO SECTION 14: REAL-TIME CLOCK MODULE 14-1

14.1 RTC Pins and Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-1

14.2 RTC Operation Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-1

14.3 RTC Trim Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-2

14.4 RTC Register Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-4

14.4.1 RTC Trim Register (RTRM, M0[18h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-4

14.4.2 RTC Control Register (RCNT, M0[19h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-4

14.4.3 Real-Time Subsecond Counter Register (RTSS, M0[1Ah]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-6

14.4.4 RTC Seconds Counter High Register (RTSH, M0[1Bh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-6

14.4.5 RTC Seconds Counter Low Register (RTSL, M0[1Ch]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-6

14.4.6 RTC Subsecond Alarm Register (RSSA, M0[1Dh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-7

14.4.7 RTC Time-of-Day Alarm High Register (RASH, M0[1Eh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-7

14.4.8 RTC Time-of-Day Alarm Low Register (RASL, M0[1Fh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-7

14.5 RTC Example: Starting and Setting the Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-8

ADDENDUM TO SECTION 15: TEST ACCESS PORT (TAP) 15-1

ADDENDUM TO SECTION 16: IN-CIRCUIT DEBUG MODE 16-1

16.1 Register Read and Write Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-1

16.2 Data Memory Read Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-1

16.3 Data Memory Write Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-1

16.4 Program Stack Read Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-1

16.5 Read Register Map Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-1

iv

Page 5

MAXQ Family User’s Guide:

MAXQ2010 Supplement

TABLE OF CONTENTS (continued)

ADDENDUM TO SECTION 17: IN-SYSTEM PROGRAMMING (JTAG) 17-1

17.1 JTAG Bootloader Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-1

17.2 Family 0 Commands (Not Password Protected) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-2

17.3 Family 1 Commands: Load Variable Length (Password Protected) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-4

17.4 Family 2 Commands: Dump Variable Length (Password Protected) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-5

17.5 Family 3 Commands: CRC Variable Length (Password Protected) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-6

17.6 Family 4 Commands: Verify Variable Length (Password Protected). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-6

17.7 Family 5 Commands: Load and Verify Variable Length (Password Protected) . . . . . . . . . . . . . . . . . . . . . . . .17-7

17.8 Family E Commands: Erase Fixed Length (Password Protected). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-7

ADDENDUM TO SECTION 18: MAXQ FAMILY INSTRUCTION SET SUMMARY 18-1

SECTION 19: ANALOG-TO-DIGITAL CONVERTER (SPECIFIC TO MAXQ2010) 19-1

19.1 Analog-to-Digital Converter Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-1

19.2 Analog-to-Digital Pins and Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-2

19.2.1 Analog-to-Digital Converter Status Register (ADST, M4[06h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-3

19.2.2 ADC Conversion Sequence Address Register (ADADDR, M4[07h]) . . . . . . . . . . . . . . . . . . . . . . . . . . .19-5

19.2.3 ADC Control Register (ADCN, M4[0Eh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-5

19.2.4 ADC Data Register (ADDATA, M4[0Fh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-7

19.2.5 ADC Data Buffer Registers (ADBUF[0] to ADBUF[15], ADDATA[00h] to ADDATA[0Fh]) . . . . . . . . . . .19-7

19.2.6 ADC Conversion Configuration Registers (ADCFG[0] to ADCFG[7], ADDATA[10h] to ADDATA[17h]) 19-8

19.3 Analog-to-Digital Converter Code Examples. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-9

19.3.1 ADC Example 1: Single Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-9

19.3.2 ADC Example 2: Continuous Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-9

SECTION 20: LCD CONTROLLER (SPECIFIC TO MAXQ2010) 20-1

20.1 LCD Controller Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-1

20.2 LCD Controller Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-2

20.2.1 LCD Configuration Register (LCFG, M2[06h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-2

20.2.2 LCD Contrast Adjust Register (LCRA, M2[0Ah]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-3

20.2.3 LCD Display Register 0 (LCD0, M2[0Bh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-4

20.2.4 LCD Display Register 1 (LCD1, M2[0Ch]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-4

20.2.5 LCD Display Register 2 (LCD2, M2[0Dh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-4

20.2.6 LCD Display Register 3 (LCD3, M2[0Eh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-4

20.2.7 LCD Display Register 4 (LCD4, M2[0Fh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-4

20.2.8 LCD Display Register 5 (LCD5, M2[10h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-4

20.2.9 LCD Display Register 6 (LCD6, M2[11h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-5

20.2.10 LCD Display Register 7 (LCD7, M2[12h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-5

20.2.11 LCD Display Register 8 (LCD8, M2[13h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-5

20.2.12 LCD Display Register 9 (LCD9, M2[14h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-5

v

Page 6

MAXQ Family User’s Guide:

MAXQ2010 Supplement

TABLE OF CONTENTS (continued)

20.2.13 LCD Display Register 10 (LCD10, M2[15h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-5

20.2.14 LCD Display Register 11 (LCD11, M2[16h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-5

20.2.15 LCD Display Register 12 (LCD12, M2[17h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-6

20.2.16 LCD Display Register 13 (LCD13, M2[18h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-6

20.2.17 LCD Display Register 14 (LCD14, M2[19h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-6

20.2.18 LCD Display Register 15 (LCD15, M2[1Ah]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-6

20.2.19 LCD Display Register 16 (LCD16, M2[1Bh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-6

20.2.20 LCD Display Register 17 (LCD17, M2[1Ch]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-6

20.2.21 LCD Display Register 18 (LCD18, M2[1Dh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-7

20.2.22 LCD Display Register 19 (LCD19, M2[1Eh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-7

20.2.23 LCD Display Register 20 (LCD20, M2[1Fh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-7

20.3 LCD Controller Operation Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-7

20.4 LCD Drive Voltages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-7

20.5 Selecting the LCD Display Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-7

20.6 Segment Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-7

20.7 LCD Internal Adjustable Contrast Resistor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-8

20.8 LCD Frame Frequency. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-9

20.9 LCD Display Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-10

20.10 Display Waveform Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-12

20.11 LCD Controller Static Drive Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-13

20.12 LCD Controller 1/2 Duty Cycle Drive Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-15

20.13 LCD Controller 1/3 Duty Cycle Drive Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-15

20.14 LCD Controller 1/4 Duty Cycle Drive Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-18

20.15 LCD Controller Example: Initializing the LCD Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-19

SECTION 21: TIMER/COUNTER B MODULE (SPECIFIC TO MAXQ2010) 21-1

21.1 Timer/Counter B Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-2

21.1.1 Timer B Timer/Counter 0/1/2 Capture/Reload Register (TB0R, TB1R, TB2R; M4[00h],

M4[02h], M4[04h]). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-2

21.1.2 Timer B Timer/Counter 0/1/2 Compare Register (TB0C, TB1C, TB2C; M4[01h], M4[03h], M4[05h]) . .21-2

21.1.3 Timer B Timer/Counter 0/1/2 Control Register (TB0CN, TB1CN, TB2CN; M4[08h], M4[0Ah], M4[0Ch]) 21-3

21.1.4 Timer B Timer/Counter 0/1/2 Value Register (TB0V, TB1V, TB2V; M4[09h], M4[0Bh], M4[0Dh]). . . . . .21-4

21.2 Timer/Counter B Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-5

21.2.1 Timer B 16-Bit Timer/Counter Mode with Autoreload . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-5

21.2.2 Timer B 16-Bit Capture Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-6

21.2.3 Timer B 16-Bit Up/Down Count with Autoreload Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-7

21.2.4 Timer B Clock Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-8

21.2.5 Timer B PWM/Output Control Functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-8

21.2.6 16-Bit Up Count PWM/Output Control Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-9

vi

Page 7

MAXQ Family User’s Guide:

MAXQ2010 Supplement

TABLE OF CONTENTS (continued)

21.2.7 16-Bit Up/Down Count PWM/Output Control Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-10

21.2.8 EXENB Control During PWM/Output Control Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-12

21.3 Timer B Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-12

21.3.1 Timer B Example: Reloading Timer Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-12

SECTION 22 : I2C BUS INTERFACE (SPECIFIC TO MAXQ2010) 22-1

22.1 I2C Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-1

22.1.1 I2C Data Buffer Register (I2CBUF, M3[00h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-1

22.1.1.1 I2C Data Read and Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-2

22.1.1.2 I2C Address Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-2

22.1.2 I2C Status Register (I2CST, M3[01h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-2

22.1.3 Interrupt Enable Register (I2CIE, M3[02h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-3

22.1.4 I2C Control Register (I2CCN, M3[0Ch]). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-4

22.1.5 Clock Control Register (I2CCK, M3[0Dh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-5

22.1.6 I2C Timeout Register (I2CTO, M3[0Eh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-6

22.1.7 I2C Slave Address Register (I2CSLA, M3[0Fh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-6

22.2 I2C Code Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-7

22.2.1 I2C Example 1: Master Mode Transmit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-7

22.2.2 I2C Example 2: Master Mode Receive. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-7

22.2.3 I2C Example 3: Slave Mode Receive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-8

22.2.4 I2C Example 4: Slave Mode Receive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-8

SECTION 23: SUPPLY VOLTAGE MONITOR AND POWER CONTROL

(SPECIFIC TO MAXQ2010) 23-1

23.1 SVM and Power Control Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23-1

23.1.1 Power Control Register (PWCN, M0[0Fh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23-1

23.1.2 Supply Voltage Monitor Register (SVM, M1[0Dh]). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23-3

SECTION 24: UTILITY ROM (SPECIFIC TO MAXQ2010) 24-1

24.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-1

24.2 In-Application Programming Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-2

24.2.1 UROM_flashWrite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-2

24.2.2 UROM_flashErasePage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-2

24.2.3 UROM_flashEraseAll . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-2

24.3 Data Transfer Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-3

24.3.1 UROM_moveDP0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-4

24.3.2 UROM_moveDP0inc. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-4

24.3.3 UROM_moveDP0dec . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-4

24.3.4 UROM_moveDP1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-5

24.3.5 UROM_moveDP1inc. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-5

vii

Page 8

MAXQ Family User’s Guide:

MAXQ2010 Supplement

TABLE OF CONTENTS (continued)

24.3.6 UROM_moveDP1dec . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-5

24.3.7 UROM_moveBP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-6

24.3.8 UROM_moveBPinc. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-6

24.3.9 UROM_moveBPdec . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-6

24.3.10 UROM_copyBuffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-7

24.4 Utility ROM Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-7

24.4.1 Utility ROM Example 1: Reading Constant Word Data from Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-7

24.4.2 Utility ROM Example 2: Reading Constant Byte Data from Flash (Indirect Function Call) . . . . . . . . . . .24-8

APPENDIX 1: SAMPLE MAXQ2010 DEVICE INCLUDE FILE FOR MAX-IDE A1-1

REVISION HISTORY R-1

viii

Page 9

MAXQ Family User’s Guide:

MAXQ2010 Supplement

LIST OF FIGURES

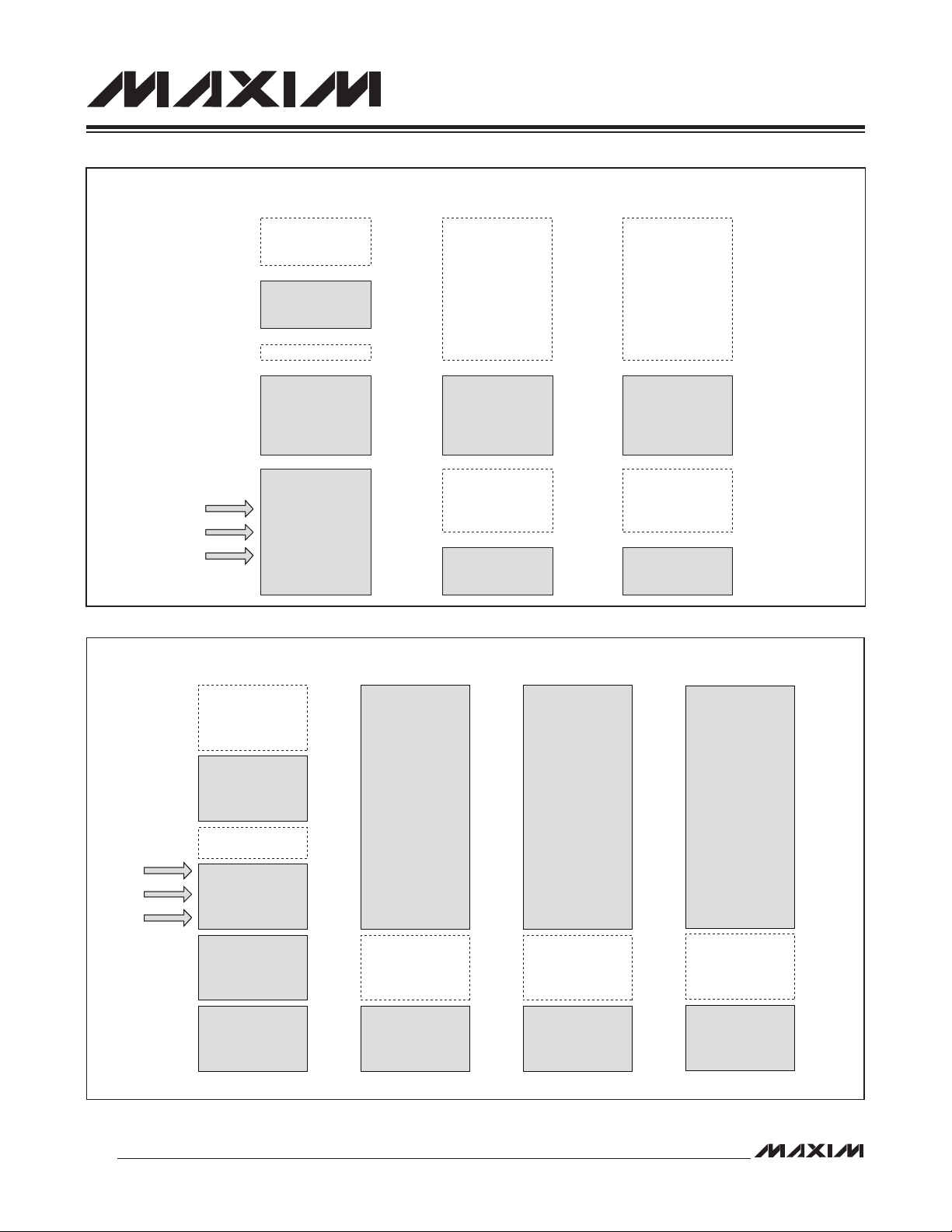

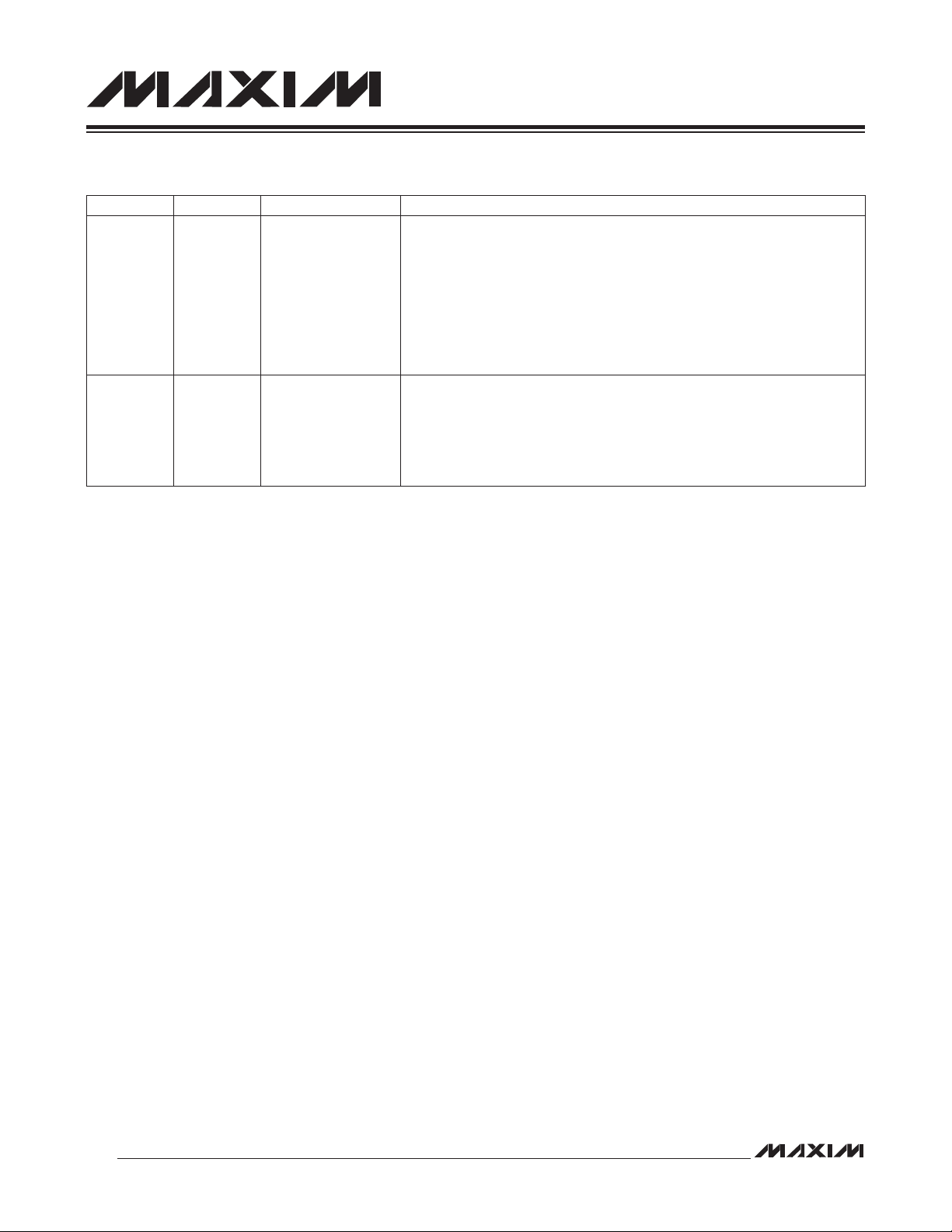

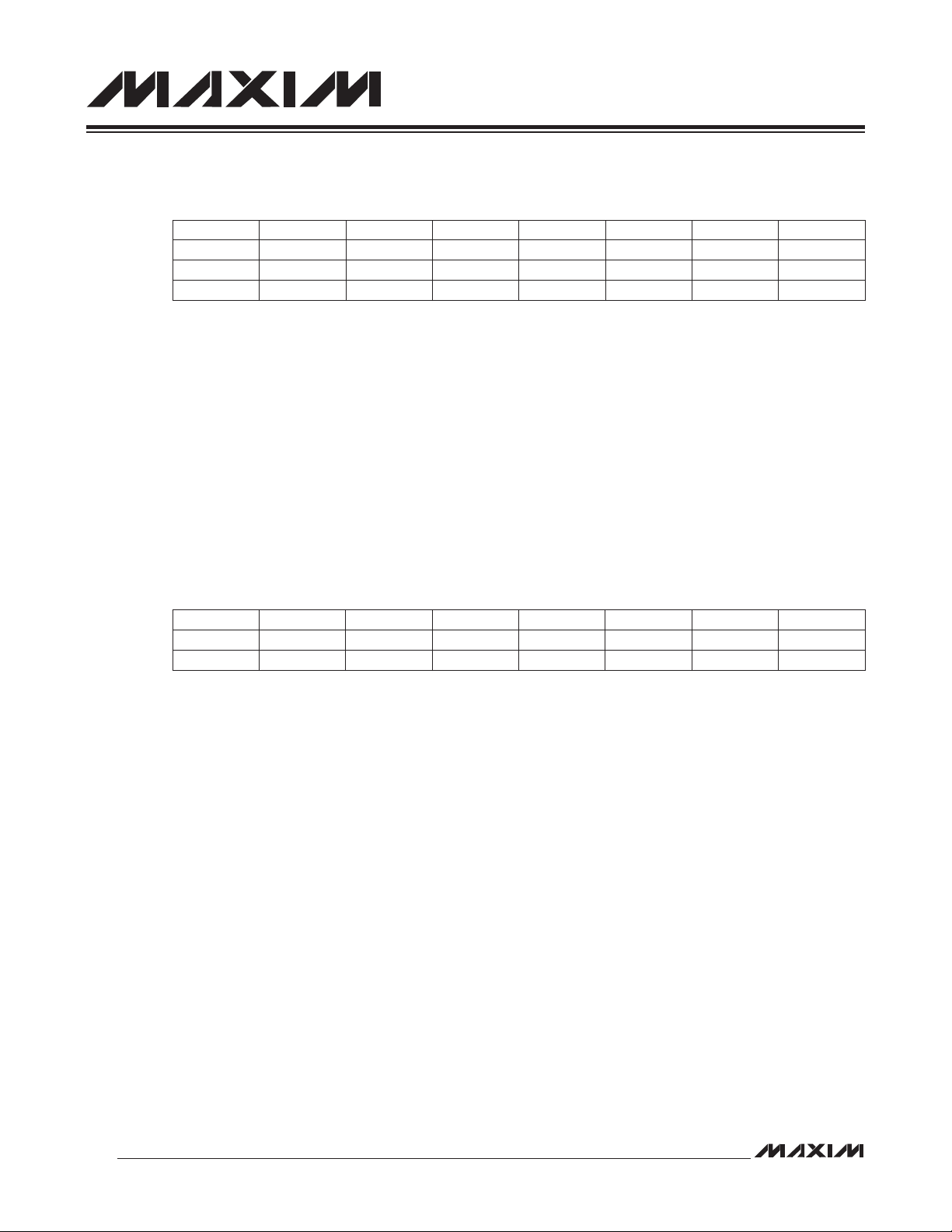

Figure 2-1. MAXQ2010 System and Peripheral Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2

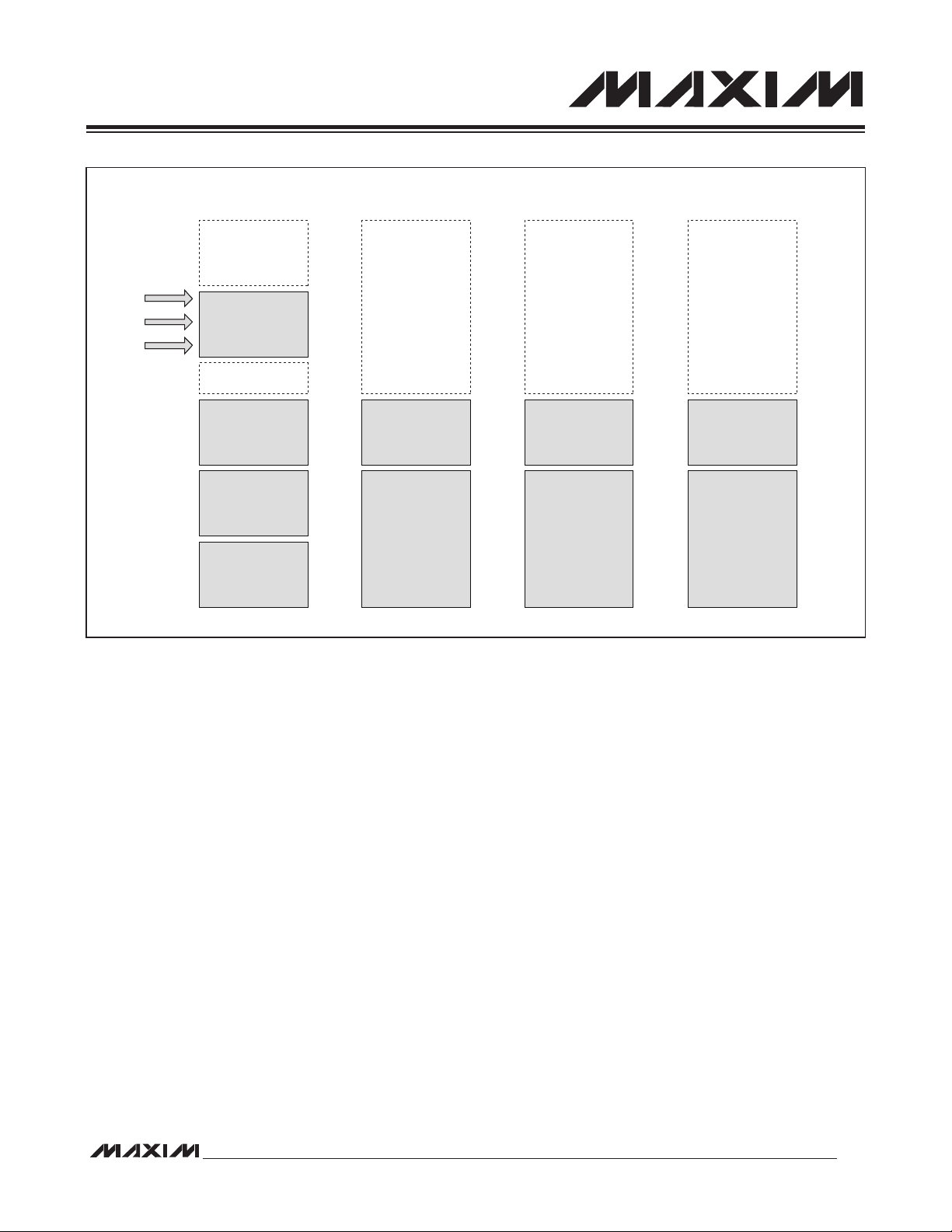

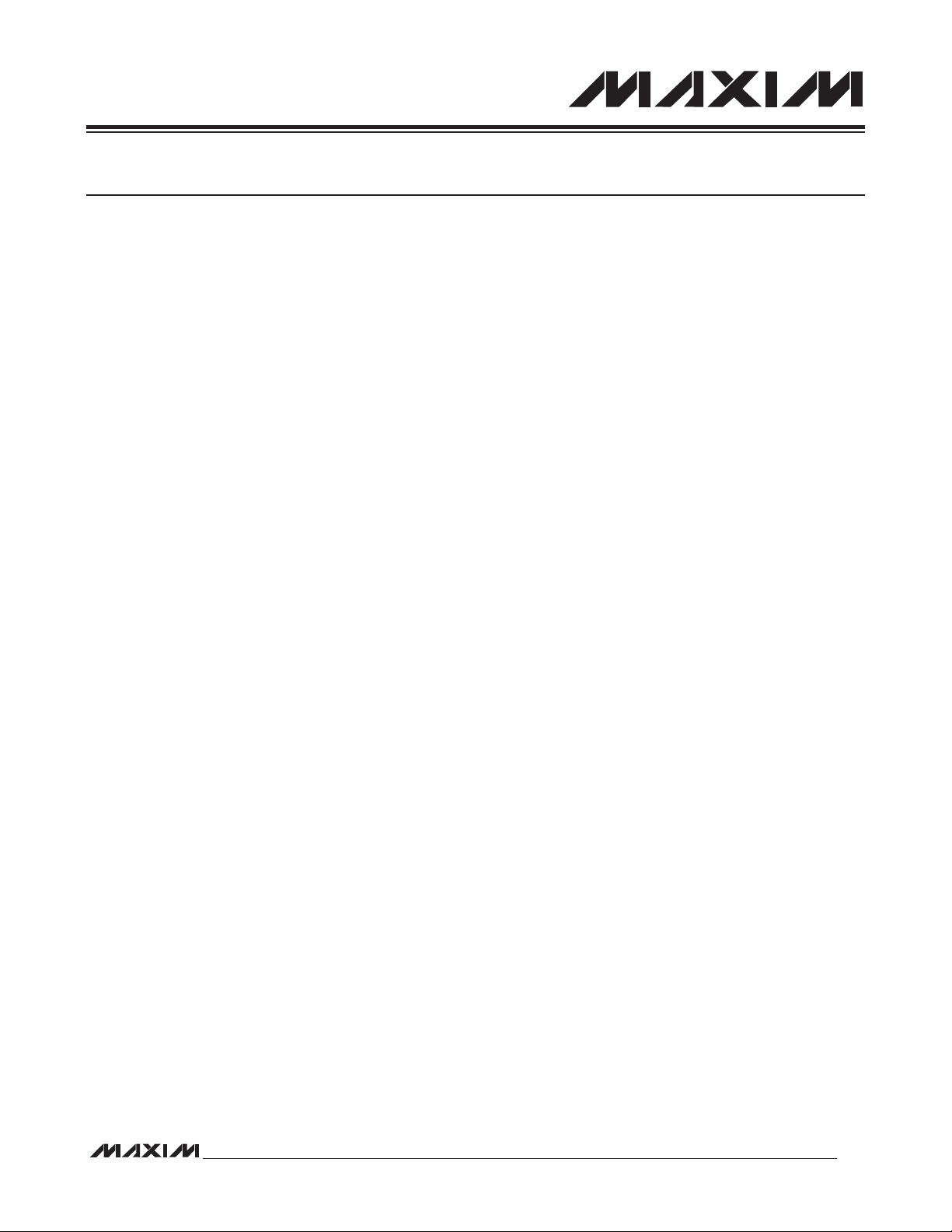

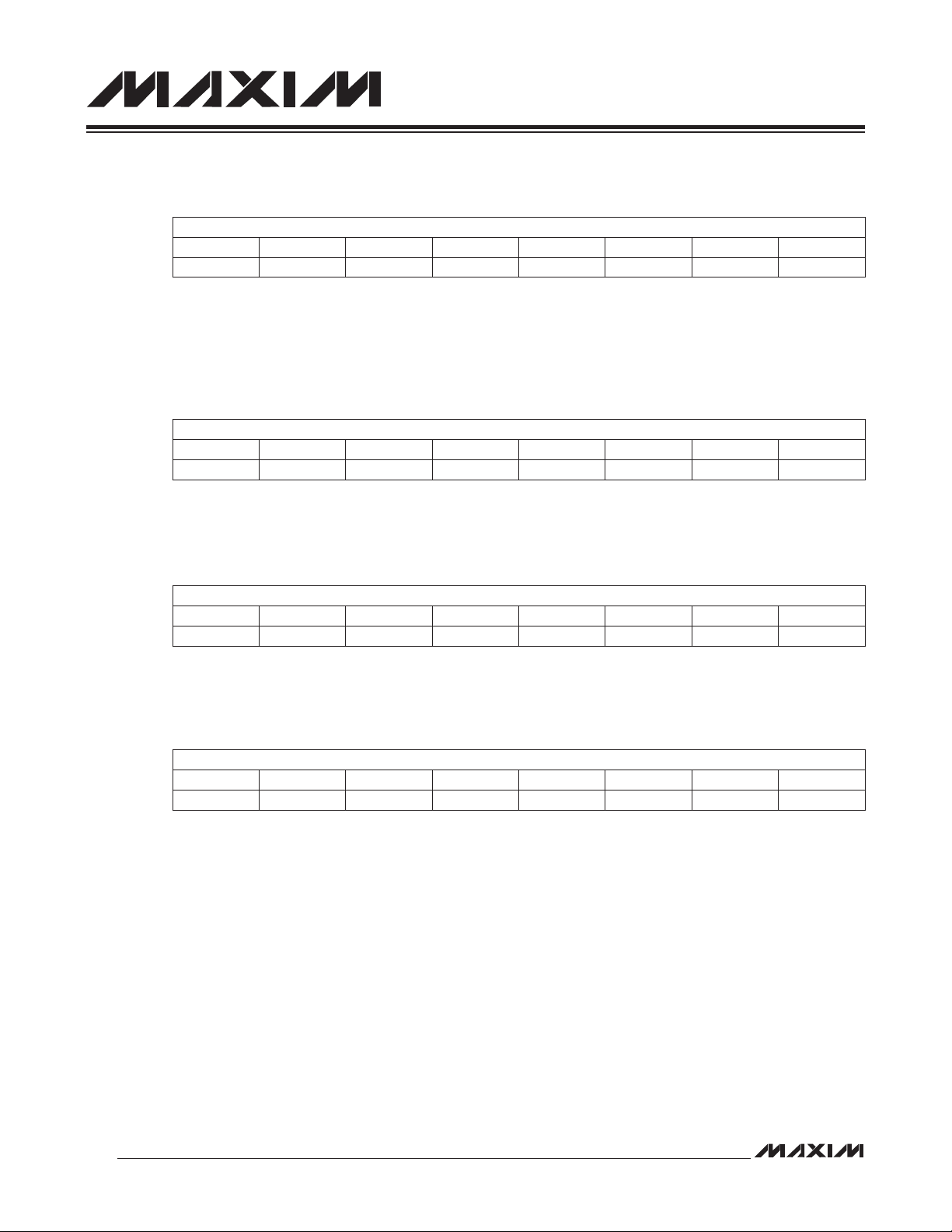

Figure 2-2. Memory Map When Executing from Program Flash Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

Figure 2-3. Memory Map When Executing from Utility ROM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

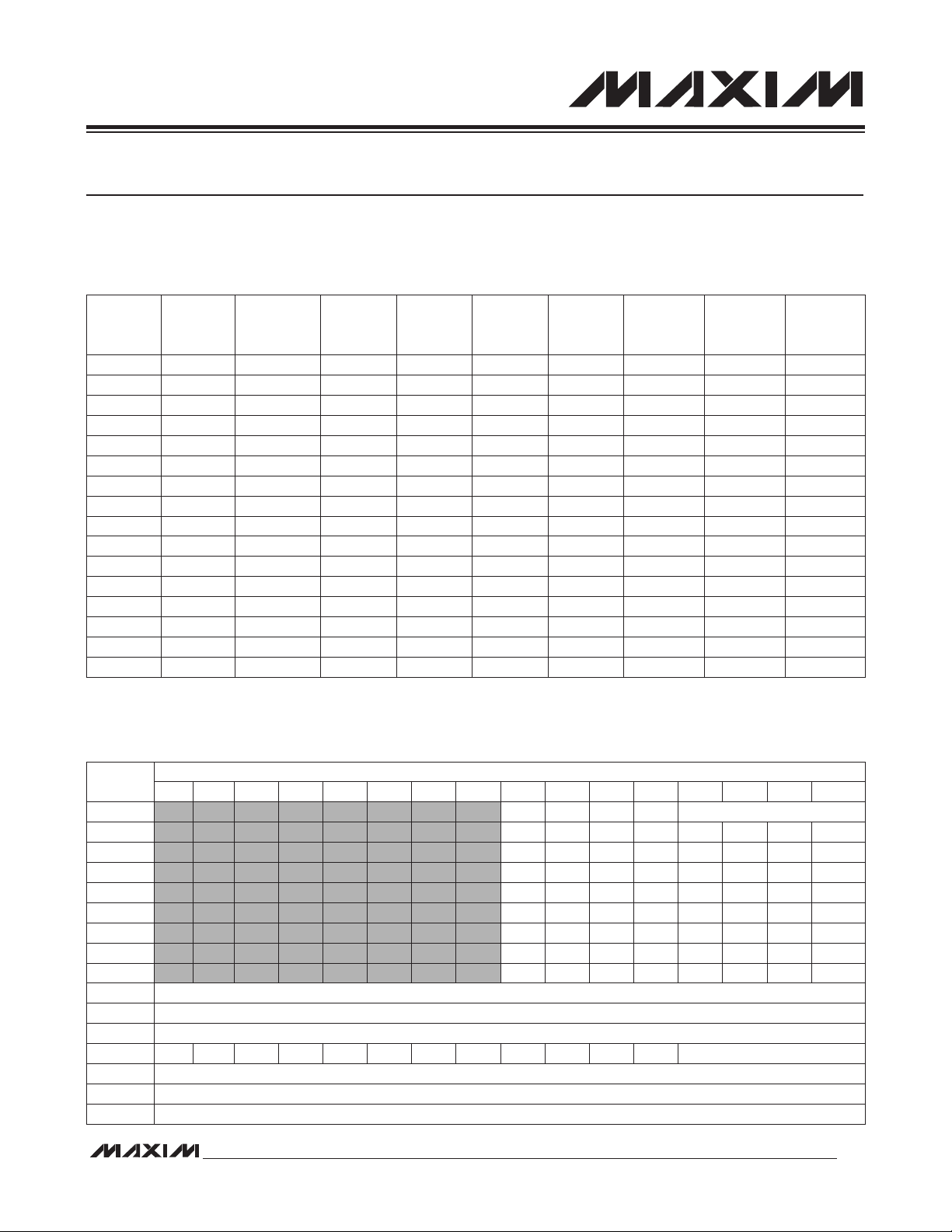

Figure 2-4. Memory Map When Executing from Data SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

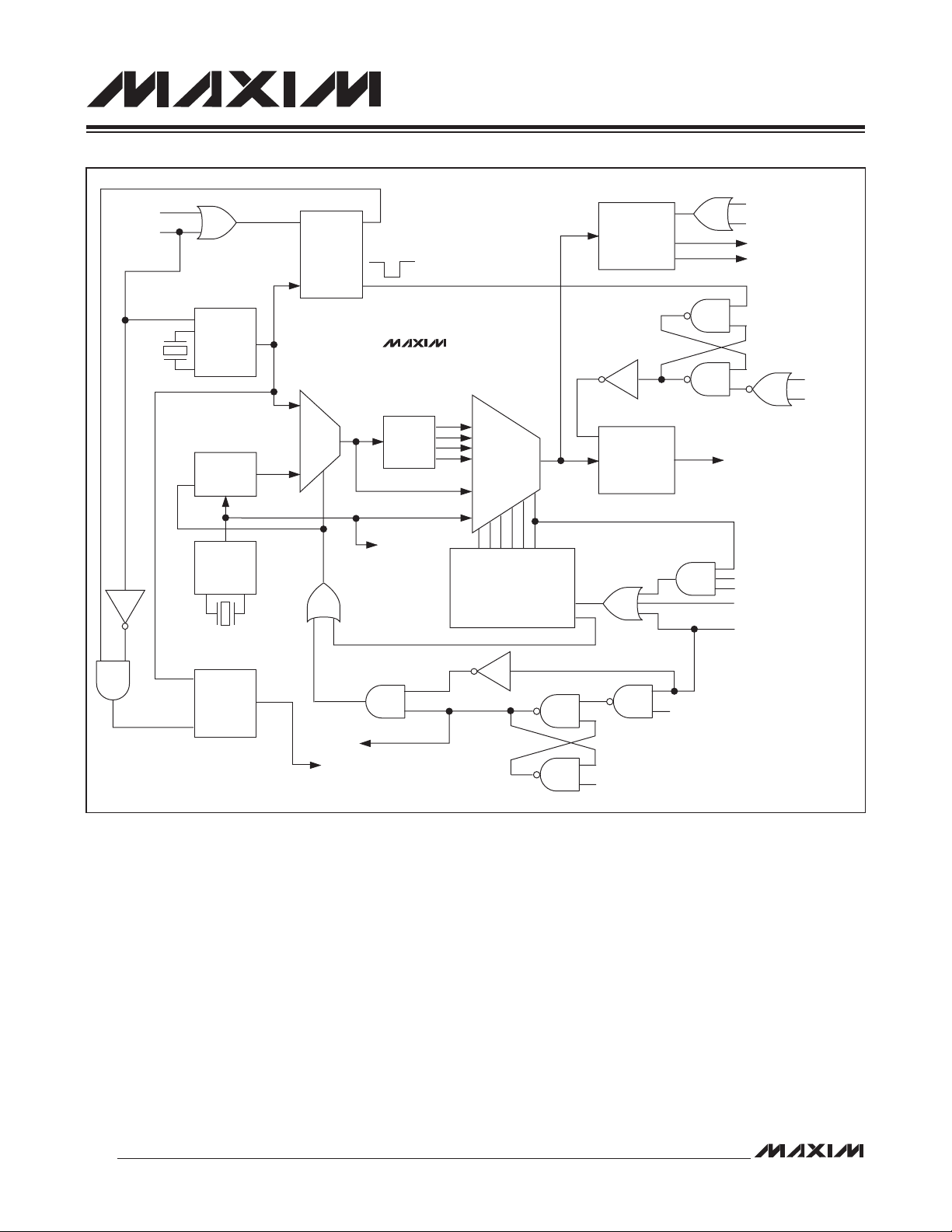

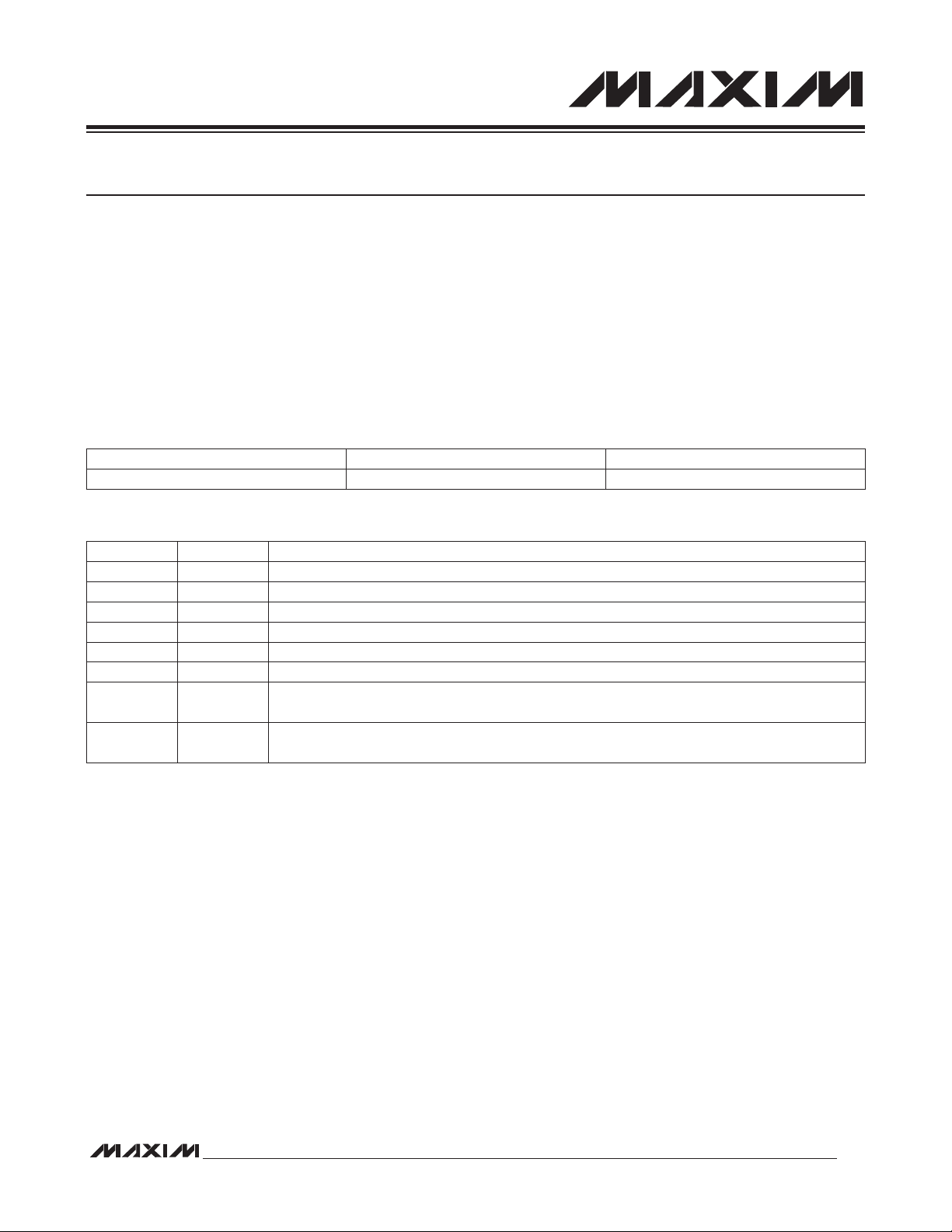

Figure 2-5. MAXQ2010 Clock Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

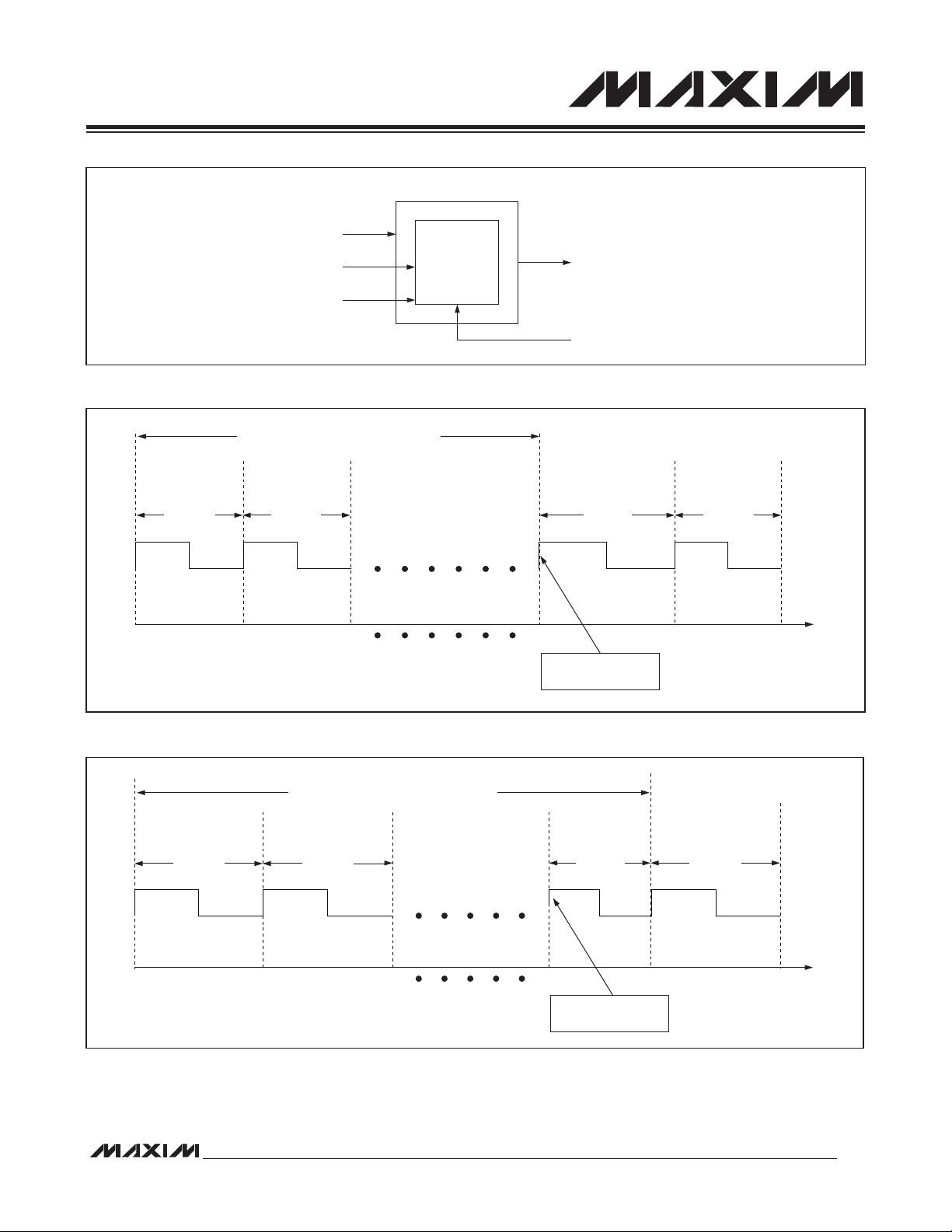

Figure 2-6. Power-On Reset Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

Figure 2-7. External Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

Figure 14-1. RTC Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-2

Figure 14-2. RTC Prescaler and Trim . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-3

Figure 14-3. RTC Trim Adjustment (TSGN = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-3

Figure 14-4. RTC Trim Adjustment (TSGN = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-3

Figure 19-1. ADC Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-1

Figure 20-1. LCD Controller Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-1

Figure 20-2. LCD Drive Voltage Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-8

Figure 20-3. LCD Internal and External Display Contrast Adjustment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-9

Figure 20-4. Sample 7-Segment LCD Display. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-13

Figure 20-5. Static Drive Example Display Connection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-13

Figure 20-6. Static Drive Example Waveform Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-14

Figure 20-7. 1/2 Duty Drive Example Display Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-15

Figure 20-8. 1/2 Duty Drive Example Waveform Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-16

Figure 20-9. 1/3 Drive Example Display Connection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-16

Figure 20-10. 1/3 Duty Drive Example Waveform Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-17

Figure 20-11. 1/4 Duty Drive Example Display Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-18

Figure 20-12. 1/4 Duty Drive Example Waveform Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-19

Figure 21-1. Timer B Autoreload Mode Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-6

Figure 21-2. Timer B 16-Bit Capture Mode Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-6

Figure 21-3. Timer B 16-Bit Up/Down Count with Autoreload Mode Block Diagram . . . . . . . . . . . . . . . . . . . . . . . .21-7

Figure 21-4. Timer B Clock Output Mode Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-8

Figure 21-5. Up-Count PWM/Output Control Mode Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-9

Figure 21-6. Timer B PWM/Output Control Mode Waveform (Count Up) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-10

Figure 21-7. Timer B Up/Down-Count PWM/Output Control Mode Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . .21-11

Figure 21-8. Timer B PWM/Output Control Mode Waveform (Up/Down Count) . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-11

Figure 24-1. Memory Map When Executing from Utility ROM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-3

ix

Page 10

MAXQ Family User’s Guide:

MAXQ2010 Supplement

LIST OF TABLES

Table 2-1. System Clock Generation and Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

Table 2-2. Interrupt Sources and Control Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

Table 2-3. System Power-Management Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

Table 4-1. System Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-1

Table 4-2. System Register Bit Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-1

Table 4-3. System Register Reset Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-2

Table 4-4. System Clock Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-6

Table 5-1. Peripheral Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-1

Table 5-2. Peripheral Register Bit Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-2

Table 5-3. Peripheral Register Bit Reset Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-4

Table 6-1. Port Pin Special and Alternate Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-1

Table 6-2. Port Pin Input/Output States (in Standard Mode). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-4

Table 10-1. Serial USART Input and Output Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-1

Table 10-2. Serial USART Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-1

Table 11-1. SPI Input and Output Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-1

Table 11-2. SPI Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-1

Table 12-1. Hardware Multiplier Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-1

Table 14-1. RTC Output Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-1

Table 14-2. RTC Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-1

Table 16-1. Output from DebugReadMap Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-2

Table 17-1. Bootloader Status Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-1

Table 17-2. Bootloader Status Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-3

Table 18-1. Instruction Set Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-1

Table 19-1. ADC Input and Power-Supply Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-2

Table 19-2. ADC Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-2

Table 19-3. ADC Sample Rates Using a 10MHz Crystal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-6

Table 20-1. LCD Display Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-8

Table 20-2. Approximate LCD Frame Frequencies (Hz) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-9

Table 20-3. LCD Display Memory Map (Static) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-10

Table 20-4. LCD Display Memory Map (1/2 Duty) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-11

Table 20-5. LCD Display Memory Map (1/3 Duty) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-11

Table 20-6. LCD Display Memory Map (1/4 Duty) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-12

Table 20-7. Static Drive Example Common Signal Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-14

Table 20-8. Static Drive Example Register Content . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-14

Table 20-9. 1/2 Duty Drive Example Common Signal Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-15

Table 20-10. 1/2 Duty Drive Example Register Content . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-15

Table 20-11. 1/3 Duty Drive Example Common Signal Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-17

Table 20-12. 1/3 Duty Drive Example Register Content . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-17

x

Page 11

MAXQ Family User’s Guide:

MAXQ2010 Supplement

LIST OF TABLES (continued)

Table 20-13. 1/4 Duty Drive Example Common Signal Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-18

Table 20-14. 1/4 Duty Drive Example Register Content . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-18

Table 21-1. Type B Timer/Counter Input and Output Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-1

Table 21-2. Type B Timer/Counter Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-1

Table 21-3. Timer/Counter B Mode Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-5

Table 21-4. Timer B PWM/Output Control Function. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-8

Table 22-1. I2C Input and Output Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-1

Table 22-2. I2C Interface Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-1

Table 24-1. Functions for MAXQ2010 Utility ROM Version 1.00 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-1

xi

Page 12

MAXQ Family User’s Guide:

MAXQ2010 Supplement

ADDENDUM TO SECTION 1: OVERVIEW

This document is provided as a supplement to the MAXQ Family User’s Guide, covering new or modified features

specific to the MAXQ2010. This document must be used in conjunction with the MAXQ Family User’s Guide, available

on our website at www.maxim-ic.com/MAXQUG. Addenda are arranged by section number, which correspond to

sections in the MAXQ Family User’s Guide. Additions and changes, with respect to the MAXQ Family User’s Guide,

are contained in this document, and updates/additions are added when available.

The MAXQ2010 is a low-power, high-performance, 16-bit, RISC microcontroller based on the MAXQM architecture

design. It includes support for integrated, in-system-programmable, flash memory and a wide range of peripherals

including an 8-channel, 12-bit successive-approximation analog-to-digital converter (SAR ADC) and an LCD driver

supporting up to 1/4-duty multiplexed displays. The MAXQ2010 is uniquely suited for any application that requires high

performance and low-power operation.

1.1 References

Refer to the MAXQ Family User’s Guide for the following information:

• Description of the core architecture, instruction set, and memory mapping common to all MAXQ microcontrollers.

• Definitions and functions of the common system register set, including accumulators, data pointers, loop counters,

and general-purpose registers.

• Descriptions of common clock generation, interrupt handling, and reset/power-management modes.

• Descriptions and programming examples for common MAXQ peripherals found on the MAXQ2010 including the

serial universal synchronous/asynchronous receiver-transmitter (USART), SPIK interface, and hardware multiplier.

• Description of the test access port (TAP) and in-circuit debug interface.

• Description of the in-system programming mode.

The MAXQ2010 data sheet, which contains electrical/timing specifications and pin descriptions, is available at

www.maxim-ic.com/MAXQ2010.

Errata sheets for the MAXQ2010 and other MAXQ micros are available at www.maxim-ic.com/errata.

For more information on other MAXQ microcontrollers, development hardware and software, frequently asked questions, and software examples, visit the MAXQ page at www.maxim-ic.com/MAXQ.

MAXQ is a registered trademark of Maxim Integrated Products, Inc.

SPI is a trademark of Motorola, Inc.

1-1

Page 13

MAXQ Family User’s Guide:

MAXQ2010 Supplement

ADDENDUM TO SECTION 2: ARCHITECTURE

The MAXQ2010 shares the common architecture features with other members of the MAXQ microcontroller family.

Details are discussed in the following sections.

2.1 Instruction Set

This device uses the standard 16-bit MAXQ20 core instruction set as described in the MAXQ Family User’s Guide.

2.2 Harvard Memory Architecture

Program memory, data memory, and register space follow the Harvard architecture model. Each type of memory

is kept separate and is accessed by a separate bus, allowing different word lengths for different types of memory.

Registers can be either 8 bits or 16 bits in width. Program memory is 16 bits in width to accommodate the standard

MAXQ20 16-bit instruction set. Data memory is also 16 bits in width, but can be accessed in 8-bit or 16-bit modes for

maximum flexibility.

The MAXQ2010 includes a flexible memory-management unit (MMU) that allows code to be executed from either the

program flash, the utility ROM, or the internal data SRAM. Any of these three memory spaces can also be accessed

in data space at any time, with the single restriction that the physical memory area that is currently being used as program space cannot be simultaneously read from in data space. In the event that it is necessary to read data from the

program segment that is currently in use (for example, when executing code from program flash that utilizes a lookup

table also located in program flash), standardized data transfer functions provided in the utility ROM can be used to

do so. See Section 24: Utility ROM for more details.

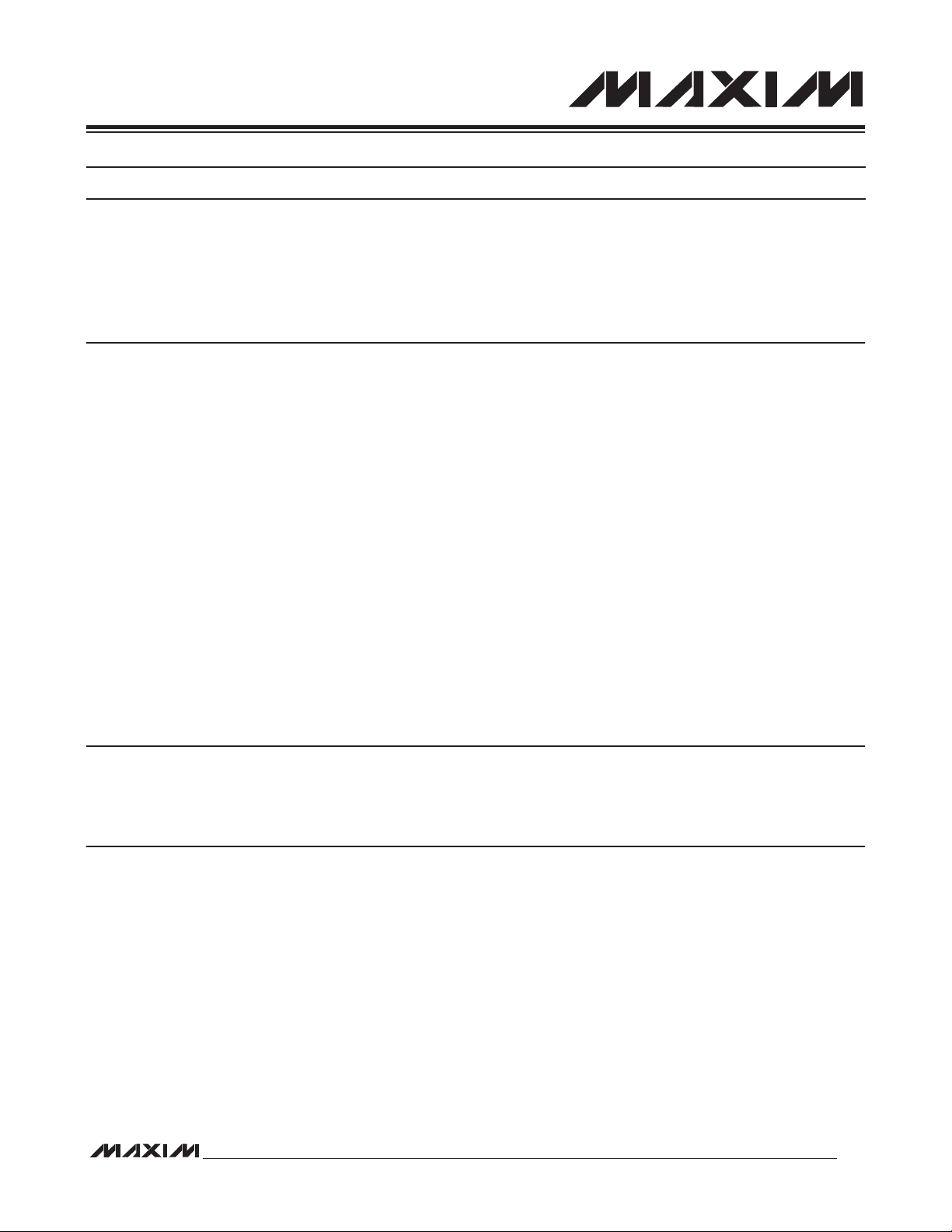

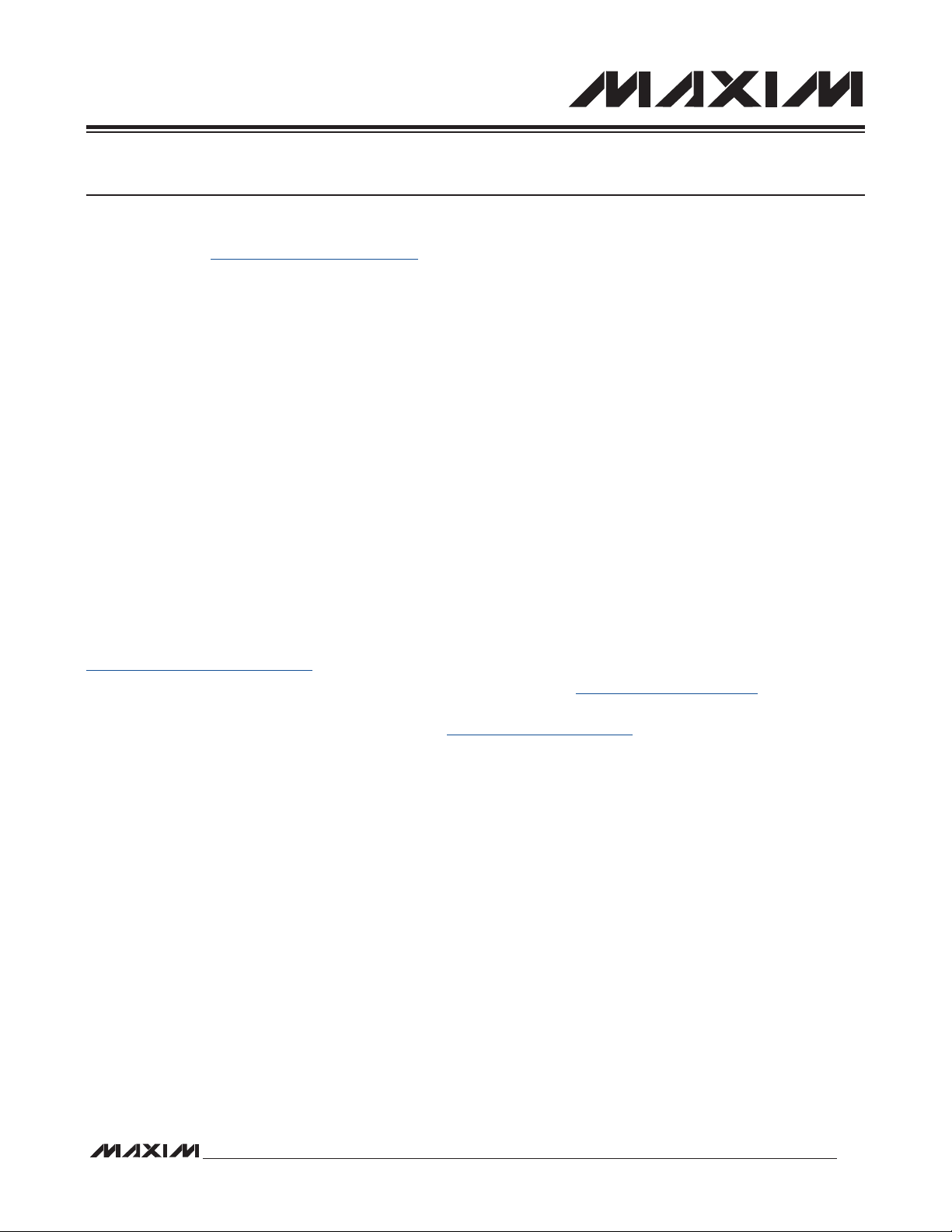

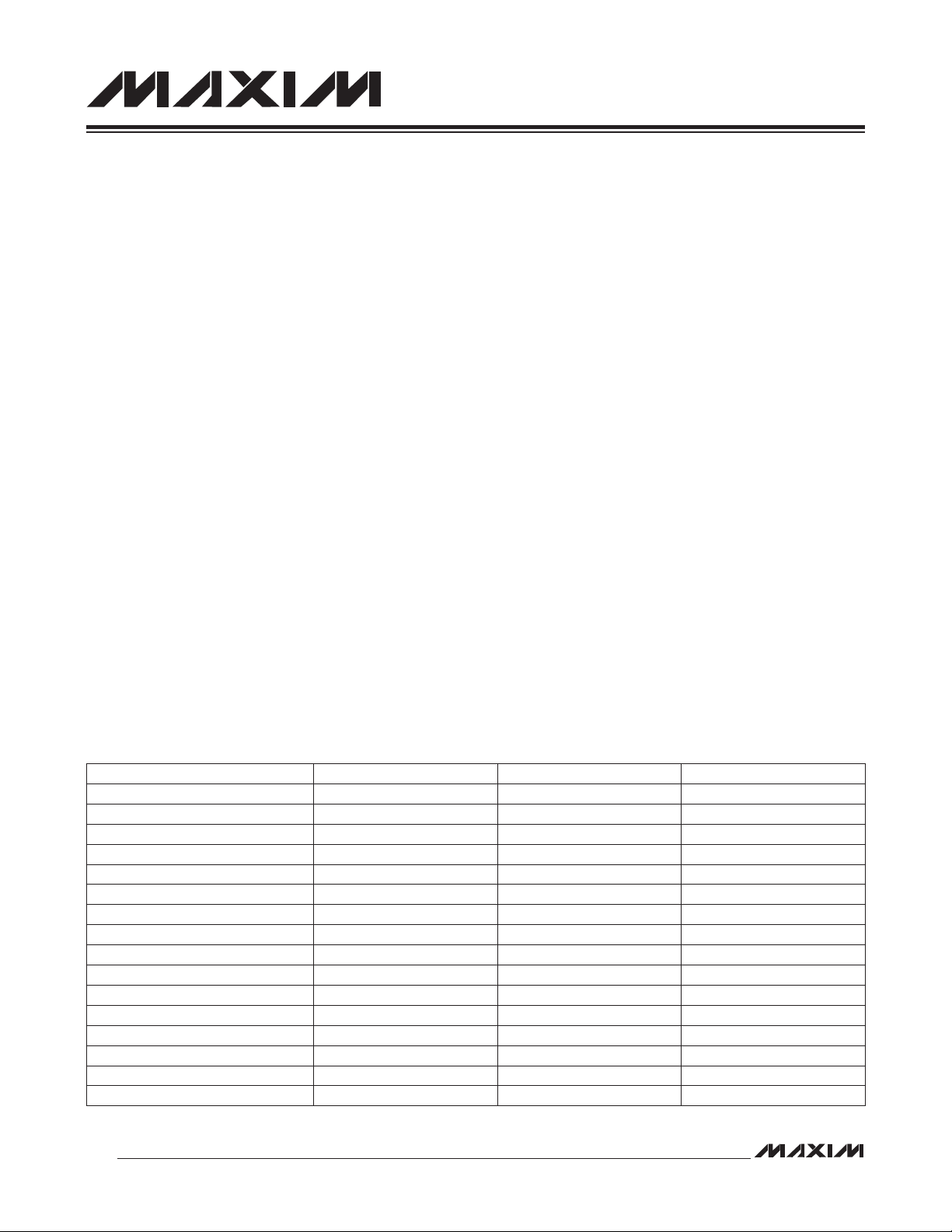

2.3 Register Space

The MAXQ2010 contains the standard set of MAXQ20 system registers as described in the MAXQ Family User’s Guide,

but with differences noted in this guide where they exist.

Peripheral register space (modules 0 to 4) contains registers that are used to access the following peripherals:

• 12-bit SAR ADC converter with up to eight single-ended or four differential input channels

• General-purpose 8-bit I/O ports (P0 to P6)

• External interrupts (up to 23)

• Three programmable Type B timer/counters

• Two serial USART interfaces

• I2C interface

• SPI interface

• Hardware multiplier

• Real-time clock (RTC)

• LCD controller

The lower 8 bits of all registers in modules 0 to 4 (as well as the AP module M8) are bit addressable.

2-1

Page 14

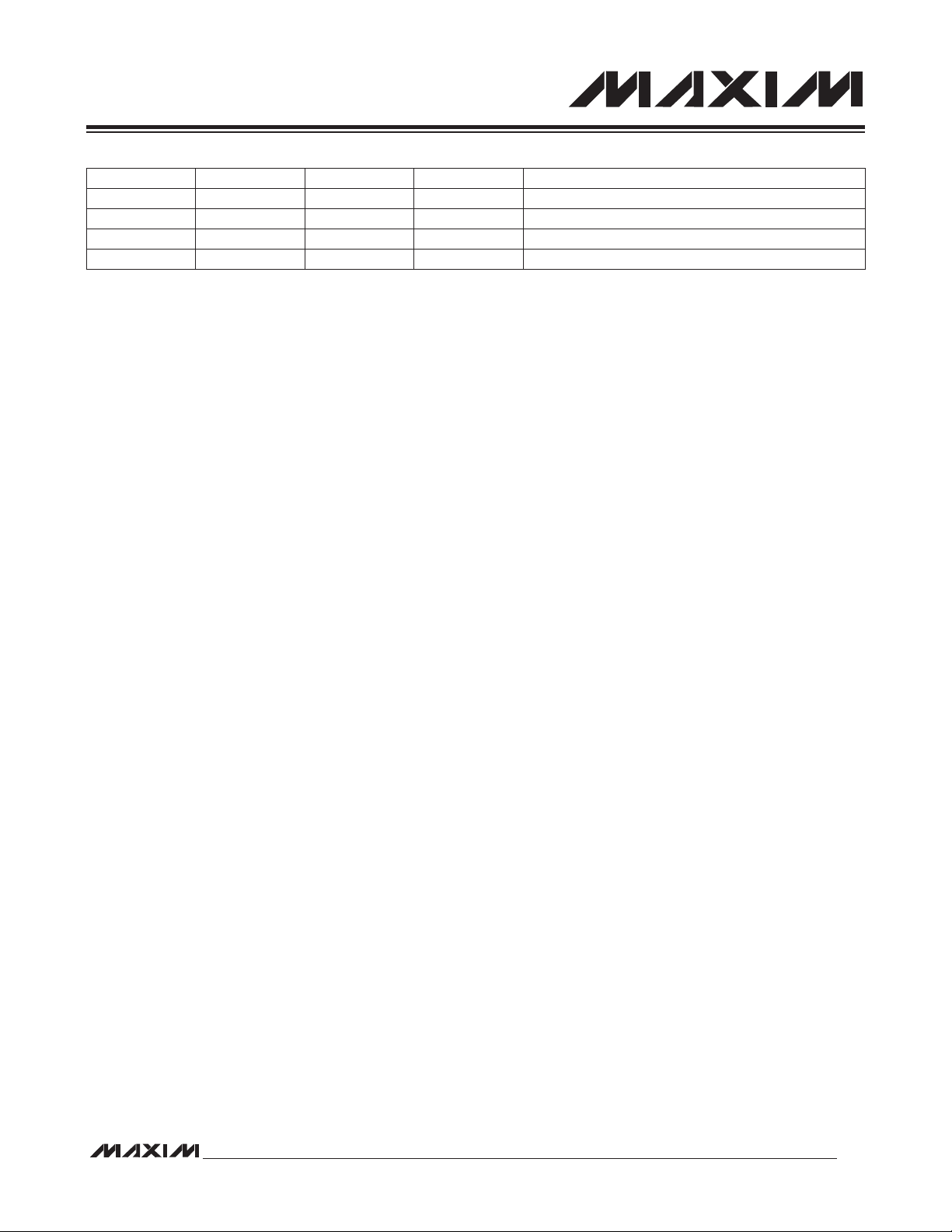

OOh

O1h

O2h

O3h

O4h

O5h

O6h

O7h

O8h

O9h

0Ah

OBh

OCh

ODh

OEh

OFh

10h

REGISTER INDEX

11h

12h

13h

14h

15h

16h

17h

18h

19h

1Ah

1Bh

1Ch

1Dh

1Eh

1Fh

MAXQ Family User’s Guide:

REGISTER MODULE

M0 M1 M2 M3 M4 M8 M9

PO0

PO1

PO2

PO3

EIFO MC1 TB2REIF1

PD0 PD4 LCD5

PD1

PD2 PD6

PD3

SPICN

SPICF LCD11

SPICK LCD12

RTRM LCD13

RCNT LCD14

RTSS LCD15

RTSH LCD16

RTSL LCD17

RSSA LCD18

RASH LCD19

RASL LCD20

MCNT

PO4 I2CBUF TBOR AP A[O] IP

MA

PO5

PO6

SPIB

SVM

PD5

MB

MC2

LCD6

LCD7

LCD8

LCD9

LCD10

I2CST

I2CIE

SCON0

SBUFO ICEIEO MC0 TB2CEIE1

SCON1 IMRLCFG ADSTEIF2

SBUF1 ADADDREIE2

SMD0 SCPIO MC1R TB0CNP14

PR0PI1 MC0R TBOVPI5

SMD1PF2 LCRA TB1CNPI6

PR1 IIRP13 LCD0 TB1VEIES1

I2CCNEIES0 LCD1 TB2CNEIES2

I2CCKLCD2 TB2V

I2CTOLCD3 ADCN

I2CSLALCD4PWCN

TBOC

TB1R

TB1C

ADDATA

APC A[1]

PSF

CKCN

WDCN

MAXQ2010 Supplement

A[2]

A[3]

A[4]

A[5]

A[6]

A[7]

A[8]

A[9]

A[10]

A[11]

A[12]

A[13]

A[14]

A[15]

M11

PFX

M12 M13 M14 M15

SP

IV

OFFS DP[O]

DPC

GR

LC[0] GRL

BPLC[1] DP[1]

GRS

GRH

GRXL

BP[OFFS]

RESERVED

OR

OP CODE

8-CHANNEL

SAR ADC

PORT PINS

(GPIO)

REAL-TIME

CLOCK

INTERRUPT

CONTROL

Figure 2-1. MAXQ2010 System and Peripheral Register Map

2-2

HARDWARE

MULTIPLIER

SERIAL,

SPI, I

2

C

LCD

CONTROLLER

TIMERS

ACC

ARRAY,

CONTROL

OTHER

FUNCTIONS

Page 15

MAXQ Family User’s Guide:

MAXQ2010 Supplement

2.4 Memory Organization

As with all MAXQ microcontrollers, the MAXQ2010 contains logically separate program and data memory spaces. All

memory is internal, and physical memory segments (other than the stack and register memories) can be accessed as

either program memory or as data memory, but not both at once.

The MAXQ2010 contains the following physical memory segments.

2.4.1 Register Space

As described in the MAXQ Family User’s Guide, register space on MAXQ microcontrollers consists of 16 register modules, each of which could contain up to 32 registers. Of these possible 16 register modules, only 12 are used on the

MAXQ2010: seven for system registers and five for peripheral registers.

2.4.2 Program Stack

The MAXQ2010 provides a 16 x 16 hardware stack to support subroutine calls and system interrupts. This stack is used

automatically by CALL/RET and PUSH/POP instructions, and can also be accessed directly through the SP register as

described in the MAXQ Family User’s Guide.

When using the in-circuit debugging features, one word of the stack must be reserved to store the return location when

execution branches into the debugging routines in the utility ROM. If in-circuit debug is not used, the entire stack is

available for application use.

2.4.3 Data SRAM

The MAXQ2010 contains up to 1024 words (2KB) of on-chip data SRAM, which can be mapped into either program or

data space. The contents of this SRAM are indeterminate after power-on reset, but are maintained during stop mode

and across non-POR resets.

When using the in-circuit debugging features, the highest 19 bytes of the SRAM must be reserved for saved state storage and working space for the debugging routines in the utility ROM. If in-circuit debug is not used, the entire SRAM

is available for application use.

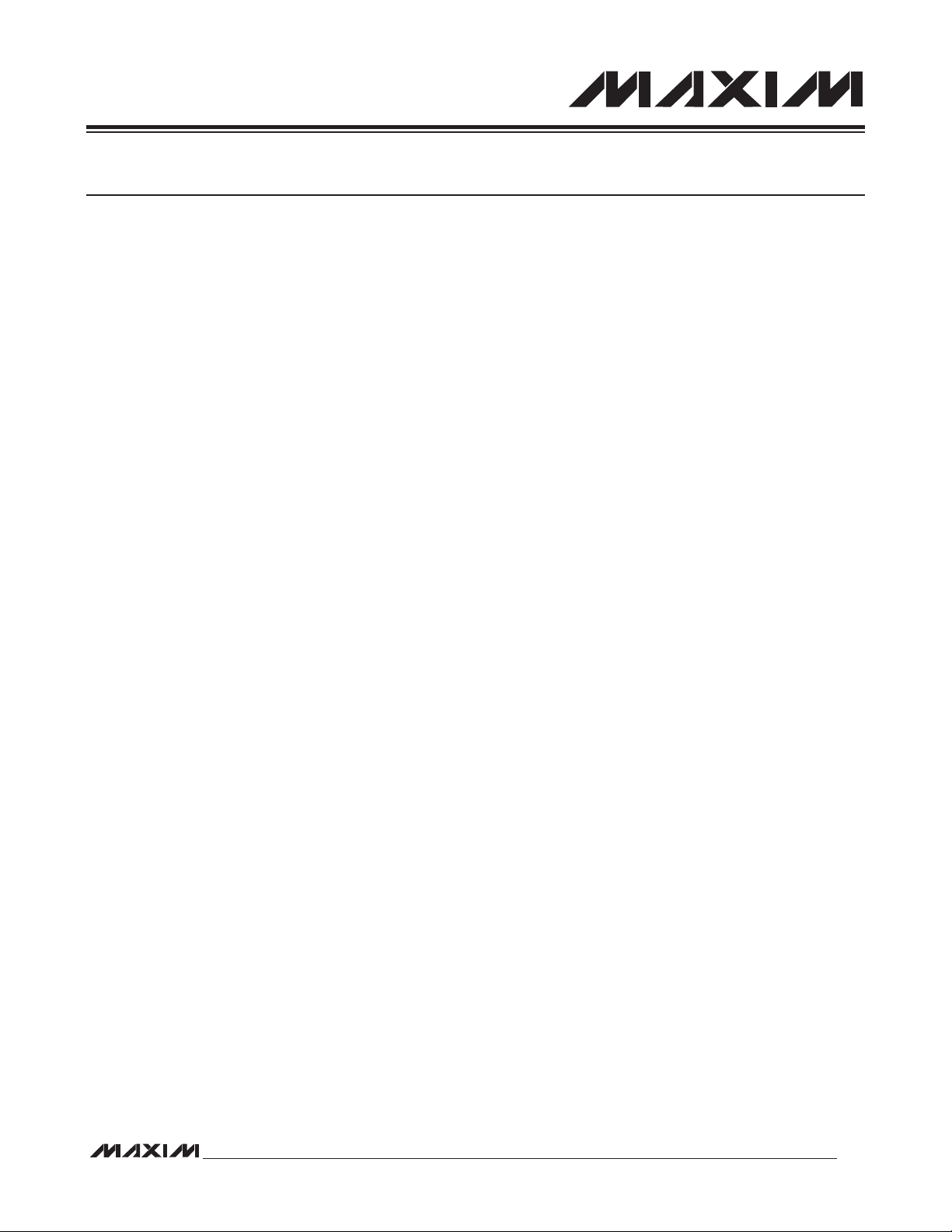

2.4.4 Program Flash

The MAXQ2010 contains 32KWords (32K x 16) of flash memory, which normally serves as program memory. When

executing from the data SRAM or utility ROM, this memory is mapped to data space (as 32KWords or 64KB) and can

be used for lookup tables and similar functions.

Since program memory is mapped into data space starting at address 8000h, only half the available program memory

can be mapped into data space at one time when operating in byte-access mode. The CDA0 (code data access) bit

is used to control which half of program memory is available in data space as shown in Figure 2-3 and Figure 2-4, and

as described in the MAXQ Family User’s Guide. When operating in word-access mode, the entire 32KWord program

memory can be mapped into data space at once.

Flash memory mapped into data space can be read from directly, like any other type of data memory. However, writing

to flash memory must be done indirectly by calling the in-application functions provided by the utility ROM. See Section

24: Utility ROM for more details.

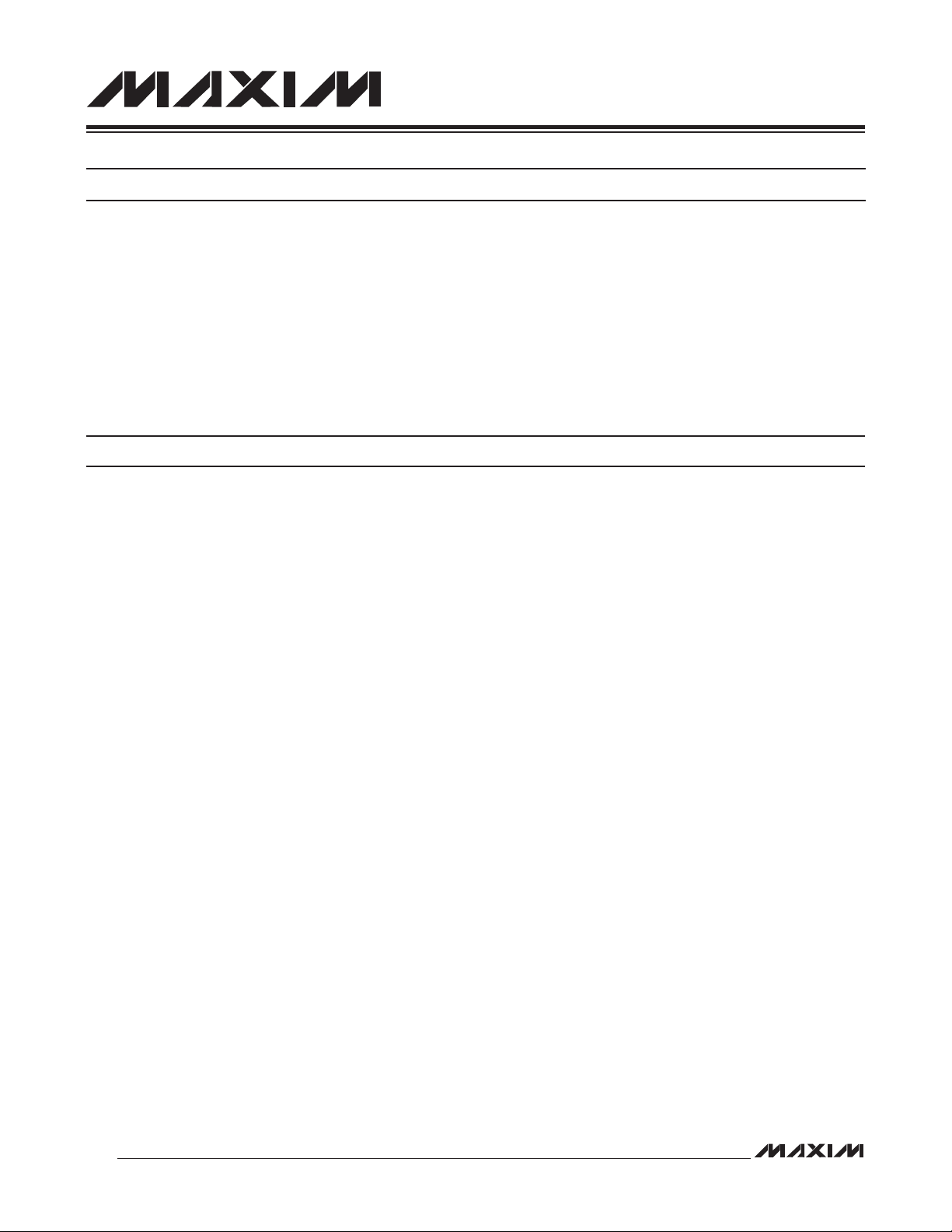

2.5 Program and Data Memory Mapping

Figures 2-2, 2-3, and 2-4 show the mapping of physical memory segments into the program and data memory space.

The mapping of memory segments into program space is always the same. The mapping of memory segments into

data space varies depending on which memory segment is currently being executed from.

In all cases, whichever memory segment is currently being executed from in program space may not be accessed in

data space.

2-3

Page 16

MAXQ Family User’s Guide:

MAXQ2010 Supplement

DATA SPACE

(BYTE MODE)

4K x 8

UTILITY ROM

2K x 8

DATA SRAM

EXECUTING FROM

PROGRAM

SPACE

1K x 16

DATA SRAM

2K x 16

UTILITY ROM

32K x 16

PROGRAM FLASH

FFFFh

A3FFh

A000h

87FFh

8000h

7FFFh

0000h

Figure 2-2. Memory Map When Executing from Program Flash Memory

DATA SPACE

(WORD MODE)

FFFFh FFFFh

8FFFh

8000h

07FFh

0000h

2K x 16

UTILITY ROM

1K x 16

DATA SRAM

87FFh

8000h

03FFh

0000h

EXECUTING FROM

PROGRAM

SPACE

1K x 16

DATA SRAM

2K x 16

UTILITY ROM

16K x 16

PROGRAM FLASH

(PAGE 1)

16K x 16

PROGRAM FLASH

(PAGE 0)

DATA SPACE

(BYTE MODE, CDA0 = 0)

FFFFh FFFFh

A3FFh

A000h

87FFh

8000h

7FFFh

4000h

3FFFh

0000h

32K x 8

LOWER HALF

(PAGE 0) OF

PROGRAM FLASH

MEMORY

8000h

07FFh

2K x 8

DATA SRAM

0000h

DATA SPACE

(BYTE MODE, CDA0 = 1)

32K x 8

UPPER HALF

(PAGE 1) OF

PROGRAM FLASH

MEMORY

2K x 8

DATA SRAM

FFFFh

8000h

07FFh

0000h

DATA SPACE

(WORD MODE)

FFFFh

32K x 16

PROGRAM FLASH

8000h

03FFh

1K x 16

DATA SRAM

0000h

Figure 2-3. Memory Map When Executing from Utility ROM

2-4

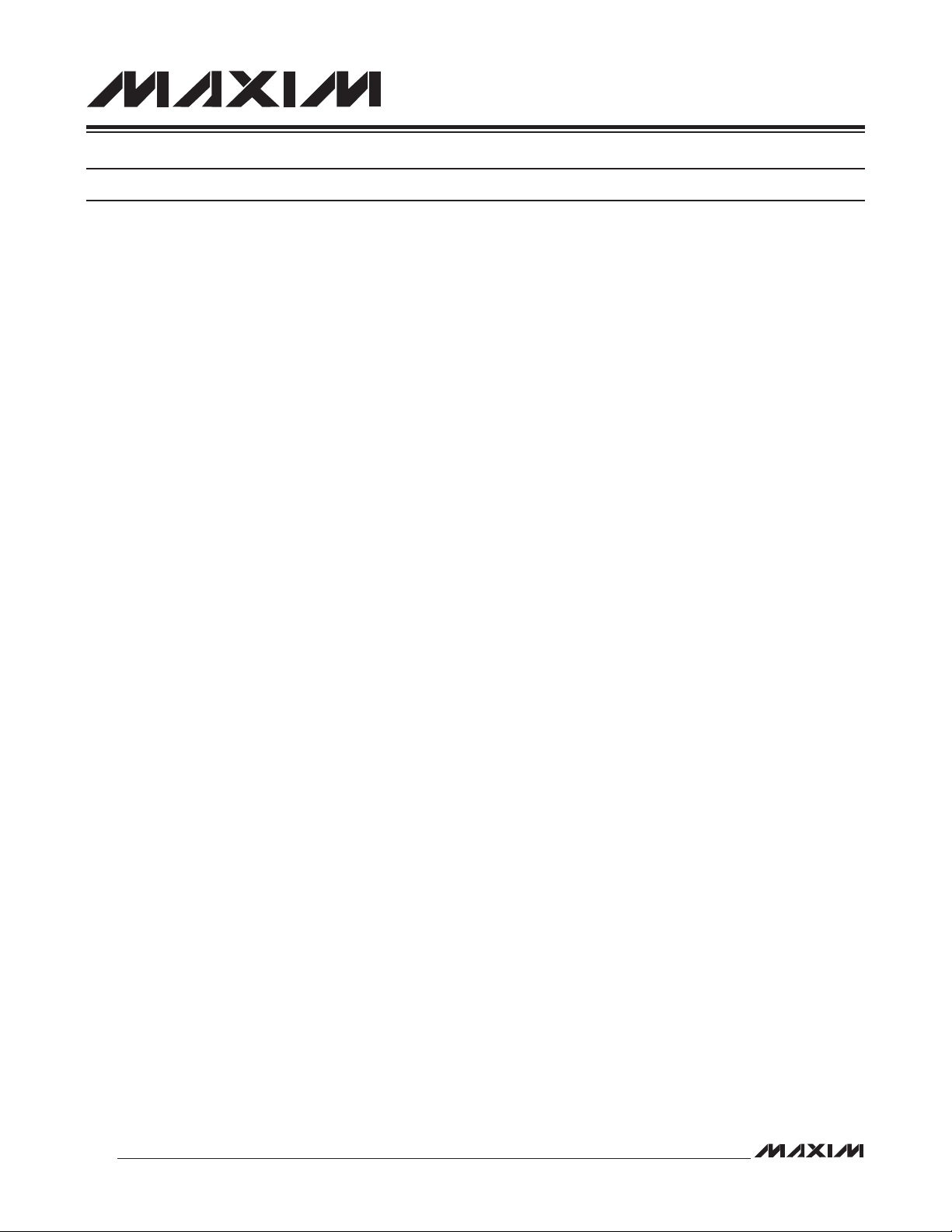

Page 17

MAXQ Family User’s Guide:

MAXQ2010 Supplement

EXECUTING FROM

PROGRAM

SPACE

1K x 16

DATA SRAM

2K x 16

UTILITY ROM

16K x 16

PROGRAM FLASH

(PAGE 1)

16K x 16

PROGRAM FLASH

(PAGE 0)

DATA SPACE

(BYTE MODE, CDA0 = 0)

FFFFh FFFFh

A3FFh

A000h

87FFh

4K x 8

UTILITY ROM

8000h

7FFFh

4000h

3FFFh

0000h

32K x 8

LOWER HALF

(PAGE 0) OF

PROGRAM FLASH

MEMORY

8000h

7FFFh

0000h

DATA SPACE

(BYTE MODE, CDA0 = 1)

4K x 8

UTILITY ROM

32K x 8

UPPER HALF

(PAGE 1) OF

PROGRAM FLASH

MEMORY

FFFFh

8000h

7FFFh

0000h

DATA SPACE

(WORD MODE)

FFFFh

87FFh8FFFh8FFFh

2K x 8

UTILITY ROM

8000h

7FFFh

32K x 16

PROGRAM FLASH

0000h

Figure 2-4. Memory Map When Executing from Data SRAM

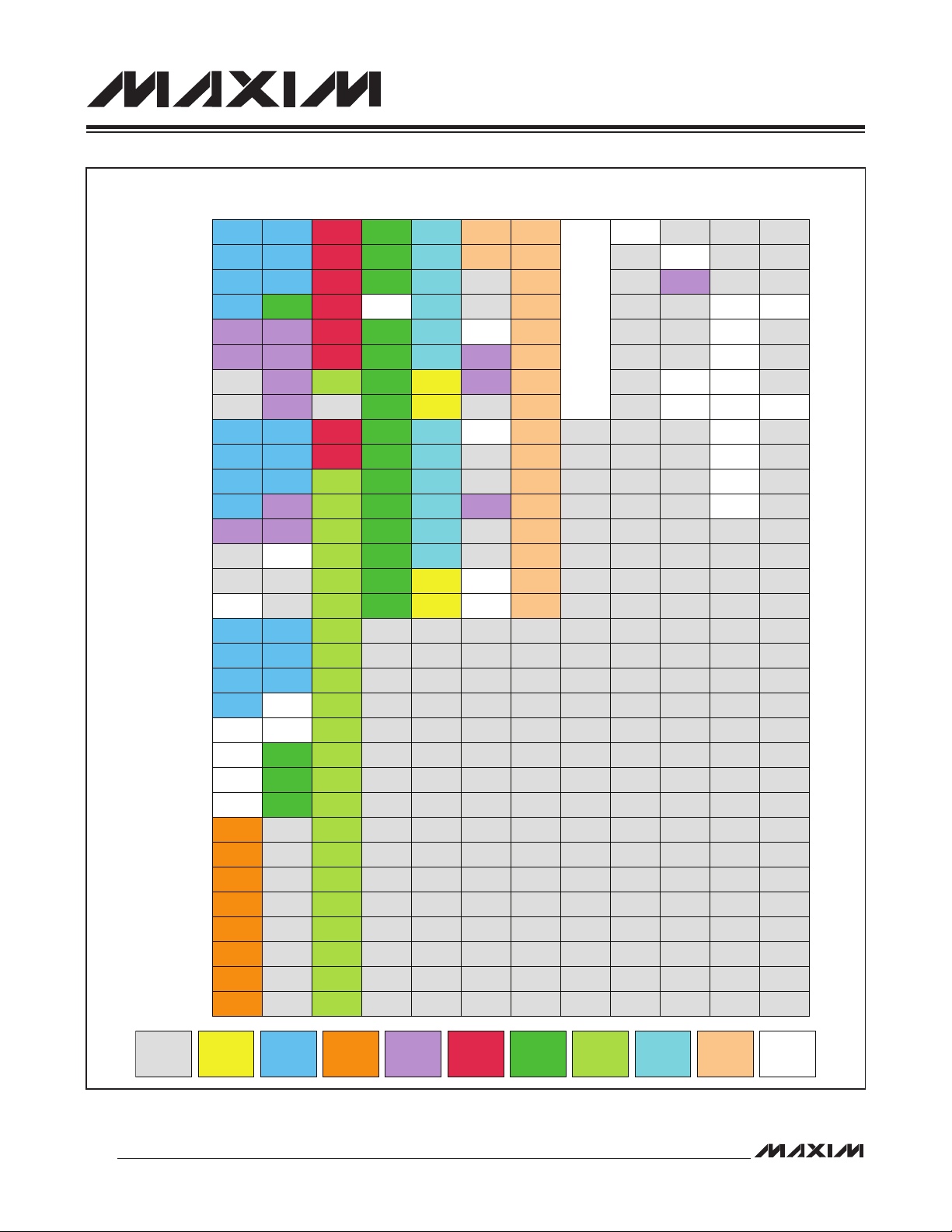

2.6 Clock Generation

All functional modules in the MAXQ2010 are synchronized to a single system clock. This system clock can be generated from one of the following clock sources:

• External high-frequency clock

• Internal high-frequency oscillator using external crystal or resonator circuit

• External 32kHz clock

• Internal 32kHz oscillator using external crystal or resonator circuit

• 256x frequency-locked loop (FLL) using 32kHz clock as an input source

The MAXQ2010 does not support an external RC relaxation oscillator circuit, and the FLL takes the place of the ring

oscillator found in some other devices. The 32kHz crystal oscillator could also be used directly by the LCD controller

and the RTC, regardless of the currently selected system clock source.

The following registers and bits are used to control clock generation and selection. For more information, see the register descriptions in this guide and in the MAXQ Family User’s Guide.

2.6.1 External High-Frequency Oscillator Circuit

The high-frequency oscillator operates as described in Section 2.7: Clock Generation of the MAXQ Family User’s

Guide. If used, the external crystal or resonator circuit for this oscillator should be connected between the HFXIN and

HFXOUT pins.

The high-frequency oscillator can be disabled by setting HFXD (PWCN.4) to 1; this is only allowed if the high-frequency

oscillator is not currently being used as the clock source (FLLMD and FLLSL must both equal 1). In this configuration,

an external clock can be used to directly drive HFXIN; refer to the IC data sheet for more details.

2-5

Page 18

MAXQ Family User’s Guide:

MAXQ2010 Supplement

POWER-ON

RESET

STOP

CRYSTAL KLL

HF

CRYSTAL

FLL

ENABLE

32kHz

CRYSTAL

RESET XDOG COUNT

XDOG

STARTUP

TIMER

CLK INPUT

MUX

GLITCH-FREE

XDOG DONE

MAXQ2010

CLOCK

DIVIDER

WAKE-UP

TIMER, LCD

CONTROLLER

DIV 1

DIV 2

SELECTOR

MUX

GLITCH-FREE

DIV 4

DIV 8

32kHz

PMM1

DEFAULT

FLL SELECT

RESET DOG

WATCHDOG

TIMER

ENABLE

CLOCK

GENERATION

RWT

RESET

WATCHDOG RESET

WATCHDOG INTERRUPT

SYSTEM CLOCK

SWB

INTERRUPT/SERIAL PORT

RESET

STOP

STOP

POWER-ON

RESET

INPUT

CRYSTAL

MONITOR

ENABLE

FLLMD

POWER-ON RESET

XDOG DONE

FLLSL

Figure 2-5. MAXQ2010 Clock Sources

2.6.2 External 32kHz Crystal Oscillator Circuit

The 32kHz oscillator operates as described in Section 2.7: Clock Generation of the MAXQ Family User’s Guide. It cannot be used directly as a system clock source, but instead works as an input to the FLL. It can also be used directly by

the LCD controller and RTC modules, regardless of the current system clock source selection. This clock can be generated by an internal 32kHz crystal oscillator, using an external crystal connected between the 32KIN and 32KOUT pins.

Setting X32D (PWCN.2) to 1 disables the 32kHz clock source completely. This should only be done when all the following conditions are true:

• Either the high-frequency oscillator is being used as the system clock source, or if the FLL is being used as the

system clock source, it is already enabled and locked.

• The 32kHz clock is not being used to drive either the RTC or the LCD controller.

If X32D = 0, the control bit X32KBYP (PWCN.5) can be used to switch between the internal oscillator and external

32kHz clock modes of operation.

2-6

Page 19

MAXQ Family User’s Guide:

MAXQ2010 Supplement

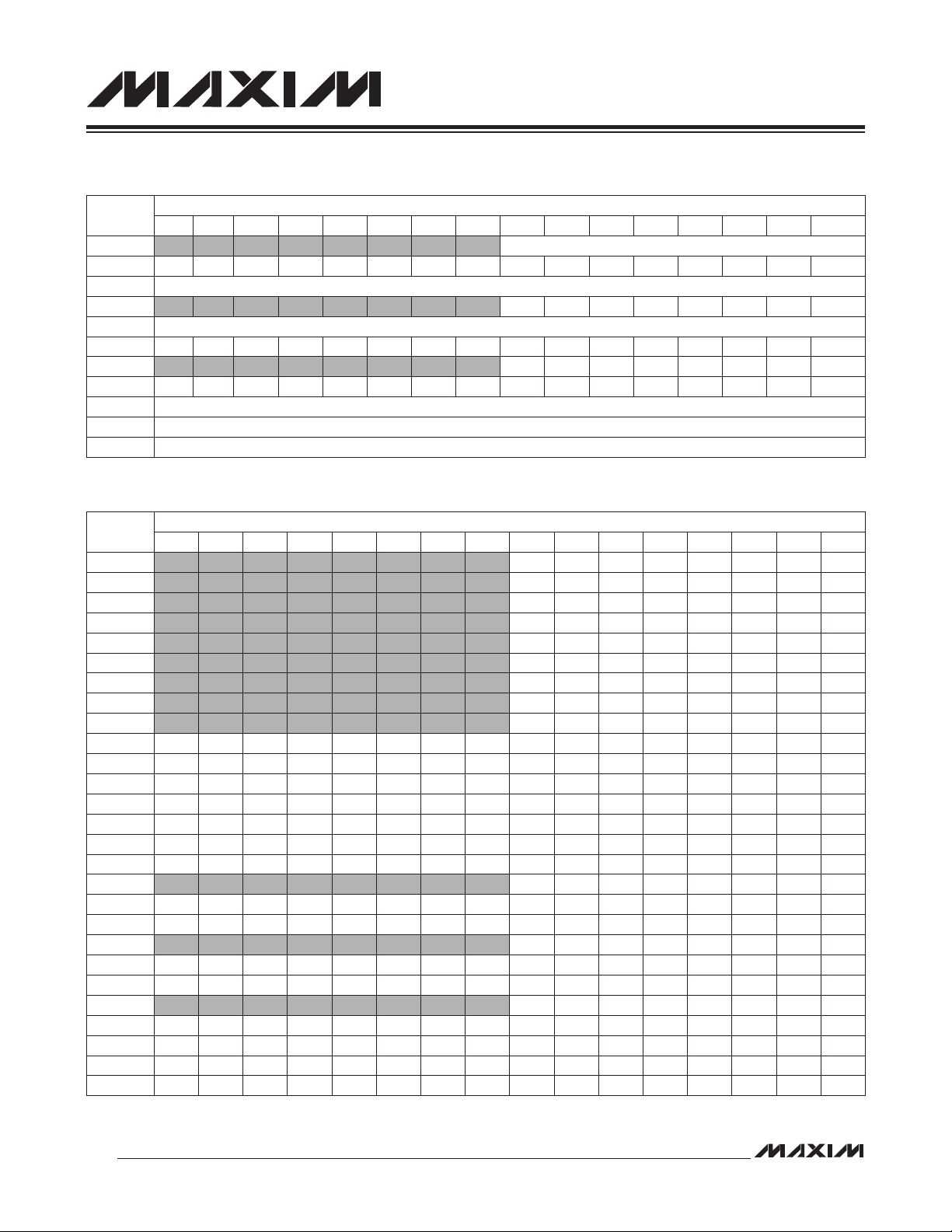

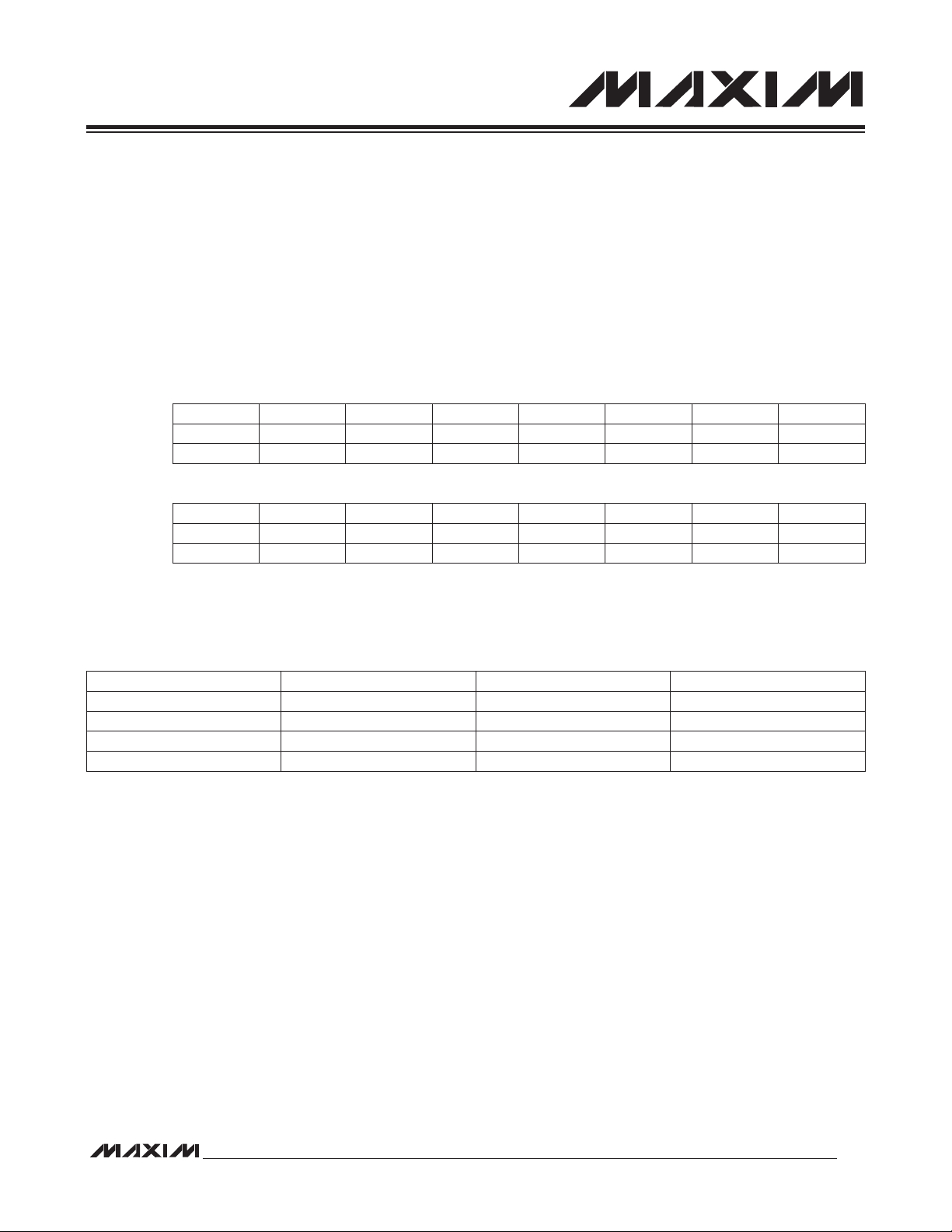

Table 2-1. System Clock Generation and Control Registers

REGISTER ADDRESS BIT(S) FUNCTION

000: System clock = high-frequency clock divided by 1.

001: System clock = high-frequency clock divided by 2.

010: System clock = high-frequency clock divided by 4.

011: System clock = high-frequency clock divided by 8.

1xx: System clock = high-frequency clock/256.

CKCN M8[0Eh]

[2:0]—PMME,

CD[1:0]

CKCN M8[0Eh] 5—FLLMD

CKCN M8[0Eh] 6—FLLSL

PWCN M0[0Fh] 0—FLLEN

PWCN M0[0Fh] 1—FLOCK

PWCN M0[0Fh] 2—X32D

PWCN M0[0Fh] 3—X32KRDY

PWCN M0[0Fh] 4—HFXD

PWCN M0[0Fh] 5—X32KBYP

PWCN M0[0Fh] [9:8]—X32KMD

0: System clock is being provided by an external source.

1: System clock is being provided by the FLL.

0: Selects an external source for system clock generation.

1: Selects the FLL for system clock generation.

0: Disables the FLL (unless it is providing the system clock).

1: Enables the FLL and locks it to the 32kHz input.

0: Indicates the FLL is disabled or in the process of locking.

1: Indicates the FLL is locked to the 32kHz input.

0: 32kHz clock or oscillator operates normally (default).

1: Disables the 32kHz source completely (except in stop).

0: Indicates the 32kHz oscillator is still warming up.

1: Indicates the 32kHz oscillator is ready for use.

0: High-frequency oscillator operates normally (default).

1: Disables the high-frequency oscillator, allowing an external clock to be

provided at HFXIN.

0: 32kHz clock is provided by internal oscillator (default).

1: Disables the 32kHz oscillator, allowing an external clock to be provided at

32KIN.

00: 32kHz oscillator operates in noise immune mode.

01: 32kHz oscillator operates in quiet mode.

10: 32kHz oscillator operates in noise immune mode normally and in quiet mode

during stop mode. (Note: This setting should not be used on devices of rev

B3 or earlier; refer to the device errata for more details.)

11: 32kHz oscillator operates in quiet mode normally and in noise immune mode

during stop mode.

2.6.3 Frequency-Locked Loop (FLL)

The MAXQ2010 contains an FLL circuit that provides an optional, low-cost method of generating a high-frequency

system clock. The FLL uses the 32kHz clock as an input, multiplying its frequency by 256 to generate a clock output of

approximately 8.4MHz (refer to the IC data sheet for details). This clock output can be used as a system clock source.

On power-on reset, the FLL is automatically enabled as the system clock source while the high-frequency oscillator

warms up. Once the warmup count for the high-frequency oscillator has completed, the clock source switches to the

high-frequency oscillator automatically. If no external crystal or resonator circuit is provided at HFXIN, the switchover

never occurs, and the clock runs from the FLL indefinitely.

To select the FLL as the system clock source permanently, the FLLSL bit (CKCN.6) must be set to 1. Setting this bit

immediately switches over the system clock source to the FLL. The FLLMD (CKCN.5) bit indicates the current system

clock source. If the FLL is currently providing the system clock, FLLMD = 1; otherwise, FLLMD = 0.

Since the FLLSL bit is cleared by power-on reset only, if this bit is set before entering stop mode, the FLL is still used

as the system clock source when stop mode is exited. In this case, a four-cycle warmup delay is required when exiting

stop mode before execution resumes using the FLL as the system clock source.

2-7

Page 20

MAXQ Family User’s Guide:

MAXQ2010 Supplement

When the system clock source is switched back from the FLL to the high-frequency oscillator by clearing FLLSL to

zero, the FLL is still used as the system clock source until the warmup period has completed for the high-frequency

oscillator. This is reflected by the value of the FLLMD bit, which remains at 1 until the warmup for the high-frequency

oscillator has completed and the clock switches over, at which point FLLMD switches to 0.

2.7 Interrupts

In general, interrupt handling on the MAXQ2010 operates as described in the MAXQ Family User’s Guide. All interrupt

sources have the same priority, and all interrupts cause program execution to branch to the location specified by the

Interrupt Vector (IV) register, which defaults to 0000h.

Table 2-2 lists all possible interrupt sources for the MAXQ2010, along with their corresponding module interrupt enable

bits, local interrupt enable bits, and interrupt flags.

• Each module interrupt enable bit, when cleared to 0, blocks interrupts originating in that module from being acknowledged. When the module interrupt enable bit is set to 1, interrupts from that module are acknowledged (unless all

interrupts have been disabled globally).

• Each local interrupt enable bit, when cleared to 0, disables the corresponding interrupt. When the local interrupt-

enable bit is set to 1, the interrupt is triggered whenever its interrupt flag is set to 1 by hardware or by software.

• Each interrupt flag bit, when set to 1, causes its corresponding interrupt to trigger. Interrupt flag bits are typically set

by hardware and must be cleared by software (generally in the interrupt handler routine).

Note that for an interrupt to fire, the following five conditions must exist:

• Interrupts must be enabled globally by setting IGE (IC.0) to 1.

• The module interrupt enable bit for the interrupt source’s module must be set to 1.

• The local interrupt enable bit for the specific interrupt source must be set to 1.

• The interrupt flag for the interrupt source must be set to 1. Typically, this is done by hardware when the condition

that requires interrupt service occurs.

• The interrupt-in-service (INS) bit must be cleared to 0. This bit is set automatically upon vectoring to the interrupt

handler (IV) address and cleared automatically upon exit (RETI/POPI), so the only reason to clear this bit manually

(inside the interrupt handler routine) is to allow nested interrupt handling.

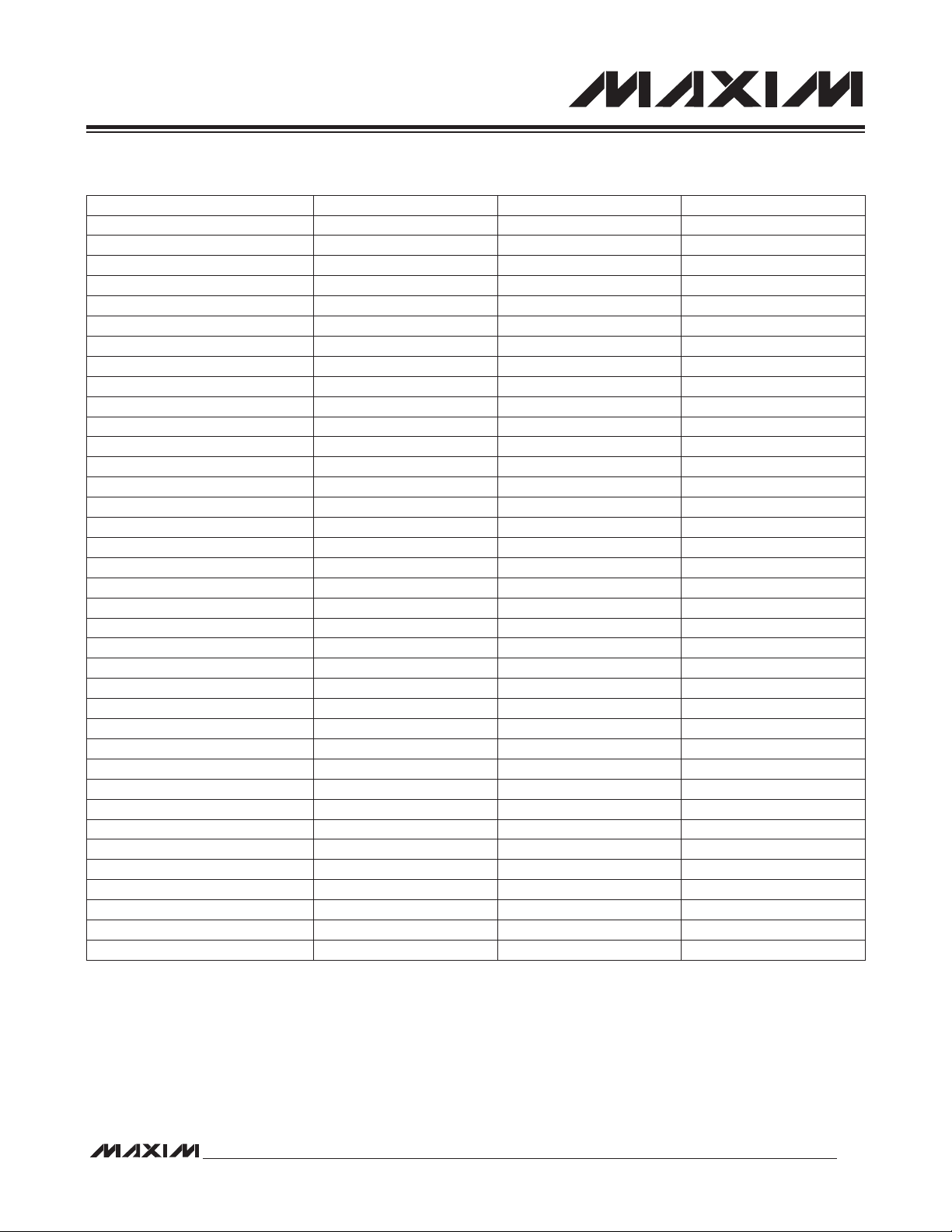

Table 2-2. Interrupt Sources and Control Bits

INTERRUPT MODULE ENABLE BIT LOCAL ENABLE BIT INTERRUPT FLAG

Watchdog Interrupt IMS (IMR.7) EWDI (WDCN.6) WDIF (WDCN.3)

External Interrupt 0 (P0.0) IM0 (IMR.0) EX0 (EIE0.0) IE0 (EIF0.0)

External Interrupt 1 (P0.1) IM0 (IMR.0) EX1 (EIE0.1) IE1 (EIF0.1)

External Interrupt 2 (P0.2) IM0 (IMR.0) EX2 (EIE0.2) IE2 (EIF0.2)

External Interrupt 3 (P0.3) IM0 (IMR.0) EX3 (EIE0.3) IE3 (EIF0.3)

External Interrupt 4 (P0.4) IM0 (IMR.0) EX4 (EIE0.4) IE4 (EIF0.4)

External Interrupt 5 (P0.5) IM0 (IMR.0) EX5 (EIE0.5) IE5 (EIF0.5)

External Interrupt 6 (P0.6) IM0 (IMR.0) EX6 (EIE0.6) IE6 (EIF0.6)

External Interrupt 7 (P0.7) IM0 (IMR.0) EX7 (EIE0.7) IE7 (EIF0.7)

RTC Time-of-Day Alarm IM0 (IMR.0) ADE (RCNT.1) ALDF (RCNT.6)

RTC Subsecond Alarm IM0 (IMR.0) ASE (RCNT.2) ALSF (RCNT.7)

External Interrupt 8 (P5.0) IM1 (IMR.1) EX8 (EIE1.0) IE8 (EIF1.0)

External Interrupt 9 (P5.1) IM1 (IMR.1) EX9 (EIE1.1) IE9 (EIF1.1)

External Interrupt 10 (P5.2) IM1 (IMR.1) EX10 (EIE1.2) IE10 (EIF1.2)

External Interrupt 11 (P5.3) IM1 (IMR.1) EX11 (EIE1.3) IE11 (EIF1.3)

External Interrupt 12 (P5.4) IM1 (IMR.1) EX12 (EIE1.4) IE12 (EIF1.4)

2-8

Page 21

MAXQ Family User’s Guide:

MAXQ2010 Supplement

Table 2-2. Interrupt Sources and Control Bits (continued)

INTERRUPT MODULE ENABLE BIT LOCAL ENABLE BIT INTERRUPT FLAG

External Interrupt 13 (P5.5) IM1 (IMR.1) EX13 (EIE1.5) IE13 (EIF1.5)

External Interrupt 14 (P5.6) IM1 (IMR.1) EX14 (EIE1.6) IE14 (EIF1.6)

External Interrupt 15 (P6.0) IM1 (IMR.1) EX15 (EIE2.0) IE15 (EIF2.0)

External Interrupt 16 (P6.1) IM1 (IMR.1) EX16 (EIE2.1) IE16 (EIF2.1)

External Interrupt 17 (P6.2) IM1 (IMR.1) EX17 (EIE2.2) IE17 (EIF2.2)

External Interrupt 18 (P6.3) IM1 (IMR.1) EX18 (EIE2.3) IE18 (EIF2.3)

External Interrupt 19 (P6.4) IM1 (IMR.1) EX19 (EIE2.4) IE19 (EIF2.4)

External Interrupt 20 (P6.5) IM1 (IMR.1) EX20 (EIE2.5) IE20 (EIF2.5)

External Interrupt 21 (P6.6) IM1 (IMR.1) EX21 (EIE2.6) IE21 (EIF2.6)

External Interrupt 22 (P6.7) IM1 (IMR.1) EX22 (EIE2.7) IE22 (EIF2.7)

Supply Voltage Monitor Interrupt IM1 (IMR.1) SVMIE (SVM.2) SVMI (SVM.3)

SPI Mode Fault Interrupt IM1 (IMR.1) ESPII (SPICF.7) MODF (SPICN.3)

SPI Write Collision Interrupt IM1 (IMR.1) ESPII (SPICF.7) WCOL (SPICN.4)

SPI Receive Overrun Interrupt IM1 (IMR.1) ESPII (SPICF.7) ROVR (SPICN.5)

SPI Transfer Complete Interrupt IM1 (IMR.1) ESPII (SPICF.7) SPIC (SPICN.6)

I2C START Condition Interrupt IM3 (IMR.3) I2CSRI (I2CST.0) I2CSRIE (I2CIE.0)

I2C Transmit Complete Interrupt IM3 (IMR.3) I2CTXI (I2CST.1) I2CTXIE (I2CIE.1)

I2C Receive Ready Interrupt IM3 (IMR.3) I2CRXI (I2CST.2) I2CRXIE (I2CIE.2)

I2C Clock Stretch Interrupt IM3 (IMR.3) I2CSTRI (I2CST.3) I2CSTRIE (I2CIE.3)

I2C Timeout Interrupt IM3 (IMR.3) I2CTOI (I2CST.4) I2CTOIE (I2CIE.4)

I2C Slave Address Match Interrupt IM3 (IMR.3) I2CAMI (I2CST.5) I2CAMIE (I2CIE.5)

I2C Arbitration Loss Interrupt IM3 (IMR.3) I2CALI (I2CST.6) I2CALIE (I2CIE.6)

I2C NACK Interrupt IM3 (IMR.3) I2CNACKI (I2CST.7) I2CNACKIE (I2CIE.7)

I2C General Call Address Interrupt IM3 (IMR.3) I2CGCI (I2CST.8) I2CGCIE (I2CIE.8)

I2C Receiver Overrun Interrupt IM3 (IMR.3) I2CROI (I2CST.9) I2CROIE (I2CIE.9)

I2C STOP Condition Interrupt IM3 (IMR.3) I2CSPI (I2CST.11) I2CSPIE (I2CIE.11)

Serial Port 0 Receive IM3 (IMR.3) ESI (SMD0.2) RI (SCON0.0)

Serial Port 0 Transmit IM3 (IMR.3) ESI (SMD0.2) TI (SCON0.1)

Serial Port 1 Receive IM3 (IMR.3) ESI (SMD1.2) RI (SCON1.0)

Serial Port 1 Transmit IM3 (IMR.3) ESI (SMD1.2) TI (SCON1.1)

ADC Data Available Interrupt IM4 (IMR.4) ADDAIE (ADCN.5) ADDAI (ADST.5)

Type B Timer 0—External Trigger IM4 (IMR.4) EXFB (TB0CN.6) ETB (TB0CN.1)

Type B Timer 0—Overflow IM4 (IMR.4) TFB (TB0CN.7) ETB (TB0CN.1)

Type B Timer 1—External Trigger IM4 (IMR.4) EXFB (TB1CN.6) ETB (TB1CN.1)

Type B Timer 1—Overflow IM4 (IMR.4) TFB (TB1CN.7) ETB (TB1CN.1)

Type B Timer 2—External Trigger IM4 (IMR.4) EXFB (TB2CN.6) ETB (TB2CN.1)

Type B Timer 2—Overflow IM4 (IMR.4) TFB (TB2CN.7) ETB (TB2CN.1)

2.8 Reset Conditions

There are four possible reset sources for the MAXQ2010. While in the reset state, the enabled system clock oscillator

continues running, but no code execution occurs. Once the reset condition has been removed or has completed, code

execution resumes at address 8000h for all reset types.

2-9

Page 22

MAXQ Family User’s Guide:

MAXQ2010 Supplement

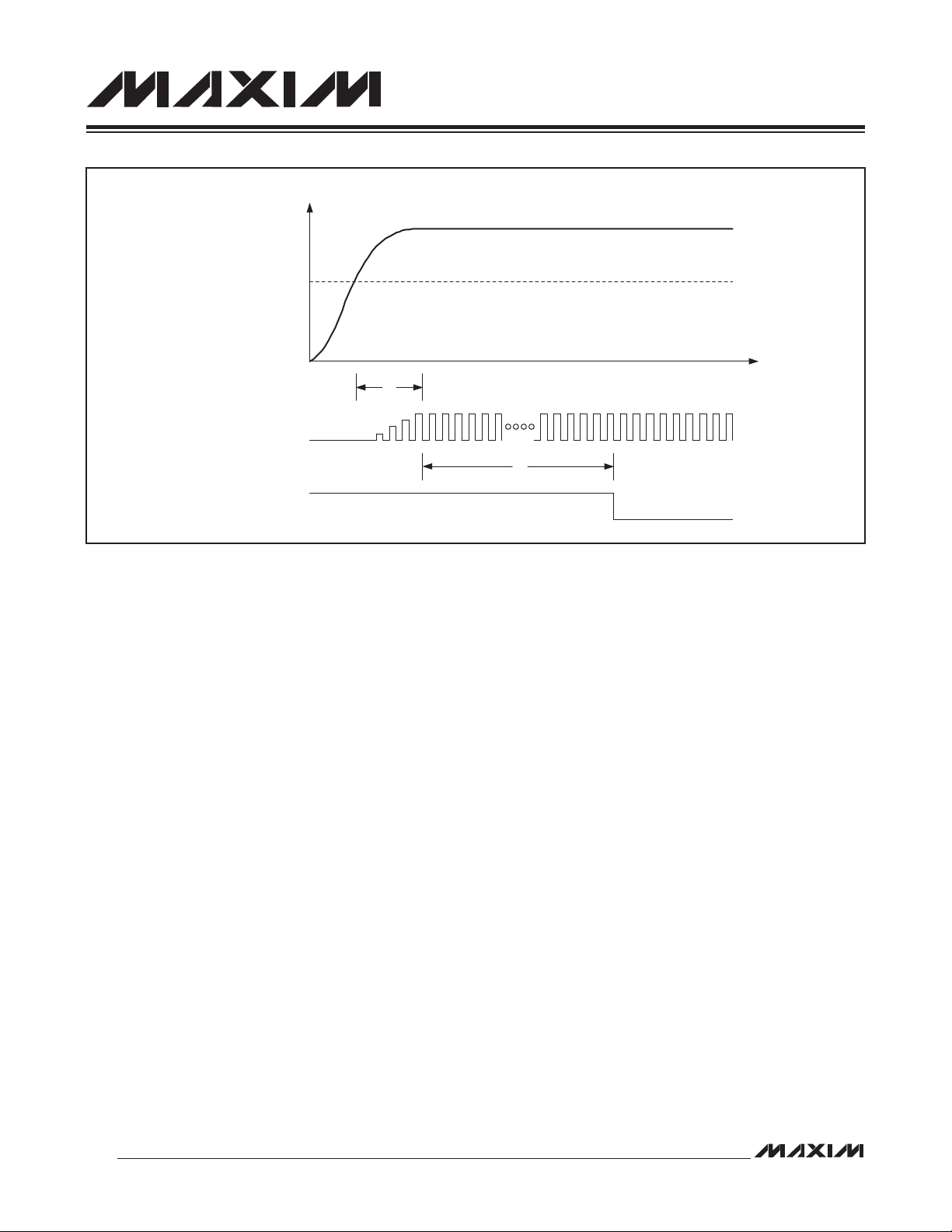

SUPPLY AT V

FREQUENCY-LOCKED LOOP

INTERNAL RESET

Figure 2-6. Power-On Reset Timing

DD

V

RST

T1

(T1 = STARTUP TIME FOR FLL)

T2

(T2 = 65,536 FLL CYCLES, OR 7.84ms AT 8.4MHz)

2.8.1 Power-On Reset

When power is first applied to the MAXQ2010, or when the supply voltage at VDD drops below the V

processor is held in a power-on reset state. See Figure 2-6. For the MAXQ2010 to exit power-on reset, the following

two conditions must apply:

• The supply voltage at VDD is above the power-on reset level V

RST.

• The FLL has completed 65,536 cycles (delay for power supply to stabilize).

level, the

RST

2.8.2 Watchdog Timer Reset

The watchdog timer on the MAXQ2010 functions as described in the MAXQ Family User’s Guide.

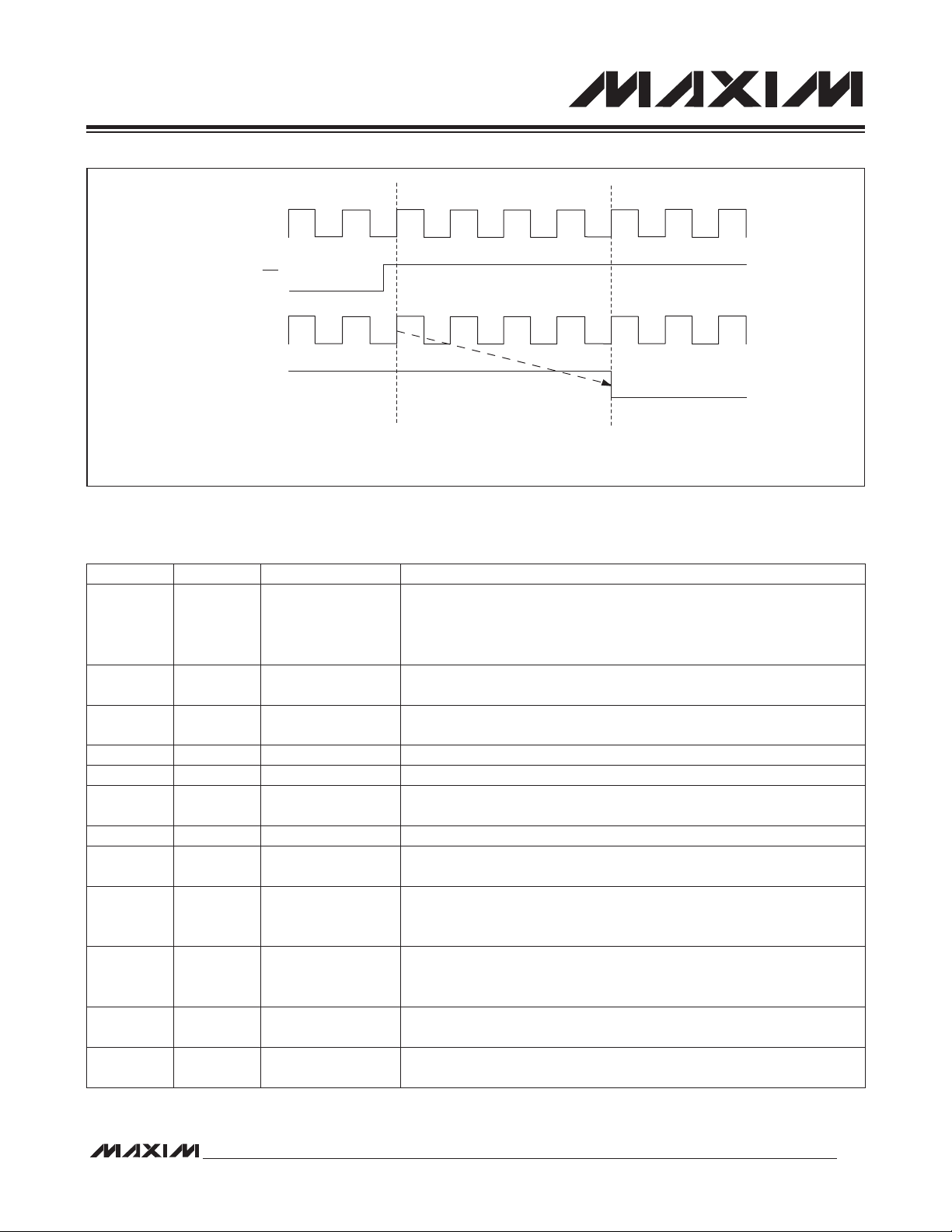

2.8.3 External Reset

External reset through the RST input is a synchronous reset source. After the external reset low has been removed and

sampled, execution resumes following a delay of four clock cycles, as shown in Figure 2-7.

2.9 Power-Management Features

The MAXQ2010 provides the following features to assist in power management:

• Divide-by-256 (PMM) mode to reduce current consumption.

• Switchback mode to exit PMM mode automatically when rapid processing is required.

• Ultra-low-power stop mode.

• Selective regulator and brownout detection disable during stop mode.

• Selectable noise immune mode or quiet mode for 32kHz oscillator operation.

Table 2-3 shows the system registers and bits used to control power-management features. For more information, see

the register descriptions in this document and in the MAXQ Family User’s Guide.

2-10

Page 23

MAXQ Family User’s Guide:

MAXQ2010 Supplement

CLOCK

RST

RESET SAMPLING

INTERNAL RESET

Figure 2-7. External Reset Timing

FIRST

INSTRUCTION

FETCH

Table 2-3. System Power-Management Registers

REGISTER ADDRESS BIT FUNCTION

00: System clock = high-frequency clock divided by 1.

CKCN M8[0Eh] [1:0]—CD[1:0]

CKCN M8[0Eh] 2—PMME

CKCN M8[0Eh] 3—SWB

CKCN M8[0Eh] 4—STOP When set to 1, causes the processor to enter stop mode.

PWCN M0[0Fh] 0—FLLEN When set to 1, enables the FLL and causes it to lock to the 32kHz input.

PWCN M0[0Fh] 1—FLOCK

PWCN M0[0Fh] 2—X32D When set to 1, disables the 32kHz clock source.

PWCN M0[0Fh] 3—X32KRDY

PWCN M0[0Fh] 4—HFXD

PWCN M0[0Fh] 5—X32KBYP

PWCN M0[0Fh] 6—REGEN

PWCN M0[0Fh] 7—BOD

01: System clock = high-frequency clock divided by 2.

10: System clock = high-frequency clock divided by 4.

11: System clock = high-frequency clock divided by 8.

0: System clock is determined by the settings of CD[1:0].

1: System clock = high-frequency clock divided by 256.

When set to 1, enables automatic switchback from PMM (divide-by-256

mode) to normal clock-divide mode under certain conditions.

0: FLL is disabled or warming up.

1: FLL is enabled and locked to the 32kHz input.

Read-only status bit; when 1, indicates that the 32kHz clock is ready for

use.

0: Enables the high-frequency oscillator.