Page 1

General Description

The MAX5865 evaluation kit (EV kit) is a fully assembled

and tested circuit board that contains all the components

necessary to evaluate the performance of the MAX5865

40Msps analog front end. The MAX5865 integrates a

dual-channel analog-to-digital converter (ADC), a dualchannel digital-to-analog converter (DAC), and a 1.024V

internal voltage reference. The EV kit board accepts

AC- or DC-coupled, differential or single-ended analog

inputs for the receive ADC and includes circuitry that

converts the transmit DAC differential output signals to

single-ended analog outputs. The EV kit includes circuitry that generates a clock signal from an AC sine

wave input signal. The EV kit operates from a +3.0V

analog power supply, +3.0V digital power supply, and

±5V bipolar power supply.

The EV kit comes with Windows98/2000/XP-compatible

software that provides an interface to exercise the features of the MAX5865. The program is menu driven and

offers a graphical user interface (GUI) with control buttons and status displays. The GUI is used to control the

MAX5865 SPI-compatible serial interface.

The MAX5865 EV kit evaluates the 22Msps MAX5864 or

the 7.5Msps MAX5863 analog front end (IC replacement is required).

Features

♦ Quick Dynamic Performance Evaluation

♦ 50Ω Matched Clock Input and Analog Signal Lines

♦ Single-Ended to Fully Differential Analog Input

Signal Configuration

♦ Differential to Single-Ended Output Signal-

Conversion Circuitry

♦ AC- or DC-Coupled Input Signals Configuration

♦ SMA Coaxial Connectors for Clock Input, Analog

Inputs, and Analog Output

♦ On-Board Clock-Shaping Circuit

♦ High-Speed PC Board Design

♦ Fully Assembled and Tested

♦ Windows-Compatible Software

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

________________________________________________________________ Maxim Integrated Products 1

19-3000; Rev 1; 2/04

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim’s website at www.maxim-ic.com.

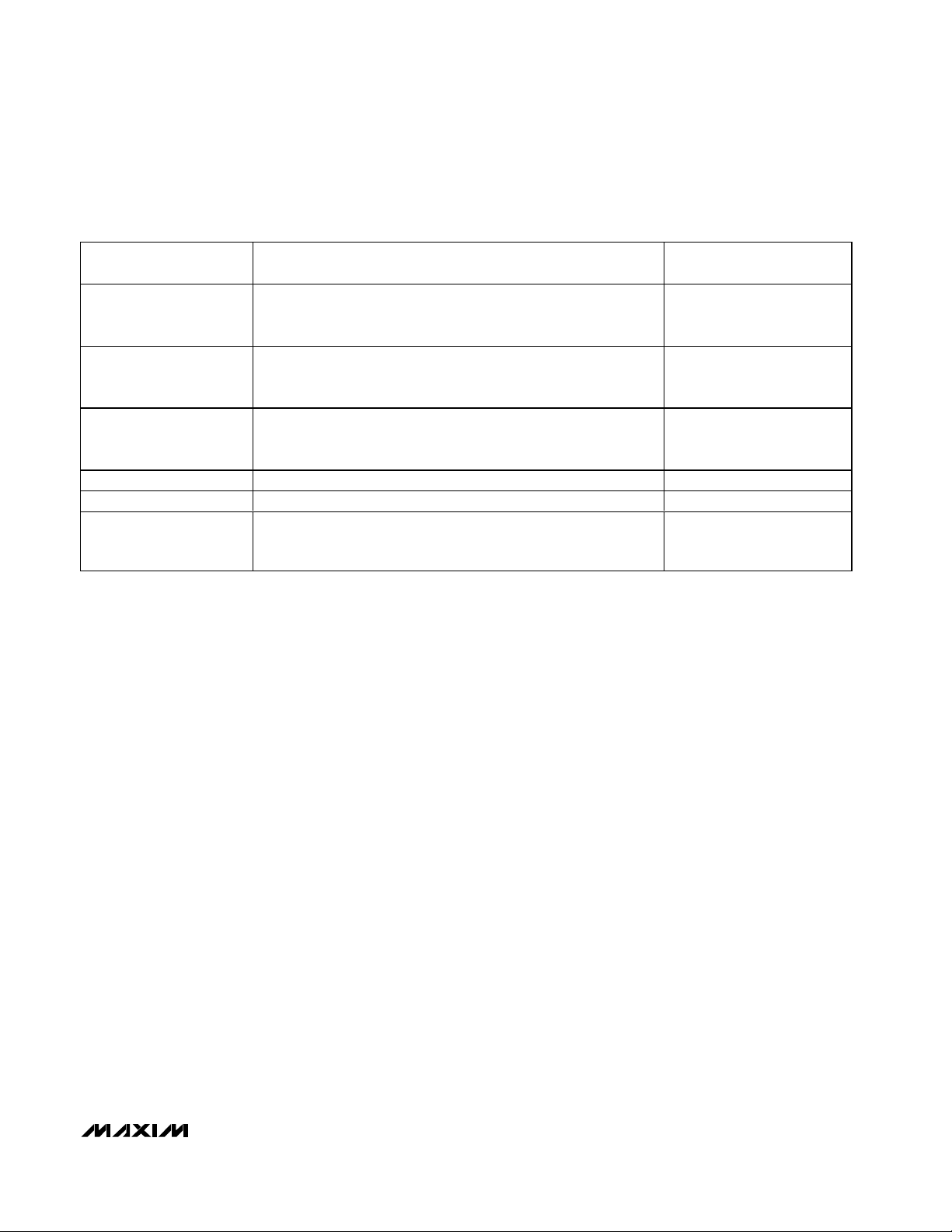

Ordering Information

PART TEMP RANGE IC PACKAGE

MAX5865EVKIT 0°C to +70°C

48 Thin QFN-EP*

*EP = Exposed pad.

Windows is a registered trademark of Microsoft Corp.

Component Suppliers

SUPPLIER PHONE FAX WEBSITE

AVX 843-946-0238 843-626-3123 www.avxcorp.com

Kemet 864-963-6300 864-963-6322 www.kemet.com

Murata 770-436-1300 770-436-3030 www.murata.com

Pericom 800-435-2336 408-435-1100 www.pericom.com

Taiyo Yuden 800-348-2496 847-925-0899 www.t-yuden.com

TDK 847-803-6100 847-390-4405 www.component.tdk.com

Texas Instruments 972-644-5580 214-480-7800 www.ti.com

Note: Please indicate that you are using the MAX5865 when contacting these component suppliers.

Part Selection Table

PART

MAXIMUM SAMPLING SPEED (Msps)

MAX5863ETM 7.5

MAX5864ETM 22

MAX5865ETM 40

MAX5865 EV Kit Software Files

PROGRAM DESCRIPTION

INSTALL.EXE Installs the EV kit software

MAX5865.EXE Application program

HELPFILE.HTM MAX5865 EV kit Help file

PORT95NT.EXE

SST's freeware DLPortIO driver

IMAGE 1.GIF Interface figure

UNINST.INI Uninstalls the EV kit software

Page 2

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

2 _______________________________________________________________________________________

Component List

DESIGNATION

DESCRIPTION

R1–R4

24.9Ω ±1% resistors (0402)

R5–R9

2kΩ ±1% resistors (0603)

R10, R11

4.02kΩ ±1% resistors (0603)

R12

6.04kΩ ±1% resistor (0603)

R13

5kΩ ±10% 1/4in potentiometer,

12 turn

R14–R21

10kΩ ±1% resistors (0603)

R22–R25

Not installed resistors (0402)

R26, R27, R28,

R36, R71–R80

Not installed resistors (0603)

R29–R35

49.9Ω ±1% resistors (0603)

R37–R44

100Ω ±5% resistors (0603)

R45–R66, R70

51Ω ±5% resistors (0603)

R67, R68, R69

10kΩ ±5% resistors (0603)

T1, T2

Transformers (1:1)

Coilcraft TTWB3010-1

U1

MAX5865ETM (48-pin thin QFN-EP)

U2

Dual-CMOS differential line receiver

(8-pin SO)

Maxim MAX9113ESA

U3, U4

Low-jitter operational amplifiers

(8-pin SO)

Maxim MAX4108ESA

U5

Buffer/driver tri-state output

(48-pin TSSOP)

Texas Instruments

SN74ALVCH16244DGGR or

Pericom PI74ALVCH16244A

U6

Hex buffer/driver

(14-pin TSSOP)

Texas Instruments SN74LV07APWR

None

MAX5865 PC board

None

Software CD-ROM disk

MAX5865 EV kit

None

Shunts (JU1–JU11)

DESIGNATION QTY DESCRIPTION

0.1µF ±10%, 10V X5R ceramic

C1–C8 8

C9–C15, C27,

C68–C71

C16–C19 4

C20, C21, C22,

C23, C24, C25 3

C28–C34,

C36–C39,

C41–C55, C66,

C56–C59 0

C60–C65 6

IA, IAP, IAN, QA,

QAP, QAN,

CLOCK, ID, QD

J1, J2, J3 3 2 x 10 pin headers

JU1–JU8 8 3-pin headers

JU9, JU10, JU11 3 2-pin headers

C26

C67

J4 1 DB25 right-angle male plug

L1 1

capacitors (0402)

Taiyo Yuden LMK105BJ104KV or

TDK C1005X5R1A104K

2.2µF ±10%, 10V X5R ceramic

capacitors (0603)

12

Taiyo Yuden JMK107BJ225KA or

TDK C1608X5R0J225K

22pF ±5%, 50V C0H ceramic

capacitors (0402)

Murata GRP1555C1H220J or

Taiyo Yuden UMK105CH220JW

1000pF ±10%, 50V X7R ceramic

capacitors (0402)

4

Taiyo Yuden UMK105BJ102KW or

TDK C1005X7R1H102KT

0.33µF ±10%, 10V X5R ceramic

capacitors (0603)

Taiyo Yuden LMK107BJ334KA

0.1µF ±10%, 25V X7R ceramic

capacitors (0603)

28

Murata GRM188R71E104K or

TDK C1608X7R1E104K

Not installed, ceramic capacitors

(0402)

10µF ±10%, 10V tantalum

capacitors (A)

AVX TAJA106K010R or

Kemet T494A106K010AS

9 SMA PC-mount vertical connectors

Ferrite bead (1206)

Panasonic EXC-CL3216U1

QTY

4

5

2

1

1

8

0

0

7

8

23

3

2

1

1

2

1

1

1

1

11

Page 3

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

_______________________________________________________________________________________ 3

Quick Start

Recommended Equipment

• Two +3.0VDC power supplies

• Two +2.0VDC power supplies

• One ±5.0V bipolar DC power supply

• One function generator with low phase noise and

low jitter for clock input (e.g., HP 8662A)

• Two function generators for single-ended analog

inputs (e.g., HP 8662A)

• One 10-bit digital pattern generator for data inputs

(e.g., Tektronix DG2020A)

• Two spectrum analyzers (e.g., HP 8560E)

• One logic analyzer or data-acquisition system

(e.g., HP 1663EP, HP 16500C)

• Voltmeter

• Oscilloscope

• MAX5865 evaluation software

• Windows 98/2000/XP computer with a spare

printer port

• 25-pin female-to-male I/O extension cable

• Analog input filters (select appropriate ADC input

filters per application specific)

Procedure

The MAX5865 EV kit is a fully assembled and tested

surface-mount board. Follow the steps below for proper

board operation. Do not turn on power supplies or

enable signal generators until all connections are

completed:

1) Verify that shunts are installed across pins 1 and 2

of jumpers JU1, JU2, JU3, and JU4 (single-ended

analog signals IA and QA converted to differential

input signals with transformers T1 and T2).

2) Verify that shunts are installed across pins 2 and 3

of jumpers JU5, JU6, JU7, and JU8 (differential

analog output signals converted to single-ended

signals ID and QD with operational-amplifier circuits

U3 and U4).

3) Verify that no shunts are installed across jumpers

JU9 and JU10.

4) Verify that a shunt is installed across jumper JU11

(internal reference).

5) Connect the 25-pin I/O extension cable from the

computer’s parallel port to the MAX5865 EV kit

board DB25 right-angle male plug J4. The EV kit

software uses a loopback connection to confirm

that the correct port has been selected.

6) Install the evaluation software on your computer by

running the INSTALL.EXE program on the CD-ROM.

The program files are copied and icons are created

for them in the Start menu.

7) Connect the clock-function signal generator (HP

8662A) to the CLOCK SMA connectors on the

EV kit.

8) Connect the two function generators to SMA connectors IA and QA.

9) Synchronize the two function generators to the

clock function generator.

10) Connect the logic analyzer to the 2 x 10 square pin

header J1. The CLOCK signal is available on pin

J1-2 and bits DA0–DA7 are available on the even

pins J1-4 to J1-18. All other header J1 pins are connected to ground. The clock pin and data pins are

labeled CLK and DA0–DA7 on the EV board.

11) Verify that the logic analyzer is programmed for an

8-bit input at CMOS voltage levels.

12) Verify that the 10-bit digital pattern generator is programmed for valid CMOS output voltage levels.

13) Connect the digital pattern generator DG2020A output to the J3 input header connector on the EV kit

board. The input header pins are labeled for proper

connection with the digital pattern generator (i.e.,

connect bit 0 to the J3-19 header pin labeled DD0,

connect bit 1 to the J3-17 header pin labeled DD1,

etc. Input data pins are the odd pins of header J3.

All other pins are connected to ground).

14) Synchronize the digital pattern generator with the

clock function generator.

15) Connect a +3.0V power supply to the VDD pad.

Connect the ground terminal of this supply to the

GND pad.

16) Connect a +3.0V power supply to the VCLK pad.

Connect the ground terminal of this supply to the

GND pad.

17) Connect a +2.0V power supply to the OVDD pad.

Connect the ground terminal of this supply to the

OGND pad.

18) Connect a +2.0V power supply to the VDDRV pad.

Connect the ground terminal of this supply to the

OGND pad.

19) Connect the +5.0V terminal of the bipolar power

supply to the VCC pad. Connect the ground terminal of this supply to the GND pad.

Page 4

20) Connect the -5.0V terminal of the bipolar power

supply to the VEE pad.

21) Turn on the five power supplies.

22) Probe resistor pad R28 with an oscilloscope and

adjust potentiometer R13 to set the clock duty cycle

to 50%.

23) Start the MAX5865 program by opening its icon in

the Start menu.

24) Click on the Xcvr control command to set the

MAX5865 in receive/transmit (transceiver) operational mode.

25) Enable the clock function generator (HP 8662A).

Set the clock function generator output power to

2.4V

P-P

(11.6dBm) and the frequency (f

CLK

) to

greater than 22MHz but less than or equal

to 40MHz.

26) Enable the function generators.

27) Set the IA function-generator output signal to

1.024V

P-P

and the frequency to ≤ f

CLK

/2.

28) Set the QA function-generator output signal to

1.024V

P-P

and and the frequency to ≤ f

CLK

/2.

29) Use the logic analyzer to analyze the 8-bit ADC digital output. The IA channel digital data is available

on the falling edge of the clock. The QA digital data

is available on the rising edge of the clock. Ensure

that the ADC input is not overdriven by observing

the output digital codes and adjusting the input signal level for code of -0.5dB full scale.

30) Enable the digital pattern generator. Program the

digital pattern generator to transmit the digital data

for the DAC I channel on the falling edge of the

clock and transmit the digital data for the Q channel

on the rising edge of the clock.

31) Connect the spectrum analyzers to the ID and QD

SMA connectors to analyze the analog outputs.

32) Use the spectrum analyzer to analyze the analog

output spectrum or view the analog output waveforms using an oscilloscope.

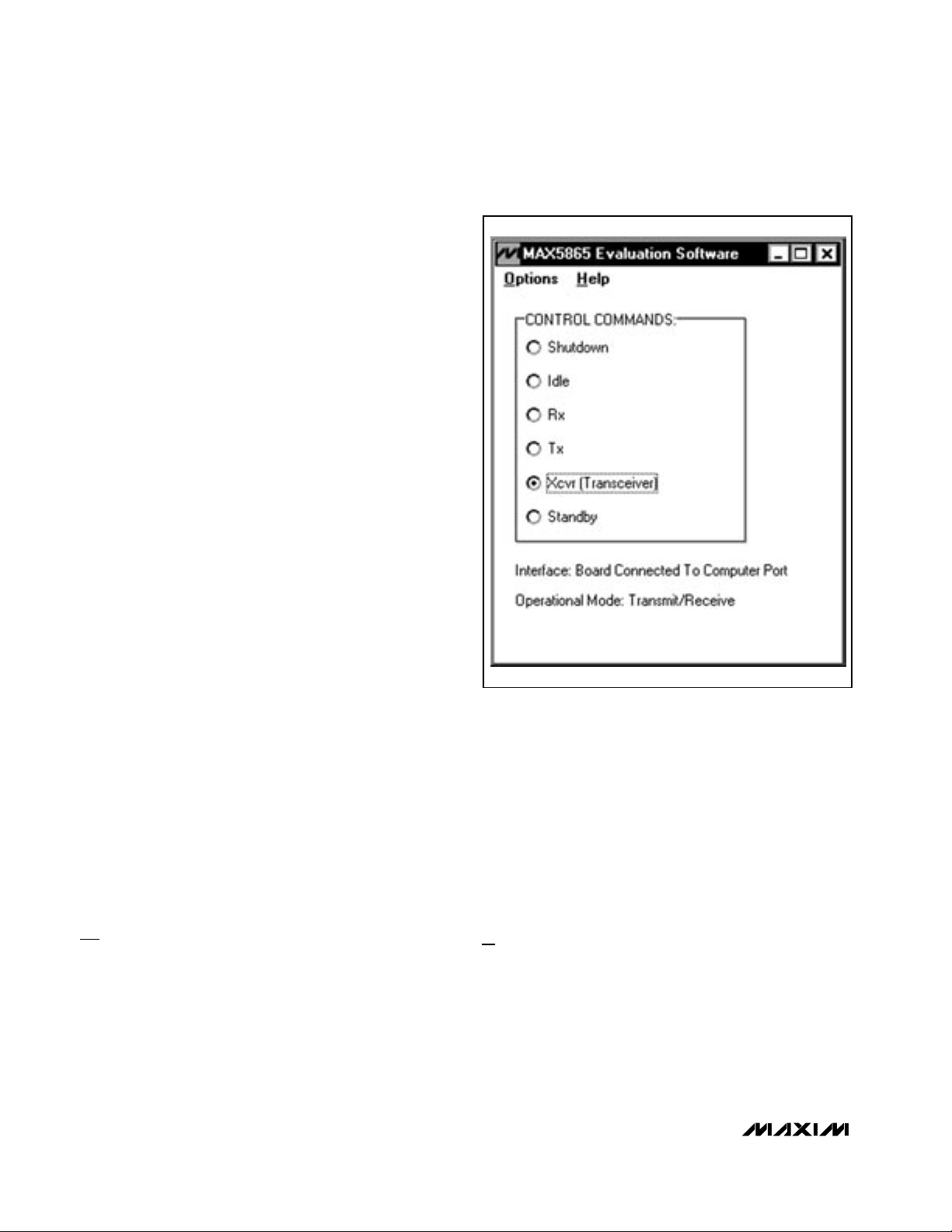

Detailed Description of Software

The evaluation software’s main window (shown in

Figure 1) can be used to program the MAX5865 to one

of the six operational modes: shutdown, idle, receive

(Rx), transmit (Tx), transceiver (Xcvr), and standby.

Click one of the buttons to program the MAX5865 to the

desired operational mode after power has been

applied to the EV kit. Use the keyboard arrow keys to

cycle through the control commands. See Table 1 for

the description of each operational mode.

The MAX5865 evaluation software uses a 3-wire bit-banging interface that is compatible with SPITM/ QSPITM/

MICROWIRETM/DSP interfaces to program the MAX5865

through the parallel port on the computer. Table 1 lists the

byte command for each operational mode.

Detailed Description of Hardware

The MAX5865 EV kit is a fully assembled and tested circuit board that contains all the components necessary to

evaluate the performance of the MAX5865, MAX5864, or

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

4 _______________________________________________________________________________________

SPI and QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corp.

Figure 1. MAX5865 EV Kit Software Main Window

Page 5

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

_______________________________________________________________________________________ 5

MAX5863 analog front end. The MAX5863/MAX5864/

MAX5865 integrate a 1.024V temperature-stable voltage

reference, a dual-input 8-bit parallel-output receive

ADC, and a 10-bit parallel-input dual-output transmit

DAC. The MAX5863/MAX5864/MAX5865 accept ACcoupled or DC-coupled, differential, or single-ended

analog inputs at the receive ADC. The digital output

produced by the ADC can be easily captured with a

high-speed logic analyzer or data-acquisition system.

The MAX5863/MAX5864/MAX5865 digital inputs at the

transmit DAC are designed for CMOS-compatible voltage levels. The DAC produces differential analog outputs with 1.4VDC common mode.

The EV kit comes with the MAX5865 installed, which

operates at speeds of up to 40Msps. The EV kit operates from a +3.0V analog power supply, +3.0V digital

power supply, and ±5V bipolar operational amplifier

power supply. For best dynamic performance, set the

digital power supply to +2V. The EV kit includes circuitry that generates a clock signal from an AC sine wave

provided by the user. Other features include: circuitry

to convert single-ended inputs to differential input analog signals and circuitry to convert the differential outputs of the DAC to single-ended analog signals. The

MAX5865 EV kit can be used to evaluate the 22Msps

MAX5864 or the 7.5Msps MAX5863 after replacing the

MAX5865.

Power Supplies

The MAX5865 EV kit can operate from a single +3.0V

power supply connected to the VDD, OVDD, VCLK,

and VDDRV input power pads and their respective

ground pads for simple board operation. An additional

ended output circuitry (U3 and U4) is used. See the

Transmit Dual DAC Outputs section for further details.

However, two +3.0V (VDD and VCLK) and two +2V

(OVDD and VDDRV) power supplies are recommended

for best dynamic performance. The EV kit PC board

ground layer is divided into two sections: digital

(OGND) and analog (GND). The EV kit PC board power

plane is divided into four sections: VDD (MAX5865 analog circuit), OVDD (MAX5865 output driver circuit),

VCLK (clock-shaping circuit U2), and VDDRV (digital

components U5 and U6). VDD, VCLK, VCC, and VEE

inputs are referenced to analog ground GND. OVDD

and VDDRV inputs are referenced to the OGND

ground. Using separate power supplies for each input

section reduces crosstalk noise and improves the integrity of the output signals. Another advantage of using separate power supplies is that the input power sources do

not have to be at the same voltage level for the EV kit circuit to operate normally. VDD has a +2.7V to +3.3V input

range, OVDD has a +1.8V to VDD input range, VCLK has

a +2.7V to +3.3V input range , and VDDRV has a +2.0V

to +3.3V input range.

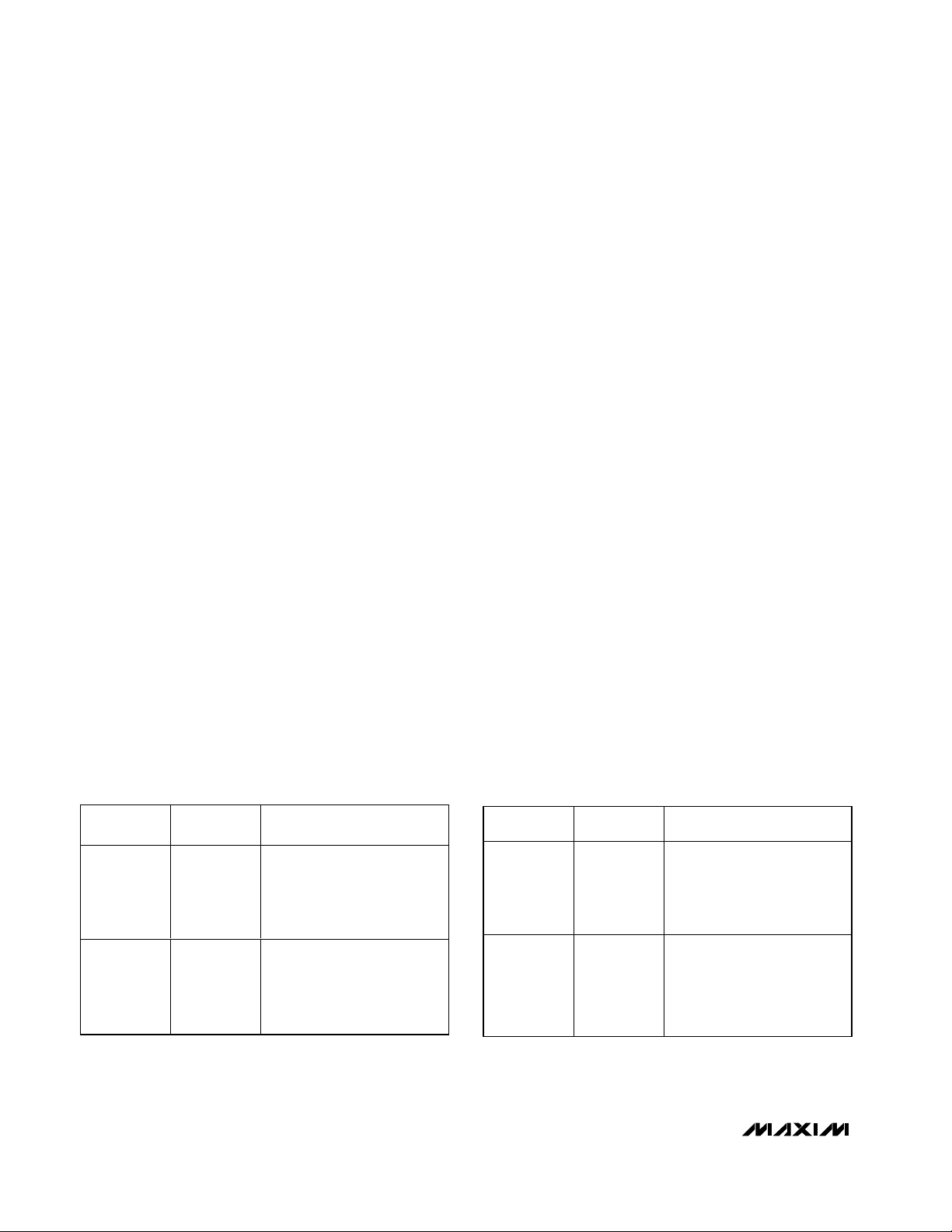

MODE

EV KIT

FUNCTION

COMMAND BYTE SENT TO

MAX5865

Shutdown

Device shutdown. REF is off, ADCs are off, the ADC bus is tri-stated,

and DACs are off. The DAC input bus must be set to zero or OV

DD

to

achieve the lowest shutdown-mode power consumption.

xxxx x000

Idle

REF is on, ADCs are off, the ADC bus is tri-stated, and DACs are off.

The DAC input bus must be set to zero or OVDD to achieve the

lowest Idle Mode™ power consumption.

xxxx x001

Receive (Rx)

REF is on, ADCs are on, and DACs are off. The DAC input bus must

be set to zero or OV

DD

to achieve the lowest Rx-mode power

consumption.

xxxx x010

Transmit (Tx)

xxxx x011

Transceive (Xcvr) REF is on, ADCs and DACs are on. xxxx x100

Standby

REF is on, ADCs are off, the ADC bus is tri-stated, and DACs are off.

The DAC input bus must be set to zero or OVDD to achieve the

lowest standby-mode power consumption.

xxxx x101

Table 1. Operational Modes

x = Don’t care

Idle Mode is a trademark of Maxim Integrated Products, Inc.

REF is on, ADCs are off, the ADC bus is tri-stated, and DACs are on.

±5V bipolar power supply is needed at VCC and VEE

when the operational-amplifier differential to single-

Page 6

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

6 _______________________________________________________________________________________

JU5

POSITION

JU6

EV KIT FUNCTION

1-2 1-2

ID channel DC-coupled

differential output available at

the IDP (DAC voltage output)

and IDN (complementary DAC

voltage output) PC pads

2-3 2-3

ID channel differential output

converted to single-ended

signal using operationalamplifier configuration;

available at ID SMA connector

Table 2. DAC ID Channel Analog Output

Selection

Table 3. DAC QD Channel Analog Output

Selection

Clock Signal

An on-board clock-shaping circuit generates a clock

signal from an AC sine wave signal applied to the

CLOCK SMA connector. The input clock signal should

not exceed a magnitude of 2.6V

P-P

. The frequency of the

signal determines the sampling frequency (f

CLK

) of the

MAX5865 EV kit circuit and should not exceed 40MHz.

The differential line receiver (U2) processes the input

signal to generate the CMOS clock signal. The clock signal’s duty cycle can be adjusted with potentiometer R13.

A 50% duty cycle is recommended. The clock signal is

available at the J1-2 header pin (CLK) and can be used

as the external clock for the logic analyzer.

Transmit Dual 10-Bit DAC Input

The MAX5865 integrates a dual 10-bit DAC capable of

operating with clock speeds up to 40Msps. The digital

data for the I and Q channels are alternately clocked

onto the DAC’s bus DD0–DD9. Data for the I channel is

latched on the falling edge of the clock signal and data

for the Q channel is latched on the rising edge of the

clock signal. The MAX5865 EV kit provides a 0.1in 2 x

10 header (J3) to interface a 10-bit CMOS pattern generator to the EV kit. The header data pins are labeled

on the board with the appropriate data bits designation.

Use the labels on the EV kit to match the data bits from

the pattern generator to the corresponding data pins on

header J3. Header pins J3-1 through J3-19 (odd pins)

are data pins DD0–DD9. All other header pins are connected to digital ground OGND.

Transmit Dual DAC Outputs

The MAX5865 transmit DAC outputs are ±400mV

P-P

full-

scale differential analog signals and are biased to

1.4VDC common mode. The full-scale output and DC

common-mode level are set by the internal voltage reference. A variation in the reference voltage results in proportional changes to the DAC full-scale output and the

DC common-mode level. The ID and QD outputs are

simultaneously updated on the rising edge of the clock

signal. The differential ID and QD output signals can be

sampled at the IDP, IDN, QDP, and QDN PC pads or

converted to single-ended signals using on-board operational-amplifier circuits. Configure jumpers JU5, JU6,

JU7, and JU8 to select the output signal format. See

Tables 2 and 3 to configure jumpers JU5–JU8. When

jumpers JU5–JU8 are configured for operational-amplifier

conversion, the differential signals are converted into a

50Ω single-ended signal with operational amplifiers U3

and U4. The single-ended output signals can be sampled at the ID SMA connector for the ID channel and QD

SMA connector for the QD channel. When jumpers

JU5–JU8 are configured for DC-coupled differential outputs, the DC-coupled differential signals can be sampled

at the IDP and IDN PC pads for the ID channel. The QD

channel can be probed at the QDP and QDN PC pads.

POSITION

JU7

POSITION

1-2 1-2

2-3 2-3

JU8

POSITION

EV KIT FUNCTION

QD channel DC-coupled

differential output available at

the QDP (DAC voltage output)

and QDN (complementary

DAC voltage output) PC pads

QD channel differential output

converted to single-ended

signal using operationalamplifier configuration;

available at QD SMA

connector

Page 7

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

_______________________________________________________________________________________ 7

Receive Dual ADC Analog Inputs

The MAX5865 integrates a dual 8-bit ADC that accepts

differential or single-ended analog input signals. The

inputs are simultaneously sampled on the rising edge

of the clock. The EV kit is designed to accept differential or single-ended, AC- or DC-coupled input signals

with full-scale amplitude of less than 1.024V

P-P

(+4dBm). Ensure that the ADC input is not overdriven

by observing the output digital codes and adjusting the

input signal level for code of -0.5dB full scale. See

Table 4 for instructions to configure jumpers JU1, JU2,

JU3, JU4, JU9, and JU10 for the desired analog input.

During single-ended operation the signal is applied

directly to the ADC input. While in differential mode, an

on-board transformer uses the single-ended analog

input to generate a differential analog signal that is

applied at the ADC’s differential input pins.

The EV kit does not include analog input filters for the

ADC channels. Note that function generators exhibit

high harmonic distortions that could degrade the true

performance of the ADC. Select appropriate filters per

specific applications, test tones, and improve the signal

integrity of the function generators.

Note: When a differential signal is applied to the ADC,

the positive and negative input pins of the ADC each

receive half of the input signal supplied at SMA connectors IA and QA with an offset voltage of VDD/2.

Receive Dual 8-Bit ADC Output

The 8-bit digital output data for the IA and QA channels

are multiplexed at output data bus DA0–DA7. The IA

channel data is available on the falling edge of the clock.

The QA channel data is available on the rising edge of

the clock. The MAX5865 EV kit provides a 0.1in 2 x 10

header (J1) to interface with a logic-analyzer or dataacquisition system. The header data pins are labeled on

the board with the appropriate data bit designations. Use

the labels on the EV kit to match the output data bits to

nected to digital ground OGND.

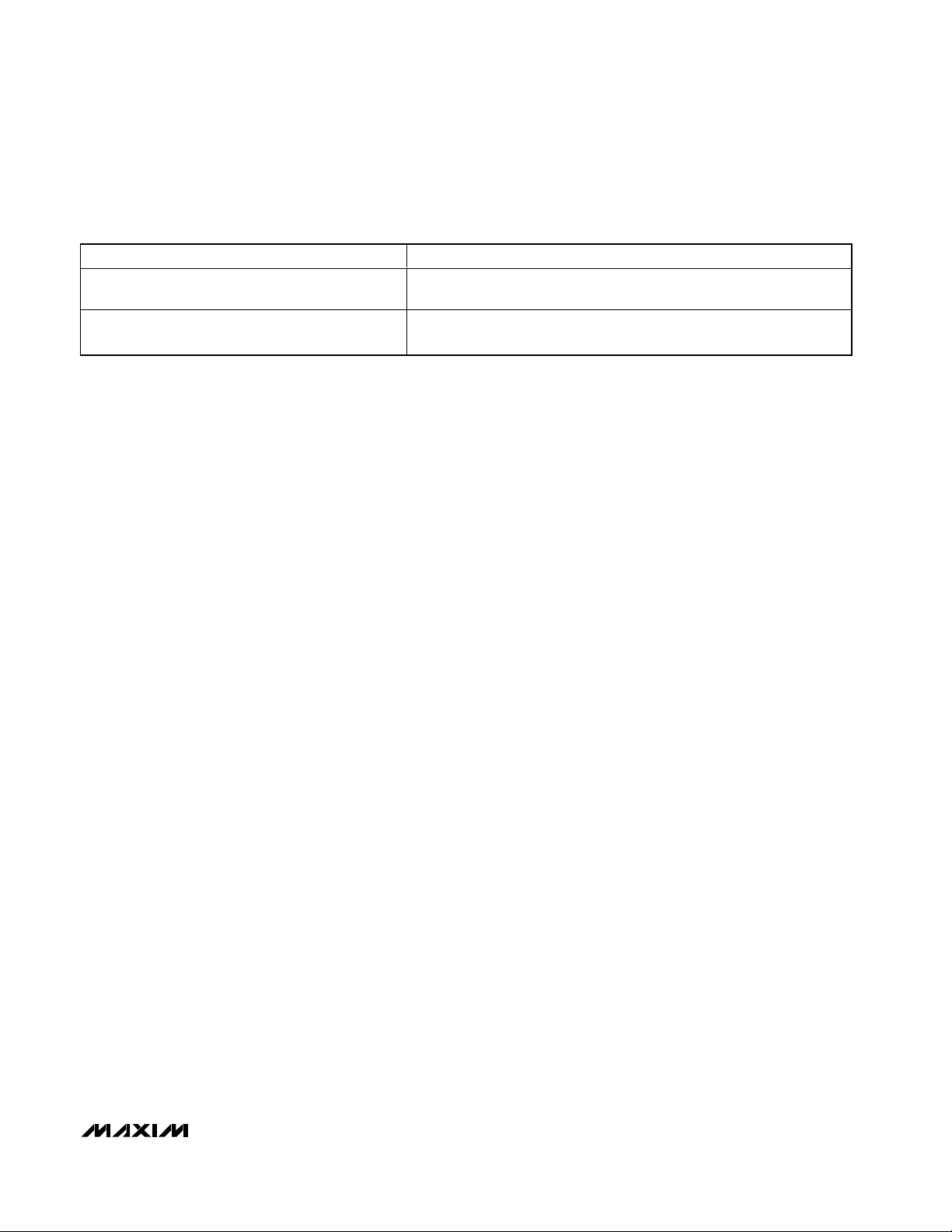

Reference Voltage Options

tion that can be selected by applying a voltage input to

the REFIN pin. The reference voltage sets the full-scale

input voltage of the ADC and the full-scale output voltage of the DAC. The MAX5865 EV kit provides jumper

JU11 and the REFIN PC board pad that allows access

to the input pin and selects one of the two reference

modes: internal reference mode or buffered external

reference mode. See Table 5 for instructions to select

the voltage reference mode. Using an external reference enhances accuracy and drift performance or can

be used for gain control.

JUMPER

SHUNT

POSITION

PIN CONNECTION EV KIT OPERATION

JU1 2 and 3

IA+ pin AC-coupled to SMA connector IAP

through R1 and C28.

JU2 2 and 3 IA- pin connected to COM pin through R2.

JU9 Installed

IA+ pin assumes the DC offset at REFP and

REFN.

Single-ended input, AC-coupled. Analog

input signal is applied to the IAP SMA

connector, channel IA:

• R26 opened (default).

JU1 2 and 3

IA+ pin DC-coupled to SMA connector IAP

through R1 and R26.

JU2 2 and 3 IA- pin connected to COM pin through R2.

JU9 Not installed

IA+ pin assumes the DC offset from the

analog input source.

Single-ended input, DC-coupled. Analog

input signal is applied to the IAP SMA

connector, channel IA:

• R26 shorted (0Ω)

• C28 opened (removed)

• R29 opened (removed)

JU1 1 and 2

IA+ pin connected to pin 6 of transformer T1

through R1.

JU2 1 and 2

IA- pin connected to pin 4 of transformer T1

through R2.

Differential input, AC-coupled. Singleended analog input signal is applied to IA

SMA connector, channel IA.

Table 4. Single-Ended/Differential/AC-Coupled/DC-Coupled Jumper Configuration

the data-acquisition system. Header pins J1-4 through

J1-18 (even pins) are data pins DA0–DA7. Header pin

J1-2 is a clock signal pin. All other header pins are con-

The MAX5865 provides two reference modes of opera-

Page 8

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

8 _______________________________________________________________________________________

JUMPER

SHUNT

POSITION

PIN CONNECTION EV KIT OPERATION

JU1 2 and 3

IA+ pin DC-coupled to SMA connector IAP

through R1 and R26.

JU2 Not installed

IA- pin DC-coupled to SMA connector IAN

through R2.

JU9 Not installed

IA+ and IA- pins assume the DC offset from

the analog input source.

Differential input, DC-coupled. Analog input

signals are applied to IAP and IAN SMA

connectors, channel IA:

• R26 shorted (0Ω)

• C28 opened (removed)

• R29 opened (removed)

JU3 2 and 3

QA+ pin AC-coupled to SMA connector QAP

through R4 and C30.

JU4 2 and 3 QA- pin connected to COM pin through R3.

JU10 Installed

QA+ pin assumes the DC offset at the REFP

and REFN.

Single-ended input, AC-coupled. Analog

input signal is applied to the QAP SMA

connector, channel QA:

• R27 opened (default)

JU3 2 and 3

QA+ pin DC-coupled to SMA connector QAP

through R4 and R27.

JU4 2 and 3 QA- pin connected to COM pin through R3.

JU10 Not installed

QA+ pin assumes the DC offset from the

analog input source.

Single-ended input, DC-coupled. Analog

input signal is applied to the QAP SMA

connector , channel QA:

• R27 shorted (0Ω)

• C30 opened (removed)

• R31 opened (removed)

JU3 1 and 2

QA+ pin connected to pin 3 of transformer T2

through R4.

JU4 1 and 2

QA- pin connected to pin 1 of transformer T2

through R3.

Differential input, AC-coupled. Singleended analog input signal is applied to QA

SMA connector, channel QA.

JU3 2 and 3

QA+ pin DC-coupled to SMA connector QAP

through R4 and R27.

JU4 Not installed

QA- pin DC-coupled to SMA connector QAN

through R3

JU10 Not installed

QA+ and QA- pins assume the DC offset from

the analog input source.

Differential input, DC-coupled. Analog input

signals are applied to QAP and QAN SMA

connectors, channel QA:

• R27 shorted (0Ω)

• C30 opened (removed)

• R31 opened (removed)

Table 4. Single-Ended/Differential/AC-Coupled/DC-Coupled Jumper Configuration

(continued)

Page 9

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

_______________________________________________________________________________________ 9

Table 5. Voltage Reference Modes

REFIN VOLTAGE REFERENCE MODE

VDD

(shunt across jumper JU11)

Internal reference mode. Internal reference voltage equal to 0.512V. Sets

the full-scale ADC input to 1.024V

P-P

and DAC output voltage to 400mV

P-P

.

External 1.024V

(remove shunt from jumper JU11)

Buffered external reference mode. ADC full-scale input voltage set to

REFIN. DAC full-scale output voltage proportional to REFIN.

Loopback Test

The MAX5865 EV kit circuit provides header J2 that,

when configured, connects the ADC digital output bus

to the DAC digital input. This allows a preliminary evaluation of the MAX5865 using analog input signals only.

Note: Configuring header J2 supplies an 8-bit output

pattern to the 10-bit input, resulting in a loss of the DAC

performance. Install shunts across the J2 pin headers

to connect the DA7 output bit to the DD9 input bit, DA6

output bit to the DD8 input bit, etc. The maximum frequency for the ADC output loopback to DAC input is

25MHz. The maximum frequency for the ADC output

loopback DAC input can be increased to 30MHz by

changing resistors R37 through R44 to 25Ω.

TDD Mode

A time-division duplex (TDD) operating mode can also

be implemented by connecting the ADC digital output

to the DAC digital input bus. Use the MAX5865 EV kit

software to switch between receive and transmit mode

to implement TDD mode. Operating in this configuration, the ADC digital buffer (U5) is bypassed. Avoid

excessive digital ground currents by keeping the digital

bus capacitance to a minimum in this mode. Refer to

the FDD and TDD Modes section in the MAX5865 data

sheet for further details.

Evaluating the MAX5864 or MAX5863

The MAX5865 EV kit can be used to evaluate the

MAX5864 or MAX5863, which are pin and function

compatible with the MAX5865. The MAX5863 operates

at clock frequencies of >2MHz, but ≤7.5MHz. The

MAX5864 operates at clock frequencies >7.5MHz, but

≤22MHz. Replace the MAX5865 (U1) with the MAX5864

or the MAX5863 and refer to the respective data sheet

for detailed technical information.

Board Layout

The MAX5865 EV kit is a four-layer board design optimized for high-speed signals. All high-speed signal

lines are routed through 50Ω impedance-matched

transmission lines. The length of these 50Ω transmis-

sion lines is matched to within 40 mils (1mm) to minimize layout-dependent data skew. The board layout

separates the digital and analog ground plane of the

circuit for optimum performance.

Page 10

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

10 ______________________________________________________________________________________

Figure 2. MAX5865 EV Kit Schematic (Sheet 1 of 3)

36

35

48 47 46

REFP

V

DD

IA+

IA-

GND

CLK

GND

V

DD

QA-

QA+

VDDGND

CS

V

DD

DIN

SCLK

DD9

DD8

DD7

DD6

DD5

DD4

DD3

DD2

REFN

ID+

REFIN

COM

ID-

V

DD

GND

QD-

QD+

V

DD

N.C.

GND

DA0

DA3

DA2

DA1

OGND

OV

DD

DA4

DA5

DA6

DA7

DD0

DD1

45 44 43 42 41 40 39 38 37

34

33

U1

REFP

REFN

COM

VDD

R37

100Ω

C14

2.2µF

C7

0.1µF

R4

24.9Ω

1%

R27

OPEN

JU3

1

2

3

COM

CLK

COM

V1

JU10

QAP

QA

OVDD

C15

2.2µF

C8

0.1µF

DA0

R38

100Ω

DA1

R39

100Ω

DA2

R40

100Ω

DA3

R41

100Ω

DA4

R42

100Ω

DA5

R43

100Ω

DA6

R44

100Ω

DA7

CS

SCLK

DIN

31

30

29

DD8

32

DD9

DD7

DD6

28

27

26

DD5

DD4

DD3

25

13

14

15

16

17

18 19

20

21

22

23

24

DD2

VDD

QAN

12

11

C9

2.2µF

C1

0.1µF

10

C16

22pF

C31

0.1µF

C67

0.1µF

C30

0.1µF

R3

24.9Ω

1%

R2

24.9Ω

1%

R31

49.9Ω

1%

JU4

T2

1

1

2

2

3

3

4

5

6

9

C17

22pF

DD0 DD1

5

VDD

8

7

6

VDD

VDD

C10

2.2µF

C2

0.1µF

C24

0.33µF

C21

1000pF

C12

2.2µF

C11

2.2µF

C3

0.1µF

R32

49.9Ω

1%

JU2

1

REFN

IA

IAP

IAN

C19

22pF

C5

0.1µF

C66

0.1µF

C29

0.1µF

JU1

T1

1

1

2

2

2

3

3

3

4

5

6

4

COM ID+

C18

22pF

R1

24.9Ω

1%

3

R5

2kΩ

1%

2

C4

0.1µF

C56

OPEN

ID-

VDD

VDD

C57

OPEN

C25

0.33µF

C22

1000pF

C23

0.33µF

C28

0.1µF

C20

1000pF

R6

2kΩ

1%

R26

OPEN

1

V1

JU9

JU11

REFN

R7

2kΩ

1%

R8

2kΩ

1%

R22

OPEN

R23

OPEN

R24

OPEN

QD- QD+

C58

OPEN

C13

2.2µF

R25

OPEN

C6

0.1µF

C59

OPEN

R29

49.9Ω

1%

R30

49.9Ω

1%

MAX5865

REFIN

Page 11

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

______________________________________________________________________________________ 11

Figure 3. MAX5865 EV Kit Schematic (Sheet 2 of 3)

J4-14

J4-8

J4-8

J4-4

1Y

1

3

5

8

10

12

14

2

4

6

7

9

11

13

J4-2

J4-13

VDDRV

VDDRV

CS

CS

J4-24

J4-22

J4-20

J4-101A

2Y

2A

3Y

3A

GND

U6

4Y

4A

5Y

5A

6Y

6A

V

CC

J4-12

J4-18

DB25 MALE CONNECTOR

J4

L1

R66

51Ω

R69

10kΩ

C41

0.1µF

J4-3

J4-11

J4-5

J4-15

J4-1

J4-19

J4-7

J4-21

J4-9

J4-23

J4-16

J4-17

J4-25

VDDRV

C43

0.1µF

C61

10µF

VDDRV

OGND

SCLK

SCLK

OGND

R65

51Ω

R64

51Ω

R68

10kΩ

DIN

DIN

R67

10kΩ

OVDD

C42

0.1µF

C60

10µF

OVDD

OGND

VCLK

C44

0.1µF

C62

10µF

VCLK

GND

VDD

C45

0.1µF

C63

10µF

VDD

GND

VEE

C46

0.1µF

C64

10µF

VEE

VCC

C47

0.1µF

C65

10µF

VCC

GND

R18

10kΩ

1%

R19

10kΩ

1%

R21

10kΩ

1%

R20

10kΩ

1%

C38

0.1µF

C54

0.1µF

C70

2.2µF

C39

0.1µF

C55

0.1µF

C71

2.2µF

R35

49.9Ω

1%

VEE

QD+

JU7

1

2

3

QDP

GND

ID

QD

VCC

QDN

QD-

JU8

1

2

3

3

8

7

6

2

U4

4

5

R15

10kΩ

1%

R14

10kΩ

1%

R17

10kΩ

1%

R16

10kΩ

1%

C37

0.1µF

C52

0.1µF

C68

2.2µF

C36

0.1µF

C53

0.1µF

C69

2.2µF

R34

49.9Ω

1%

VEE

ID+

JU5

1

2

3

IDP

GND

VCC

IDN

ID-

JU6

1

2

3

3

8

7

6

2

U3

4

5

IN1-

7

8

6

5

4

1

2

3

IN2-

GND

U2

OUT1

OUT2

IN1+

CLOCK

IN2+

V

CC

R28

SHORT

(PC TRACE)

R36

SHORT

(PC TRACE)

R33

49.9Ω

1%

C34

0.1µF

C33

0.1µF

R11

4.02kΩ

1%

R12

6.04kΩ

1%

VCLK

R9

2kΩ

1%

R13

5kΩ

R10

4.02kΩ

1%

VCLK

TPI

CLK

CLK2

C27

2.2µF

C26

1000pF

C32

0.1µF

Page 12

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

12 ______________________________________________________________________________________

Figure 4. MAX5865 EV Kit Schematic (Sheet 3 of 3)

J1-15

J1-17

J1-19

J1-13

J1-11

J1-9

J1-7

J1-1

J1-3

J1-5

R70

51Ω

CLK2

HEADER 2 × 10

J2-14

J2-16

J3-18

J3-20

J2-2

4A4

4A2

U5

3A4

3A2

2A3

2A1

1A4

1A3

1Y1

1Y3

1Y4

2Y1

2Y3

3Y2

3Y4

4Y2

4Y4

V

CC

V

CC

V

CC

V

CC

1DE

2DE

VDDRV

3DE

4DE

GND

GND

GND

GND

GND

GND

GND

GND

1A2

2A2

2A4

3A1

3A3

4A1

4A3

J2-6

J2-8

J2-10

J2-12

R63

51Ω

R53

51Ω

R52

51Ω

R51

51Ω

R50

51Ω

R49

51Ω

R48

51Ω

R47

51Ω

R46

51Ω

R45

51Ω

C48

0.1µF

R62

51Ω

R73

OPEN

DD9

DA7

26

DD8

DD7

DD6

DD5

DD4

DD3

DD2

R72

OPEN

DD0

DD1

R71

OPEN

J2-4

J3-16

J3-14

J3-12

J3-10

J3-8

J3-2

J3-4

J3-6

J1-16

J1-18

J1-20

J1-14

J1-12

J1-10

J1-8

J1-2

J1-4

J1-6

J2-18

J2-20

J3-1

J3

HEADER 2 × 10

HEADER 2 × 10

J2

J1

J3-3

J3-5

J3-7

J2-1

J3-9

J3-11

J3-13

J3-15

J3-17

J3-19

R61

51Ω

R74

OPEN

R60

51Ω

R75

OPEN

R59

51Ω

R76

OPEN

R58

51Ω

R77

OPEN

R57

51Ω

R78

OPEN

R56

51Ω

R79

OPEN

R55

51Ω

R80

OPEN

R54

51Ω

DA8

29

J2-3

DA5

32

J2-5

DA4

35

J2-7

DA3

38

J2-9

DA2

41

J2-11

DA1

43

J2-13

DA0

44

2

5

6

8

11

14

17

20

23

7

18

31

42

1

J2-15

J2-17

J2-19

48

25

24

4

10

15

21

28

34

39

45

46

40

37

36

33

30

27

1Y2

2Y2

2Y4

3Y1

33Y

4Y1

4Y3

1A1

3

9

12

13

16

19

22

47

C49

0.1µF

C50

0.1µF

C51

0.1µF

Page 13

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

______________________________________________________________________________________ 13

Figure 5. MAX5865 EV Kit Component Placement Guide—Component Side

Page 14

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

14 ______________________________________________________________________________________

Figure 6. MAX5865 EV Kit PC Board Layout—Component Side

Page 15

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

______________________________________________________________________________________ 15

Figure 7. MAX5865 EV Kit PC Board Layout—Ground Planes

Page 16

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

16 ______________________________________________________________________________________

Figure 8. MAX5865 EV Kit PC Board Layout—Power Planes

Page 17

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

______________________________________________________________________________________ 17

Figure 9. MAX5865 EV Kit PC Board Layout—Solder Side

Page 18

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are

implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

18 ____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2004 Maxim Integrated Products Printed USA is a registered trademark of Maxim Integrated Products.

Evaluates: MAX5863/MAX5864/MAX5865

MAX5865 Evaluation Kit

Figure 10. MAX5865 EV Kit Component Placement Guide—Solder Side

Loading...

Loading...