Page 1

For pricing, delivery, and

ordering information, please contact Maxim Direct

at 1-888-629-4642, or visit Maxim’s website at www.maximintegrated.com.

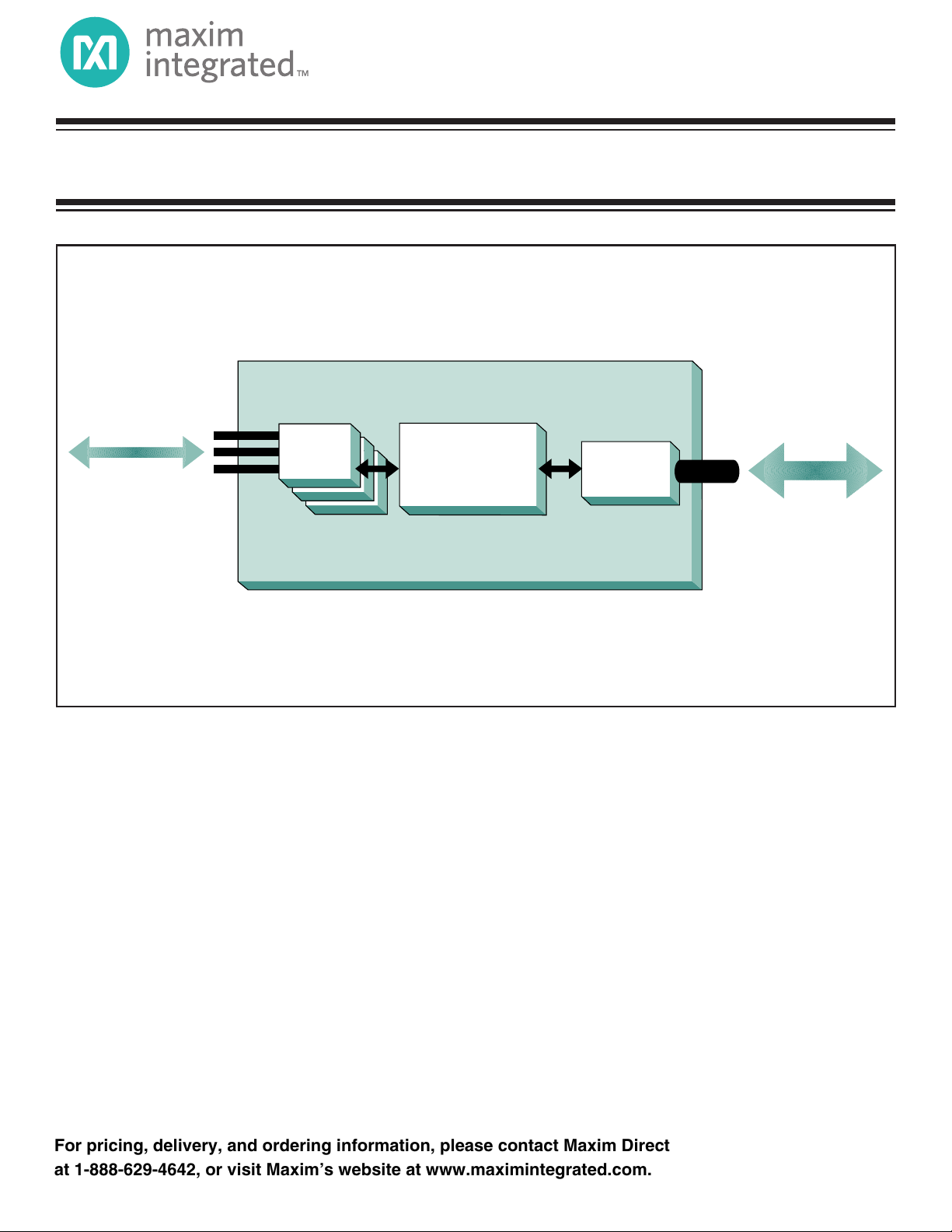

x3

SERIAL

UARTs

COMMUNICATE WITH

NEW AND LEGACY

EQUIPMENT

REMOTE MONITORING

AND CONTROL

VIA THE NETWORK

8051 µC

WITH TCP/IPv4/6

NETWORK STACK IN

ROM

10/100

ETHERNET

MAC

DS80C400/DS80C410/DS80C411

NETWORKED MICROCONTROLLER

HIGH-SPEED MICROCONTROLLER USER’S GUIDE:

NETWORK MICROCONTROLLER SUPPLEMENT

This document is provided as a supplement to the High-Speed Microcontroller User’s Guide, covering new or modified features spe-

cific to the DS80C400/DS80C410/DS80C411. This document must be used in conjunction with the High-Speed

Microcontroller User’s Guide, available from Maxim. Addenda are arranged by section number, which correspond to sections in the High-Speed Microcontroller User’s Guide.

Unless otherwise specified, the references to the DS80C400 and its features also apply to the DS80C410 and DS80C411. Exceptions

include differences in the amount of internal memory and the inclusion/exclusion of the CAN module.

The following additions and changes, with respect to the High-Speed Microcontroller User’s Guide, are contained in this document.

This document is a work in progress, and updates/additions are added when available.

Rev: 12; 9/08

Page 2

High-Speed Microcontroller User’s

Maxim Integrated

Guide: Network Microcontroller

Supplement

TABLE OF CONTENTS

ADDENDUM TO SECTION 1: INTRODUCTION 14

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

ADDENDUM TO SECTION 2: ORDERING INFORMATION 15

Refer to the device-specific data sheet(s) for more information.

ADDENDUM TO SECTION 3: ARCHITECTURE 15

CPU Core and CPU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

ADDENDUM TO SECTION 4: PROGRAMMING MODEL 16

Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Bit-Addressable Locations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Working Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Stack . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Special-Function Register Maps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Special-Function Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Special-Function Register Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Special-Function Register Reset Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Special-Function Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Port 4 (P4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Stack Pointer (SP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Data Pointer Low 0 (DPL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Data Pointer High 0 (DPH) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Data Pointer Low 1 (DPL1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Data Pointer High 1 (DPH1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Data Pointer Select (DPS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Power Control (PCON) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Timer/Counter Control (TCON) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Timer Mode Control (TMOD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Timer 0 LSB (TL0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Timer 1 LSB (TL1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Timer 0 MSB (TH0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Timer 1 MSB (TH1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Clock Control (CKCON) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Port 1 (P1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

External Interrupt Flag (EXIF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Port 4 Control Register (P4CNT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Data Pointer Extended Register 0 (DPX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

2

Page 3

High-Speed Microcontroller User’s

Maxim Integrated

Guide: Network Microcontroller

Supplement

Data Pointer Extended Register 1 (DPX1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

CAN 0 Receive Message Stored Register 0 (C0RMS0) . . . . . . . . . . . . . . . . . . . . . . . . . . .36

CAN 0 Receive Message Stored Register 1 (C0RMS1) . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Serial Port 0 Control (SCON0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

Serial Data Buffer 0 (SBUF0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

Extended Stack Pointer Register (ESP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Address Page Register (AP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Address Control Register (ACON) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

CAN 0 Transmit Message Acknowledgment Register 0 (C0TMA0) . . . . . . . . . . . . . . . . . .41

CAN 0 Transmit Message Acknowledgment Register 1 (C0TMA1) . . . . . . . . . . . . . . . . . .42

Port 2 (P2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Port 5 (P5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Port 5 Control Register (P5CNT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

CAN 0 Control Register (C0C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

CAN 0 Status Register (C0S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

CAN 0 Interrupt Register (C0IR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

CAN 0 Receive-Error Register (C0RE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

Interrupt Enable (IE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

Slave Address Register 0 (SADDR0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

Slave Address Register 1 (SADDR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

CAN 0 Message Center 1 Control Register (C0M1C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

CAN 0 Message Center 2 Control Register (C0M2C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

CAN 0 Message Center 3 Control Register (C0M3C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

CAN 0 Message Center 4 Control Register (C0M4C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

CAN 0 Message Center 5 Control Register (C0M5C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

Port 3 (P3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

Port 6 (P6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

Port 6 Control Register (P6CNT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

CAN 0 Message Center 6 Control Register (C0M6C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

CAN 0 Message Center 7 Control Register (C0M7C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

CAN 0 Message Center 8 Control Register (C0M8C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

CAN 0 Message Center 9 Control Register (C0M9C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

CAN 0 Message Center 10 Control Register (C0M10C) . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Interrupt Priority (IP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

Slave Address Mask Enable Register 0 (SADEN0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

Slave Address Mask Enable Register 1 (SADEN1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

CAN 0 Message Center 11 Control Register (C0M11C) . . . . . . . . . . . . . . . . . . . . . . . . . . .66

CAN 0 Message Center 12 Control Register (C0M12C) . . . . . . . . . . . . . . . . . . . . . . . . . . .66

CAN 0 Message Center 13 Control Register (C0M13C) . . . . . . . . . . . . . . . . . . . . . . . . . . .66

CAN 0 Message Center 14 Control Register (C0M14C) . . . . . . . . . . . . . . . . . . . . . . . . . . .67

3

Page 4

High-Speed Microcontroller User’s

Maxim Integrated

Guide: Network Microcontroller

Supplement

CAN 0 Message Center 15 Control Register (C0M15C) . . . . . . . . . . . . . . . . . . . . . . . . . . .67

Serial Port Control (SCON1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

Serial Data Buffer 1 (SBUF1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

Power-Management Register (PMR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

Status Register (STATUS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

Memory Control Register (MCON) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

Timed-Access Register (TA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

Timer 2 Control (T2CON) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

Timer 2 Mode (T2MOD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

Timer 2 Capture LSB (RCAP2L) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

Timer 2 Capture MSB (RCAP2H) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

Timer 2 LSB (TL2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

Timer 2 MSB (TH2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

Clock Output Register (COR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

Program Status Word (PSW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

Multiplier Control Register 0 (MCNT0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

Multiplier Control Register 1 (MCNT1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

Multiplier A Register (MA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

Multiplier B Register (MB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

Multiplier C Register (MC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

Memory Control Register 1 (MCON1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

Memory Control Register 2 (MCON2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

Watchdog Control (WDCON) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

Slave Address Register 2 (SADDR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

Breakpoint Address Register 1 (BPA1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

Breakpoint Address Register 2 (BPA2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

Breakpoint Address Register 3 (BPA3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

Accumulator (AC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

One’s Complement Adder Data (OCAD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

CSR Data (CSRD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

CSR Address (CSRA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

Ethernet Buffer Size (EBS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

Buffer Control Unit Data (BCUD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

Buffer Control Unit Control (BCUC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

Extended Interrupt Enable (EIE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

MOVX Address Extended Register (MXAX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

Data Pointer Extended Register 2 (DPX2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

Data Pointer Extended Register 3 (DPX3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

1-Wire Master Address Register (OWMAD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

1-Wire Master Data Register (OWMDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

4

Page 5

High-Speed Microcontroller User’s

Maxim Integrated

Guide: Network Microcontroller

Supplement

B Register (B) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

Slave Address Mask Enable Register 2 (SADEN2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

Data Pointer Low Register 2 (DPL2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

Data Pointer High Register 2 (DPH2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

Data Pointer Low Register 3 (DPL3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

Data Pointer High Register 3 (DPH3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

Data Pointer Select Register 1 (DPS1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

Status Register 1 (STATUS1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

Extended Interrupt Priority (EIP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

Parallel I/O Port (P7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92

Timer 3 LSB (TL3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92

Timer 3 MSB (TH3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92

Timer 3 Control/Mode Register (T3CM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .93

Serial Port 2 Control Register (SCON2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94

Serial Data Buffer 2 (SBUF2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94

ADDENDUM TO SECTION 5: CPU TIMING 95

External Clock Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .95

System Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .95

Changing the System Clock/Machine Cycle Clock Frequency . . . . . . . . . . . . . . . . . . . . . . . . .96

ADDENDUM TO SECTION 6: MEMORY ACCESS 97

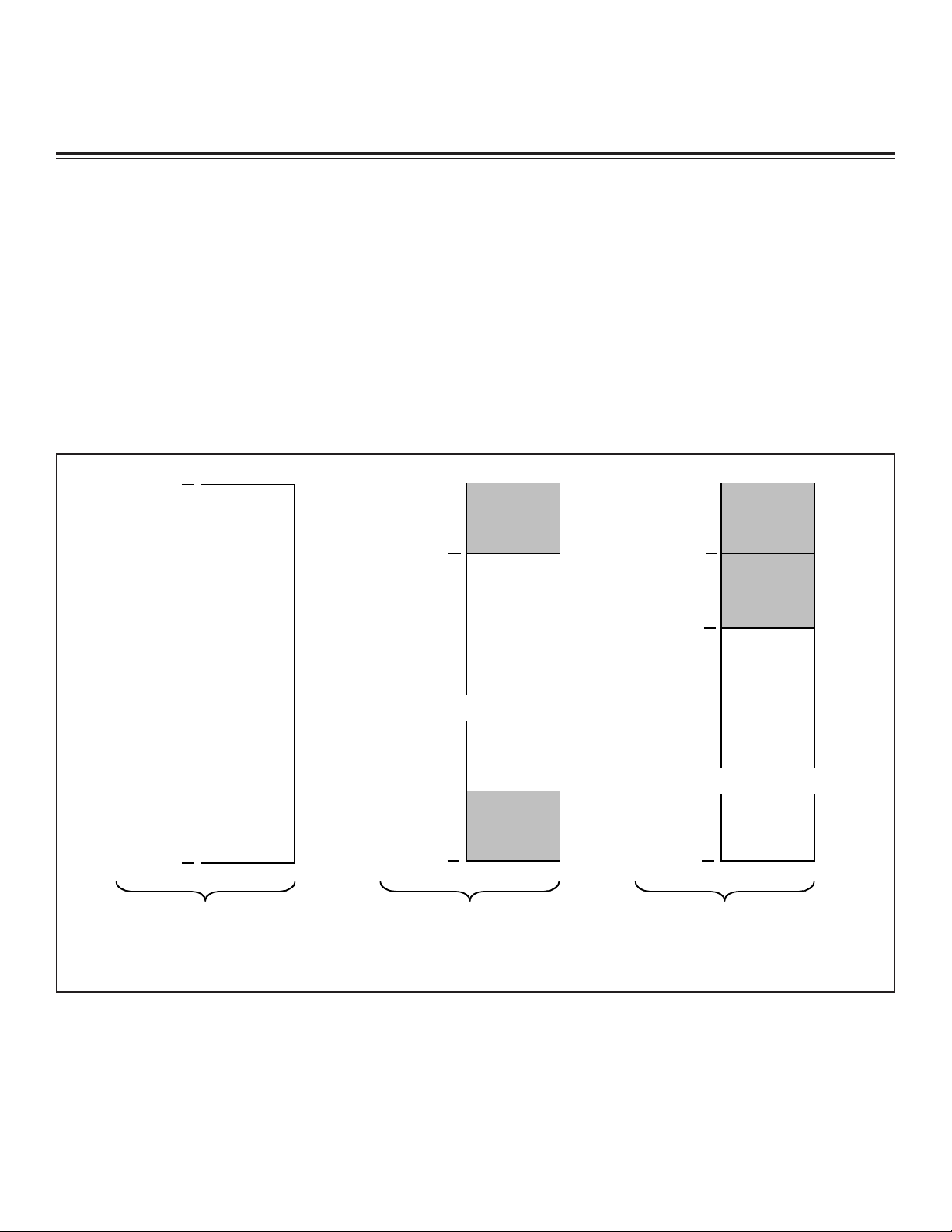

Internal Program Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .97

Internal Data Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98

DS80C400 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98

DS80C410/DS80C411 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

External Memory Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

Using the Combined Chip-Enable Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104

Write-Protection Feature (DS80C400 Only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

Enhanced Quad Data Pointers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

ADDENDUM TO SECTION 7: POWER MANAGEMENT 109

Precision Voltage Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .109

Early Warning Power-Fail Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

Power-Fail Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

Power-On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

Bandgap Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

Power-Management Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

Power-Management Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

PMM and Peripheral Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

Switchback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

5

Page 6

High-Speed Microcontroller User’s

Maxim Integrated

Guide: Network Microcontroller

Supplement

Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

Pin States in Idle or Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

Switching Between Clock Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

ADDENDUM TO SECTION 8: RESET CONDITIONS 111

Reset Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

Power-On/Power-Fail Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112

Watchdog Timer Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112

External Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112

Oscillator Fail-Detect Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112

Reset Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

Reset Output Low (RSTOL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

Reset State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

In-System Disable Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

ADDENDUM TO SECTION 9: INTERRUPTS 114

ADDENDUM TO SECTION 10: PARALLEL I/O 116

Port 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .116

Ports 4–7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .116

General-Purpose I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .116

Alternate Functions A0–A7, A16–A21, CE0–7, and PCE0–3 . . . . . . . . . . . . . . . . . . . . . . . . . . .116

Current-Limited Transitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .116

5V-Tolerant I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .117

ADDENDUM TO SECTION 11: PROGRAMMABLE TIMERS 118

Divide-by-13 Option . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

Programmable Clock Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

IrDA Clock Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

ADDENDUM TO SECTION 12: SERIAL I/O 124

Serial Mode Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124

Baud Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124

Mode 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125

Mode 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

Mode 1 or 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

Using Timer 1 or Timer 3 for Baud-Rate Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

Using Timer 2 for Baud-Rate Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

ADDENDUM TO SECTION 13: TIMED-ACCESS PROTECTION 129

ADDENDUM TO SECTION 14: REAL-TIME CLOCK 129

Refer to the High-Speed Microcontroller User’s Guide. Not applicable to the DS80C400/410/411.

6

Page 7

High-Speed Microcontroller User’s

Maxim Integrated

Guide: Network Microcontroller

Supplement

ADDENDUM TO SECTION 15: BATTERY BACKUP 129

Refer to the High-Speed Microcontroller User’s Guide. Not applicable to the DS80C400/410/411.

ADDENDUM TO SECTION 16: INSTRUCTION SET DETAILS 130

16-Bit (8051 Standard) Addressing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

24-Bit Paged Addressing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

24-Bit Contiguous Addressing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132

ADDENDUM TO SECTION 17: TROUBLESHOOTING 133

Software Breakpoint Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

Generating a Breakpoint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

Exiting a Breakpoint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

ADDENDUM TO SECTION 18: MICROCONTROLLER

DEVELOPMENT SUPPORT 135

Refer to the High-Speed Microcontroller User’s Guide.

SECTION 19: CONTROLLER AREA NETWORK (CAN) MODULE 136

MOVX Message Centers for CAN 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .137

CAN MOVX Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .138

CAN 0 Media ID Mask Register 0 (COMID0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139

CAN 0 Media ID Mask Register 1 (COMID1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139

CAN 0 Media Arbitration Register 0 (C0MA0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139

CAN 0 Media Arbitration Register 1 (C0MA1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139

CAN 0 Bus Timing Register 0 (C0BT0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .140

CAN 0 Bus Timing Register 1 (C0BT1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .141

CAN 0 Standard Global Mask Register 0 (C0SGM0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .142

CAN 0 Standard Global Mask Register 1 (C0SGM1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .142

CAN 0 Extended Global Mask Register 0 (C0EGM0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .142

CAN 0 Extended Global Mask Register 1 (C0EGM1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .142

CAN 0 Extended Global Mask Register 2 (C0EGM2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .142

CAN 0 Extended Global Mask Register 3 (C0EGM3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143

CAN 0 Message Center 15 Mask Register 0 (C0M15M0) . . . . . . . . . . . . . . . . . . . . . . . . . .143

CAN 0 Message Center 15 Mask Register 1 (C0M15M1) . . . . . . . . . . . . . . . . . . . . . . . . . .143

CAN 0 Message Center 15 Mask Register 2 (C0M15M2) . . . . . . . . . . . . . . . . . . . . . . . . . .143

CAN 0 Message Center 15 Mask Register 3 (C0M15M3) . . . . . . . . . . . . . . . . . . . . . . . . . .144

CAN Message Center MOVX Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .144

CAN 0 Message Center y Arbitration Register 0 (C0MyAR0) . . . . . . . . . . . . . . . . . . . . . . .144

CAN 0 Message Center y Arbitration Register 1 (C0MyAR1) . . . . . . . . . . . . . . . . . . . . . . .144

CAN 0 Message Center y Arbitration Register 2 (C0MyAR2) . . . . . . . . . . . . . . . . . . . . . . .144

CAN 0 Message Center y Arbitration Register 3 (C0MyAR3) . . . . . . . . . . . . . . . . . . . . . . .145

7

Page 8

High-Speed Microcontroller User’s

Maxim Integrated

Guide: Network Microcontroller

Supplement

CAN 0 Message Center y Format Register (C0MyF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .146

CAN 0 Message Center y Data Byte 0 (C0MyD0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

CAN 0 Message Center y Data Byte 1 (C0MyD1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

CAN 0 Message Center y Data Byte 2 (C0MyD2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

CAN 0 Message Center y Data Byte 3 (C0MyD3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

CAN 0 Message Center y Data Byte 4 (C0MyD4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

CAN 0 Message Center y Data Byte 5 (C0MyD5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

CAN 0 Message Center y Data Byte 6 (C0MyD6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

CAN 0 Message Center y Data Byte 7 (C0MyD7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

Frame Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .148

Initializing the CAN Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .152

CAN Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .152

Arbitration/Masking Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153

Message Center 15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .154

Transmitting and Receiving Messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .154

Transmitting Data Messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .154

Receiving Data Messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .155

Transmitting Remote Frame Requests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .155

Receiving/Responding to Remote Frame Requests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .155

Remote Frame Handling in Relation to the DTBYC Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .158

Overwrite Enable/Disable Feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .158

Case 1: WTOE = 1 (Overwrites allowed) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .159

Case 2: WTOE = 0 (Overwrites disabled) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .159

Special Considerations for Message Center 15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .159

Using the Autobaud Feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .159

Bus-Off/Bus-Off Recovery and Error Counter Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .161

Bit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .162

Threefold Bit Sampling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163

Bus Rate Timing Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164

Additional Bit Timing Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164

SECTION 20: ARITHMETIC ACCELERATOR 165

SECTION 21: 1-WIRE BUS MASTER 168

Divide (32-bit by 16-bit or 16-bit by 16-bit) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .166

Multiply (16-bit by 16-bit) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .166

Shift right/left . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .166

Normalize . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .167

40-Bit Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .167

Hardware Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .168

8

Page 9

High-Speed Microcontroller User’s

Maxim Integrated

Guide: Network Microcontroller

Supplement

Setting Up and Using the 1-Wire Master . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .168

Setting Up the 1-Wire Master . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .169

Sending a 1-Wire Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .169

Sending a Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .169

Search ROM Accelerator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .170

Accelerated ROM Search Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .171

SECTION 22: ETHERNET CONTROLLER 172

Assigning a Physical MAC Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173

Configuring the MAC Operational Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173

Media Independent Interface (MII) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174

ENDEC Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175

ENDEC Mode—Heartbeat Signal Quality Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .176

MAC Primary Functions—Packet Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .176

Using the MII Serial Management Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .177

Half-Duplex Operation—CSMA/CD and Flow Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .177

Deferral Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .178

Disable Retry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .178

Back-Off Limit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .178

Late Collision Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .178

Flow Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .179

Full-Duplex Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .179

Pause Control Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .179

Loopback Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .180

Address Filtering Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .181

Using the Hash Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .182

VLAN Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .182

Partitioning the 8kB Ethernet Data Buffer Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .182

Transmit/Receive Data Buffer Word Orientation: Edianess . . . . . . . . . . . . . . . . . . . . . . . . . . . .184

Transmitting Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184

Receiving Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .186

Using Wake-Up Frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .187

Magic Packet Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .187

Network Wake-Up Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .187

SECTION 23: EMBEDDED DS80C400 SILICON SOFTWARE 189

9

Serial Loader . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .189

Autobaud-Rate Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .189

Command Line Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .189

Command Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .189

Page 10

High-Speed Microcontroller User’s

Maxim Integrated

Guide: Network Microcontroller

Supplement

Exported RAM Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .190

Utility Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .191

Memory Manager Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193

Socket Function Calling Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .195

Input Parameter Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .195

Output Return Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .195

Socket Functions/Pointers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .196

PARAMBUFFER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .196

DHCP Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .203

TFTP Functions/Pointers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .204

Task Scheduler Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .205

Task Scheduler User Hooks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .208

1-Wire Master . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .209

Additional Functions Available in ROM Version 1.2.0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .210

Initialization Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .214

Asynchronous TCP/IP Maintenance Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .216

ROM Redirect Function Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .217

ROM Redirect Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .218

Timeslice and Task Scheduler Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .220

REVISION HISTORY 221

10

Page 11

High-Speed Microcontroller User’s

Maxim Integrated

Guide: Network Microcontroller

Supplement

LIST OF FIGURES

Figure 5-1. System Clock Control Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .95

Figure 6-1. Program Memory Map Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .97

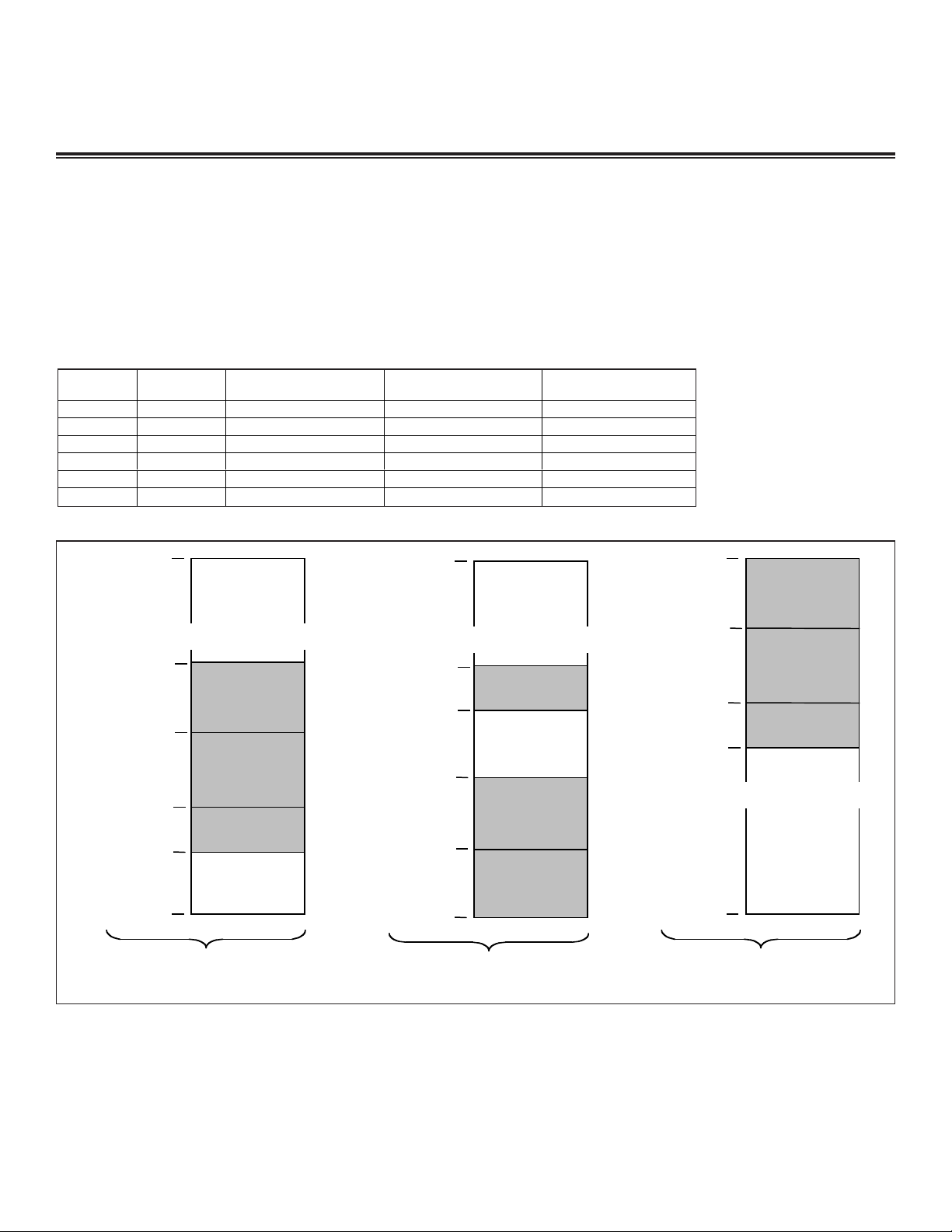

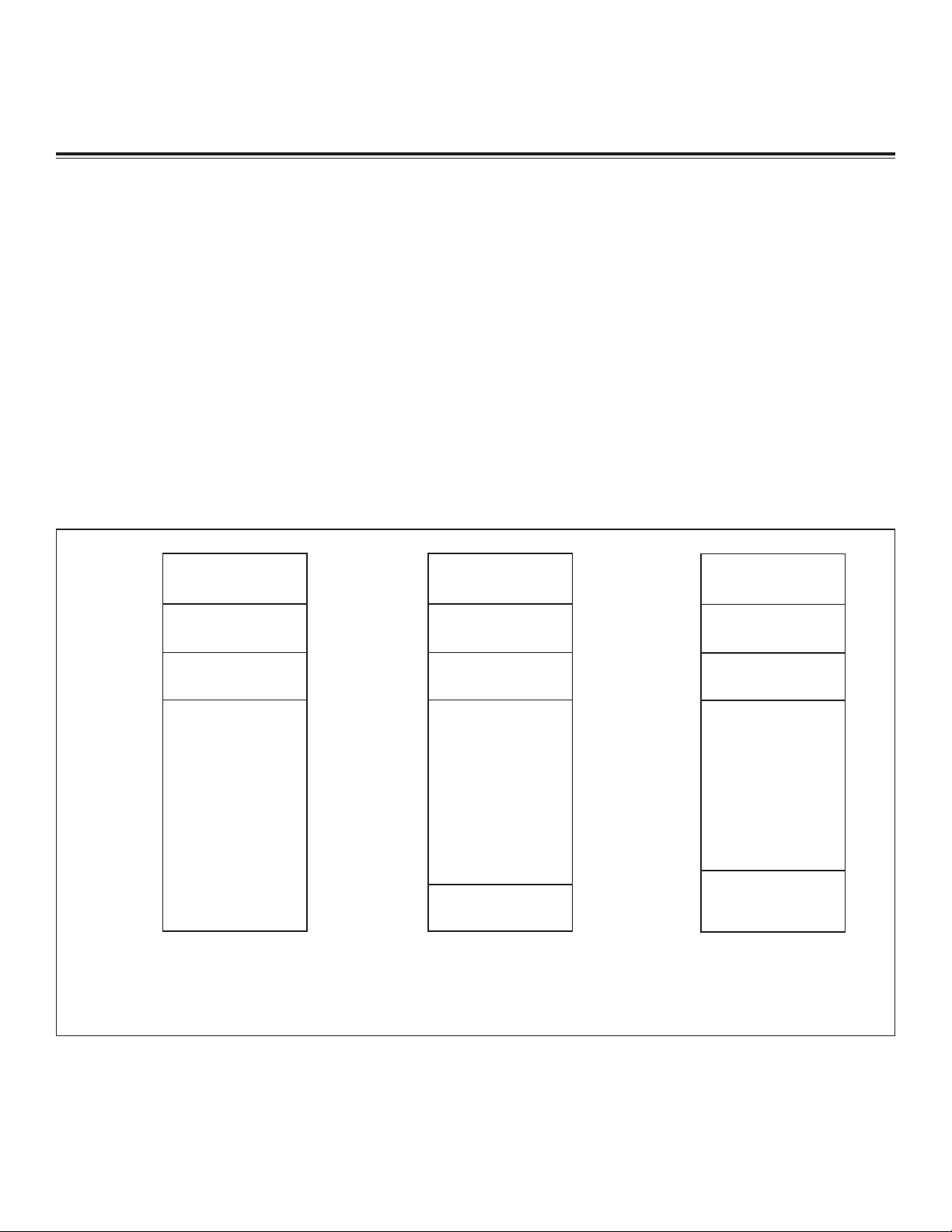

Figure 6-2. Example Data Memory Map Configurations (DS80C400) . . . . . . . . . . . . . . . . . . . . . . .98

Figure 6-3. Example Data Memory Map Configurations (DS80C400/DS80C411) . . . . . . . . . . . . . .99

Figure 6-4. Multiplexed Address/Data Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103

Figure 6-5. Demultiplexed Address/Data Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104

Figure 6-6. Merged Program/Data Access Under CE0, CE2, PCE0–PCE3

Becomes Inaccessible . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

Figure 6-7. Merged Program/Data Access Under CE2, CE3, PCE2, and PCE3

Becomes Inaccessible . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .106

Figure 6-8. Merged Program/Data Access Under CE1, CE2, PCE1, and PCE2

Becomes Inaccessible . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .106

Figure 6-9. Merged Program/Data Access Under CE0 and PCE0 Becomes

Partially Inaccessible . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107

Figure 6-10. Full 16MB Program/Data Memory Map Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107

Figure 9-1. 1-Wire Interrupt Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114

Figure 9-2. Interrupt Functional Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

Figure 10-1. 5V-Tolerant I/O Pad . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .117

Figure 11-1. Timers/Counters 0, 1, and 3, Modes 0 and 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .118

Figure 11-2. Timers/Counters 0, 1, and 3, Mode 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

Figure 11-3. Timer/Counter 0, Mode 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

Figure 11-4. Timer/Counter 2 Clock-Out Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .120

Figure 11-5. Timer/Counter 2 Baud-Rate Generator Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .120

Figure 11-6. Timer/Counter 2 Autoreload Mode, DCEN = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

Figure 11-7. Timer/Counter 2 Autoreload Mode, DCEN = 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

Figure 11-8. Timer/Counter 2 with Optional Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

Figure 11-9. Operation of Divide-by-13 Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

Figure 11-10. Sample IrDA Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

Figure 12-1. Serial Port Mode 0 Block Diagram Change . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125

Figure 12-2. Serial Port Mode 2 Block Diagram Change . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

Figure 12-3. Serial Port Modes 1, 3 Block Diagram Change . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .128

Figure 17-1. Force Feeding a Breakpoint During An Instruction Other Than MOVC or MOVX . . . .134

Figure 17-2. Force Feeding a Breakpoint During a MOVX (2-Cycle) . . . . . . . . . . . . . . . . . . . . . . .134

Figure 17-3. Force Feeding a Breakpoint MOVC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .135

Figure 19-1. CAN 2.0A (Standard) Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .148

Figure 19-2. CAN 2.0B (Extended) Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .148

Figure 19-3. Control Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .149

Figure 19-4. CRC Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .149

Figure 19-5. Acknowledge Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150

11

Page 12

High-Speed Microcontroller User’s

Maxim Integrated

Guide: Network Microcontroller

Supplement

Figure 19-6. Intermission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150

Figure 19-7. Remote Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150

Figure 19-8. Error Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151

Figure 19-9. Overload Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151

Figure 19-10. CAN Interrupt Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153

Figure 19-11. Bit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .162

Figure 21-1. Typical 1-Wire External Hardware Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . .168

Figure 22-1. Ethernet Controller Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173

Figure 22-2. MII Signal Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175

Figure 22-3. MII Mode-Byte/Bit Transmit and Receive Order . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175

Figure 22-4. ENDEC Signal Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .176

Figure 22-5. Serial ENDEC Mode-Byte/Bit Transmit and Receive Order . . . . . . . . . . . . . . . . . . . . .176

Figure 22-6. MII Management Frame Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .177

Figure 22-7. Half-Duplex Transmit Deferral/Collision Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . .179

Figure 22-8. Internal Loopback Mode (MAC Control OM1:0 = 01b) . . . . . . . . . . . . . . . . . . . . . . . .180

Figure 22-9. External Loopback Mode (MAC Control OM1:0 = 10b) . . . . . . . . . . . . . . . . . . . . . . .181

Figure 22-10. Example 8kB Data Memory Partition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .183

Figure 22-11. Big/Little-Endian Data Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184

Figure 22-12. Transmit Flow Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .185

Figure 22-13. Receive Flow Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .186

Figure 22-14. Wake-Up Frame Filter 0 Programming Example . . . . . . . . . . . . . . . . . . . . . . . . . . . .188

Figure 23-1. Timer 0 Interrupt Routing (WOS_tick) Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .220

12

Page 13

High-Speed Microcontroller User’s

Maxim Integrated

Guide: Network Microcontroller

Supplement

LIST OF TABLES

Table 5-1. System Clock Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

Table 5-2. Effect of Clock Modes on Timer Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

Table 6-2. External Memory Addressing Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

Table 6-3. Extended Address Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

Table 6-4. Chip-Enable Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

Table 6-5. Peripheral Chip-Enable Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

Table 6-6. Program Memory Chip-Enable Boundaries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

Table 6-7. Write-Protection Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

Table 6-8. Data Pointer SFR Locations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

Table 11-1. Timer 3 SFR Bit Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .118

Table 12-1. Serial Port 2 Special Function Registers/Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124

Table 12-2. Serial I/O Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124

Table 12-3. Baud-Rate Generation, Mode 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125

Table 12-4. Baud-Rate Generation, Mode 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

Table 12-5. Relationship Between External Crystal Frequency and Timer 1 . . . . . . . . . . . . . . . . . .127

Table 12-6. Relationship Between External Crystal Frequency and Timer 2 . . . . . . . . . . . . . . . . . .128

Table 20-1. Arithmetic Accelerator Execution Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .165

Table 21-1. ROM ID Read Time Slot Possibilities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .170

Table 21-2. Transmit/Receive Byte Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .171

Table 22-1. Source of MAC Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173

Table 22-2. MAC Control Register Bit Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174

Table 22-3. Packet Filter and Filter Fail Status for Various Received Frames . . . . . . . . . . . . . . . . .181

Table 22-4. Network Wake-Up Frame Patterns . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .187

Table 23-1. ROM Redirect Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .217

13

Page 14

High-Speed Microcontroller User’s

Maxim Integrated

Guide: Network Microcontroller

Supplement

ADDENDUM TO SECTION 1: INTRODUCTION

The DS80C400 is the third-generation microcontroller in the Maxim 8051 family. It is derived from the DS87C520, but adds a full CAN

2.0B controller, a 16/32-bit arithmetic accelerator, a 1-Wire®bus master, and an IEEE 802.3-compliant Ethernet media access controller. It incorporates the 8051-compatible high-speed microcontroller core, which has been redesigned to reduce the original 8051’s

twelve clocks per instruction cycle to four clocks, while using less power. The DS80C400 offers a maximum system clock speed of

75MHz. The DS80C400 also supports a larger program space, data memory space, and stack memory.

The DS80C400 supports three programmable address modes. The 16-bit 8051 address mode of operation is identical with the original 8051 operation. The 24-bit paged address mode is fully compatible with the 8051 operation, but is still capable of supporting a

larger memory address range within a multiple page mode configuration. The 24-bit contiguous address mode is supported by a full

24-bit program counter and has eight instructions modified to operate in the 24-bit address range. The 24-bit contiguous address mode

requires assembler, compiler, and linker support. The DS80C400 also supports an extended stack in 1kB of internal data RAM.

The DS80C400 provides four data pointers and implements programmable features that are capable of modifying the INC DPTR

instruction to actually decrement the active data pointer, automatically toggle the selection of the data pointer, and automatically increment/decrement the select data pointer.

Features

Seven bidirectional parallel ports

Four 16-bit timers/counters with one up/down timer, capture, and baud-rate generation features

Power-on reset flag

Stop mode exit on interrupts, reset, and CAN bus activity

256 bytes of scratchpad memory

Low-power CMOS

High-speed, four clocks-per-machine cycle architecture

Clock rates: DC to 75MHz (18.75 MIPS)

Minimum instruction cycle of 53ns

24-bit program/data address memory access

Program counter with selectable 16-bit, 24-bit paged, or 24-bit contiguous mode

16MB external interface

64kB on-chip ROM for bootstrap loader

Supports network boot over Ethernet using DHCP and TFTP

Full application-accessible TCP/IP network stack

Supports IPv4 and IPv6

Implements UDP, TCP, DHCP, ICMP, and IGMP

Preemptive, priority-based task scheduler

MAC address acquisition from IEEE-registered DS2502-E48

9kB(DS80C400) / 65kB(DS80C410/411) data SRAM

Four data pointers with auto INC/DEC function

Extended 1kB stack

High-speed math accelerator for 16/32-bit multiply and divide calculations

One’s complement adder

1-Wire bus master

Ethernet controller supports 100/10Mbps full-duplex and half-duplex operation

Three serial port UARTs with framing error detection and automatic address recognition

1-Wire is a registered trademark of Maxim Integrated Products, Inc.

14

Page 15

High-Speed Microcontroller User’s

Maxim Integrated

Guide: Network Microcontroller

Supplement

16 interrupt sources, 6 external and 10 internal with three levels of interrupt nesting and two programmable priority levels

Crash-proof, bandgap-referenced power-fail warning; voltage sense reset; and automatic power-up reset timeout

Programmable system clock divide control of crystal oscillator. Options include:

Divide-by-1–18.75MHz max. crystal

Divide-by-2–37.5MHz max. crystal

Divide-by-4–Standard operation

Divide-by-1024–Low-speed/power

Status register to verify active-interrupt nesting and real-time serial port transmit/receive activity

User-selectable multiplexed or nonmultiplexed external address/data interface

Programmable watchdog timer

Programmable clock-out and reset-out for additional external stand-alone CAN support

Full CAN 2.0B controller (DS80C400 and DS80C410):

15 message centers

Standard 11-bit or extended 29-bit identification modes

Two data byte masks and associated IDs for DeviceNet™, SDS, and other higher-layer CAN protocol

External transmit disable for autobaud

SIESTA low-power mode

100-pin QFP package

ADDENDUM TO SECTION 2: ORDERING INFORMATION

Refer to the individual data sheets for the available versions.

ADDENDUM TO SECTION 3: ARCHITECTURE

The DS80C400 is designed to provide direct compatibility to all of the traditional 80C32 functions, including a 256-byte special function register (SFR), SRAM memory, a third timer (timer 2), and serial port framing-error detection and automatic address recognition.

Features on the DS80C400 that are compatible with the DS87C520 include a bandgap-based power monitor for interrupt and reset,

timed-access protection, programmable on-board data memory (expanded to 9kB x 8 on the DS80C400, 65kB on the DS80C410/411),

programmable system-clock divide ratios, two serial ports, and a programmable watchdog timer. Expanding on these features, the

DS80C400 also contains an expanded interrupt capability of 16 interrupts with two programmable interrupt priorities, levels for 15 of

the interrupts, and a third-level interrupt priority for power-fail. Additional features include, a math accelerator, a one’s complement

adder, a 1-Wire bus master, a full CAN 2.0B processor (DS80C400/410), an IEEE 802.3-compliant Ethernet media access controller, a

selectable external multiplexed or nonmultiplexed address/data interface, 16-bit, 24-bit paged or 24-bit contiguous addressing operation, and internally decoded chip enables.

The DS80C400 is designed to function similarly to the DS80C390 and run with external program and data memory. The DS80C400 has

been designed to operate with an extended 24-bit address map and to support external memories with a minimum of external logic.

The DS80C400 also supports an optional extended stack pointer and a 1kB stack memory.

CPU Core and CPU Registers

The CPU core of the DS80C400 executes the same binary-compatible instruction set as that of the 80C32. The principal difference

between the core of the DS80C400 and the 80C32 is the number of clocks required to execute specific instructions. The DS80C400

uses a divide-by-4 of the crystal oscillator, and the 80C32 functions with a divide-by-12 of the crystal oscillator. A machine cycle in the

DS80C400 defaults to four periods of the crystal oscillator. A machine cycle in the 80C32 is interpreted as 12 cycles of the oscillator.

The four MOVX data memory instructions of the DS80C400 have the additional capability of being stretched (external data memory

bus access only) from the original data memory access (read or write) time. The MOVX instruction ranges from two machine cycles to

12 machine cycles across eight programmable settings. This MOVX stretch control is user-selectable with the MD2, MD1, and MD0

bits in the clock control register. The ability to do an instruction-based decrement of the DPTR registers is also now supported, through

additional control bits in the DPS1 and DPS SFRs.

DeviceNet is a trademark of OpenDeviceNet Vendor Association Inc.

15

Page 16

High-Speed Microcontroller User’s

Maxim Integrated

Guide: Network Microcontroller

Supplement

The DS80C400 supports one of three different addressing modes, as selected by software through the AM1 and AM0 bits in the ACON

SFR. The microcontroller functions in either the traditional 16-bit address mode, a 24-bit paged address mode, or in a 24-bit contiguous program mode. The microprocessor defaults after a reset to the traditional 16-bit mode, which is identical to the DS80C320

(A23–A16 are forced to 00h). The 24-bit paged address mode is binary code compliant with traditional compilers for the standard 16bit address range, but allows for up to 16MB of program and 4MB of data memory. A new address page SFR implements an internal

bank-switching mechanism in response to a certain set of call/return instructions. The 24-bit contiguous mode requires a 24-bit address

compiler that supports contiguous program flow over the entire 24-bit address range by the addition of an operand and/or cycles to

eight basic instructions (without the need of bank switching).

The instruction is fetched and sent over the 8-bit internal data bus to the instruction register. The ALU performs math functions, logical

operations, and makes comparisons and general decisions. The ALU primarily uses the accumulator and the B register as either the

source or destination for most operations.

All peripherals and operations that are not explicit instructions in the DS80C400 are controlled by SFRs. The accumulator is the primary register used in the CPU. It is the source or destination for most operations. The B register is used as the second 8-bit argument

in multiply and divide operations. When not used in these operations, the B register can be used as a general-purpose register.

The program status word (PSW) contains a selection of bit flags that include the carry flag, auxiliary carry flag, general-purpose flag,

register bank select, overflow flag, and parity flag.

The data pointers are used in accessing program or data memory with the MOVC or MOVX instruction. Two pairs of pointers are provided, simplifying source and destination address tracking when moving data from one memory area to another memory area or to a

memory-mapped peripheral.

The DS80C400 provides a stack in either the original 8052 scratchpad area or a 1kB programmable area of the on-chip SRAM. The

stack pointer register or register pair, when using the extended 1kB stack, denotes the last used location at the top of the stack.

There are three internal buses, which include a 24-bit address bus and two 8-bit data buses. The address bus provides addresses for op

code/operand fetching. The DA data bus is used for addressing SFRs, fetching instructions and operands from external memory, and providing addresses for the internal stack. The DB data bus is used for data exchange between SFRs and the output of all ALU operations.

ADDENDUM TO SECTION 4: PROGRAMMING MODEL

The DS80C400 microprocessor is based on the industry-standard 80C32. The core is an accumulator-based architecture using internal registers for data storage and peripheral control. It executes the standard 8051 instruction set. This section provides a brief description of each architecture feature. Details concerning the programming model, instruction set, and register description are provided in

Section 4.

The high-speed microcontroller uses several distinct memory areas. These are registers, program memory, and data memory. Registers

serve to control on-chip peripherals and as RAM. Note that registers (on-chip RAM) are separate from data memory. Registers are

divided into three categories including directly addressed on-chip RAM, indirectly addressed on-chip RAM, and SFRs. As follows, the

program and data memory areas are discussed under Memory Map, and the registers are discussed under Registers Map.

Memory Map

The DS80C400 microcontroller defaults to the memory compatibility of the 8051. This device can address up to 1kB of on-chip SRAM.

In addition to the standard 16-bit address mode, the DS80C400 can operate in 24-bit paged or 24-bit contiguous address mode. The

DS80C400 has four internal memory areas: 256 bytes of scratchpad RAM, 9kB(DS80C400) / 65kB(DS80C410/411) SRAM, 256 bytes

of RAM reserved for the CAN message centers, and 64kB of embedded ROM firmware. A 22-bit address bus and an 8-bit data bus

operating in multiplexed or demultiplexed mode can address 16MB of external memory. By configuring the SFRs, eight available chipenable pins are used to access 16MB of external program memory. Also, 4MB of external data memory is accessible by configuring

four peripheral, chip-enable bits in the SFRs. The addresses of the program and data segments can overlap since they are accessed

in different ways. Program memory is fetched by the microprocessor automatically. These addresses are never written by software.

There is one instruction (MOVC) that is used to explicitly read the program area. This is commonly used to read lookup tables. The data

memory area is accessed explicitly using the MOVX instruction. This instruction provides multiple ways of specifying the target

address. In addition, the DS80C400 can be configured to permit a merged von Neumann-style program/data memory space. Detailed

descriptions of the memory mapping alternatives are discussed in a separate section of this user’s guide supplement.

16

Page 17

High-Speed Microcontroller User’s

Maxim Integrated

Guide: Network Microcontroller

Supplement

Register Map

The register map is separate from the program and data memory areas mentioned above. A separate class of instructions is used to

access the registers. There are 256 potential register location values. In practice, the high-speed microcontroller has 256 bytes of

scratchpad RAM and up to 128 SFRs. This is possible since the upper 128 scratchpad RAM locations can only be accessed indirectly.

That is, the contents of a working register, described later, designate the RAM location. Thus, a direct reference to one of the upper

128 locations must be an SFR access. Direct RAM is reached at locations 0 to 7Fh (0–127). SFRs are accessed directly between 80h

and FFh (128–255). The RAM locations between 128 and 255 can be reached through an indirect reference to those locations.

Scratchpad RAM is available for general-purpose data storage. It is commonly used in place of off-chip RAM when the total data contents are small. When off-chip RAM is needed, the scratchpad area still provides the fastest general-purpose access. Within the 256

bytes of RAM, there are several special-purpose areas, which are described as follows.

Bit-Addressable Locations

In addition to direct register access, some individual bits in both the RAM and SFR area are also accessible. In the scratchpad RAM

area, registers 20h to 2Fh are bit addressable. This provides 128 (16 x 8) individual bits available to software. The type of instruction

distinguishes a bit access from a full register access. In the SFR area, any register location ending in a 0 or 8 is bit addressable.

Working Registers

As part of the lower 128 bytes of RAM, there are four banks of general-purpose working registers, each bank containing registers

R0–R7. The bank is selected by bits in the program status word register. Since there are four banks, the currently selected bank is used

by any instruction using R0–R7. This allows software to change context by switching banks. The working registers also allow their contents to be used for indirect addressing of the upper 128 bytes of RAM. Thus, an instruction can designate the value stored in R0, for

example, to address the upper RAM. This value might be the result of another calculation.

Stack

Another use of the scratchpad area is for the programmer’s stack. This area is selected using the stack pointer (SP: 81h) SFR.

Whenever a call or interrupt is invoked, the return address is placed on the stack. It is also available to the programmer for variables,

etc. The stack pointer defaults to 07h on reset, but can be relocated as needed. A convenient location would be the upper RAM area

(> 7Fh), since this is only available indirectly. The SP points to the last used value. Therefore, the next value placed on the stack is put

at SP + 1. Each PUSH or CALL increments the SP by the appropriate value. Each POP or RET decrements, as well.

The DS80C400 supports an optional 10-bit (1kB) stack. This greatly increases programming efficiency and allows the device to support large programs. When enabled by setting the stack address (SA) bit in the ACON register, 1kB of the internal SRAM is allocated

for use as the stack. The 10-bit address is formed by concatenating the lower 2 bits of the extended stack pointer (ESP: 9Bh) and the

8-bit stack pointer (SP: 81h). The exact address of the 1kB is dependent on the setting of the IDM1-0 bits.

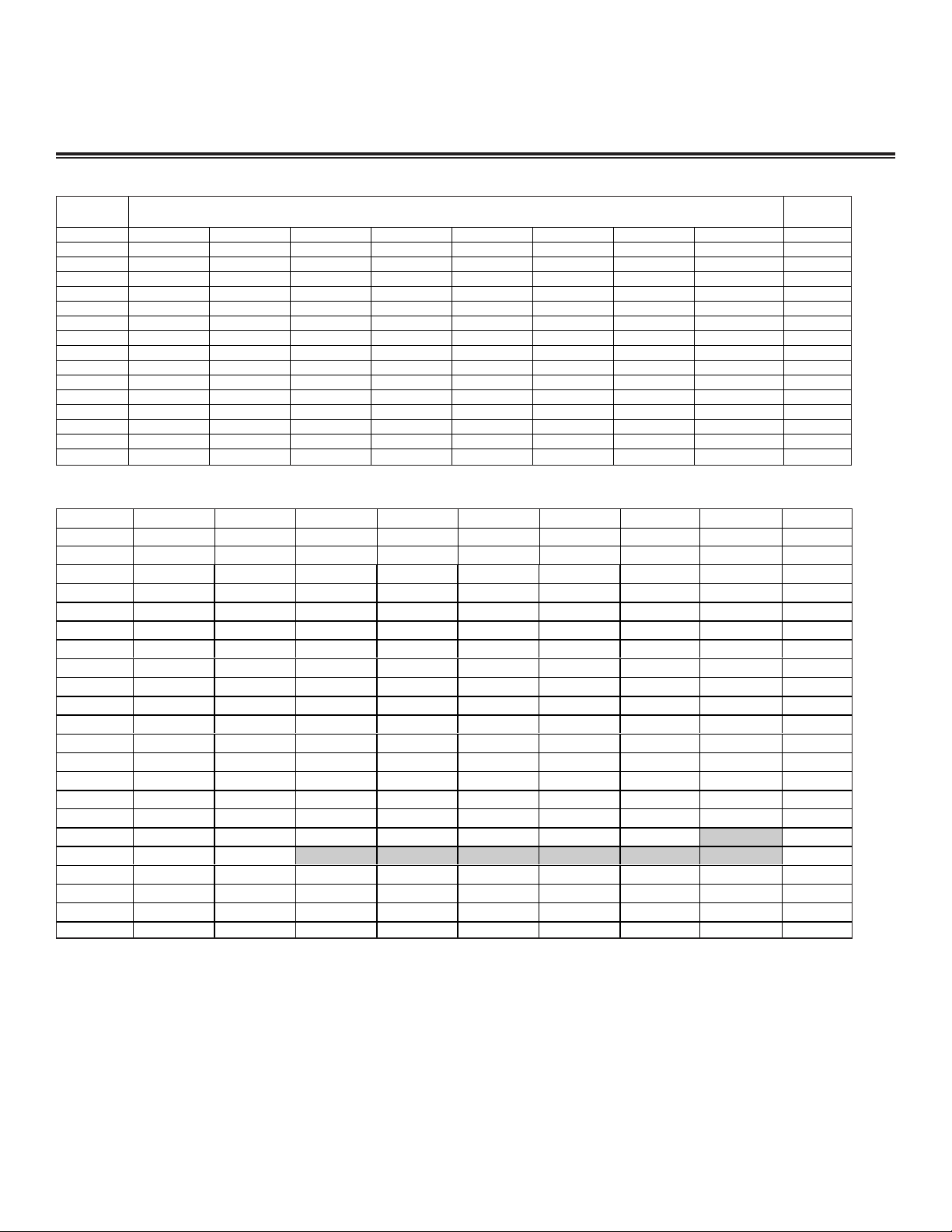

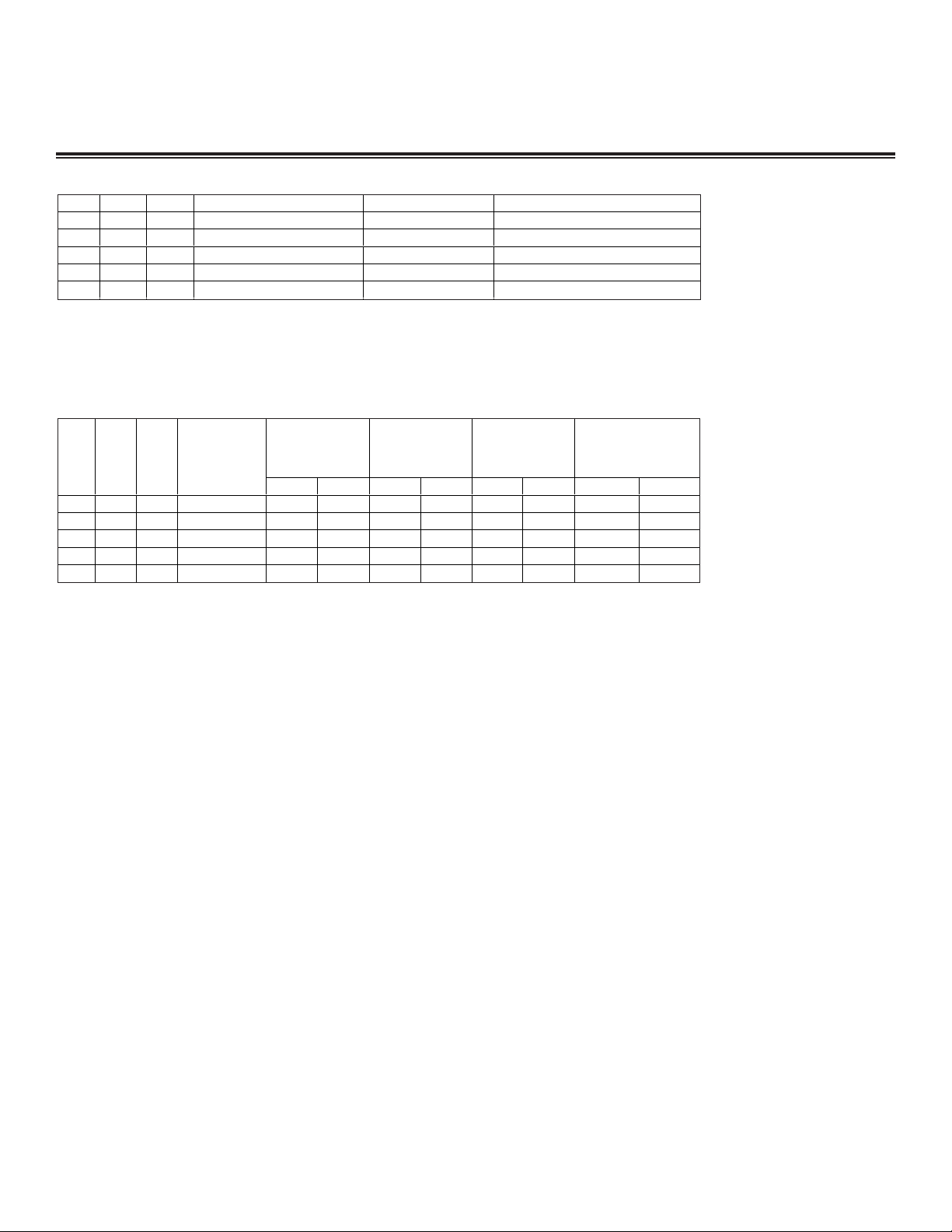

Special-Function Register Maps

Most of the unique features of the high-speed microcontroller family are controlled by bits in SFRs located in unused locations in the

8052 SFR map. This allows for increased functionality, while maintaining complete instruction set compatibility. The SFRs reside in register locations 80h–FFh and are accessed using direct addressing. SFRs that end in 0h or 8h are bit addressable.

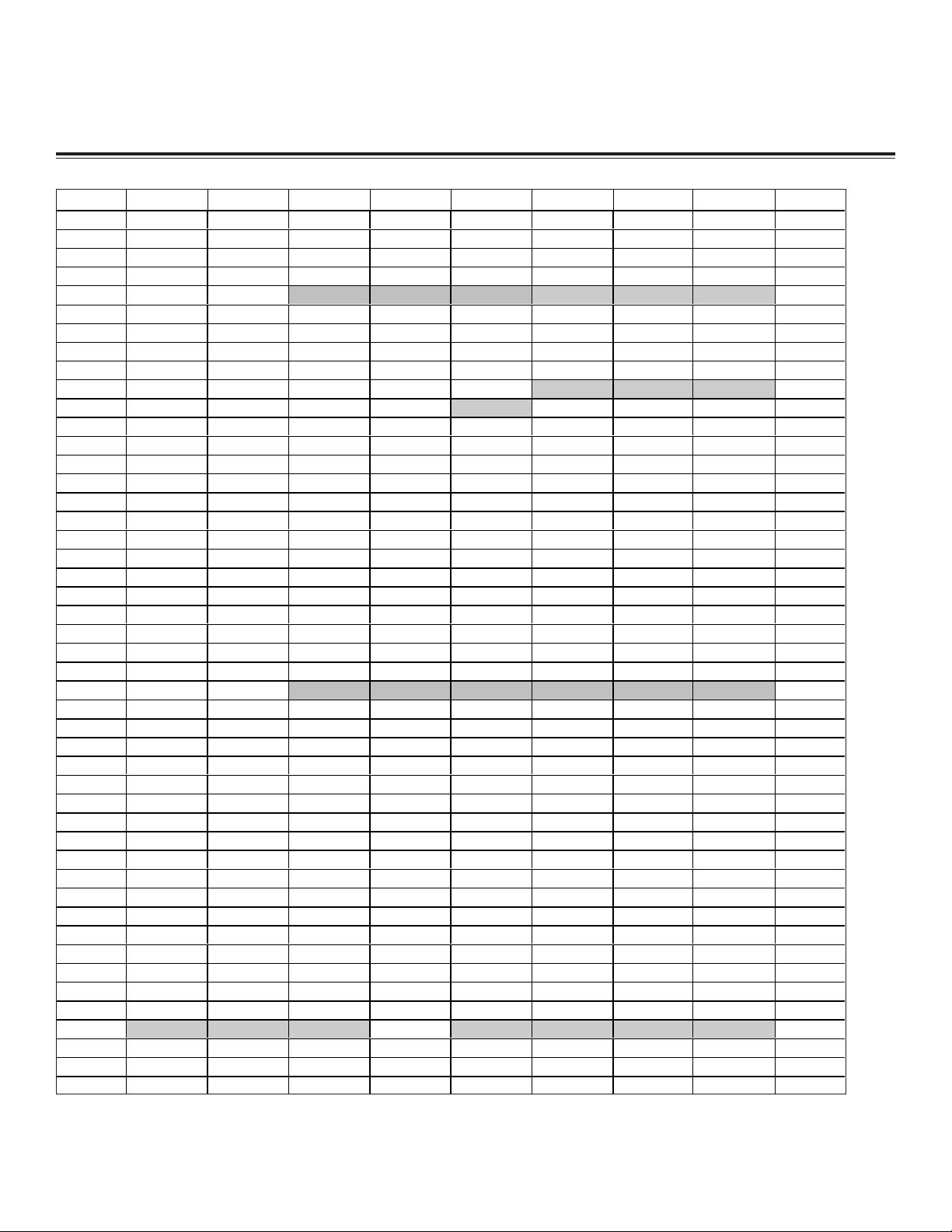

The Special Function Register Map table indicates the names and locations of the SFRs used by the DS80C400. The Special Function

Register Location table shows individual bits in those registers. Bits protected by the timed-access function are shaded. The Special

Function Register Reset Values table indicates the reset state of all SFR bits. Following these tables is a complete description of

DS80C400 SFRs that are new to the 8051 architecture or have new or modified functionality.

17

Page 18

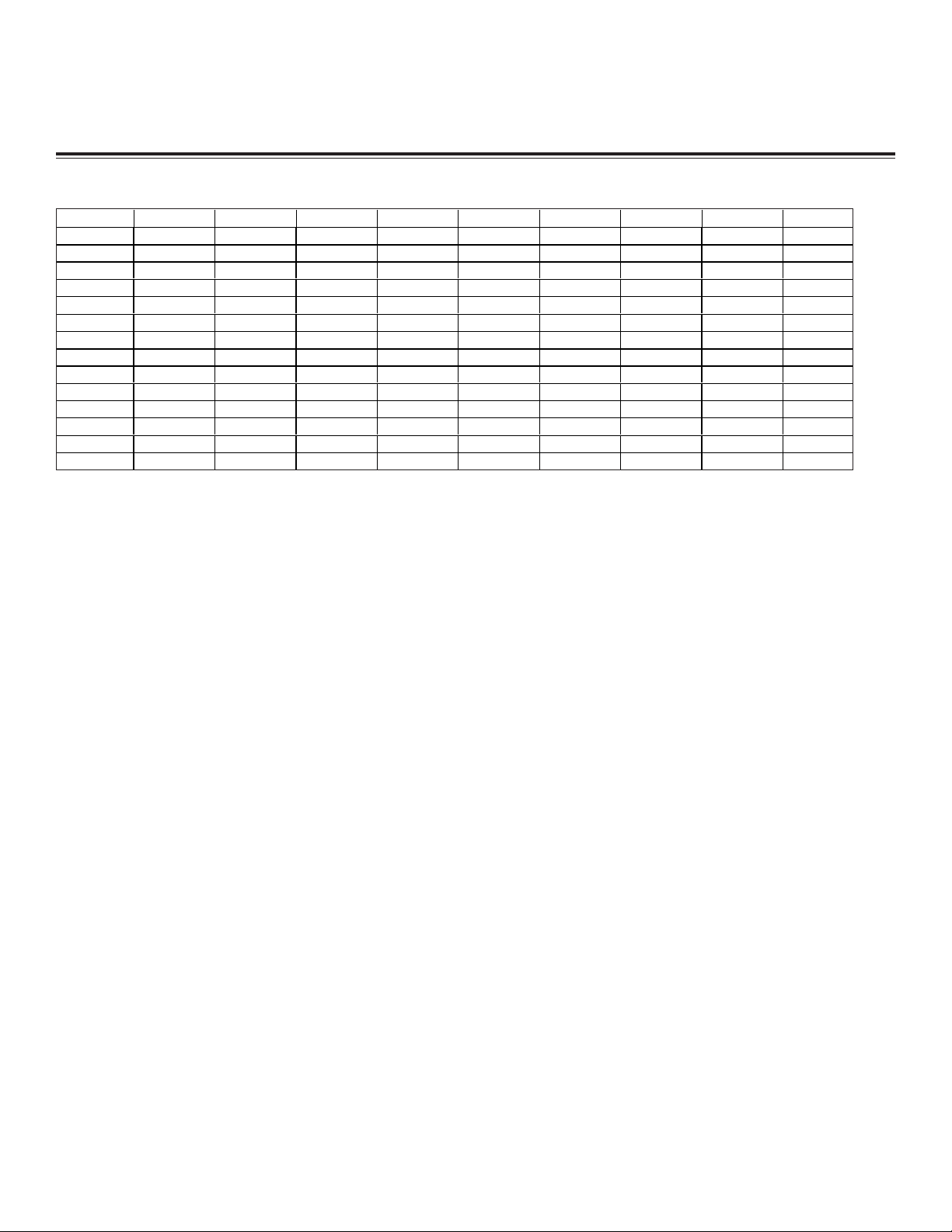

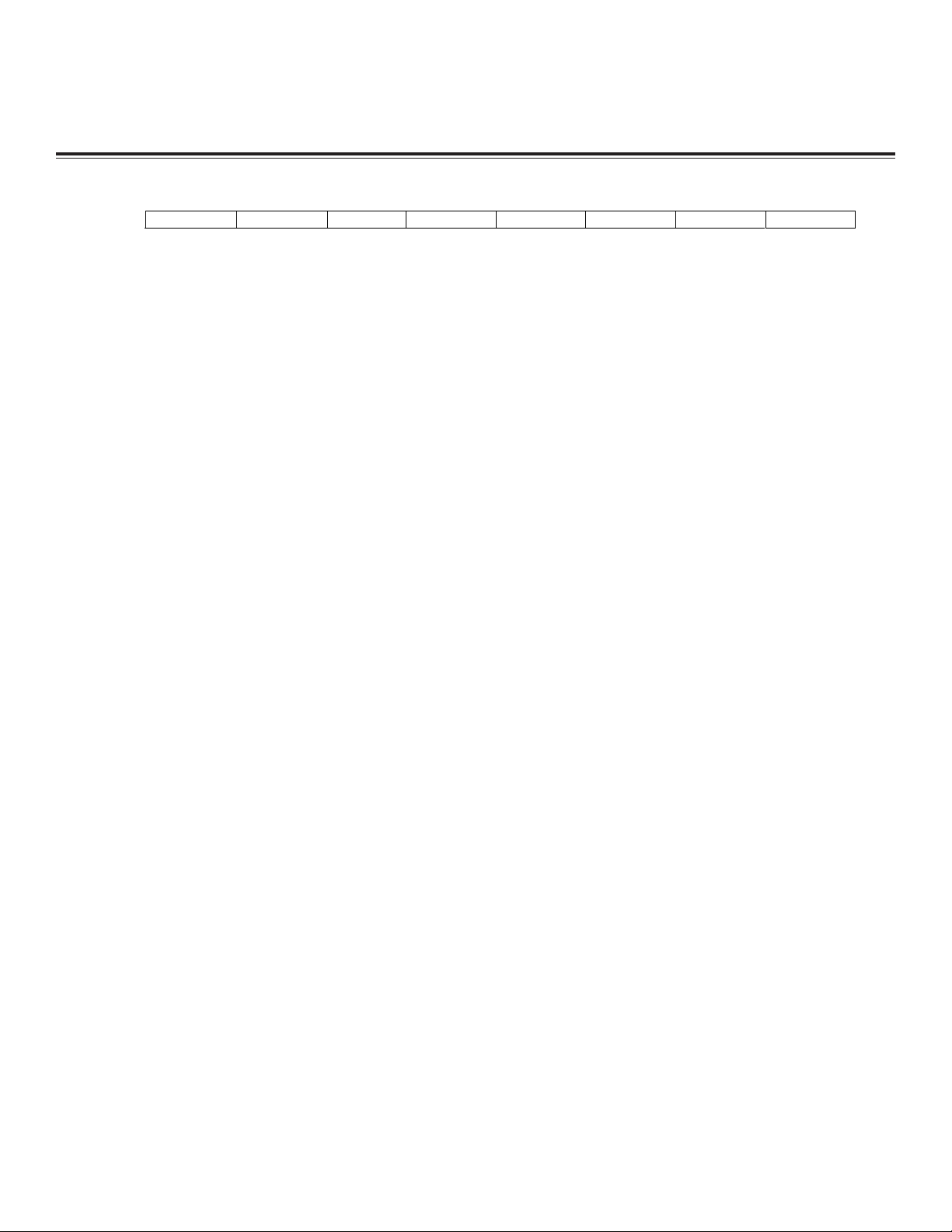

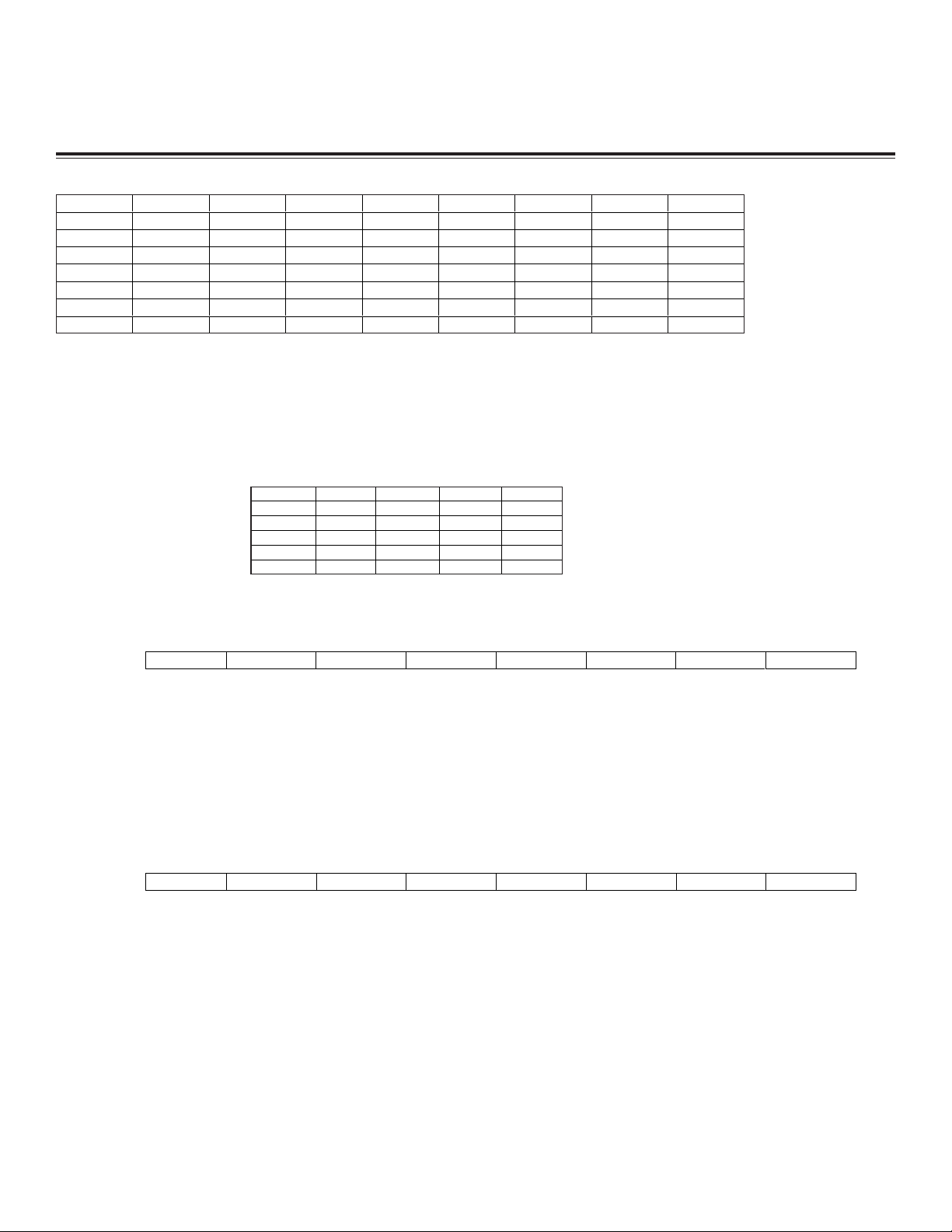

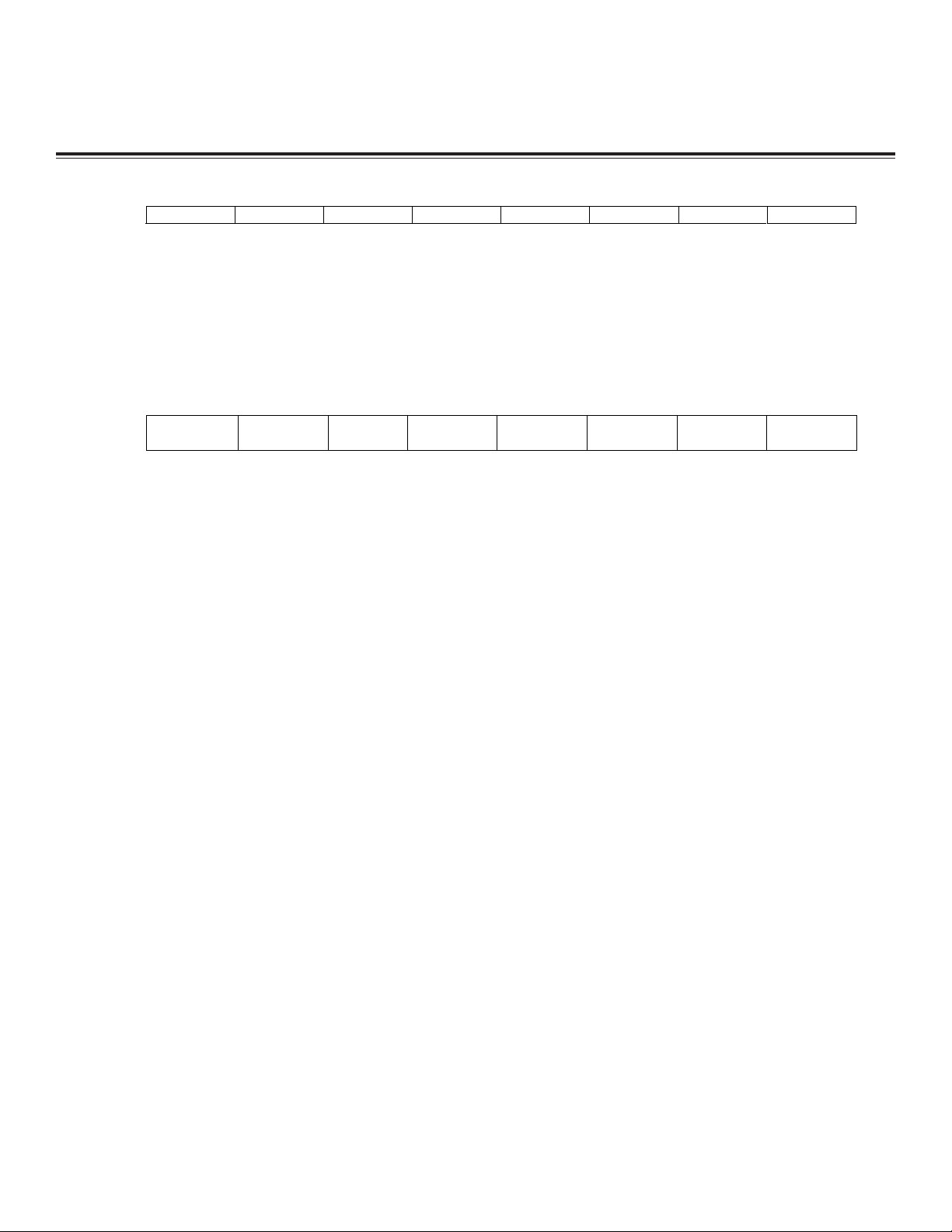

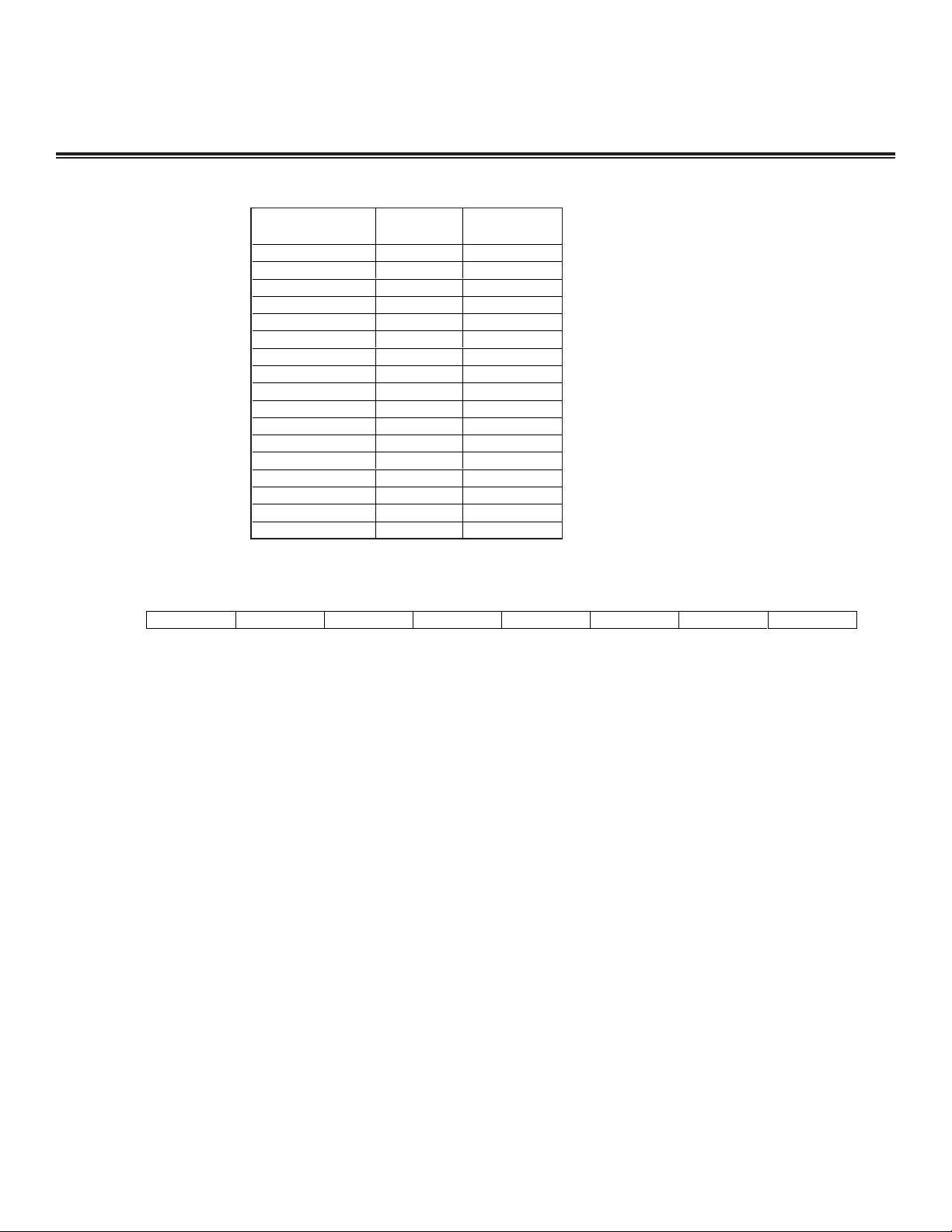

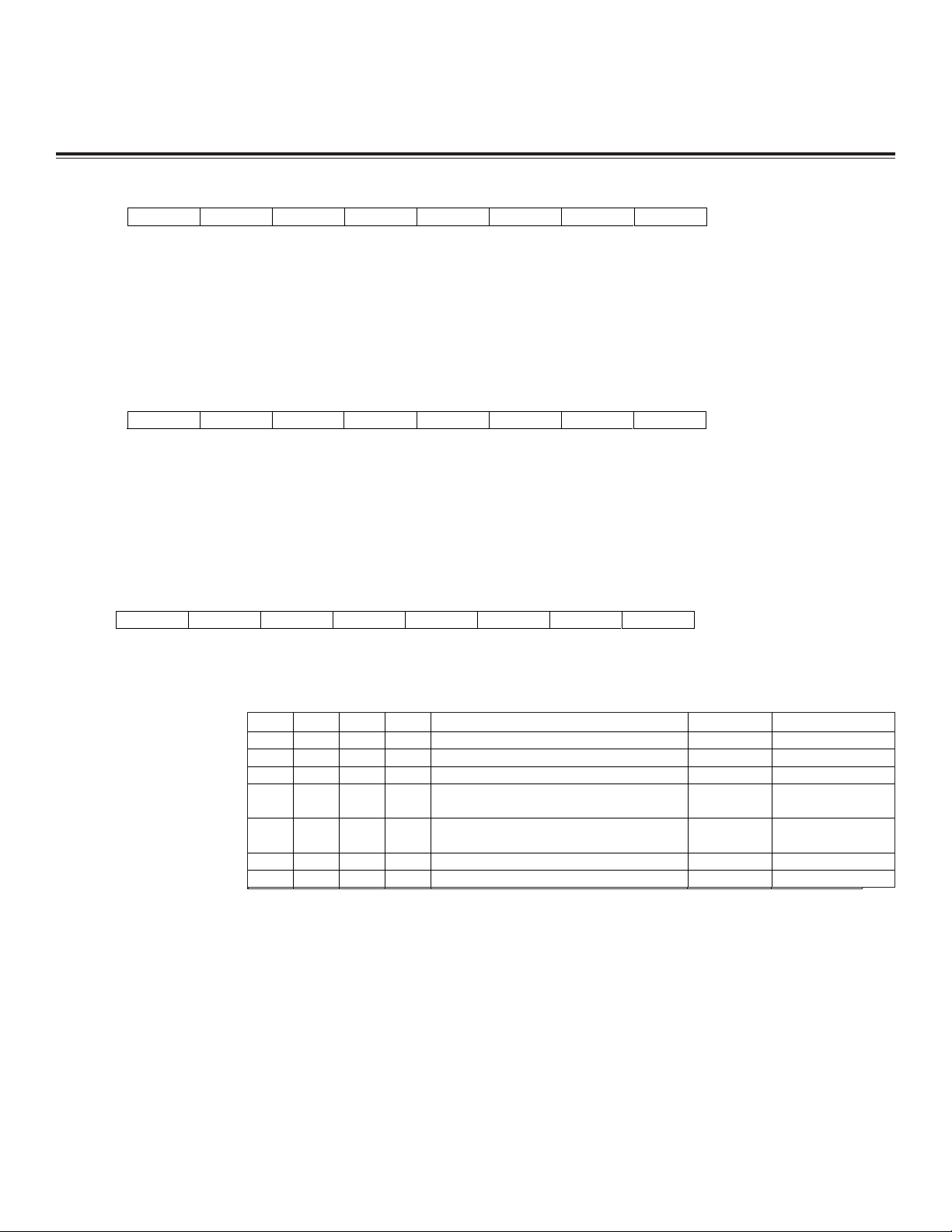

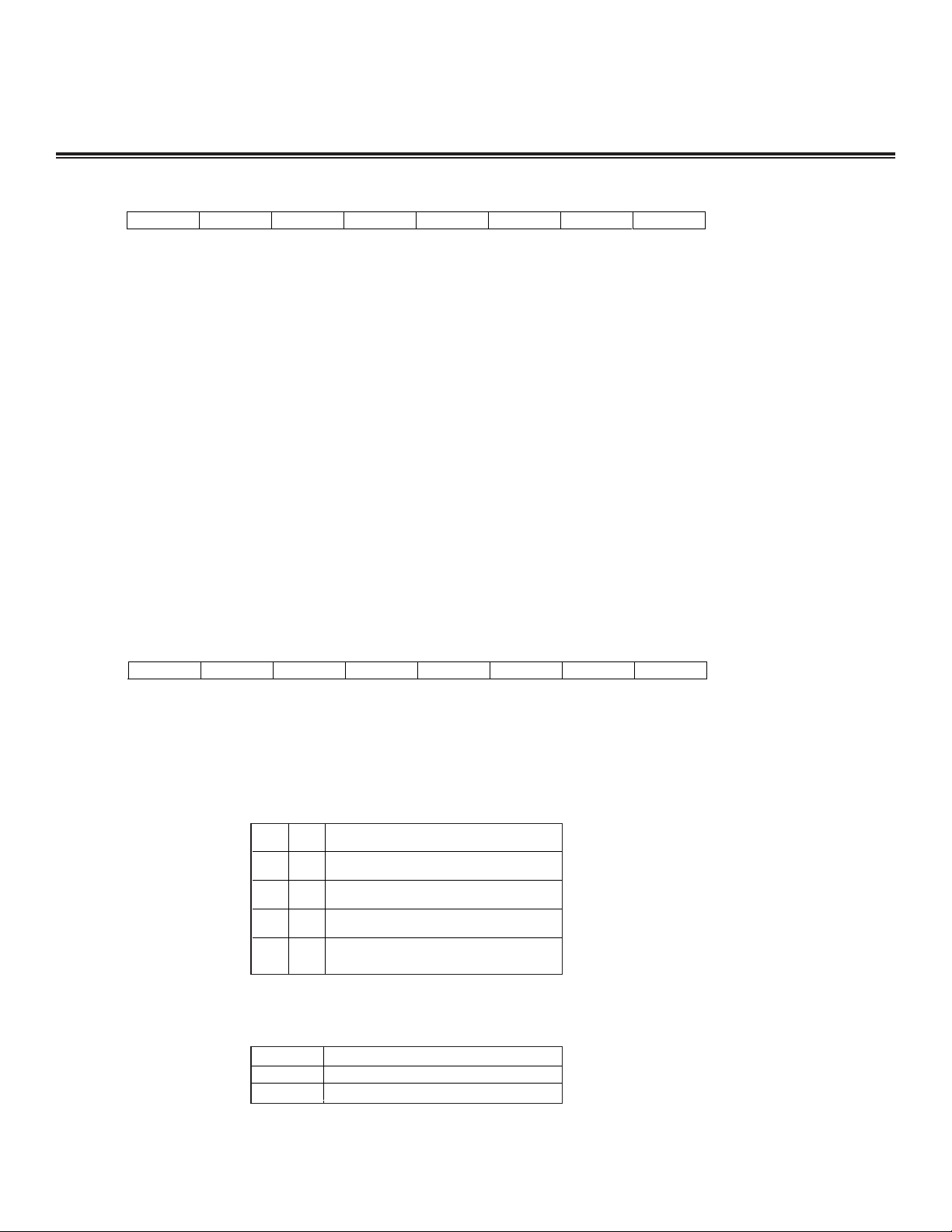

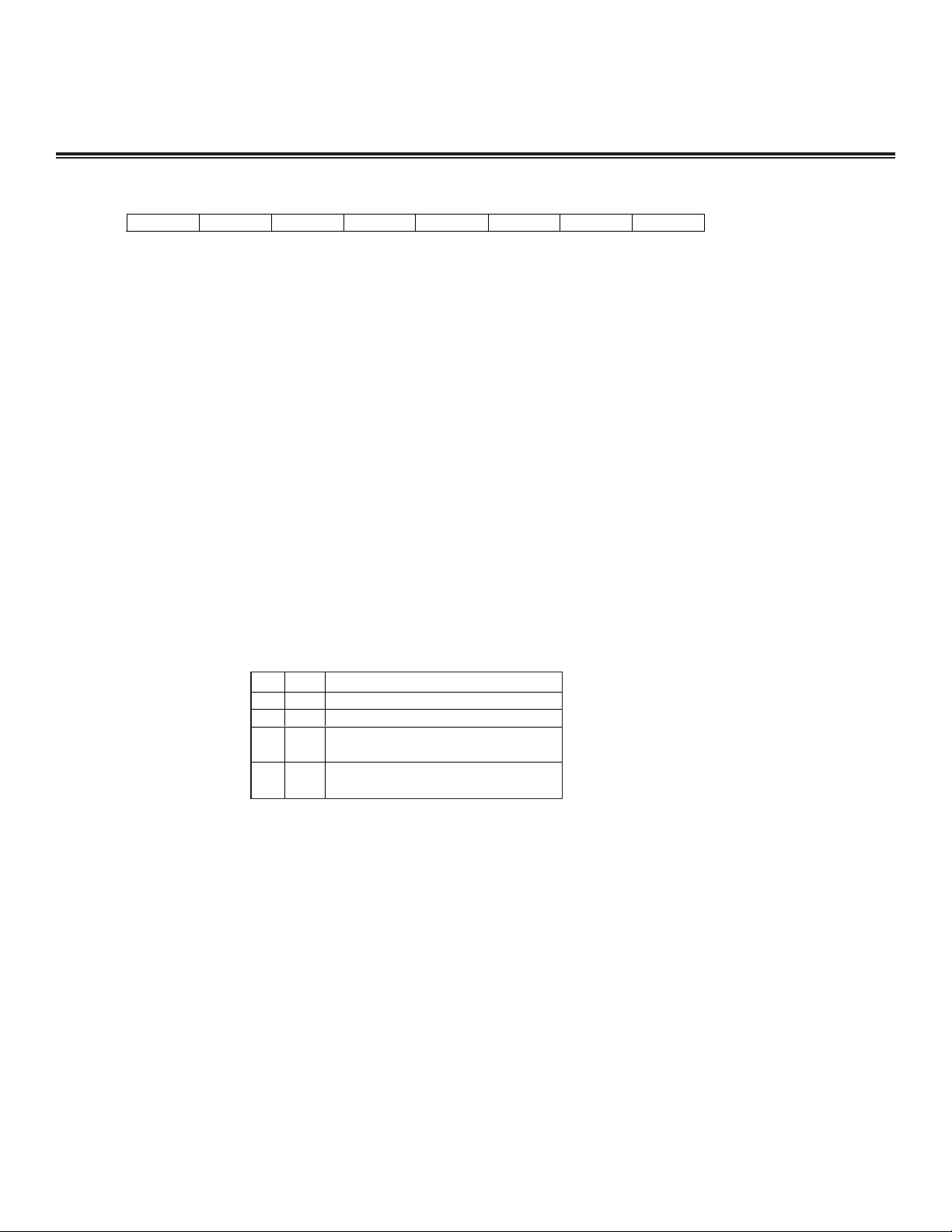

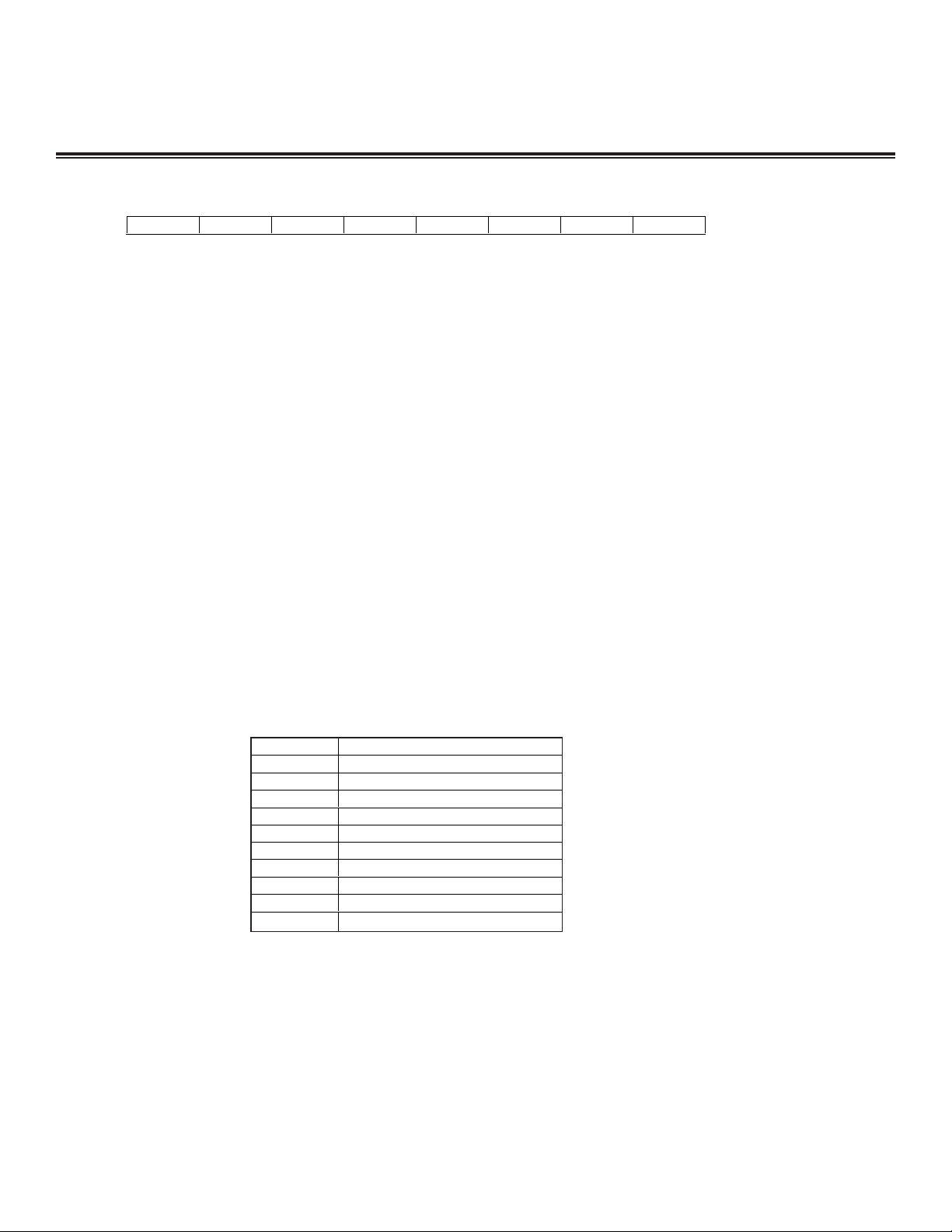

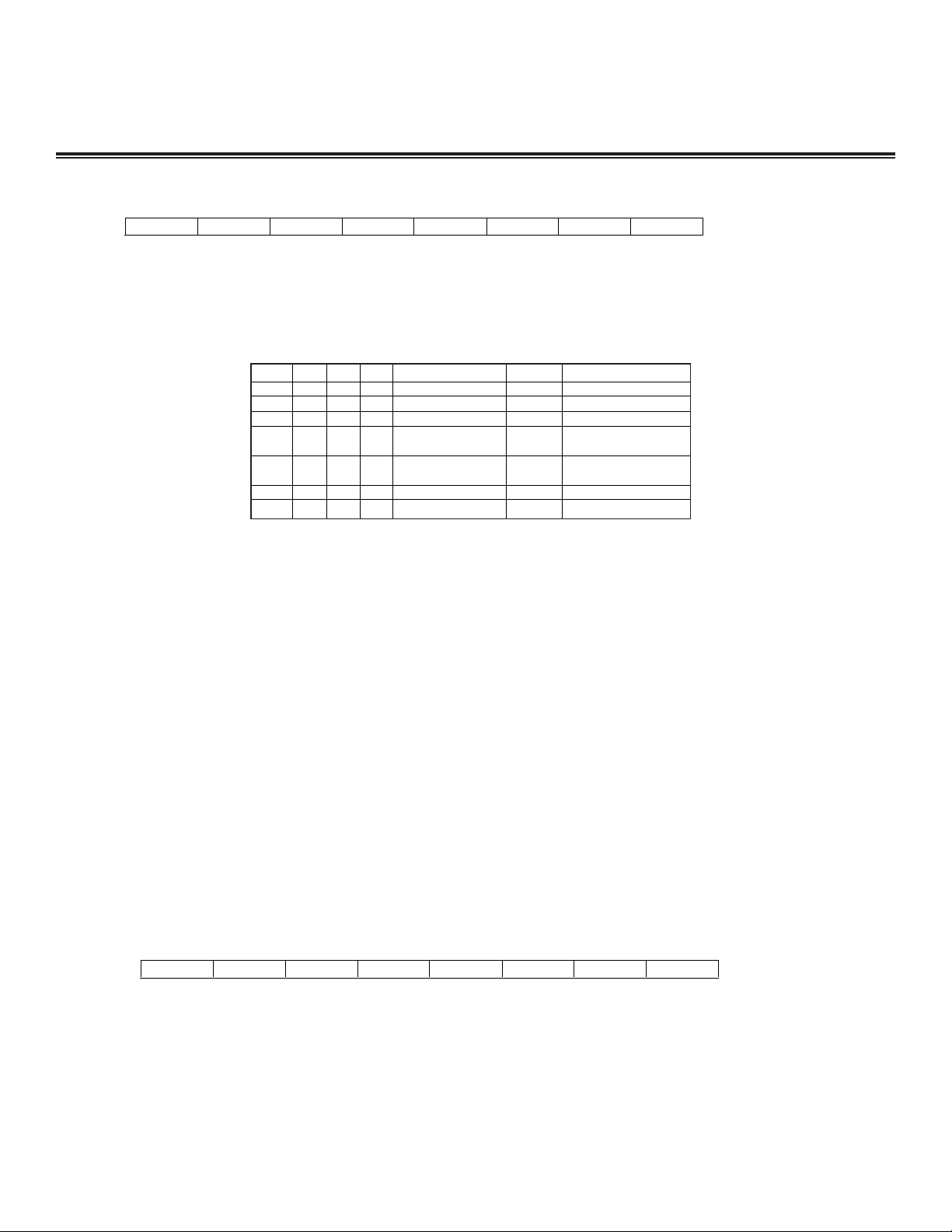

Special-Function Register Map

START

ADDRESS

SFR NAMES

END

ADDRESS

80 P4 SP DPL DPH DPL1 DPH1 DPS PCON 87

88 TCON TMOD TL0 TL1 TH0 TH1 CKCON 8F

90 P1 EXIF P4CNT DPX DPX1 C0RMS0 C0RMS1 97

98 SCON0 SBUF0 ESP AP ACON C0TMA0 C0TMA1 9F

A0 P2 P5 P5CNT C0C C0S C0IR C0TE C0RE A7

A8 IE SADDR0 SADDR1 C0M1C C0M2C C0M3C C0M4C C0M5C AF

B0 P3 P6 P6CNT C0M6C C0M7C C0M8C C0M9C C0M10C B7

B8 IP SADEN0 SADEN1 C0M11C C0M12C C0M13C C0M14C C0M15C BF

C0 SCON1 SBUF1 PMR STATUS MCON TA C7

C8 T2CON T2MOD RCAP2L RCAP2H TL2 TH2 COR CF

D0 PSW MCNT0 MCNT1 MA MB MC MCON1 MCON2 D7

D8 WDCON SADDR2 BPA1 BPA2 BPA3 DF

E0 ACC OCAD CSRD CSRA EBS BCUD BCUC E7

E8 EIE MXAX DPX2 DPX3 OWMAD OWMDR EF

F0 B SADEN2 DPL2 DPH2 DPL3 DPH3 DPS1 STATUS1 F7

F8 EIP P7 TL3 TH3 T3CM SCON2 SBUF2 FF

REGISTER

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

ADDRESS

P4 80h

SP 81h

DPL 82h

DPH 83h

DPL1 84h

DPH1 85h

DPS ID1 ID0 TSL AID SEL1 — — SEL 86h

PCON SMOD_0 SMOD0 OFDF OFDE GF1 GF0 STOP IDLE 87h

TCON TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 88h

TMOD GATE C/ T M1 M0 GATE C/T M1 M0 89h

TL0 8Ah

TL1 8Bh

TH0 8Ch

TH1 8Dh

CKCON WD1 WD0 T2M T1M T0M MD2 MD1 MD0 8Eh

P1 90h

EXIF IE5 IE4 IE3 IE2 CKRY RGMD RGSL BGS 91h

P4CNT — — P4CNT.5 P4CNT.4 P4CNT.3 P4CNT.2 P4CNT.1 P4CNT.0 92h

DPX 93h

DPX1 95h

C0RMS0* 96h

C0RMS1* 97h

Maxim Integrated

Special-Function Register Location

High-Speed Microcontroller User’s

Guide: Network Microcontroller

Supplement

18

Page 19

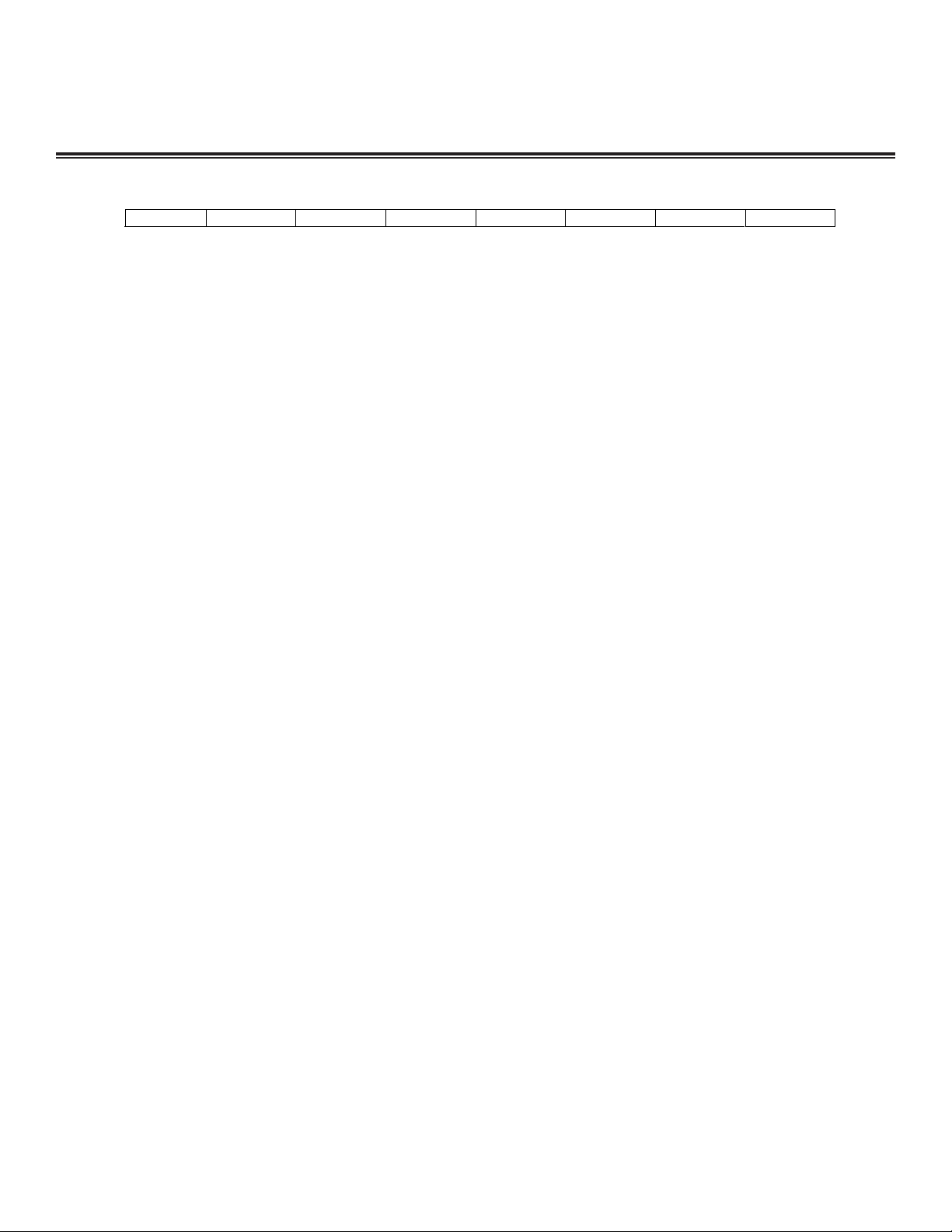

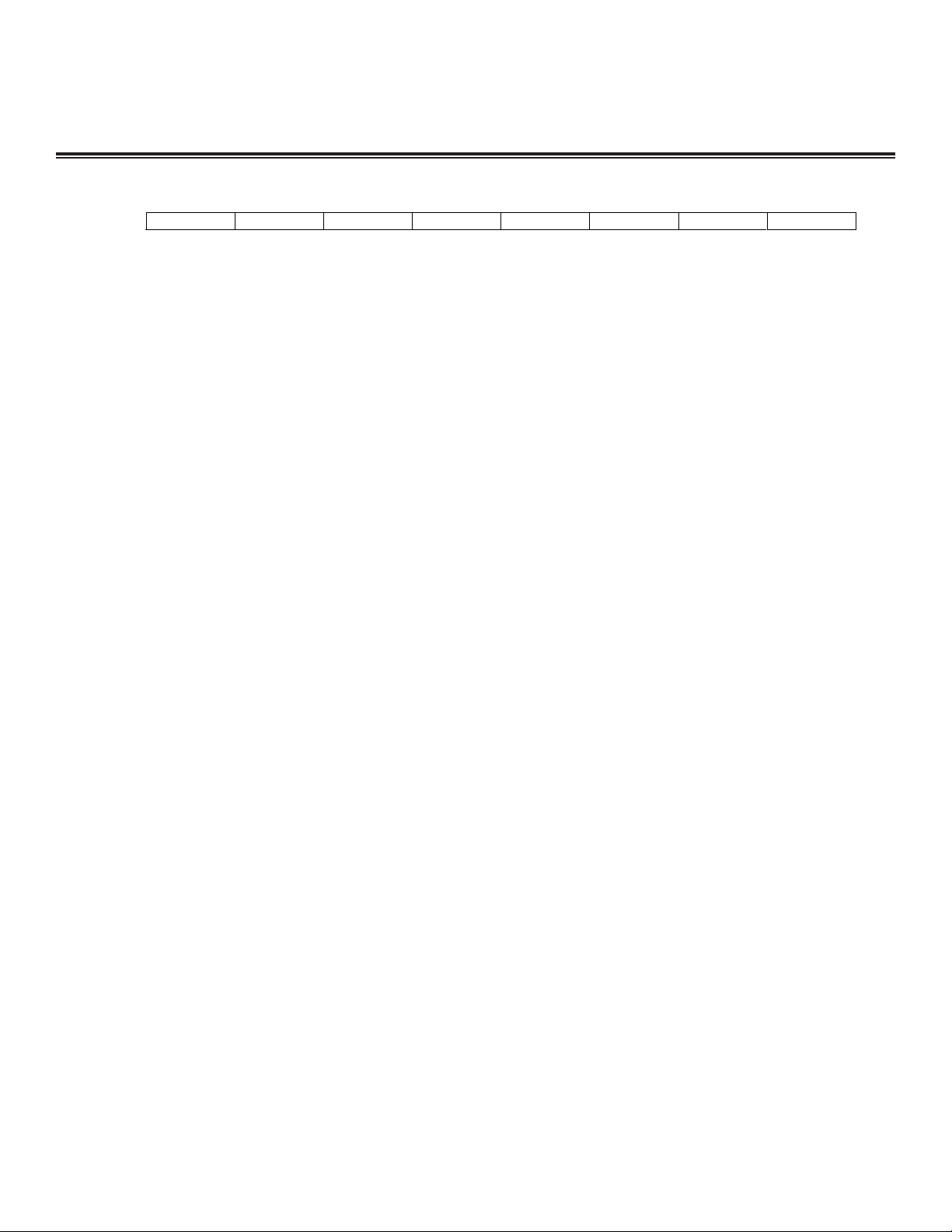

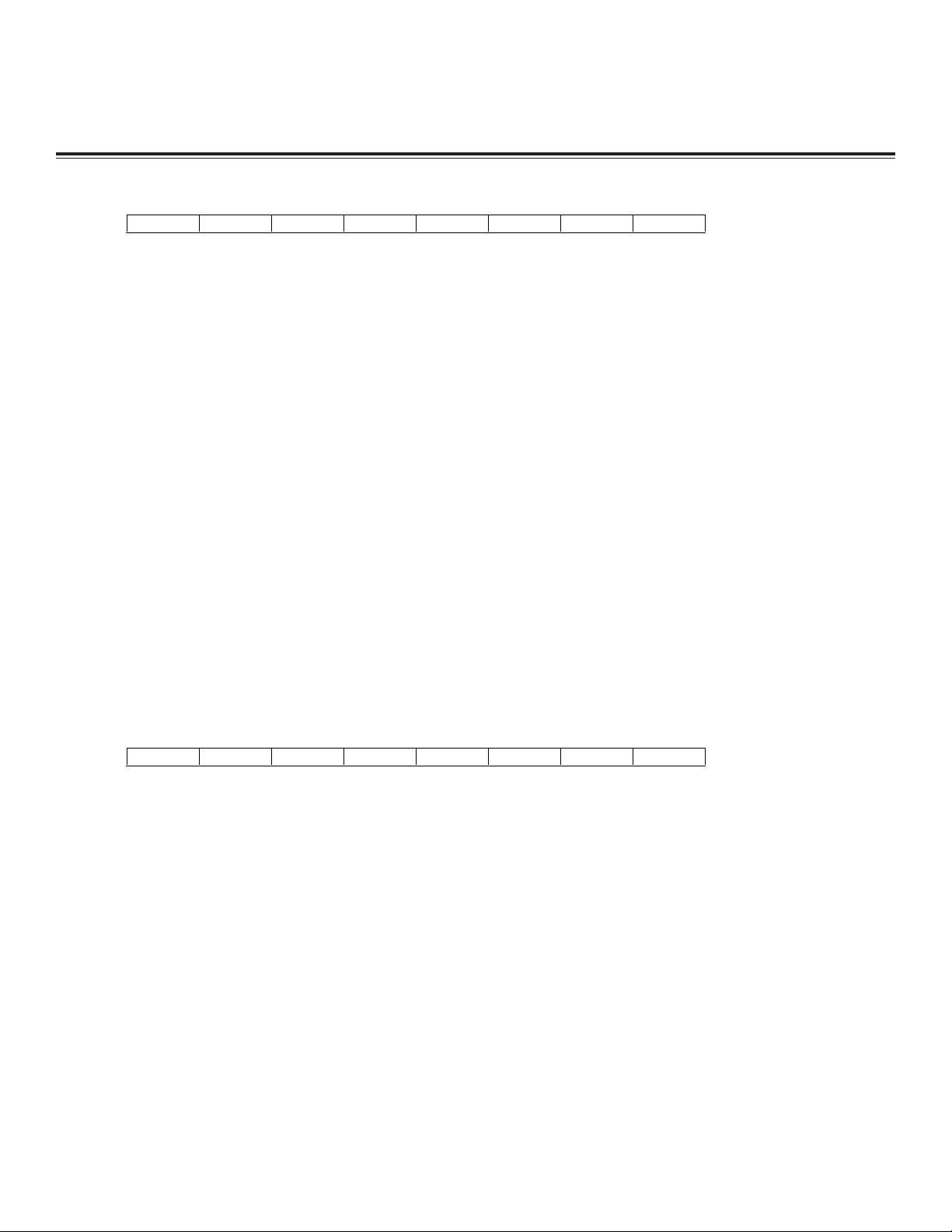

High-Speed Microcontroller User’s

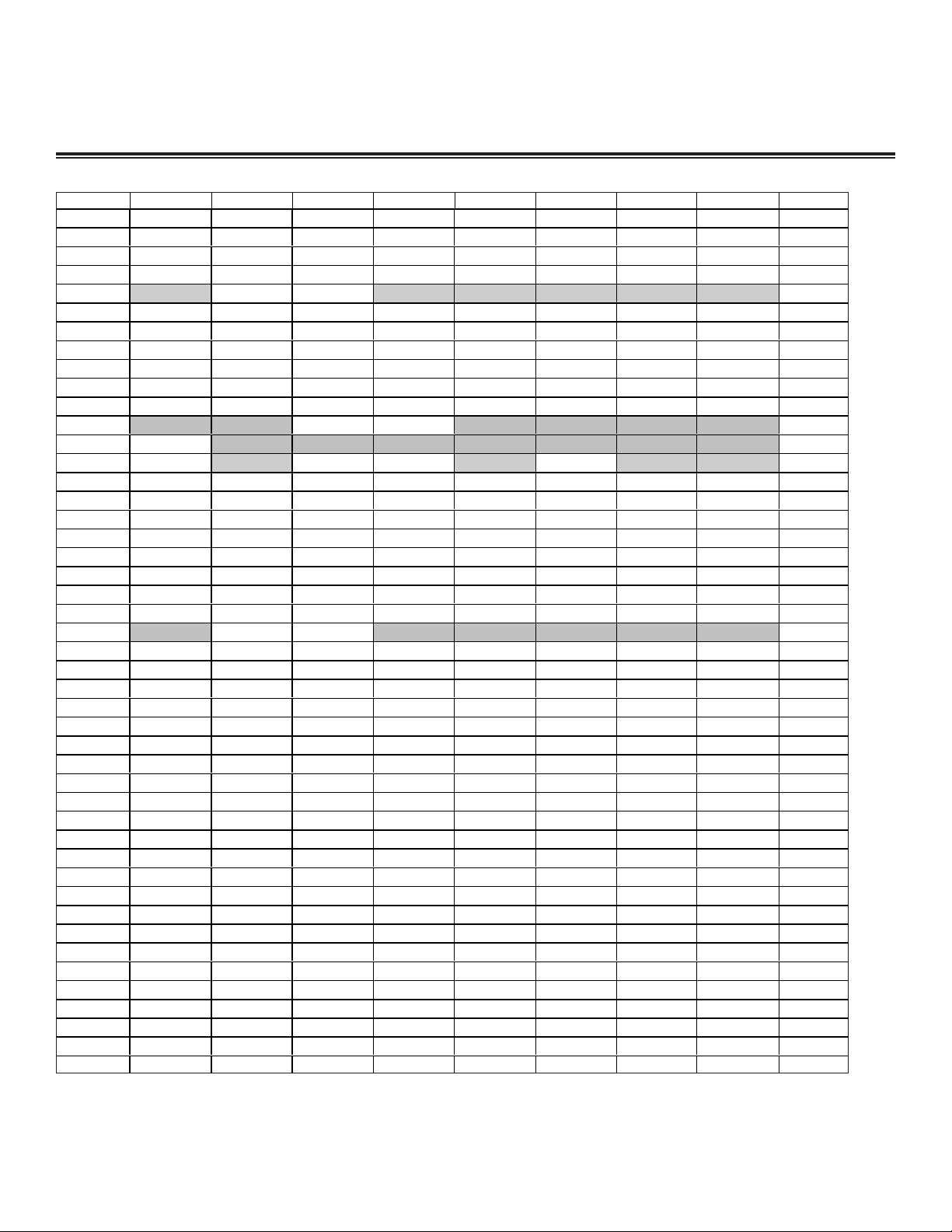

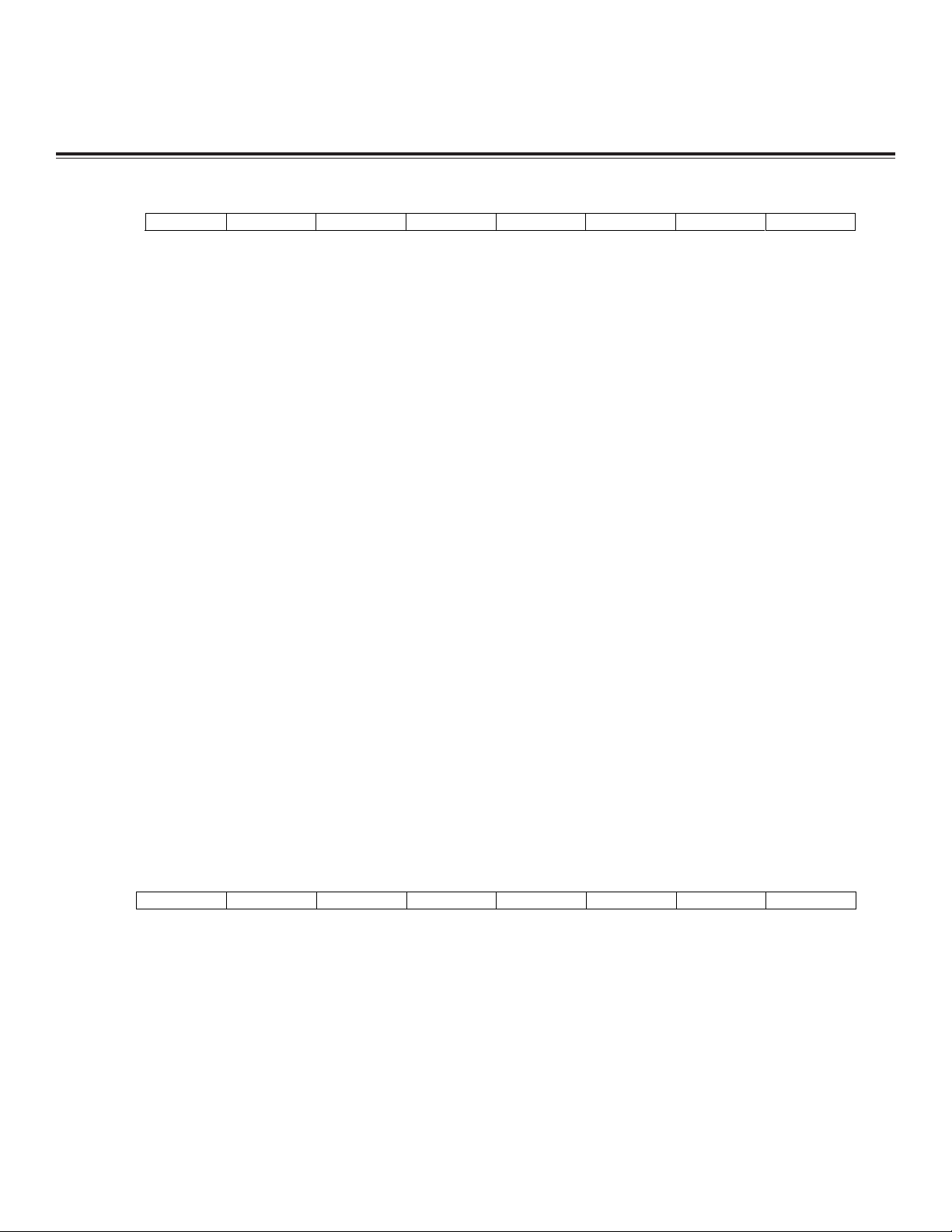

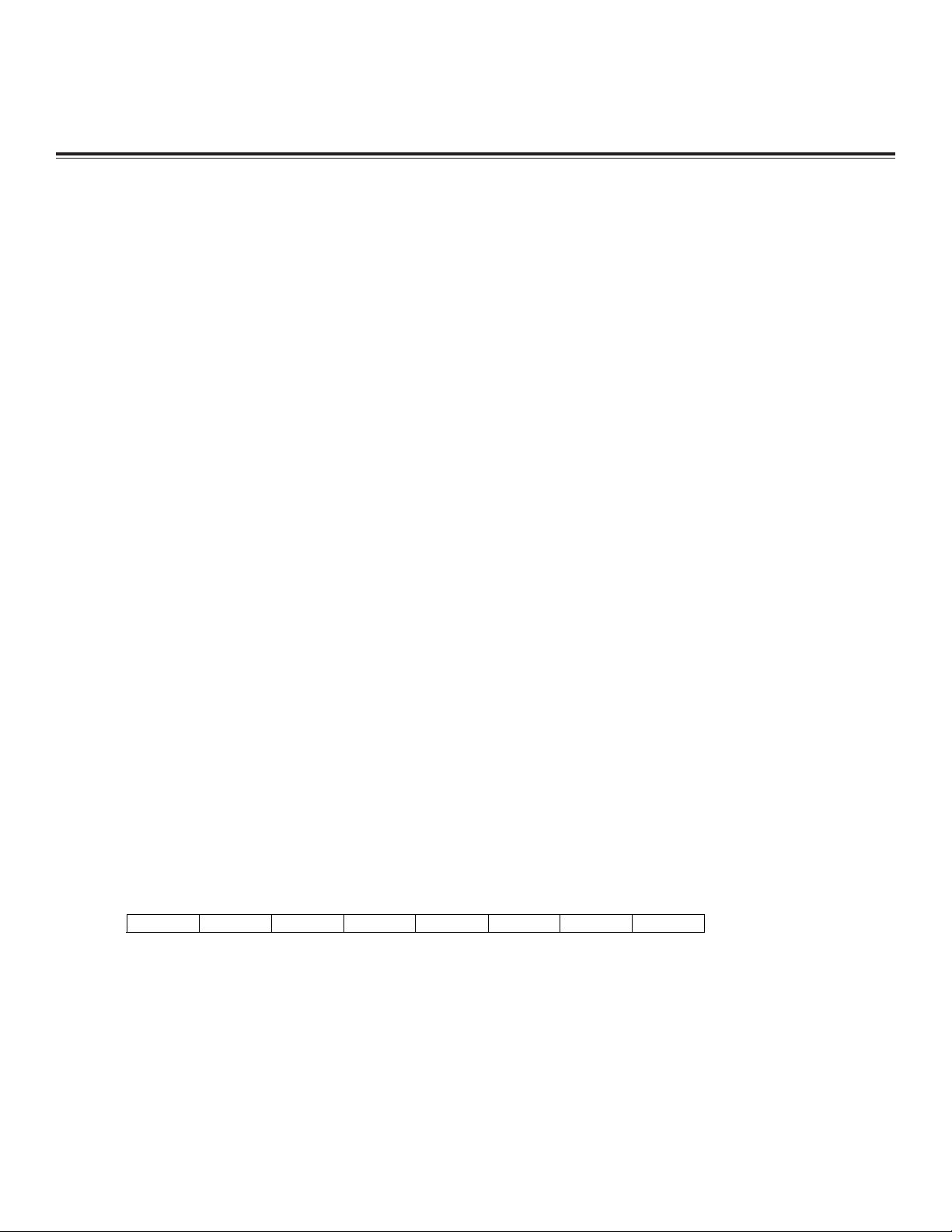

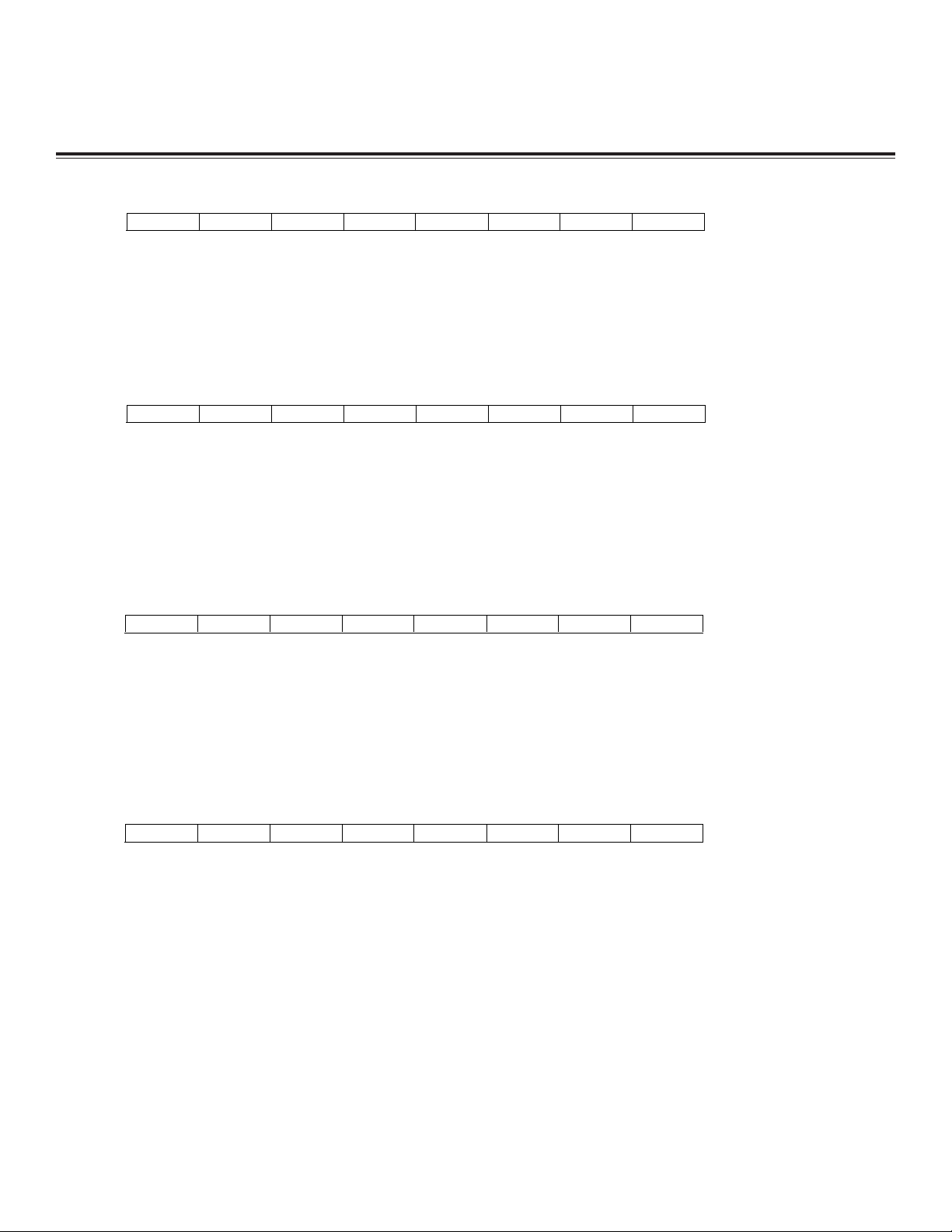

REGISTER

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

ADDRESS

SCON0 SM0/FE_0 SM1_0 SM2_0 REN_0 TB8_0 RB8_0 TI_0 RI_0 98h

SBUF0 99h

ESP — — — — — — ESP.1 ESP.0 9Bh

AP 9Ch

ACON — — MROM BPME BROM SA AM1 AM0 9Dh

C0TMA0* 9Eh

C0TMA1* 9Fh

P2 A0h

P5 A1h

P5CNT* — CAN0BA — — C0_I/O P5CNT.2 P5CNT.1 P5CNT.0 A2h

C0C* ERIE STIE PDE SIESTA CRST AUTOB ERCS SWINT A3h

C0S* BSS EC96/128 WKS RXS TXS ER2 ER1 ER0 A4h

C0IR* INTIN7 INTIN6 INTIN5 INTIN4 INTIN3 INTIN2 INTIN1 INTIN0 A5h

C0TE* A6h

C0RE* A7h

IE EA ES1 ET2 ES0 ET1 EX1 ET0 EX0 A8h

SADDR0 A9h

SADDR1 AAh

C0M1C* MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP ABh

C0M2C* MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP ACh

C0M3C* MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP ADh

C0M4C* MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP AEh

C0M5C* MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP AFh

P3 B0h

P6 B1h

P6CNT — — P6CNT.5 P6CNT.4 P6CNT.3 P6CNT.2 P6CNT.1 P6CNT.0 B2h

C0M6C* MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP B3h

C0M7C* MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP B4h

C0M8C* MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP B5h

C0M9C* MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP B6h

C0M10C* MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP B7h

IP — PS1 PT2 PS0 PT1 PX1 PT0 PX0 B8h

SADEN0 B9h

SADEN1 BAh

C0M11C* MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP BBh

C0M12C* MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP BCh

C0M13C* MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP BDh

C0M14C* MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP BEh

C0M15C* MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP BFh

SCON1 SM0/FE_1 SM1_1 SM2_1 REN_1 TB8_1 RB8_1 TI_1 RI_1 C0h

SBUF1 C1h

PMR CD1 CD0 SWB CTM 4X/2X ALEOFF — — C4h

STATUS PIP HIP LIP — SPTA1 SPRA1 SPTA0 SPRA0 C5h

MCON* IDM1 IDM0 CMA — PDCE3 PDCE2 PDCE1 PDCE0 C6h

TA C7h

T2CON TF2 EXF2 RCLK TCLK EXEN2 TR2 C/T2 CP/RL2 C8h

T2MOD — — — D13T1 D13T2 — T2OE DCEN C9h

Maxim Integrated

Guide: Network Microcontroller

Supplement

Special-Function Register Location (continued)

19

Page 20

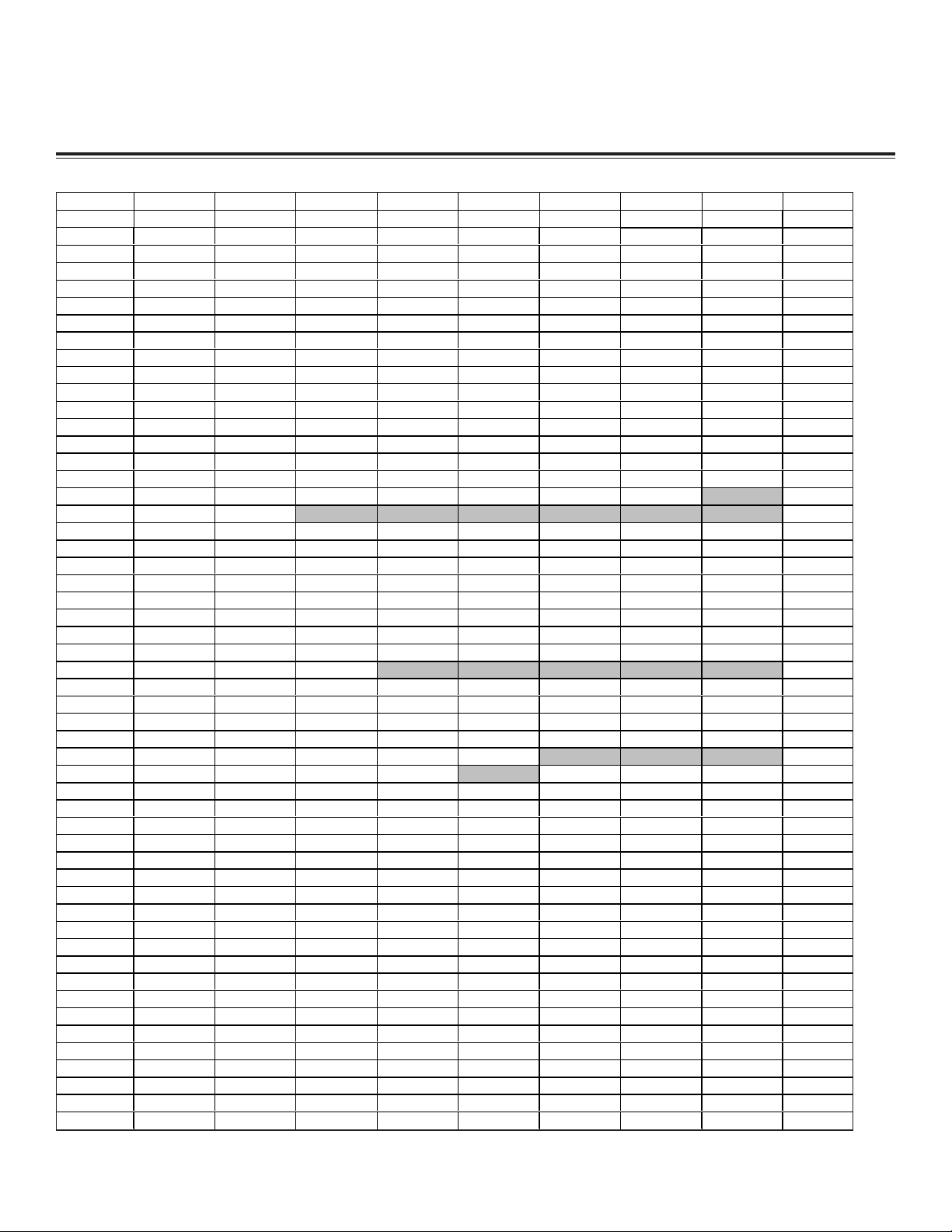

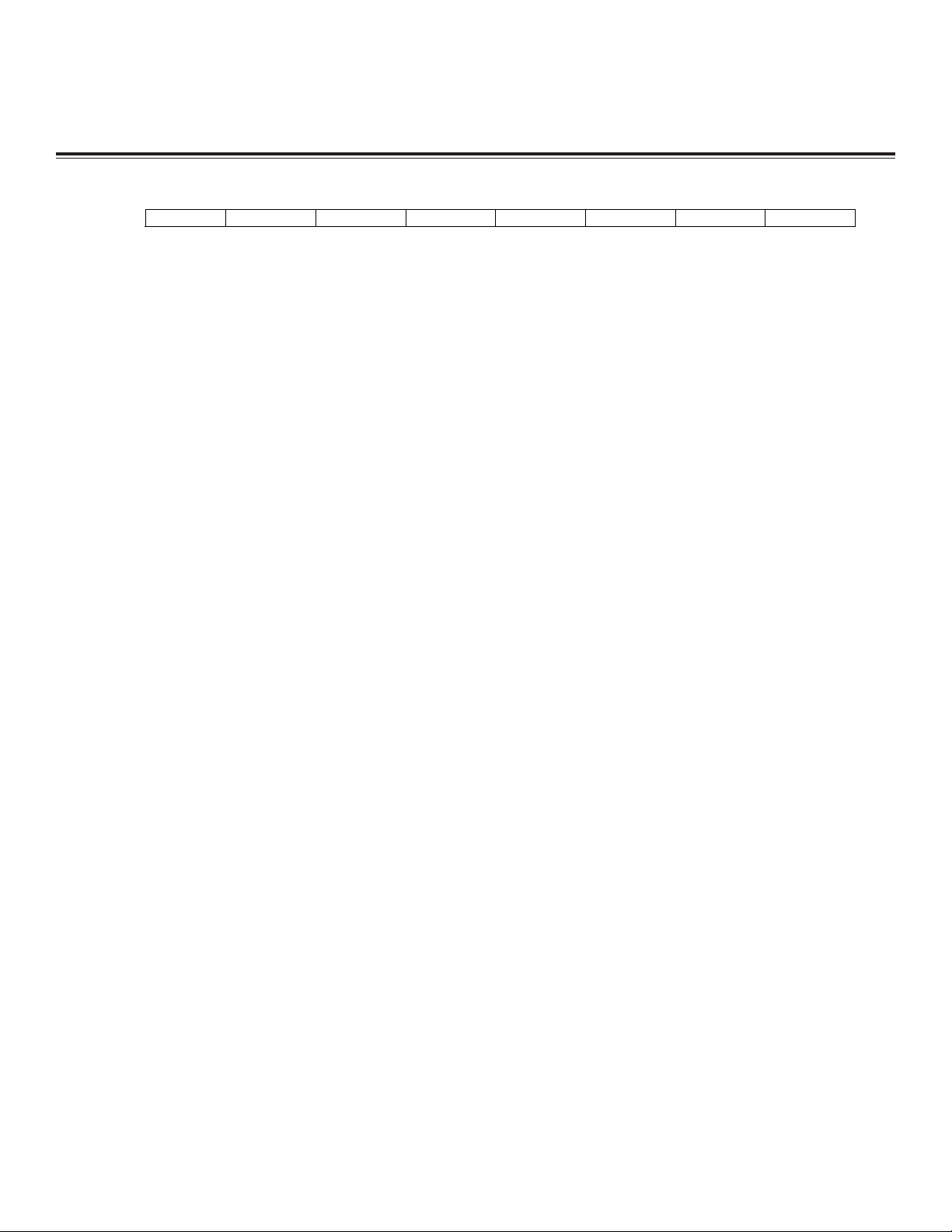

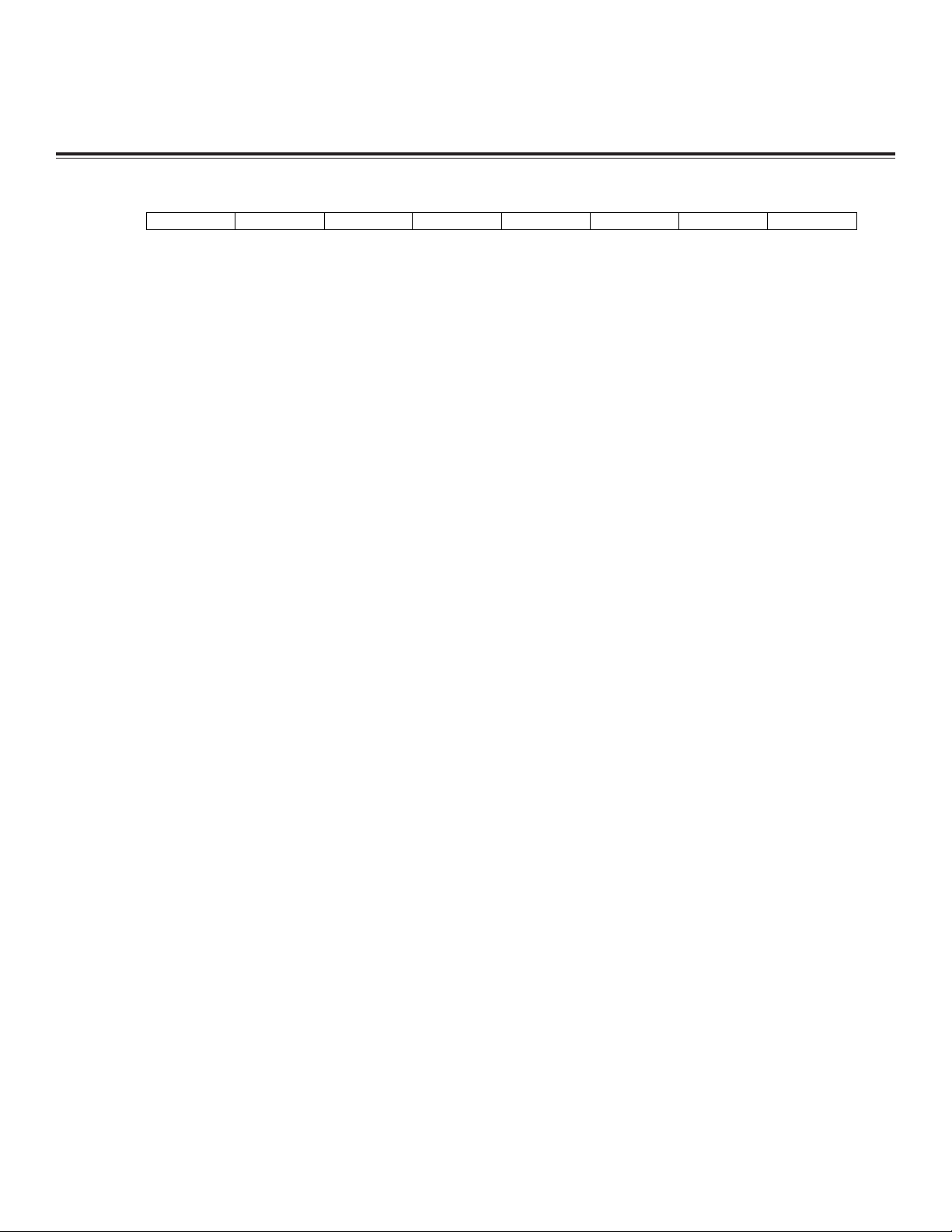

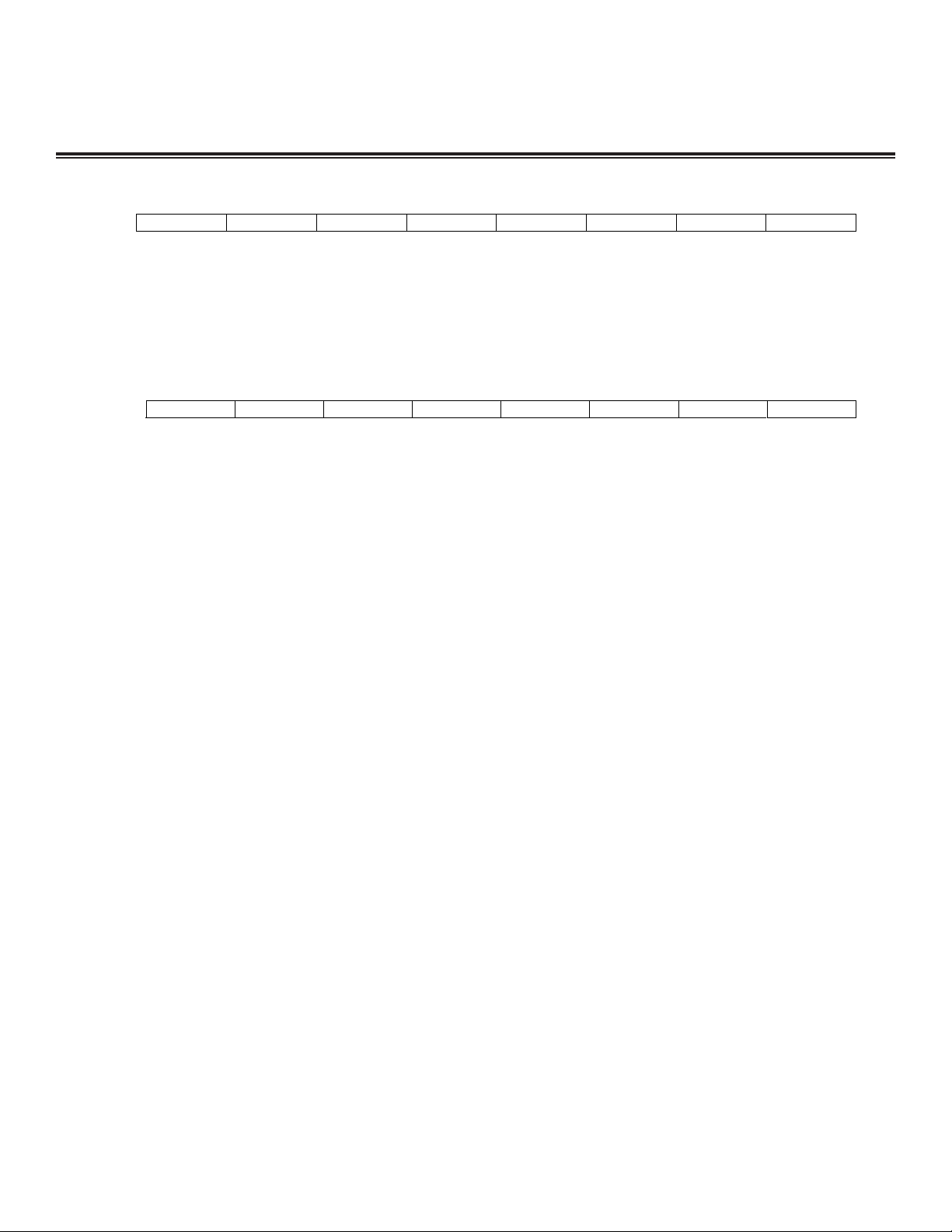

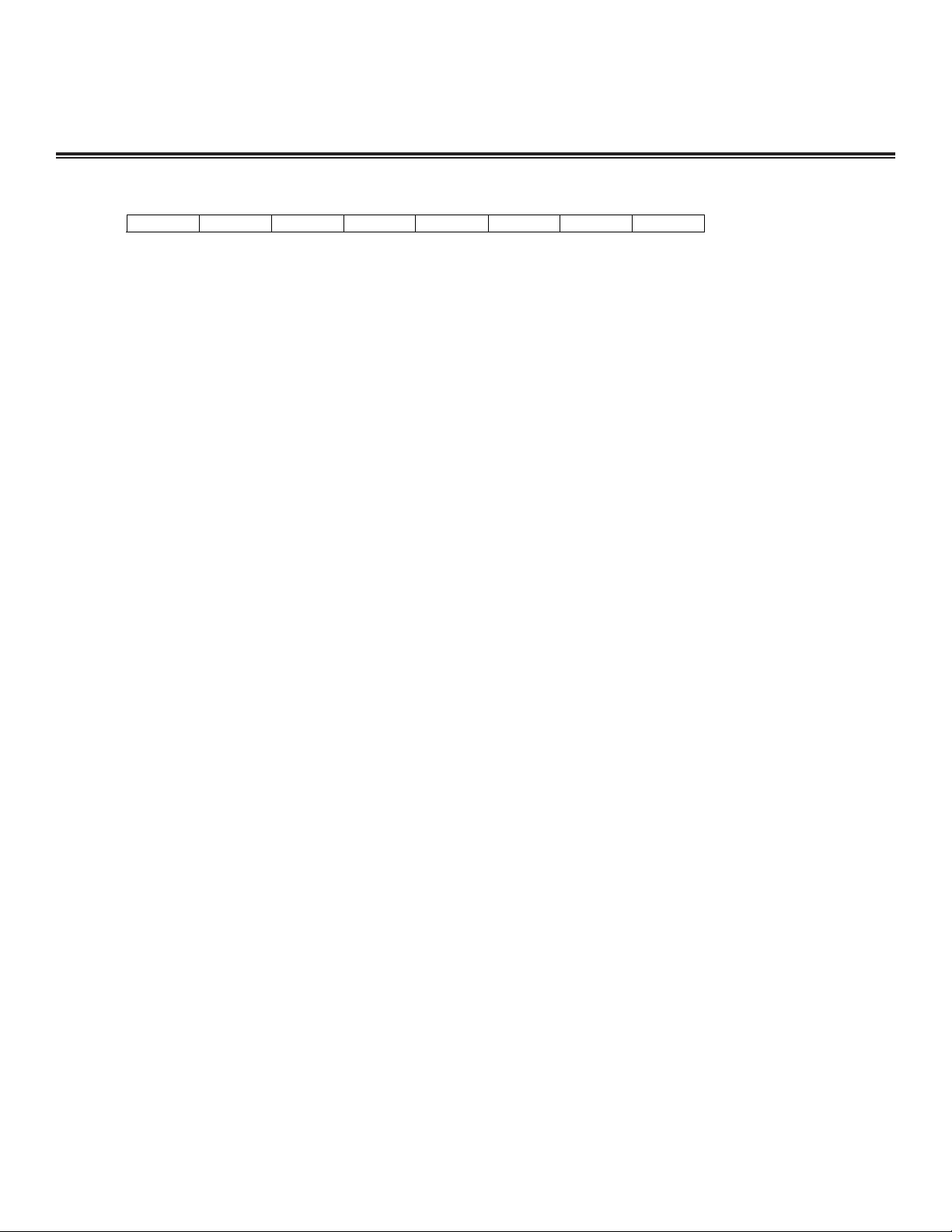

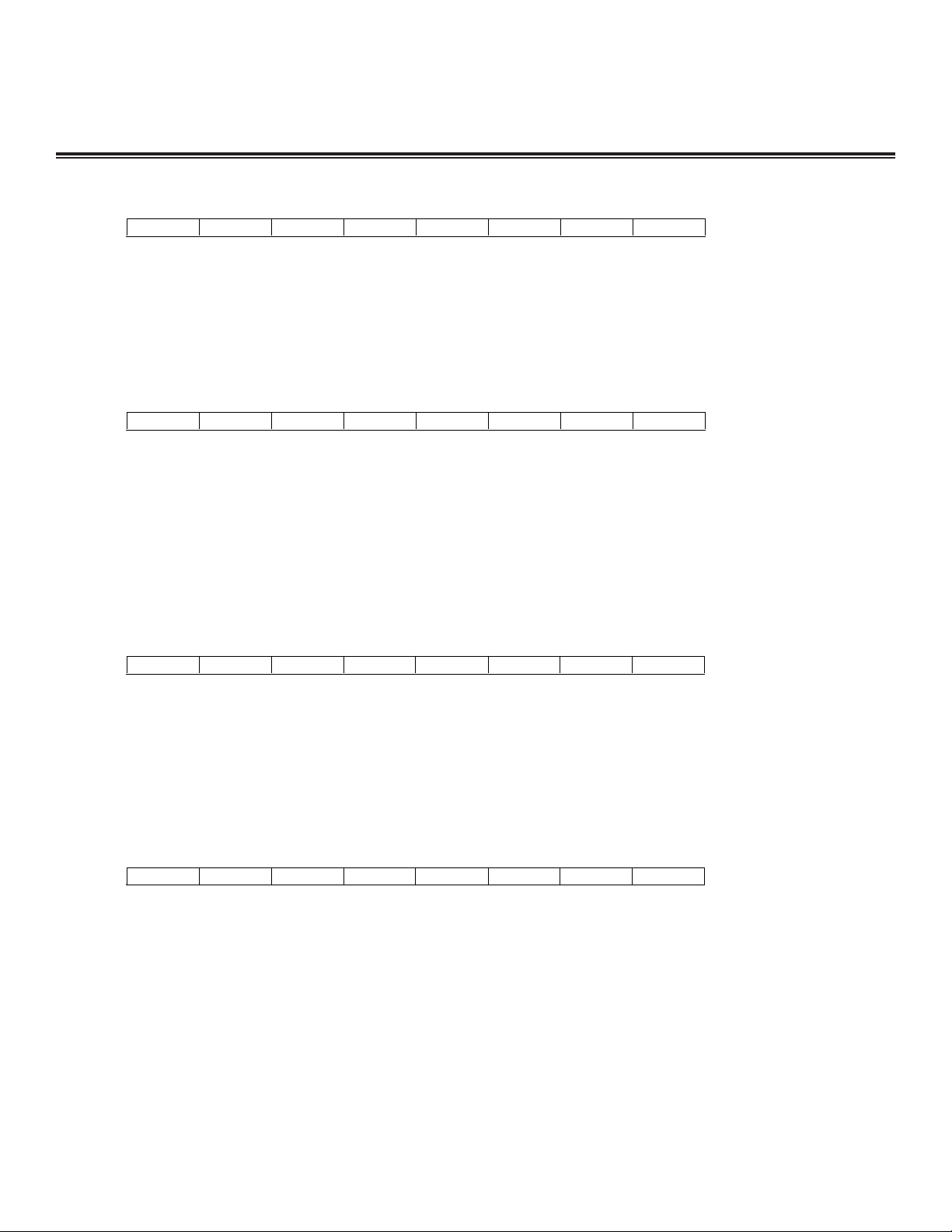

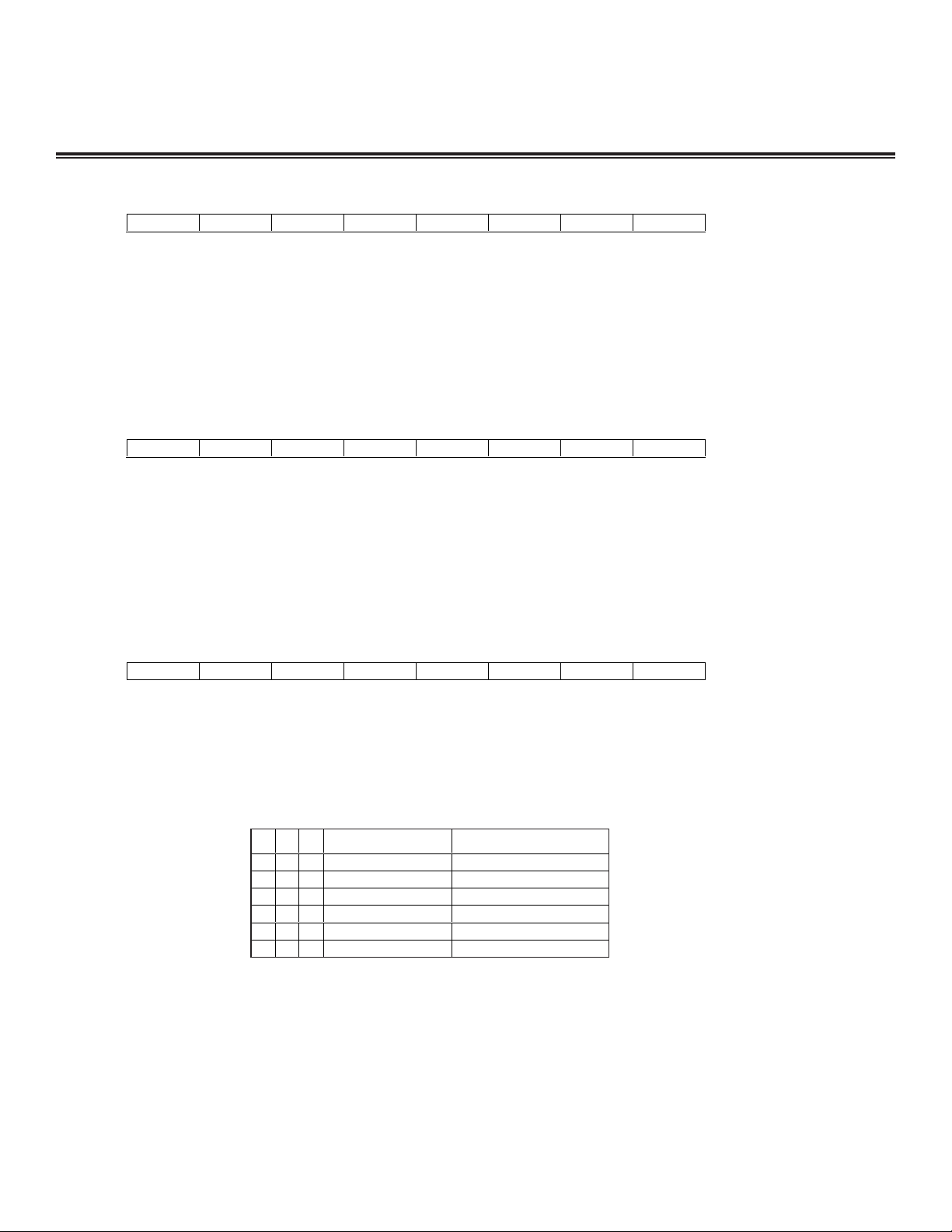

High-Speed Microcontroller User’s

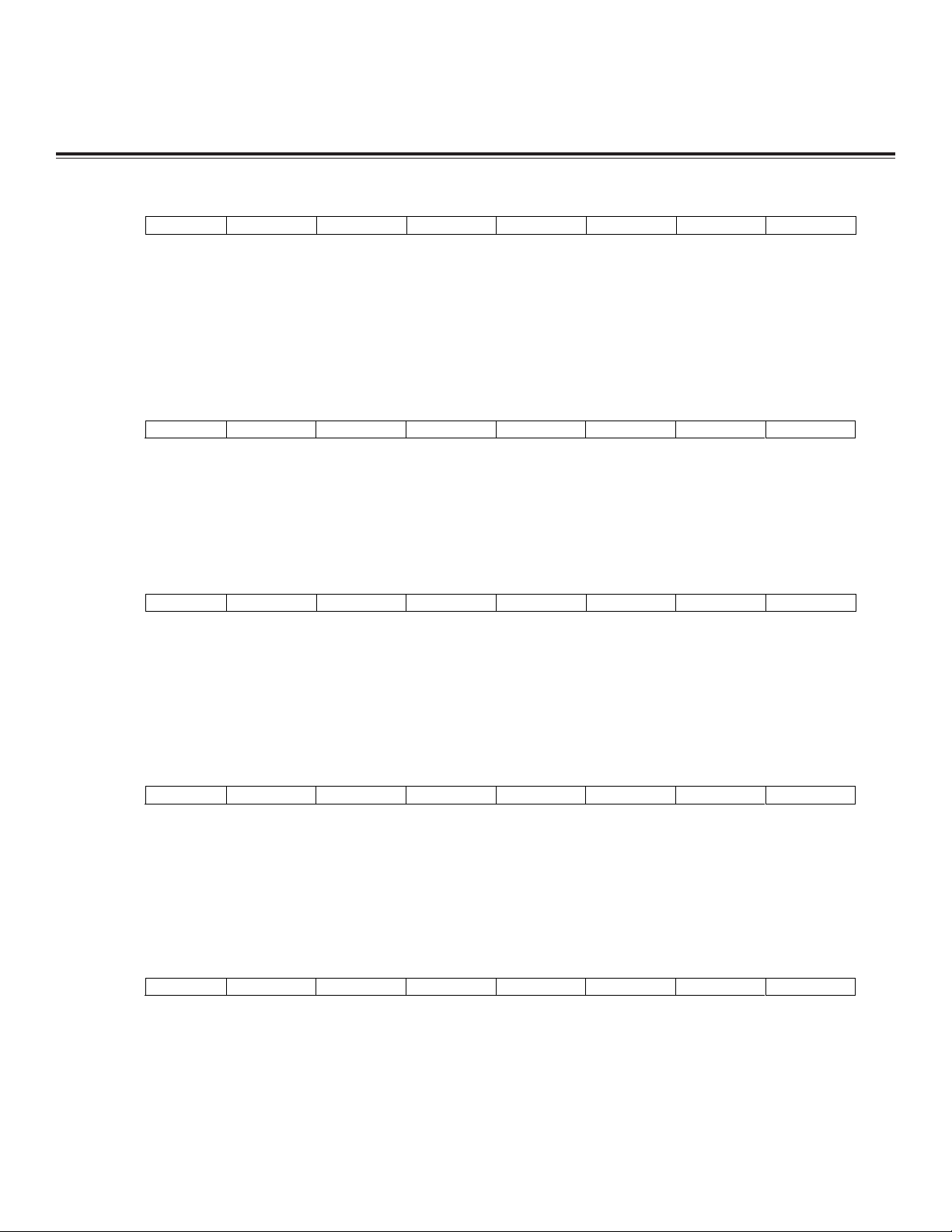

REGISTER

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

ADDRESS

RCAP2L CAh

RCAP2H CBh

TL2 CCh

TH2 CDh

COR* IRDACK ——C0BPR7 C0BPR6 COD1 COD0 XCLKOE CEh

PSW CY AC F0 RS1 RS0 OV F1 P D0h

MCNT0 LSHIFT CSE SCE MAS4 MAS3 MAS2 MAS1 MAS0 D1h

MCNT1 MST MOF SCB CLM — — — — D2h

MA D3h

MB D4h

MC D5h

MCON1* IRAMD PRAME — — PDCE7 PDCE6 PDCE5 PDCE4 D6h

MCON2* WPIF WPR2 WPR1 WPR0 WPE3 WPE2 WPE1 WPE0 D7h

WDCON SMOD_1 POR EPF1 PF1 WDIF WTRF EWT RWT D8h

SADDR2 D9h

BPA1 DAh

BPA2 DBh

BPA3 DCh

ACC E0h

OCAD E1h

CSRD E3h

CSRA E4h

EBS FPE RBF — BS4 BS3 BS2 BS1 BS0 E5h

BCUD E6h

BCUC BUSY EPMF TIF RIF BC3 BC2 BC1 BC0 E7h

EIE* EPMIE C0IE EAIE EWDI EWPI ES2 ET3 EX2-5 E8h

MXAX EAh

DPX2 EBh

DPX3 EDh

OWMAD — — — — — A2 A1 A0 EEh

OWMDR EFh

B F0h

SADEN2 F1h

DPL2 F2h

DPH2 F3h

DPL3 F4h

DPH3 F5h

DPS1 ID3 ID2 — — — — — — F6h

STATUS1 — — — — V1PF V3PF SPTA2 SPRA2 F7h

EIP* EPMIP C0IP EAIP PWDI PWPI PS2 PT3 PX2-5 F8h

P7 F9h

TL3 FBh

TH3 FCh

T3CM TF3 TR3 T3M SMOD_2 GATE C/T3 M1 M0 FDh

SCON2 SM0/FE_2 SM1_2 SM2_2 REN_2 TB8_2 RB8_2 TI_2 RI_2 FEh

SBUF2 FFh

Maxim Integrated

Guide: Network Microcontroller

Special-Function Register Location (continued)

*Bits in this SFR may have different functions depending on the specific device. Consult the SFR description for details.

Supplement

20

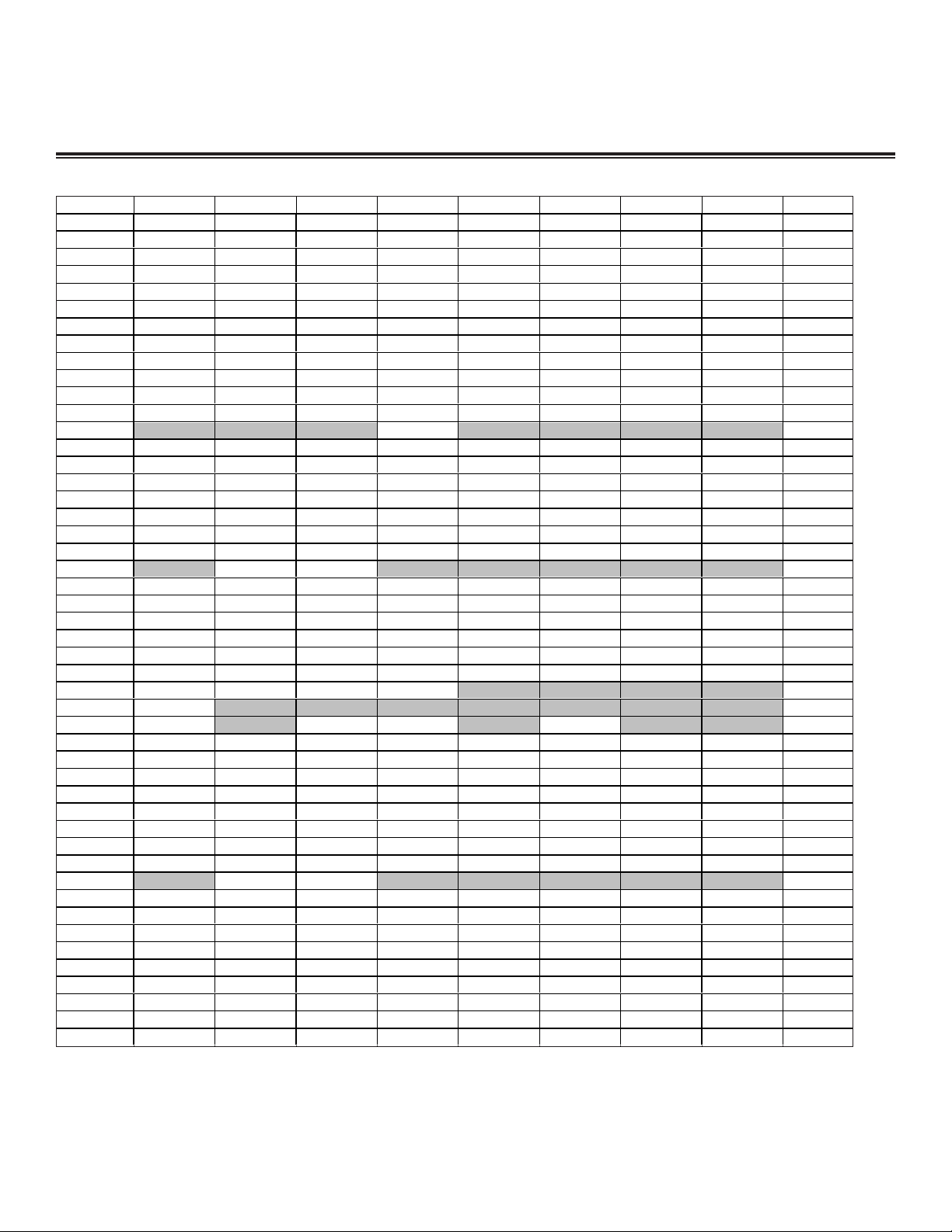

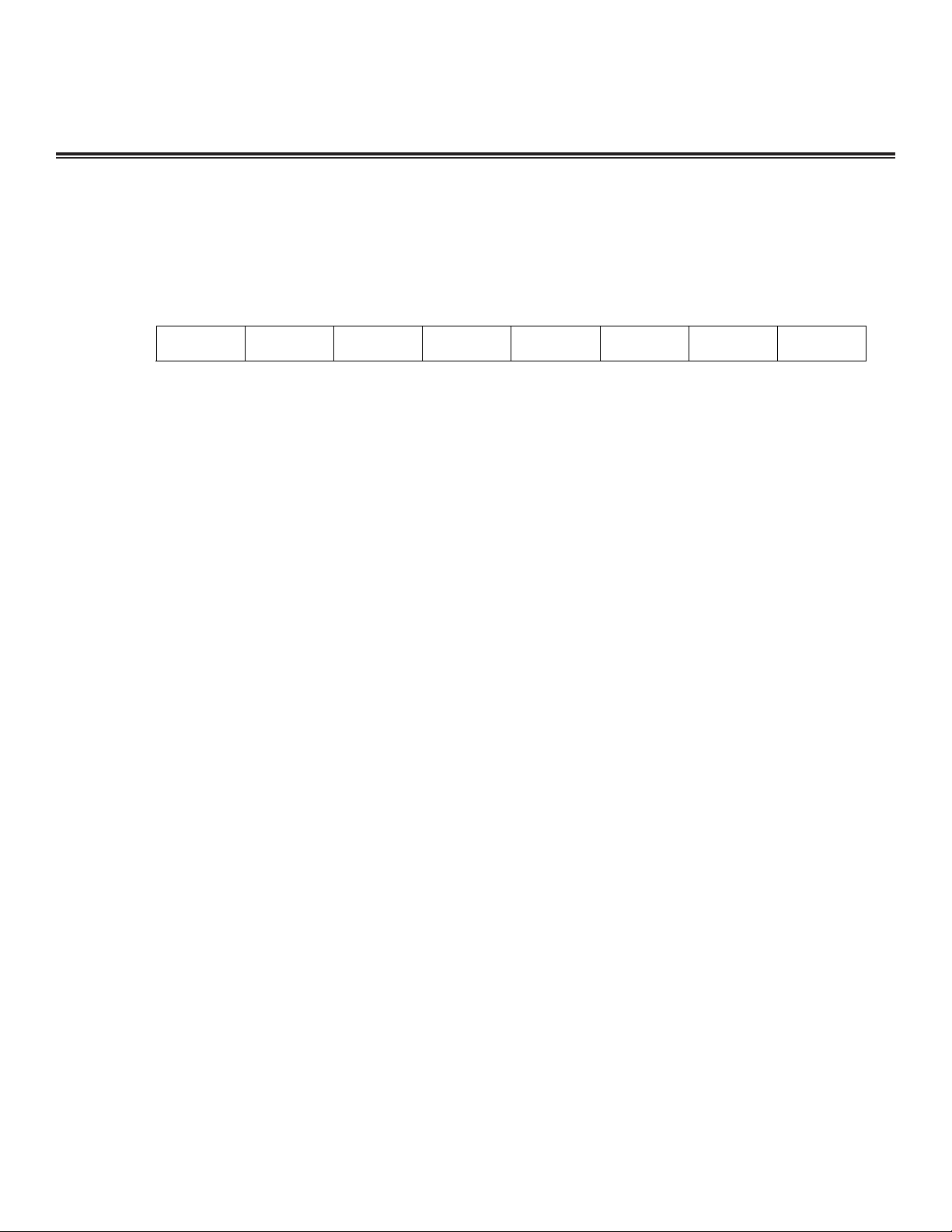

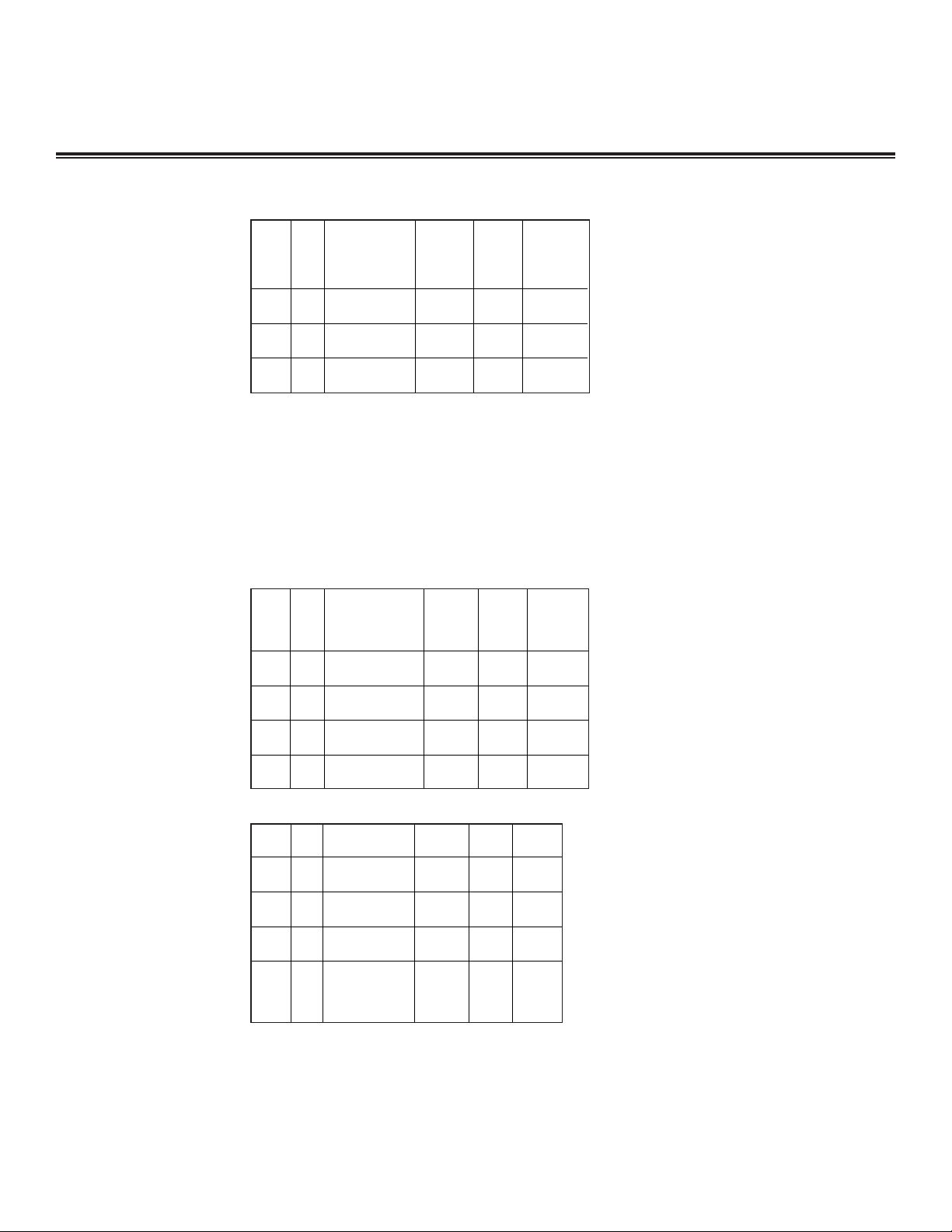

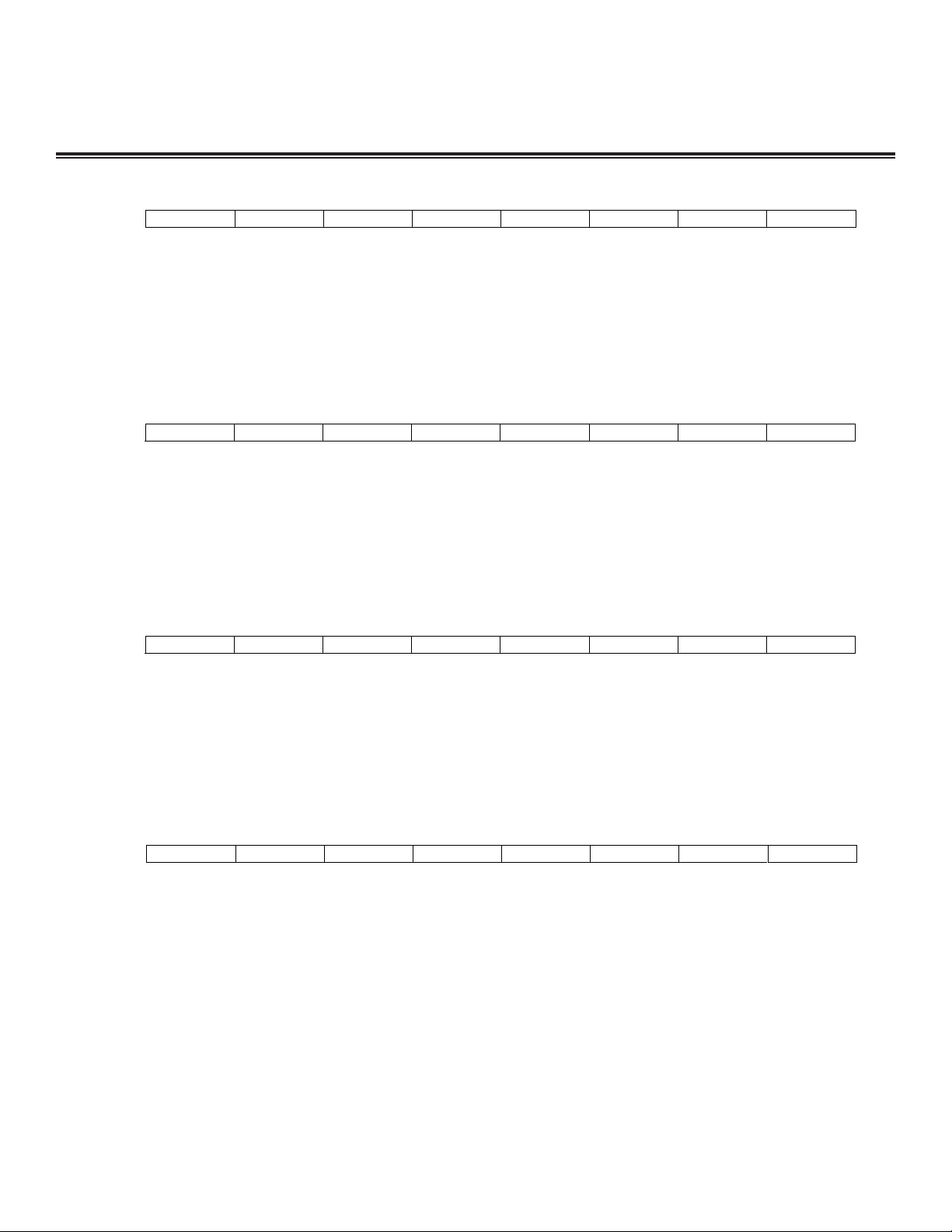

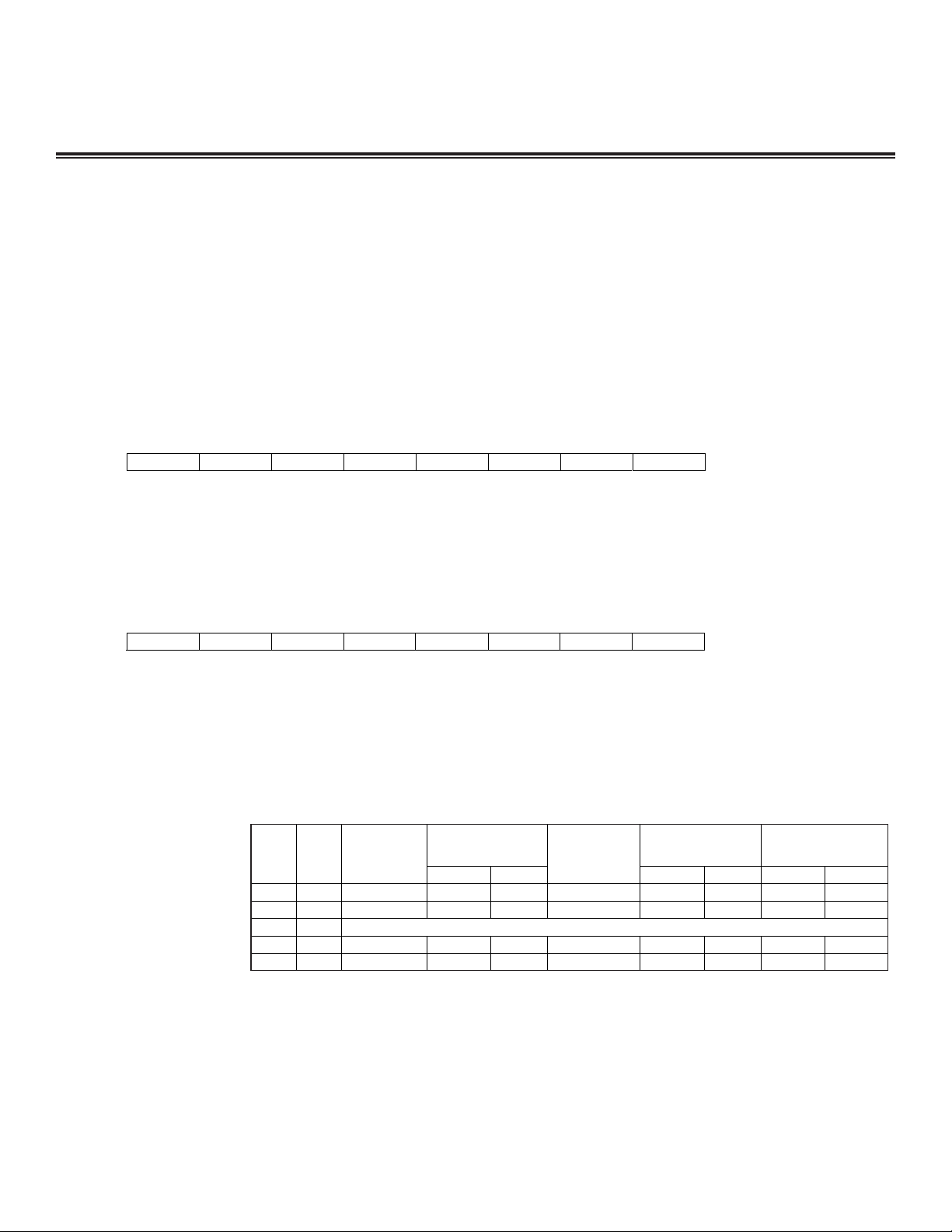

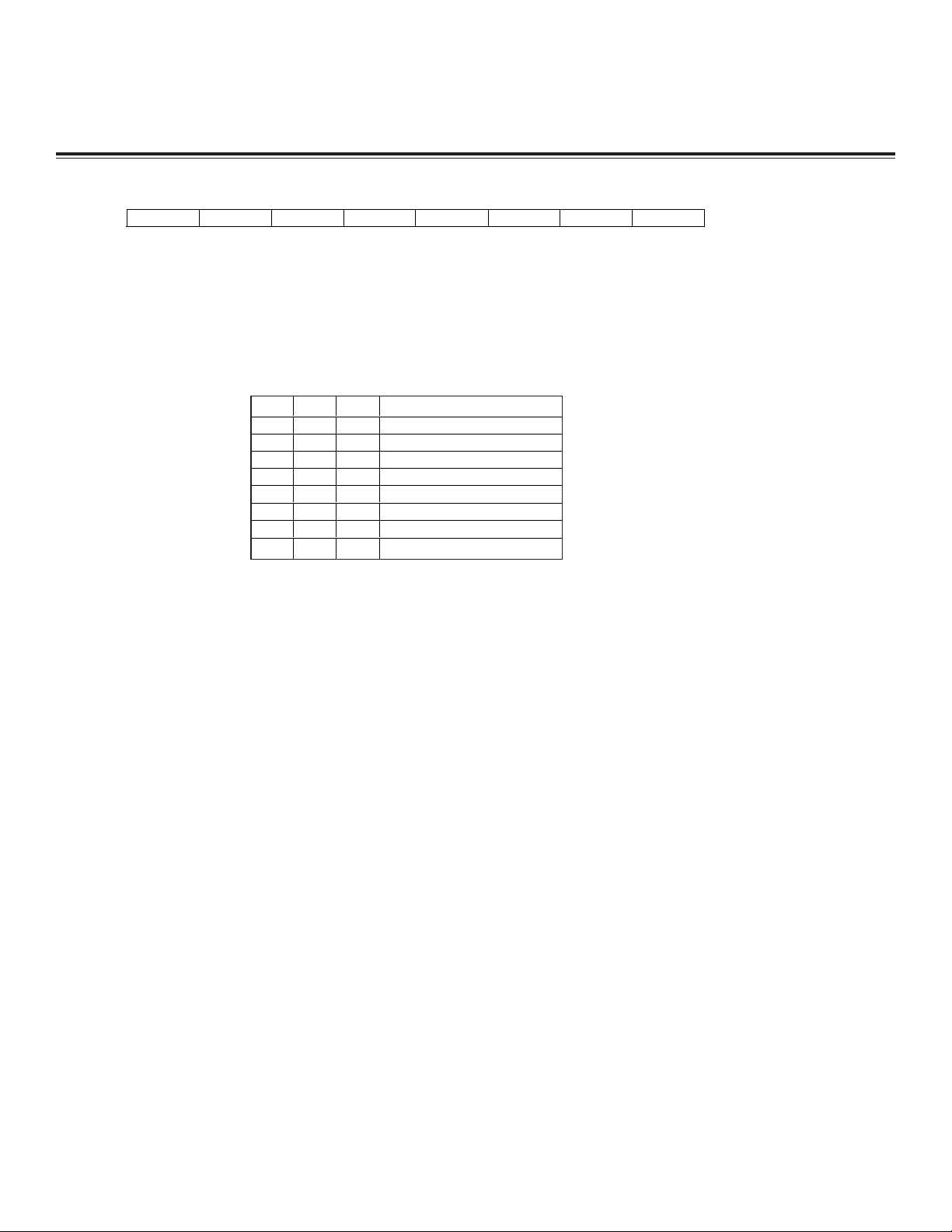

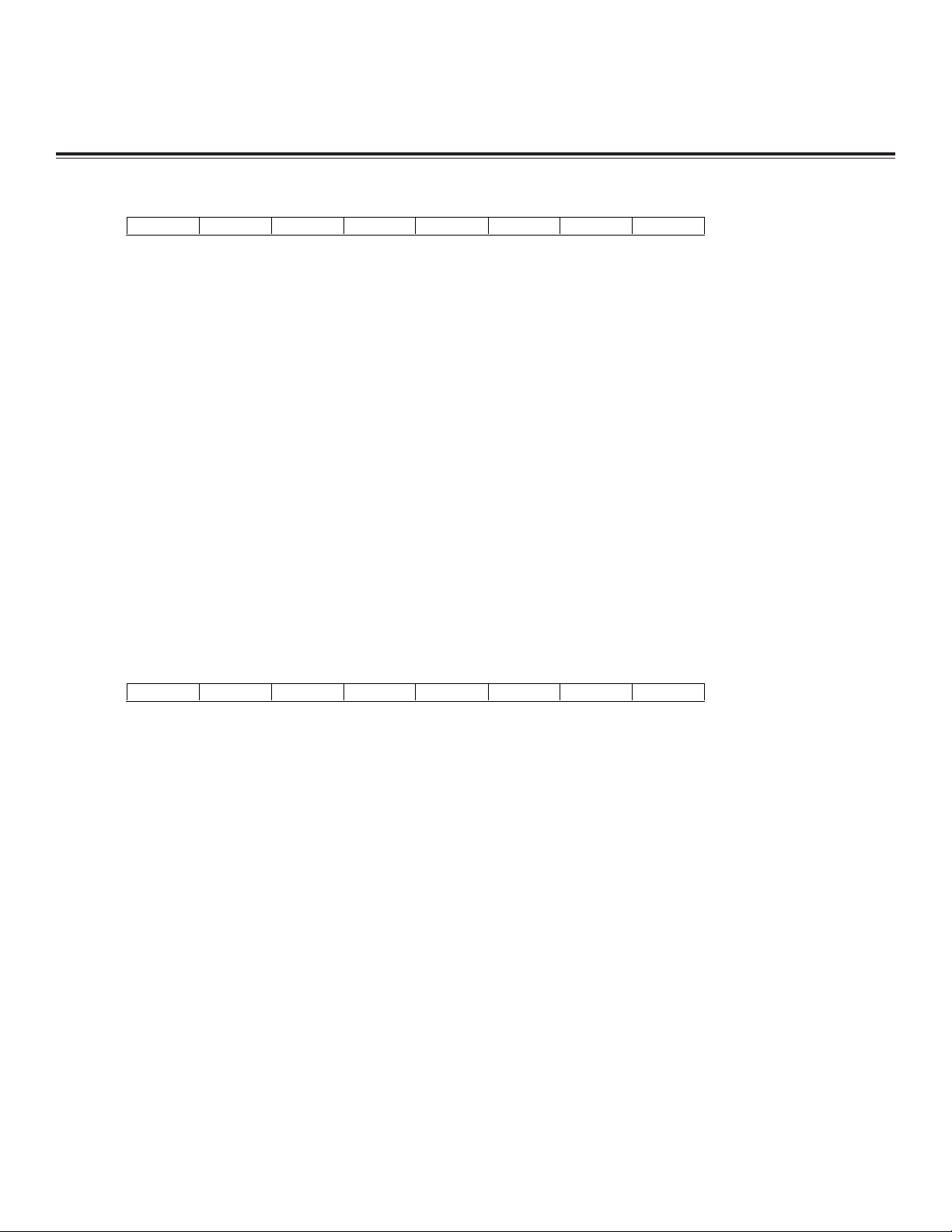

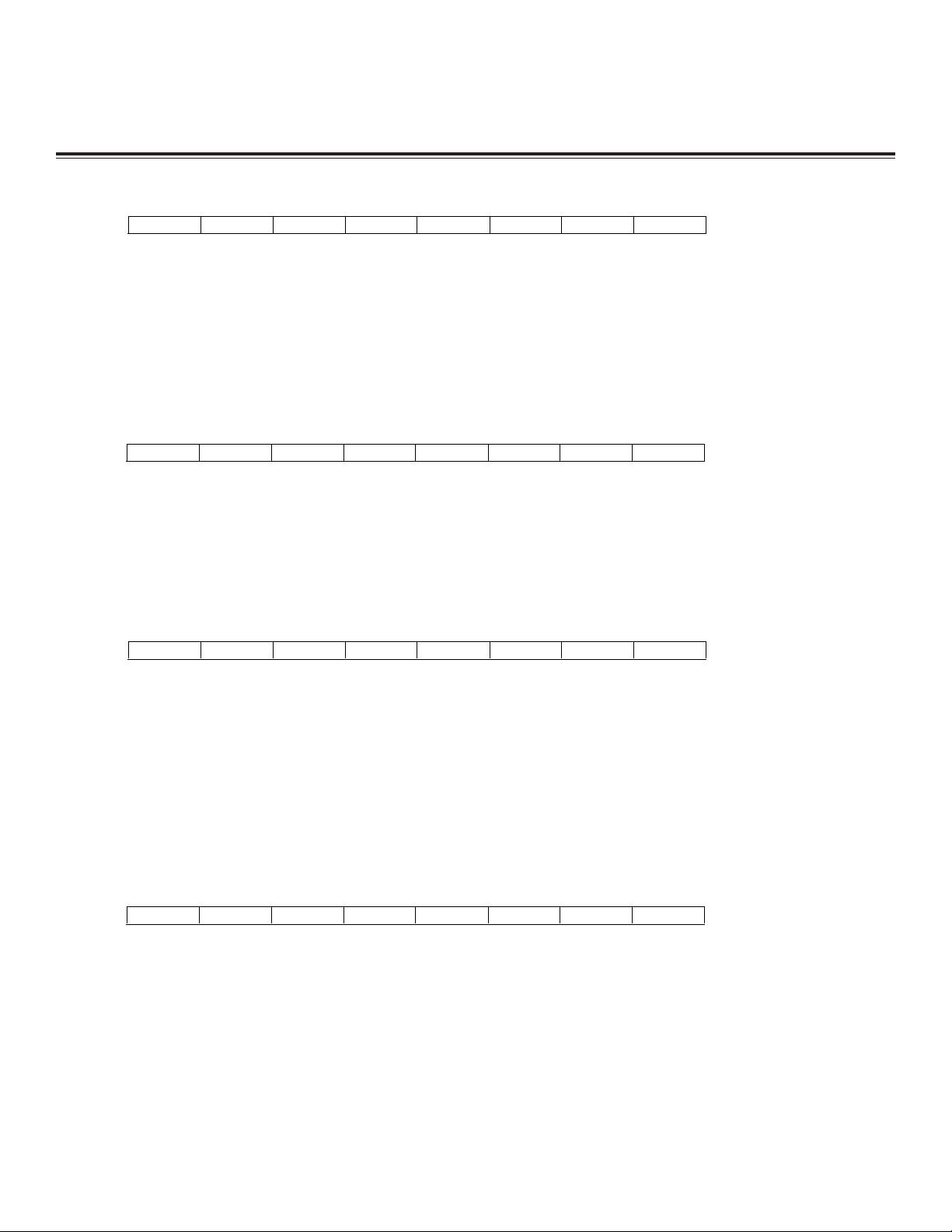

Page 21

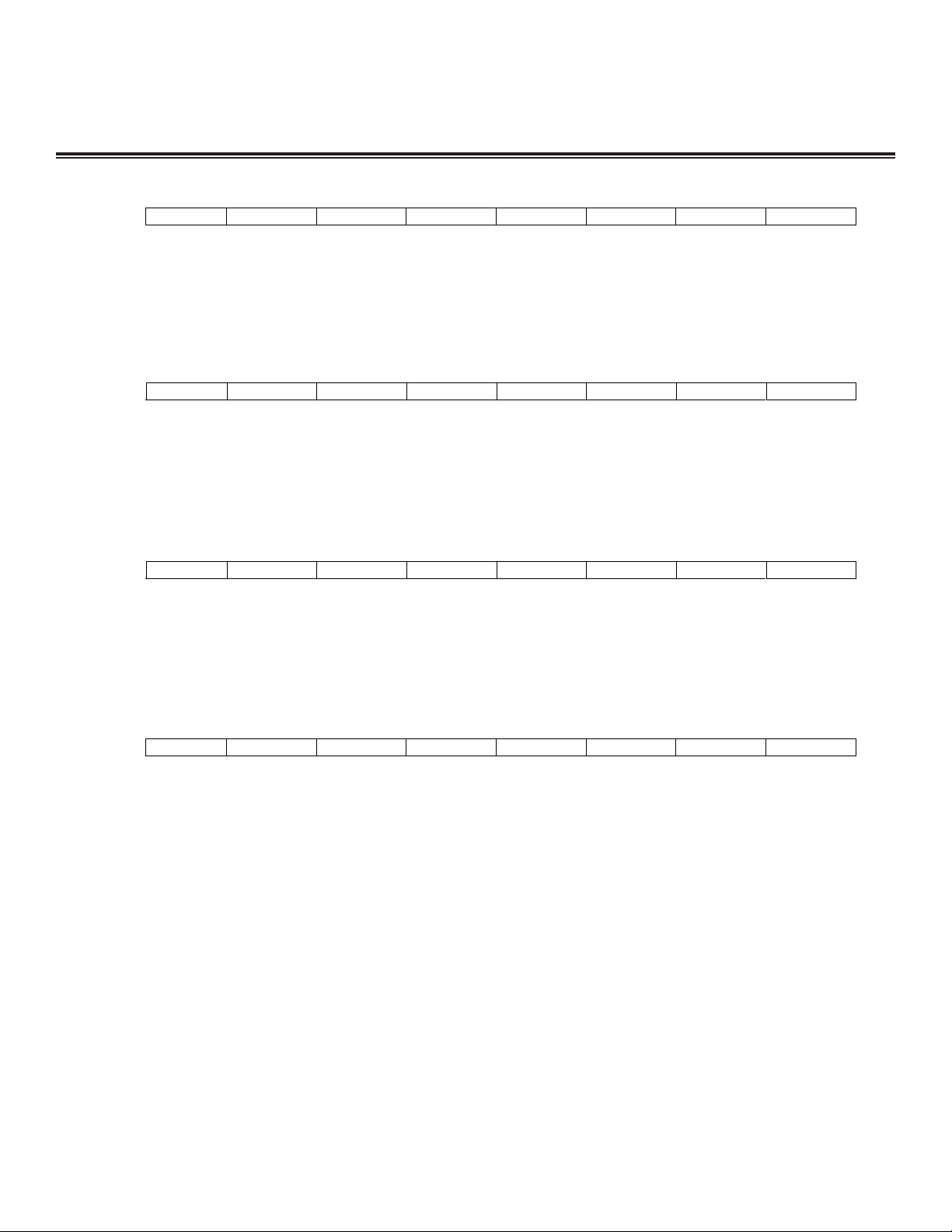

High-Speed Microcontroller User’s

REGISTER

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

ADDRESS

P41111111180h

SP0000011181h

DPL 0 0 0 0 0 0 0 0 82h

DPH 0 0 0 0 0 0 0 0 83h

DPL1 0 0 0 0 0 0 0 0 84h

DPH1 0 0 0 0 0 0 0 0 85h

DPS 0 0 0 0 0 1 0 0 86h

PCON 0 0 SPECIAL 0 0 0 0 0 87h

TCON 0 0 0 0 0 0 0 0 88h

TMOD 0 0 0 0 0 0 0 0 89h

TL0 0 0 0 0 0 0 0 0 8Ah

TL1 0 0 0 0 0 0 0 0 8Bh

TH0 0 0 0 0 0 0 0 0 8Ch

TH1000000008Dh

CKCON 0 0 0 0 0 0 0 1 8Eh

P11111111190h

EXIF 0 0 0 0 SPECIAL SPECIAL SPECIAL 0 91h

P4CNT 1 1 1 1 1 1 1 1 92h

DPX 0 0 0 0 0 0 0 0 93h

DPX1 0 0 0 0 0 0 0 0 95h

C0RMS0* 0 0 0 0 0 0 0 0 96h

C0RMS1* 0 0 0 0 0 0 0 0 97h

SCON0 0 0 0 0 0 0 0 0 98h

SBUF0 0 0 0 0 0 0 0 0 99h

ESP 1 1 1 1 1 1 0 0 9Bh

AP000000009Ch

ACON 1 1 0 0 SPECIAL 0 0 0 9Dh

C0TMA0* 0 0 0 0 0 0 0 0 9Eh

C0TMA1* 0 0 0 0 0 0 0 0 9Fh

P211111111A0h

P511111111A1h

P5CNT* 1 0 0 0 0 0 0 0 A2h

C0C* 0 0 0 0 1 0 0 1 A3h

C0S* 0 0 0 0 0 0 0 0 A4h

C0IR* 0 0 0 0 0 0 0 0 A5h

C0TE* 0 0 0 0 0 0 0 0 A6h

C0RE* 0 0 0 0 0 0 0 0 A7h

IE00000000A8h

SADDR0 0 0 0 0 0 0 0 0 A9h

SADDR1 0 0 0 0 0 0 0 0 AAh

C0M1C* 0 0 0 0 0 0 0 0 ABh

C0M2C* 0 0 0 0 0 0 0 0 ACh

C0M3C* 0 0 0 0 0 0 0 0 ADh

C0M4C* 0 0 0 0 0 0 0 0 AEh

C0M5C* 0 0 0 0 0 0 0 0 AFh

P311111111B0h

P611111111B1h

P6CNT 0 0 0 0 0 0 0 0 B2h

C0M6C* 0 0 0 0 0 0 0 0 B3h

C0M7C* 0 0 0 0 0 0 0 0 B4h

C0M8C* 0 0 0 0 0 0 0 0 B5h

C0M9C* 0 0 0 0 0 0 0 0 B6h

C0M10C* 0 0 0 0 0 0 0 0 B7h

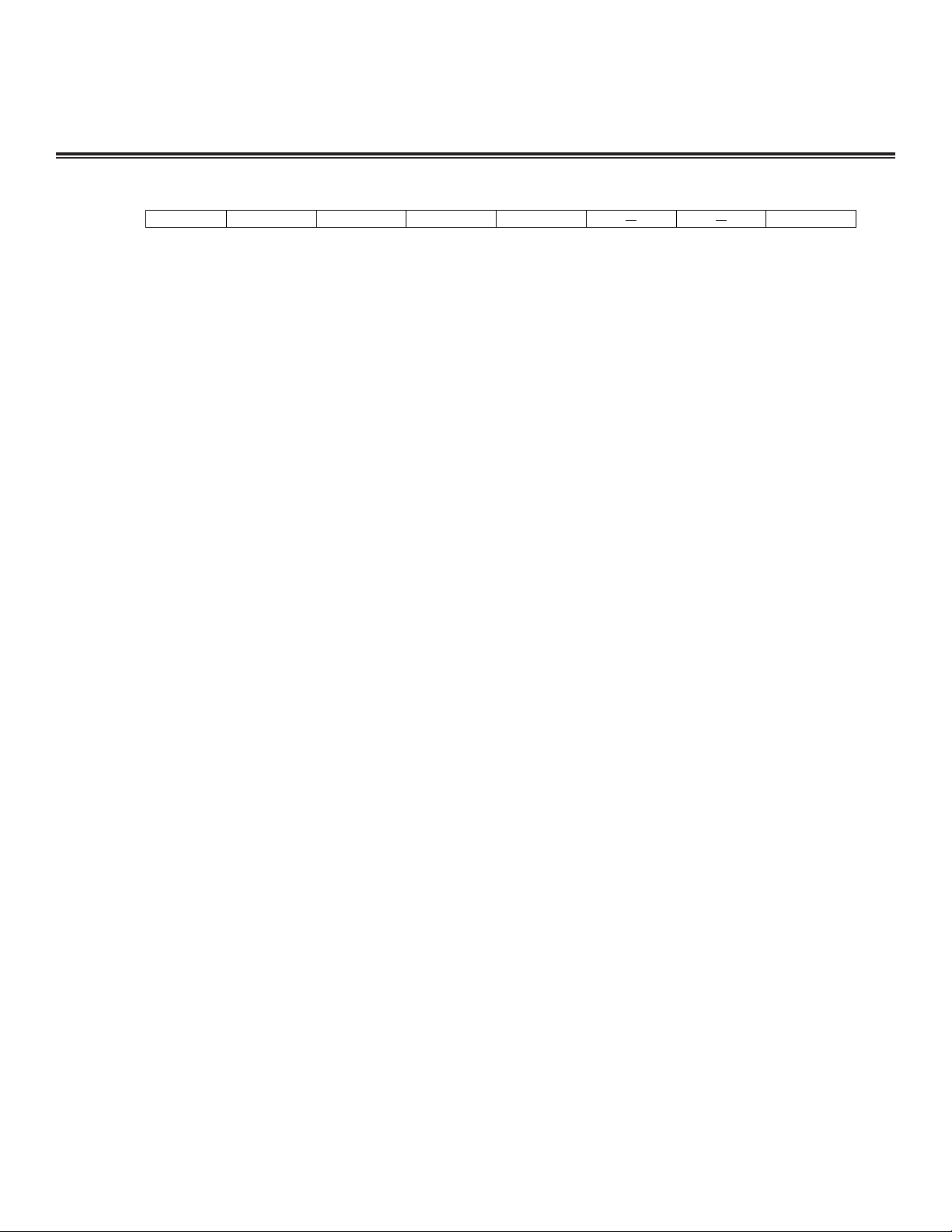

Maxim Integrated

Guide: Network Microcontroller

Supplement