Page 1

71M6531/71M6533/71M6534

Energy Meter IC Family

SOFTWARE USER’S GUIDE

5/8/2008

TERIDIAN Semiconductor Corporation

6440 Oak Canyon Rd., Suite 100

Irvine, CA 92618-5201

Ph: (714) 508-8800 ▪ Fax: (714) 508-8878

Meter.support@teridian.com

http://www.teridian.com/

Page 2

71M653X Software User’s Guide

TERIDIAN Semiconductor Corporation makes no warranty for the use of its products, other than expressly contained in the

Company’s warranty detailed in the TERIDIAN Semiconductor Corporation standard Terms and Conditions. The company assumes

no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed

herein at any time without notice and does not make any commitment to update the information contained herein.

v1.1

TERIDIAN Proprietary 2 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 3

71M653X Software User’s Guide

71M653X

Energy Meter IC FAMILY

SOFTWARE USER’S GUIDE

v1.1 TERIDIAN Proprietary 3 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 4

71M653X Software User’s Guide

Table of Contents

1 INTRODUCTION............................................................................................................................ 11

1.1 Using this Document .............................................................................................................. 11

1.2 Related Documentation ......................................................................................................... 12

1.3 Compatibility Statement ......................................................................................................... 12

2 DESIGN GUIDE ............................................................................................................................. 13

2.1 Hardware Requirements ........................................................................................................ 13

2.2 Software Requirements ......................................................................................................... 13

2.3 Software Architecture ............................................................................................................ 14

2.4 Utilities ..................................................................................................................................... 15

2.4.1 D_MERGE ............................................................................................................................. 15

2.4.2 CE_MERGE ........................................................................................................................... 15

2.4.3 BANK_MERGE ...................................................................................................................... 16

3 DESIGN REFERENCE .................................................................................................................. 17

3.1 Program Memory .................................................................................................................... 17

3.2 Data Memory ........................................................................................................................... 17

3.3 Programming the 71M653X Chips ........................................................................................ 18

3.4 Debugging of the 71M653X Chips ......................................................................................... 18

3.5 Test Tools ................................................................................................................................ 18

3.5.1 Running the 653X_Demo.hex Program.................................................................................. 19

3.5.2 CLI Commands ...................................................................................................................... 20

3.5.3 Command (Macro) Files ......................................................................................................... 20

4 TOOL INSTALLATION GUIDE ..................................................................................................... 21

4.1 Installing the Programs for the ADM51 Emulator ............................................................... 21

4.2 Installing the Wemu Program (Chameleon Debugger) ....................................................... 21

4.3 Installing the ADM51 USB Driver .......................................................................................... 22

4.4 Installing Updates to the Emulator Program and Hardware .............................................. 23

4.5 Creating a Project ................................................................................................................... 24

4.6 Installing the Keil Compiler ................................................................................................... 27

4.7 Creating a Project for the Keil Compiler .............................................................................. 28

4.7.1 Directory Structure ................................................................................................................. 28

4.7.2 Adjusting the Keil Compiler Settings ...................................................................................... 29

4.7.3 Manually Controlling the Keil Compiler Settings ..................................................................... 30

4.8 Output File Format .................................................................................................................. 32

4.8.1 Basic Intel Hex Format ........................................................................................................... 33

4.8.2 Intel Hex386 File Format ........................................................................................................ 34

4.9 Writing Bank-Switched Code ................................................................................................ 35

4.9.1 Hardware Overview ................................................................................................................ 35

4.9.2 Software Overview ................................................................................................................. 35

4.9.3 Software Tool Versions .......................................................................................................... 36

v1.1v1.1 TERIDIAN Proprietary 4 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 5

71M653X Software User’s Guide

4.9.4 Setup of the Compiler Project ................................................................................................ 36

4.9.5 Startup ................................................................................................................................... 37

4.9.6 Bank-Switching Code ............................................................................................................. 37

4.9.7 Page Table Setup and Debug ................................................................................................ 37

4.9.8 Producing a Banked Hex File ................................................................................................. 39

4.9.9 Placing Interrupts in Banked Code ......................................................................................... 39

4.9.10 Calling Banked Functions via Function Pointers .................................................................... 39

4.9.11 Putting Constants in Banks .................................................................................................... 40

4.9.12 Write-Protecting Flash in the 653X ......................................................................................... 40

4.10 Project Management Tools .................................................................................................... 41

4.11 Alternative Compilers ............................................................................................................. 41

4.12 Alternative Editors .................................................................................................................. 41

4.13 Alternative Linkers ................................................................................................................. 42

5 Demo Code Description .............................................................................................................. 43

5.1 80515 Data Types and Compiler-Specific Information ....................................................... 43

5.1.1 Data Types ............................................................................................................................. 43

5.1.2 Compiler-Specific Information ................................................................................................ 46

5.2 Demo Code Options and Program Size................................................................................ 47

5.3 Program Flow .......................................................................................................................... 51

5.3.1 Startup and Initialization ......................................................................................................... 52

5.4 Basic Code Architecture ........................................................................................................ 52

5.4.1 Initialization ............................................................................................................................ 53

5.4.2 Interrupts ................................................................................................................................ 53

5.4.2.1 Pulse Counting Interrupts ................................................................................................ 54

5.4.2.2 FWCOL0 and FWCOL1 ................................................................................................... 55

5.4.2.3 CE_BUSY Interrupt .......................................................................................................... 55

5.4.2.4 PLL_ISR ........................................................................................................................... 55

5.4.2.5 EEPROM Isr ..................................................................................................................... 56

5.4.2.6 Timer Interrupt .................................................................................................................. 56

5.4.2.7 The XFER_BUSY, RTC and NEAR_OVERFLOW Interrupt ............................................ 56

5.4.2.8 SERIAL Interrupt .............................................................................................................. 57

5.4.3 Background Tasks ................................................................................................................. 57

5.4.3.1 meter_run() ...................................................................................................................... 57

5.4.3.2 Command Line Interpreter (CLI) ...................................................................................... 58

5.4.3.3 Auto-Calibration ............................................................................................................... 58

5.4.3.4 EEPROM Read/Write ...................................................................................................... 61

5.4.3.5 Battery Test ...................................................................................................................... 61

5.4.3.6 Power Factor Measurement............................................................................................. 61

5.4.4 Watchdog Timer ..................................................................................................................... 62

5.4.5 Real-Time Clock (RTC) .......................................................................................................... 62

5.5 Managing Mission and Battery Modes ................................................................................. 62

5.6 Data Flow ................................................................................................................................. 63

5.7 CE/MPU Interface .................................................................................................................... 64

v1.1v1.1 TERIDIAN Proprietary 5 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 6

71M653X Software User’s Guide

5.8 Boot Loader ............................................................................................................................. 64

5.9 Source Files ............................................................................................................................ 6 4

5.10 Auxiliary Files.......................................................................................................................... 66

5.11 Include/Header Files ............................................................................................................... 66

5.11.1 OPTIONS.H ........................................................................................................................... 66

5.11.2 Register Definitions ................................................................................................................ 67

5.11.3 Other Include/Header Files .................................................................................................... 67

5.12 CE Image Files ........................................................................................................................ 68

5.13 Common MPU Addresses ...................................................................................................... 69

5.14 Firmware Application Information ........................................................................................ 77

5.14.1 General Design Considerations ............................................................................................. 77

5.14.1.1 Multitasking ................................................................................................................... 77

5.14.1.2 Synchronization ............................................................................................................ 77

5.14.1.3 Bank Switching ............................................................................................................. 77

5.14.1.4 Economic Usage of RAM.............................................................................................. 78

5.14.1.5 Trading Space for Speed .............................................................................................. 78

5.14.1.6 Object-Oriented Design ................................................................................................ 78

5.14.1.7 Reconfiguring “Glue Logic” ........................................................................................... 79

5.14.1.8 DSP Operations ............................................................................................................ 79

5.14.1.9 Coping with Various Current Sensors .......................................................................... 79

5.14.1.10User Interface ............................................................................................................... 79

5.14.1.11Operating without User Interface .................................................................................. 79

5.14.1.12Communication with a Computer ................................................................................. 79

5.14.1.13Support of Automatic Meter Reading ........................................................................... 79

5.14.1.14Communication between MPU and CE ........................................................................ 80

5.14.1.15Timing Control .............................................................................................................. 80

5.14.1.166531: Calculation of max(VA*IA, VA*IB) Option, Equation 0 ....................................... 80

5.14.1.176534: Calculation of VA*IA+VB*IB+VC*IC Option, Equation 5 .................................... 81

5.14.1.18How Register Data is Stored ........................................................................................ 82

5.14.1.19Managing Power Failures ............................................................................................. 83

5.14.1.20Pulse Counting ............................................................................................................. 83

5.14.1.21Battery Modes ............................................................................................................... 83

5.14.1.22Real-Time Performance................................................................................................ 83

5.14.2 Firmware Application: Selected Tasks ................................................................................... 84

5.14.2.1 Sag Detection ............................................................................................................... 84

5.14.2.2 Temperature Measurement .......................................................................................... 84

5.14.2.3 Temperature Compensation for Measurements ........................................................... 85

5.14.2.4 Temperature Compensation for the RTC ..................................................................... 85

5.14.2.5 Validating the Battery .................................................................................................... 86

5.15 Alphabetical Function Reference .......................................................................................... 87

5.16 Errata ........................................................................................................................................ 98

5.17 Porting 71M6511/6513 Code to the 71M653x ....................................................................... 99

v1.1v1.1 TERIDIAN Proprietary 6 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 7

71M653X Software User’s Guide

5.17.1 Flash Use ............................................................................................................................... 99

5.17.2 Extra RAM .............................................................................................................................. 99

5.17.3 CE Data Location is at XDATA 0x0000 .................................................................................. 99

5.17.4 CE Data Access is Transparent to the MPU .......................................................................... 99

5.17.5 Read-only areas in MPU RAM ............................................................................................... 99

5.17.6 CE Code Location .................................................................................................................. 99

5.17.7 CE Causes Flash Write-Protection ......................................................................................... 99

5.17.8 Watchdog Location .............................................................................................................. 100

5.17.9 Software Watchdog Now Deprecated .................................................................................. 100

5.17.10 Real Time Clock Compensation ........................................................................................... 100

5.17.11 Battery Modes ...................................................................................................................... 100

5.18 Porting 71M6521 Code to the 71M653x .............................................................................. 101

5.18.1 Flash Use ............................................................................................................................. 101

5.18.2 Extra RAM ............................................................................................................................ 101

5.18.3 CE Data Location is at XDATA 0x0000 ................................................................................ 102

5.18.4 CE Data Access is Transparent to the MPU ........................................................................ 102

5.18.5 Read-only areas in MPU RAM ............................................................................................. 102

5.18.6 CE Code Location ................................................................................................................ 102

5.18.7 CE Causes Flash Write-Protection ....................................................................................... 102

5.18.8 Watchdog Location .............................................................................................................. 102

5.18.9 Software Watchdog Now Deprecated .................................................................................. 102

5.18.10 Real Time Clock Compensation ........................................................................................... 103

5.18.11 Battery Modes ...................................................................................................................... 103

5.18.12 Watchdog Reset .................................................................................................................. 103

5.18.13 Temperature Compensation ................................................................................................ 103

6 80515 MPU REFERENCE ........................................................................................................... 105

6.1 The 80515 Instruction Set .................................................................................................... 105

6.1.1 Instructions Ordered by Function ......................................................................................... 106

6.1.2 Instructions Ordered by Opcode (Hexadecimal) .................................................................. 110

6.1.3 Instructions that Affect Flags ................................................................................................ 113

7 Appendix ..................................................................................................................................... 115

7.1 Acronyms .............................................................................................................................. 115

7.2 Revision History ................................................................................................................... 116

v1.1v1.1 TERIDIAN Proprietary 7 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 8

71M653X Software User’s Guide

List of Figures

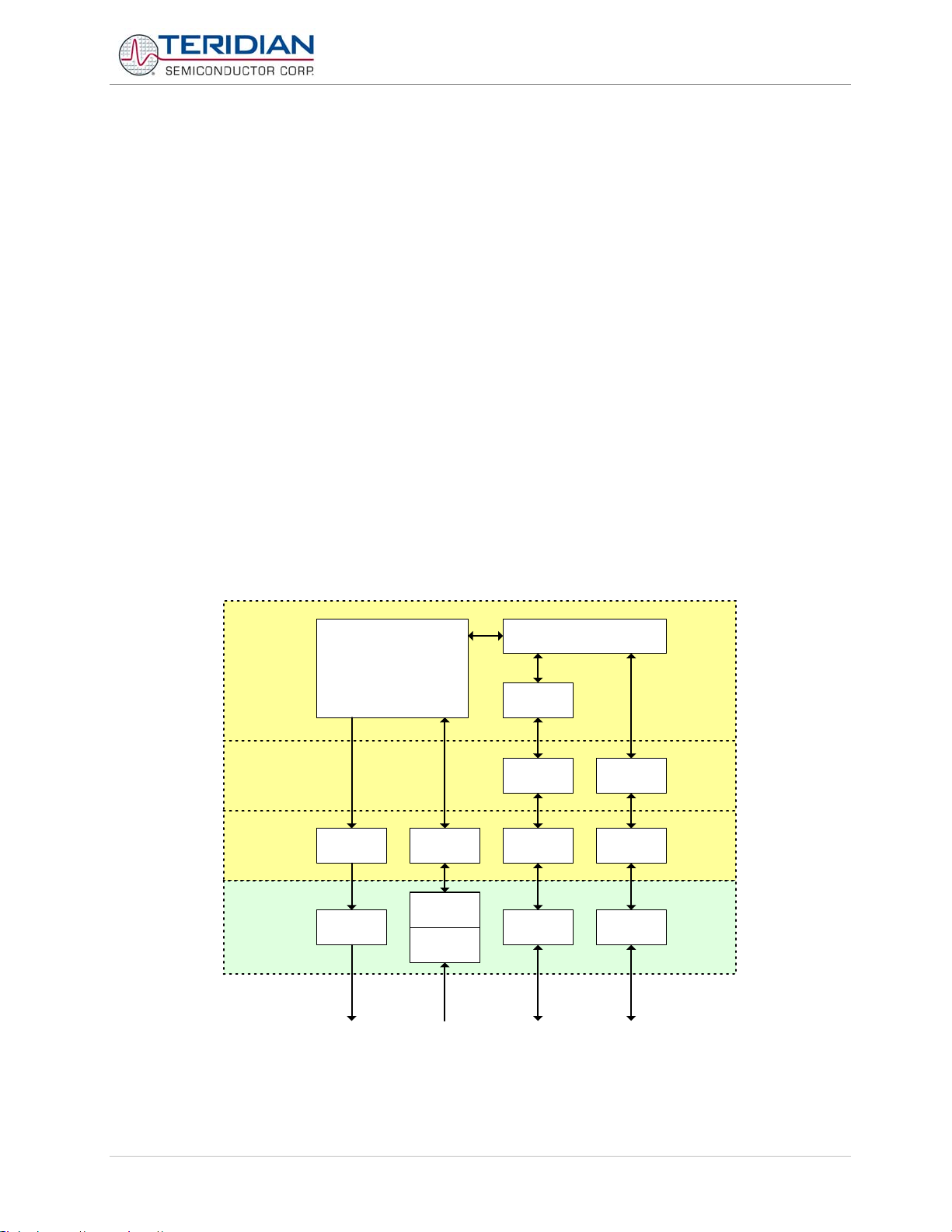

Figure 2-1: Software Structure ....................................................................................................................................... 14

Figure 3-1: Port Speed and Handshake Setup ............................................................................................................... 19

Figure 4-1, Setup of Keil Compiler for bank-switched code ............................................................................................ 36

Figure 4-2, Selecting a Bank for a File Group in Keil C .................................................................................................. 37

Figure 4-3, Setting Keil’s Linker for Bank-switched Code ............................................................................................... 38

Figure 5-1: Sag and Dip Conditions ............................................................................................................................... 84

Figure 5-2: Sag Event .................................................................................................................................................... 84

Figure 5-3: Crystal Frequency over Temperature........................................................................................................... 85

Figure 5-4: Crystal Compensation .................................................................................................................................. 86

Figure 5-5, State Diagram of Operating Modes ............................................................................................................ 101

List of Tables

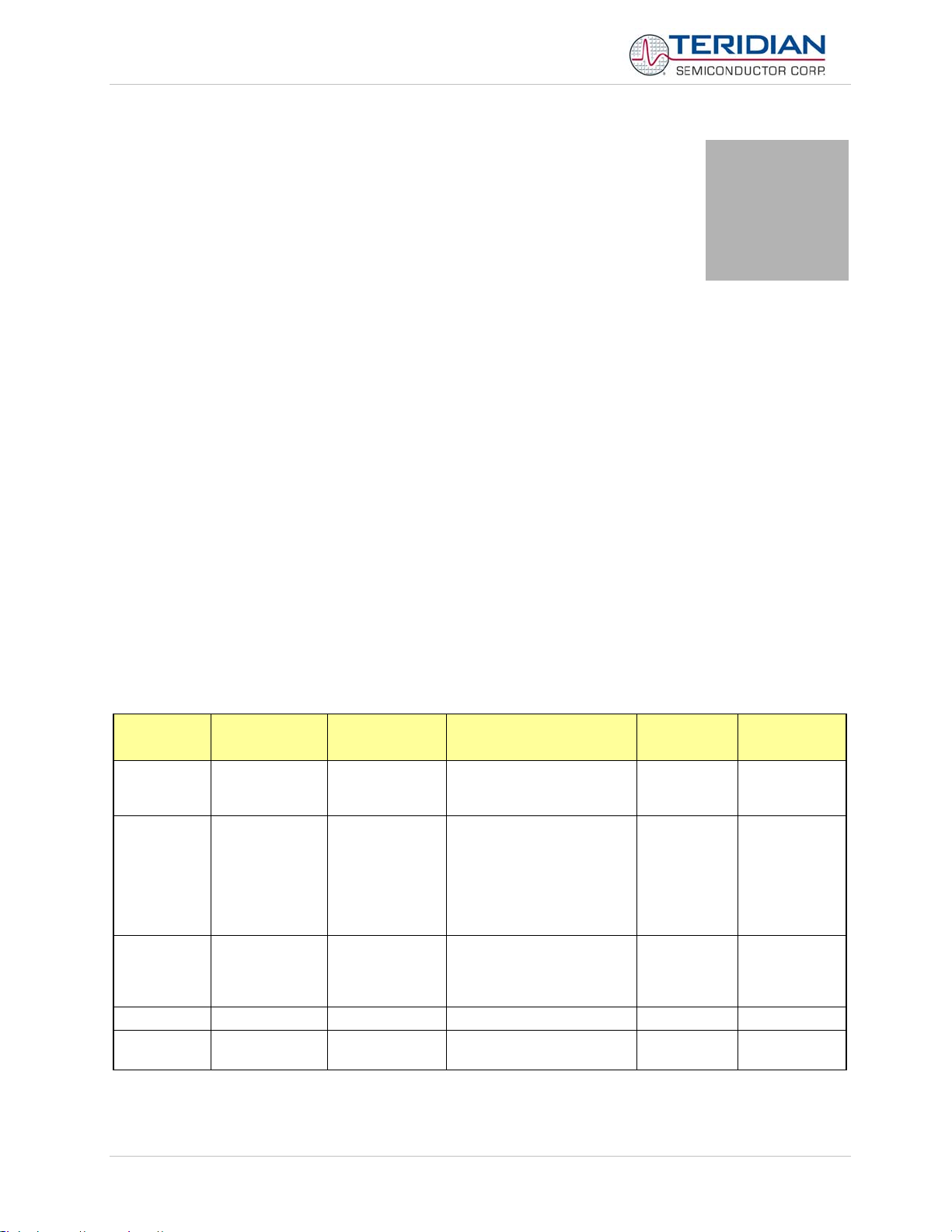

Table 3-1: Memory Map ................................................................................................................................................. 17

Table 4-1: Code Bank Memory Addresses and Availability ............................................................................................ 35

Table 5-1: Internal Data Memory Map ............................................................................................................................ 43

Table 5-2: Internal Data Types ....................................................................................................................................... 46

Table 5-3: Demo Code Versions .................................................................................................................................... 47

Table 5-4: Current Sensing Options ............................................................................................................................... 47

Table 5-5: Compensation Features ................................................................................................................................ 48

Table 5-6: Power Registers and Pulse Output Features ................................................................................................ 49

Table 5-7: Creep Functions ............................................................................................................................................ 50

Table 5-8: Operating Modes ........................................................................................................................................... 50

Table 5-9: Calibration and Various Services .................................................................................................................. 51

Table 5-10: Interrupt Service Routines ........................................................................................................................... 53

Table 5-11: Interrupt Priority Assignment ....................................................................................................................... 54

Table 5-12: MPU Memory Locations .............................................................................................................................. 74

Table 5-13: MPU Status Bits .......................................................................................................................................... 76

Table 5-14: Frequency over Temperature ...................................................................................................................... 85

Table 6-7: Notes on Data Addressing Modes ............................................................................................................... 105

Table 6-8: Notes on Program Addressing Modes ........................................................................................................ 105

Table 6-9: Arithmetic Operations .................................................................................................................................. 106

Table 6-10: Logic Operations ....................................................................................................................................... 107

Table 6-11: Data Transfer Operations .......................................................................................................................... 108

Table 6-12: Program Branches .................................................................................................................................... 109

Table 6-13: Boolean Manipulations .............................................................................................................................. 109

Table 6-14: Instruction Set in Hexadecimal Order ........................................................................................................ 110

Table 6-15: Instruction Set in Hexadecimal Order ........................................................................................................ 111

Table 6-16: Instruction Set in Hexadecimal Order ........................................................................................................ 112

Table 6-17: Instructions Affecting Flags ....................................................................................................................... 113

v1.1v1.1 TERIDIAN Proprietary 8 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 9

71M653X Software User’s Guide

LIMITED USE LICENSE AGREEMENT

Acceptance

(“Licensed Software”) and provided by TERIDIAN Semiconductor Corporation (“TSC”), the recipient of the software

(“Licensee”) accepts, and agrees to be bound by the terms and conditions hereof.

Acknowledgment

TSC’s meter products: 71M6531, 71M6534, and 71M653xB. Licensee acknowledges that the Licensed Software was

not designed for use with, nor has it been checked for performance with, any other devices.

Title

: Title to the Licensed Software and related documentation remains with TSC and its licensors. Nothing contained

in this Agreement shall be construed as transferring any right, title, or interest in the Licensed Software to Licensee

except as expressly set forth herein. TSC expressly disclaims liability for any patent infringement claims based upon

use of the Licensed Software either solely or in conjunction with third party software or hardware.

Licensee shall not make nor to permit the making of copies of the Licensed Software (including its documentation)

except as authorized by this License Agreement or otherwise authorized in writing by TSC. Licensee further agrees not

to engage in, nor to permit the recompilation, disassembly, or other reverse engineering of the Licensed Software.

License Grant

ferable license to use the software solely in conjunction with the meter devices manufactured and sold by TSC.

Non-disclosure and confidentiality

Licensed Software and related documentation and information received by Licensee from TSC. All Confidential

Information shall be maintained in confidence by Licensee and shall not be disclosed to any third party and shall be

protected with the same degree of care as the Licensee normally uses in the protection of its own confidential

information, but in no case with any less degree than reasonable care. Licensee further agrees not to use any

Confidential Information received from TSC except as contemplated by the license granted herein.

Disclaimer of Warranty

Software, including any implied warranty of title, no infringement, merchantability, or fitness for a particular purpose,

regardless of whether TSC knows or has reason to know Licensee’s particular needs. TSC does not warrant that the

functions of the Licensed Software will be free from error or will meet Licensee’s requirements. TSC shall have no

responsibility or liability for errors or product malfunction resulting from Licensee’s use and/or modification of the

Licensed Software.

Limitation of Damages/Liability

LICENSEE FOR INDIRECT, INCIDENTAL, SPECIAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH,

OR ARISING OUT OF, THIS LICENSE AGREEMENT OR USE OF THE LICENSED SOFTWARE.

Export: Licensee shall adhere to the U.S. Export Administration Laws and Regulations (“EAR”) and shall not export or

re-export any technical data or products received from TSC or the direct product of such technical data to any

proscribed country listed in the EAR unless properly authorized by the U.S. Government.

Termination

material breach within thirty (30) days from receipt of notice from TSC. Upon termination, Licensee shall return or, at

TSC’s option certify destruction of, all copies of the Licensed Software in its possession.

Law: This Agreement shall be construed in accordance with the laws of the State of California. The Courts located in

Orange County, CA shall have exclusive jurisdiction over any legal action between TSC and Licensee arising out of this

License Agreement.

Integration: This License Agreement constitutes the entire agreement of the parties as to the subject matter hereof.

No modification of the terms hereof shall be binding unless approved in writing by TSC.

: By using the Application Programming Interface and / or other software described in this document

: The Licensed Software has been developed for use specifically and exclusively in conjunction with

: TSC grants Licensee a limited, non-exclusive, non-sub licensable, non-assignable and non-trans-

: For the purpose of this Agreement, “Confidential Information” shall mean the

: TSC makes no representations or warranties, express or implied, regarding the Licensed

: IN NO EVENT WILL TSC NOR ITS VENDORS OR AGENTS BE LIABLE TO

: TSC shall have the right to terminate the license granted herein in the event Licensee fails to cure any

v1.1v1.1 TERIDIAN Proprietary 9 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 10

71M653X Software User’s Guide

v1.1v1.1 TERIDIAN Proprietary 10 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 11

71M653X Software User’s Guide

1

1 INTRODUCTION

TERIDIAN Semiconductor Corporation’s (TSC) 71M653X single chip Energy Meter Controllers are a family of Systemson-Chip that supports all the functionalities required to build energy meters. Demo Boards are available for each chip

(71M6531, 71M6532, 71M6533, 71M6534) to allow development of embedded applications, in conjunction with an InCircuit Emulator.

Development of a 71M653X application can be started in either 80515 assembly language, or preferably in C using the

Demo Boards. TSC provides, along with the 71M653X Demo Boards, a development toolkit that includes a

demonstration program (“Demo Code”) written in ANSI C that controls all features present on the Demo Boards. This

Demo Code includes functions to manage the low level 80515 core such as memory, clock, power modes, interrupts;

and high level functions such as the LCD, Real Time Clock, Serial interfaces and I/Os. The use of Demo Code portions

will help reduce development time dramatically, since they allow the developer to focus on developing the application

without dealing with the low-level layer such as hardware control, timing, etc. This document describes the different

software layers and how to use them.

The Demo Code should allow customers to evaluate various resources of the 653X ICs but should not be

regarded as production code. The Demo Code and all its components, with the exception of the CE code, are

only example code and the use of it is “as is” and without implied guarantees. Customers may use the Demo

Code as a starting point at any given released revision level but should keep themselves informed about

subsequent revisions of the Demo Code. Demo Code revisions may not be directly compatible with previously

released revisions and/or embedded software used by customers. Custo mers need to ad apt the Demo Code or

other example code supplied by TERIDIAN Application Engineering to their own code base, and in this context

TERIDIAN Semiconductor can only provide indirect assistance and support.

This Software User’s Guide provides information on the following separate subjects:

• General software architecture and minimum requirements (Design Guide)

• Memory model, programming, test tools (Design Reference)

• Demo code structure, data flow, functions (Demo Code Description)

• Installing and using the EEP, compiler, ICE (Tool Installation Guide)

• Understanding and using the 80515 micro controller (80515 Reference)

1.1 USING THIS DOCUMENT

The reader should have a basic familiarity with microprocessors, particularly the 80515 architecture, firmware, software

development and power meter applications. Prior experience with, or knowledge of, the applicable ANSI and/or IEC

standards will also be helpful.

This document presents the features included in the 71M653X Demo Boards in terms of software and some hardware.

To get the most out of this document, the reader should also have available other 71M653X publications such as the

71M653X Demo Board User’s Manual, respective data-sheets, errata list and application notes for additional details

and recent developments.

v1.1v1.1 TERIDIAN Proprietary 11 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 12

71M653X Software User’s Guide

1.2 RELATED DOCUMENTATION

Please refer to the following documents for further information:

• 71M653X Demo Board User’s Manual for the IC of interest

• 71M653X Data Sheet for the IC of interest.

• Signum Systems ADM-51 In-Circuit Emulator Manual (Software Version 3.11.4 or later)

• Keil Compiler Manual (Version 7.5 or later)

• μVision2 (Version 2.20a or later) Manual

TERIDIAN’s web site (http://www.teridian.com

helpful information.

Questions to TERIDIAN Applications Engineering can be directed via e-mail to the address:

• meter.support@teridian.com

) should be frequently checked for updates, application notes and other

1.3 COMPATIBILITY STATEMENT

Information presented in this manual applies to the following hardware and software revisions:

• 71M6531 and 71M6534 Demo Code Revision 4.4.15

• 71M6531 and Demo Board D6531N12A1 (68-pin QFN) Revision 1.0 or later

• 71M6534 Demo Board D6534T4A1 (120-pin LQFP) Revision 1.0 or later

• Signum Systems Wemu51 Software 4.4.11 (8/15/2007) or later

• Signum Systems ADM51 firmware version 4.4.11 (2007/07/15) or later

The revision 4.15 of the Demo Board Code is the basis for all discussed sources, commands, register

addresses and so forth. If applicable, known issues with revision 4.15 are disclosed within the code

description, and workarounds or improvements are shown.

v1.1v1.1 TERIDIAN Proprietary 12 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 13

71M653X Software User’s Guide

2

2 DESIGN GUIDE

This section provides designers with some basic guidance in developing power meter applications utilizing the TSC

71M653X devices. There are two types of applications that can be developed:

• Embedded application using the sources provided by TERIDIAN, or

• Embedded application using only customer generated functions.

2.1 HARDWARE REQUIREMENTS

The following are the minimum hardware requirements for developing custom programs:

• TERIDIAN 71M6531 Demo Board. This board interfaces with a PC via the RS232 serial interface (COM

port).

• AC Adaptor (AC/DC output) or variable power supply.

• PC Pentium with 512MB RAM and 10GB hard drive, 1 COM port and 1 USB port, running either Windows

2000, or Windows ME or Windows XP.

• Signum Systems ADM-51 In-Circuit Emulator (for loading and debugging the embedded application) and

its associated cables. Signum references this device as ADM-51.

2.2 SOFTWARE REQUIREMENTS

The following are the minimum software requirements for embedded application programming:

• Keil Compiler version 8.03a or later.

• μVision2 version 3.33 (Note: this version comes with Keil Compiler version 8.03a).

• Signum Systems software Wemu51 (comes with Signum Systems ADM-51 ICE hardware).

The following software tools/programs are included in the 71M653X development kit and should be present on the

development PC:

• Demo Code with Command Line Interface (CLI) - Used to interface directly to metering functions and to

the chip hardware.

• Source files

• Demo Code object file (hex file).

v1.1v1.1 TERIDIAN Proprietary 13 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 14

71M653X Software User’s Guide

In order to generate and test software, the Keil compiler and the Signum in-circuit emulator (ICE) must be installed per

the instructions in section 4. The include files and header files must also be present on the development PC. Typically,

a design session consists of the following steps:

• Editing C source code using µVision2

• Compiling the source code using the Keil compiler

• Modifying the source code and recompiling until all compiler error messages are resolved

• Using the assembler and linker to generate executable code

• Downloading the executable code to the ICE

• Executing the code and watching its effects on the target

2.3 SOFTWARE ARCHITECTURE

The 71M653X software architecture is partitioned into three separate layers:

1. The lowest level is the device or hardware layer, i.e. the layer that directly communicates with the discrete

functional blocks of the chip and the peripheral components (“hardware”), such as serial interfaces, AFE, LCD

etc.

2. The second layer consists of buffers needed for some functions.

3. The third layer is the application layer. This layer is partially implemented by the Demo Code for evaluation

purposes, but extensions and enhancements can be added by the application software developer to design

suitable electronic power meter applications.

Figure 2-1: shows the partitions of each software component. As illustrated, there are many different designs an

application can develop depending on its usage. Section 5 describes in more detail the functions within each

component.

Application

Layer

Buffer

Layer

Hardware

Layer

Hardware

Meter

CE

CE RAM

LCD

AFE

Display Sensors

Figure 2-1: Software Structure

Totals (Meter Data)

CLI

SerCLI FLAG

Ser0 Ser1LCD

UART0 UART1

Terminal/

PC

AMR

v1.1v1.1 TERIDIAN Proprietary 14 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 15

71M653X Software User’s Guide

The Demo Code is modular. Each device in the chip and on the Demo Board has a corresponding set of driver

software in the Hardware Layer. These driver software modules are very basic, enabling customers to easily locate and

reuse the logic. For the serial devices and for the CE, the buffer handling has been separated from the driver modules.

Where there are several similar devices (e.g. ser0, ser1, or tmr0, tmr1), the Demo Code simulates a virtual object base

class using C preprocessor macros. For example, to initialize the first serial interface, ser0, the source file can include

ser0.h, and then call ser_initialize(). To transmit a byte on ser0, the file can include ser0.h, and then call

ser_xmit(). The convenience is that high-level code can be ported to another device by just (for example) including

ser1.h, rather than ser0.h. Just by making variables static, entire high-level protocols can be written and maintained by

copying the code debugged on one device, and having it include the other device’s .h file.

The demo firmware uses this technique for the command line interface (ser0cli.c, ser1cli.c), the FLAG AMR interface

(flag0.c, flag1.c) and for the software timer module (stm.c). The base-class emulation uses macros because on the

80515 MPU macros execute faster and are also more compact than the standard C++ (object-oriented) design with an

implicit structure containing function pointers.

The Demo Code is also designed with an “options.h” file, which enables and disables entire features in the firmware.

The macro approach combined with the “options.h” file permitted the firmware team to adapt the same Demo Code to

both the 6531 and 6534 versions.

2.4 UTILITIES

Three utilities are offered that make it possible to perform certain operations on the object (HEX) files without having to

use a compiler:

• D_MERGE.EXE allows combining the object file with a text script in order to change certain default settings of

the program. For example, modified calibration coefficients resulting from an actual calibration can be inserted

into the object file.

• CE_MERGE.EXE allows combining the object file with an updated image of the CE code.

• BANK_MERGE.EXE combines the hex files the Keil tools provide for each code bank.

All utilities are executed from a DOS window (DOS command prompt). To invoke the DOS window, the “command

prompt” option is selected after selecting Start – All Programs – Accessories.

The GUI subdirectory contains an unsupported MS Windows .NET implementation of a FLAG hand-held unit.

2.4.1 D_MERGE

Many changes to the firmware’s defaults can be made permanent by merging them into the object file. The first step for

this is to create a macro file (macro.txt) containing the commands adjusting the I/O RAM or other defaults, such as the

following commands affecting calibration:

]8=+16381

]9=+16397

]E=+237

The d_merge program updates the 653x_demo.hex file with the values contained in the macro file. The d_merge

program must be in the same directory as the source files, or a path to the executable must be declared. Executing the

d_merge program with no arguments will display the syntax description. To merge the file macro.txt and the object file

old_653x_demo.hex into the new object file new_653x_demo.hex, use the command:

d_merge old_653x_demo.hex macro.txt new_653x_demo.hex

2.4.2 CE_MERGE

The ce_merge program updates the 653x_demo.hex file with the CE program image contained in the CE.CE file

and the data image CE.DAT. Both CE.CE and CE.DAT must be i

source format but in the compiled format (intel hex). These files will be made available from Teridian in the

cases when updates to the CE images are necessary.

To merge the object file old_653x_demo.hex with CE.CE and CE.DAT into the new object file new_653x_demo.hex,

use the command:

n Intel HEX format, i.e. both files are not in the

v1.1v1.1 TERIDIAN Proprietary 15 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 16

71M653X Software User’s Guide

ce_merge old_653x_demo.hex ce.ce ce.dat 653x_demo.hex

2.4.3 BANK_MERGE

If using Keil’s professional package, bank_merge.exe is not needed to produce Intel-386 files from banked code.

Simply go to the pull-down hex file selection in the output section of the project configuration of uVision, and select

“i386”. Keil’s premium OHX51 hex file converter will automatically produce a single intel-386 file containing all the code

banks.

If producing banked code with Keil’s standard package, the BL51 linker is tightly coupled to the OC51 and OH51 code

converters. These produce one 64K Intel hex file for each code bank. The Signum emulator and TSC’s TFP (in-circuit

programmer) require that banked code be in a different format, a single Intel-386 hex file.

Bank_merge.exe is a program that converts Keils’ multiple hex files into a single Intel-386 hex file.

Usage: bank_merge <Number of Banks> <ROM Size> <Input Name> <Output>\n");

<Number of Bank> - 3 for 6531, and 7 for 6534");

<ROM Size> - The memory size of ROM in kbyte (128,256,...)"

<Input> - Compiled files' name without extension"

<Output> - Output file name. Must have '.hex' extension\n");

For example:

bank_merge 3 128 banktest31 new_code.hex

This merges the three compiled hex files, banktest31.H01, banktest31.H02, banktest31.H03 and produces

new_code.hex in a 128kbyte intel-386 hex file.

v1.1v1.1 TERIDIAN Proprietary 16 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 17

71M653X Software User’s Guide

3

3 DESIGN REFERENCE

As depicted in Figure 1 of section 2, the 71M653X provides a great deal of design flexibility for the application developer. Programming details are described below.

3.1 PROGRAM MEMORY

The embedded 80515 MPU within the 71M653X has separate program (128K or 256K bytes) and data memory (4K

bytes). The code for the Compute Engine program resides in the MPU program memory (flash).

The Flash program memory is addressed as a 64KB block. The upper 32K is a window on a code banked. It can be

switched to other code banks by writing a banke numbe rto the banked register FL_BANK. The flash memory is further

segmented in 512-byte pages which can be individually erased. Selection of these individual blocks is accomplished

using the function calls related to flash memory, which are described in more detail below.

3.2 DATA MEMORY

The 71M653X has 4K bytes of Data Memory used by the embedded 80C515 MPU, and shared with the proprietary

computer-engine (CE). In most configurations, the CE uses 1K of this RAM, leaving 3K for use by the MPU. See Table

3-1: for a summary.

Address

(hex)

0000-7FFF Flash Memory Non-volatile

8000-FFFF Flash Memory Non-volatile

0000-03FF Static RAM Volatile

0400-1000 Static RAM Volatile MPU data 0 3KB

2000-20FF Static RAM

Memory

Technology

Memory Type Typical Usage

Common code area for the

program and non-volatile

data.

Bank window code area for

the program and nonvolatile data. The 6531, 32,

and 33 have 3 banks

yielding 128K total. The

6534 has 7 banks, yielding

256K total

CE data, actual last byte

may be somewhat less than

1K, depending on the CE

code.

Volatile 0 256

Miscellaneous I/O RAM

(configuration RAM)

Wait States

(at 5MHz)

0 32K

0 32K

0 1KB

Memory Size

(bytes)

Table 3-1: Memory Map

v1.1v1.1 TERIDIAN Proprietary 17 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 18

71M653X Software User’s Guide

3.3 PROGRAMMING THE 71M653X CHIPS

There are two ways to download a hex file to the 71M653X Flash Memory:

• Using a Signum Systems ADM-51 ICE.

• Using the TERIDIAN Semiconductor Flash Download FDBM-TFP-2 Stand-Alone Module

Note: For both programming and debugging code it is important that the hardware watchdog timer is

disabled. See the Demo Board User’s Manual for details.

Before downloading code to a 71M653x:

• Stop the MPU

• Disable the CE by writing a 0 to XDATA at address 0x2000.

• Erase the flash memory.

3.4 DEBUGGING OF THE 71M653X CHIPS

When debugging with the ADM51 in-circuit emulator, the CE continues to run, and this disables flash memory access

because the code of the CE is located in flash memory.

When setting breakpoints, only tw o breakpoints can be used, because the first two breakpoints are

“hardware” breakpoints, while the rest attempt to write to flash memory.

3.5 TEST TOOLS

A command line interface operated via the serial interface of the 71M653X MPU provides a test tool that can be used

to exercise the functions provided by the low-level libraries. The command-line interface requires the following

environment:

1) Demo Code (653X_demo.hex) must be resident in flash memory

2) The Demo Board is connected via a Debug Board to a PC running Hyperterminal or another type of terminal

program.

3) The communication parameters are set at 300 bps, 7N2, XON/XOFF flow control, as described in section

3.5.1 .

v1.1v1.1 TERIDIAN Proprietary 18 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 19

71M653X Software User’s Guide

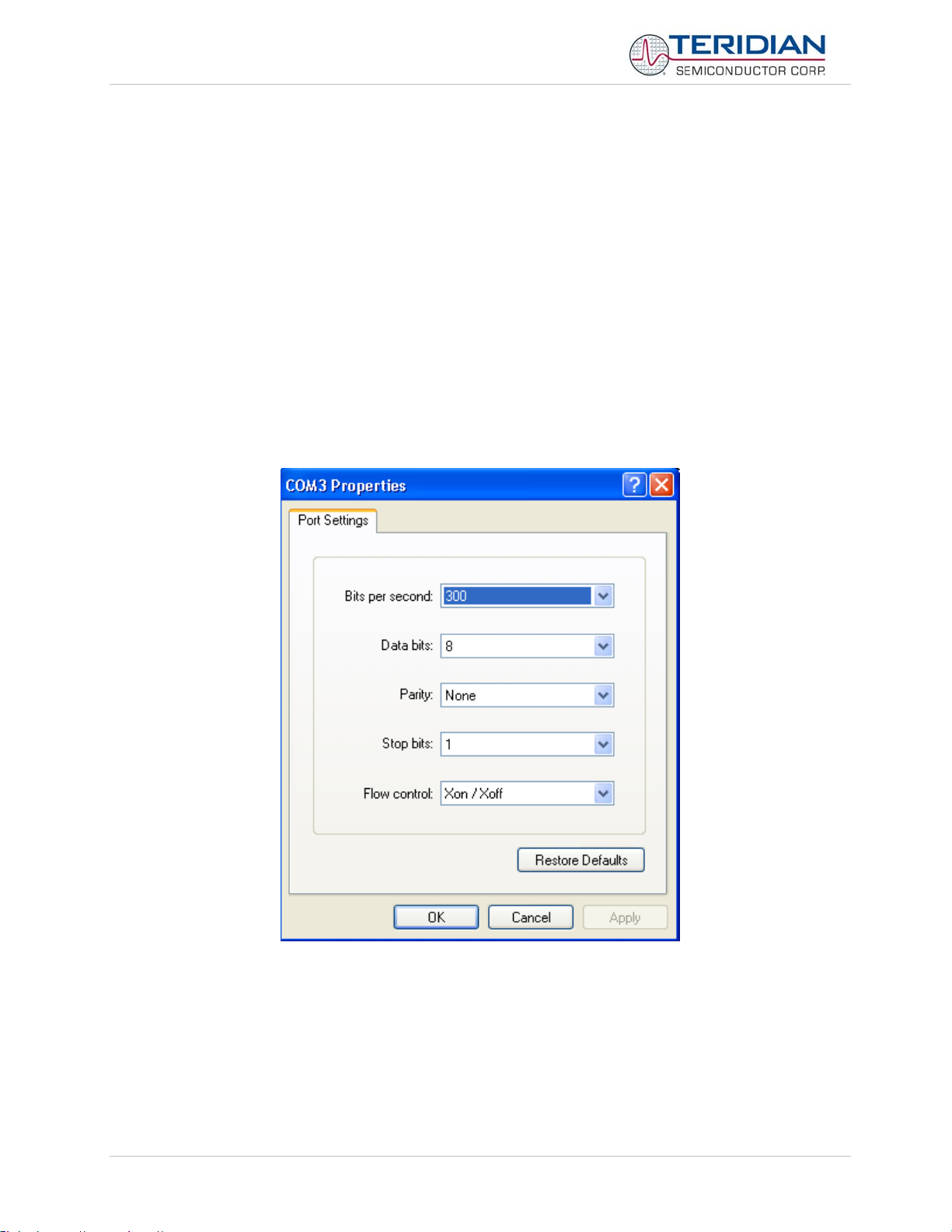

3.5.1 Running the 653X_Demo.hex Program

This object file is the 71M653X embedded application developed by TERIDIAN to exercise all low-level function calls

using a serial interface. Demo Boards ship pre-installed with this program. To run this program:

• Connect a serial cable between the serial port of the Debug Board RS232 and a COM port of a Windows

PC.

• Open a Windows’ Hyperterminal session at 2400 or 300 bps (depending on jumper settings – see the

DBUM), 8N1, one stop bit with XON/XOFF flow control enabled. The setup dialog box is shown in Figure

3-1: Port Speed and Handshake Setup.

• Power on the Demo Board and hit <CR> a few times on the PC keyboard until ‘>’ is displayed on the

Hyperterminal screen.

• Type a command from the CLI Reference ( 3.5.2 )

• All references to ‘c’ (lower case c) indicate any ASCII character, all other lowercase letters are one-byte

numbers

• Numbers can be entered in decimal by preceding them with a plus-sign (e.g. hex 20 = +32)

The 71M653x Demo Board User’s Manual contains instructions on how to connect the serial cable.

Figure 3-1: Port Speed and Handshake Setup

©

Note: HyperTerminal can be found by selecting Programs ÆAccessories Æ Communications from the Windows

start

menu. The connection parameters are configured by selecting File Æ Properties and then by pressing the

Configure button. Port speed and flow control are configured under the General tab, bit settings are configured

by pressing the Configure button (Figure 3-1: Port Speed and Handshake Setup) as shown below.

v1.1v1.1 TERIDIAN Proprietary 19 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 20

71M653X Software User’s Guide

3.5.2 CLI Commands

The Demo Board User’s Manual (DBUM) for the 71M653x contains a complete list of the available commands.

3.5.3 Command (Macro) Files

Commands or series of commands may be stored in text (ASCII) files and sent to the 71M653X using the “Transfer –

Send Text File” command of Hyperterminal or any other terminal program.

v1.1v1.1 TERIDIAN Proprietary 20 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 21

71M653X Software User’s Guide

4

4 TOOL INSTALLATION GUIDE

This section provides detailed installation instructions for the Signum ADM-51 in-circuit emulator and for the Keil

compiler.

4.1 INSTALLING THE PROGRAMS FOR THE ADM51 EMULATOR

The AMD51 ICE interfaces with the PC is via the USB serial interface.

The installation process consists of the following steps:

1. Installing the Chameleon Debugger used with the Signum ICE

2. Installing the ADM51 USB driver

3. Installing updates

4. Creating a project

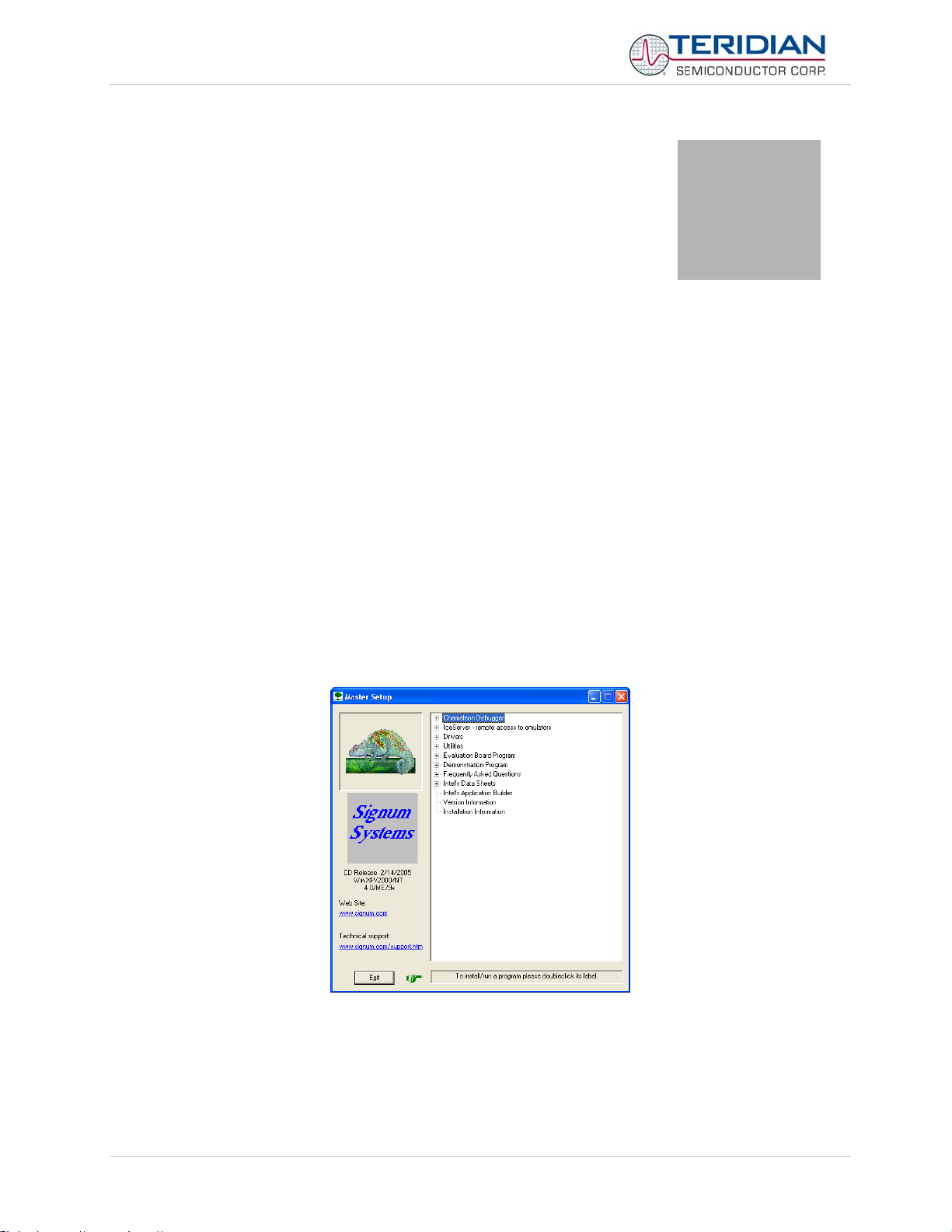

4.2 INSTALLING THE WEMU PROGRAM (CHAMELEON DEBUGGER)

Insert the CD from Signum Systems and connect the ICE ADM51 to the PC with the provided USB cable.

The following dialog box will appear (this dialog box also shows the release date of the program):

Click on “Chameleon Debugger” and then select “ADM51 Emulator”.

Follow the instructions given by the installation program.

v1.1v1.1 TERIDIAN Proprietary 21 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 22

71M653X Software User’s Guide

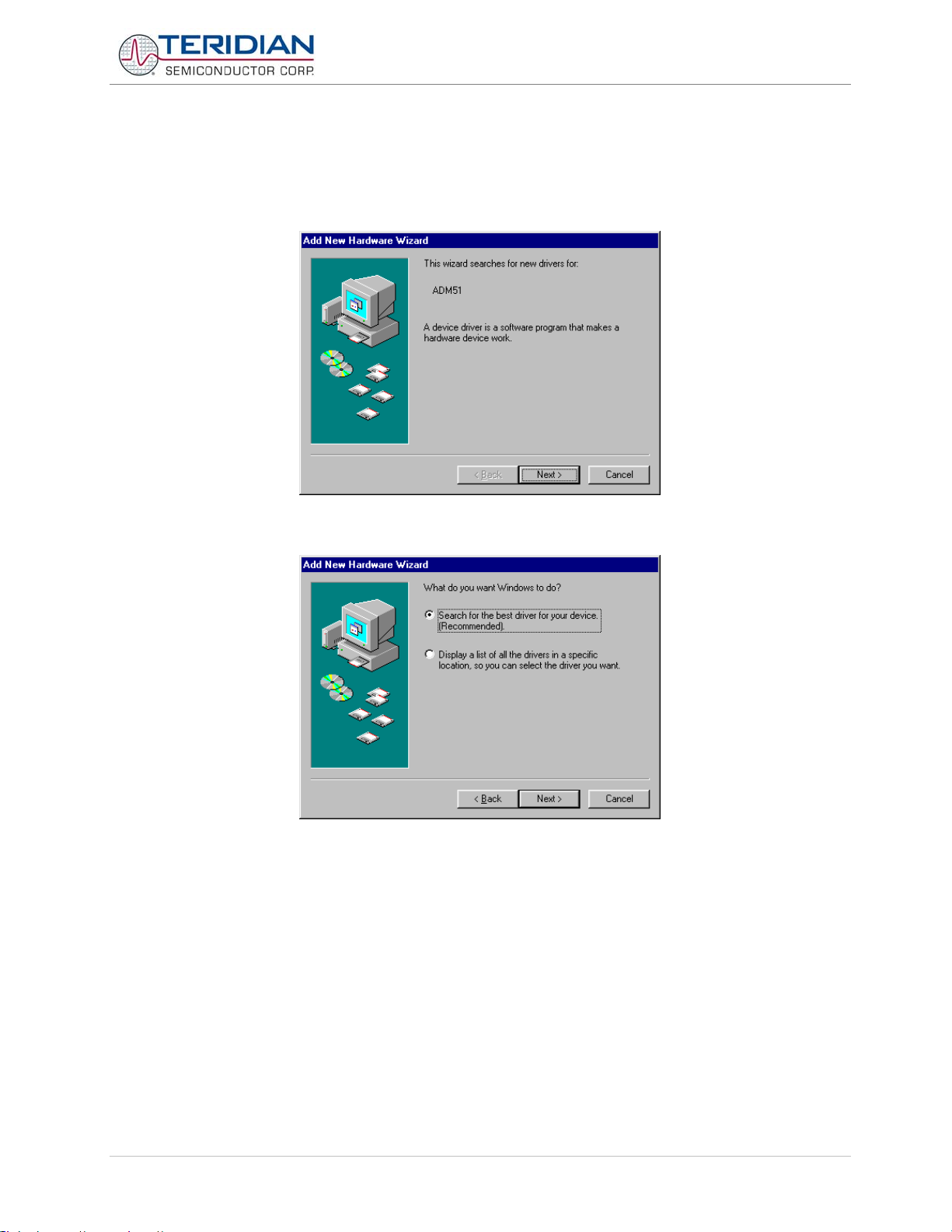

4.3 INSTALLING THE ADM51 USB DRIVER

The Wemu51 program communicates with the emulator ADM51 via the USB interface of the PC. The USB driver for

the ADM51 has to be installed prior to using the emulator. After plugging in the USB cable into the PC and the ADM51

ICE the status light of the ADM51 emulator should come on.

A dialog box will appear, asking you to install the ADM51 driver.

Click Next. Another dialog box will appear, asking how to search for the driver. Use the recommended method.

Click Next.

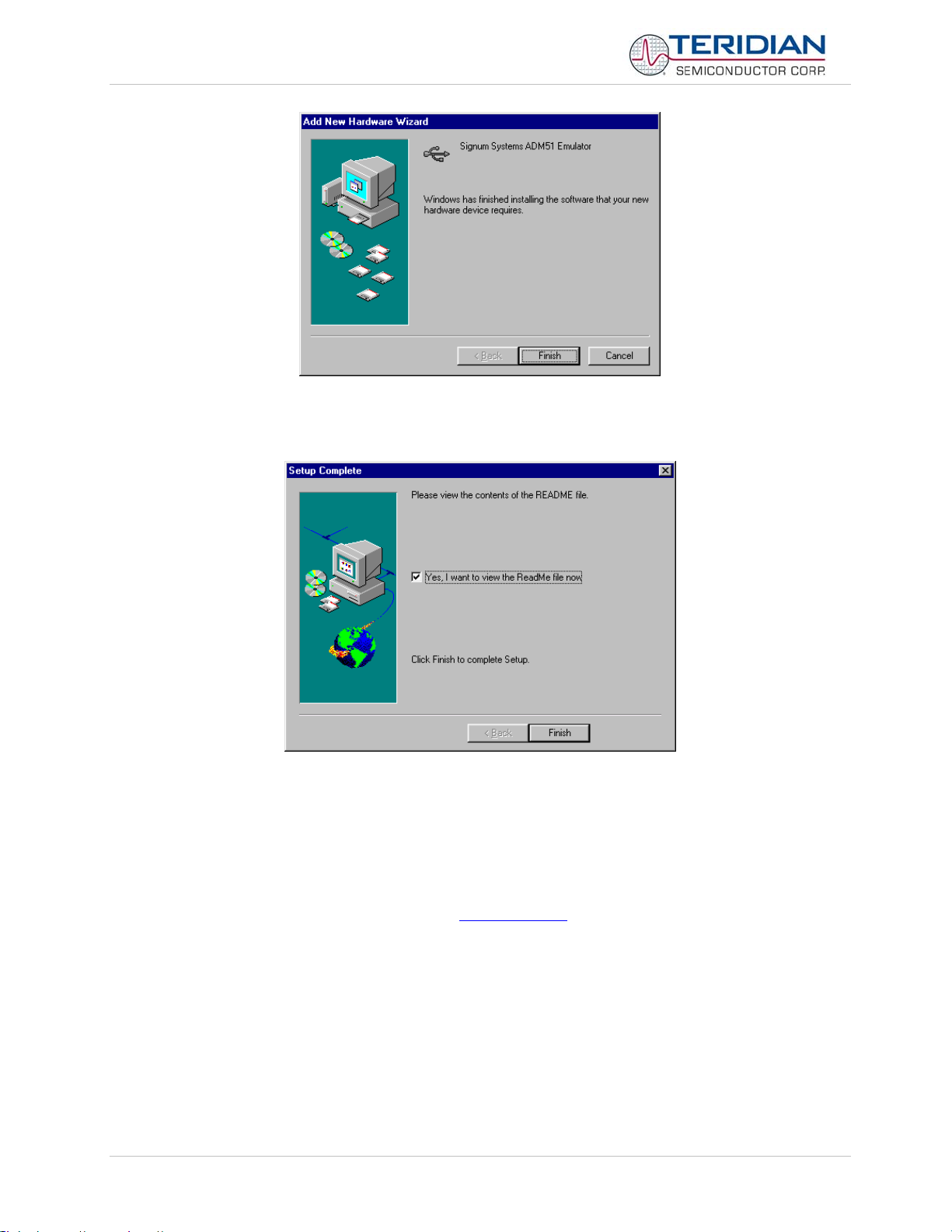

Another screen (not shown) will appear asking to locate the driver. Select Specific Path and browse to:

C:\Program Files\Signum Systems\Wemu51\Drivers\USB. Click Next.

v1.1v1.1 TERIDIAN Proprietary 22 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 23

71M653X Software User’s Guide

Click Finish.

Click Finish again.

Note: USB 1.1 is sufficient for operation of the ADM51. If higher performance is desired and no USB 2.0 port is

available on the host PC, a USB 2.0 card can be installed as an option.

4.4 INSTALLING UPDATES TO THE EMULATOR PROGRAM AND HARDWARE

If the Wemu51 program is revision 3.11.4 or later, no special precautions have to be taken. Otherwise, the program

should be updated using the Signum Systems web site (www.signum.com

When running the Wemu51 program revision 3.11.4 or later, the firmware in the ADM51 will be checked automatically.

ADM51 emulators with outdated firmware will not function properly. The Wemu51 will offer an automatic update for the

ADM51, if necessary. For a successful upgrade it is vital to follow the instructions on screen precisely.

v1.1v1.1 TERIDIAN Proprietary 23 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

).

Page 24

71M653X Software User’s Guide

4.5 CREATING A PROJECT

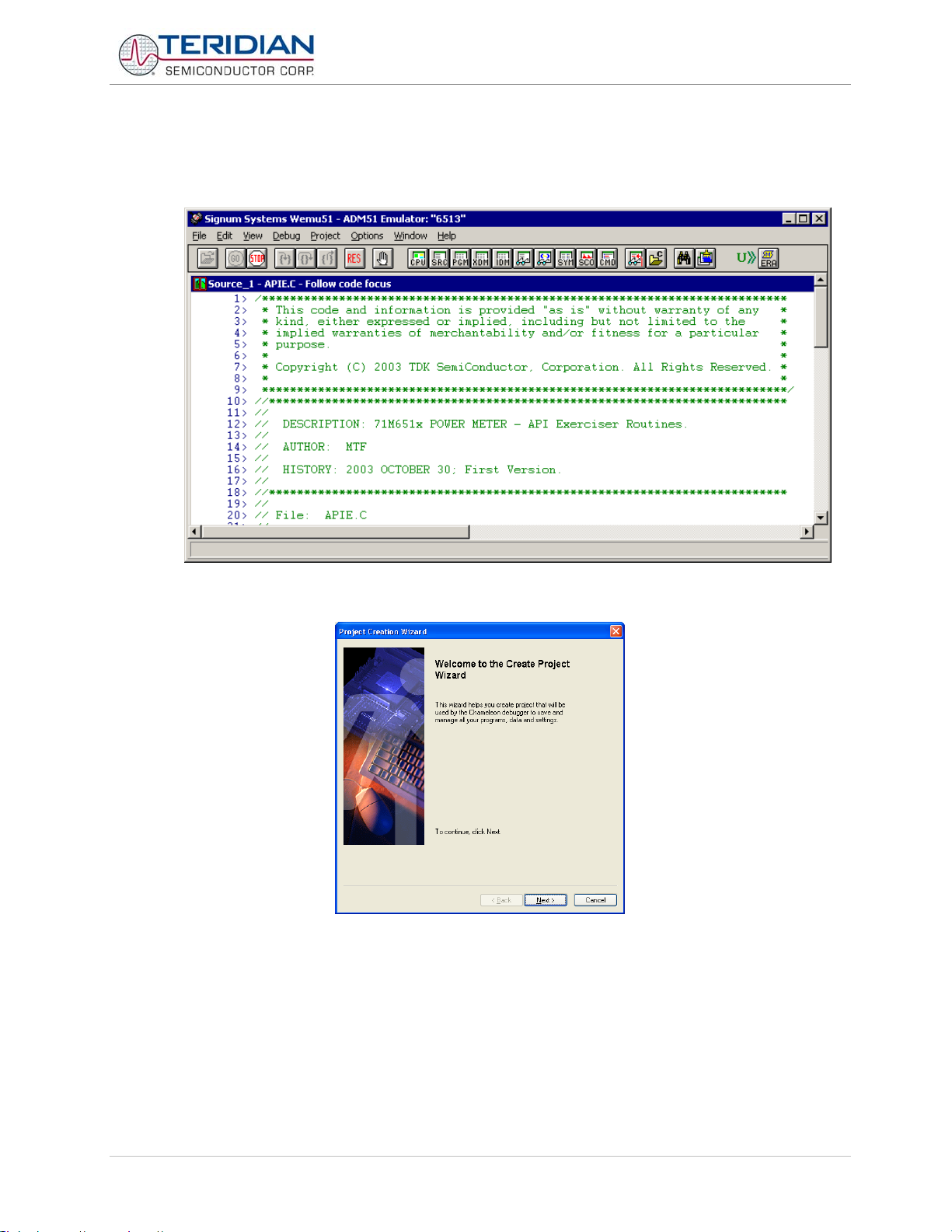

Double click on the WEMU51 icon to start the Chameleon debugger.

Click Project/Create New Project. The following screen will appear:

Follow the instructions of the Create Project Wizard by selecting Next.

v1.1v1.1 TERIDIAN Proprietary 24 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 25

71M653X Software User’s Guide

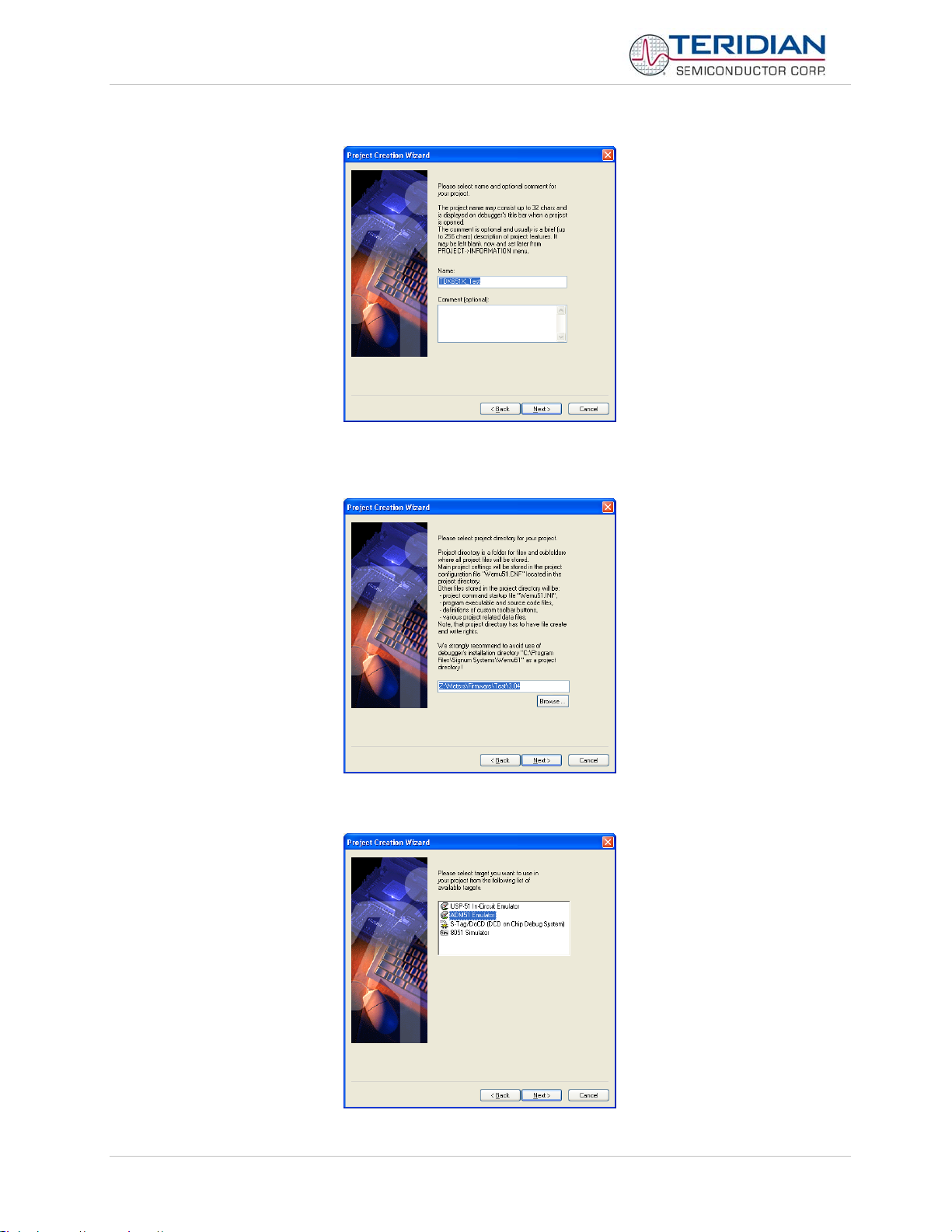

When prompted for the project name to be used, type a convenient project name. Click Next.

When prompted for the project directory to be used, select an existing folder on the PC. Do NOT select any folder in

the Wemu51 installation directory! Click Next.

When prompted for the emulator to be used, select ADM51 Emulator. Click Next.

v1.1v1.1 TERIDIAN Proprietary 25 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 26

71M653X Software User’s Guide

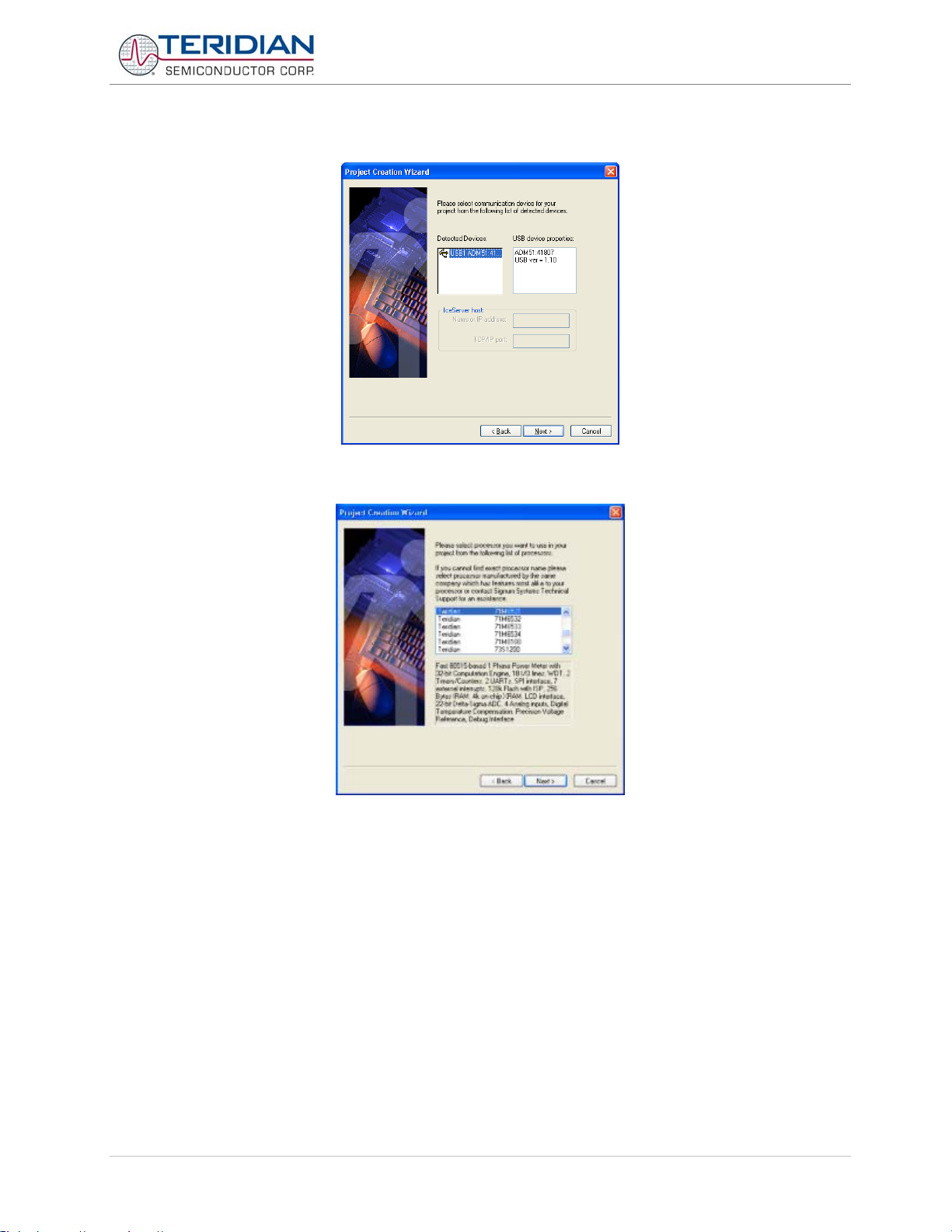

When prompted for the communication device to be used, select USB ADM51. Click Next.

When prompted for the processor to be used, select the correct IC. Click Next.

Click Finish.

v1.1v1.1 TERIDIAN Proprietary 26 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 27

71M653X Software User’s Guide

4.6 INSTALLING THE KEIL COMPILER

After inserting the Keil CD-ROM into the CD drive of the PC, the on-screen instructions should be followed to install the

Keil compiler.

The installer will display the following screen:

Select Install Products & Updates

Select C51 Compiler and Tools

Follow the on-screen instructions of the installation program. When prompted for the add-on disk, insert the disk in the

floppy drive and click Next or browse to the location of the files (if they were previously copied to the hard drive of the

PC) by clicking Browse.

v1.1v1.1 TERIDIAN Proprietary 27 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 28

71M653X Software User’s Guide

4.7 CREATING A PROJECT FOR THE KEIL COMPILER

4.7.1 Directory Structure

The following directory structure is established when the files from the archive 653X_Demo.zip are unpacked while

maintaining the structure of subdirectories:

<drive letter>:\…\meter project\

<drive letter>:\…\meter project\CE

<drive letter>:\…\meter project\CLI

<drive letter>:\…\meter project\docs

<drive letter>:\…\meter project\flag

<drive letter>:\…\meter project\IO

<drive letter>:\…\meter project\Main

<drive letter>:\…\meter project\Main_653x_CLI

<drive letter>:\…\meter project\Meter

<drive letter>:\…\meter project\Util

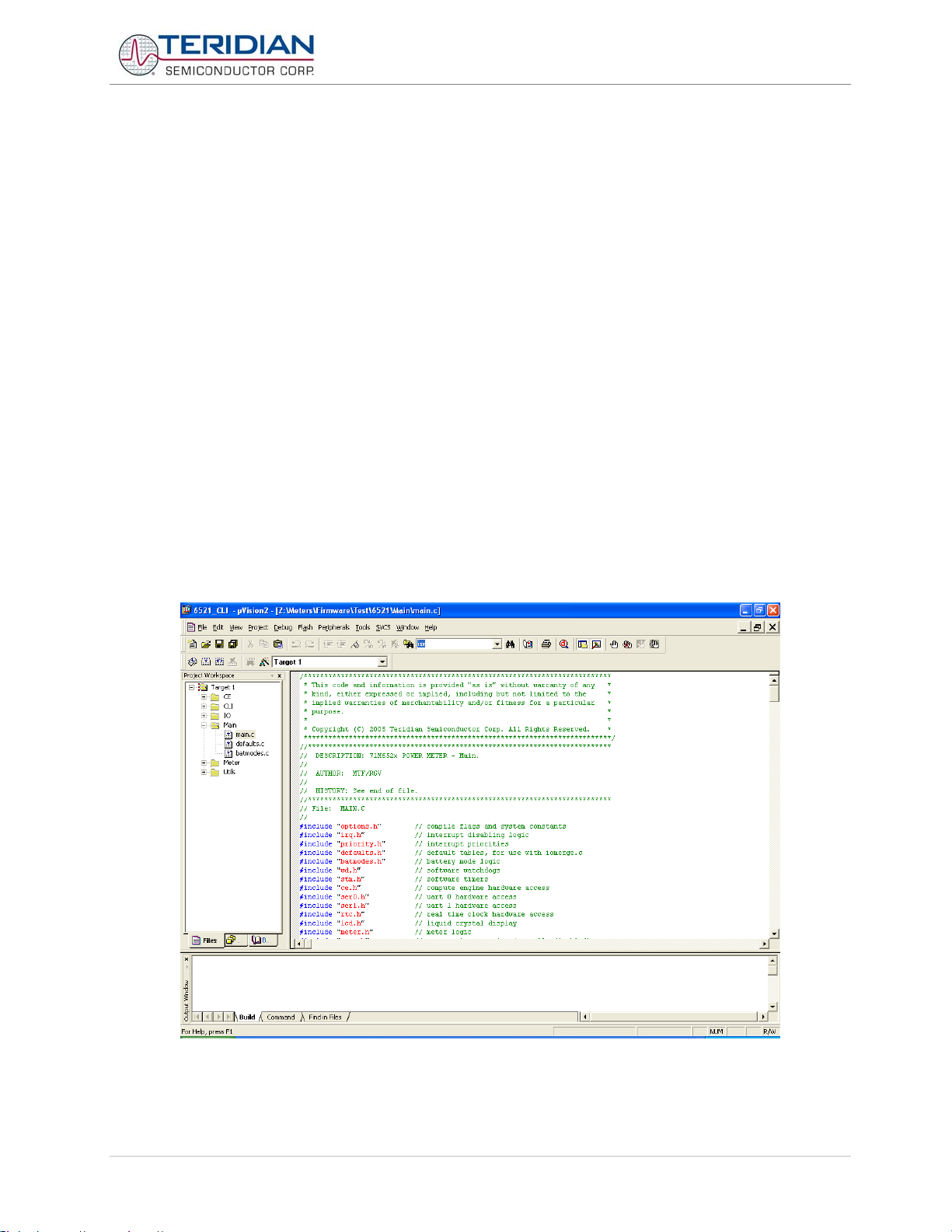

The project control file 653X_demo.uv2 will be in the directory <drive letter>:\…\meter project. The Keil compiler can be

configured easily by loading the file 653X_demo.uv2, using the Project Menu and selecting the Open Project

command.

The window shown below should appear when the project control file is opened.

The Project Workspace screen on the left side of the window shows the main components of the source (CE, CLI, IO,

Main, Meter, Utils) in folders. Folders can be opened by clicking on the plus sign next to them. Opening the folders will

display the source files associated with them.

v1.1v1.1 TERIDIAN Proprietary 28 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 29

71M653X Software User’s Guide

It should be noted that not all header files are physically present in the project directory. The files absacc.h, string.h,

ctype.h, and setjmp.h are provided by the compiler manufacturer, and they are located in the Keil\C51\INC directory.

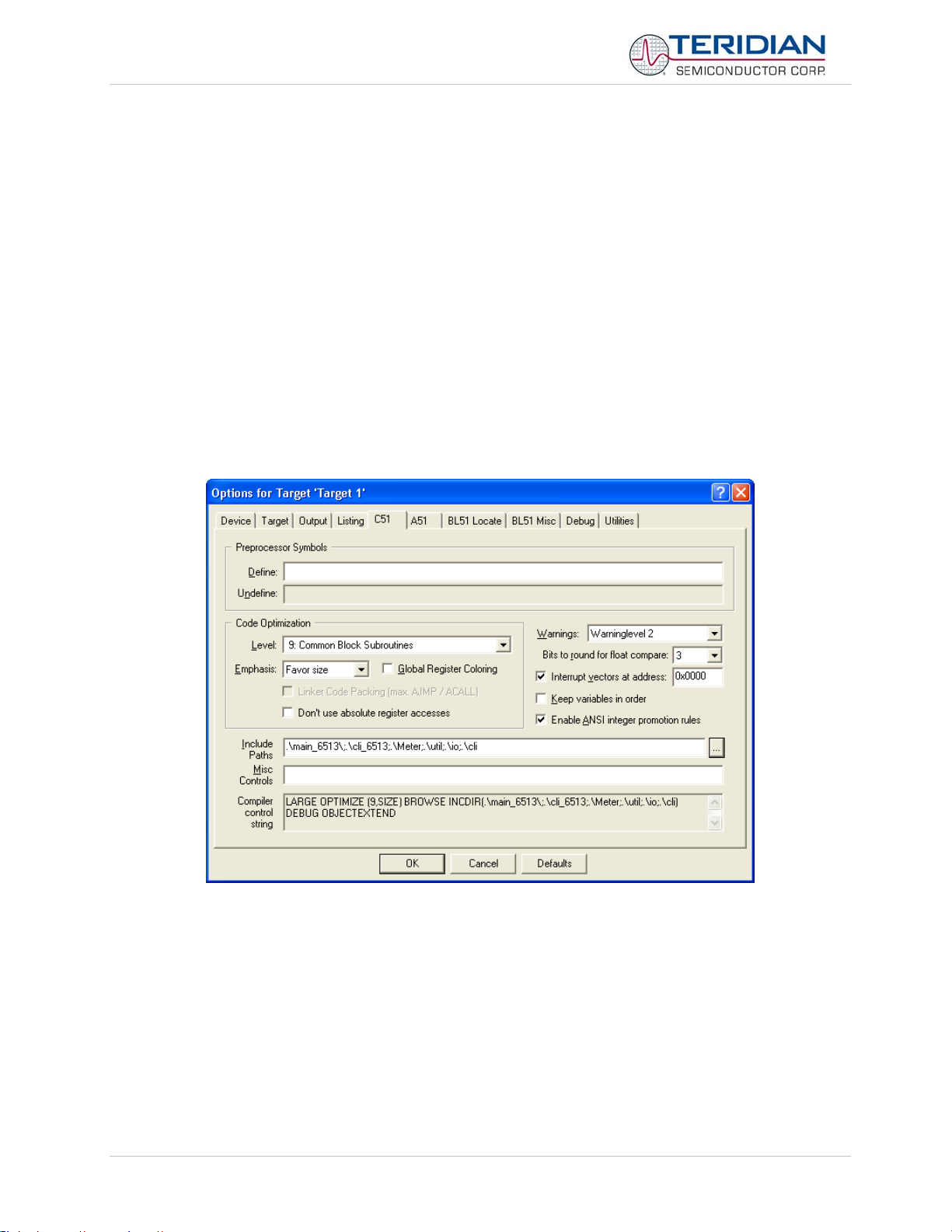

4.7.2 Adjusting the Keil Compiler Settings

Once, the Keil compiler is installed, the most convenient method to start the project is to double-click on the file

653x.UV2 (or 653x.UV3). This will start the Keil compiler with the proper settings stored in the 653x.UV2 file.

Directory structures and drive names vary from PC to PC. The settings for the compiler can be adjusted using the

following method:

1. Select “target1” in the leftmost window.

2. Select “project” from the top menu and then select “options for target 1”.

3. Select the “C51” tab.

4. Click the button right next to the “Include Paths” window. Three paths will be listed, pointing to meter

projects, meter projects\demo, and meter projects\demo\header files.

5. If necessary, delete these path entries (X button) and replace them with the corresponding path

entries for your PC ( button).

The dialog box should look like shown below. After making the necessary changes, the project file (653X_demo.UV2)

should be stored.

v1.1v1.1 TERIDIAN Proprietary 29 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 30

71M653X Software User’s Guide

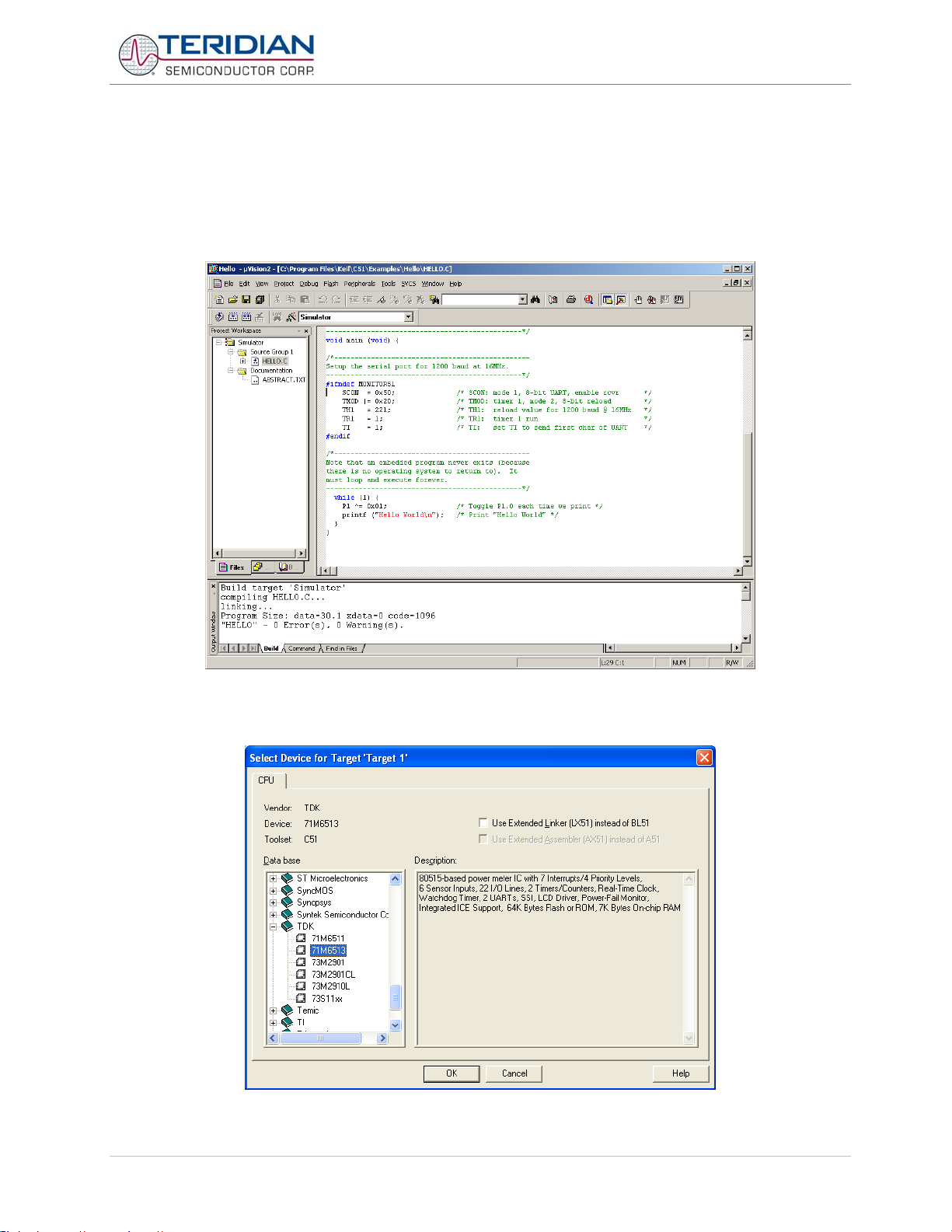

4.7.3 Manually Controlling the Keil Compiler Settings

If the method described in section “Adjusting the Keil Compiler Settings” is not used, the Keil compiler settings can also

be controlled manually.

The target options should be selected in order to adapt the compiler controls properly to the target. The uVision

compiler environment is started by selecting Programs Æ Keil Æ uVision2. uVision should start up and present the

following window:

Under Project Æ Options for Target1, select the Device tab and check the selected device. Newer versions of the Keil

Compiler offer selection of TERIDIAN (labeled “TDK”) 71M653x devices:

v1.1v1.1 TERIDIAN Proprietary 30 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 31

71M653X Software User’s Guide

For older versions of the Keil compiler, select the TERIDIAN folder (labeled “TDK”), open it by clicking on the + sign

and select 73M2910L as the target device. Confirm by clicking OK.

Under Project Æ Options for Target1, select the Target tab and enter the values in the fields as shown above. Confirm

by clicking OK.

v1.1v1.1 TERIDIAN Proprietary 31 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 32

71M653X Software User’s Guide

Under the Output tab, select a name for the executable (object) file with .abs extension’ in the field labeled “Name of

the executable” and check the fields by “Debug Information”, “Browse Information” and “Create HEX File”. This will

guarantee that high-level source information will be embedded in the output file. Select HEX-80 as the output format,

as shown below:

Under the C51 tab, provide path names for the source files to be included, as shown below.

Click OK to set all the options selected for project and return to the main menu.

With the source and header files now existing in the newly created project, the files can be compiled using the Build

Target option under the Project menu.

4.8 OUTPUT FILE FORMAT

Both the Keil compiler and the Signum WEMU51 emulator program accept executable programs for download to the

653X ICs in Intel Hex format.

v1.1v1.1 TERIDIAN Proprietary 32 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 33

71M653X Software User’s Guide

4.8.1 Basic Intel Hex Format

The Intel HEX file is an ASCII text file with lines of text that follow the Intel HEX file format. Each line in an Intel HEX file

contains one HEX record. These records are made up of hexadecimal numbers that represent machine language code

and/or constant data. Intel HEX files are often used to transfer the program and data that would be stored in a ROM or

EPROM. Most EPROM programmers or emulators can use Intel HEX files.

Record Format

An Intel HEX file is composed of any number of HEX records. Each record is made up of five fields that are arranged in

the following format:

:llaaaatt[dd...]cc

Each group of letters corresponds to a different field, and each letter represents a single hexadecimal digit. Each field

is composed of at least two hexadecimal digits-which make up a byte-as described below:

: is the colon that starts every Intel HEX record.

ll is the record-length field that represents the number of data bytes (dd) in the record.

aaaa is the address field that represents the starting address for subsequent data in the record.

tt is the field that represents the HEX record type, which may be one of the following:

00 - data record

01 - end-of-file record

02 - extended segment address record

04 - extended linear address record

dd is a data field that represents one byte of data. A record may have multiple data bytes. The number of data

bytes in the record must match the number specified by the ll field.

cc is the checksum field that represents the checksum of the record. The checksum is calculated by summing

the values of all hexadecimal digit pairs in the record modulo 256 and taking the two's complement.

Data Records

The Intel HEX file is made up of any number of data records that are terminated with a carriage return and

a linefeed. Data records appear as follows:

:10246200464C5549442050524F46494C4500464C33

This record is decoded as follows:

:10246200464C5549442050524F46494C4500464C33

||||||||||| CC->Checksum

|||||||||DD->Data

|||||||TT->Record Type

|||AAAA->Address

|LL->Record Length

:->Colon

where:

10 is the number of data bytes in the record.

2462 is the address where the data are to be located in memory.

00 is the record type 00 (a data record).

464C...464C is the data.

33 is the checksum of the record.

v1.1v1.1 TERIDIAN Proprietary 33 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 34

71M653X Software User’s Guide

4.8.2 Intel Hex386 File Format

For banked code, the Intel Hex386 file format (Extended Linear Address Records) is used:

Extended linear address records are also known as 32-bit address records and HEX386 records. These records

contain the upper 16 bits (bits 16-31) of the data address. The extended linear address record always has two data

bytes and appears as follows:

:02000004FFFFFC

where:

02 is the number of data bytes in the record.

0000 is the address field. For the extended linear address record, this field is always 0000.

04 is the record type 04 (an extended linear address record).

FFFF is the upper 16 bits of the address.

FC is the checksum of the record and is calculated as

01h + NOT(02h + 00h + 00h + 04h + FFh + FFh).

When an extended linear address record is read, the extended linear address stored in the data field is saved and is

applied to subsequent records read from the Intel HEX file. The linear address remains effective until changed by

another extended address record.

The absolute-memory address of a data record is obtained by adding the address field in the record to the shifted

address data from the extended linear address record. The following example illustrates this process:

Address from the data record's address field 2462

Extended linear address record data field FFFF

-------Absolute-memory address FFFF2462

v1.1v1.1 TERIDIAN Proprietary 34 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 35

71M653X Software User’s Guide

4.9 WRITING BANK-SWITCHED CODE

The 80515 microcontroller contained in the 71M653X Energy Meter chips can only address 64Kbytes of code. This

section explains how to design firmware with more than 64K of code for the 71M653X Energy Meter chips.

4.9.1 Hardware Overview

In the 71M6531 there is a 32K area from code address 0x0000 to 0x7FFF. The code in this area is always available to

the 8051. This area is “common” and is the same memory area as “bank 0”. Since it is always present, it never needs

to be switched into the bank area.

A 32K bank is selected by writing the bank’s number in the register FL_BANK, an SFR at 0xB6. After this, the bank’s

code is visible to the MPU in addresses 0x8000 to 0xFFFF.

The 71M6531 has four 32K banks (128K bytes total). Bank 0 is the common area. Banks 1, 2, and 3 are the banked

code areas selected by FL_BANK.

The 71M6534 has eight 32K banks (256K total). Bank 0 is the common area. Banks 1 through 7 are the banked code

areas selected by FL_BANK.

A reset sets FL_BANK to 1, so any 71M653x IC can run 64K of non-bank-switching code.

The 71M653x ICs have two write protect registers to protect ranges at the beginning and end of flash.

The beginning is protected by BOOT_SIZE, XDATA 0x20A7 when WRPROT_BT is set in FLSHCTL, SFR 0xB2.

The end can be protected by placing the CE program at the start of the area to protect, and setting WRPROT_CE in

FLSHCTL, SFR 0xB2.

Address Range for

FL_BANK

[2:0]

000 0x0000-0x7FFF 0x0000-0x7FFF X X X

001 0x0000-0x7FFF 0x8000-0xFFFF X X X

010 0x0000-0x7FFF 0x10000-0x17FFF X X X

011 0x0000-0x7FFF 0x18000-0x1FFFF X X X

100 0x0000-0x7FFF 0x20000-0x27000 X

101 0x0000-0x7FFF 0x28000-0x2FFFF X

110 0x0000-0x7FFF 0x30000-0x37FFF X

111 0x0000-0x7FFF 0x38000-0x3FFFF X

The 71M653x ICs’ flash memory are very similar to the ROM arrangement in Keil’s example “Banking With Common

Area” of chapter 9 (linker) of Keil’s “Macro assembler and Utilities” manual.

Lower Bank

(Common)

(0x000-0x7FFF)

Table 4-1: Code Bank Memory Addresses and Availability

Address Range for

Upper Bank

(0x8000-0xFFFF)

6531

128KB

6533

128KB

6534

256KB

4.9.2 Software Overview

Teridian’s demonstration code uses the Keil compiler’s standard bank switching system (www.Keil.com).

This is completely supported by Keil, a major compiler vendor for 8051s, and Signum, the emulator vendor. Code can

be ported from non-banked projects, and full symbolic banked debugging is available.

Keil’s scheme puts a “page table” in common memory. Code calls an entry in the page table. Each entry is a bit of

code that switches to the subroutine’s bank, and jumps to the subroutine in the bank.

Keil’s linker automatically produces the page table. In Teridian’s demo code, the size of this table is less than 1K.

Code using the page table is slower than native 16-bit code, because it has to set the page register.

v1.1v1.1 TERIDIAN Proprietary 35 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 36

71M653X Software User’s Guide

Interrupts must start in the common (non-banked) area, because the bank register could have any value.

Calls via function pointers (e.g. “callback routines”) are supported, but need to be made global, and mapped to their

caller with the linker’s overlay functions. Keil’s linker often omits callback routines from the page table when it

optimizes the page table, and this causes incorrect operation.

Constant values have to be accessed from the same bank, or common code. When accessed from common code the

bank has to be switched manually with switchbank(), a subroutine in the bank logic.

4.9.3 Software Tool Versions

The development software used with these examples was Keil C version 8.03, with the BL51 linker (the Lx51 linker is

actually easier to use, but not shown). The Signum emulator software used was version 3.11.04.

4.9.4 Setup of the Compiler Project

This dialogue is for the project options of a 71M6531, which has 4 banks (see Figure 4-1).

Figure 4-1, Setup of Keil Compiler for bank-switched code

When opening individual files by right-clicking on the file names (after opening the group folders listed under “Target”) ,

file options can be edited. These options can be set to assign code to pages (as shown in Figure 4-2, ).

v1.1v1.1 TERIDIAN Proprietary 36 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 37

71M653X Software User’s Guide

Figure 4-2, Selecting a Bank for a File Group in Keil C

4.9.5 Startup

TSC provides special start-up code on the CD-ROMs shipped with the 71M653X Demo Kits. The code can be found at

Util\startup_30_banked.a51. This file sets up the bank-switching logic. It must be included in the build. Any other

startup.a51 file must be removed.

4.9.6 Bank-Switching Code

TSC has already ported Keil’s bank-switching code, Util\L51_bank.a51. TSC’s version of this file should be included in

the build. TSC has already selected the fastest standard bank-switching method as the default.

During performance testing, TSC made a good-faith attempt to port the other bank-switching methods in this code,

including features needed by Keil’s advanced Lx51 linker. However these versions are not extensively tested.

4.9.7 Page Table Setup and Debug

Keil’s linkers produce the page table automatically, once paging is selected in the Microvision options->target dialogue.

Keil usually places the page table at an address of 0x100 in the common bank. It is visible in the linker .m51 file. To

see how it works, one can use the emulator to single-step through at a banked function call at the assembly language

level.

To call a paged subroutine, Keil’s linker arranges to call one of the entries of the page table. The page table consists

of one entry per subroutine. Each entry is a small piece of code that loads the address of the banked subroutine into

the 8051 register DPTR, and then jumps to paging code. The paging code sets the bank register FL_BANK, and then

jumps to the banked code’s address contained in the DPTR.

v1.1v1.1 TERIDIAN Proprietary 37 of 116

© Copyright 2005-2008 TERIDIAN Semiconductor Corporation

Page 38

71M653X Software User’s Guide

Keil’s linkers minimize the size of the page table. A subroutine has an entry in the page table only if:

1. The subroutine is in a bank, and

2. The subroutine is called from outside its bank.

Most problems with banking code occur because the linker omits a function from the page table. The result is that the

call to a function in a different bank goes to code in the current bank, causing unexpected code in the current bank to

be executed.

One major cause of this is a callback subroutine called via a function pointer. Another is an interrupt defined in banked

assembly language file (fortunately, Keil detects and flags banked interrupts in C code).

To solve problems stemming from callback routines, all subroutines called from other banks should be made global, so

that the linker can use their data.

Next, overlay commands should be used to inform the Keil linker that a banked function is called from a caller in a

different bank. This forces the linker to put the callee function into the page table. To use the overlay command in the

linker, see the discussion of “overlay” in the Keil linker’s documentation. Here’s an example of the overlay commands

from the demo code. They map the callback routines that are called from the software timer, and hardware timer

interrupt 0.

Figure 4-3, Setting Keil’s Linker for Bank-switched Code

However, if there should be other problems, there is a way to isolate them:

1. Remove code from the project until all code fits in common and bank 1.

2. Move modules individually each to a bank until the problem occurs.

3. At some point, the problem is likely to show up as an unexpected reset. What is happening is that the call to

code in bank 1 is probably going to uninitialized code memory in another bank. It will execute until the