Page 1

General Description

The MXL1543B is a three-driver/three-receiver multiprotocol transceiver that operates from a +5V single supply. The MXL1543B, along with the MXL1544/MAX3175

and the MXL1344A, form a complete software-selectable data terminal equipment (DTE) or data communication equipment (DCE) interface port that supports the

V.28 (RS-232), V.10/V.11 (RS-449/V.36, EIA-530, EIA530A, X.21), and V.35 protocols. The MXL1543B transceivers carry the high-speed clock and data signals

while the MXL1544/MAX3175 carry the control signals.

The MXL1543B can be terminated by the MXL1344A

software-selectable resistor termination network or by

discrete termination networks.

An internal charge pump and a proprietary low-dropout

transmitter output stage allow V.11- , V.28- , and V.35compliant operation from a +5V single supply. A nocable mode is entered when all mode pins (M0, M1,

and M2) are pulled high or left unconnected. In nocable mode, supply current decreases to 0.5µA and all

transmitter and receiver outputs are disabled (high

impedance). Short-circuit current limiting and thermal

shutdown circuitry protect the drivers against excessive

power dissipation.

Applications

Features

♦ MXL1543B, MXL1544/MAX3175, and MXL1344A

Chipset Is Pin Compatible with LTC1543,

LTC1544, and LTC1344A

♦ Supports RS-232, RS-449, EIA-530, EIA-530A,

V.35, V.36, and X.21

♦ Software-Selectable Cable Termination Using the

MXL1344A

♦ Complete DTE or DCE Port with MXL1544/

MAX3175, and MXL1344A

♦ +5V Single-Supply Operation

♦ 0.5µA No-Cable Mode

♦ TUV-Certified NET1/NET2 and TBR1/TBR2-

Compliant

MXL1543B

+5V Multiprotocol, 3Tx/3Rx, Software-

Selectable Clock/Data Transceivers

________________________________________________________________ Maxim Integrated Products 1

Ordering Information

19-3444; Rev 0; 10/04

PART TEMP RANGE PIN-PACKAGE

MXL1543BCAI 0° to +70°C 28 SSOP

Data Networking

CSU and DSU

Data Routers

PCI Cards

Telecommunications

Equipment

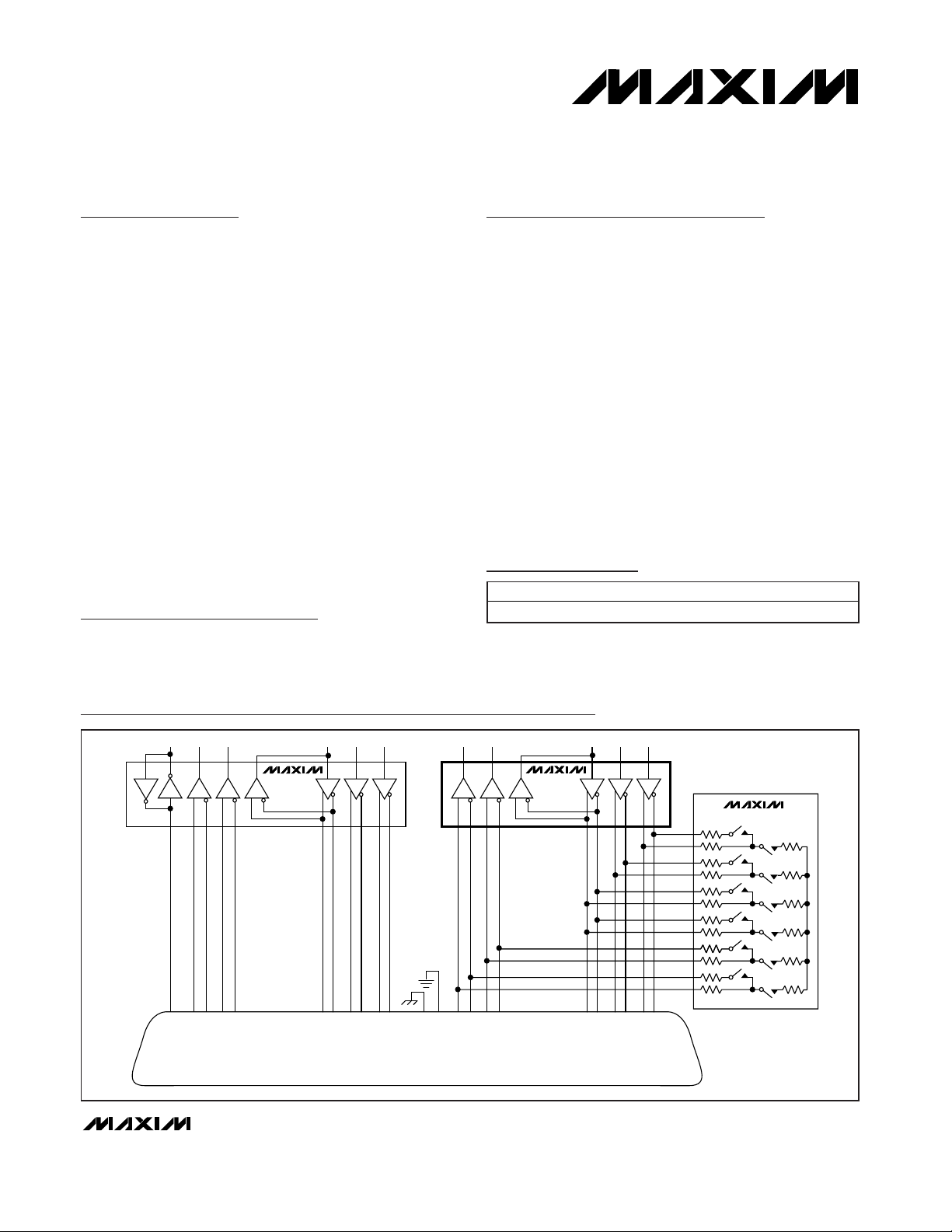

Typical Operating Circuit

D1D2

D3D4

R1

R2R3

MXL1543B

RXD RXC TXDTXC SCTE

D1D2

D3

R1

R2R3

MXL1544

MAX3175

CTS DSR RTSDTRDCD

RXC B

RXD A (104)

RXD B

SG (102)

SHIELD (101)

RTS A (105)

RTS B

DTR A (108)

DTR B

DCD A (107)

DCD B

DSR A (109)

CTS A (106)

DSR B

CTS B

LL A (141)

TXD B

SCTE A (113)

SCTE B

TXC A (114)

TXC B

TXD A (103)

DB-25 CONNECTOR

13

R4

LL

RXC A (115)

18 5 10 8 22 6 23 20 19 4 1 7 16 3 9 17 12 15 11 24 14 2

MXL1344A

Pin Configuration appears at end of data sheet.

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim’s website at www.maxim-ic.com.

Page 2

MXL1543B

+5V Multiprotocol, 3Tx/3Rx, SoftwareSelectable Clock/Data Transceivers

2 _______________________________________________________________________________________

ABSOLUTE MAXIMUM RATINGS

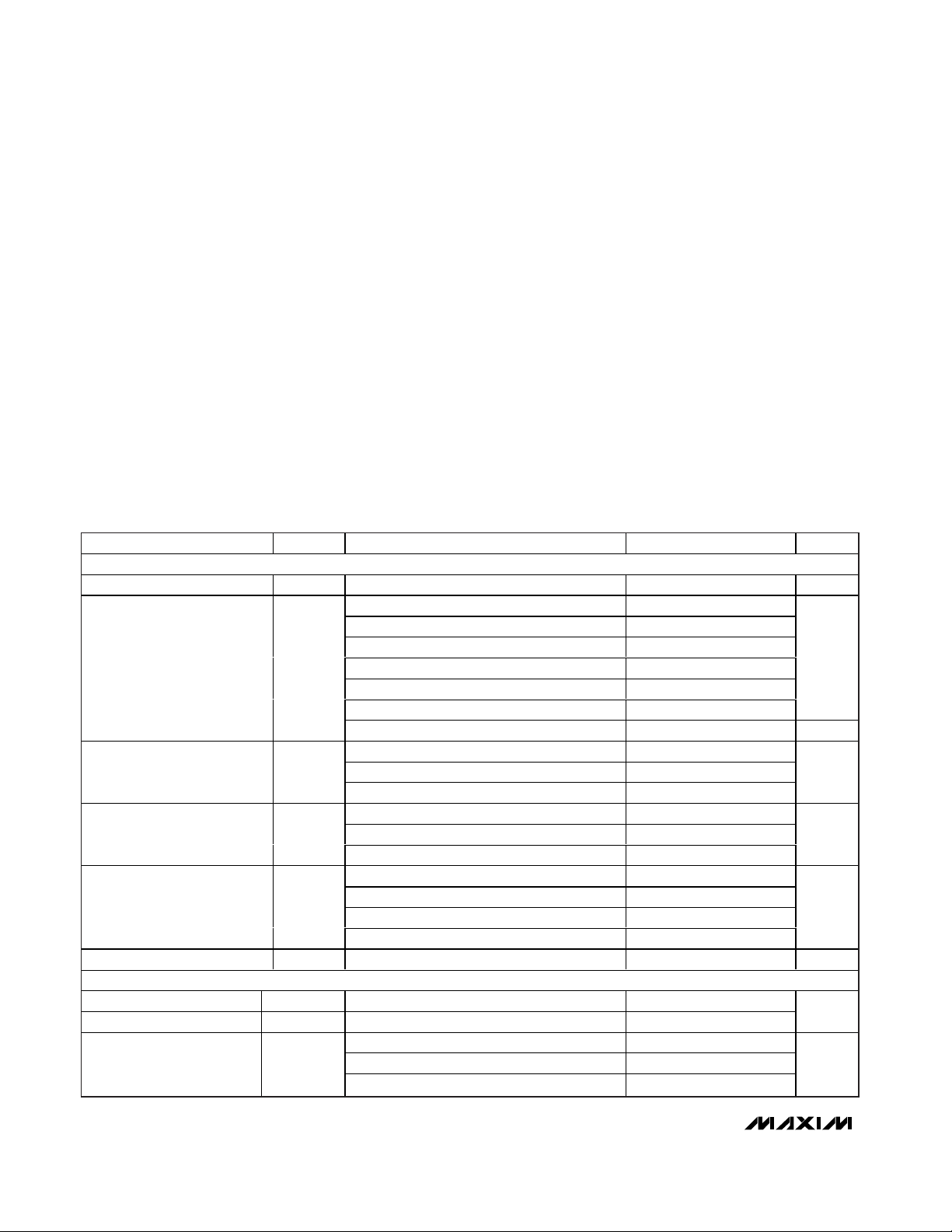

ELECTRICAL CHARACTERISTICS

(VCC= +5.0V, C1 = C2 = C4 = 1µF, C3 = C5 = 4.7µF, (Figure 10), TA = T

MIN

to T

MAX

. Typical values are at TA = +25°C, unless other-

wise noted.)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

All Voltages Referenced to GND Unless Otherwise Noted.

Supply Voltages

V

CC

.......................................................................-0.3V to +6V

V

DD

....................................................................-0.3V to +7.3V

V

EE

.....................................................................+0.3V to -6.5V

V

DD

to V

EE

(Note 1)................................................................13V

Logic Input Voltages

M0, M1, M2, DCE/

DTE, T_IN ................................-0.3V to +6V

Logic Output Voltages

R_OUT....................................................-0.3V to (V

CC

+ 0.3V)

Transmitter Outputs

T_OUT_, T3OUT_/R1IN_.....................................-15V to +15V

Short-Circuit Duration............................................Continuous

Receiver Input

R_IN_T3OUT_/R1IN_ ..........................................-15V to +15V

R_IN A to R_IN B..............................-15V to 0V or 0V to +15V

Continuous Power Dissipation (T

A

= +70°C)

28-Pin SSOP (derate 9.5mW/°C above +70°C) ...........762mW

Operating Temperature Range

MXL1543BCAI .....................................................0°C to 70°C

Junction Temperature .......................................................150°C

Storage Temperature Range ...........................-65°C to +150°C

Lead Temperature (soldering, 10s) ...............................+300°C

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

DC CHARACTERISTICS

V

CC

Operating Range V

CC

V

RS-530, RS-530A, X.21, no load 13

RS-530, RS-530A, X.21, full load 100 130

V.35 mode, no load 20

V.35 mode, full load 126 170

V.28 mode, no load 20

V.28 mode, full load 40 75

mA

Supply Current

(DCE Mode)

(Digital Inputs = GND or

V

CC

)

(Transmitter Outputs Static)

I

CC

No-cable mode 0.5 10 µA

RS-530, RS-530A, X.21, full load 230

V.35 mode, full load 600

Internal Power Dissipation

(DCE Mode)

P

D

V.28 mode, full load 140

mW

Any mode (except no-cable mode), no load 6.4 6.8

V.28 mode, with load 6.4 6.8

Positive Charge-Pump

Output Voltage

V

DD

V.28, V.35 modes, with load, IDD = 10mA 6.4 6.8

V

V.28, V.35, no load

V.28 mode, full load

-5.4

V.35 mode, full load

-5.4

Negative Charge-Pump

Output Voltage

V

EE

RS-530, RS-530A, X.21, full load

-5.4

V

Supply Rise Time t

r

No-cable mode or power-up to turn on 500 µs

LOGIC INPUTS (M0, M1, M2, DCE/DTE, T1IN, T2IN, T3IN)

Input High Voltage V

IH

2.0

Input Low Voltage V

IL

0.8

V

T1IN, T2IN, T3IN ±10

M0, M1, M2, DCE/DTE = GND

-50 -30

Logic Input Current I

IN

M0, M1, M2, DCE/DTE = V

CC

±10

µA

Note 1: VDDand VEEabsolute difference cannot exceed 13V.

4.75 5.25

-100

-5.6

-5.6

-5.6

-5.6

Page 3

MXL1543B

+5V Multiprotocol, 3Tx/3Rx, Software-

Selectable Clock/Data Transceivers

_______________________________________________________________________________________ 3

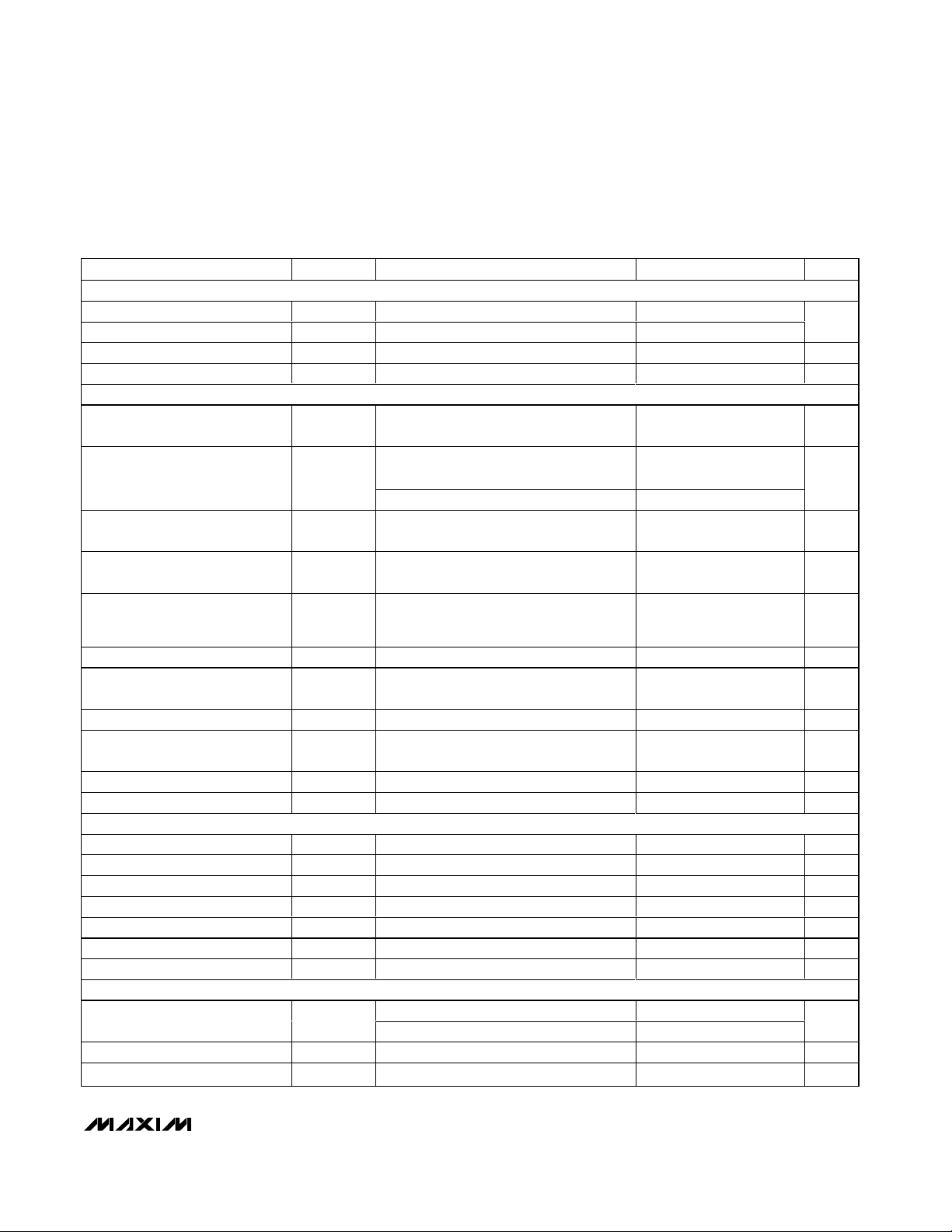

ELECTRICAL CHARACTERISTICS (continued)

(VCC= +5.0V, C1 = C2 = C4 = 1µF, C3 = C5 = 4.7µF, (Figure 10), TA= T

MIN

to T

MAX

. Typical values are at TA = +25°C, unless oth-

erwise noted.)

PARAMETER

CONDITIONS

UNITS

LOGIC OUTPUTS (R1OUT, R2OUT, R3OUT)

Output High Voltage V

OH

I

SOURCE

= 4mA 3 4.5

Output Low Voltage V

OL

I

SINK

= 4mA 0.3 0.8

V

Output Short-Circuit Current I

SC

0 ≤ V

OUT

≤ V

CC

±50 mA

Output Pullup Current I

L

V

OUT

= 0, no-cable mode 70 µA

V.11 TRANSMITTER

Open-Circuit Differential Output

Voltage

V

ODO

Open circuit, R = 1.95kΩ (Figure 1) ±5V

R = 50Ω (Figure 1), TA = +25oC

0.67

✕

Loaded Differential Output

Voltage

V

ODL

R = 50Ω (Figure 1) ±2

V

Change in Magnitude of Output

Differential Voltage

∆V

OD

R = 50Ω (Figure 1) 0.2 V

Common-Mode Output Voltage V

OC

R = 50Ω (Figure 1) 3.0 V

Change in Magnitude of Output

Common-Mode Voltage

∆V

OC

R = 50Ω (Figure 1) 0.2 V

Short-Circuit Current I

SC

V

OUT

= GND 150 mA

Output Leakage Current I

Z

-0.25V ≤ V

OUT

≤ +0.25V, power-off or

no-cable mode

±1

µA

Rise or Fall Time t

r

,

t

f

(Figures 2, 6) 2 10 25 ns

Transmitter Input to Output

Delay

(Figures 2, 6) 40 80 ns

Data Skew

(Figures 2, 6) 2 12 ns

Output to Output Skew t

SKEW

(Figures 2, 6) 3 ns

V.11 RECEIVER

Differential Threshold Voltage V

TH

-7V ≤ VCM ≤ 7V

200 mV

Input Hysteresis ∆V

TH

-7V ≤ VCM ≤ 7V 15 40 mV

Receiver Input Current I

IN

-10V ≤ V

A, B

≤10V

mA

Receiver Input Resistance R

IN

-10V ≤ V

A, B

≤ 10V 15 30 kΩ

Rise or Fall Time tr, t

f

(Figures 2, 7) 15 ns

Receiver Input to Output Delay

(Figures 2, 7) 50 80 ns

Data Skew

(Figures 2, 7) 2 16 ns

V.35 TRANSMITTER

Open circuit (Figure 3) ±7

Differential Output Voltage V

OD

With load, -4V ≤ VCM ≤ 4V (Figure 3)

V

Output High Current I

OH

V

A,B

= 0 -13 -11 -9 mA

Output Low Current I

OL

V

A,B

= 0 9 11 13 mA

SYMBOL

MIN TYP MAX

0.5

V

✕

ODO

V

ODO

±100

t

t

PHL

PLH

,

It

- t

PHL

I

PLH

-200

±0.66

t

PHL,tPLH

|t

- t

PLH

|

PHL

±0.44 ±0.55 ±0.66

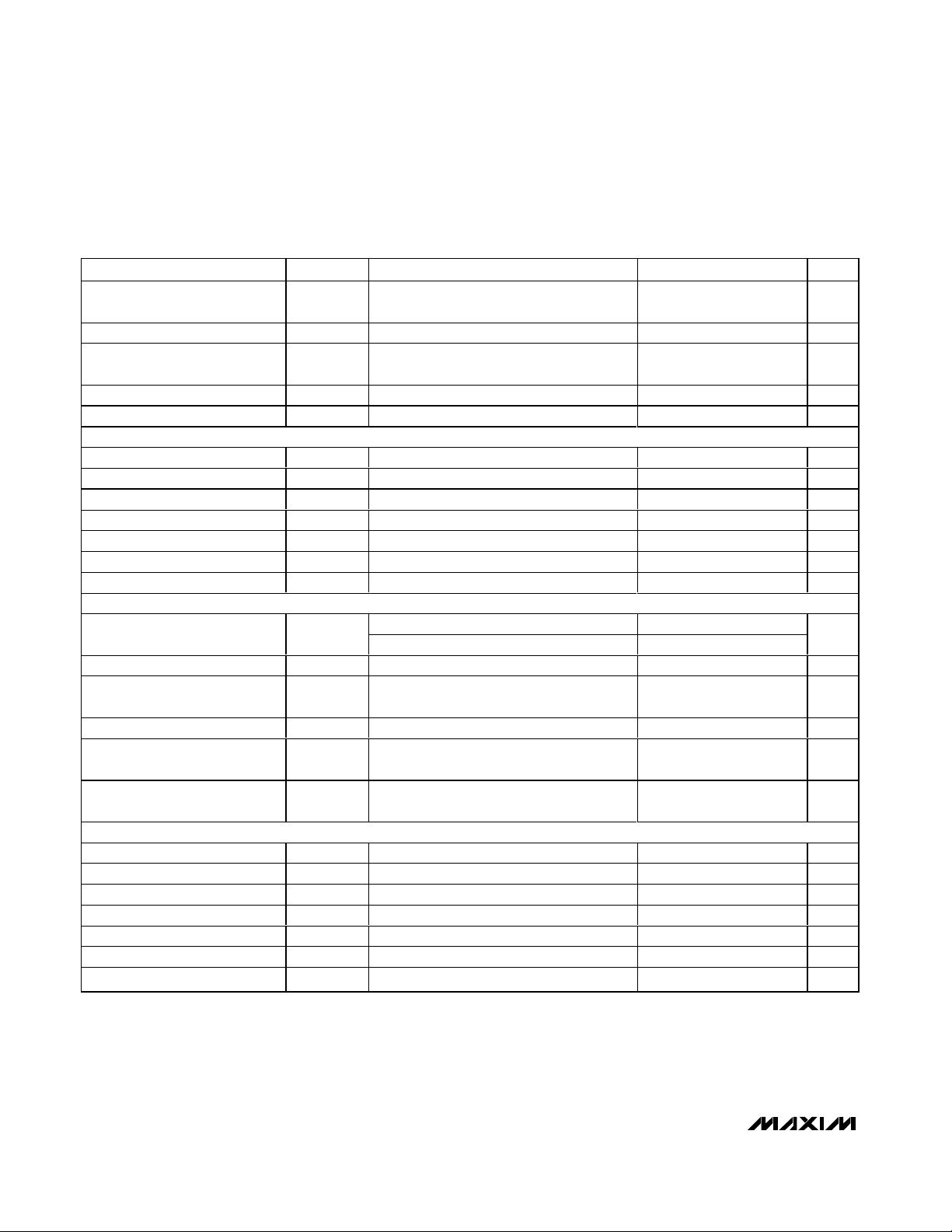

Page 4

MXL1543B

+5V Multiprotocol, 3Tx/3Rx, SoftwareSelectable Clock/Data Transceivers

4 _______________________________________________________________________________________

PARAMETER

CONDITIONS

UNITS

Output Leakage Current I

Z

-0.25V ≤ V

OUT

≤ +0.25V, power-off or no-

cable mode

±1

µA

Rise or Fall Time tr, t

f

(Figures 3, 6) 5 ns

Transmitter Input to Output

Delay

,

(Figures 3, 6) 35 80 ns

Data Skew

(Figures 3, 6) 2 16 ns

Output-to-Output Skew t

SKEW

(Figures 3, 6) 4 ns

V.35 RECEIVER

Differential Input Voltage V

TH

-2V ≤ VCM ≤ 2V (Figure 3)

200 mV

Input Hysteresis ∆V

TH

-2V ≤ VCM ≤ 2V (Figure 3) 15 40 mV

Receiver Input Current I

IN

-10V ≤ VA,B ≤ 10V

mA

Receiver Input Resistance R

IN

-10V ≤ VA,B ≤ 10V 15 30 kΩ

Rise or Fall Time tr, t

f

(Figures 3, 7) 15 ns

Receiver Input to Output Delay

(Figures 3, 7) 50 80 ns

Data Skew

(Figures 3, 7) 2 16 ns

V.28 TRANSMITTER

Open circuit ±7

Output Voltage Swing (Figure 4)

V

O

RL = 3kΩ±5 ±6

V

Short-Circuit Current I

SC

mA

Output Leakage Current I

Z

-0.25V ≤ V

OUT

≤ +0.25V, power-off or no-

cable mode

±1

µA

Output Slew Rate SR RL = 3kΩ, CL = 2500pF (Figures 4, 8) 4 30

V/µs

Transmitter Input to Output

Delay

t

PHL

RL = 3kΩ, CL = 2500pF (Figures 4, 8) 1.5 2.5 µs

Transmitter Input to Output

Delay

t

PLH

RL = 3kΩ, CL = 2500pF (Figures 4, 8) 1.5 3 µs

V.28 RECEIVER

Input Threshold Low V

IL

0.8 1.2 V

Input Threshold High V

IH

1.2 2.0 V

Input Hysteresis V

HYST

0.3 V

Input Resistance R

IN

-15V ≤ VIN ≤ +15V 3 5 7 kΩ

Rise or Fall Time tr, t

f

(Figures 5, 9) 15 ns

Receiver Input to Output Delay t

PHL

(Figures 5, 9) 60 100 ns

Receiver Input to Output Delay t

PLH

(Figures 5, 9) 160 250 ns

ELECTRICAL CHARACTERISTICS (continued)

(VCC= +5.0V, C1 = C2 = C4 = 1µF, C3 = C5 = 4.7µF, (Figure 10), TA= T

MIN

to T

MAX

. Typical values are at TA = +25°C, unless oth-

erwise noted.)

SYMBOL

t

t

PHL

PLH

|t

PHL–tPLH

|

MIN TYP MAX

±100

-200

t

, t

PHL

PLH

|t

PHL–tPLH

|

0.05

±0.66

±150

±100

Page 5

MXL1543B

+5V Multiprotocol, 3Tx/3Rx, Software-

Selectable Clock/Data Transceivers

_______________________________________________________________________________________ 5

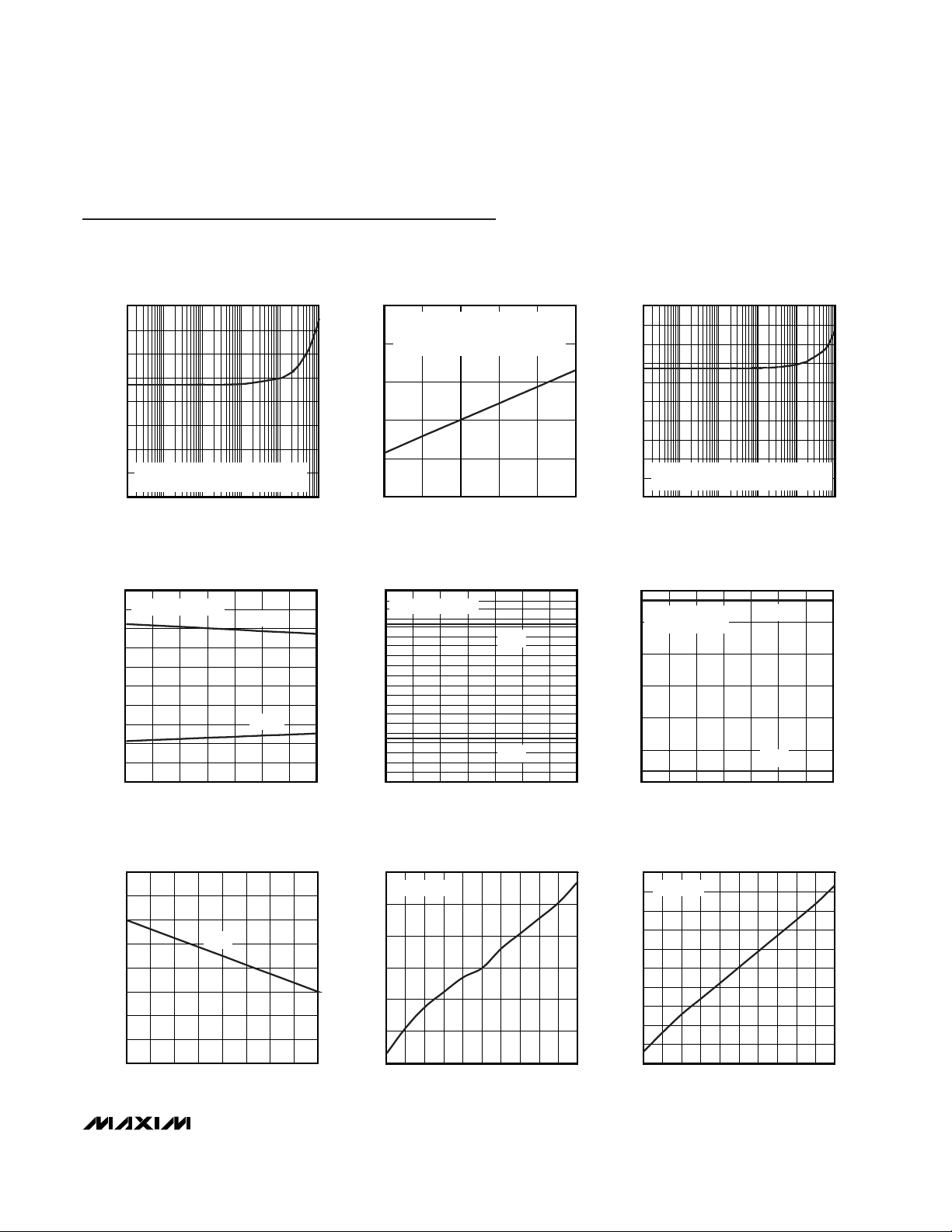

160

0

0.1 100 1000

V.11 SUPPLY CURRENT

vs. DATA RATE

40

20

60

80

100

120

140

MXL1543B toc01

DATA RATE (kbps)

SUPPLY CURRENT (mA)

10110,000

DCE MODE, R = 50Ω, ALL TRANSMITTERS

OPERATING AT THE SPECIFIED DATA RATE

0

20

60

40

80

100

010050 150 200 250

V.28 SUPPLY CURRENT

vs. DATA RATE

MXL1543B toc02

DATA RATE (kbps)

SUPPLY CURRENT (mA)

DCE MODE ALL TRANSMITTERS

OPERATING AT THE SPECIFIED DATA RATE

R

L

= 3kΩ, CL = 2500pF

160

0

0.1 100 1000

V.35 SUPPLY CURRENT

vs. DATA RATE

40

20

60

80

100

120

140

MXL1543B toc03

DATA RATE (kbps)

SUPPLY CURRENT (mA)

100.1 10,000

DCE MODE, FULL LOAD, ALL TRANSMITTERS

OPERATING AT THE SPECIFIED DATA RATE

180

200

-5

-2

-3

-4

0

-1

4

3

2

1

5

010203040506070

V.11 DRIVER DIFFERENTIAL OUTPUT

VOLTAGE vs. TEMPERATURE

MXL1543B toc04

TEMPERATURE (°C)

DRIVER DIFFERENTIAL OUTPUT VOLTAGE (V)

DCE MODE, R = 50

Ω

V

OUT+

V

OUT-

8

V.28 OUTPUT VOLTAGE

vs. TEMPERATURE

MXL1543B toc05

TEMPERATURE (°C)

OUTPUT VOLTAGE (V)

0304010 20 50 60 70

10

4

6

0

2

-4

-2

-8

-6

-10

DCE MODE, RL = 3k

Ω

V

OUT+

V

OUT-

-0.66

-0.22

-0.44

0.22

0

0.44

0.66

0304010 20 50 60 70

OUTPUT VOLTAGE (V)

V.35 OUTPUT VOLTAGE

vs. TEMPERATURE

MXL1543B toc06

TEMPERATURE (°C)

DCE MODE, VCM = 0

FULL LOAD

V

OL

V

OH

520

540

530

560

550

570

580

590

600

-4 -2 -1-3 01234

V.35 DIFFERENTIAL OUTPUT VOLTAGE

vs. COMMON-MODE VOLTAGE

MXL1543B toc07

COMMON-MODE VOLTAGE (V)

DIFFERENTIAL OUTPUT VOLTAGE (mV)

|VOD|

-300

0

-100

-200

100

200

300

-10 -2-4-8 -6 0246810

V.11/V.35 RECEIVER INPUT CURRENT

vs. INPUT VOLTAGE

MXL1543B toc08

INPUT VOLTAGE (V)

RECEIVER INPUT CURRENT (

µ

A)

DCE MODE

-0.5

1.0

0.5

0

1.5

2.0

2.5

-10 -2-4-8 -6 0246810

V.28 RECEIVER INPUT CURRENT

vs. INPUT VOLTAGE

MXL1543B toc09

INPUT VOLTAGE (V)

RECEIVER INPUT CURRENT (mA)

DCE MODE

-2.0

-2.5

-1.5

-1.0

Typical Operating Characteristics

(VCC= +5.0V, C1 = C2 = C4 =1µF, C3 = C5 = 4.7µF, (Figure 10), TA= T

MIN

to T

MAX

, TA = +25°C, unless otherwise noted.)

Page 6

MXL1543B

+5V Multiprotocol, 3Tx/3Rx, SoftwareSelectable Clock/Data Transceivers

6 _______________________________________________________________________________________

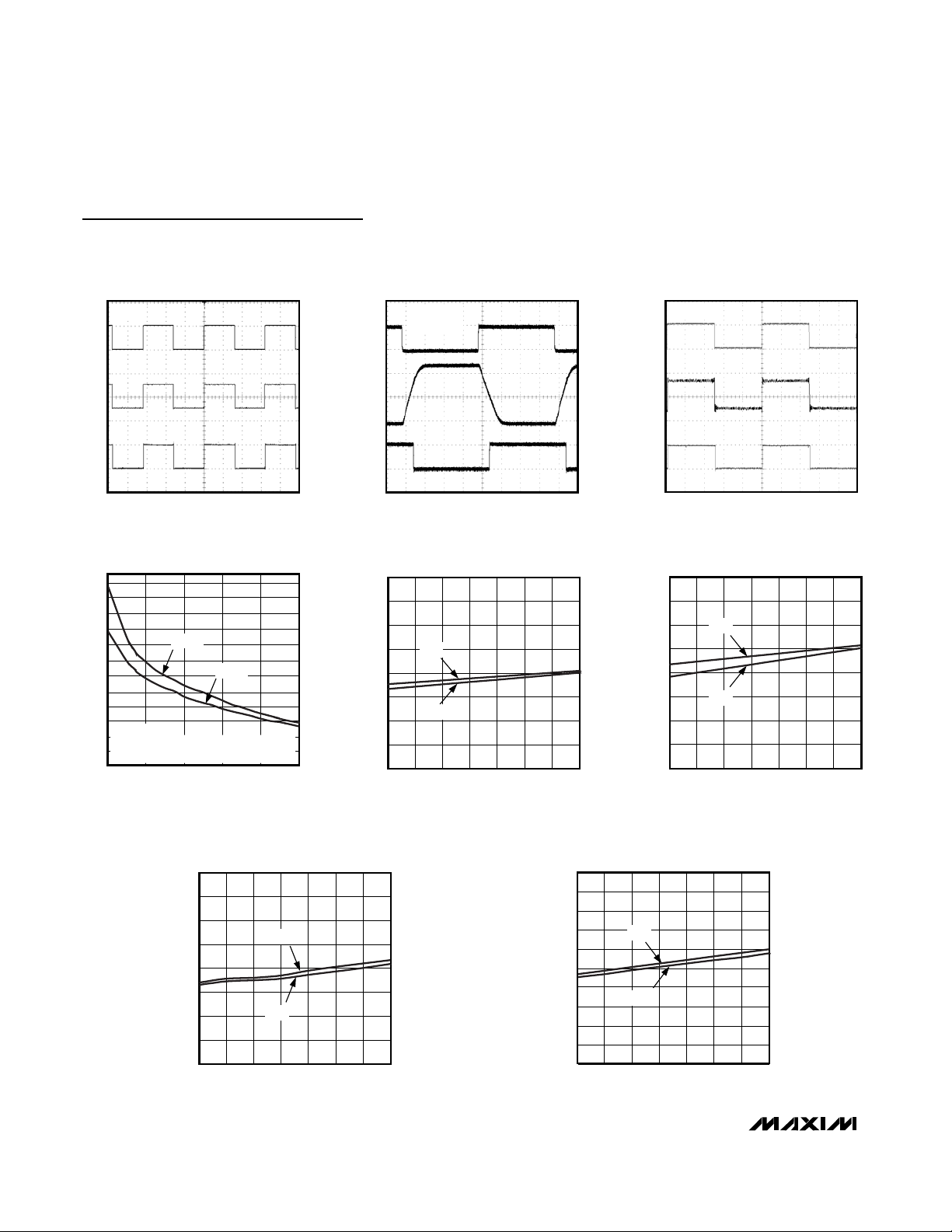

200ns/div

V.11 LOOPBACK OPERATION

T

IN

T

OUT/RIN

R

OUT

5V/div

5V/div

5V/div

MXL1543B toc10

R = 50

Ω

1µs/div

V.28 LOOPBACK OPERATION

T

IN

T

OUT/RIN

R

OUT

5V/div

5V/div

5V/div

MXL1543B toc11

CL = 2500pF

RL = 3k

Ω

V.11 TRANSMITTER PROPAGATION DELAY

vs. TEMPERATURE

MXL1543B toc14

0

10

30

20

60

70

50

40

80

PROPAGATION DELAY (ns)

0203010

40

50 60 70

TEMPERATURE (°C)

t

PLH

t

PHL

V.11 RECEIVER PROPAGATION DELAY

vs. TEMPERATURE

MXL1543B toc15

0

10

30

20

60

70

50

40

80

PROPAGATION DELAY (ns)

0203010

40

50 60 70

TEMPERATURE (°C)

t

PLH

t

PHL

V.35 TRANSMITTER PROPAGATION DELAY

vs. TEMPERATURE

MXL1543B toc16

0

10

30

20

60

70

50

40

80

PROPAGATION DELAY (ns)

0203010

40

50 60 70

TEMPERATURE (°C)

t

PLH

t

PHL

V.35 RECEIVER PROPAGATION DELAY

vs. TEMPERATURE

MXL1543B toc17

0

10

30

20

60

70

50

40

80

PROPAGATION DELAY (ns)

0203010

40

50 60 70

TEMPERATURE (°C)

90

100

t

PHL

t

PLH

200ns/div

V.35 LOOPBACK OPERATION

T

IN

T

OUT/RIN

R

OUT

1V/div

5V/div

5V/div

MXL1543B toc12

FULL LOAD

0

4

2

6

8

10

12

14

16

18

20

22

24

0 1000 2000 3000 4000 5000

V.28 SLEW RATE vs. C

LOAD

MXL1543B toc13

C

LOAD

(pF)

SLEW RATE (V/µs)

+SLEW

-SLEW

RL = 3k

Ω

1 TRANSMITTER SWITCHING AT 250kbps.

OTHER TRANSMITTERS SWITCHING AT 15kbps

Typical Operating Characteristics (continued)

(VCC= +5.0V, C1= C2 = C4 =1µF, C3 = C5 = 4.7µF (Figure 10), TA = +25°C, unless otherwise noted.)

Page 7

MXL1543B

+5V Multiprotocol, 3Tx/3Rx, Software-

Selectable Clock/Data Transceivers

_______________________________________________________________________________________ 7

V

OC

R

R

V

OD

Figure 1. V.11 DC Test Circuit

C

L

R

L

V

O

A

D

Figure 4. V.28 Driver Test Circuit

D

A

R

15pF

Figure 5. V.28 Receiver Test Circuit

100pF

15pF

100pF

100

Ω

R

B

A

B

A

D

Figure 2. V.11 AC Test Circuit

V

CM

15pF

50

Ω

50

Ω

125

Ω

125

Ω

50

Ω

50

Ω

R

B

A

B

A

D

V

OD

Figure 3. V.35 Transmitter/Receiver Test Circuit

Test Circuits

Page 8

MXL1543B

+5V Multiprotocol, 3Tx/3Rx, SoftwareSelectable Clock/Data Transceivers

8 _______________________________________________________________________________________

f = 1MHz: tr ≤10ns: tf ≤ 10ns

V

DIFF

= V(A) - V(B)

1.5V

1/2 V

0

V

0

90%

10%

50%

t

PLH

5V

0

V

0

-V

0

D

A

B

B — A

t

r

t

SKEW

1.5V

t

PHL

t

SKEW

90%

10%

50%

t

f

Figure 6. V.11, V.35 Driver Propagation Delays

V

0

-V

0

V

0H

V

0L

B — A

R

0

INPUT

OUTPUT

0

1.5V

f = 1MHz: tr ≤10ns: tf ≤ 10ns

t

PLH

1.5V

t

PHL

Figure 7. V.11, V.35 Receiver Propagation Delays

1.5V

0

t

PHL

3V

0

V

0

-V

0

D

A

-3V

3V

t

r

1.5V

0

t

PLH

3V

-3V

t

r

Figure 8. V.28 Driver Propagation Delays

V

IH

V

IL

V

0H

V

0L

A

R

1.3V

t

PHL

0.8V

1.7V

t

PLH

2.4V

Figure 9. V.28 Receiver Propagation Delays

Timing Diagrams

Page 9

Detailed Description

The MXL1543B is a three-driver/three-receiver, multiprotocol transceiver that operates from a single +5V supply.

The MXL1543B, along with the MXL1544/MAX3175 and

MXL1344A, form a complete software-selectable DTE or

DCE interface port that supports the V.28 (RS-232),

V.10/V.11 (RS-449/V.36, EIA-530, EIA-530A, X.21), and

V.35 protocols. The MXL1543B transceivers carry the

high-speed clock and data signals, while the

MXL1544/MAX3175 transceivers carry serial interface

control signaling. The MXL1543B can be terminated by

the MXL1344A software-selectable resistor termination

network or by a discrete termination network. The

MXL1543B features a 0.5µA no-cable mode, true fail-safe

operation, and thermal shutdown circuitry. Thermal shutdown protects the drivers against excessive power dissipation. When activated, the thermal shutdown circuitry

places the driver outputs into a high-impedance state.

Mode Selection

The state of the mode-select pins M0, M1, and M2

determines which serial interface protocol is selected

(Table 1). The state of the DCE/DTE input determines

whether the transceiver will be configured as a DTE or

DCE serial port. When the DCE/DTE input is logic

HIGH, driver T3 is activated and receiver R1 is disabled. When the DCE/DTE input is logic LOW, driver T3

is disabled and receiver R1 is activated. M0, M1, M2,

MXL1543B

+5V Multiprotocol, 3Tx/3Rx, Software-

Selectable Clock/Data Transceivers

_______________________________________________________________________________________ 9

Pin Description

PIN NAME FUNCTION

1 C1- Capacitor C1 Negative Terminal. Connect a 1µF ceramic capacitor between C1+ and C1-.

2 C1+ Capacitor C1 Positive Terminal. Connect a 1µF ceramic capacitor between C1+ and C1-.

3VDDGenerated Positive Supply. Connect a 4.7µF ceramic capacitor to ground.

4VCC+5V Supply Voltage (±5%). Decouple with a 1µF capacitor to ground.

5 T1IN Transmitter 1 TTL-Compatible Input

6 T2IN Transmitter 2 TTL-Compatible Input

7 T3IN Transmitter 3 TTL-Compatible Input

8 R1OUT Receiver 1 CMOS Output

9 R2OUT Receiver 2 CMOS Output

10 R3OUT Receiver 3 CMOS Output

11 M0 Mode-Select Pin with Internal Pullup to V

CC

12 M1 Mode-Select Pin with Internal Pullup to V

CC

13 M2 Mode-Select Pin with Internal Pullup to V

CC

14 DCE/DTE DCE/DTE Mode-Select Pin with Internal Pullup to V

CC

15 R3INB Noninverting Receiver Input

16 R3INA Inverting Receiver Input

17 R2INB Noninverting Receiver Input

18 R2INA Inverting Receiver Input

19

Noninverting Transmitter Output/Noninverting Receiver Input

20

Inverting Transmitter Output/Inverting Receiver Input

21 T2OUTB Noninverting Transmitter Output

22 T2OUTA Inverting Transmitter Output

23 T1OUTB Noninverting Transmitter Output

24 T1OUTA Inverting Transmitter Output

25 GND Ground

26 V

EE

Generated Negative Supply. Connect a 4.7µF ceramic capacitor to ground.

27 C2- Capacitor C2 Negative Terminal. Connect a 1µF ceramic capacitor between C2+ and C2-.

28 C2+ Capacitor C2 Positive Terminal. Connect a 1µF ceramic capacitor between C2+ and C2-.

T3OUTB/R1INB

T3OUTA/R1INA

Page 10

MXL1543B

and DCE/DTE are internally pulled up to VCCto ensure

a logic HIGH if left unconnected.

No-Cable Mode

The MXL1543B will enter no-cable mode when the

mode-select pins are left unconnected or connected

high (M0 = M1 = M2 = 1). In this mode, the multiprotocol drivers and receivers are disabled and the supply

current drops to 0.5µA. The receivers’ outputs enter a

high-impedance state in no-cable mode, which allow

these output lines to be shared with other receivers’

outputs (the receivers’ outputs have internal pullup

resistors to pull the outputs HIGH if not driven). Also, in

no-cable mode, the transmitter outputs enter a highimpedance state so that these output lines can be

shared with other devices.

Dual Charge-Pump Voltage Converter

The MXL1543B’s internal power supply consists of a

regulated dual charge pump that provides positive and

negative output voltages from a +5V supply. The

charge pump operates in discontinuous mode. If the

output voltage is less than the regulated voltage, the

charge pump is enabled. If the output voltage exceeds

the regulated voltage, the charge pump is disabled.

Each charge pump requires a flying capacitor (C1, C2)

and a reservoir capacitor (C3, C5) to generate the V

DD

and VEEsupplies. Figure 10 shows charge-pump connections.

Fail-Safe Receivers

The MXL1543B guarantees a logic-high receiver output

when the receiver inputs are shorted or open, or when

they are connected to a terminated transmission line

with all the drivers disabled. This is done by setting the

receivers’ threshold between -25mV and -200mV in the

V.11 and V.35 modes. If the differential receiver input

+5V Multiprotocol, 3Tx/3Rx, SoftwareSelectable Clock/Data Transceivers

10 ______________________________________________________________________________________

MXL1543B

MODE NAME

M2 M1 M0

DCE/

DTE

T1 T2 T3 R1 R2 R3

Not Used (Default V.11)

0000V.11V.11 Z V.11 V.11 V.11

RS-530A 0 0 1 0 V.11 V.11 Z V.11 V.11 V.11

RS-530 0 1 0 0 V.11 V.11 Z V.11 V.11 V.11

X.21 0 1 1 0 V.11 V.11 Z V.11 V.11 V.11

V.35 1 0 0 0 V.35 V.35 Z V.35 V.35 V.35

RS-449/V.36 1 0 1 0 V.11 V.11 Z V.11 V.11 V.11

V.28/RS-232 1 1 0 0 V.28 V.28 Z V.28 V.28 V.28

No Cable 1 1 1 0 Z Z Z Z Z Z

Not Used (Default V.11)

0001V.11V.11 V.11 Z V.11 V.11

RS-530A 0 0 1 1 V.11 V.11 V.11 Z V.11 V.11

RS-530 0 1 0 1 V.11 V.11 V.11 Z V.11 V.11

X.21 0 1 1 1 V.11 V.11 V.11 Z V.11 V.11

V.35 1 0 0 1 V.35 V.35 V.35 Z V.35 V.35

RS-449/V.36 1 0 1 1 V.11 V.11 V.11 Z V.11 V.11

V.28/RS-232 1 1 0 1 V.28 V.28 V.28 Z V.28 V.28

No Cable 1 1 1 1 Z Z Z Z Z Z

Table 1. Mode Selection

C2-

V

EE

C2+

MXL1543B

GND

C1-

5V

V

CC

V

DD

C1+

C1

1µF

C5

4.7µF

C2

1µF

C3

4.7µF

C4

1µF

Figure 10. Charge Pump

Page 11

MXL1543B

+5V Multiprotocol, 3Tx/3Rx, Software-

Selectable Clock/Data Transceivers

______________________________________________________________________________________ 11

CTS A

4

25

21

18

2

14

24

11

15

12

17

9

3

16

7

19

20

23

8

10

6

22

5

13

CTS B

DSR A

DSR B

DCD A

DCD B

DTR A

DTR B

RTS A

RTS B

RXD A

RXD B

RXC A

RXC B

TXC A

TXC B

SCTE A

SCTE B

TXD A

TXD B

CHARGE

PUMP

DTE

DCE

RTS A

RTS B

DTR A

DTR B

DCD A

DCD B

DSR A

DSR B

CTS A

CTS B

TXD A

TXD B

SCTE A

SCTE B

TXC A

TXC B

RXC A

RXC B

RXD A

RXD B

SG

M2

C12

1µF

C13

1µF

C5

4.7µF

C2

1µF

C1

1µF

C4

1µF

C3

4.7µF

2

21

D1

D2

D3

R1

R2

R3

28

27

26

25

24

23

22

21

20

19

18

17

16

15

3

V

CC

5V

1

2

4

5

6

7

8

9

10

11

12

13

14

14

3

4679101615 18 17 19 20 22 23 24 15

8111213

C6

100pFC7100pFC8100pF

M1

M0

DCE/DTE

M1

M2

DCE/DTE

M0

V

CC

V

CC

V

CC

V

EE

V

EE

V

CC

V

DD

GND

LATCH

MXL1344A

MXL1543B

D1

D2

D3

D4

R1

R2

R3

26

27

28

25

24

23

22

21

20

19

18

17

5

6

7

8

9

4

3

1

2

R4

16

15

10

11

12

13

NC

NC

14

M1

M2

DCE/DTE INVERT

M0

DB-25

CONNECTOR

MXL1544

MAX3175

C11

1µF

C10

1µF

C9

1µF

1

SHIELD

DTE_TXD/DCE_RXD

DTE_SCTE/DCE_RXC

DTE_TXC/DCE_TXC

DTE_RXC/DCE_SCTE

DTE_RXD/DCE_TXD

DTE_RTS/DCE_CTS

DTE_DTR/DCE_DSR

DTE_DCD/DCE_DCD

DTE_DSR/DCE_DTR

DTE_CTS/DCE_RTS

M1

DCE/DTE

M0

Figure 11. Cable-Selectable Multiprotocol DTE/DCE Port

Page 12

MXL1543B

+5V Multiprotocol, 3Tx/3Rx, SoftwareSelectable Clock/Data Transceivers

12 ______________________________________________________________________________________

voltage (B - A) is ≥ -25mV, R_OUT is logic HIGH. If (B A) is ≤ -200mV, R_OUT is logic LOW. In the case of a

terminated bus with all transmitters disabled, the

receiver’s differential input voltage is pulled to zero by

the termination. With the receiver thresholds of the

MXL1543B, this results in a logic HIGH with a 25mV

minimum noise margin.

Applications Information

Capacitor Selection

The capacitors used for the charge pumps, as well as

for supply bypassing, should have a low equivalent

series resistance (ESR) and low temperature coefficient. Multilayer ceramic capacitors with an X7R dielectric offer the best combination of performance, size,

and cost. The flying capacitors (C1, C2) and the

bypass capacitor (C4) should have a value of 1µF,

while the reservoir capacitors (C3, C5) should have a

minimum value of 4.7µF (Figure 10). To reduce the ripple present on the transmitter outputs, capacitors C3,

C4, and C5 can be increased. The values of C1 and C2

should not be increased.

Cable Termination

The MXL1344A software-selectable resistor network is

designed to be used with the MXL1543B. The

MXL1344A multiprotocol termination network provides

V.11- and V.35-compliant termination, while V.28

receiver termination is internal to the MXL1543B. These

cable termination networks provide compatibility with

V.11, V.28, and V.35 protocols. Using the MXL1344A

termination networks provide the advantage of not having to build expensive termination networks out of resistors and relays, manually changing termination

modules, or building custom termination networks

Cable-Selectable Mode

A cable-selectable multiprotocol interface is shown in

Figure 11. The mode control lines M0, M1, and

DCE/DTE are wired to the DB-25 connector. To select

the serial interface mode, the appropriate combination

of M0, M1, and DCE/DTE are grounded within the cable

wiring. The control lines that are not grounded are

pulled high by the internal pullups on the MXL1543B.

The serial interface protocol of the MXL1543B,

MXL1544/MAX3175, and MXL1344A is selected based

on the cable that is connected to the DB-25 interface.

V.11 Interface

As shown in Figure 12, the V.11 protocol is a fully balanced differential interface. The V.11 driver generates a

minimum of ±2V between nodes A and B when a 100Ω

(min) resistance is presented at the load. The V.11

receiver is sensitive to ±200mV differential signals at

receiver inputs A’ and B’. The V.11 receiver rejects

common-mode signals developed across the cable

(referenced from C to C’) of up to ±7V, allowing for

error-free reception in noisy environments. The receiver

inputs must comply with the impedance curve shown in

Figure 13.

For high-speed data transmission, the V.11 specification recommends terminating the cable at the receiver

with a 100Ω resistor. This resistor, although not

required, prevents reflections from corrupting transmitted data. In Figure 14, the MXL1344A is used to terminate the V.11 receiver. Internal to the MXL1344A, S1 is

closed and S2 is open to present a 100Ω minimum differential resistance. The MXL1543B’s internal V.28 termination is disabled by opening S3.

V.35 Interface

Figure 15 shows a fully-balanced, differential standard

V.35 interface. The generator and the load must both

present a 100Ω ±10Ω differential impedance and a

150Ω ±15Ω common-mode impedance as shown by

the resistive T networks in Figure 15. The V.35 driver

generates a current output (±11mA, typ) that develops

an output voltage of ±550mV across the generator and

load termination networks. The V.35 receiver is sensitive to ±200mV differential signals at receiver inputs A’

and B’. The V.35 receiver rejects common-mode sig-

100

Ω

MIN

A

′

B

′

C

′

A

B

C

GND GND

GENERATOR

BALANCED

INTERCONNECTING

CABLE

CABLE

TERMINATION

RECEIVER

LOAD

Figure 12. Typical V.11 Interface

-3.25mA

3.25mA

-10V

+10V

-3V

+3V

V

Z

I

Z

Figure 13. Receiver Input Impedance

Page 13

MXL1543B

+5V Multiprotocol, 3Tx/3Rx, Software-

Selectable Clock/Data Transceivers

______________________________________________________________________________________ 13

R6

12kΩ

R8

5kΩ

R3

124Ω

R2

52Ω

R1

52Ω

A′

B′

C′

A

B

GND

R5

12kΩ

R7

12kΩ

R4

12kΩ

MXL1344A

MXL1543B

S3

S2

S1

RECEIVER

Figure 16. V.35 Termination and Internal Resistance Networks

R6

12kΩ

R8

5kΩ

R3

124Ω

R2

52Ω

R1

52Ω

A′

B′

C′

A

B

GND

R5

12kΩ

R7

12kΩ

R4

12kΩ

MXL1344A

MXL1543B

S3

S1

RECEIVER

S2

Figure 14. V.11 Termination and Internal Resistance Networks

50Ω

50Ω

125Ω

50Ω

50Ω

125Ω

A′

B′

C′

A

B

C

GND GND

GENERATOR

BALANCED

INTERCONNECTING

CABLE

CABLE

TERMINATION

RECEIVER

LOAD

Figure 15. Typical V.35 Interface

Page 14

MXL1543B

+5V Multiprotocol, 3Tx/3Rx, SoftwareSelectable Clock/Data Transceivers

14 ______________________________________________________________________________________

Figure 17. Typical V.28 Interface

A

′

C

′

A

C

GND GND

GENERATOR

UNBALANCED

INTERCONNECTING

CABLE

CABLE

TERMINATION

RECEIVER

LOAD

Figure 18. V.28 Termination and Internal Resistance Networks

nals developed across the cable (referenced from C to

C’) of up to ±4V, allowing for error-free reception in

noisy environments.

In Figure 16, the MXL1344A is used to implement the

resistive T network that is needed to properly terminate

the V.35 driver and receiver. Internal to the MXL1344A,

S1 and S2 are closed to connect the T-network resistors to the circuit. The V.28 termination resistor (internal

to the MXL1543B) is disabled by opening S3 to avoid

interference with the T-network impedance.

V.28 Interface

The V.28 interface is an unbalanced single-ended interface (Figure 17). The V.28 driver generates a minimum

of ±5V across a 3kΩ load impedance between A’ and

C’. The V.28 receiver has a single-ended input. To aid

in rejecting system noise, the MXL1543B’s V.28 receiver has a typical hysteresis of 0.05V.

Figure 18 shows the MXL1344A’s termination network

disabled by opening S1 and S2. The MXL1543B’s internal 5kΩ V.28 termination is enabled by closing S3.

DTE vs. DCE Operation

Figure 19 shows a DCE or DTE controller-selectable

interface. DCE/DTE (pin 14) switches the port’s mode

of operation. See Table 1.

This application requires only one DB-25 connector,

but separate cables for DCE or DTE signal routing. See

Figure 19 for complete signal routing in DCE and DTE

modes.

Complete Multiprotocol X.21 Interface

A complete DTE-to-DCE interface operating in X.21

mode is shown in Figure 20. The MXL1543B is used to

generate the clock and data signals, and the

MXL1544/MAX3175 generate the control signals and

A′

R1

MXL1344A

52Ω

S1

R3

S2

124Ω

R2

52Ω

B′

C′

A

R5

12kΩ

R8

5kΩ

R6

12kΩ

S3

R7

12kΩ

R4

B

12kΩ

GND

MXL1543B

RECEIVER

Page 15

MXL1543B

+5V Multiprotocol, 3Tx/3Rx, Software-

Selectable Clock/Data Transceivers

______________________________________________________________________________________ 15

CTS A

4

2

14

24

11

15

12

17

9

3

16

7

19

20

23

8

10

6

22

5

13

18

CTS B

DSR A

DSR B

DCD A

DCD B

DTR A

DTR B

RTS A

RTS B

RXD A

RXD B

RXC A

RXC B

TXC A

TXC B

SCTE A

SCTE B

TXD A

TXD B

CHARGE

PUMP

DTE

DCE

RTS A

RTS B

DTR A

DTR B

DCD A

DCD B

DSR A

DSR B

CTS A

CTS B

LLA

LLA

TXD A

TXD B

SCTE A

SCTE B

TXC A

TXC B

RXC A

RXC B

RXD A

RXD B

SG

M2

C12

1µF

C13

1µF

C5

4.7µF

C2

1µF

C1

1µF

C4

1µF

C3

4.7µF

2

21

D1

D2

D3

R1

R2

R3

28

27

26

25

24

23

22

21

20

19

18

17

16

15

3

V

CC

5V

1

2

4

5

6

7

8

9

10

11

12

13

14

14

3

4679101615 18 17 19 20 22 23 24 15

8111213

C6

100pFC7100pFC8100pF

M1

M0

DCE/DTE

M1

M2

DCE/DTE

M0

V

CC

V

CC

V

EE

V

EE

V

CC

V

DD

GND

LATCH

MXL1344A

MXL1543B

D1

D2

D3

D4

R1

R2

R3

26

27

28

25

24

23

22

21

20

19

18

17

5

6

7

8

9

4

3

1

2

R4

16

15

10

11

12

13

14

M1

M2

DCE/DTE

INVERT

M0

M1

M2

DCE/DTE

M0

DB-25

CONNECTOR

MXL1544

MAX3175

C11

1µF

C10

1µF

C9

1µF

1

SHIELD

DTE_TXD/DCE_RXD

DTE_SCTE/DCE_RXC

DTE_TXC/DCE_TXC

DTE_RXC/DCE_SCTE

DTE_RXD/DCE_TXD

DTE_RTS/DCE_CTS

DTE_DTR/DCE_DSR

DTE_DCD/DCE_DCD

DTE_DSR/DCE_DTR

DTE_CTS/DCE_RTS

DTE_LL/DCE_LL

Figure 19. Multiprotocol DCE/DTE Port

Page 16

MXL1543B

+5V Multiprotocol, 3Tx/3Rx, SoftwareSelectable Clock/Data Transceivers

16 ______________________________________________________________________________________

D1

D2

D3

R3

R2

R1

D1

D2

D3

D4

TXD

SCTE

TXC

RXC

RXD

LL

D4

R4

R4

R3

R2

R1

104Ω

104Ω

104Ω

104Ω

104Ω

MXL1543BMXL1344A

MXL1344AMXL1543B

D1

D2

D3

R3

R2

R1

D3

D2

D1

RTS

DTR

DCD

DSR

CTS

R1

R2

R3

MXL1544

MAX3175

MXL1544

MAX3175

SERIAL

CONTROLLER

TXD

SCTE

TXC

RXC

RXD

RTS

DTR

DCD

DSR

CTS

LL

SERIAL

CONTROLLER

TXD

SCTE

TXC

RXC

RXD

RTS

DTR

DCD

DSR

CTS

LL

DCE

DTE

Figure 20. DCE-to-DTE X.21 Interface

local loopback (LL). The MXL1344A is used to terminate the clock and data signals to support the V.11 protocol for cable termination. The control signals do not

need external termination.

Compliance Testing

A European Standard EN 45001 test report is pending

for the MXL1543B/MXL1544/MXL1344A chipset. A

copy of the test report will be available from Maxim

upon completion.

Page 17

MXL1543B

+5V Multiprotocol, 3Tx/3Rx, Software-

Selectable Clock/Data Transceivers

______________________________________________________________________________________ 17

Chip Information

TRANSISTOR COUNT: 2619

PROCESS: BiCMOS

28

27

26

25

24

23

22

21

20

19

18

17

16

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

C2+

C2-

V

EE

GND

T1OUTA

T1OUTB

R3INB

T2OUTA

T2OUTB

T3OUTA/R1INA

T3OUTB/R1INB

R2INA

R2INB

R3INA

DCE/DTE

M2

M1

M0

R3OUT

R2OUT

R1OUT

T3IN

T2IN

T1IN

V

CC

V

DD

C1+

C1-

SSOP

TOP VIEW

MXL1543B

Pin Configuration

Page 18

MXL1543B

+5V Multiprotocol, 3Tx/3Rx, SoftwareSelectable Clock/Data Transceivers

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are

implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

18 ____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2004 Maxim Integrated Products Printed USA is a registered trademark of Maxim Integrated Products.

SSOP.EPS

PACKAGE OUTLINE, SSOP, 5.3 MM

1

1

21-0056

C

REV.DOCUMENT CONTROL NO.APPROVAL

PROPRIETARY INFORMATION

TITLE:

NOTES:

1. D&E DO NOT INCLUDE MOLD FLASH.

2. MOLD FLASH OR PROTRUSIONS NOT TO EXCEED .15 MM (.006").

3. CONTROLLING DIMENSION: MILLIMETERS.

4. MEETS JEDEC MO150.

5. LEADS TO BE COPLANAR WITHIN 0.10 MM.

7.90

H

L

0∞

0.301

0.025

8∞

0.311

0.037

0∞

7.65

0.63

8∞

0.95

MAX

5.38

MILLIMETERS

B

C

D

E

e

A1

DIM

A

SEE VARIATIONS

0.0256 BSC

0.010

0.004

0.205

0.002

0.015

0.008

0.212

0.008

INCHES

MIN

MAX

0.078

0.65 BSC

0.25

0.09

5.20

0.05

0.38

0.20

0.21

MIN

1.73 1.99

MILLIMETERS

6.07

6.07

10.07

8.07

7.07

INCHES

D

D

D

D

D

0.239

0.239

0.397

0.317

0.278

MIN

0.249

0.249

0.407

0.328

0.289

MAX

MIN

6.33

6.33

10.33

8.33

7.33

14L

16L

28L

24L

20L

MAX

N

A

D

e

A1

L

C

HE

N

12

B

0.068

Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,

go to www.maxim-ic.com/packages

.)

Loading...

Loading...