July 23, 2010

MG3500/MG2580 HD H.264 CODEC

Advance Information

DATA SHEET

For pricing, delivery, and ordering information, please contact Maxim Direct at

1-888-629-4642 or visit Maxim’s website at www.maxim-ic.com.

Document Release 1.4

Document Number: PN1100

Maxim Integrated Products

120 San Gabriel Drive

Sunnyvale, CA 94086

United States

408-737-7600

http://www.maxim-ic.com/support

Copyright © 2010 Maxim Integrated Products

This document contains advanced information and is subject to change without prior notice.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a

Maxim product. Maxim retains the right to make changes to its products or specifications to improve

performance, reliability or manufactur-ability. All information in this document, including descriptions of

features, functions, performance, technical specifications and availability, is subject to change without notice

at any time. While the information furnished herein is held to be accurate and reliable, no responsibility will

be assumed by Maxim for its use. Furthermore, the information contained herein does not convey to the

purchaser of microelectronic devices any license under the patent right of any manufacturer.

Maxim products are not intended for use in life support products where failure of a Maxim product could

reasonably be expected to result in death or personal injury. Anyone using a Maxim product in such an

application without express written consent of an officer of Maxim does so at their own risk, and agrees to

fully indemnify Maxim for any damages that may result from such use or sale.

is a registered trademark of Maxim Integrated Products, Inc.

All other products or service names used in this publication are for identification purposes only, and may be

trademarks or registered

trademarks of their respective companies. All other trademarks or registered trademarks mentioned herein

are the property of their

respective holders.

1.0: Description 13

1.1: Hardware Overview 14

1.2: Support Tools 18

2.0: Device Overview, Pin Assignments 21

2.1: Naming Conventions 21

2.2: Pinout Diagrams 22

2.3: Pin Descriptions (by Interface) 27

2.4: Power and Ground Pins 52

2.5: Pin List by Power Group 55

2.6: Hookup Recommendations when Interfaces Are

Unused 57

3.0: Device Configuration 67

3.1: Reset 67

3.2: Boot modes for the MMEs and the ARM 67

3.3: Firmware Loader 68

3.4: API Configuration 68

3.5: Pin Multiplexing, GPIOs, etc. 68

3.6: Debug Mode 68

3.7: JTAG ID Register 68

4.0: Device Operating Conditions 71

4.1: Absolute Maximum Ratings 71

4.2: Recommended Operation Conditions 71

4.3: Essential Characteristics 72

4.4: Power Supply Currents for the Different Power

Domains73

4.5: AC Timing 73

5.0: Block Level Operation 97

5.1: Detailed Block Diagram 97

5.2: Reset Logic 98

5.3: Clocks and PLLs 99

5.4: Video Interfaces 103

5.5: Video Scaling 111

5.6: Audio Interfaces 118

5.7: Host Interfaces 120

5.8: Configuration and Status Register (CSR) Defini-

tion 132

5.9: DMA Engine Register Definition 136

5.10: Bitstream Write Register Definition 144

5.11: Special Registers 145

5.12: Memory Interfaces 152

5.13: Serial Interfaces 167

5.14: USB 2.0 On-the-Go Interface 178

5.15: Ethernet Media Access Controller 184

5.16: High-Speed Bitstreams 188

6.0: System Design and Applications 193

6.1: Power Supply Design and Recommendations 193

6.2: Power Supply Sequencing 193

6.3: Reset timing Diagrams 193

6.4: Oscillator Connections, Values and Formulas194

7.0: Ordering Information 197

7.1: Product Information 197

7.2: MG3500 Family Reflow Profile 198

8.0: Packaging Information 201

8.1: Package Diagram 201

8.2: Thermal Data 202

9.0: Marking 203

Maxim Integrated Products Advance Information | 3

Maxim Integrated Products Advance Information | 4

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

Change Log

This section of the data sheet lists the changes that have occurred since the last release. Customers

should be aware that not all releases are public, and therefore they might see gaps in the release

numbering system.

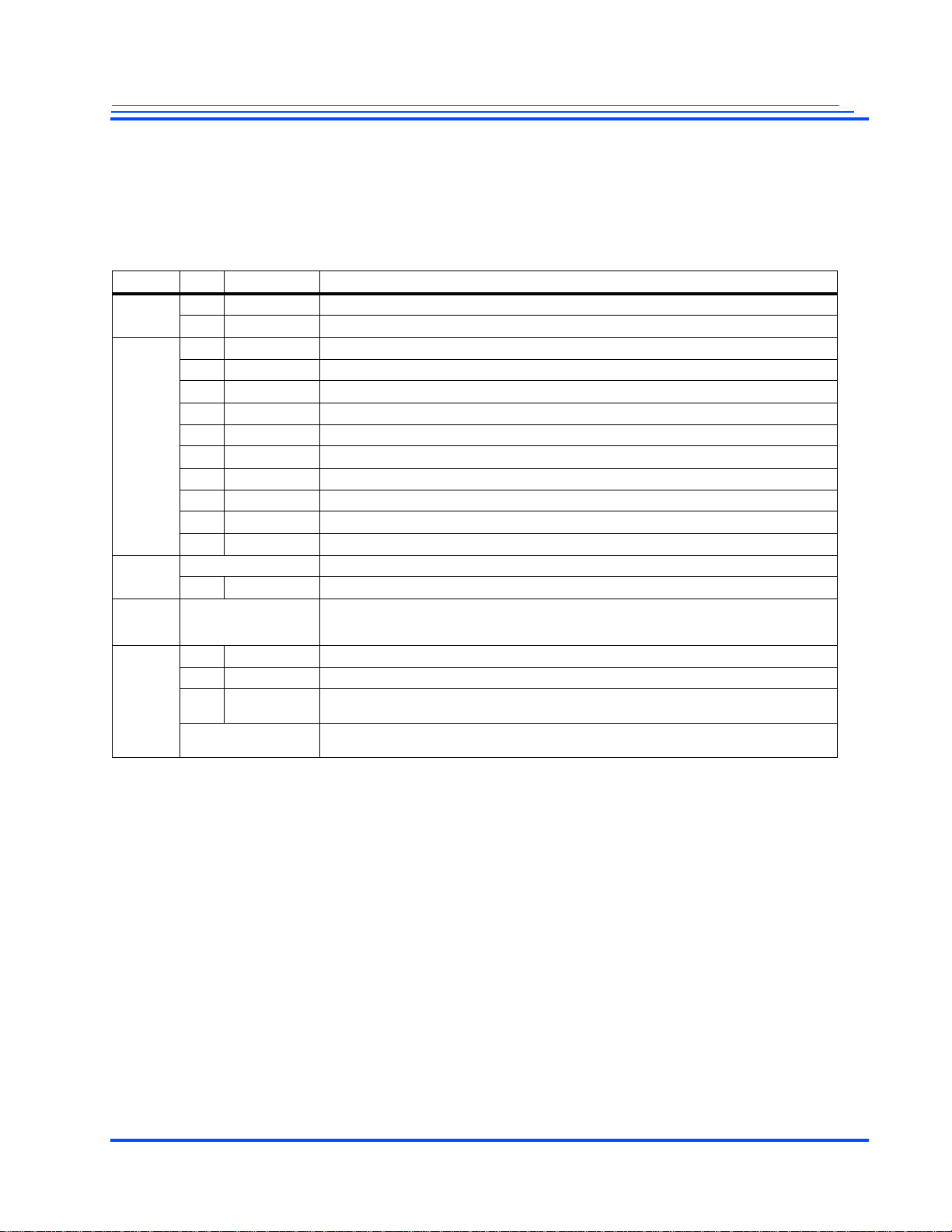

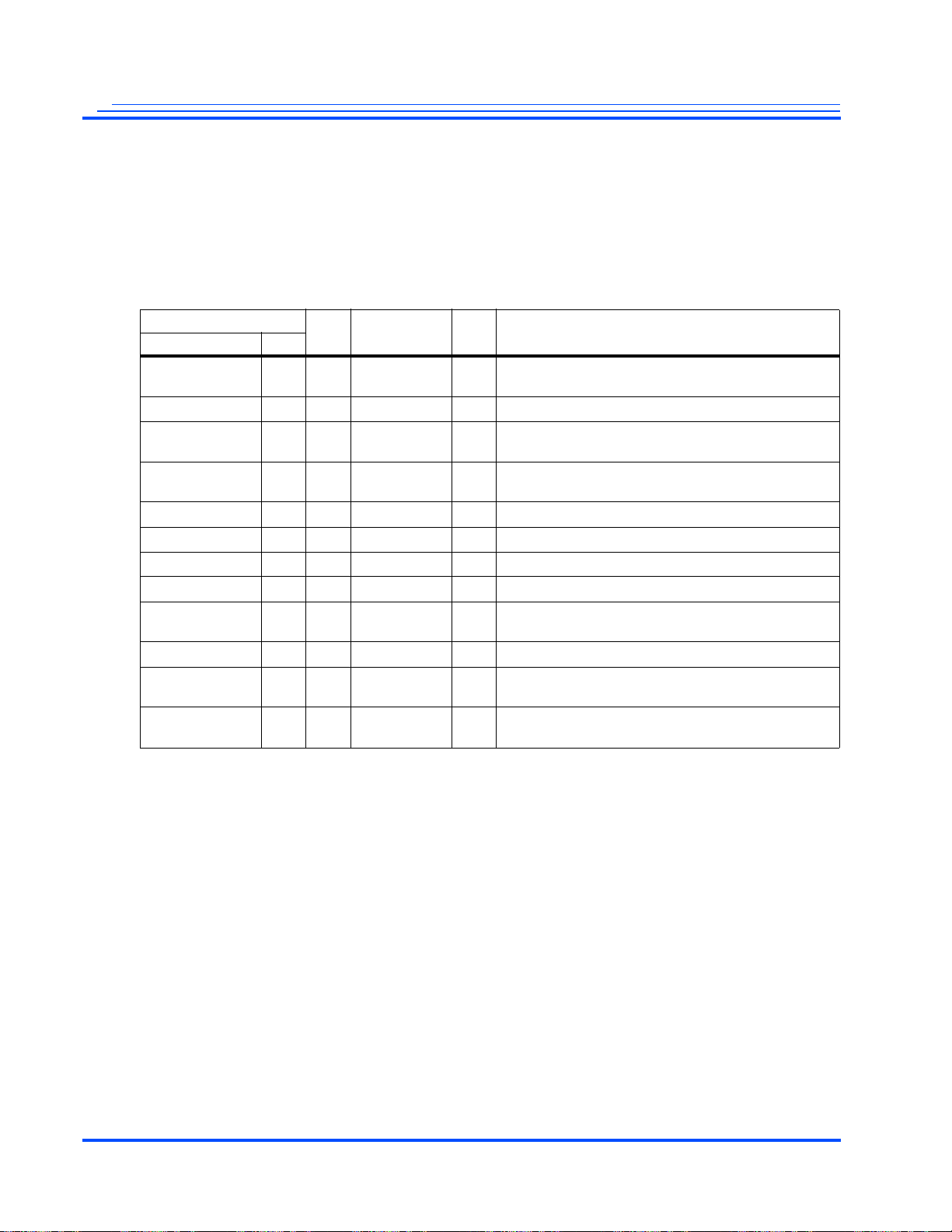

Change Log

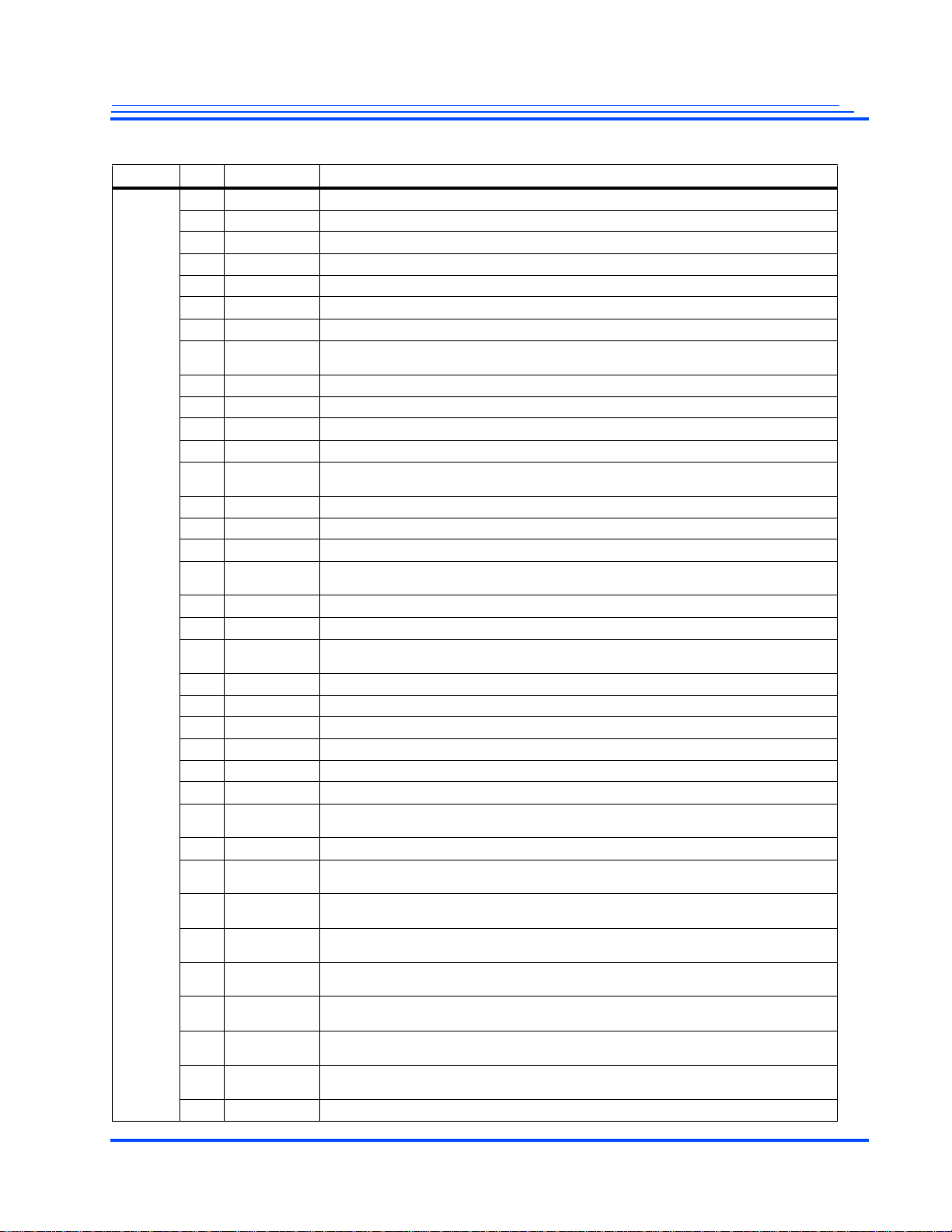

Revision Page Section Change

0.18

0.19

0.20 Throughout Made minor changes throughout the book.

0.21 Throughout Valid value for EWait of EM1Config is 1; EM1Cmd register set to 0x00; removal of several reg-

1.0 14 1.1.2 The heading title and description has been changed.

71 4.1 The Core power supply current was changed from 1000 mA. typical to 1000 mA. maximum.

195 6.4.3 A new section was added describing use when only an external clock is used.

43 2.3.8 Specified the resistance of the external USB Bias Current resistor.

43 2.3.9 Modified the timing specification for the SD and MMC Interface.

46 2.3.14 Specified the resistance of the internal pull-up and pull-down resistors

89 4.5.6 Added a new section showing the bitstream timing.

99 5.3 This entire section was re-written to clarify the clock structure.

111 5.5 The definition of the VOUT register was altered.

145 5.11 The specification for the ChipID register was added.

152 5.12 The SDRAM Requirements for Various Profiles table was updated.

184 5.15 Added note regarding the use of an external switch.

190 5.16.5 Updated the Bitstream Register section.

120 5.7.1 Added timing diagrams showing Master Host Interface (MHIF) access timing.

isters, Slave Host Interface; Valid value for EM1 is 0; Corrections to S/PDIF and I2S I/Os; BFifostatus changed to EM1fifostatus.

15 1.1.2 Figure 1-2, only one independent video output is supported.

16 1.1.3 The maximum pixel rate that VIP can process corresponds to the video input of resolution

Throughout Made editorial changes, added definitions, made updates and corrections to several diagrams

1920x1080i at 30 frames per seconds.

and tables throughout the book.

Maxim Integrated Products Advance Information | 5

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

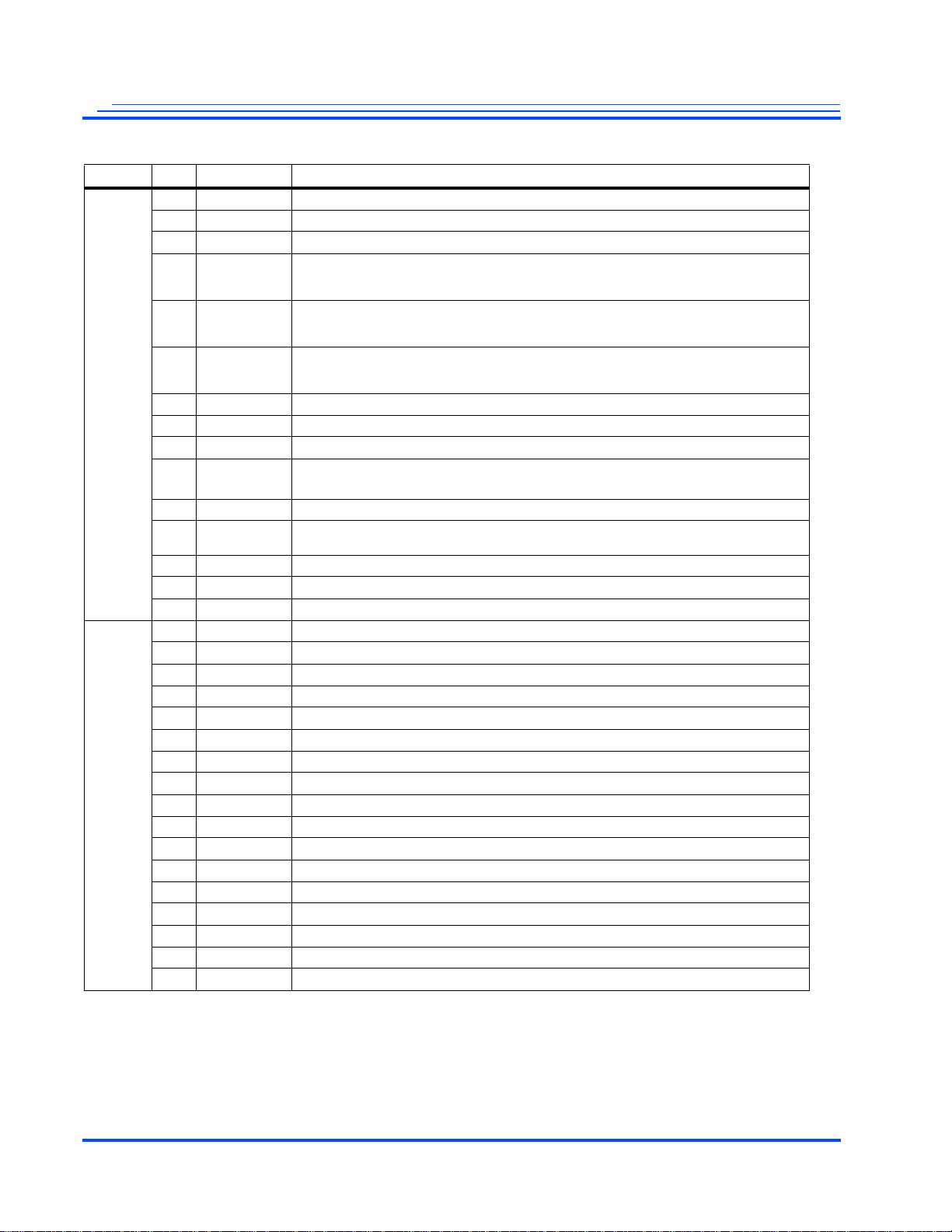

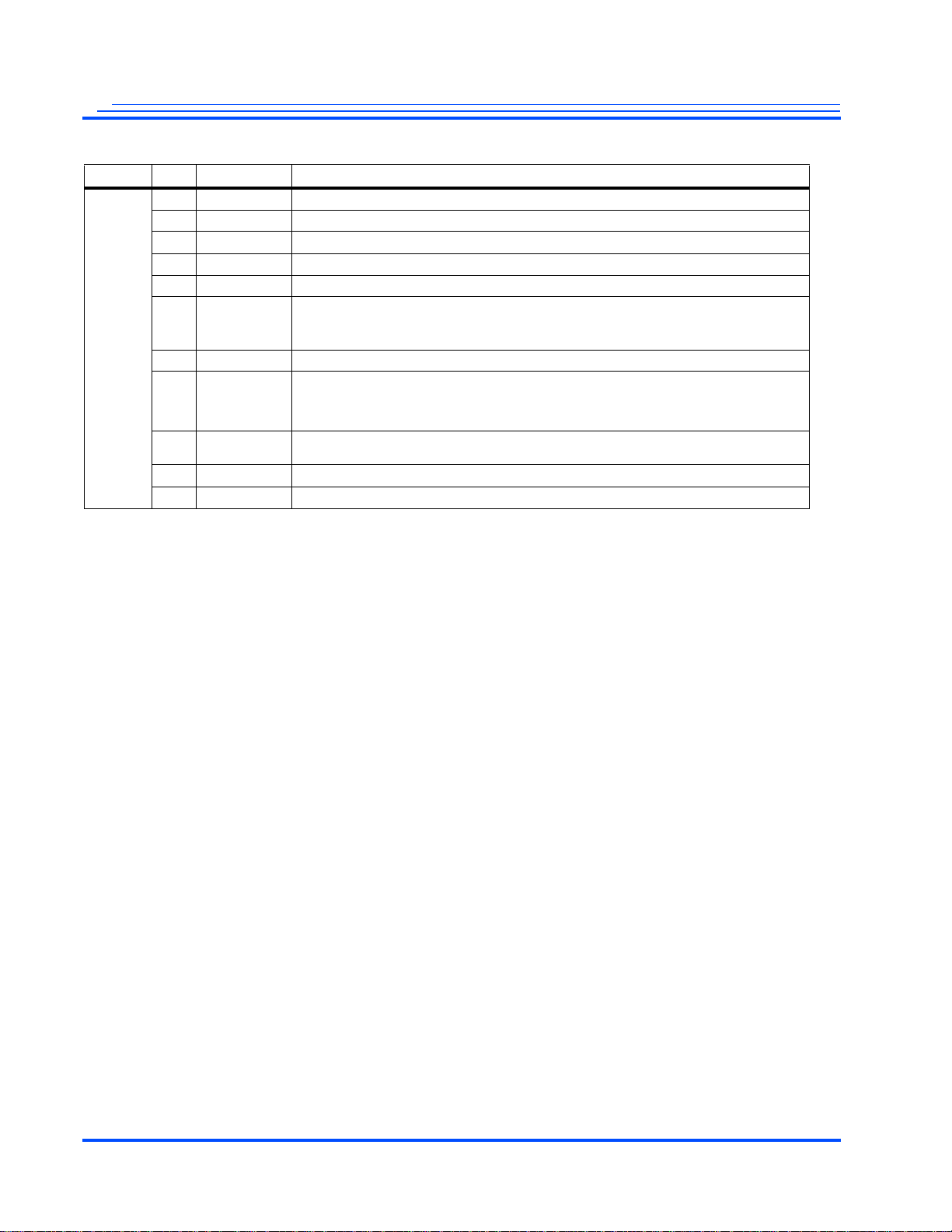

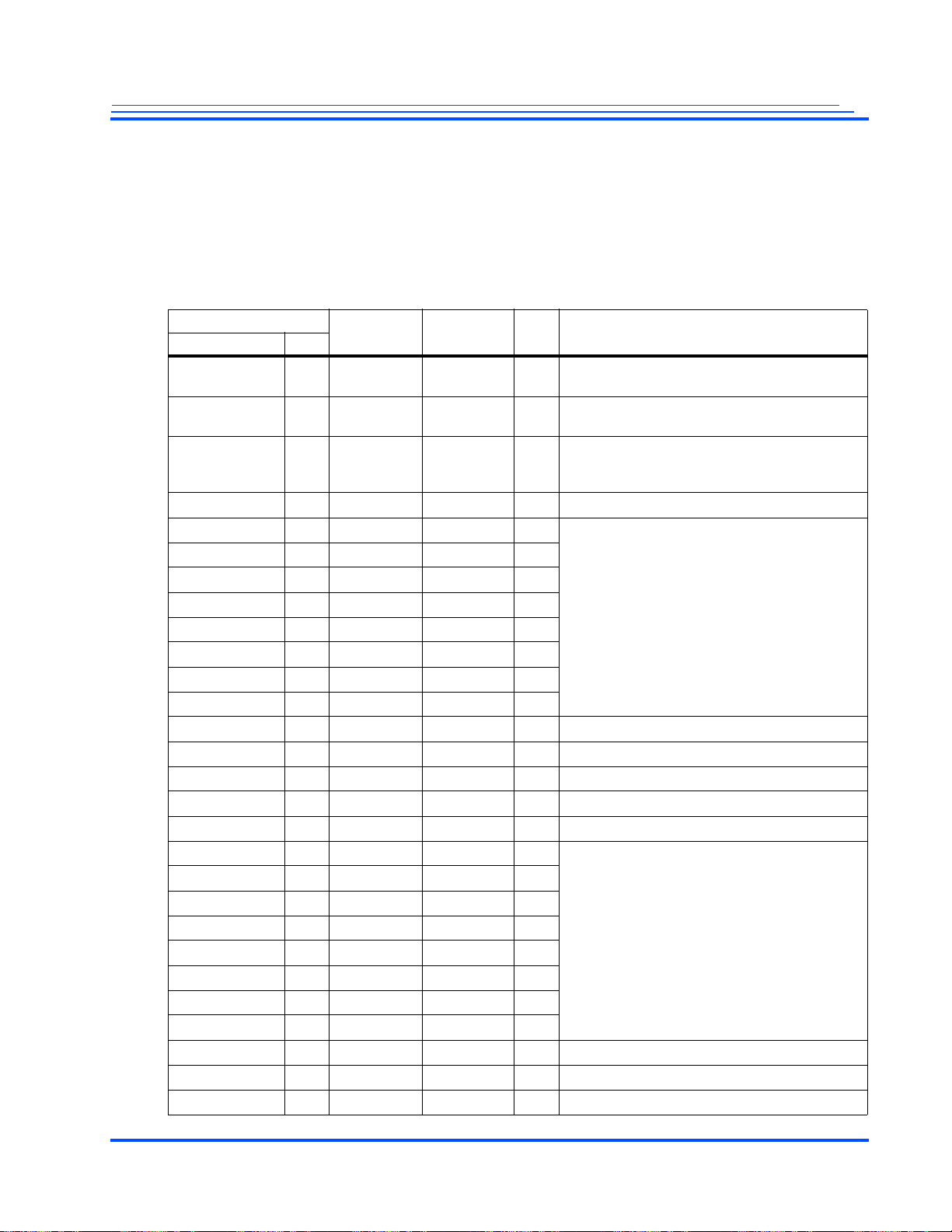

Change Log

Revision Page Section Change

1.1 71 4.1 The core supply voltage has been changed to 1.05v ± 5%.

71 4.2 The minimum, typical, and maximum ranges of the core supply voltage have been re-adjusted.

78 4.5.2 Modified the Video Interface Timing Diagram to incorporate the new t

78 4.5.2 Modified Table 4-7 to indicate that VIDOUT_DATA is an output delay from VID_CLK for the

78 4.5.2 Modified Table 4-8 to indicate that VIDOUT_DATA is an output delay from VID_CLK for the

78 4.5.2 Modified Table 4-9 to indicate that VIDOUT_DATA is an output delay from VID_CLK for the

144 5.10 Made corrections to the bit settings of the BiFiStatus and BiFiConfig registers.

188 5.16.1 Changed the description for the bitstream interface.

190 5.16.5 Removed the old section “High-Speed Bitstream” since it is not supported.

189 5.16.4 Modified Figure 5-39 to show signal BS-DATA is 8 bits long.

189 5.16.4 Changed the definition for Cycle 7 of the waveform diagram.

190 5.16.5 In Bitstream Control 2, removed the unsupported value 1 for BSClkEnMode, BSStopCond,

190 5.16.5 Bitstream Interface Control registers 8, A, and C have been removed.

193 6.2 The second half of the RESETn signal in Figure 6-1has been removed.

201 8.0 Added a new Ordering Information section.

1.2 14 1.1 Added Hardware Description section back.

78 4.5.2 Corrected the note below Table 4-7 to say the clock should be supplied by MG3500.

78 4.5.2 Re-adjusted the t

78 4.5.2 Re-adjusted the t

81 4.5.3 Inverted the AUD_LRCK signal in Figure 4-6.

81 4.5.3 Re-adjusted the shaded area for ETH_RXDV and ETH_RXER signals in Figure 4-10.

81 4.5.3 Modified the description for Figure 4-7.

81 4.5.2 Completely re-drew Figure 4-7.

84 4.5.4 The ETH_TXD signal was corrected to ETH_RXD in Table 4-12.

84 4.5.4 Changed the description for t

86 4.5.4 Changed signals ETH_RXDV and ETH_RXER in Table 4-14.

86 4.5.4 Changed the description for t

88 4.5.4 Changed signals ETH_RXDV and ETH_RXER in Table 4-16.

88 4.5.4 Changed the ETH_RXDV signal in Table 4-16.

81 4.5.3 Re-adjusted the shaded area for ETH_RXDV and ETH_RXER signals in Figure 4-14.

203 9.0 Removed the approval table from the Marking section.

197 7.1.3 Changed the maximum height.

standard definition video interface AC timing values. It also specifies the minimum and maximum timing value in ns.

high definition video interface AC timing values. It also specifies the minimum and maximum

timing value in ns.

high-speed video interface AC timing values. It also specifies the minimum and maximum timing value in ns.

Changed the definition for Cycle 7 of the waveform diagram.

and BSStrobeModeEn signals.

parameter in Figure 4-5.

VCQ

parameter in Figure 4-5.

VIH

to indicate a clock High time in Table 4-12.

ETH

to indicate a clock High time in Table 4-14.

ETH

parameter.

VCQ

6 | Advance Information Maxim Integrated Products

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

Change Log

Revision Page Section Change

1.3 11 “SoC Features” Separated Definitions of output ports for Audio Codecs and Decoders.

11 “SoC Features” Changed SDRAM voltage for DDR_VDD.

13 1.0 Changed the description to provide a summary of both MG3500 and MG2580.

13 1.0 Changed Table 1-1 to specify the features of both MG3500 and MG2580.

13 1.0 Added the slave mode support for MG2580 in Table 1-1.

14 1.1.1 Added the total number of macroblocks required for the H.264 Codec.

14 1.1.2 Changed the description for video processors and interfaces for clarity.

15 1.1.2 Added a note following the text describing Figure 1-2 to indicate that video composition fea-

15 1.1.2 Added a column to Table 1-2 that shows video modes for the video composition.

16 1.1.4 Added a note to indicate the supported formats for video output processor.

16 1.1.7 Modified the description for valid input and outputs for audio interfaces.

17 1.1.12 Removed IDE from the list of external devices that can communicate with the host interface.

18 1.2 Removed the evaluation applications and demonstration product applications supplied by Mo-

19 1.2 Changed the middle box at the bottom of Figure 1-4 to say Mobilygen Software.

31 2.3.3 Added pin descriptions for MG2580 to Table 2-4.

46 2.3.14 Indicated in Table 2-17 that GPIO_2-12, -13, and -15 are not applicable for MG2580.

57 2.6 Indicated in Table 2-24 that VID23_MISO, _MOSI, and _MSS are not available for MG2580

57 2.6 Removed the descriptions for the USB and Ethernet pin names in Table 2-24.

57 2.6 Specified that USB_ADD is recommended for USB_REXT in Table 2-24.

57 2.6 Added a footnote to Table 2-24 that recommends a two-step procedure on how to connect the

71 4.0 Changed the range for the DDR_VDD IO voltage in Table 4-2.

71 4.0 Changed the operating conditions range for DDR_VREF in Table 4-2.

86 4.5.4 Changed ETH_RXER[3:0] to ETH_RXD[3:0] in Figure 4-12.

88 4.5.4 Changed ETH_RXER[1:0] to ETH_RXD[1:0] in Figure 4-14.

125 5.7.1 Specified the bit range for AddrInc and WEn in the “DevConfigAn Register” table.

126 5.7.1 Specified the bit range for RHold in the “DevConfigBn Register” table.

168 5.13.3 Added a new section to describe TWI on MG2580. This includes description as well as a new

169 5.13.2 Changed Figure 5-33 to show that VID23_SDA is not applicable to MG2580.

170 5.13.4 Indicated that this section is about SPI on MG3500. Added a note to imply that V23 SPI port

171 5.13.5 Changed Figure 5-35 to show that VID23_MSS, VID23_MCLK, VID23_MOSI, and

171 5.13.5 Added a new section for SPI on MG2580. This includes descriptions as well as a modified di-

173 5.13.8 Indicated in the Serial I/O Control table that V23_MCLK_AltSeL and V23_MOSI_AltSeL are

173 5.13.8 Indicated in the GPIO 2 Sel that table GPIO_2_12, GPIO_2_13, and GPIO_2_15 fields will

173 5.13.8 Indicated in the GPIO 2 Pull-up Enable table GPIO_2_12, GPIO_2_13, and GPIO_2_15 fields

173 5.13.8 Indicated in the GPIO 2 Pull-up Enable table GPIO_2_12, GPIO_2_13, and GPIO_2_15 fields

197 7.1.3 Removed the part number to order MG2580A2 since this part will no longer be built.

tures are not available when two VIPs are used as inputs.

bilygen.

for VIDEO_PORT 2/3.

USB pins when the USB block is not used on MG3500.

diagram, Figure 5-33.

is not available on MG2580.

VID23_MISO are not applicable to MG2580.

agram, Figure 5-35.

not available on MG2580.

have no effect on MG2580 since GPIO pins are not connected.

will have no effect on MG2580 since GPIO pins are not connected.

will have no effect on MG2580 since GPIO pins are not connected.

Maxim Integrated Products Advance Information | 7

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

Change Log

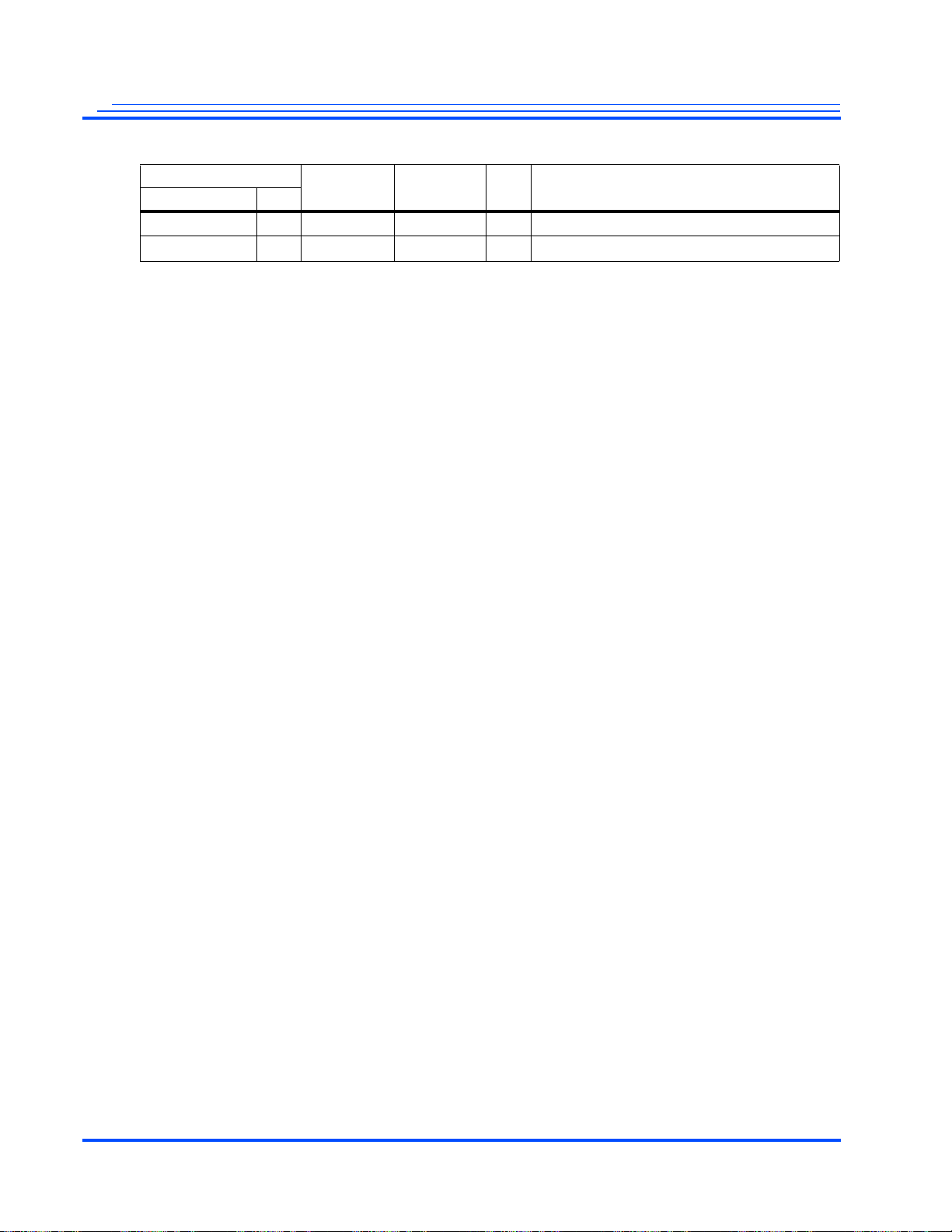

Revision Page Section Change

1.4 29/30 2.3.2 Changed VID0_PIXCLK and VID1_PIXCLK to IO

40 2.3.6 Added a note for DDR_DQ[31:16] and DDR_DQM[3:] pins are not connected in 16-bit mode

46 2.3.14 Removed alternate functionality for GPIO_6 and GPIO_7

56 2.5 Removed signal USB_VBUS from 3.3V Power Group

71 4.2 Updated ETH_VDD 3.3V +/- 5%

78 4.5.2 Included tVH(min) and tVH(max) in Table 4-7, Table 4-8 and Table 4-9

Added HSYNC, VSYNC, and FRAME signals to the timing diagram. Clarified Setup and Hold

time description with reference to VID_CLK for VID_DATA and VIDOUT_DATA.

81 4.5.3 Updated figure 4-6 as it was not readable in v1.3

87/88 4.5.4 Updated RMII Transmit/Receive Timing Diagram in Figure 4-13 by replacing TXCLK with RX-

103/

104

165 5.12.5 Removed 512 byte page size under NAND flash bulleted item

166 5.12.5 Updated NAND/NOR Flash Interface connected to NOR Flash Memory Figure 5-30

5.4 Included separate block diagrams for MG3500 and MG2580 video paths

CLK. Updated Tables 4-15 accordingly by removing transmit and replacing it with receive

clock.. Changed Min. and Max. values in Table 4-16 for ECYC-ETH_CLK, ETL- Low and ETHHigh Time signal.

8 | Advance Information Maxim Integrated Products

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

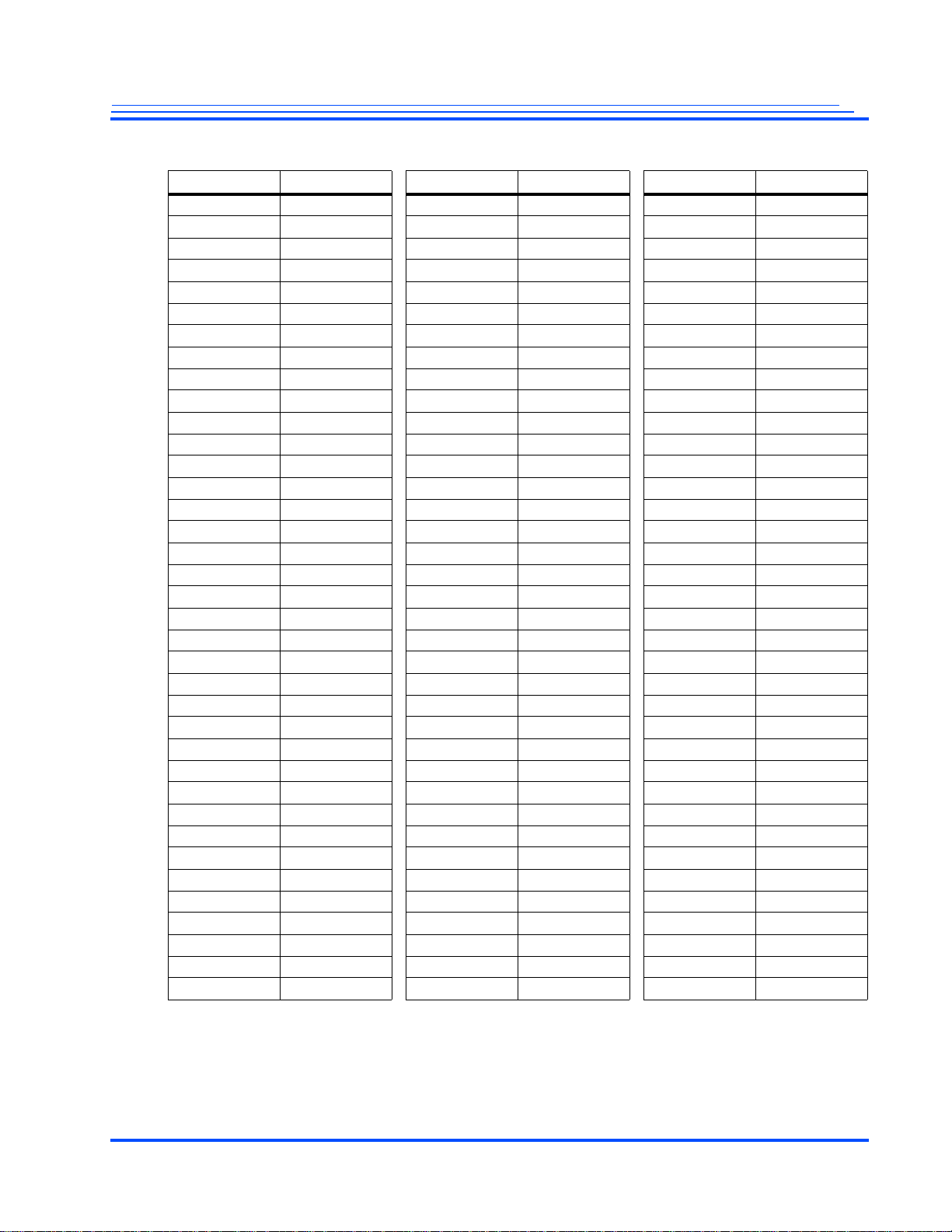

Table 1 Pin Name Changes

Old Name New Name Old Name New Name Old Name New Name

ENET_COL ETH_COL HOST_A08 HOST_A8 DDR_D27 DDR_DQ27

ENET_RXD1 ETH_RXD1 HOST_A05 HOST_A5 DDR_D31 DDR_DQ31

ENET_RXERR ETH_RXERR HOST_A06 HOST_A6 DDR_D29 DDR_DQ29

ENET_RXDV ETH_RXDV CF_WAITn CF_WAITn DDR_D30 DDR_DQ30

ENET_CRS ETH_CRS HOST_A02 HOST_A2 DDR_D28 DDR_DQ28

ENET_RXCLK ETH_RXCLK HOST_A09 HOST_A9 DDR_D24 DDR_DQ24

ENET_RXD0 ETH_RXD0 HOST_A07 HOST_A7 DDR_D26 DDR_DQ26

ENET_RXD2 ETH_RXD2 HOST_A03 HOST_A3 DDR_D23 DDR_DQ23

ENET_RXD7 ETH_RXD7 HOST_A04 HOST_A4 DDR_D21 DDR_DQ21

ENET_MDCLK ETH_MDCLK HOST_A01 HOST_A1 DDR_D22 DDR_DQ22

ENET_RXD3 ETH_RXD3 DDR_A03 DDR_A3 DDR_D19 DDR_DQ19

ENET_MDIO ETH_MDIO DDR_A02 DDR_A2 DDR_D20 DDR_DQ20

ENET_RXD6 ETH_RXD6 DDR_A01 DDR_A1 DDR_D16 DDR_DQ16

ENET_RXD4 ETH_RXD4 DDR_A00 DDR_A0 DDR_D17 DDR_DQ17

ENET_TXD0 ETH_TXD0 DDR_A08 DDR_A8 DDR_D18 DDR_DQ18

ENET_RXD5 ETH_RXD5 DDR_A04 DDR_A4 JTAG_TEST TEST

ENET_TXD2 ETH_TXD2 DDR_A07 DDR_A7 RESETn RESETn

ENET_TXD4 ETH_TXD4 DDR_A06 DDR_A6 JTAG_T_SELL JTAG_TAP_SEL

ENET_TXEN ETH_TXEN DDR_A09 DDR_A9 VID1_OCLK VID1_OUTCLK

ENET_TXD3 ETH_TXD3 DDR_D05 DDR_DQ5 VID1_PXCLK VID1_PIXCLK

ENET_TXD5 ETH_TXD5 DDR_D00 DDR_DQ0 VID0_OCLK VID0_OUTCLK

ENET_TXERR ETH_TXER DDR_D07 DDR_DQ7 VID0_PXCLK VID0_PIXCLK

ENET_TXCLK ETH_TXCLK DDR_D04 DDR_DQ4 USB_VDD_D USB_DVDD

ENET_TXD1 ETH_TXD1 DDR_D01 DDR_DQ1 USB_VDDA USB_AVDD

ENET_TXD6 ETH_TXD6 DDR_D06 DDR_DQ6 USB_GNDA USB_AGND

ENET_TXD7 ETH_TXD7 DDR_D02 DDR_DQ2 USB_GNDA USB_AGND

HOST_D08 HOST_D8 DDR_D03 DDR_DQ3 USB_GNDA USB_AGND

HOST_D09 HOST_D9 DDR_D14 DDR_DQ14 USB_VDDA USB_AVDD

HOST_D04 HOST_D4 DDR_D08 DDR_DQ8 USB_VDDAC USB_ACVDD

HOST_D05 HOST_D5 DDR_D15 DDR_DQ15 USB_GNDAC USB_ACGND

HOST_D06 HOST_D6 DDR_DQ9 DDR_DQ9 USB_A_TST USB_ANA_TEST

HOST_D02 HOST_D2 DDR_D10 DDR_DQ10 VID3_FIELD VID23_GPIO

HOST_D03 HOST_D3 DDR_VREF1 DDR_VREF VID3_VSYNC VID_DATA_16

HOST_D07 HOST_D7 DDR_D13 DDR_DQ13 USB_VBUSD USB_D_VBUS

HOST_D01 HOST_D1 DDR_D12 DDR_DQ12 VID3_HSYNC VID_DATA_17

HOST_D00 HOST_D0 DDR_D11 DDR_DQ11 VID2_PXClK VID2_PIXCLK

CF_IACKn CF_INPACKn DDR_D25 DDR_DQ25

Maxim Integrated Products Advance Information | 9

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

10 | Advance Information Maxim Integrated Products

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

SoC Features

HD H.264 Codec

• Dual-Stream High-Definition (HD) or Standard-Definition (SD) H.264 Codecs

• Full-duplex HD or SD operation

• Dual Encode HD or SD or

• Dual Decode HD or SD

• H.264 Codec supports High, Main, and Baseline

profiles

• H.264 Codec up to level 4.1

• H.264 Encoding or decoding up to 1920x1080i

• Programmable resolutions and frame rates

• Multi-stream SD encode or decode

• Video bit rates: 64 kbps – 62.5 Mbps

• Macro-Block Level Adaptive Frame/Field

(MBAFF) support

MPEG-2 Decoder

• HD and SD decoder

• Enables real-time HD MPEG-2 to HD H.264

transcoding

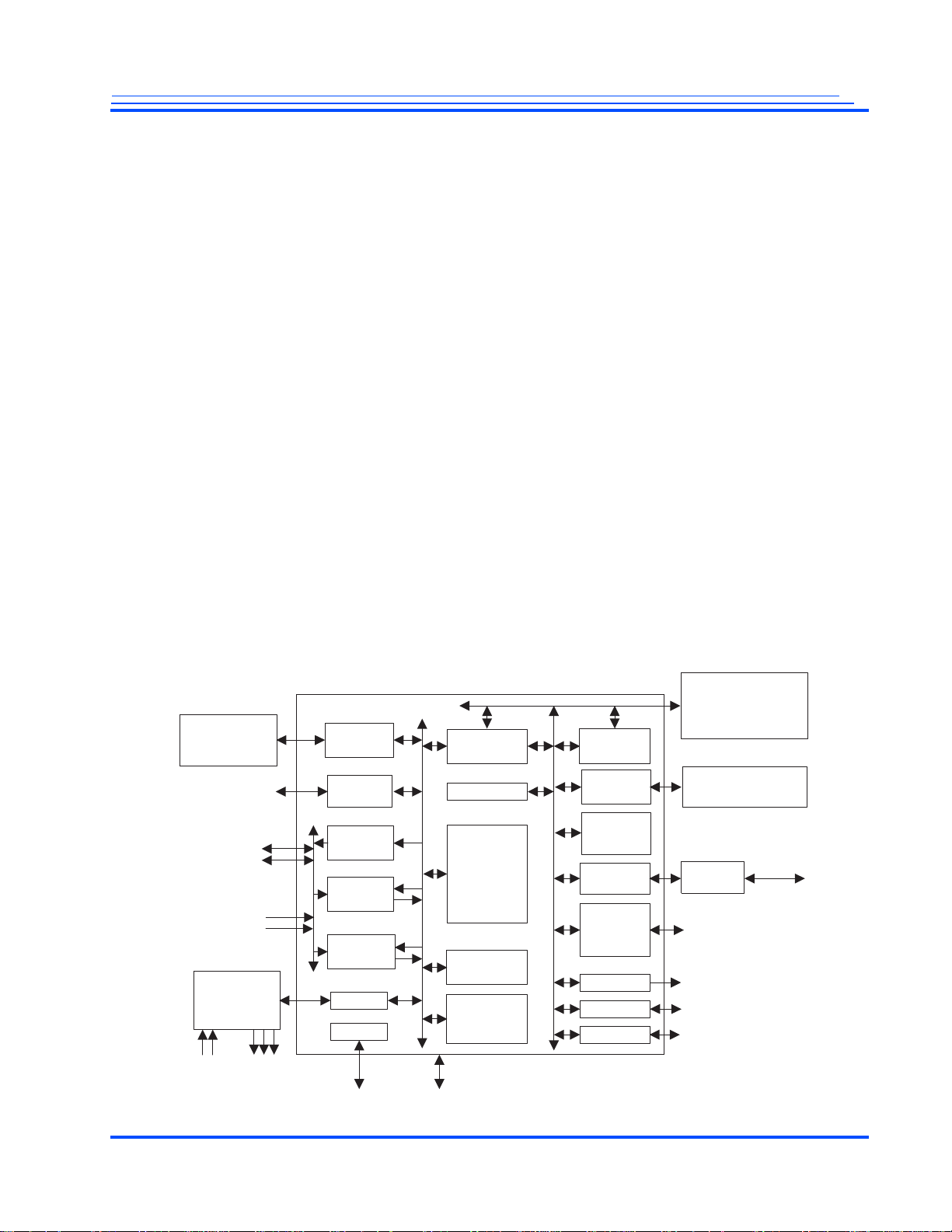

Block Diagram

• Multi-stream SD MPEG-2 decoding

JPEG Codec

• JPEG Encoder and Decoder

• HD or SD MJPEG Support

• Exchangeable Image File Format (EXIF) Support

Audio Codecs & Decoders

• High-fidelity, 2-channel AAC-LC codec

• MPEG-1/2 Audio Layer II codec (MP2)

• MPEG-1/2 Audio Layer I and III decoder (MP1

and MP3)

• Dolby Digital 5.1 decode and down mix

•G.711 Codec

• Flexible bit rates and sample rates

• Additional codecs planned

• One S/PDIF output port

•Two I

2

S Audio input ports and three I2S Audio

output ports

DDR2 SDRAM

(1 or 2 Chips)

High-Speed

Bitstream

Video I/O

ITU-R BT.1120 or

ITU-R BT.656 (2X)

Video Input

ITU-R BT.1120 or

ITU-R BT.656 (2X)

Audio

Codec(s)

Two

Stereo

Inputs

Stereo

Outputs

Three

SDRAM

Controller

Bitstream

I/F

VOP

HD/SD

VIP1

HD/SD

VIP2

HD/SD

I2S

Clocks

XTAL

JTAG

Slave Host/

Bridge

AES/SHA

HD H.264

Codec

HD MPEG2

Decoder

HD JPEG

Codec

Video MME

Audio/

System

MME

Master

Host

SD/MMC

Controller

ARM926

Processor

Ethernet

MAC

USB

Including

a PHY

PWM

Serial I/O

Serial I/O

Master/ Slave Host

I/F/ NAND/NOR/

CF/IDE

16 Data, 23 Address

SDIO/MMC/

CE_ATA

Ethernet

Ethernet

USB 2.0

PWM (3X)

UART (2X)

TWI/SPI (2X)

10/100/GigE

PHY

Maxim Integrated Products Advance Information | 11

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

Video Input Processors (VIPs)

• Flexible direct video inputs

• Two ITU-R BT.1120 parallel interfaces

• Four ITU-R BT.656 parallel interfaces

• Two advanced Video Input Processors (VIPs)

• Digital Image Stabilization

• Smooth Digital Zoom

Video Output Processor (VOP)

• HD or SD output support via ITU-R BT.1120 or

ITU-R BT.656

• Multi-stream decode supports scaled PIP and

multi-channel compositing on video output

• LCD Interface, 16-Bit, 18-bit or 8-bit RGB

• High-quality Video output video scaling

• Two overlay planes with alpha blending and

cursor

• Generates optional external sync signals

Integrated ARM926-EJ Processor

• 240 MHz general purpose processor

• 16 kByte Data Cache

• 16 kByte Instruction Cache

• 16 kByte Scratch Pad Memory

• Three Pulse Width Modulators

• Up to 72 GPIO, 8 dedicated

System

• Core Voltage: 1.05V ± 5%

• SDRAM Voltage: 1.8V ±0.1V

• I/O Voltages: 1.8V, 2.5V, 3.3V ±10%

• On-Chip A/V PLLs driven from single crystal

Power Consumption (MG3500+SDRAM)

• H.264 HD 30fps + AAC Encode 750 mW

Packaging

• 376-ball FPBGA, 18x18mm, 0.8mm pitch,

RoHS compliant

System Connectivity

• 10/100/GigE Ethernet MAC

1

• USB 2.0 On-The-Go (OTG) ports including the

physical layer

• High Speed Bit-stream I/O

• AES and SHA hardware acceleration

Peripheral Interfaces

• Secure Digital (SD), Secure Digital Input/

Output (SDIO), Multi-Media Card (MMC), and

Consumer Electronics AT Attachment (CEATA)

• Compact FLASH, IDE

General Purpose Interfaces

• Two SPI or Two Wire Interface ports

• Three UARTs

1. When both 10/100 and GigE need to be enabled, an

external switch must be installed to select the clock.

Maxim Integrated Products Advance Information | 12

1.0 Description

The Maxim High-Profile H.264 Codecs currently comprises two devices: MG3500 HD H.264 Codec

SoC and MG2580 720p30 H.264 Codec SoC. The MG3500 HD H.264 Codec SoC is a full HD 1080p30

H.264 Codec. It is the ideal choice for any 1080p30 H.264 application as well as multi-channel D1

applications as found in the security surveillance space. Similarly , the MG2580 SoC is the cost-reduced

version of the High-Profile H.264 Codecs that performs 720p30 H.264 and MJPEG encoding

operations. The MG2580 is particularly adapted for both IP camera a nd H.264 webcam designs. Both

chips encompass an ARM926-EJ processor as well as a complete set of System-On-a-Chip (SoC)

features.

Table 1-1 shows the features for each of the devices. Specific information for both of these devices are

covered in this datasheet.

All references to MG3500 throughout this manual also apply to the MG2580 as well unless stated

otherwise.

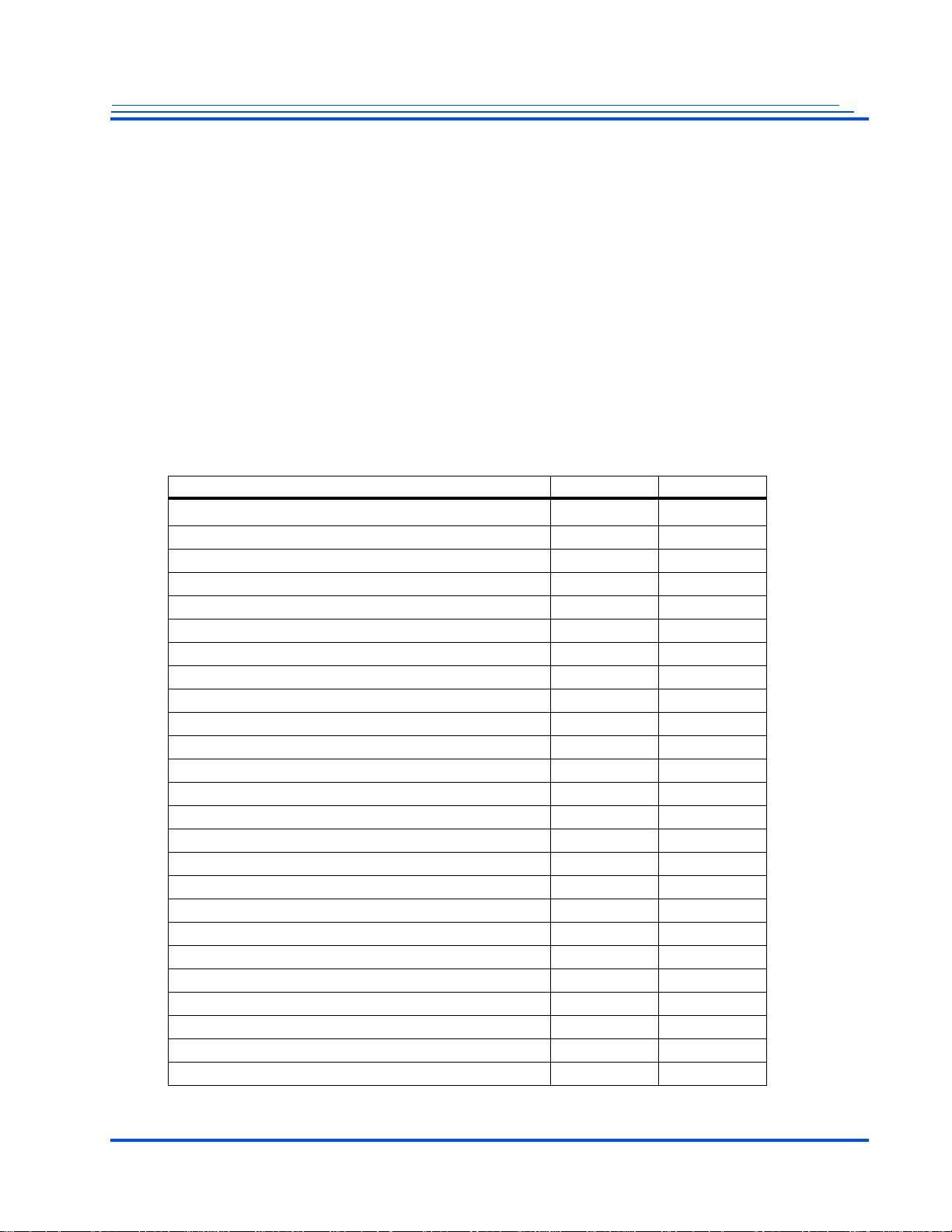

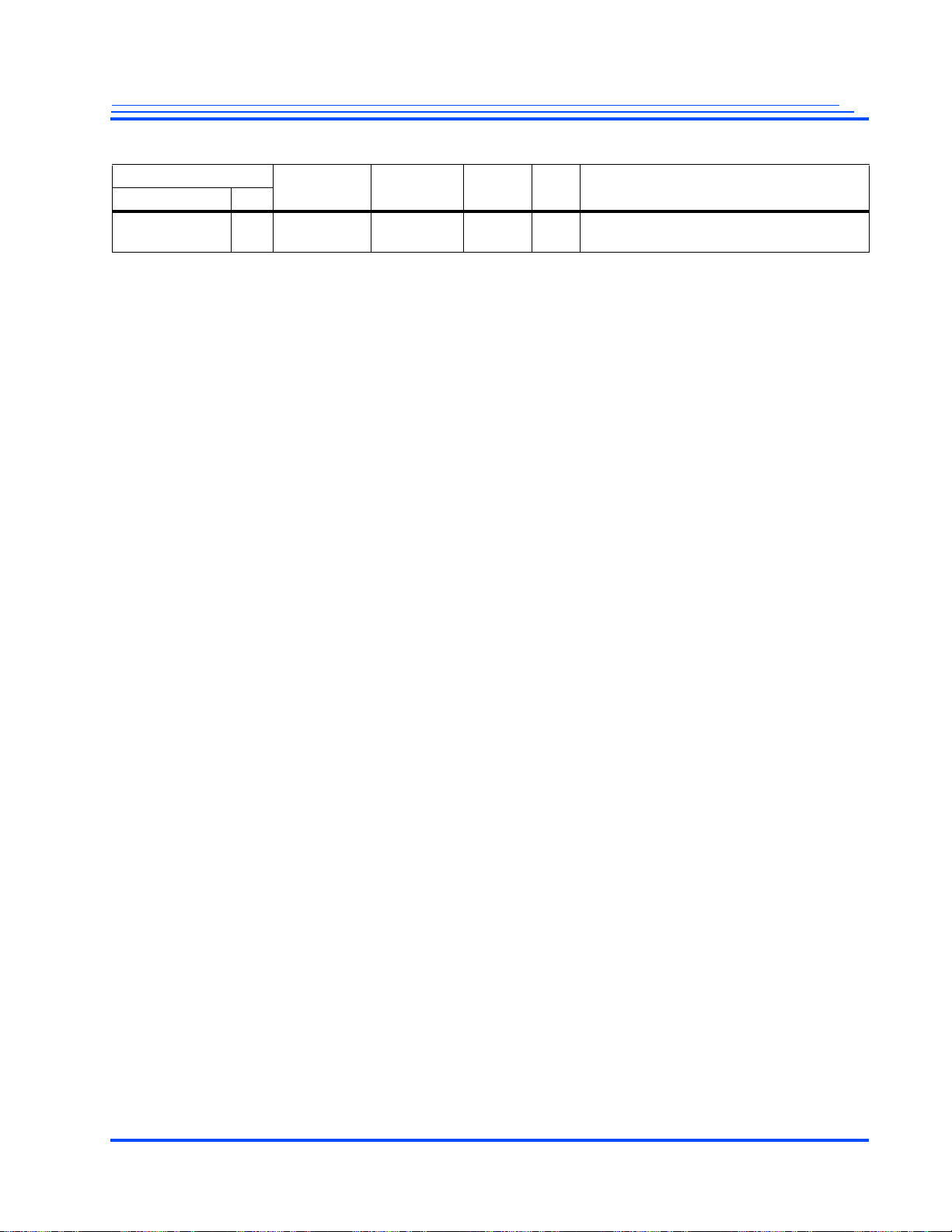

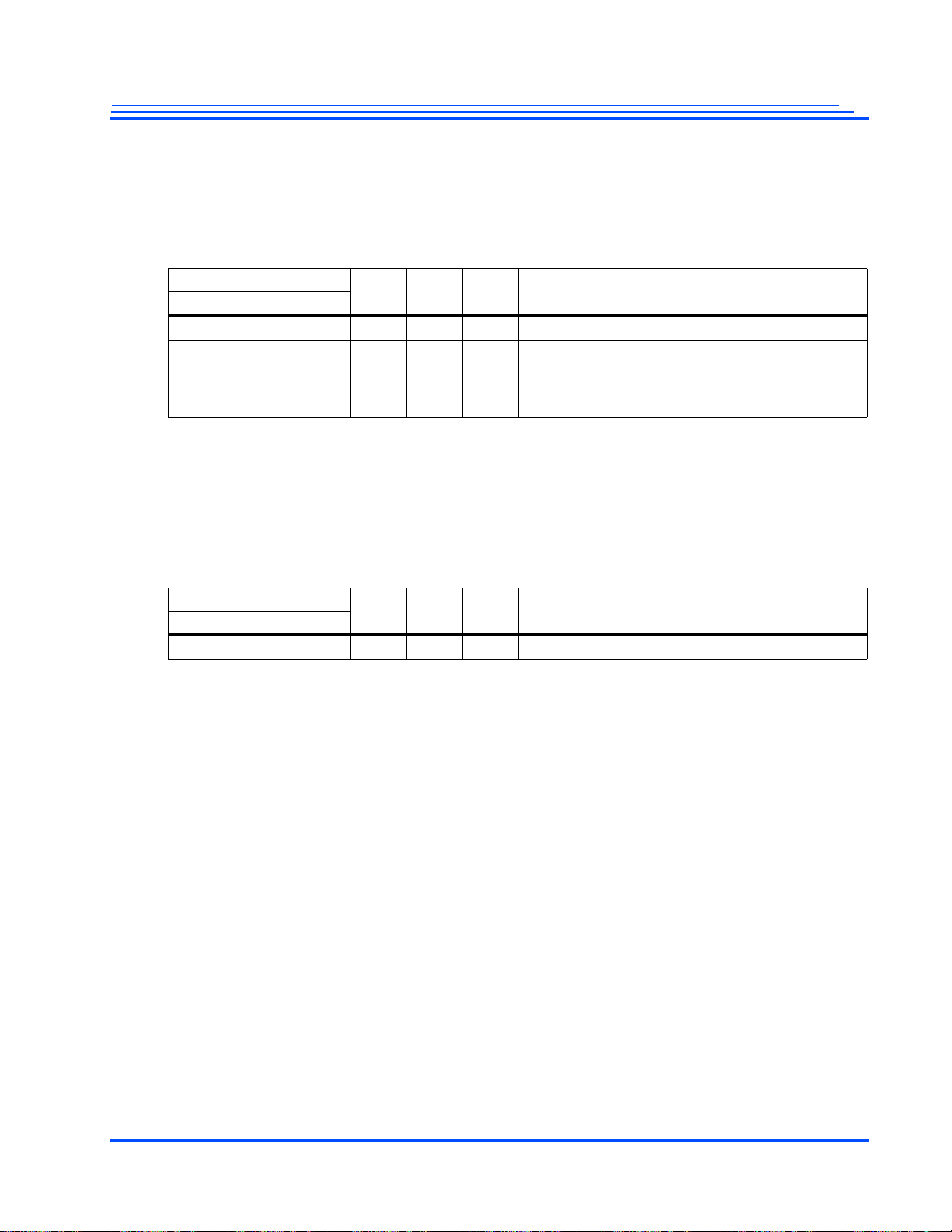

Table 1-1 MG3000 Family of High-Definition H.264 Codecs

Standard Definition Codec

High Definition H.264 Codec 1080p30 720p30

MPEG-2 Decoder

JPEG Codec

Video Input Ports Supported (8-bit or 16-bit) 2 1

Frame Multiplexed Video Inputs 4 –

Video Input Processors 2 2

Video Output Ports Supported (8-bit or 16-bit)

Video Output Prcessors 1 1

Audio Input Ports 2 1

Audio Codecs and Decoders

High-Speed Bitstream I/O –

Embedded ARM926-EJ Processor

Master Mode Operation

Slave Mode Operation

Embedded 10/100/GigE Ethernet MAC

USB On-The-Go including Physical Layer

SD, SDIO, MMC, CE-ATA Peripheral Interface

Compact Flash

32-Bit SDRAM Interface

SPI or Two-Wire Interface 3 2

UARTs 3 3

Pulse Width Modulators 3 3

GPIO, Shared 64 61

GPIO, Dedicated 8 8

1.The MG2580 supports 8-bit output only. MG3500 can support an 8-bit or 16-bit output.

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

Feature MG3500 MG2580

1

11

Maxim Integrated Products Advance Information | 13

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

1.1 Hardware Overview

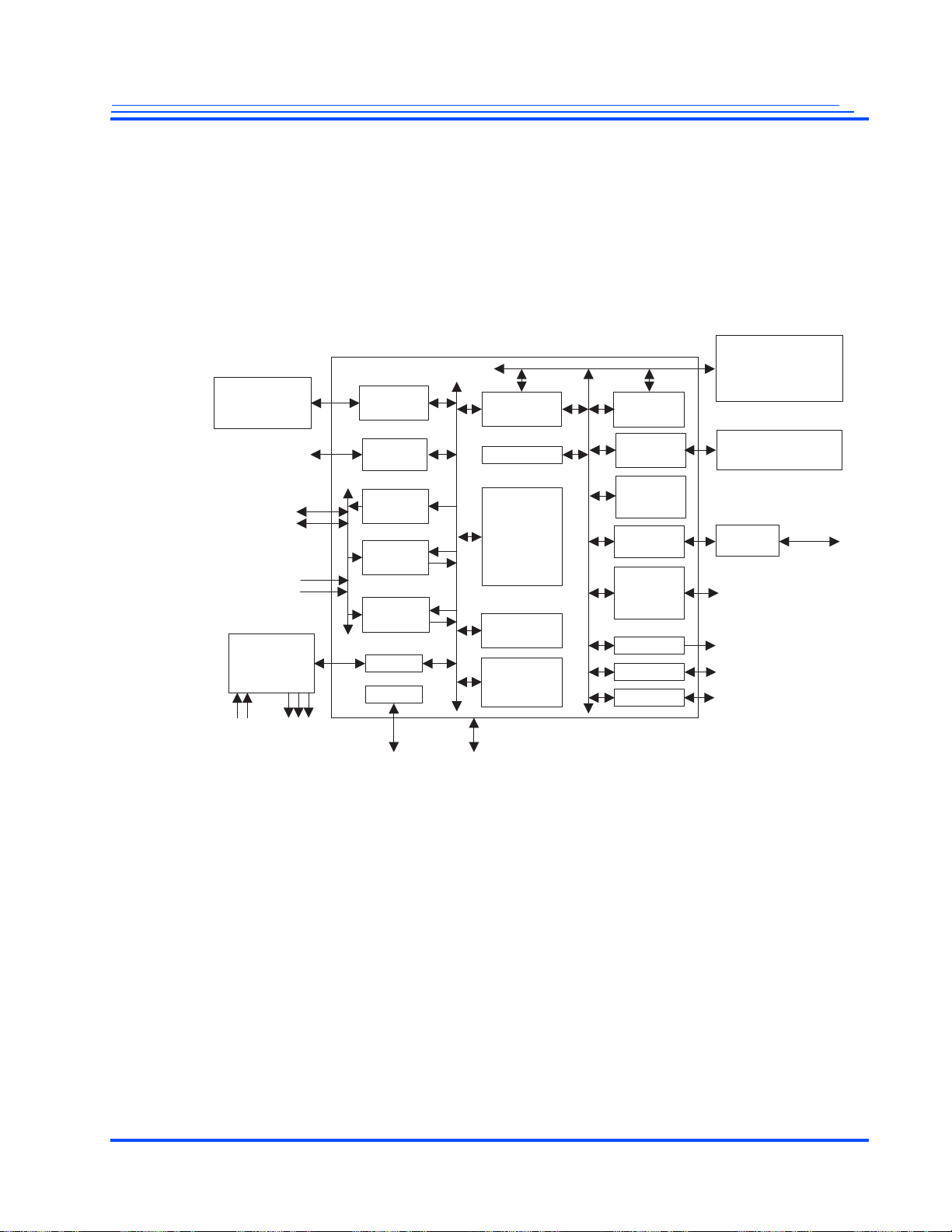

This section provides an overview of each of the blocks in the MG3500 SoC. See “Block Diagram” on

page 11.

1.1.1 Video Codecs

The MG3500 SoC includes efficient hardware implementations of two HD encoders and three HD

decoders:

• H.264 Encoder/Decoder

•MPEG2 Decoder

• JPEG/MJPEG Encoder/Decoder

As shown in Figure 1-2, the H.264 Codec, MPEG2 Decoder and JPEG/MJPEG Codec are implemented

as separate elements in order to support real time trans-coding from one format to another.

The H.264 Codec hardware pipeline allows the highest processing power at the lowest power

consumption to support all of the H.264 tools for the High, Main, and Baseline profiles. The processing

power that enables HD Encoding or Decoding can also be applied to Encoding or Decoding multiple

reduced resolution or SD streams.

The H.264 Codec is capable of encoding or decoding up to 1920 pixels per line (horizontal) and up to

2000 lines (vertical) as long as the total number of 16x16 macroblocks does not exceed 8192 and the

macroblocks per second does not exceed 244800.

The HD MPEG2 Decoder is also capable of decoding up to a maximum of 1920 pixels per line

(horizontal) and 2000 lines (vertical). It does not have encoding capabilities.

The JPEG/MJPEG Codec is also capable of decoding up to a maximum of 1920 pixels per line

(horizontal) and 2000 lines (vertical) for real time video, but in addition, it can encode or decode up to

8k by 8k still images that reside in the memory.

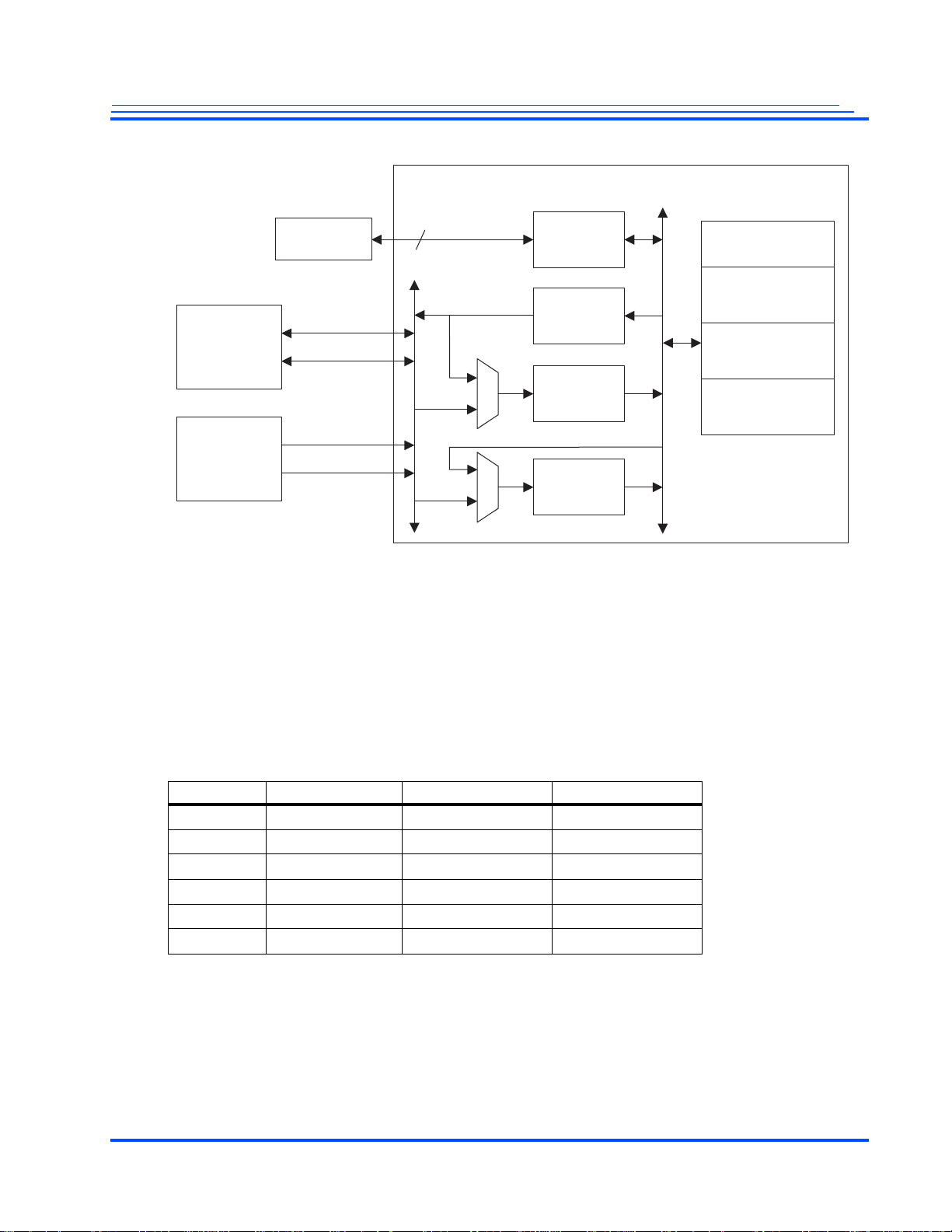

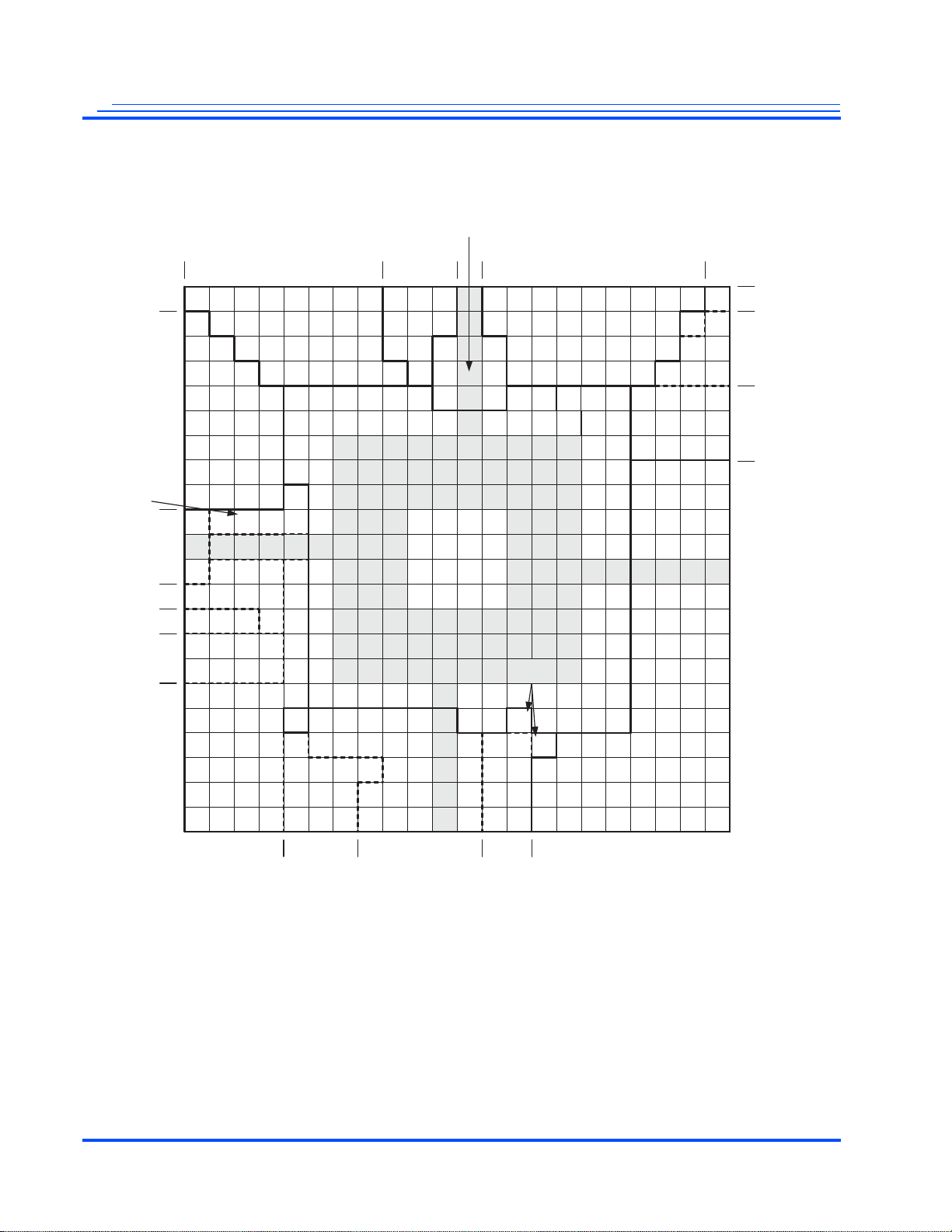

1.1.2 Video Processors and Interfaces

As shown in Figure 1-2, the MG3500 SoC video path has two Video Input Processors (VIP: VIP1 and

VIP2) and one Video Output Processor (VOP).

The Codec has two 8-bit video inputs (VID0 and VID1) that can be used either as two individual 8-bit

ITU-R BT 656 video inputs or a single 16-bit ITU-R BT 1 120 video input fo r HD inputs from an HDMI

receiver or other HD input.

Additionally, the Codec provides two bi-directional ports (VID2 and VID3) that can be used either as

an HD input or as an output (one 8-bit or one 16-bit output).

These bi-directional ports can be clocked at higher frequency to support non-standard video interfaces.

These two 8-bit interfaces can be combined to create a single 16-bit HD ITU-R BT 1120 interface.

The bi-directional video ports can also be used to drive an LCD display in one of two modes. As an

standard output, it can drive an 8-bit RGB LCD interface or it can be used as a 16-bit HD output. Two

additional bits are available to drive an 18-bit RGB LCD interface.

Each video input supports independent clocks and synchronization signals. The clock frequency can be

driven over 100 MHz in order to support non-standard video inputs including HD sensors with 8- bit

interfaces.

14 | Advance Information Maxim Integrated Products

Memory

Controller

VIP2

180 MHz

VIP1

180 MHz

VOP

125 MHz

Two 8-Bit

Video I/Os

125 MHz

Maximum

Memory

Two 8-Bit

Video Inputs

125 MHz

Maximum

Video Portion of the MG3500 and MG3264 Codec

From Memory

RGB or

YUV 4:2:2

Video

Codecs

High Definition

H.264 Codec

High Definition

MPEG2 Decoder

High Definition

JPEG Codec

VID0_D[7:0]

VID1_D[7:0]

VID2_D[7:0]

VID3_D[7:0]

32-bit Data

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

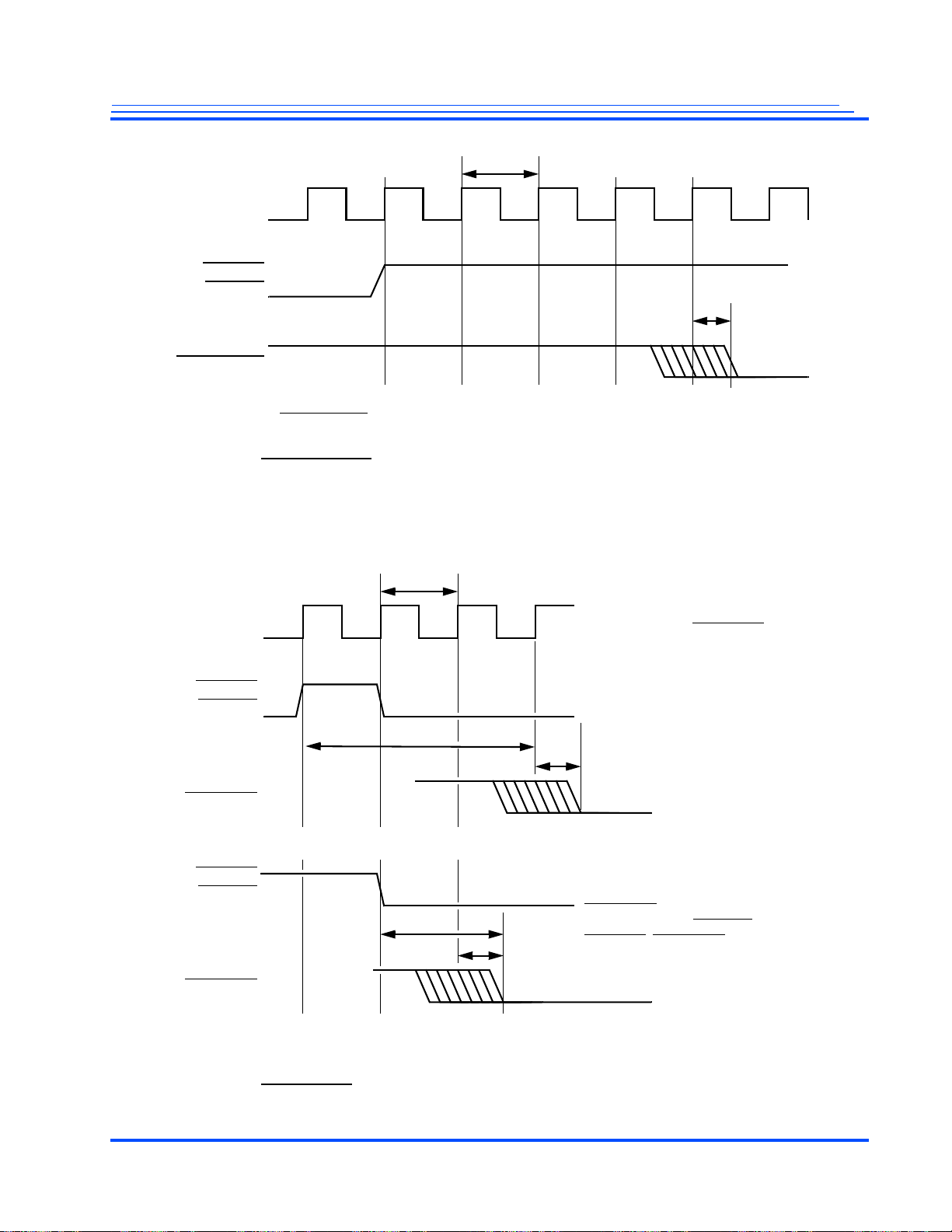

Figure 1-2 Block Diagram of the Video Input Section

The two VIPs and one VOP provide the capability of processing two independent video inputs and one

independent video output. Together with the flexible Video Interfaces described above, the modes

shown in Table 1-2 are supported.

Note: Video composition features, such as memory-based scaling or merging multiple videos into one

screen are not available when two VIPs are both used as inputs.

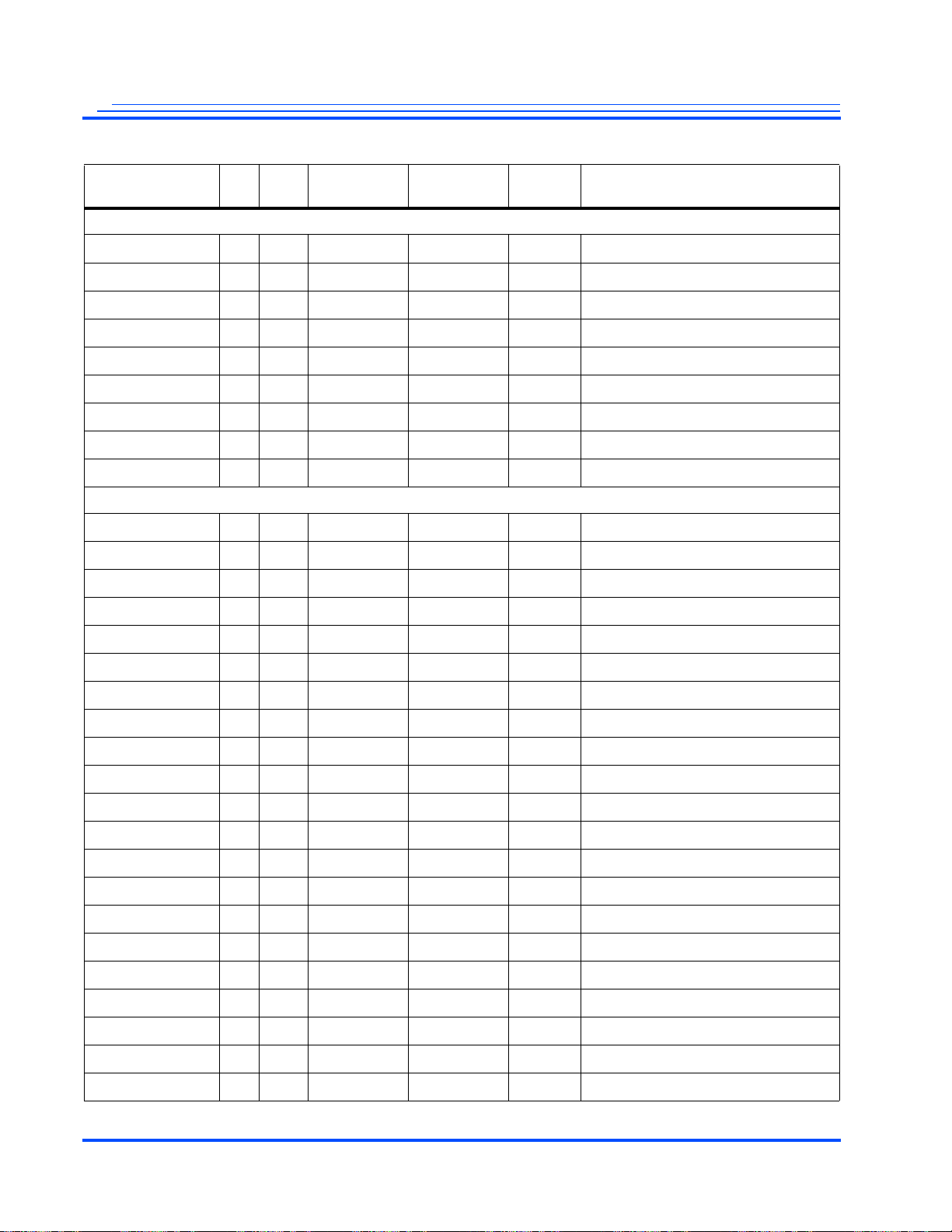

Table 1-2 Video Modes

Video Mode Video Inputs Video Outputs Video Composition

11 HD 1 HD Yes

2 1 HD 1 SD Yes

3 2 HD None Not Available

4 2 SD 1 HD Not Available

5 1 SD + 1 HD 1 SD Not Available

6 2 SD 1 SD Not Available

Note: The HD output can be used as an 18-bit LCD interface and an SD output can be used as an 8-bit

LCD interface.

Maxim Integrated Products Advance Information | 15

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

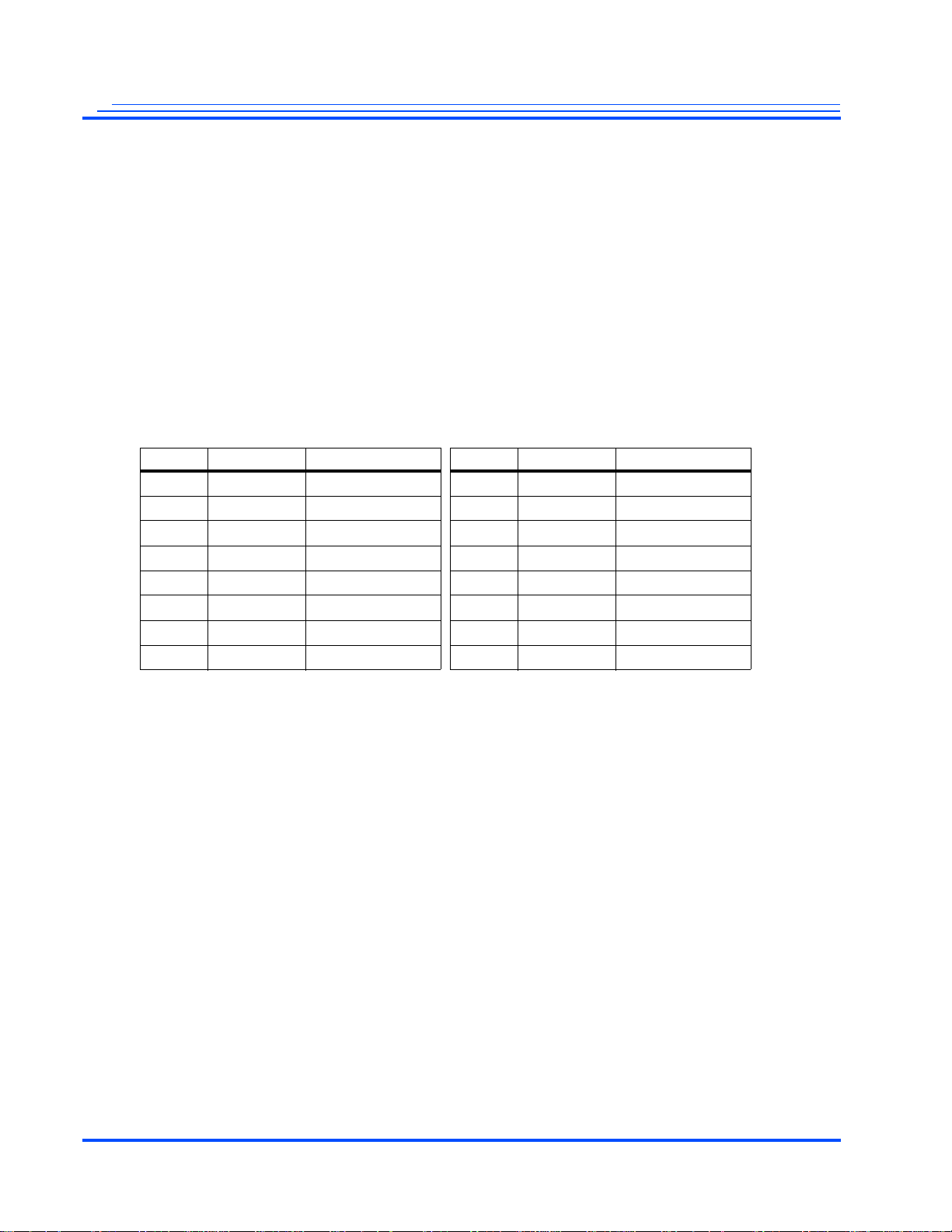

1.1.3 Video Input Processor

There are two identical Video Input Processors (VIPs) that perform high quality scaling, chroma and

gamma adjustment, filtering, and the extraction of video analytics. The maximum pixel rate that the VIP

can process corresponds to video input of resolution 1920x1080i at 30 frames per seconds.

1.1.4 Video Output Processor

The Video Output Processor (VOP) performs high quality scaling of un-compressed video, overlays it

with two graphic planes, performs gamma and chroma adjustment, overlays a hardware cursor, and

outputs the combined video to a video port. Each graphic plane can be from 1 to 32 bits. Graphic planes

using less than eight bits use a Look-Up Table (LUT).

Note: Some formats may not be possible depending on the output resolution and available system memory

bandwidth. For example 32 bits/pixel modes are not possible for 1080i60 resolution output.

Table 1-3 Video Output Modes

Mode Bits/Pixel Format Mode Bits/Pixel Format

0 1 Indexed 16 16 RGB 4:4:4

1 1 Grayscale 17 16 RGB 4:4:4:4

2 2 Indexed 18 16 RGB 5:5:5

3 2 Grayscale 19 16 RGB 5:5:5:1

4 4 Indexed 20 16 RGB 5:6:5

5 4 Grayscale 21 16 RGB 5:6:4:1

6 8 Indexed 24 32 RGB 8:8:8

7 8 Grayscale 25 32 RGB 8:8:8:8

The video output can be either be YCbCr via an 8-bit ITU-R BT 656 interface, YCbCr via a 16-bit

ITU-R BT 1120 interface, RGB via an 8-bit interface, or RGB via an 18-bit interface. In some of the

output modes, the MG3500/MG2580 HD H.264 Codec SoC is also capable of generating optional

external sync signals.

1.1.5 Video Multi-Media Engine

The V ideo Multi-Media Engine (MME) is a proprietary Reduced Instruction Set Computer (RISC) that

has been optimized for single cycle context switching and low power. The Video MME controls all

aspects of the VIPs, Video Cores, and the VOP (see the MG3500/MG2580 HD H.264 Codec SoC Block

Diagram on page 3 for more information).

1.1.6 Audio Multi-Media Engine

The Audio MME implements all audio Codecs in firmware.

1.1.7 Audio Interfaces

There are two I2S inputs, three I2S outputs, and one S/PDIF output. One of the two I2S inputs is

associated with one of the audio clocks. The other audio input, the three audio outputs, and the S/PDIF

output must share a common clock and sample rate. The three I

2

S outputs and the S/PDIF output must

also share a common format.

16 | Advance Information Maxim Integrated Products

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

1.1.8 SDRAM

The MG3500/MG2580 HD H.264 Codec SoC has a high performance memory subsystem that uses

either a 16- or 32-bit wide external SDRAM. The SDRAM is DDR2, and runs up to 264 MHz.

1.1.9 ARM926-EJ

The MG3500/MG2580 HD H.264 Codec SoC has an embedded ARM926-EJ processor that runs at

speeds up to 240 MHz. This processor is not used for Audio or Video Codec functions, so it is

completely available to implement any required system level functions. Mobilygen provides Codec and

Data Streaming APIs under Linux 2.6.20.

1.1.10 Ethernet Media Access Controller

The Ethernet MAC supports 10/100/1000 Mbps Ethernet interfaces.1 This is typically connected to an

external Physical Layer (Phy) device but can also be connected directly to Ethernet switches that

support Reverse MII interfaces.

1.1.11 USB 2.0

The USB interface is USB 2.0, High-Speed with the ability to operate as Device, Host, or On-The-Go

(OTG) at speeds of up to 480 MHz. The USB interface includes the Physical Layer.

1.1.12 FLASH, IDE and Host Interface

The host interface can be used to communicate to external devices including NOR FLASH, NAND

FLASH, and COMPACT FLASH, as well as other devices.

1.1.13 SD/MMC Interface

The SD/MMC interface is designed to support Secure Digital (SD), Secure Digital Input/Output

(SDIO), Multi-Media Card (MMC), and Consumer Electronics A T Attachment (CE-AT A) devices. This

four-bit wide interface supports up to a 25 MHz clock rate (100 Mbits/sec. transfer rate).

1.1.14 AES and SHA Hardware Acceleration

The MG3500 SoC design includes hardware acceleration for the Advanced Encryption Standard (AES)

and Secure Hashing Algorithm (SHA). The AES accelerator supports CBC, CTR, ECB, and CCM

modes with 128, 192, and 256 bit keys for secure data storage and transmission. The SHA accelerator

supports the creation of 128, 224, and 256 bit digests for Digital Signatures and Digital Time Stamps.

1.1.15 Serial and Misc. IO

The MG3500 SoC has several UARTs for communication, Pulse Width Modulators (PWMs) for

control, I

2

C-compatible T wo W ire Interfaces (TWIs) for device control, and Serial Peripheral Interfaces

(SPIs) for device control.

The MG3500 SoC also has eight dedicated General Purpose Input/O utput (GPIO) pins and up to 64

shared GPIO pins that can be used for system control. The shared GPIO pins are multiplexed with other

functions and are only available when the primary function for the pin is not being used. For example,

if your design does not require a SPI interface (see “SPI/Bitstream Interface Timing” on page 89), the

four pins dedicated to that interface can be used as GPIO pins.

1. When both 10/100 and GigE need to be enabled, an external switch must be installed to select the clock.

Maxim Integrated Products Advance Information | 17

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

Customer Production

Applications or Mobilygen

Demonstrations, Web-

based Applications,

Command Line Shell

Applications, and Plug-ins

APPLICATION SOFTWARE

Built on Mobilygen's Demonstration Product Applications,

Web-based, Command Line Shell, and Plug-in Modules

Mobilygen Software can

run on an Embedded

ARM926 or an External

Processor

Mobilygen CODECs

and Silicon

SUPPORT SOFTWARE

Production Ready Drivers and APIs

CODECs and SILICON

Production Ready Firmware and Silicon

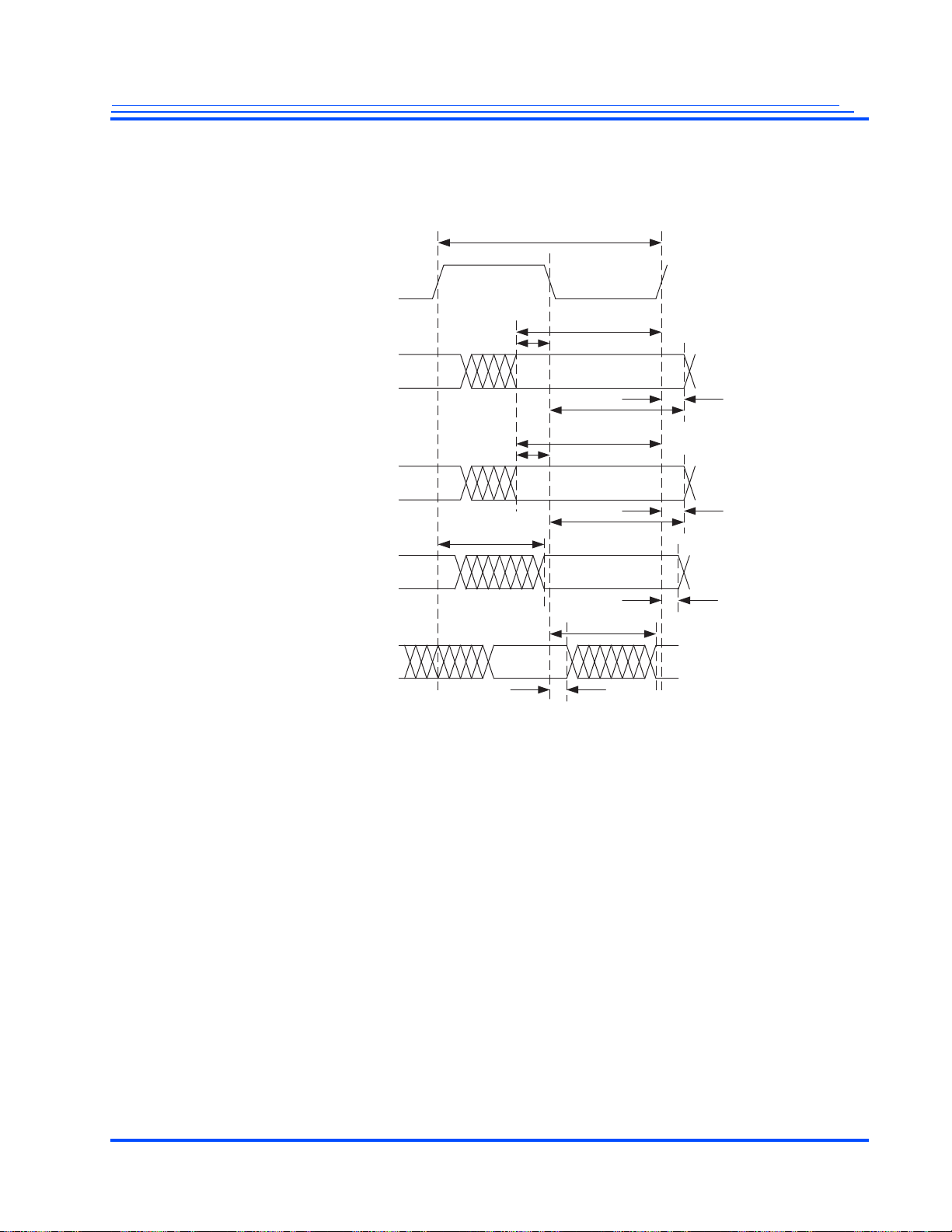

1.2 Support Tools

This section provides an overview of the software and hardware development tools that are available to

support the part.

Figure 1-3 Software Architecture

The Mobilygen-developed MG3500 SoC software is developed for Linux 2.6.20. Mobilygen supplies

these APIs and Drivers:

•Codec API

• qHAL Hardware Abstraction Layer

• Data Streaming API

• On-Chip Device Drivers

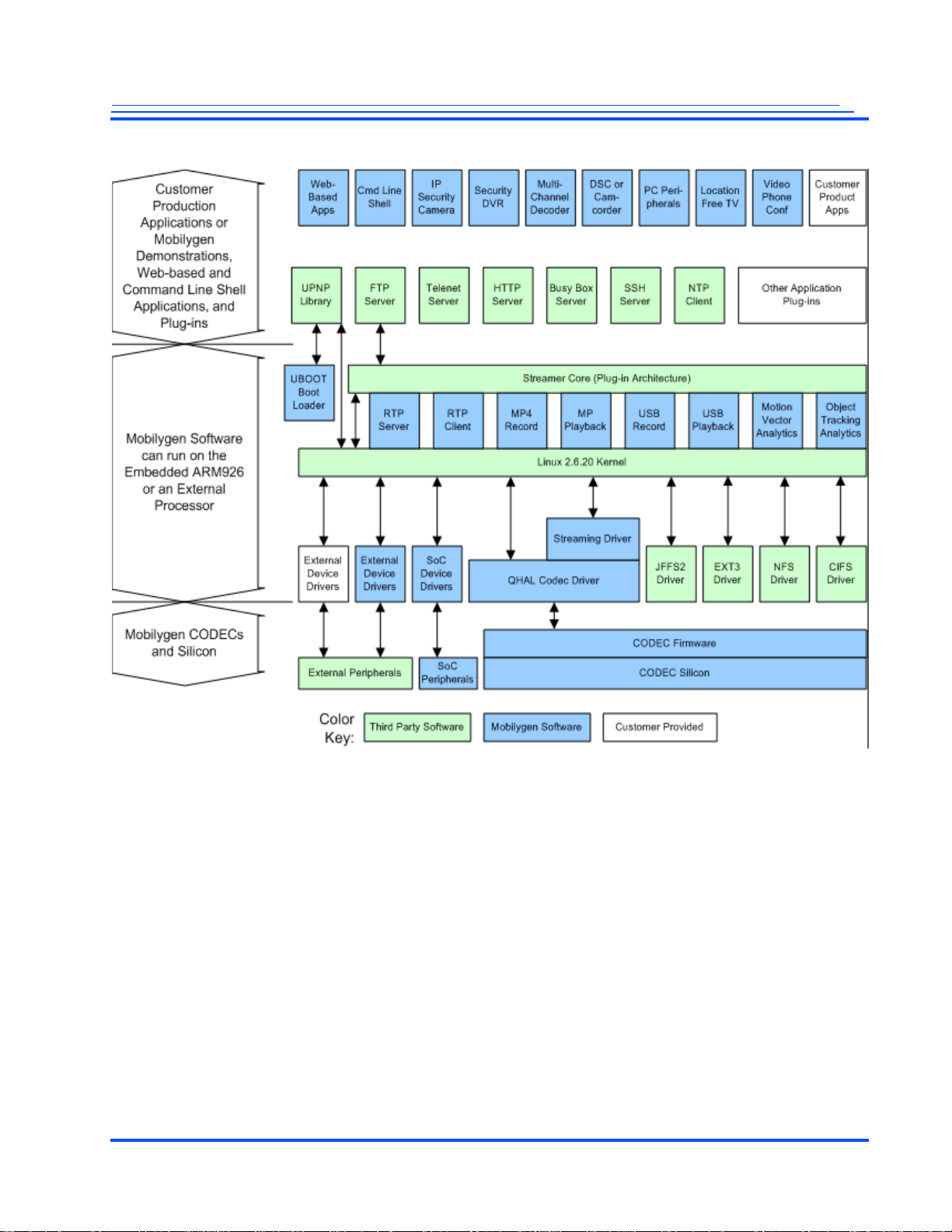

Figure 1-4 shows an expanded version of Figure 1-3 that has all of the elements of the system software

included. In this figure:

• Blue boxes are applications, firmware, drivers, and silicon supplied by Mobilygen.

• Green boxes are applications that are available from third-party vendors (public domain or Linux

vendors)

• White boxes are customer-written applications

18 | Advance Information Maxim Integrated Products

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

Figure 1-4 Software Elements

Note: As shown in Figure 1-4, the Mobilygen supplied drivers and higher-level functions (the lower

two-thirds of Figure 1-4) are production ready and fully supported by Mobilygen. The Customer

Production Applications and Mobilygen Demonstration programs (the upper third of Figure 1-4) are

available for customers to use as an advanced starting point, but are not production ready.

Maxim Integrated Products Advance Information | 19

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

20 | Advance Information Maxim Integrated Products

2.0 Device Overview, Pin Assignments

2.1 Naming Conventions

The MG3500 SoC has both signal and power connections. Each signal has a unique name. Power

connections do not necessarily have unique names.

The signals are organized by signal groups. The signal names typically have two parts separated by an

underscore. When that is the case the first part represents the name of the signal group a nd the second

part defines the function within that group. The signal gr oup names do not have an underscore in them,

so the first underscore separates the signal group name from the function name. The function name may

have an underscore in it. Signals that are active low end with a lower case ‘n’.

Power connection names also have two parts separated by an underscore. The first part represents the

power domain, and the second part represents the power type.

All pins have a Primary function, and the name that is assigned to the pin reflects that primary function.

Many of the pins have an Alternate (ALT) function that can be used if the primary function is not used.

Some pins are capable of being used as General Purpose I/O pins (GPIO) is neither their primary or their

secondary functions are being used. These pins are available for customer-assigned uses.

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

The pinout diagrams and tables in this section list the pins by their Primary name. The pinout tables also

show the Alternate and GPIO capabilities of the pins if any are assigned to them.

Maxim Integrated Products Advance Information | 21

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

RESET Group

AUDIO Power

1234567891011

A

B

C

D

E

F

G

H

J

K

L

12 13 14 15 16 17 18 19 20 21 22

M

N

P

R

T

U

V

W

Y

AA

AB

12345678910111213141516171819202122

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

JTAG Group

AUDIO Power

AUDIOGroup

AUDIO Power

DDR Group

DDR Power

CF Group

HOST Power

HOST Group

HOST Power

HOST Group

HOST Power

PWM Group

HOST Power

UART Group

HOST Power

TWI Group

HOST Power

DDR Group

DDR Power

VID01 Group

VID01 Power

VID23 Group

VID23 Power

USB Group

USB Power

CONFIG Group

VID01 Power

ETH Group

ETH Power

SPI Group

HOST Power

SDMMC Group

HOST Power

GPIO Group

HOST Power

HOST

CS0n

HOST

CS5n

GPIO3GPIO2GPIO

1

GPIO7GPIO6GPIO

5

GPIO

0

GPIO

4

UART0

RTS

UART0

TXD

UART1

RXD

UART0

CTS

UART0

RXD

UARTD

TXD

UARTD

RXD

UART1

TXD

TWI0

SDA

PWM2PWM1PWM

0

HOST

D12

HOST

D13

HOST

D14

HOSTD8HOSTD9HOST

D10

HOSTD4HOSTD5HOST

D6

HOSTD2HOSTD3HOST

WEn

HOSTD1HOST

D_EN

HOST

WAIT

HOST

D15

HOST

D11

HOST

D7

CF

INPACKn

HOST

A12

HOST

ALEnCFIORDnCFBVD2

HOST

INTnCFIOWRnCFCD1

HOST

A11

HOST

A10

HOST

A8

CF

RESETCFREGn

HOST

A6

CFWPHOSTA5HOST

A2

HOST

A7

HOST

A3

HOSTD0HOST

REn

HOST

DMARQ

HOSTWPCF

BVD1CFCD2CFWAITn

HOSTA4HOST

A1

HOST

A22

HOST

A21

HOST

VDD

HOST

A20

HOST

A19

CORE

VDD

HOST

A18

HOST

VDD

HOST

A17

HOST

A16

HOST

VDD

HOST

VDD

HOST

VDD

HOST

A15

HOST

A14

HOST

A13

HOST

VDD

HOST

A9

CORE

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

HOST

CS4n

HOST

CS3n

HOST

CS2n

HOST

CS1n

CLK

IN

SDMMCCDSDMMC

D1

SDMMCWPSDMMC

D0

SDMMCD3SDMMC

CLK

DDR

BA0

DDR

WEn

DDRA1DDR

BA1

DDR

CASn

DDRA2DDR

A10

DDR

RASn

DDR

CKE

DDR

DQ5

DDR

DQ7

DDR

A12

DDRA6DDR

DQ0

DDRA8DDRA7DDR

A9

DDR

DQS0n

DDR

DQS0

DDR

DQ1

DDR

DQ3

DDR

DQ4

DDR

DQ2

SDMMCD2SDMMC

CMD

DDRA3DDRA0DDR

CSn

DDRA5DDRA4DDR

A11

DDR

VREF

DDR

DQ6

DDR

VDD

DDR

VDD

DDR

VDD

DDR

VDD

DDR

PADHI

DDR

DQ31

DDR

PADLO

DDR

DQ25

DDR

VDD

DDR

DQS1n

DDR

DQM1

DDR

DQ9

DDR

DQS1

DDR

DQ30

DDR

DQ28

DDR

DQ27

DDR

DQ29

DDR

CLK1

DDR

CLK1n

DDR

CLK0

DDR

CLK0n

HOST

VDD

CORE

VDD

PLL

VDD

CORE

VDD

CLK

SEL

CORE

VDD

DDR

VDD

CORE

VDD

DDR

VDD

DDR

VDD

DDR

DQ14

DDR

DQ15

DDR

DQM0

DDR

DQ8

DDR

DQ13

DDR

DQ11

DDR

DQ10

DDR

DQ12

CORE

GND

CORE

GND

CORE

GND

CORE

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

CLK Grp

HOST Pwr

JTAG

TDO

TEST

JTAG

TAP_SEL

JTAG

TDI

JTAG

TRSTn

JTAG

TCK

JTAG

TMS

CFG

HOST1

CFG

HOST0

VID0

FIELD

VID0

OUTCLK

VID0

PIXCLK

VID0

VSYNC

VID0

HSYNC

VID0

D0

VID0D1VID0D5VID1

PIXCLK

VID0D2VID0

D6

VID1

OUTCLK

VID0D3VID0D7VID1

VSYNC

VID0D4VID1

FIELD

VID1

HSYNC

VID1D0VID1D4VID1

D7

VID1D1VID1D5VID01

MOSI

VID1D2VID1D6VID01

MCLK

VID1D3VID01

MSS

VID01

MISO

RESETn

CFG

0

VID01

VDD

AUD1

MCLK

AUD1

BCK

AUD1

LRCK

AUD1

IDAT

CORE

VDD

VID01

VDD

VID01

VDD

CORE

VDD

AUD

VDD

CORE

VDD

DDR

VDD

DDR

VDD

AUD

VDD

AUD0

ODAT1

AUD0

ODAT2

AUD0

MCLK

AUD0

BCK

DDR

VDD

DDR

DQ18

DDR

DQM2

DDR

DQ19

DDR

DQ20

DDR

DQM3

DDR

DQ23

AUD0

IDAT

AUD0

SPDIF

AUD0

LRCK

AUD0

ODAT0

DDR

DQS2n

DDR

DQS2

DDR

DQ17

DDR

DQ16

DDR

DQ21

DDR

DQ22

DDR

VDD

DDR

DQ26

DDR

DQ24

DDR

DQS3n

DDR

DQS3

CORE

GND

DDR

GND

DDR

GND

DDR

GND

CORE

GND

CORE

GND

VID01

GND

AUD

GND

AUD

GND

DDR

GND

DDR

GND

VID01

GND

CFG

3

CFG

2

VID23

MCLK

VID2D0VID2D1VID2D4VID2D6VID2

PIXCLK

ETH

RXERR

VID23

MISO

VID2D2VID2D5VID2D7VID2

FIELD

ETH

RXCLK

ETH

RXDV

VID23

MOSI

VID2D3VID2

VSYNC

VID23

D16

ETH

RXD7

ETH

RXD2

ETH

RXD1

VID23

MSS

VID2

HSYNC

VID3

D1

VID3D2VID3D6USB

XIN

USBDMUSB

DP

VID3D3VID3D7USBXOUSB

VBUS

USB

ID

VID3D0VID3

D4

USB

D_VBUS

USB

REXT

VID3D5VID23

D17

VID23

GPIO

USB

ANA_TST

ETH

RXD6

ETH

RXD3

ETH

RXD0

ETH

COL

ETH

RXD5

ETH

RXD4

ETH

MDCLK

ETH

CRS

ETH

TXEN

ETH

TXD4

ETH

TXD0

ETH

MDIO

ETH

TXERR

ETH

TXD5

ETH

TXD3

ETH

TXD2

ETH

TXD7

ETH

TXD6

ETH

TXCLK

ETH

TXD1

TWI0

SCL

SPI

MOSI

SPI

MCLK

SPI

MSS1

VID23

VDD

VID23

VDD

ETH

VDD

ETH

VDD

USB

AGND

USB

AGND

USB

AGND

USB

ACGND

CFG

1

VID23

VDD

USB

AVDD

USB

AVDD

USB

ACVDD

USB

DVDD

SPI

MISO

CORE

VDD

SPI

MSS0

ETH

GND

ETH

GND

VID23

GND

VID23

GND

CORE

GND

CORE

GND

USB

DGND

VID23

GND

VID01

GND

CORE

VDD

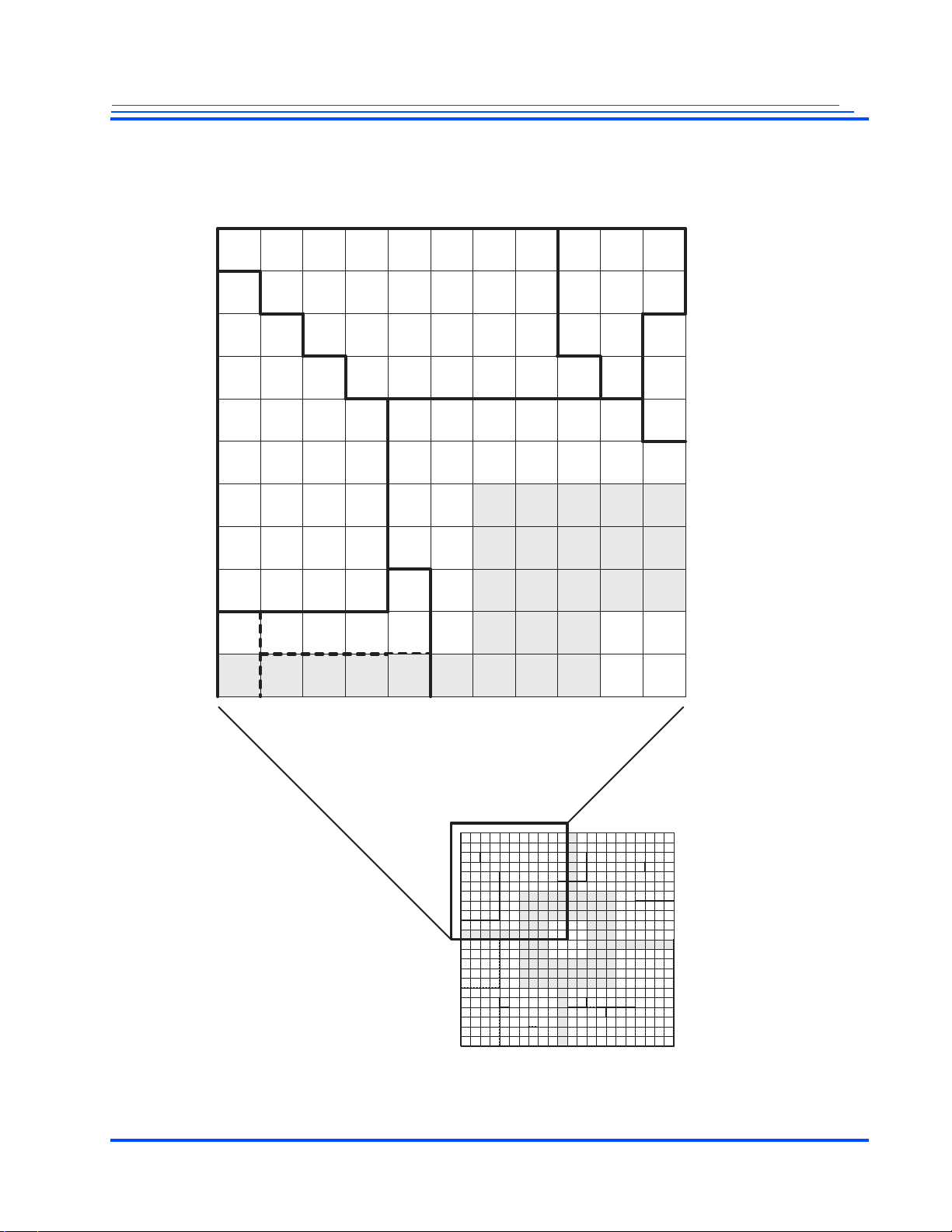

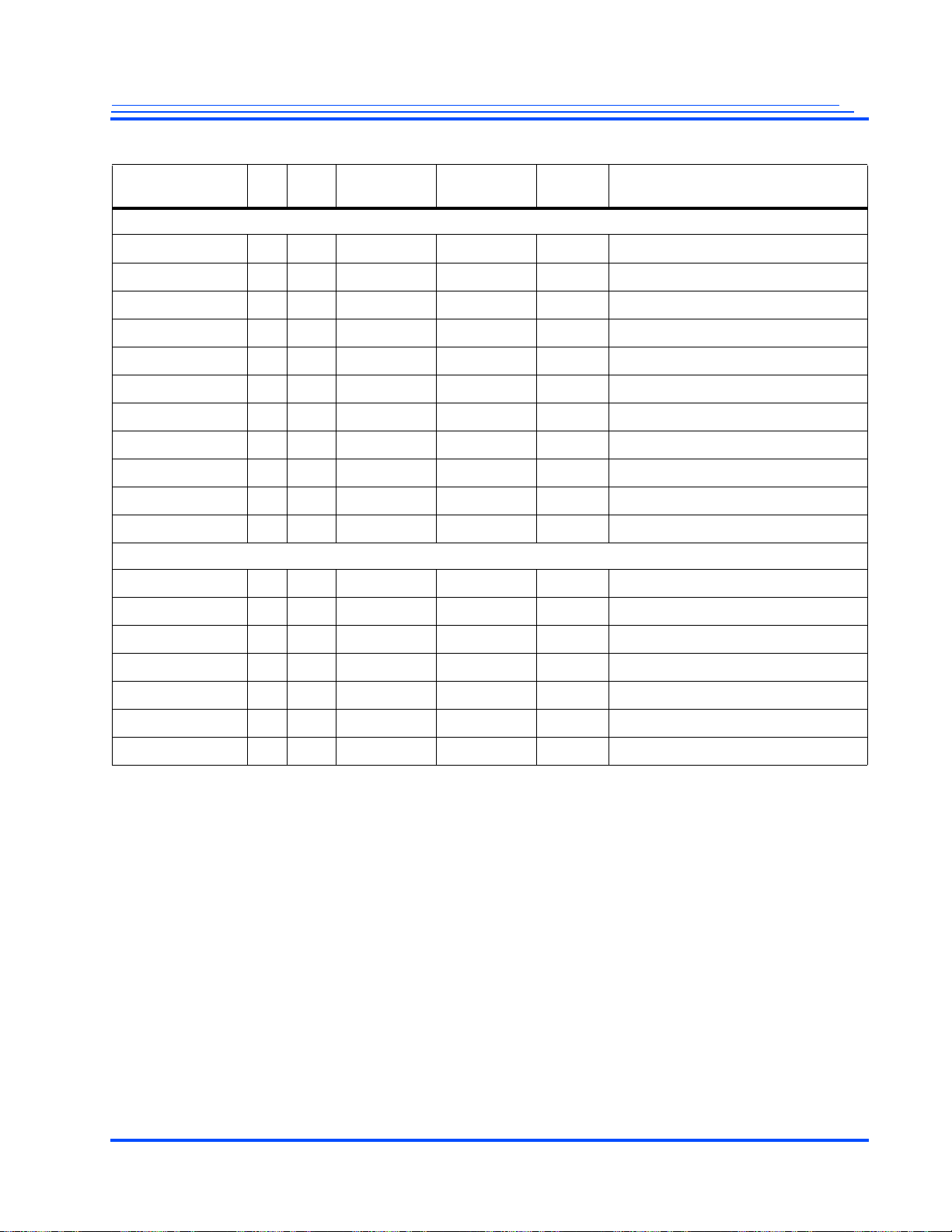

2.2 Pinout Diagrams

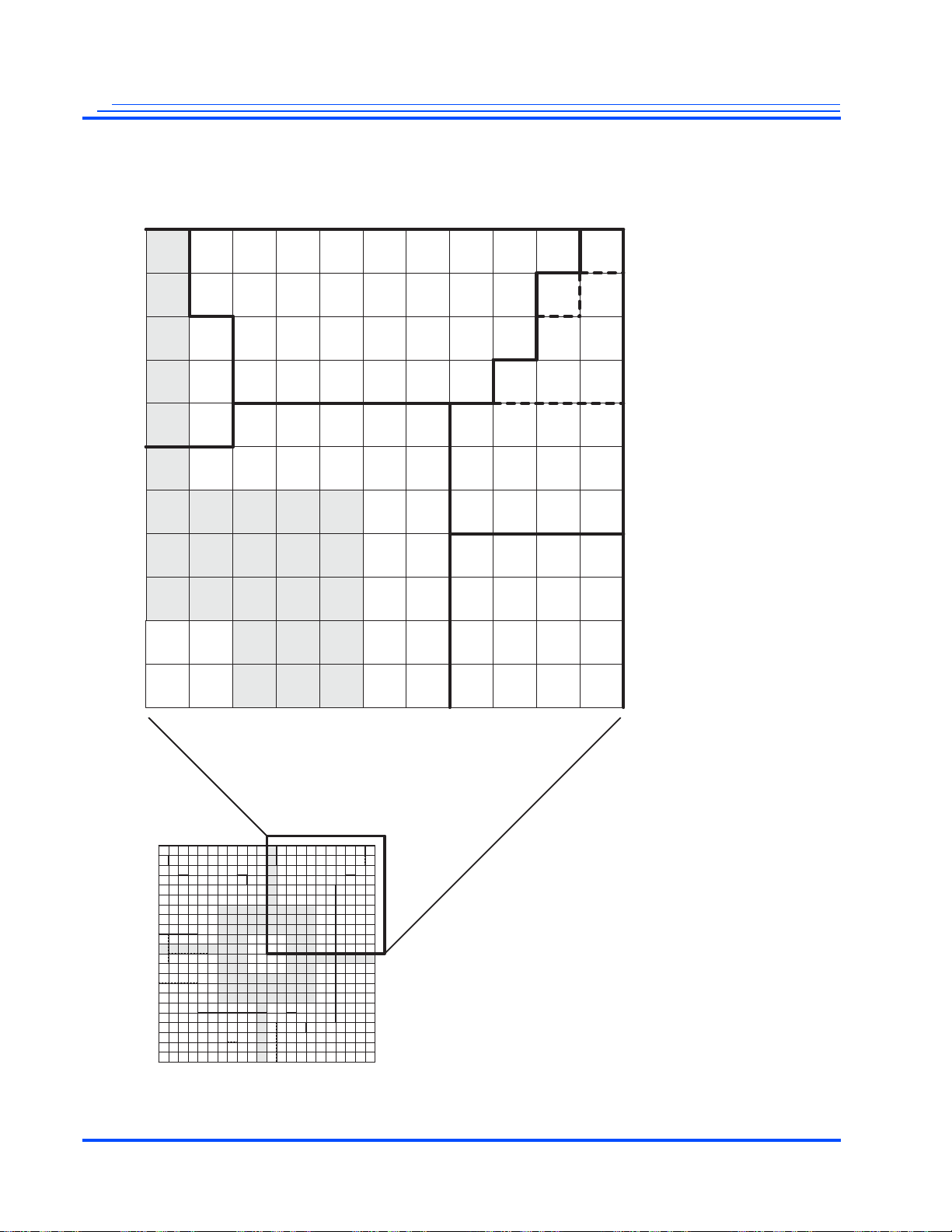

Figure 2-1 shows a map of all the signal positions.

22 | Advance Information Maxim Integrated Products

Figure 2-1 Map of all the MG3500 SoC Signal Positions (Top View)

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

1234567891011

A

B

C

D

E

F

G

H

J

K

L

CFG

3

CFG

2

VID23

MCLK

VID2D0VID2D1VID2D4VID2D6VID2

PIXCLK

ETH

RXERR

VID23

MISO

VID2D2VID2D5VID2D7VID2

FIELD

ETH

RXCLK

ETH

RXDV

VID23

MOSI

VID2D3VID2

VSYNC

VID23

D16

ETH

RXD7

ETH

RXD2

ETH

RXD1

VID23

MSS

VID2

HSYNC

VID3

D1

VID3D2VID3D6USB

XIN

USBDMUSB

DP

VID3D3VID3D7USBXOUSB

VBUS

USB

ID

VID3D0VID3

D4

USB

D_VBUS

USB

REXT

VID3D5VID23

D17

VID23

GPIO

USB

ANA_TST

ETH

RXD6

ETH

RXD3

ETH

RXD0

ETH

COL

ETH

RXD5

ETH

RXD4

ETH

MDCLK

ETH

CRS

ETH

TXEN

ETH

TXD4

ETH

TXD0

ETH

MDIO

ETH

TXERR

ETH

TXD5

ETH

TXD3

ETH

TXD2

ETH

TXD7

ETH

TXD6

ETH

TXCLK

ETH

TXD1

TWI0

SCL

SPI

MOSI

SPI

MCLK

SPI

MSS1

VID23

VDD

VID23

VDD

ETH

VDD

ETH

VDD

USB

AGND

USB

AGND

USB

AGND

USB

ACGND

CFG

1

VID23

VDD

USB

AVDD

USB

AVDD

USB

ACVDD

USB

DVDD

SPI

MISO

CORE

VDD

SPI

MSS0

ETH

GND

ETH

GND

VID23

GND

VID23

GND

CORE

GND

CORE

GND

USB

DGND

VID23

GND

VID01

GND

1234567891011

A

B

C

D

E

F

G

H

J

K

L

CFG

3

CFG

2

VID23

MCLK

VID2D0VID2D1VID2D4VID2D6VID2

PIXCLK

ETH

RXERR

VID23

MISO

VID2D2VID2D5VID2D7VID2

FIELD

ETH

RXCLK

ETH

RXDV

VID23

MOSI

VID2D3VID2

VSYNC

VID23

D16

ETH

RXD7

ETH

RXD2

ETH

RXD1

VID23

MSS

VID2

HSYNC

VID3

D1

VID3D2VID3D6USB

XIN

USBDMUSB

DP

VID3D3VID3D7USBXOUSB

VBUS

USB

ID

VID3D0VID3

D4

USB

D_VBUS

USB

REXT

VID3D5VID23

D17

VID23

GPIO

USB

ANA_TST

ETH

RXD6

ETH

RXD3

ETH

RXD0

ETH

COL

ETH

RXD5

ETH

RXD4

ETH

MDCLK

ETH

CRS

ETH

TXEN

ETH

TXD4

ETH

TXD0

ETH

MDIO

ETH

TXERR

ETH

TXD5

ETH

TXD3

ETH

TXD2

ETH

TXD7

ETH

TXD6

ETH

TXCLK

ETH

TXD1

TWI0

SCL

SPI

MOSI

SPI

MCLK

SPI

MSSI

VID23

VDD

VID23

VDD

ETH

VDD

ENET

VDD

USB

AGND

USB

AGND

USB

AGND

USB

ACGND

CFG

1

VID23

VDD

USB

AVDD

USB

AVDD

USB

ACVDD

USB

DVDD

SPI

MISO

CORE

VDD

SPI

MSSO

ETH

GND

ETH

GND

VID23

GND

VID23

GND

CORE

GND

CORE

GND

USB

DGND

VID23

GND

VID01

GND

12 13 14 15 16 17 18 19 20 21 22

A

B

C

D

E

F

G

H

J

K

L

JTAG

TDO

TEST

JTAG

TAP_SEL

JTAG

TDI

JTAG

TRSTn

JTAG

TCK

JTAG

TMS

CFG

HOST1

CFG

HOST0

VID0

FIELD

VID0

OCLK

VID0

PIXCLK

VID0

VSYNC

VID0

HSYNC

VID0

D0

VID0D1VID0D5VID1

PIXCLK

VID0D2VID0D6VID1

OCLK

VID0D3VID0D7VID1

VSYNC

VID0D4VID1

FIELD

VID1

HSYNC

VID1D0VID1D4VID1

D7

VID1D1VID1D5VID01

MOSI

VID1D2VID1D6VID01

MCLK

VID1D3VID01

MSS

VID01

MISO

RESETn

CFG0CORE

VDD

VID01

VDD

AUD1

MCLK

AUD1

BCK

AUD1

LRCK

AUD1

IDAT

CORE

VDD

VID01

VDD

VID01

VDD

CORE

VDD

AUD

VDD

CORE

VDD

DDR

VDD

DDR

VDD

AUD

VDD

AUD0

ODAT1

AUD0

ODAT2

AUD0

MCLK

AUD0

BCK

DDR

VDD

DDR

DQ18

DDR

DQM2

DDR

DQ19

DDR

DQ20

DDR

DQM3

DDR

DQ23

AUD0

IDAT

AUD0

SPDIF

AUD0

LRCK

AUD0

ODAT0

DDR

DQS2n

DDR

DQS2

DDR

DQ17

DDR

DQ16

DDR

DQ21

DDR

DQ22

DDR

VDD

DDR

DQ26

DDR

DQ24

DDR

DQS3n

DDR

DQS3

CORE

GND

DDR

GND

DDR

GND

DDR

GND

CORE

GND

CORE

GND

VID01

GND

AUD

GND

AUD

GND

DDR

GND

DDR

GND

VID01

GND

12 13 14 15 16 17 18 19 20 21 22

W

Y

AA

AB

M

N

P

R

T

U

V

HOST

CS4n

HOST

CS3n

HOST

CS2n

HOST

CS1n

CLKINSDMMCCDSDMMC

D1

SDMMCWPSDMMC

D0

SDMMCD3SDMMC

CLK

DDR

BA0

DDR

WEn

DDRA1DDR

BA1

DDR

CASn

DDRA2DDR

A10

DDR

RASn

DDR

CKE

DDR

DQ5

DDR

DQ7

DDR

A12

DDRA6DDR

DQ0

DDRA8DDRA7DDR

A9

DDR

DQS0n

DDR

DQS0

DDR

DQ1

DDR

DQ3

DDR

DQ4

DDR

DQ2

SDMMCD2SDMMC

CMD

DDRA3DDRA0DDR

CSn

DDRA5DDRA4DDR

A11

DDR

VREF

DDR

DQ6

DDR

VDD

DDR

VDD

DDR

VDD

DDR

VDD

DDR

PADHI

DDR

DQ31

DDR

PADLO

DDR

DQ25

DDR

VDD

DDR

DQS1n

DDR

DQM1

DDR

DQ9

DDR

DQS1

DDR

DQ30

DDR

DQ28

DDR

DQ27

DDR

DQ29

DDR

CLK1

DDR

CLK1n

DDR

CLK0

DDR

CLK0n

HOST

VDD

CORE

VDD

PLL

VDD

CORE

VDD

CLK

SEL

CORE

VDD

DDR

VDD

CORE

VDD

DDR

VDD

DDR

VDD

DDR

DQ14

DDR

DQ15

DDR

DQM0

DDR

DQ8

DDR

DQ13

DDR

DQ11

DDR

DQ10

DDR

DQ12

CORE

GND

CORE

GND

CORE

GND

CORE

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

M

N

P

R

T

U

V

W

Y

AA

AB

1234567891011

HOST

CS0n

HOST

CS5n

GPIO3GPIO2GPIO

1

GPIO7GPIO6GPIO

5

GPIO

0

GPIO

4

UART0

RTS

UART0

TXD

UART1

RXD

UART0

CTS

UART0

RXD

UARTD

TXD

UARTD

RXD

UART1

TXD

TWI0

SDA

PWM2PWM1PWM

0

HOST

D12

HOST

D13

HOST

D14

HOSTD8HOSTD9HOST

D10

HOSTD4HOSTD5HOST

D6

HOSTD2HOSTD3HOST

WEn

HOSTD1HOST

D_EN

HOST

WAIT

HOST

D15

HOST

D11

HOST

D7

CF

INPACKn

HOST

A12

HOST

ALEnCFIORDnCFBVD2

HOST

INTnCFIOWRnCFCD1

HOST

A11

HOST

A10

HOST

A8

CF

RESETCFREGn

HOST

A6

CFWPHOSTA5HOST

A2

HOST

A7

HOST

A3

HOSTD0HOST

REn

HOST

DMARQ

HOSTWPCF

BVD1CFCD2CFWAITn

HOSTA4HOST

A1

HOST

A22

HOST

A21

HOST

VDD

HOST

A20

HOST

A19

CORE

VDD

HOST

A18

HOST

VDD

HOST

A17

HOST

A16

HOST

VDD

HOST

VDD

HOST

VDD

HOST

A15

HOST

A14

HOST

A13

HOST

VDD

HOST

A9

CORE

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

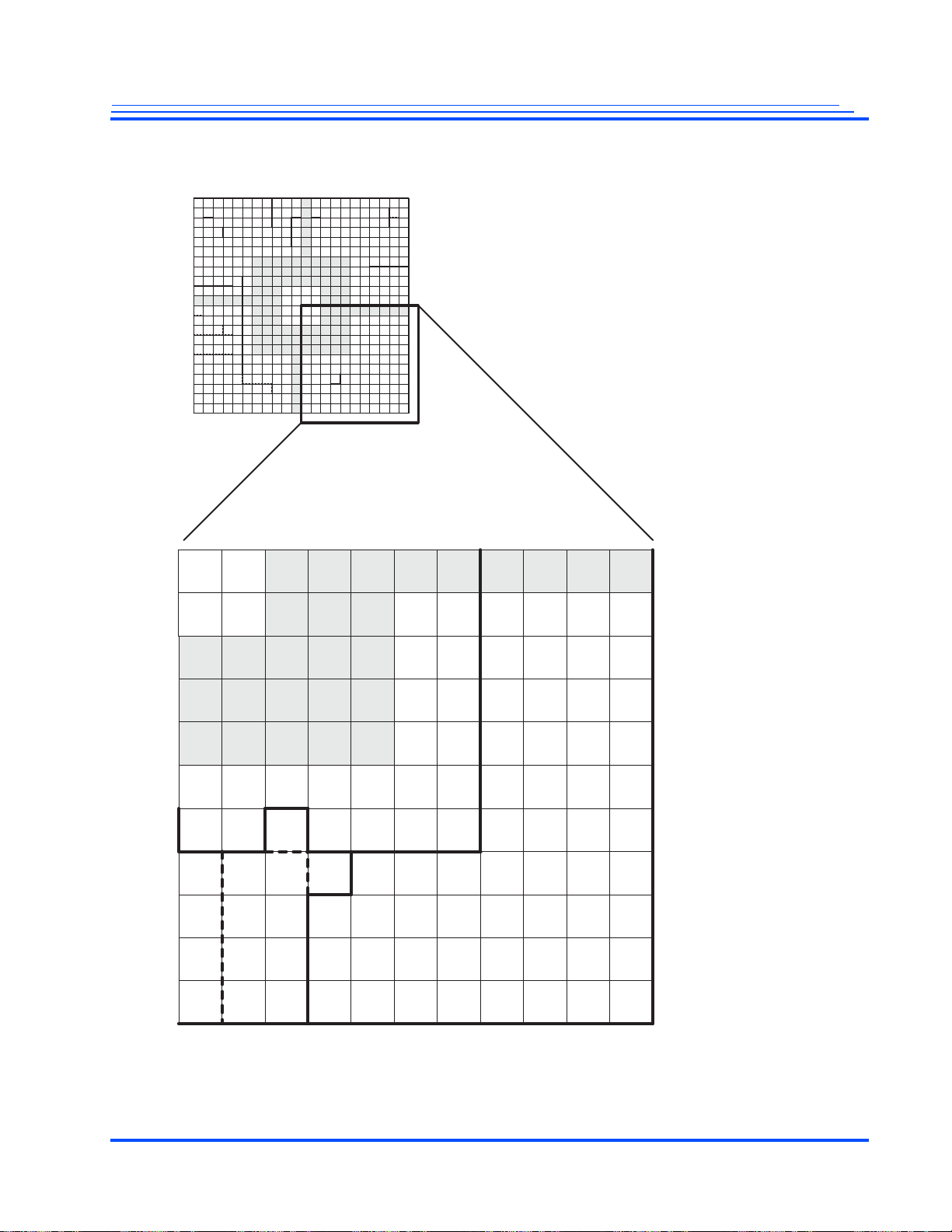

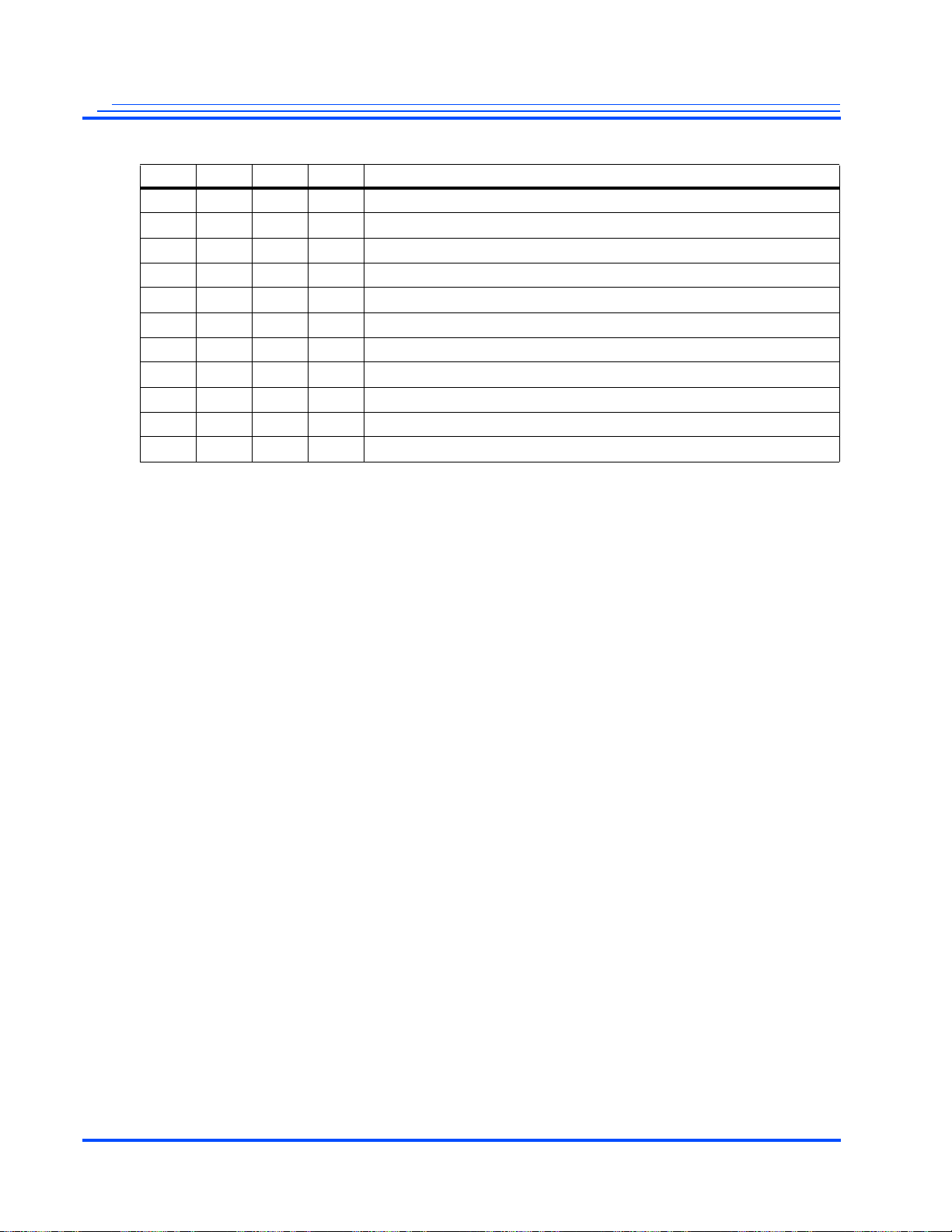

Figure 2-2 is a map of the upper-left quadrant.

Figure 2-2 Map of the Upper-left Quadrant (Top View)

Maxim Integrated Products Advance Information | 23

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

12 13 14 15 16 17 18 19 20 21 22

A

B

C

D

E

F

G

H

J

K

L

JTAG

TDO

TEST

JTAG

TAP_SEL

JTAG

TDI

JTAG

TRSTn

JTAG

TCK

JTAG

TMS

CFG

HOST1

CFG

HOST0

VID0

FIELD

VID0

OUTCLK

VID0

PIXCLK

VID0

VSYNC

VID0

HSYNC

VID0

D0

VID0D1VID0D5VID1

PIXCLK

VID0D2VID0

D6

VID1

OUTCLK

VID0D3VID0D7VID1

VSYNC

VID0D4VID1

FIELD

VID1

HSYNC

VID1D0VID1D4VID1

D7

VID1D1VID1D5VID01

MOSI

VID1D2VID1D6VID01

MCLK

VID1D3VID01

MSS

VID01

MISO

RESETn

CFG0CORE

VDD

VID01

VDD

AUD1

MCLK

AUD1

BCK

AUD1

LRCK

AUD1

IDAT

CORE

VDD

VID01

VDD

VID01

VDD

CORE

VDD

AUD

VDD

CORE

VDD

DDR

VDD

DDR

VDD

AUD

VDD

AUD0

ODAT1

AUD0

ODAT2

AUD0

MCLK

AUD0

BCK

DDR

VDD

DDR

DQ18

DDR

DQM2

DDR

DQ19

DDR

DQ20

DDR

DQM3

DDR

DQ23

AUD0

IDAT

AUD0

SPDIF

AUD0

LRCK

AUD0

ODAT0

DDR

DQS2n

DDR

DQS2

DDR

DQ17

DDR

DQ16

DDR

DQ21

DDR

DQ22

DDR

VDD

DDR

DQ26

DDR

DQ24

DDR

DQS3n

DDR

DQS3

CORE

GND

DDR

GND

DDR

GND

DDR

GND

CORE

GND

CORE

GND

VID01

GND

AUD

GND

AUD

GND

DDR

GND

DDR

GND

VID01

GND

1234567891011

A

B

C

D

E

F

G

H

J

K

L

CFG

3

CFG

2

VID23

MCLK

VID2D0VID2D1VID2D4VID2D6VID2

PIXCLK

ETH

RXERR

VID23

MISO

VID2D2VID2D5VID2D7VID2

FIELD

ETH

RXCLK

ETH

RXDV

VID23

MOSI

VID2D3VID2

VSYNC

VID23

D16

ETH

RXD7

ETH

RXD2

ETH

RXD1

VID23

MSS

VID2

HSYNC

VID3

D1

VID3D2VID3D6USB

XIN

USBDMUSB

DP

VID3D3VID3D7USBXOUSB

VBUS

USB

ID

VID3D0VID3

D4

USB

D_VBUS

USB

REXT

VID3D5VID23

D17

VID23

GPIO

USB

ANA_TST

ETH

RXD6

ETH

RXD3

ETH

RXD0

ETH

COL

ETH

RXD5

ETH

RXD4

ETH

MDCLK

ETH

CRS

ETH

TXEN

ETH

TXD4

ETH

TXD0

ETH

MDIO

ETH

TXERR

ETH

TXD5

ETH

TXD3

ETH

TXD2

ETH

TXD7

ETH

TXD6

ETH

TXCLK

ETH

TXD1

TWI0

SCL

SPI

MOSI

SPI

MCLK

SPI

MSSI

VID23

VDD

VID23

VDD

ETH

VDD

ENET

VDD

USB

AGND

USB

AGND

USB

AGND

USB

ACGND

CFG

1

VID23

VDD

USB

AVDD

USB

AVDD

USB

ACVDD

USB

DVDD

SPI

MISO

CORE

VDD

SPI

MSSO

ETH

GND

ETH

GND

VID23

GND

VID23

GND

CORE

GND

CORE

GND

USB

DGND

VID23

GND

VID01

GND

12 13 14 15 16 17 18 19 20 21 22

A

B

C

D

E

F

G

H

J

K

L

JTAG

TDO

TEST

JTAG

TAP_SEL

JTAG

TDI

JTAG

TRSTn

JTAG

TCK

JTAG

TMS

CFG

HOST1

CFG

HOST0

VID0

FIELD

VID0

OCLK

VID0

PIXCLK

VID0

VSYNC

VID0

HSYNC

VID0

D0

VID0D1VID0D5VID1

PIXCLK

VID0D2VID0D6VID1

OCLK

VID0D3VID0D7VID1

VSYNC

VID0D4VID1

FIELD

VID1

HSYNC

VID1D0VID1D4VID1

D7

VID1D1VID1D5VID01

MOSI

VID1D2VID1D6VID01

MCLK

VID1D3VID01

MSS

VID01

MISO

RESETn

CFG0CORE

VDD

VID01

VDD

AUD1

MCLK

AUD1

BCK

AUD1

LRCK

AUD1

IDAT

CORE

VDD

VID01

VDD

VID01

VDD

CORE

VDD

AUD

VDD

CORE

VDD

DDR

VDD

DDR

VDD

AUD

VDD

AUD0

ODAT1

AUD0

ODAT2

AUD0

MCLK

AUD0

BCK

DDR

VDD

DDR

DQ18

DDR

DQM2

DDR

DQ19

DDR

DQ20

DDR

DQM3

DDR

DQ23

AUD0

IDAT

AUD0

SPDIF

AUD0

LRCK

AUD0

ODAT0

DDR

DQS2n

DDR

DQS2

DDR

DQ17

DDR

DQ16

DDR

DQ21

DDR

DQ22

DDR

VDD

DDR

DQ26

DDR

DQ24

DDR

DQS3n

DDR

DQS3

CORE

GND

DDR

GND

DDR

GND

DDR

GND

CORE

GND

CORE

GND

VID01

GND

AUD

GND

AUD

GND

DDR

GND

DDR

GND

VID01

GND

12 13 14 15 16 17 18 19 20 21 22

W

Y

AA

AB

M

N

P

R

T

U

V

HOST

CS4n

HOST

CS3n

HOST

CS2n

HOST

CS1n

CLKINSDMMCCDSDMMC

D1

SDMMCWPSDMMC

D0

SDMMCD3SDMMC

CLK

DDR

BA0

DDR

WEn

DDRA1DDR

BA1

DDR

CASn

DDRA2DDR

A10

DDR

RASn

DDR

CKE

DDR

DQ5

DDR

DQ7

DDR

A12

DDRA6DDR

DQ0

DDRA8DDRA7DDR

A9

DDR

DQS0n

DDR

DQS0

DDR

DQ1

DDR

DQ3

DDR

DQ4

DDR

DQ2

SDMMCD2SDMMC

CMD

DDRA3DDRA0DDR

CSn

DDRA5DDRA4DDR

A11

DDR

VREF

DDR

DQ6

DDR

VDD

DDR

VDD

DDR

VDD

DDR

VDD

DDR

PADHI

DDR

DQ31

DDR

PADLO

DDR

DQ25

DDR

VDD

DDR

DQS1n

DDR

DQM1

DDR

DQ9

DDR

DQS1

DDR

DQ30

DDR

DQ28

DDR

DQ27

DDR

DQ29

DDR

CLK1

DDR

CLK1n

DDR

CLK0

DDR

CLK0n

HOST

VDD

CORE

VDD

PLL

VDD

CORE

VDD

CLK

SEL

CORE

VDD

DDR

VDD

CORE

VDD

DDR

VDD

DDR

VDD

DDR

DQ14

DDR

DQ15

DDR

DQM0

DDR

DQ8

DDR

DQ13

DDR

DQ11

DDR

DQ10

DDR

DQ12

CORE

GND

CORE

GND

CORE

GND

CORE

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

M

N

P

R

T

U

V

W

Y

AA

AB

1234567891011

HOST

CS0n

HOST

CS5n

GPIO3GPIO2GPIO

1

GPIO7GPIO6GPIO

5

GPIO

0

GPIO

4

UART0

RTS

UART0

TXD

UART1

RXD

UART0

CTS

UART0

RXD

UARTD

TXD

UARTD

RXD

UART1

TXD

TWI0

SDA

PWM2PWM1PWM

0

HOST

D12

HOST

D13

HOST

D14

HOSTD8HOSTD9HOST

D10

HOSTD4HOSTD5HOST

D6

HOSTD2HOSTD3HOST

WEn

HOSTD1HOST

D_EN

HOST

WAIT

HOST

D15

HOST

D11

HOST

D7

CF

INPACKn

HOST

A12

HOST

ALEnCFIORDnCFBVD2

HOST

INTnCFIOWRnCFCD1

HOST

A11

HOST

A10

HOST

A8

CF

RESETCFREGn

HOST

A6

CFWPHOSTA5HOST

A2

HOST

A7

HOST

A3

HOSTD0HOST

REn

HOST

DMARQ

HOSTWPCF

BVD1CFCD2CFWAITn

HOSTA4HOST

A1

HOST

A22

HOST

A21

HOST

VDD

HOST

A20

HOST

A19

CORE

VDD

HOST

A18

HOST

VDD

HOST

A17

HOST

A16

HOST

VDD

HOST

VDD

HOST

VDD

HOST

A15

HOST

A14

HOST

A13

HOST

VDD

HOST

A9

CORE

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

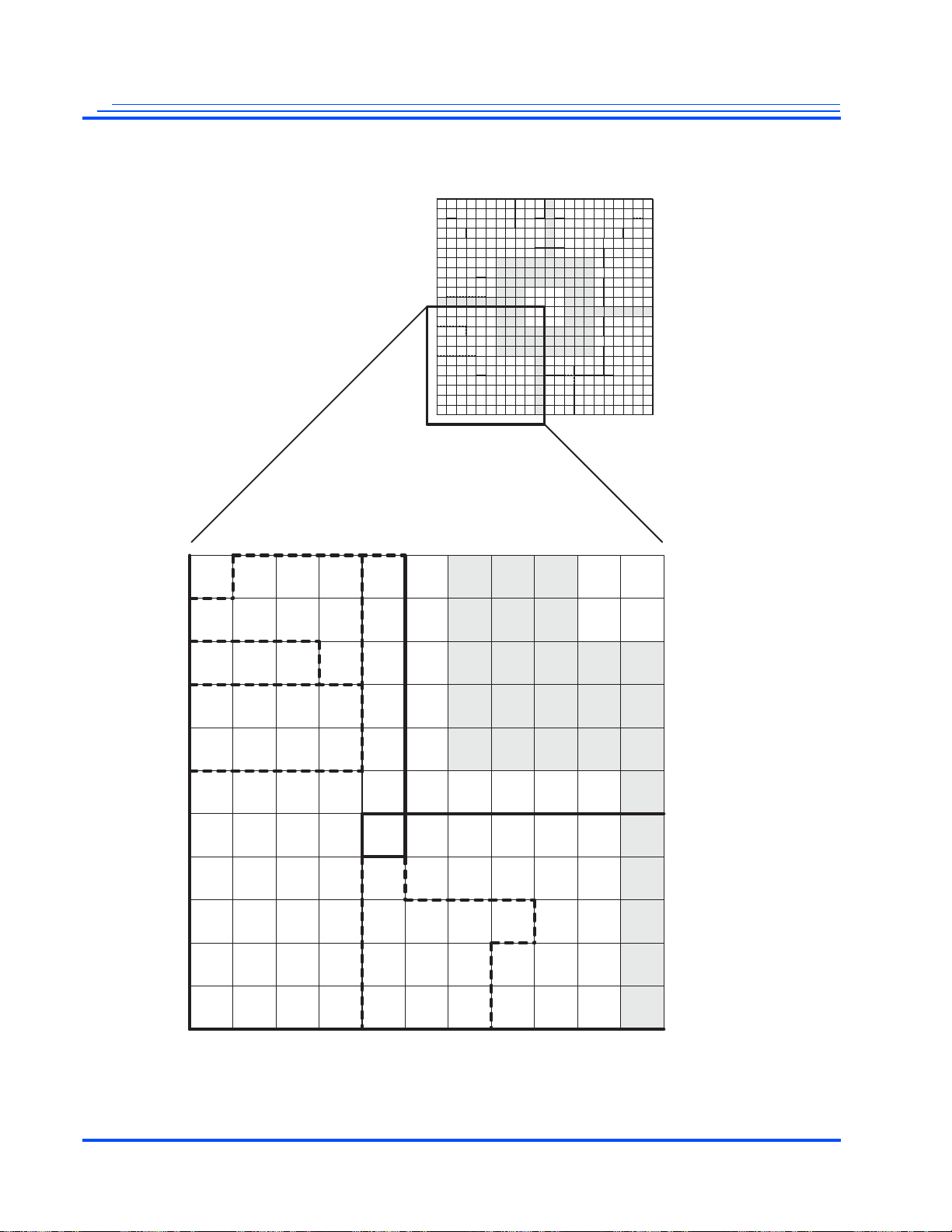

Figure 2-3 is a map of the upper-right quadrant.

24 | Advance Information Maxim Integrated Products

Figure 2-3 Map of the Upper-Right Quadrant (Top View)

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

12 13 14 15 16 17 18 19 20 21 22

W

Y

AA

AB

M

N

P

R

T

U

V

HOST

CS4n

HOST

CS3n

HOST

CS2n

HOST

CS1n

CLK

IN

SDMMCCDSDMMC

D1

SDMMCWPSDMMC

D0

SDMMCD3SDMMC

CLK

DDR

BA0

DDR

WEn

DDRA1DDR

BA1

DDR

CASn

DDRA2DDR

A10

DDR

RASn

DDR

CKE

DDR

DQ5

DDR

DQ7

DDR

A12

DDRA6DDR

DQ0

DDRA8DDRA7DDR

A9

DDR

DQS0n

DDR

DQS0

DDR

DQ1

DDR

DQ3

DDR

DQ4

DDR

DQ2

SDMMCD2SDMMC

CMD

DDRA3DDRA0DDR

CSn

DDRA5DDRA4DDR

A11

DDR

VREF

DDR

DQ6

DDR

VDD

DDR

VDD

DDR

VDD

DDR

VDD

DDR

PADHI

DDR

DQ31

DDR

PADLO

DDR

DQ25

DDR

VDD

DDR

DQS1n

DDR

DQM1

DDR

DQ9

DDR

DQS1

DDR

DQ30

DDR

DQ28

DDR

DQ27

DDR

DQ29

DDR

CLK1

DDR

CLK1n

DDR

CLK0

DDR

CLK0n

HOST

VDD

CORE

VDD

PLL

VDD

CORE

VDD

CLK

SEL

CORE

VDD

DDR

VDD

CORE

VDD

DDR

VDD

DDR

VDD

DDR

DQ14

DDR

DQ15

DDR

DQM0

DDR

DQ8

DDR

DQ13

DDR

DQ11

DDR

DQ10

DDR

DQ12

CORE

GND

CORE

GND

CORE

GND

CORE

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

1234567891011

A

B

C

D

E

F

G

H

J

K

L

CFG

3

CFG

2

VID23

MCLK

VID2D0VID2D1VID2D4VID2D6VID2

PIXCLK

ETH

RXERR

VID23

MISO

VID2D2VID2D5VID2D7VID2

FIELD

ETH

RXCLK

ETH

RXDV

VID23

MOSI

VID2D3VID2

VSYNC

VID23

D16

ETH

RXD7

ETH

RXD2

ETH

RXD1

VID23

MSS

VID2

HSYNC

VID3

D1

VID3D2VID3D6USB

XIN

USBDMUSB

DP

VID3D3VID3D7USBXOUSB

VBUS

USB

ID

VID3D0VID3

D4

USB

D_VBUS

USB

REXT

VID3D5VID23

D17

VID23

GPIO

USB

ANA_TST

ETH

RXD6

ETH

RXD3

ETH

RXD0

ETH

COL

ETH

RXD5

ETH

RXD4

ETH

MDCLK

ETH

CRS

ETH

TXEN

ETH

TXD4

ETH

TXD0

ETH

MDIO

ETH

TXERR

ETH

TXD5

ETH

TXD3

ETH

TXD2

ETH

TXD7

ETH

TXD6

ETH

TXCLK

ETH

TXD1

TWI0

SCL

SPI

MOSI

SPI

MCLK

SPI

MSSI

VID23

VDD

VID23

VDD

ETH

VDD

ENET

VDD

USB

AGND

USB

AGND

USB

AGND

USB

ACGND

CFG

1

VID23

VDD

USB

AVDD

USB

AVDD

USB

ACVDD

USB

DVDD

SPI

MISO

CORE

VDD

SPI

MSSO

ETH

GND

ETH

GND

VID23

GND

VID23

GND

CORE

GND

CORE

GND

USB

DGND

VID23

GND

VID01

GND

12 13 14 15 16 17 18 19 20 21 22

A

B

C

D

E

F

G

H

J

K

L

JTAG

TDO

TEST

JTAG

TAP_SEL

JTAG

TDI

JTAG

TRSTn

JTAG

TCK

JTAG

TMS

CFG

HOST1

CFG

HOST0

VID0

FIELD

VID0

OCLK

VID0

PIXCLK

VID0

VSYNC

VID0

HSYNC

VID0

D0

VID0D1VID0D5VID1

PIXCLK

VID0D2VID0D6VID1

OCLK

VID0D3VID0D7VID1

VSYNC

VID0D4VID1

FIELD

VID1

HSYNC

VID1D0VID1D4VID1

D7

VID1D1VID1D5VID01

MOSI

VID1D2VID1D6VID01

MCLK

VID1D3VID01

MSS

VID01

MISO

RESETn

CFG0CORE

VDD

VID01

VDD

AUD1

MCLK

AUD1

BCK

AUD1

LRCK

AUD1

IDAT

CORE

VDD

VID01

VDD

VID01

VDD

CORE

VDD

AUD

VDD

CORE

VDD

DDR

VDD

DDR

VDD

AUD

VDD

AUD0

ODAT1

AUD0

ODAT2

AUD0

MCLK

AUD0

BCK

DDR

VDD

DDR

DQ18

DDR

DQM2

DDR

DQ19

DDR

DQ20

DDR

DQM3

DDR

DQ23

AUD0

IDAT

AUD0

SPDIF

AUD0

LRCK

AUD0

ODAT0

DDR

DQS2n

DDR

DQS2

DDR

DQ17

DDR

DQ16

DDR

DQ21

DDR

DQ22

DDR

VDD

DDR

DQ26

DDR

DQ24

DDR

DQS3n

DDR

DQS3

CORE

GND

DDR

GND

DDR

GND

DDR

GND

CORE

GND

CORE

GND

VID01

GND

AUD

GND

AUD

GND

DDR

GND

DDR

GND

VID01

GND

12 13 14 15 16 17 18 19 20 21 22

W

Y

AA

AB

M

N

P

R

T

U

V

HOST

CS4n

HOST

CS3n

HOST

CS2n

HOST

CS1n

CLKINSDMMCCDSDMMC

D1

SDMMCWPSDMMC

D0

SDMMCD3SDMMC

CLK

DDR

BA0

DDR

WEn

DDRA1DDR

BA1

DDR

CASn

DDRA2DDR

A10

DDR

RASn

DDR

CKE

DDR

DQ5

DDR

DQ7

DDR

A12

DDRA6DDR

DQ0

DDRA8DDRA7DDR

A9

DDR

DQS0n

DDR

DQS0

DDR

DQ1

DDR

DQ3

DDR

DQ4

DDR

DQ2

SDMMCD2SDMMC

CMD

DDRA3DDRA0DDR

CSn

DDRA5DDRA4DDR

A11

DDR

VREF

DDR

DQ6

DDR

VDD

DDR

VDD

DDR

VDD

DDR

VDD

DDR

PADHI

DDR

DQ31

DDR

PADLO

DDR

DQ25

DDR

VDD

DDR

DQS1n

DDR

DQM1

DDR

DQ9

DDR

DQS1

DDR

DQ30

DDR

DQ28

DDR

DQ27

DDR

DQ29

DDR

CLK1

DDR

CLK1n

DDR

CLK0

DDR

CLK0n

HOST

VDD

CORE

VDD

PLL

VDD

CORE

VDD

CLK

SEL

CORE

VDD

DDR

VDD

CORE

VDD

DDR

VDD

DDR

VDD

DDR

DQ14

DDR

DQ15

DDR

DQM0

DDR

DQ8

DDR

DQ13

DDR

DQ11

DDR

DQ10

DDR

DQ12

CORE

GND

CORE

GND

CORE

GND

CORE

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

DDR

GND

M

N

P

R

T

U

V

W

Y

AA

AB

1234567891011

HOST

CS0n

HOST

CS5n

GPIO3GPIO2GPIO

1

GPIO7GPIO6GPIO

5

GPIO

0

GPIO

4

UART0

RTS

UART0

TXD

UART1

RXD

UART0

CTS

UART0

RXD

UARTD

TXD

UARTD

RXD

UART1

TXD

TWI0

SDA

PWM2PWM1PWM

0

HOST

D12

HOST

D13

HOST

D14

HOSTD8HOSTD9HOST

D10

HOSTD4HOSTD5HOST

D6

HOSTD2HOSTD3HOST

WEn

HOSTD1HOST

D_EN

HOST

WAIT

HOST

D15

HOST

D11

HOST

D7

CF

INPACKn

HOST

A12

HOST

ALEnCFIORDnCFBVD2

HOST

INTnCFIOWRnCFCD1

HOST

A11

HOST

A10

HOST

A8

CF

RESETCFREGn

HOST

A6

CFWPHOSTA5HOST

A2

HOST

A7

HOST

A3

HOSTD0HOST

REn

HOST

DMARQ

HOSTWPCF

BVD1CFCD2CFWAITn

HOSTA4HOST

A1

HOST

A22

HOST

A21

HOST

VDD

HOST

A20

HOST

A19

CORE

VDD

HOST

A18

HOST

VDD

HOST

A17

HOST

A16

HOST

VDD

HOST

VDD

HOST

VDD

HOST

A15

HOST

A14

HOST

A13

HOST

VDD

HOST

A9

CORE

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

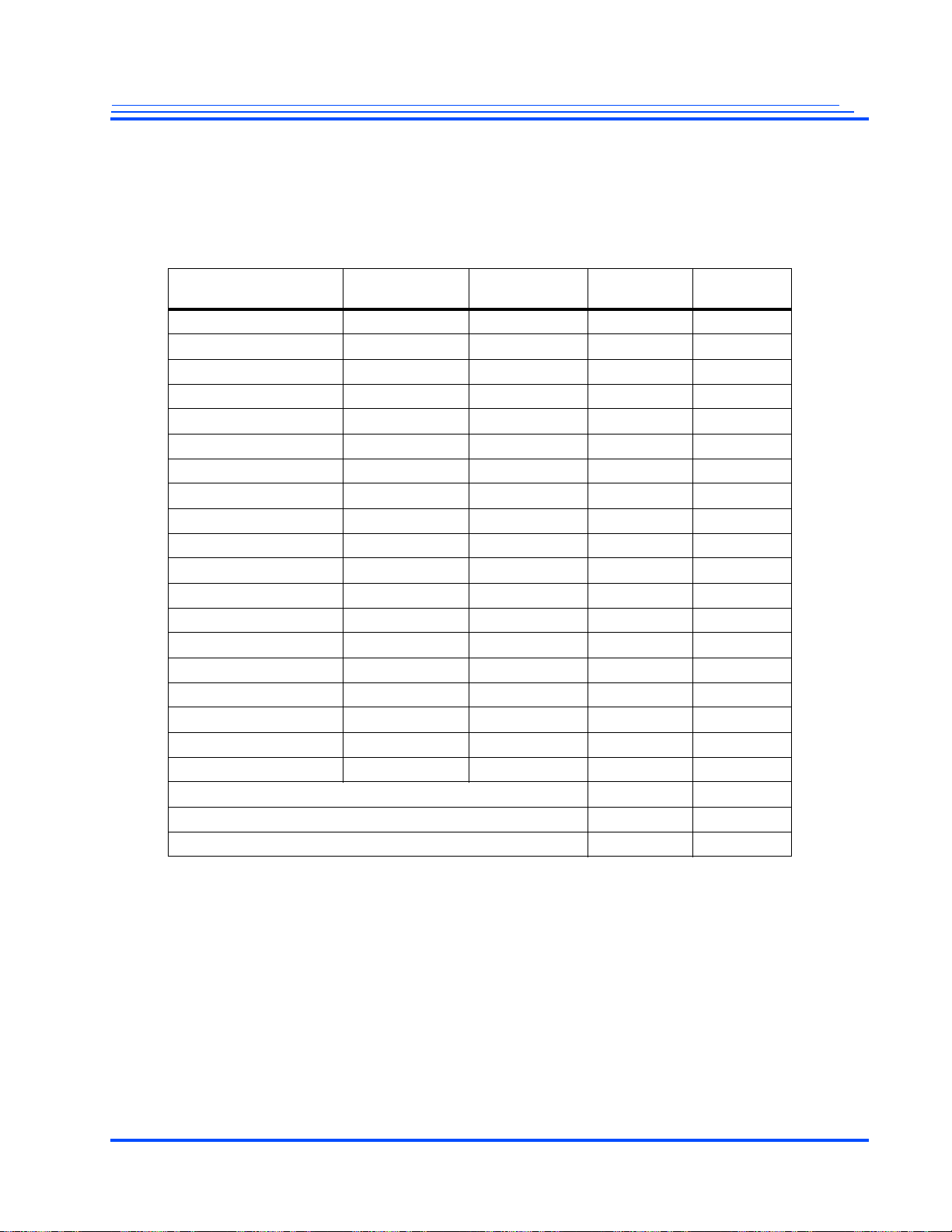

Figure 2-4 is a map of the lower-right quadrant.

Figure 2-4 Map of the Lower-Right Quadrant (Top View)

Maxim Integrated Products Advance Information | 25

MG3500/MG2580 HD H.264 Codec SoC Data Sheet

M

N

P

R

T

U

V

W

Y

AA

AB

1234567891011

HOST

CS0n

HOST

CS5n

GPIO3GPIO2GPIO

1

GPIO7GPIO6GPIO

5

GPIO

0

GPIO

4

UART0

RTS

UART0

TXD

UART1

RXD

UART0

CTS

UART0

RXD

UARTD

TXD

UARTD

RXD

UART1

TXD

TWI0

SDA

PWM2PWM1PWM

0

HOST

D12

HOST

D13

HOST

D14

HOSTD8HOSTD9HOST

D10

HOSTD4HOSTD5HOST

D6

HOSTD2HOSTD3HOST

WEn

HOSTD1HOST

D_EN

HOST

WAIT

HOST

D15

HOST

D11

HOST

D7

CF

INPACKn

HOST

A12

HOST

ALEnCFIORDnCFBVD2

HOST

INTnCFIOWRnCFCD1

HOST

A11

HOST

A10

HOST

A8

CF

RESETCFREGn

HOST

A6

CFWPHOSTA5HOST

A2

HOST

A7

HOST

A3

HOSTD0HOST

REn

HOST

DMARQ

HOSTWPCF

BVD1CFCD2CFWAITn

HOSTA4HOST

A1

HOST

A22

HOST

A21

HOST

VDD

HOST

A20

HOST

A19

CORE

VDD

HOST

A18

HOST

VDD

HOST

A17

HOST

A16

HOST

VDD

HOST

VDD

HOST

VDD

HOST

A15

HOST

A14

HOST

A13

HOST

VDD

HOST

A9

CORE

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

HOST

GND

1234567891011

A

B

C

D

E

F

G

H

J

K

L

CFG

3

CFG

2

VID23

MCLK

VID2D0VID2D1VID2D4VID2D6VID2